# **TUSB3200A**USB Streaming Controller (STC)

## Data Manual

#### **IMPORTANT NOTICE**

Texas Instruments Incorporated and its subsidiaries (TI) reserve the right to make corrections, modifications, enhancements, improvements, and other changes to its products and services at any time and to discontinue any product or service without notice. Customers should obtain the latest relevant information before placing orders and should verify that such information is current and complete. All products are sold subject to TI's terms and conditions of sale supplied at the time of order acknowledgment.

TI warrants performance of its hardware products to the specifications applicable at the time of sale in accordance with TI's standard warranty. Testing and other quality control techniques are used to the extent TI deems necessary to support this warranty. Except where mandated by government requirements, testing of all parameters of each product is not necessarily performed.

TI assumes no liability for applications assistance or customer product design. Customers are responsible for their products and applications using TI components. To minimize the risks associated with customer products and applications, customers should provide adequate design and operating safeguards.

TI does not warrant or represent that any license, either express or implied, is granted under any TI patent right, copyright, mask work right, or other TI intellectual property right relating to any combination, machine, or process in which TI products or services are used. Information published by TI regarding third-party products or services does not constitute a license from TI to use such products or services or a warranty or endorsement thereof. Use of such information may require a license from a third party under the patents or other intellectual property of the third party, or a license from TI under the patents or other intellectual property of TI.

Reproduction of information in TI data books or data sheets is permissible only if reproduction is without alteration and is accompanied by all associated warranties, conditions, limitations, and notices. Reproduction of this information with alteration is an unfair and deceptive business practice. TI is not responsible or liable for such altered documentation.

Resale of TI products or services with statements different from or beyond the parameters stated by TI for that product or service voids all express and any implied warranties for the associated TI product or service and is an unfair and deceptive business practice. TI is not responsible or liable for any such statements.

Mailing Address:

Texas Instruments

Post Office Box 655303

Dallas, Texas 75265

Copyright © 2001, Texas Instruments Incorporated

## **Contents**

| Section |        | Title     |                                                             |     |  |  |

|---------|--------|-----------|-------------------------------------------------------------|-----|--|--|

| 1       | Introd | duction . |                                                             | 1–1 |  |  |

|         | 1.1    | Feature   | s                                                           | 1–1 |  |  |

|         | 1.2    | Function  | nal Block Diagram                                           | 1–3 |  |  |

|         | 1.3    | Termina   | al Assignments – Normal Mode                                | 1–4 |  |  |

|         | 1.4    | Termina   | al Assignments – External MCU Mode                          | 1–4 |  |  |

|         | 1.5    |           | g Information                                               |     |  |  |

|         | 1.6    | Termina   | al Functions – Normal Mode                                  | 1–5 |  |  |

|         | 1.7    | Termina   | al Functions – External MCU Mode                            | 1–7 |  |  |

|         | 1.8    | Device    | Operation Modes                                             | 1–9 |  |  |

|         | 1.9    | Termina   | al Assignments for Codec Port Interface Modes               | 1–9 |  |  |

| 2       | Desci  |           |                                                             |     |  |  |

|         | 2.1    | Archited  | ctural Overview                                             | 2–1 |  |  |

|         |        | 2.1.1     | Oscillator and PLL                                          | 2–1 |  |  |

|         |        | 2.1.2     | Clock Generator and Sequencer Logic                         | 2–1 |  |  |

|         |        | 2.1.3     | Adaptive Clock Generator (ACG)                              | 2–1 |  |  |

|         |        | 2.1.4     | USB Transceiver                                             | 2–1 |  |  |

|         |        | 2.1.5     | USB Serial Interface Engine (SIE)                           | 2–1 |  |  |

|         |        | 2.1.6     | USB Buffer Manager (UBM)                                    | 2–2 |  |  |

|         |        | 2.1.7     | USB Frame Timer                                             | 2–2 |  |  |

|         |        | 2.1.8     | USB Suspend and Resume Logic                                |     |  |  |

|         |        | 2.1.9     | MCU Core                                                    | 2–2 |  |  |

|         |        | 2.1.10    | MCU Memory                                                  | 2–2 |  |  |

|         |        | 2.1.11    | USB Endpoint Configuration Blocks and Endpoint Buffer Space | 2–2 |  |  |

|         |        | 2.1.12    | DMA Controller                                              |     |  |  |

|         |        | 2.1.13    | Codec Port Interface                                        | 2–3 |  |  |

|         |        | 2.1.14    | I <sup>2</sup> C Interface                                  | 2–3 |  |  |

|         |        | 2.1.15    | Pulse Width Modulation (PWM) Output                         | 2–3 |  |  |

|         |        | 2.1.16    | General-Purpose IO Ports (GPIO)                             | 2–3 |  |  |

|         |        | 2.1.17    | Interrupt Logic                                             |     |  |  |

|         |        | 2.1.18    | Reset Logic                                                 | 2–3 |  |  |

|         | 2.2    | Device    | Operation                                                   | 2–3 |  |  |

|         |        | 2.2.1     | Clock Generation                                            | 2–3 |  |  |

|         |        | 2.2.2     | Device Initialization                                       | 2–4 |  |  |

|         |        | 2.2.3     | USB Enumeration                                             | 2–5 |  |  |

|         |        | 2.2.4     | USB Reset                                                   | 2–5 |  |  |

|         |        | 2.2.5     | USB Suspend and Resume Modes                                | 2–6 |  |  |

|    |         | 2.2.6      | Power Supply Sequencing                                                                     | 2–6  |

|----|---------|------------|---------------------------------------------------------------------------------------------|------|

|    |         | 2.2.7      | USB Transfers                                                                               | 2–7  |

|    |         | 2.2.8      | Adaptive Clock Generator (ACG)                                                              | 2-14 |

|    |         | 2.2.9      | Microcontroller Unit                                                                        | 2-16 |

|    |         | 2.2.10     | External MCU Mode Operation                                                                 | 2-16 |

|    |         | 2.2.11     | Interrupt Logic                                                                             | 2-16 |

|    |         | 2.2.12     | DMA Controller                                                                              | 2-17 |

|    |         | 2.2.13     | Codec Port Interface                                                                        | 2–17 |

|    |         | 2.2.14     | I <sup>2</sup> C Interface                                                                  | 2–22 |

| 3  | Electri | cal Speci  | ifications                                                                                  | 3–1  |

|    | 3.1     | Absolute   | Maximum Ratings Over Operating Temperature Ranges .                                         | 3–1  |

|    | 3.2     |            | ended Operating Conditions                                                                  | 3–1  |

|    | 3.3     |            | Characteristics Over Recommended                                                            |      |

|    |         |            | g Conditions                                                                                | 3–2  |

|    | 3.4     | •          | haracteristics                                                                              | 3–3  |

|    |         | 3.4.1      | Clock and Control Signals Over Recommended Operating Conditions                             | 3–3  |

|    |         | 3.4.2      | USB Transceiver Signals Over Recommended Operating Conditions                               | 3–3  |

|    |         | 3.4.3      | Codec Port Interface Signals (AC '97 Modes)                                                 | 3–4  |

|    |         | 3.4.4      | Codec Port Interface Signals (I <sup>2</sup> S Modes) Over Recommended Operating Conditions | 3–5  |

|    |         | 3.4.5      | Codec Port Interface Signals (General-Purpose Mode) Over Recommended Operating Conditions   | 3–5  |

|    |         | 3.4.6      | I <sup>2</sup> C Interface Signals Over Recommended                                         |      |

| _  |         |            | Operating Conditions                                                                        | 3–6  |

| 4  | Applic  | ation Info | ormation                                                                                    | 4–1  |

| Аp | pendix  |            |                                                                                             |      |

| Α  | MCU     | Memory a   | and Memory Mapped Registers                                                                 | A-1  |

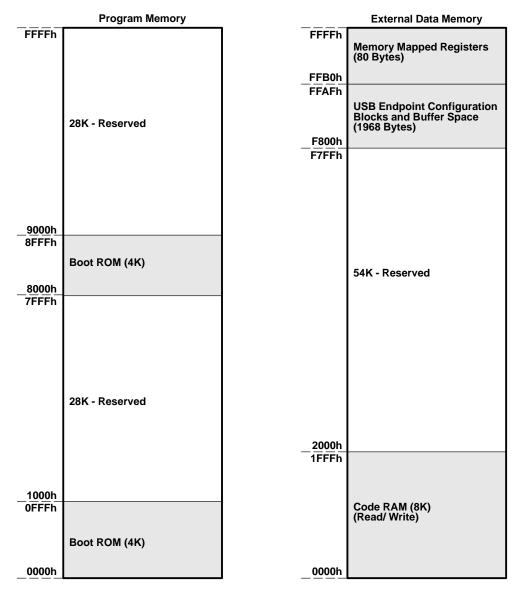

|    | A.1     | MCU Me     | emory Space                                                                                 | A-1  |

|    | A.2     | Internal I | Data Memory                                                                                 | A-2  |

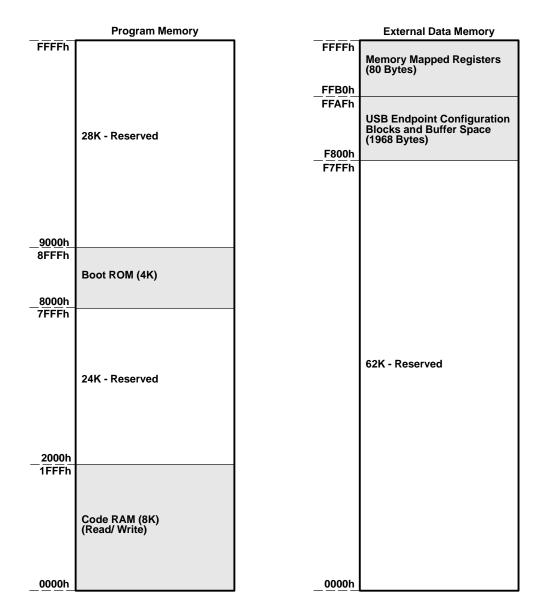

|    | A.3     |            | MCU Mode Memory Space                                                                       | A-3  |

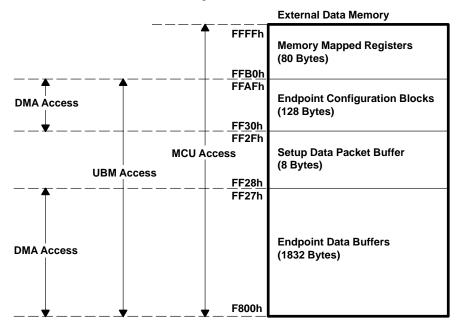

|    | A.4     | USB End    | dpoint Configuration Blocks and Data Buffers Space                                          | A-4  |

|    | A.5     | Memory-    | -Mapped Registers                                                                           | A-15 |

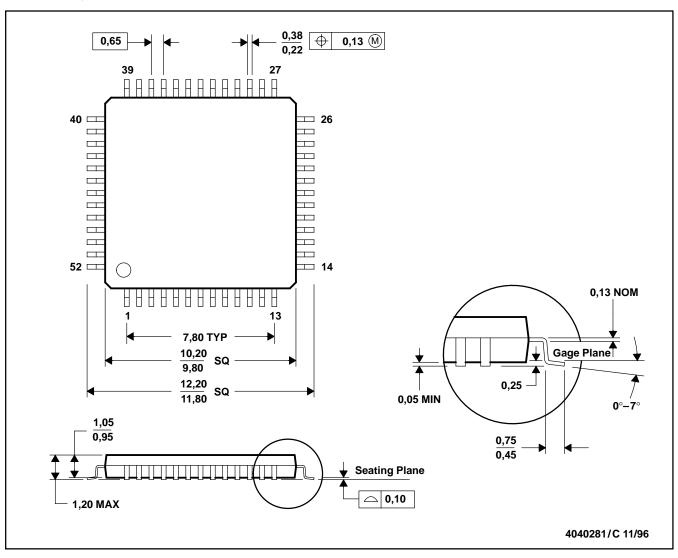

| В  | Mecha   | anical Da  | ta                                                                                          | B-1  |

## **List of Illustrations**

| Figu | ure Title                                                     | Page |

|------|---------------------------------------------------------------|------|

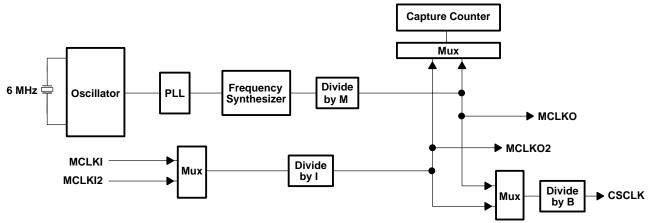

| 2–1  | Adaptive Clock Generator                                      | 2–15 |

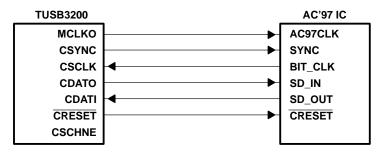

| 2–2  | Connection of the TUSB3200A to an AC '97 Codec                | 2–19 |

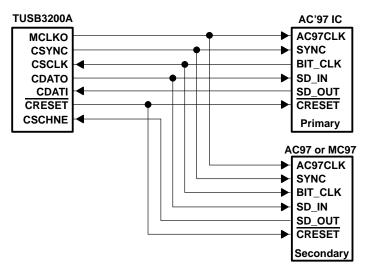

| 2–3  | Connection of the TUSB3200A to Multiple AC '97 Codecs         | 2–20 |

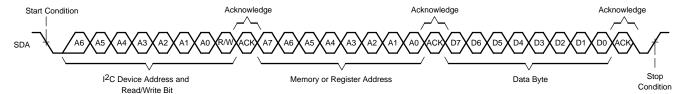

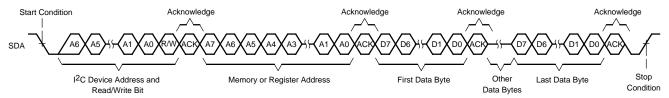

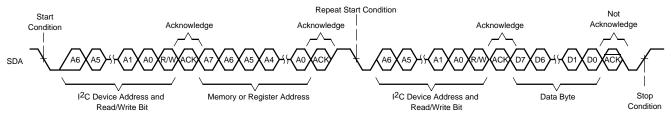

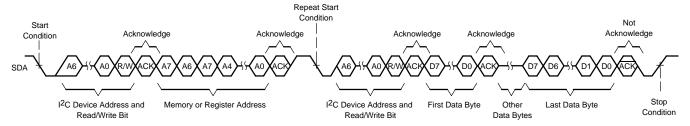

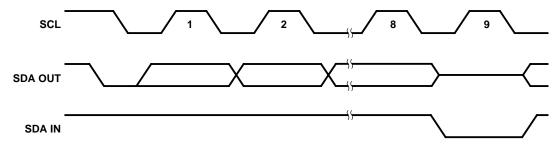

| 2–4  | Single Byte Write Transfer                                    | 2–23 |

| 2–5  | Multiple Byte Write Transfer                                  | 2–23 |

| 2–6  | Single Byte Read Transfer                                     | 2–23 |

| 2–7  | Multiple Byte Read Transfer                                   | 2–24 |

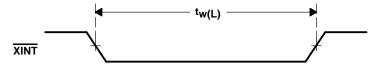

| 3–1  | External Interrupt Timing Waveform                            | 3–3  |

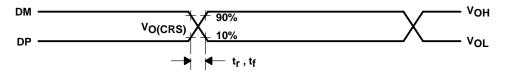

| 3–2  | USB Differential Driver Timing Waveform                       | 3–3  |

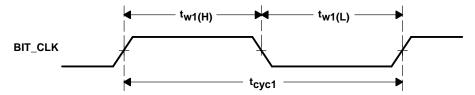

| 3–3  | BIT_CLK Timing Waveform                                       | 3–4  |

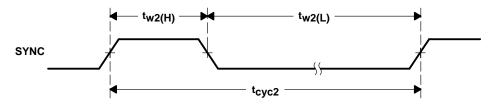

| 3–4  | SYNC Timing Waveform                                          | 3–4  |

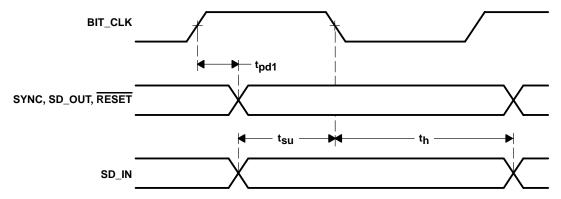

| 3–5  | Delay Time, Setup Time, and Hold Time Timing Waveforms        | 3–4  |

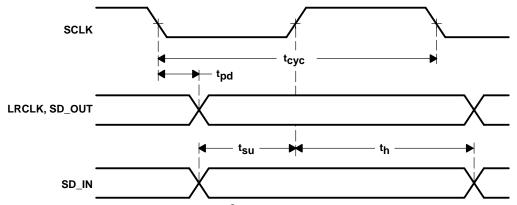

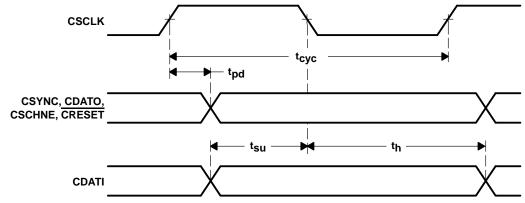

| 3–6  | I <sup>2</sup> S Mode Timing Waveforms                        | 3–5  |

| 3–7  | General-Purpose Mode Timing Waveforms                         | 3–5  |

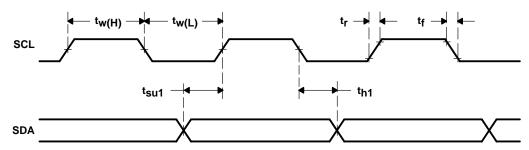

| 3–8  | SCL and SDA Timing Waveforms                                  | 3–6  |

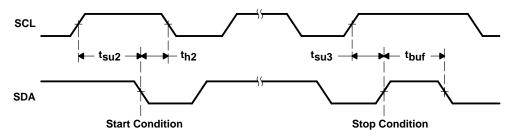

| 3–9  | Start and Stop Conditions Timing Waveforms                    | 3–6  |

| 3–10 | O Acknowledge Timing Waveform                                 | 3–6  |

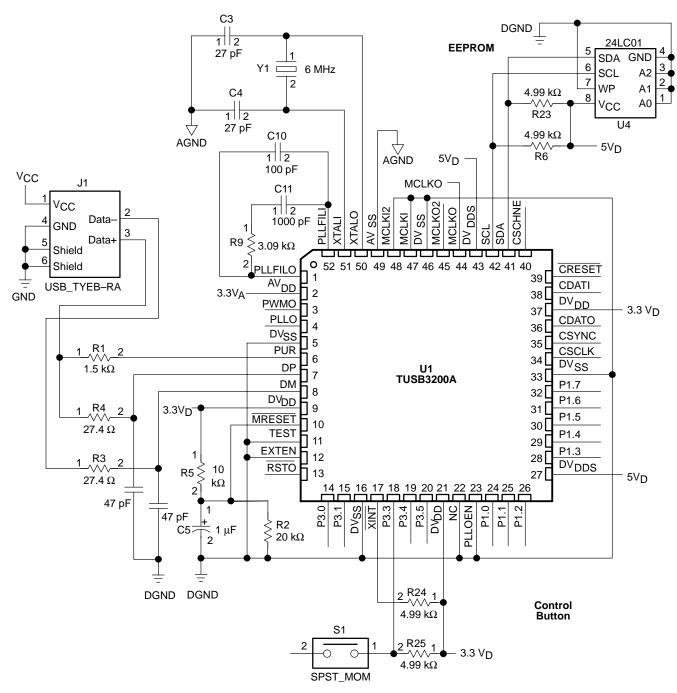

| 4–1  | Typical TUSB3200A Device Connections                          | 4–1  |

| A-1  | Boot Loader Memory Map                                        | 4–1  |

| 4–1  | Normal Operating Mode Memory Map                              | 4–1  |

| 4–1  | USB Endpoint Configuration Blocks and Buffer Space Memory Map | 4–1  |

## **List of Tables**

| Tabl | e Title                                                                     | Page |

|------|-----------------------------------------------------------------------------|------|

| 2–1  | EEPROM Header                                                               | 2–4  |

| 2–2  | USB Device Information                                                      | 2–5  |

| 2–3  | Terminal Assignments for Codec Port Interface AC '97 10 Mode                | 2–18 |

| 2–4  | Terminal Assignments for Codec Port Interface AC '97 20 Mode                | 2–19 |

| 2–5  | Terminal Assignments for Codec Port Interface I <sup>2</sup> S Modes        | 2–20 |

| 2–6  | SLOT Assignments for Codec Port Interface I <sup>2</sup> S Mode (Output)    | 2–21 |

| 2–7  | SLOT Assignments for Codec Port Interface I <sup>2</sup> S Mode (Input)     | 2–21 |

| 2–8  | Channel Order for 6-Channel Application in I <sup>2</sup> S Mode 4 (Output) | 2–21 |

| 2–9  | Terminal Assignments for Codec Port Interface General-Purpose Mode          | 2-22 |

#### 1 Introduction

The TUSB3200A integrated circuit (IC) is a universal serial bus (USB) peripheral interface device designed specifically for applications that require isochronous data streaming. Applications include digital speakers, which require the streaming of digital audio data between the host PC and the speaker system via the USB connection. The TUSB3200A device is fully compatible with the USB Specification Version 1.1 and the USB Audio Class Specification.

The TUSB3200A uses a standard 8052 microcontroller unit (MCU) core with on-chip memory. The MCU memory includes 4K bytes of program memory ROM that contains a boot loader program. At initialization, the boot loader program downloads the application program code to an 8K RAM from a nonvolatile memory on the printed-circuit board (PCB). The MCU handles all USB control, interrupt and bulk endpoint transactions. In addition, the MCU can handle USB isochronous endpoint transactions.

The USB interface includes an integrated transceiver that supports 12 Mb/s (full speed) data transfers. In addition to the USB control endpoint, support is provided for up to seven in endpoints and seven out endpoints. The USB endpoints are fully configurable by the MCU application code using a set of endpoint configuration blocks that reside in on-chip RAM. All USB data transfer types are supported.

The TUSB3200A device also includes a codec port interface (C-Port) that can be configured to support several industry standard serial interface protocols. These protocols include the audio codec (AC) '97 Revision 1.X, the audio codec (AC) '97 Revision 2.X and several Inter-IC sound (I<sup>2</sup>S) modes.

A direct memory access (DMA) controller with four channels is provided for streaming the USB isochronous data packets to/from the codec port interface. Each DMA channel can support one USB isochronous endpoint.

An on-chip phase lock loop (PLL) and adaptive clock generator (ACG) provide support for the USB synchronization modes, which include asynchronous, synchronous and adaptive.

Other on-chip MCU peripherals include an Inter-IC control (I<sup>2</sup>C) serial interface, two general-purpose input/output (GPIO) ports, and a pulse width modulation (PWM) output.

The TUSB3200A device is implemented in a 3.3-V  $0.25\,\mu m$  CMOS technology. In addition, the use of 5-V compatible input/output buffers for the codec port interface allows the TUSB3200A device to be connected to either 3.3-V or 5-V codec devices.

#### 1.1 Features

- Universal Serial Bus (USB)

- USB Specification version 1.1 compatible

- USB Audio Class Specification 1.0 compatible

- Integrated USB transceiver

- Supports 12 Mb/s data rate (full speed)

- Supports suspend/resume and remote wake-up

- Supports control, interrupt, bulk and isochronous data transfer types

- Supports up to a total of 7 in endpoints and 7 out endpoints in addition to the control endpoint

- Data transfer type, data buffer size, single or double buffering is programmable for each endpoint

- On-chip adaptive clock generator (ACG) supports asynchronous, synchronous and adaptive synchronization modes for isochronous endpoints

- To support synchronization for streaming USB audio data, the ACG can be used to generate the master clock for the codec

#### Micro-Controller Unit (MCU)

- Standard 8052 8-bit core

- 4K Bytes of program memory ROM that contains a boot loader program that loads the application firmware from external EEPROM

- 8K Bytes of program memory RAM which is loaded by the boot loader program

- 256 Bytes of internal data memory RAM

- Two GPIO ports

- MCU handles all USB control, interrupt and bulk endpoint transfers

#### DMA Controller

- Four DMA channels to support streaming USB audio data to/from the codec port interface

- Each channel can support a single USB isochronous endpoint

- For I<sup>2</sup>S modes, either a single or multiple USB isochronous endpoints can be used to support multiple DACs/ADCs

#### Codec Port Interface

- Configurable to support AC'97 1.X, AC'97 2.X or I<sup>2</sup>S serial interface formats

- I<sup>2</sup>S modes can support a combination of up to 4 DACs and/or 3 ADCs

- Can be configured as a general-purpose serial interface

#### I<sup>2</sup>C Interface

- Master only interface

- Does not support a multimaster bus environment

- Programmable to 100 kbit/s or 400 kbit/s data transfer speeds

#### Pulse Width Modulation (PWM) Output

- Programmable frequency range from 732.4 Hz to 93.75 kHz

- Programmable duty cycle

#### • General Characteristics

- Available in a 52-Pin TQFP Package

- On-chip phase-locked loop (PLL) with internal oscillator is used to generate internal clocks from a 6 MHz crystal input

- 3.3-V core and 5-V compatible input/output buffers used for codec port interface

- · Reset output available which is asserted for both system and USB reset

- External MCU mode supports application firmware development

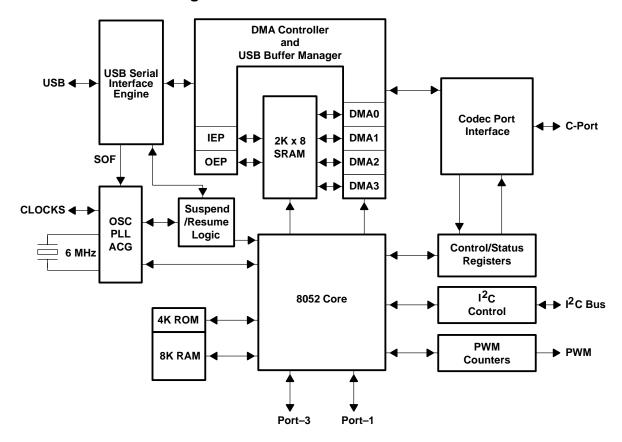

## 1.2 Functional Block Diagram

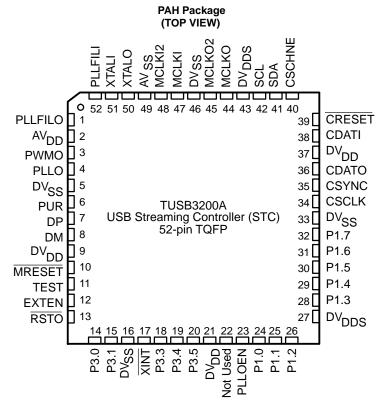

#### 1.3 Terminal Assignments – Normal Mode

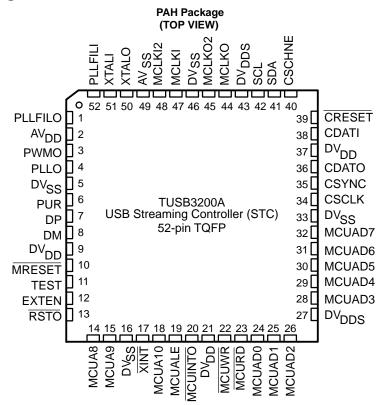

#### 1.4 Terminal Assignments – External MCU Mode

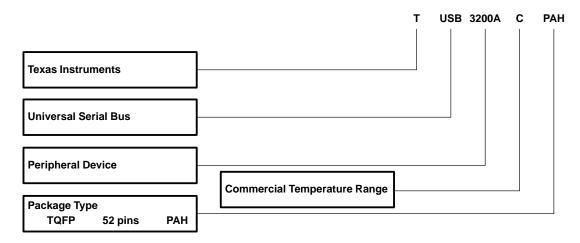

## 1.5 Ordering Information

## 1.6 Terminal Functions - Normal Mode

| TERM              | IINAL            |     |                                                                                                                                                                                                                              |  |  |  |  |  |  |

|-------------------|------------------|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| NAME              | NO.              | 1/0 | DESCRIPTION                                                                                                                                                                                                                  |  |  |  |  |  |  |

| $AV_{DD}$         | 2                |     | 3.3-V Analog supply voltage                                                                                                                                                                                                  |  |  |  |  |  |  |

| AVSS              | 49               |     | Analog ground                                                                                                                                                                                                                |  |  |  |  |  |  |

| CSCLK             | 34               | I/O | Codec port interface serial clock:CSCLK is the serial clock for the codec port interface used to clock the CSYNC, CDATO, CDATI, CRESET AND CSCHNE signals. This signal uses a 5-V compatible TTL/LVCMOS input/output buffer. |  |  |  |  |  |  |

| CSYNC             | 35               | I/O | Codec port interface frame sync: CSYNC is the frame synchronization signal for the codec port interface. This signal uses a 5-V compatible TTL/LVCMOS input/output buffer.                                                   |  |  |  |  |  |  |

| CDATO             | 36               | I/O | Codec port interface serial data output: See Section 1.9 for details. This signal uses a 5-V compatible TTL/LVCMOS input/output buffer.                                                                                      |  |  |  |  |  |  |

| CDATI             | 38               | I/O | Codec port interface serial data input: See Section 1.9 for details. This signal uses a 5-V compatible TTL/LVCMOS input/output buffer.                                                                                       |  |  |  |  |  |  |

| CRESET            | 39               | I/O | Codec port interface reset output: See Section 1.9 for details. This signal uses a 5-V compatible TTL/LVCMOS input/output buffer.                                                                                            |  |  |  |  |  |  |

| CSCHNE            | 40               | I/O | Codec port interface secondary channel enable: See Section 1.9 for details. This signal uses a 5-V compatible TTL/LVCMOS input/output buffer.                                                                                |  |  |  |  |  |  |

| DP                | 7                | I/O | USB differential pair data signal plus: DP is the positive signal of the bidirectional USB differential pair used to connect the TUSB3200A device to the universal serial bus.                                               |  |  |  |  |  |  |

| DM                | 8                | I/O | USB differential pair data signal minus: DM is the negative signal of the bidirectional USB differential pair used to connect the TUSB3200A device to the universal serial bus.                                              |  |  |  |  |  |  |

| $DV_{DD}$         | 9, 21, 37        |     | 3.3-V Digital supply voltage                                                                                                                                                                                                 |  |  |  |  |  |  |

| DV <sub>DDS</sub> | 27, 43           |     | 5-V Digital supply voltage                                                                                                                                                                                                   |  |  |  |  |  |  |

| DV <sub>SS</sub>  | 5, 16, 33,<br>46 |     | Digital ground                                                                                                                                                                                                               |  |  |  |  |  |  |

| EXTEN             | 12               | I   | External MCU mode enable: Input used to enable the device for the external MCU mode. This signal luses a 3.3-V TTL/LVCMOS input buffer.                                                                                      |  |  |  |  |  |  |

| MCLKI             | 47               | I   | Master clock input: An input that can be used as the master clock for the codec port interface or the source for MCLKO2. This signal uses a 5-V to 3.3-V level shifting input buffer.                                        |  |  |  |  |  |  |

| MCLKI2            | 48               | I   | Master clock input 2: An input that can be used as the master clock for the codec port interface or the source for MCLKO2. This signal uses a 5-V to 3.3-V level shifting input buffer.                                      |  |  |  |  |  |  |

| MCLKO             | 44               | 0   | Master clock output: The output of the ACG that can be used as the master clock for the codec port interface and the codec. This signal uses a 3.3-V TTL/LVCMOS output buffer.                                               |  |  |  |  |  |  |

## 1.6 Terminal Functions – Normal Mode (Continued)

| TERMINAL |     |     |                                                                                                                                                                                                                                                                                                                            |  |  |  |  |  |  |

|----------|-----|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| NAME     | NO. | 1/0 | DESCRIPTION                                                                                                                                                                                                                                                                                                                |  |  |  |  |  |  |

| MCLKO2   | 45  | 0   | Master clock output 2: An output that can be used as the master clock for the codec port interface and the codec. This clock signal can also be used as a miscellaneous clock. This signal uses a 3.3-V TTL/LVCMOS output buffer.                                                                                          |  |  |  |  |  |  |

| MRESET   | 10  | I   | Master reset: An active low asynchronous reset for the device that resets all logic to the default state. This signal uses a 3.3-V TTL/LVCMOS input buffer.                                                                                                                                                                |  |  |  |  |  |  |

| Not Used | 22  | I   | This pin is not used in the normal mode. This signal should be tied to digital ground for normal operation.                                                                                                                                                                                                                |  |  |  |  |  |  |

| P1.0     | 24  | I/O | General-purpose I/O port 1 bit 0: A bidirectional I/O port. This signal uses a 5-V compatible TTL/LVCMOS input/output buffer with an internal 100 μA active pullup.                                                                                                                                                        |  |  |  |  |  |  |

| P1.1     | 25  | I/O | General-purpose I/O port 1 bit 1: A bidirectional I/O port. This signal uses a 5-V compatible TTL/LVCMOS input/output buffer with an internal 100 μA active pullup.                                                                                                                                                        |  |  |  |  |  |  |

| P1.2     | 26  | I/O | General-purpose I/O port 1 bit 2: A bidirectional I/O port. This signal uses a 5-V compatible TTL/LVCMOS input/output buffer with an internal 100 μA active pullup.                                                                                                                                                        |  |  |  |  |  |  |

| P1.3     | 28  | I/O | General-purpose I/O port 1 bit 3: A bidirectional I/O port. This signal uses a 5-V compatible TTL/LVCMOS input/output buffer with an internal 100 μA active pullup.                                                                                                                                                        |  |  |  |  |  |  |

| P1.4     | 29  | I/O | General-purpose I/O port 1 bit 4: A bidirectional I/O port. This signal uses a 5-V compatible TTL/LVCMOS input/output buffer with an internal 100 μA active pullup.                                                                                                                                                        |  |  |  |  |  |  |

| P1.5     | 30  | I/O | General-purpose I/O port 1 bit 5: A bidirectional I/O port. This signal uses a 5-V compatible TTL/LVCMOS input/output buffer with an internal 100 μA active pullup.                                                                                                                                                        |  |  |  |  |  |  |

| P1.6     | 31  | I/O | General-purpose I/O port 1 bit 6: A bidirectional I/O port. This signal uses a 5-V compatible TTL/LVCMOS input/output buffer with an internal 100 μA active pullup.                                                                                                                                                        |  |  |  |  |  |  |

| P1.7     | 32  | I/O | General-purpose I/O port 1 bit 7: A bidirectional I/O port. This signal uses a 5-V compatible TTL/LVCMOS input/output buffer with an internal 100 μA active pullup.                                                                                                                                                        |  |  |  |  |  |  |

| P3.0     | 14  | I/O | General-purpose I/O port 3 bit 0: A bidirectional I/O port. This signal uses a 5-V compatible TTL/LVCMOS input/output buffer with an internal 100 μA active pullup.                                                                                                                                                        |  |  |  |  |  |  |

| P3.1     | 15  | I/O | General-purpose I/O port 3 bit 1: A bidirectional I/O port. This signal uses a 5-V compatible TTL/LVCMOS input/output buffer with an internal 100 μA active pullup.                                                                                                                                                        |  |  |  |  |  |  |

| P3.3     | 18  | I/O | General-purpose I/O port 3 bit 3: A bidirectional I/O port. This signal uses a 5-V compatible TTL/LVCMOS input/output buffer with an internal 100 μA active pullup.                                                                                                                                                        |  |  |  |  |  |  |

| P3.4     | 19  | I/O | General-purpose I/O port 3 bit 4: A bidirectional I/O port. This signal uses a 5-V compatible TTL/LVCMOS input/output buffer with an internal 100 μA active pullup.                                                                                                                                                        |  |  |  |  |  |  |

| P3.5     | 20  | I/O | General-purpose I/O port 3 bit 5: A bidirectional I/O port. This signal uses a 5-V compatible TTL/LVCMOS input/output buffer with an internal 100 μA active pullup.                                                                                                                                                        |  |  |  |  |  |  |

| PLLFILI  | 52  | I   | PLL loop filter input: Input to on-chip PLL from external filter components.                                                                                                                                                                                                                                               |  |  |  |  |  |  |

| PLLFILO  | 1   | 0   | PLL loop filter output: Output from on-chip PLL to external filter components.                                                                                                                                                                                                                                             |  |  |  |  |  |  |

| PLLO     | 4   | 0   | PLL output: The 48-MHz output of the PLL used for diagnostic purposes only. This signal uses a 3.3-V TTL/LVCMOS output buffer.                                                                                                                                                                                             |  |  |  |  |  |  |

| PLLOEN   | 23  | I   | PLL output enable: An input used to enable the PLLO output signal. This signal uses a 5-V compatible input buffer.                                                                                                                                                                                                         |  |  |  |  |  |  |

| PWMO     | 3   | 0   | PWM output: Output of the pulse width modulation circuit. This signal uses a 3.3-V to 5-V CMOS level shifting output buffer.                                                                                                                                                                                               |  |  |  |  |  |  |

| PUR      | 6   | 0   | USB data signal plus pullup resistor connect: PUR is used to connect the pullup resistor on the DP signal to 3.3-V or a 3-state. When the DP signal is connected to 3.3-V the host PC should detect the connection of the TUSB3200A device to the universal serial bus. This signal uses a 3.3-V TTL/LVCMOS output buffer. |  |  |  |  |  |  |

| RSTO     | 13  | 0   | Reset output: Output that is active while the master reset input or the USB reset is active. This signal uses a 3.3-V TTL/LVCMOS output buffer.                                                                                                                                                                            |  |  |  |  |  |  |

| SCL      | 42  | 0   | $I^2C$ interface serial clock: SCL is the clock signal for the $I^2C$ serial interface. This signal uses a 3.3-V to 5-V TTL level shifting open drain output buffer.                                                                                                                                                       |  |  |  |  |  |  |

## 1.6 Terminal Functions – Normal Mode (Continued)

| TERMI | NAL |     | DESCRIPTION                                                                                                                                                                                                                                                         |

|-------|-----|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NAME  | NO. | 1/0 | DESCRIPTION                                                                                                                                                                                                                                                         |

| SDA   | 41  | I/O | I <sup>2</sup> C interface serial data input/output: SDA is the bidirectional data signal for the I <sup>2</sup> C serial interface. This signal uses a 3.3-V to 5-VTTL level shifting open drain output buffer and a 5-V to 3.3-V TTL level shifting input buffer. |

| TEST  | 11  | I   | Test mode enable: Input used to enable the device for the factory test mode. This signal uses a 3.3-V TTL/LVCMOS input buffer.                                                                                                                                      |

| XINT  | 17  | I   | External interrrupt: An active low input used by external circuitry to interrupt the on-chip 8052 MCU. This signal uses a 5-V compatible input buffer.                                                                                                              |

| XTALI | 51  | I   | Crystal input: Input to the on-chip oscillator from an external 6-MHz crystal.                                                                                                                                                                                      |

| XTALO | 50  | 0   | Crystal Output: Output from the on-chip oscillator to an external 6-MHz crystal.                                                                                                                                                                                    |

## 1.7 Terminal Functions – External MCU Mode

| TERM              | IINAL            |     |                                                                                                                                                                                                                                   |  |  |  |  |  |  |

|-------------------|------------------|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| NAME NO.          |                  | 1/0 | DESCRIPTION                                                                                                                                                                                                                       |  |  |  |  |  |  |

| AV <sub>DD</sub>  | 2                |     | 3.3-V Analog supply voltage                                                                                                                                                                                                       |  |  |  |  |  |  |

| AVSS              | 49               |     | Analog ground                                                                                                                                                                                                                     |  |  |  |  |  |  |

| CSCLK             | 34               | I/O | Codec port interface serial clock:CSCLK is the serial clock for the codec port interface used to clock the CSYNC, CDATO, CDATI, CRESET AND CSCHNE signals. This signal uses a 5-V compatible TTL/LVCMOS input/output buffer.      |  |  |  |  |  |  |

| CSYNC             | 35               | I/O | Codec port interface frame sync: CSYNC is the frame synchronization signal for the codec port interface. This signal uses a 5-V compatible TTL/LVCMOS input/output buffer.                                                        |  |  |  |  |  |  |

| CDATO             | 36               | I/O | Codec port interface serial data output: See Section 1.9 for details. This signal uses a 5-V compatible TTL/LVCMOS input/output buffer.                                                                                           |  |  |  |  |  |  |

| CDATI             | 38               | I/O | Codec port interface serial data input: See Section 1.9 for details. This signal uses a 5-V compatible TTL/LVCMOS input/output buffer.                                                                                            |  |  |  |  |  |  |

| CRESET            | 39               | I/O | Codec port interface reset output: See Section 1.9 for details. This signal uses a 5-V compatible TTL/LVCMOS input/output buffer.                                                                                                 |  |  |  |  |  |  |

| CSCHNE            | 40               | I/O | Codec port interface secondary channel enable: See Section 1.9 for details. This signal uses a 5-V compatible TTL/LVCMOS input/output buffer.                                                                                     |  |  |  |  |  |  |

| DP                | 7                | I/O | USB differential pair data signal plus: DP is the positive signal of the bidirectional USB differential pair used to connect the TUSB3200A device to the universal serial bus.                                                    |  |  |  |  |  |  |

| DM                | 8                | I/O | USB differential pair data signal minus: DM is the negative signal of the bidirectional USB differential pair used to connect the TUSB3200A device to the universal serial bus.                                                   |  |  |  |  |  |  |

| $DV_{DD}$         | 9, 21, 37        |     | 3.3-V Digital supply voltage                                                                                                                                                                                                      |  |  |  |  |  |  |

| DV <sub>DDS</sub> | 27, 43           |     | 5 V-Digital supply voltage                                                                                                                                                                                                        |  |  |  |  |  |  |

| DVSS              | 5, 16, 33,<br>46 |     | Digital ground                                                                                                                                                                                                                    |  |  |  |  |  |  |

| EXTEN             | 12               | I   | External MCU mode enable: Input used to enable the device for the external MCU mode. This signal uses a 3.3 V TTL/LVCMOS input buffer.                                                                                            |  |  |  |  |  |  |

| MCLKI             | 47               | I   | Master clock input: An input that can be used as the master clock for the codec port interface or the source for MCLKO2. This signal uses a 5-V to 3.3-V level shifting input buffer.                                             |  |  |  |  |  |  |

| MCLKI2            | 48               | I   | Master clock input 2: An input that can be used as the master clock for the codec port interface or the source for MCLKO2. This signal uses a 5-V to 3.3-V level shifting input buffer.                                           |  |  |  |  |  |  |

| MCLKO             | 44               | 0   | Master clock output: The output of the ACG that can be used as the master clock for the codec port interface and the codec. This signal uses a 3.3-V TTL/LVCMOS output buffer                                                     |  |  |  |  |  |  |

| MCLKO2            | 45               | 0   | Master clock output 2: An output that can be used as the master clock for the codec port interface and the codec. This clock signal can also be used as a miscellaneous clock. This signal uses a 3.3-V TTL/LVCMOS output buffer. |  |  |  |  |  |  |

| MCUAD0            | 24               | I/O | MCU multiplexed address/data bit 0: Multiplexed address bit 0/data bit 0 for external MCU access to the TUSB3200A external data memory space.                                                                                     |  |  |  |  |  |  |

## 1.7 Terminal Functions – External MCU Mode (Continued)

| TERMINAL |     | 1/0 | DESCRIPTION                                                                                                                                                                                                                                                                                                                |  |  |  |  |  |  |

|----------|-----|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| NAME     | NO. | 1/0 | DESCRIPTION                                                                                                                                                                                                                                                                                                                |  |  |  |  |  |  |

| MCUAD1   | 25  | I/O | MCU multiplexed address/data bit 1: Multiplexed address bit 1/data bit 1 for external MCU access to the TUSB3200A external data memory space.                                                                                                                                                                              |  |  |  |  |  |  |

| MCUAD2   | 26  | I/O | MCU multiplexed address/data bit 2: Multiplexed address bit 2/data bit 2 for external MCU access to the TUSB3200A external data memory space.                                                                                                                                                                              |  |  |  |  |  |  |

| MCUAD3   | 28  | I/O | MCU multiplexed address/data bit 3: Multiplexed address bit 3/data bit 3 for external MCU access to the TUSB3200A external data memory space.                                                                                                                                                                              |  |  |  |  |  |  |

| MCUAD4   | 29  | I/O | MCU multiplexed address/data bit 4: Multiplexed address bit 4/data bit 4 for external MCU access to the TUSB3200A external data memory space.                                                                                                                                                                              |  |  |  |  |  |  |

| MCUAD5   | 30  | I/O | MCU multiplexed address/data bit 5: Multiplexed address bit 5/data bit 5 for external MCU access to the TUSB3200A external data memory space.                                                                                                                                                                              |  |  |  |  |  |  |

| MCUAD6   | 31  | I/O | MCU multiplexed address/data bit 6: Multiplexed address bit 6/data bit 6 for external MCU access to the TUSB3200A external data memory space.                                                                                                                                                                              |  |  |  |  |  |  |

| MCUAD7   | 32  | I/O | MCU multiplexed address/data bit 7: Multiplexed address bit 7/data bit 7 for external MCU access to the TUSB3200A external data memory space.                                                                                                                                                                              |  |  |  |  |  |  |

| MCUA8    | 14  | I   | MCU address bit 8: Multiplexed address bit 8 for external MCU access to the TUSB3200A external data memory space.                                                                                                                                                                                                          |  |  |  |  |  |  |

| MCUA9    | 15  | I   | MCU address bit 9: Multiplexed address bit 9 for external MCU access to the TUSB3200A external data memory space.                                                                                                                                                                                                          |  |  |  |  |  |  |

| MCUA10   | 18  | I   | MCU address bit 10: Multiplexed address bit 10 for external MCU access to the TUSB3200A external data memory space.                                                                                                                                                                                                        |  |  |  |  |  |  |

| MCUALE   | 19  | I   | MCU address latch enable: Address latch enable for external MCU access to the TUSB3200A external data memory space.                                                                                                                                                                                                        |  |  |  |  |  |  |

| MCUINTO  | 20  | 0   | MCU interrupt output: Interrupt output to be used for external MCU INTO input signal. All internal TUSB3200A interrupt sources are ORed together to generate this output signal.                                                                                                                                           |  |  |  |  |  |  |

| MCURD    | 23  | I   | MCU read strobe: Read strobe for external MCU read access to the TUSB3200A external data memory space.                                                                                                                                                                                                                     |  |  |  |  |  |  |

| MCUWR    | 22  | I   | MCU write strobe: Write strobe for external MCU write access to the TUSB3200A external data memory space.                                                                                                                                                                                                                  |  |  |  |  |  |  |

| MRESET   | 10  | I   | Master reset: An active low asynchronous reset for the device that resets all logic to the default state. This signal uses a 3.3-V TTL/LVCMOS input bufer.                                                                                                                                                                 |  |  |  |  |  |  |

| Not Used | 4   | 0   | This pin is not used in the external MCU mode.                                                                                                                                                                                                                                                                             |  |  |  |  |  |  |

| PLLFILI  | 52  | I   | PLL loop filter input: Input to on-chip PLL from external filter components.                                                                                                                                                                                                                                               |  |  |  |  |  |  |

| PLLFILO  | 1   | 0   | PLL loop filter output: Output to on-chip PLL from external filter components.                                                                                                                                                                                                                                             |  |  |  |  |  |  |

| PUR      | 6   | 0   | USB data signal plus pullup resistor connect: PUR is used to connect the pullup resistor on the DP signal to 3.3-V or a 3-state. When the DP signal is connected to 3.3-V the host PC should detect the connection of the TUSB3200A device to the universal serial bus. This signal uses a 3.3-V TTL/LVCMOS output buffer. |  |  |  |  |  |  |

| PWMO     | 3   | 0   | PWM output: Output of the pulse width modulation circuit. This signal uses a 3.3-V to 5-V CMOS level shifting output buffer.                                                                                                                                                                                               |  |  |  |  |  |  |

| RSTO     | 13  | 0   | Reset output: Output that is active while the master reset input or the USB reset is active. This signal uses a 3.3-V TTL/LVCMOS output buffer.                                                                                                                                                                            |  |  |  |  |  |  |

| SCL      | 42  | 0   | I <sup>2</sup> C interface serial clock: SCL is the clock signal for the I <sup>2</sup> C serial interface. This signal uses a 3.3-V to 5-V TTL level shifting open drain output buffer.                                                                                                                                   |  |  |  |  |  |  |

| SDA      | 41  | I/O | I <sup>2</sup> C interface serial data input/output: SDA is the bidirectional data signal for the I <sup>2</sup> C serial interface. This signal uses a 3.3-V to 5-V TTL level shifting open drain output buffer and a 5-V to 3.3-V TTL level shifting input buffer.                                                       |  |  |  |  |  |  |

| TEST     | 11  | I   | Test mode enable: Input used to enable the device for the factory test mode. This signal uses a 3.3-V TTL/LVCMOS input buffer.                                                                                                                                                                                             |  |  |  |  |  |  |

| XINT     | 17  | I   | External interrupt: An active low input used by external circuitry to interrupt the on-chip 8052 MCU. This signal uses a 5-V compatible input buffer.                                                                                                                                                                      |  |  |  |  |  |  |

| XTALI    | 51  | I   | Crystal input: Input to the on-chip oscillator from an external 6-MHz crystal.                                                                                                                                                                                                                                             |  |  |  |  |  |  |

| XTALO    | 50  | 0   | Crystal output: Output from the on-chip oscillator to an external 6-MHz crystal.                                                                                                                                                                                                                                           |  |  |  |  |  |  |

#### 1.8 Device Operation Modes

The EXTEN and TEST pins define the mode that the TUSB3200A will be in after reset.

| MODE                       | EXTEN | TEST |

|----------------------------|-------|------|

| Normal mode – internal MCU | 0     | 0    |

| External MCU mode          | 1     | 0    |

| Factory test               | 0     | 1    |

| Factory test               | 1     | 1    |

#### 1.9 Terminal Assignments for Codec Port Interface Modes

The codec port interface has eight modes of operation that support AC97, I<sup>2</sup>S, and AIC codecs. There is also a general-purpose mode that is not specific to a serial interface. The mode is programmed by writing to the mode select field of the codec port interface configuration register 1 (CPTCNF1). The codec port interface terminals CSYNC, CSCLK, CDATO, CDATI, CRESET, and CSCHNE take on functionality appropriate to the mode programmed as shown in the following tables.

| TERMINAL |        | GP     |               | AIC   | -      |         | AC '97 v1.X |         | .X |

|----------|--------|--------|---------------|-------|--------|---------|-------------|---------|----|

| NO.      | NAME   | Mode 0 | Mode 0 Mode 1 |       | Mode 2 |         | Mode 3      |         |    |

| 35       | CSYNC  | CSYNC  | I/O           | FS    | 0      | SYNC    | 0           | SYNC    | 0  |

| 34       | CSCLK  | CSCLK  | I/O           | SCLK  | 0      | BIT_CLK | I           | BIT_CLK |    |

| 36       | CDATO  | CDATO  | 0             | DOUT  | 0      | SD_OUT  | 0           | SD_OUT  | 0  |

| 38       | CDATI  | CDATI  | ı             | DIN   | - 1    | SD_IN   | I           | SD_IN1  |    |

| 39       | CRESET | CRESET | 0             | RESET | 0      | RESET   | 0           | RESET   | 0  |

| 40       | CSCHNE | NC     | 0             | FC    | 0      | NC      | 0           | SD_IN2  | Ι  |

| TERMINAL |        | I <sup>2</sup> S |   | l <sup>2</sup> S |   | I <sup>2</sup> S |   | I <sup>2</sup> S |   |

|----------|--------|------------------|---|------------------|---|------------------|---|------------------|---|

| NO. NAME |        | Mode 4           |   | Mode 5           |   | Mode 6           |   | Mode 7           |   |

| 35       | CSYNC  | LRCK             | 0 | LRCK             | 0 | LRCK             | 0 | LRCK             | 0 |

| 34       | CSCLK  | SCLK             | 0 | SCLK             | 0 | SCLK             | 0 | SCLK             | 0 |

| 36       | CDATO  | SDOUT1           | 0 | SDOUT1           | 0 | SDOUT1           | 0 | SDOUT1           | 0 |

| 38       | CDATI  | SDOUT2           | 0 | SDOUT2           | 0 | SDIN1            | ı | SDOUT2           | 0 |

| 39       | CRESET | SDOUT3           | 0 | SDIN1            | I | SDIN2            | I | SDOUT3           | 0 |

| 40       | CSCHNE | SDIN1            | I | SDIN2            | I | SDIN3            | ı | SDOUT4           | 0 |

NOTES: 1. Signal names and I/O direction are with respect to the TUSB3200A device. The signal names used for the TUSB3200A terminals for the various codec port interface modes reflect the nomenclature used by the codec devices.

- 2. NC indicates no connection for the terminal in a particular mode. The TUSB3200A device drives the signal as an output for these cases.

- 3. The CSYNC and CSCLK signals can be programmed as either an input or an output in the general-purpose mode.

#### 2 Description

#### 2.1 Architectural Overview

#### 2.1.1 Oscillator and PLL

Using an external 6-MHz crystal, the TUSB3200A derives the fundamental 48-MHz internal clock signal using an on-chip oscillator and PLL. Using the PLL output, the other required clock signals are generated by the clock generator and adaptive clock generator.

#### 2.1.2 Clock Generator and Sequencer Logic

Utilizing the 48-MHz input from the PLL, the clock generator logic generates all internal clock signals, except for the codec port interface master clock (MCLK) and serial clock (CSCLK) signals. The TUSB3200A internal clocks include the 48-MHz clock, a 24-MHz clock, a 12-MHz clock and a USB clock. The USB clock also has a frequency of 12-MHz. The USB clock is the same as the 12-MHz clock when the TUSB3200A is transmitting data and is derived from the data when the TUSB3200A is receiving data. To derive the USB clock when receiving USB data, the TUSB3200A utilizes an internal digital PLL (DPLL) that uses the 48-MHz clock.

The sequencer logic controls the access to the SRAM used for the USB endpoint configuration blocks and the USB endpoint buffer space. The SRAM can be accessed by the MCU, USB buffer manager (UBM) or DMA channels. The sequencer controls the access to the memory using a round robin fixed priority arbitration scheme. This basically means that the sequencer logic generates grant signals for the MCU, UBM and DMA channels at a predetermined fixed frequency.

#### 2.1.3 Adaptive Clock Generator (ACG)

The adaptive clock generator is used to generate a master clock output signal (MCLKO) to be used by the codec port interface and the codec device. To synchronize the sample rate conversion of data by the codec to the USB frame rate, the MCLKO signal generated by the adaptive clock generator must be used. The synchronization of the MCLKO signal to the USB frame rate is controlled by the MCU by programming the adaptive clock generator frequency value. The MCLKO frequency is monitored by the MCU and updated as required. For asynchronous operation, an external source can be used to generate a master clock input signal (MCLKI) to be used by the codec port interface. In this scenario, the codec device should also use the same master clock signal (MCLKI).

#### 2.1.4 USB Transceiver

The TUSB3200A provides an integrated transceiver for the USB port. The transceiver includes a differential output driver, a differential input receiver and two single ended input buffers. The transceiver connects to the USB DP and DM signal terminals.

#### 2.1.5 USB Serial Interface Engine (SIE)

The serial interface engine logic manages the USB packet protocol requirements for the packets being received and transmitted on the USB by the TUSB3200A device. For packets being received, the SIE decodes the packet identifier field (PID) to determine the type of packet being received and to ensure the PID is valid. For token packets and data packets being received, the SIE calculates the packet cycle redundancy check (CRC) and compares the value to the CRC contained in the packet to verify that the packet was not corrupted during transmission. For token packets and data packets being transmitted, the SIE generates the CRC that is transmitted with the packet. For packets being transmitted, the SIE also generates the synchronization field (SYNC) that is an eight bit filed at the beginning of each packet. In addition, the SIE generates the correct PID for all packets being transmitted. Another major function of the SIE is the overall serial-to-parallel conversion of the data packets being transmitted.

#### 2.1.6 USB Buffer Manager (UBM)

The USB buffer manager provides the control logic that interfaces the SIE to the USB endpoint buffers. One of the major functions of the UBM is to decode the USB function address to determine if the host PC is addressing the TUSB3200A device USB peripheral function. In addition, the endpoint address field and direction signal are decoded to determine which particular USB endpoint is being addressed. Based on the direction of the USB transaction and the endpoint number, the UBM will either write or read the data packet to/from the appropriate USB endpoint data buffer.

#### 2.1.7 USB Frame Timer

The USB frame timer logic receives the start of frame (SOF) packet from the host PC each USB frame. Each frame, the logic stores the 11-bit frame number value from the SOF packet in a register and asserts the internal SOF signal. The frame number register can be read by the MCU and the value can be used as a time stamp. For USB frames in which the SOF packet is corrupted or not received, the frame timer logic will generate a pseudo start of frame (PSOF) signal and increment the frame number register.

#### 2.1.8 USB Suspend and Resume Logic

The USB suspend and resume logic detects suspend and resume conditions on the USB. This logic also provides the internal signals used to control the TUSB3200A device when these conditions occur. The capability to resume operation from a suspend condition with a locally generated remote wake-up event is also provided.

#### 2.1.9 MCU Core

The TUSB3200A uses an 8-bit microcontroller core that is based on the industry standard 8052. The MCU is software compatible with the 8052, 8032, 80C52, 80C53, and 87C52 MCUs. The 8052 MCU is the processing core of the TUSB3200A and handles all USB control, interrupt and bulk endpoint transfers. In addition, the MCU can also be the source or sink for USB isochronous endpoint transfers.

#### 2.1.10 MCU Memory

In accordance with the industry standard 8052, the TUSB3200A MCU memory is organized into program memory, external data memory and internal data memory. A 4K byte boot ROM is used to download the application code to an 8K byte RAM that is mapped to the program memory space. The external data memory includes the USB endpoint configuration blocks, USB data buffers, and memory mapped registers. The total external data memory space used is 2K bytes. A total of 256 bytes are provided for the internal data memory.

#### 2.1.11 USB Endpoint Configuration Blocks and Endpoint Buffer Space

The USB endpoint configuration blocks are used by the MCU to configure and operate the required USB endpoints for a particular application. In addition to the control endpoint, the TUSB3200A supports a total of seven in endpoints and seven out endpoints. A set of six bytes is provided for each endpoint to specify the endpoint type, buffer address, buffer size, and data packet byte count.

The USB endpoint buffer space provided is a total of 1832 bytes. The space is totally configurable by the MCU for a particular application. Therefore, the MCU can configure each buffer based on the total number of endpoints to be used, the maximum packet size to be used for each endpoint, and the selection of single or double buffering.

#### 2.1.12 DMA Controller

Four DMA channels are provided to support the streaming of data for USB isochronous endpoints. Each DMA channel can support one USB isochronous endpoint, either in or out. The DMA channels are used to stream data between the USB endpoint data buffers and the codec port interface. The USB endpoint number and direction can be programmed for each DMA channel. Also, the codec port interface time slots to be serviced by each DMA channel can be programmed.

#### 2.1.13 Codec Port Interface

The TUSB3200A provides a configurable full duplex bidirectional serial interface that can be used to connect to a codec or another device for streaming USB Isochronous data. The interface can be configured to support several different industry standard protocols, including AC '97 1.X, AC '97 2.X and I<sup>2</sup>S.

#### 2.1.14 I<sup>2</sup>C Interface

The I<sup>2</sup>C interface logic provides a two-wire serial interface that can be used by the 8052 MCU to access other ICs. The TUSB3200A is an I<sup>2</sup>C master device only and supports single byte or multiple byte read and write operations. The interface can be programmed to operate at either 100 kbps or 400 kbps. In addition, the protocol supports 8-bit or 16-bit addressing for accessing the I<sup>2</sup>C slave device memory locations.

#### 2.1.15 Pulse Width Modulation (PWM) Output

The TUSB3200A provides a pulse width modulation output with programmable frequency and pulse width. The frequency can be programmed from 732 Hz to 93.7 kHz with an 8-bit register. The pulse width of the output signal is set with a 16-bit register.

#### 2.1.16 General-Purpose IO Ports (GPIO)

The TUSB3200A provides two general-purpose IO ports that are controlled by the internal 8052 MCU. The two ports, port 1 and port 3, are 8-bits and 5-bits, respectively. Note that port 3 bit locations 2, 6, and 7 have been used in the TUSB3200A for other functionality. Therefore these three bit locations are not available for GPIO use. Port 3 bit location 2 has been used as the external interrupt (XINT) input to the TUSB3200A. Port 3 bit locations 6 and 7 have been used as the external MCU write strobe and read strobe inputs for the external MCU mode of operation.

Each bit of both ports can be independently used as either an input or output. Hence each port bit consists of an output buffer, an input buffer and a pullup resistor. The pullup resistors on the GPIO pins can be disabled using the PUDIS bit in the global control register.

#### 2.1.17 Interrupt Logic

The interrupt logic monitors the various conditions that can cause an interrupt and asserts the interrupt 0 (INT0) input to the 8052 MCU accordingly. All of the TUSB3200A internal interrupt sources and the external interrupt (XINT) input are ORed together to generate the INT0 signal. An interrupt vector register is provided that is used by the MCU to identify the interrupt source.

#### 2.1.18 Reset Logic

An external master reset (MRESET) input signal that is asynchronous to the internal clocks is used to reset the TUSB3200A logic. In addition to the master reset, the TUSB3200A logic can be reset with the USB reset from the host PC. The TUSB3200A also provides a reset output (RSTO) signal that can be used by external devices. This signal is asserted when either a master reset or USB reset occurs.

#### 2.2 Device Operation

The operation of the TUSB3200A is explained in the following sections. For additional information on USB, refer to the universal serial bus Specification version 1.1.

#### 2.2.1 Clock Generation

The TUSB3200A requires an external 6-MHz crystal and PLL loop filter components connected as shown in Figure 4-1 to derive all the clocks needed for both USB and codec operation. Using the low frequency 6-MHz crystal and generating the required higher frequency clocks internal to the IC is a major advantage regarding EMI.

#### 2.2.2 Device Initialization

After a power-on reset is applied to the TUSB3200A device, the 8052 MCU will execute a boot loader program from the 4K byte boot ROM mapped to the program memory space. During device initialization, the boot loader program downloads the application program code from an external EEPROM through the I<sup>2</sup>C interface. This requires that a binary image of the application code be written to the 8K byte code RAM in the TUSB3200A device.

All memory mapped registers are initialized to a default value as defined in Appendix A, *MCU Memory and Memory-Mapped Registers*. The TUSB3200A device powers up with a default function address of zero and disconnected from the USB.

#### 2.2.2.1 Boot Load from EEPROM

Loading the application code from an external serial EEPROM requires a preprogrammed memory device containing an informative header and the application code. While the application code is being downloaded, the TUSB3200A will remain disconnected from the USB. When the code download is complete, execution of the application code should connect the TUSB3200A to the USB. In this situation, the TUSB3200A will enumerate using the vendor ID and product ID contained in the application code.

#### 2.2.2.2 EEPROM Header

For both application code and USB device information stored in a EEPROM device, a common header format is used that proceeds the data payload. Table 2-1 shows the format and information contained in the header.

| OFFSET | TYPE        | SIZE | VALUE                                                                                                                                                                                                       |  |  |  |

|--------|-------------|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| 0      | Signature   | 4    | 0x04513200                                                                                                                                                                                                  |  |  |  |

| 4      | Header size | 1    | Header size                                                                                                                                                                                                 |  |  |  |

| 5      | Version     | 1    | Firmware version                                                                                                                                                                                            |  |  |  |

| 6      | EEPROM type | 1    | 0x01 = Reserved<br>0x02 = Reserved<br>0x03 = Reserved<br>0x04 = Reserved<br>0x05 = Reserved<br>0x06 = Reserved<br>0x07 = Reserved<br>0x08 = Reserved<br>0x09 = 24C32<br>0x0A = 24C64<br>0x0B0xFF = Reserved |  |  |  |

| 7      | Data type   | 1    | 0x01 = Application code<br>0x020xFF = Reserved                                                                                                                                                              |  |  |  |

| 8      | Data size   | 2    | Data payload only size                                                                                                                                                                                      |  |  |  |

| 10     | Check sum   | 2    | Check sum of the data payload beginning at location Check Sum + 2                                                                                                                                           |  |  |  |

| 12     | Data        | -    | Data payload                                                                                                                                                                                                |  |  |  |

Table 2-1. EEPROM Header

The signature field is used for the detection of a EEPROM device connected to the TUSB3200A. The header size field supports future updates of the header. Data begins right after the header. The version field identifies the header version. The EEPROM type field identifies the specific EEPROM device being used. The data type field describes the nature of data stored in the EEPROM (application code or USB device information). The data size field holds the length of the data payload starting from the end of the header. The check sum field contains the check sum for the data payload portion of the EEPROM.

#### 2.2.2.3 EEPROM Data Type

The two types of data that are stored in the EEPROM are application code and USB device information.

#### 2.2.2.3.1 Application Code

Application firmware is stored as a binary image of the code. The binary image is mapped to the MCU program memory space starting at address zero and is stored in the EEPROM as a continuous linear block starting after the header information. A utility program is available that converts a file in Intel hexidecimal format to a binary image data file and appends it to the header.

#### 2.2.2.3.2 USB Device Information

The USB device information is comprised of the vendor ID and product ID. Optionally, a manufacturer string and product string can be included. The boot loader uses this information during enumeration to identify the USB peripheral device. Table 2-2 shows the format and information contained in the USB Device Information Section.

| OFFSET     | TYPE               | SIZE | CONTENTS                      | REMARK             |

|------------|--------------------|------|-------------------------------|--------------------|

| H+1        | Vendor ID          | 2    | Vendor ID code                |                    |

| H+3        | Product ID         | 2    | Product ID code               |                    |

| H+5        | M Offset           | 1    | Pointer to manufacture string | String is optional |

| H+6        | P Offset           | 1    | Pointer to product string     | String is optional |

| H+M Offset | Manufacture string | -    |                               | Null terminated    |

| H+P Offset | Product string     | -    |                               | Null terminated    |

Table 2-2. USB Device Information

#### 2.2.2.4 EEPROM Device Type

The TUSB3200A boot loader program supports several different types of serial EEPROM devices. The boot loader program will automatically identify the EEPROM type from the header information and use the correct serial interface protocol accordingly. The boot loader program uses an I<sup>2</sup>C slave device address of A0h for the serial EEPROM device.

These EEPPROM devices require an  $I^2C$  device address in addition to a two byte data word address. These devices require the full 7-bit  $I^2C$  device address. Depending on the memory size of the EEPROM device being used, the most significant three or four bits of the two byte data word address are don't care bits. The EEPROM types supported are: 24C32 and 24C64

All of these EEPROM devices can be used for storing and loading application code. However most applications will use devices which are capable of storing up to 8K bytes of program code.

#### 2.2.3 USB Enumeration

USB enumeration is accomplished by interaction between the host PC software and the TUSB3200A code. After power-on reset the boot loader code first reads the information from the EEPROM, then runs the application code. The application code connects the TUSB3200A to the USB. During the enumeration, the application code identifies the device as an application specific device and the host loads the appropriate host driver(s). The boot loader and application code both use the CONT, SDW, and FRSTE bits to control the enumeration process. The function connect (CONT) bit is set to a 1 by the MCU to connect the TUSB3200A device to the USB. When this bit is set to a 1, the USB data plus pullup resistor (PUR) output signal is enabled, which will connect the pullup on the PCB to the TUSB3200A 3.3-V digital supply voltage. When this bit is cleared to a 0, the PUR output is in the 3-state mode. This bit is not affected by a USB reset. The shadow the boot ROM (SDW) bit is set to a 1 by the MCU to switch the MCU memory configuration from boot loader mode to normal operating mode. The function reset enable (FRSTE) bit is set to a 1 by the MCU to enable the USB reset to reset all internal logic including the MCU. However, the shadow the ROM (SDW) and the USB function connect (CONT) bits will not be reset. When this bit is set, the reset output (RSTO) signal from the TUSB3200A device will also be active when a USB reset occurs. This bit is not affected by USB reset.

#### 2.2.4 USB Reset

The TUSB3200A can detect a USB reset condition. When the reset occurs, the TUSB3200A responds by setting the function reset (RSTR) bit in the USB status register (USBSTA). If the corresponding function reset bit in the USB

interrupt mask register is set, an MCU interrupt will be generated and the USB function reset (0x17) vector will appear in the interrupt vector register (VECINT).