## **General Description**

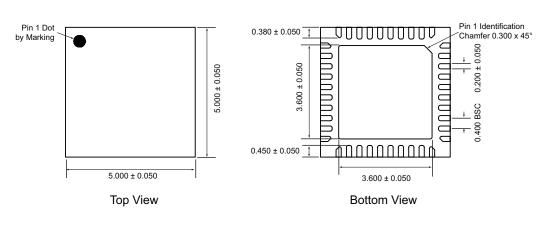

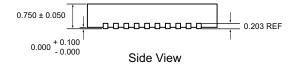

The AAT3608 is a member of Skyworks' Total Power Management IC (TPMIC™) product family. It contains a single-cell lithium ion/polymer battery charger, two 800mA switching regulators, and five low dropout (LDO) regulators in a small Pb-free 40-pin 5mmx5mm TQFN package, making it ideal for portable space-constrained systems. The single-input linear charger powers up from an adapter or a USB port. The adapter charge current is programmable with an external resistor or pin selectable between 100mA and 500mA when connected to a USB port. The device integrates a load switch for dynamic power path and features deep sleep mode operation. The step-down regulators are monolithic synchronous converters integrating the compensation network and soft start circuitry. The 1.5MHz operating frequency enables the use of tiny 2.2µH inductors and small 4.7µF output capacitors. External resistors set the output voltage for Buck 1 and Buck 2; the output voltage of Buck 2 is dynamically adjustable with I2C. The LDO regulators feature 3% output voltage accuracy over the full operating temperature range. The fast control loop of the LDO regulators also provide excellent transient response with a typical output voltage deviation of 1.5%. The AAT3608 provides protection features to safeguard from overtemperature operation, over-current operation, and a digital thermal loop to protect the battery during battery charging. The device is rated over an ambient temperature range of -40°C to 85°C.

### **Features**

- 2.7V to 5.5V Operating Input Voltage Range

- Adapter or USB Single Input Linear Charger

- Battery Charger Digital Thermal Regulation

- Battery Temperature Monitoring

- Battery Charger Includes Programmable Timer

- Input Load Switch

- Dual 800mA Monolithic Switching Converters

- 1.5MHz Switching Frequencies

- 95% Efficiency

- Independent Input Power and Ground

- Buck1 Output Programmable With External Resistors

- Buck 2 Feedback Voltage is Dynamically Adjustable between 0.5V and 0.7V with I<sup>2</sup>C Interface

- Five Channel LDO Regulators

- 300mA, Output Adjustable via Two Logic Inputs

- 80mA, Output Adjustable via I<sup>2</sup>C Interface

- 50mA, 2.5V Output Voltage

- 50mA, 3.3V Output Voltage

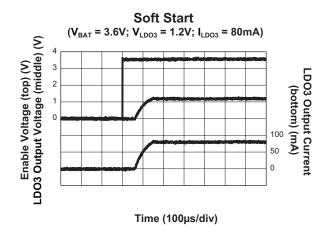

- 80mA with 1.2V Fixed Output

- 3% Accuracy and 1.5% Typical Transient Accuracy

- Very Low Shutdown Current

- Power-On Push Button

- Status Outputs

- Interrupt, Reset and Status Pins, Low Battery Flag

- Separate Enable Pin for LDO2, LDO4, LDO5, and Buck2 (when mask is removed)

- Over-Current and Over-Thermal Protection

- 5mmx5mm, 40-Pin TQFN Package

## **Applications**

- GPS

- Handheld Devices

- Mobile Media Players

- MP3

- Portable Navigation

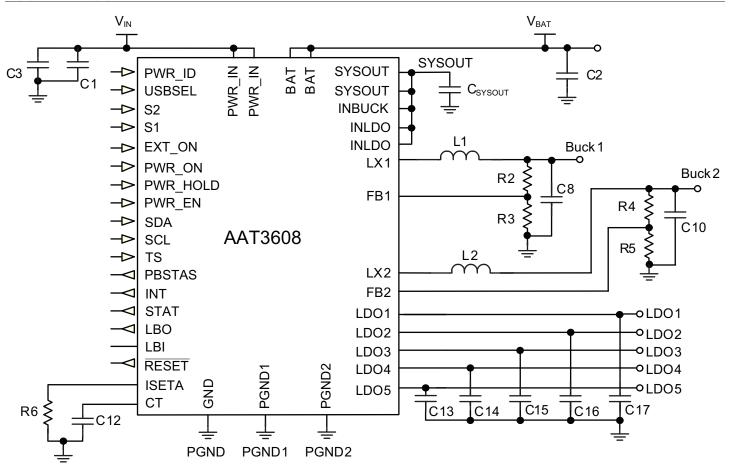

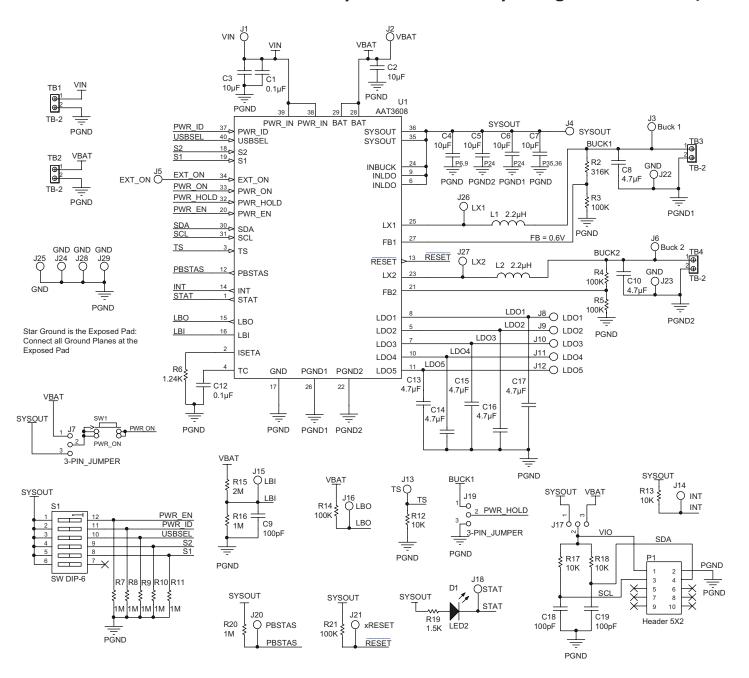

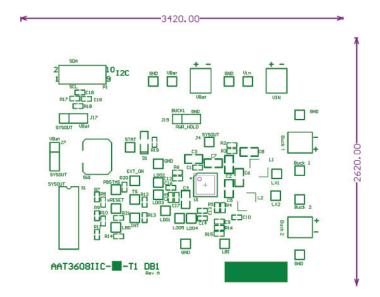

## **Typical Application Circuit**

## **Pin Descriptions**

| Pin #  | Symbol   | Function                                                                                                                                                                                                                                                                        |

|--------|----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1      | STAT     | Open drain (pull-down) output for battery charging status.                                                                                                                                                                                                                      |

| 2      | ISETA    | Input pin for charge current programming for the adapter. Connect a $1.24k\Omega$ resistor to get 800mA of charging current. Can be used to monitor charging current.                                                                                                           |

| 3      | TS       | Battery temperature sense pin with 75 $\mu$ A output current. Connect the battery's NTC 10 $k\Omega$ resistor from this pin to ground. A Beta range of 3300 to 4000 will place the typical charging temperature between -4°C and 48°C.                                          |

| 4      | СТ       | Charger safety timer pin. A $0.1\mu F$ ceramic capacitor should be connected between this pin and GND. Connect directly to GND to disable the timer function.                                                                                                                   |

| 5      | LDO2     | Output for LDO2 regulator.                                                                                                                                                                                                                                                      |

| 6      | INLDO    | Input power for LDO regulators.                                                                                                                                                                                                                                                 |

| 7      | LDO3     | Output for LDO3 regulator.                                                                                                                                                                                                                                                      |

| 8      | LDO1     | Output for LDO1 regulator.                                                                                                                                                                                                                                                      |

| 9      | INLDO    | Input power for LDO regulators.                                                                                                                                                                                                                                                 |

| 10     | LDO4     | Output for LDO4 regulator.                                                                                                                                                                                                                                                      |

| 11     | LDO5     | Output for LDO5 regulator.                                                                                                                                                                                                                                                      |

| 12     | PBSTAS   | Open drain (pull-down) output for PWR_ON status. When PWR_ON is high, PBSTAS will be low (after the debounce time). When PWR_ON is low, PBSTAS will be high (or equal to the voltage to which that external pull-up resistor is connected).                                     |

| 13     | RESET    | Open drain (pull-down) active-low output for reset. After Buck2 is OK, there is a delay of 200ms before $\overline{\text{RESET}}$ goes High. $\overline{\text{RESET}}$ pin is low in shutdown.                                                                                  |

| 14     | INT      | Open drain (pull-down) active-low output for interrupt. When any of the I <sup>2</sup> C read bits (except the DS_RDY and PWR_DS bits) change state this pin will pull low. It will be released again after a read from the I <sup>2</sup> C is complete.                       |

| 15     | LBO      | Open drain (pull-down) active-low output for low-battery comparator. When the battery is low, LBO will pull down.                                                                                                                                                               |

| 16     | LBI      | Feedback input for low-battery comparator. The LBI threshold is 1.0V.                                                                                                                                                                                                           |

| 17     | GND      | Ground.                                                                                                                                                                                                                                                                         |

| 18     | S2       | S1 and S2 bits set the output voltage for LDO1.                                                                                                                                                                                                                                 |

| 19     | S1       | S1 and S2 bits set the output voltage for LDO1.                                                                                                                                                                                                                                 |

| 20     | PWR_EN   | Enable for LDO2, LDO4, and LDO5 for default condition. Buck2 can also be controlled by PWR_EN only if the SOC masks PWR_EN through I <sup>2</sup> C, refer to the "I <sup>2</sup> C Serial Interface and Programmability" section of this datasheet for additional information. |

| 21     | FB2      | Feedback input for Buck2 regulator.                                                                                                                                                                                                                                             |

| 22     | PGND2    | Power ground for Buck2 regulator.                                                                                                                                                                                                                                               |

| 23     | LX2      | Switching node for Buck2 regulator.                                                                                                                                                                                                                                             |

| 24     | INBUCK   | Input power for Buck regulators.                                                                                                                                                                                                                                                |

| 25     | LX1      | Switching node for Buck1 regulator.                                                                                                                                                                                                                                             |

| 26     | PGND1    | Power ground for Buck1 regulator.                                                                                                                                                                                                                                               |

| 27     | FB1      | Feedback input for Buck1 regulator.                                                                                                                                                                                                                                             |

| 28, 29 | BAT      | Input for lithium-ion battery.                                                                                                                                                                                                                                                  |

| 30     | SDA      | I <sup>2</sup> C serial data pin.                                                                                                                                                                                                                                               |

| 31     | SCL      | I <sup>2</sup> C serial clock pin.                                                                                                                                                                                                                                              |

| 32     | PWR_HOLD | Enable for the system. PWR_HOLD must be held high by the processor to keep system turned on. To shut down the device, the microcontroller should pull PWR_HOLD to ground.                                                                                                       |

| 33     | PWR_ON   | Enable for the system. Connect a push-button from this pin to BAT to activate system. It is debounced for 320ms.                                                                                                                                                                |

|        |          | Alternate system enable; may be used by the RTC alarm or other system input. This pin's function is similar to PWR ON; it has a                                                                                                                                                 |

| 34     | EXT_ON   | similar 320ms debounce but does not affect the PBSTAS pin.                                                                                                                                                                                                                      |

| 35, 36 | SYSOUT   | System output. Connect to the INLDO and INBUCK input supply pins.                                                                                                                                                                                                               |

| 37     | PWR_ID   | Logic input to identify the source of PWR_IN.                                                                                                                                                                                                                                   |

| 38, 39 | PWR_IN   | Power Input. System input from adapter or USB.                                                                                                                                                                                                                                  |

| 40     | USBSEL   | Logic input to select 500mA current limit and fast charge current (USBSEL=H) or 100mA current limit and fast charge (USBSEL=L). An internal pull-down resistor is connected to this pin. If is left floating, USBSEL is pulled to ground.                                       |

| EP     | EP       | For best thermal performance the exposed thermal pad must be thermally connected to a large exposed copper pad underneath the package. Additionally, the exposed thermal pad (EP), GND, and PGND must be electrically connected to ground copper.                               |

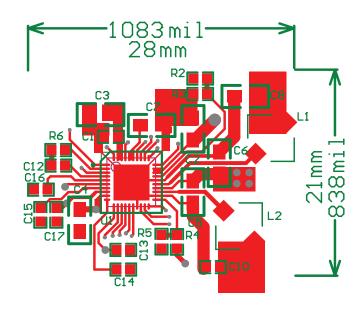

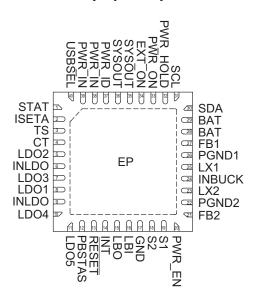

## **Pin Configuration**

TQFN55-40 (Top View)

## Absolute Maximum Ratings<sup>1</sup>

| Symbol            | Pin Name                                                                                                                                                  | Value                             | Units |

|-------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------|-------|

|                   | PWR_IN, PWR_ID, BAT, SYSOUT, SDA, SCL, RESET, STAT, USBSEL, ISETA, TS, CT, LBI, LBO, INT, PWR_EN, PWR_HOLD, PWR_ON, PBSTAS, EXT_ON, S1, S2 Voltage to GND | -0.3 to 6.5                       | V     |

|                   | INBUCK, INLDO Voltage to GND                                                                                                                              | $-0.3$ to $V_{SYSOUT} + 0.3$      | V     |

|                   | LX1, LX2, FB1, FB2 Voltage to PGND1, PGND2                                                                                                                | -0.3 to V <sub>INBUCK</sub> + 0.3 | V     |

|                   | LDO1, LDO2, LDO3, LDO4, LDO5 Voltage to GND                                                                                                               | $-0.3 \text{ to} V_{INLDO} + 0.3$ | V     |

|                   | PGND1, PGND2 to GND                                                                                                                                       | -0.3 to +0.3                      | V     |

| T <sub>1</sub>    | Operating Junction Temperature Range                                                                                                                      | -40 to 150                        |       |

| T <sub>A</sub>    | Ambient Temperature Range                                                                                                                                 | -40 to 85                         | °C    |

| Ts                | Storage Temperature Range                                                                                                                                 | -65 to 150                        |       |

| T <sub>LEAD</sub> | Maximum Junction Soldering Temperature (at leads, 10 sec.)                                                                                                | 300                               |       |

### Thermal Information<sup>2, 3, 4</sup>

| Symbol         | Description               | Value | Units |

|----------------|---------------------------|-------|-------|

| $\theta_{JA}$  | Thermal Resistance        | 25    | °C/W  |

| P <sub>D</sub> | Maximum Power Dissipation | 4     | W     |

<sup>1.</sup> Stresses above those listed in Absolute Maximum Ratings may cause permanent damage to the device. Functional operation at conditions other than the operating conditions

specified is not implied. Only one Absolute Maximum Rating should be applied at any one time.

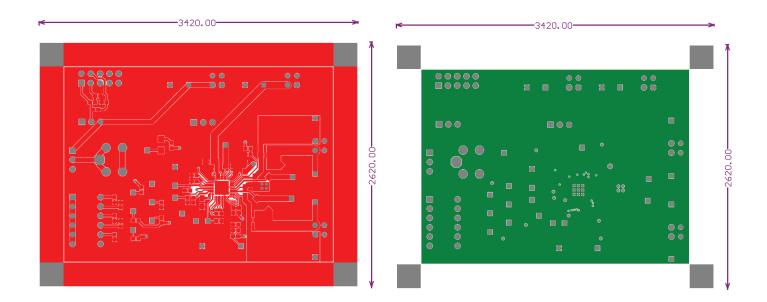

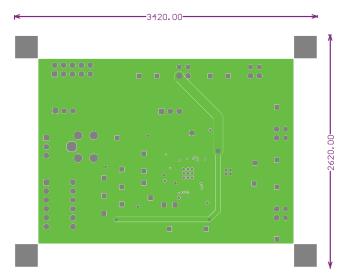

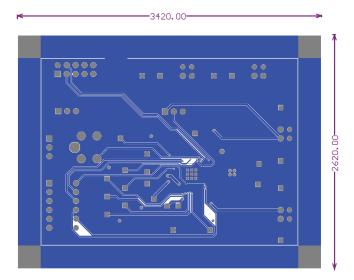

<sup>2.</sup> Thermal Resistance will be measured with the AAT3608 device on the 4-layer FR4 evaluation board in a thermal oven. The amount of power dissipation which will cause the thermal shutdown to activate will depend on the ambient temperature and the PC board layout ability to dissipate the heat.

<sup>3.</sup> Measured on the AAT3608 demo board.

<sup>4.</sup> Derate the maximum power dissipation by 40mW/°C above 25°C ambient temperature.

## **Electrical Characteristics<sup>1</sup>**

$V_{PWR\_IN} = 5V$ ,  $V_{PWR\_ID} = 5V$ ,  $V_{BAT} = 3.6V$ , -40°C  $\leq T_A \leq +85$ °C, unless noted otherwise. Typical values are  $T_A = 25$ °C.

| Symbol                                    | Description                                                      | Conditions                                                      | Min   | Тур               | Max   | Units                |

|-------------------------------------------|------------------------------------------------------------------|-----------------------------------------------------------------|-------|-------------------|-------|----------------------|

| Power Su                                  | <u> </u>                                                         |                                                                 |       |                   |       |                      |

| V <sub>IN</sub>                           | V <sub>INBUCK</sub> , V <sub>INLDO</sub> Input Operating Voltage |                                                                 | 2.7   |                   | 5.5   | V                    |

|                                           | PWR_IN UVLO Threshold                                            | Rising (100mV hysteresis)                                       |       | 4.5               |       | V                    |

| $I_{OPS}$                                 | Sleep Mode Battery Operating Current                             | V <sub>PWR_IN</sub> = 0V, Only LDO1, LDO3, and Buck1 are on     |       | 200               |       | μΑ                   |

| $I_{OPDS}$                                | Deep-Sleep Mode Battery Operating Current                        | $V_{PWR_{IN}} = 0V$ , Only Buck1 is on                          |       | 100               |       | μA                   |

| $I_{SHDN}$                                | Battery Shutdown Current                                         | $V_{PWR_{IN}} = 0V$ and system is shut down                     |       |                   | 10    | μA                   |

| Charger V                                 | oltage Regulation                                                |                                                                 |       |                   |       |                      |

| $V_{BAT\_REG}$                            | Output Charge Voltage Regulation                                 | $0^{\circ}C \leq T_A \leq +70^{\circ}C$                         | 4.158 | 4.2               | 4.242 | V                    |

| V <sub>MIN</sub>                          | Preconditioning Voltage Threshold                                |                                                                 | 2.6   | 2.8               | 3.0   | V                    |

| V <sub>RCH</sub>                          | Battery Recharge Voltage Threshold                               |                                                                 |       | 4.00              |       | V                    |

|                                           | urrent Regulation                                                | ,                                                               |       |                   |       | '                    |

| $I_{CH\_CC}$                              | Constant-Current Mode ADP Charge Current                         | $R_{ISETA} = 1.24k\Omega$ (for 0.8A) (Can be set to up to 1.2A) |       | 800               |       | mA                   |

|                                           | USB Charge Current                                               | USBSEL = H, PWR_ID = L                                          |       | 500               |       | mA                   |

|                                           | USB Charge Current                                               | USBSEL = L, PWR_ID = L                                          |       | 100               |       | mA                   |

| K <sub>ISET</sub>                         | Charge Current Set Factor: I <sub>CH_CC</sub> /I <sub>ISET</sub> | Constant Current Mode                                           |       | 800               |       | mA/ <sub>mA</sub>    |

| I <sub>CH_PRE</sub>                       | Preconditioning Charge Current                                   | $R_{ISETA} = 1.24k\Omega$                                       |       | 12                |       | % I <sub>CH CC</sub> |

| I <sub>CH_TERM</sub>                      | Charge Termination Threshold Current                             | DEN                                                             |       | 5                 |       | % I <sub>CH_CC</sub> |

| Charging                                  |                                                                  | '                                                               |       |                   |       |                      |

| R <sub>DS(ON),CHG</sub>                   | On-Resistance of Charging Transistor                             | SYSOUT to BAT Switch                                            |       | 0.6               | 0.9   | Ω                    |

|                                           | trol / Protection                                                | •                                                               |       |                   |       |                      |

| V <sub>PWR HOLD</sub> ,                   | Input High Threshold                                             |                                                                 | 1.4   |                   |       | V                    |

| V <sub>PWR_ON</sub> , V <sub>USBSEL</sub> | Input Low Threshold                                              |                                                                 |       |                   | 0.3   | V                    |

| V <sub>INT</sub> , V <sub>STAT</sub>      | Output Low Voltage                                               | Pin Sinks 4mA                                                   |       |                   | 0.4   | V                    |

| V <sub>OVP</sub>                          | Over-Voltage Protection Threshold                                |                                                                 |       | 4.3               |       | V                    |

| $I_{OCP}$                                 | Over Current Protection Threshold                                |                                                                 |       | 105               |       | % I <sub>CH_CC</sub> |

| T <sub>C</sub>                            | Constant Current Mode Time Out                                   |                                                                 |       | 3                 |       | Hours                |

| T <sub>K</sub>                            | Trickle Charge Time Out                                          | $C_{CT} = 100nF$                                                |       | T <sub>c</sub> /8 |       | Hours                |

| T <sub>V</sub>                            | Constant Voltage Mode Time Out                                   |                                                                 |       | 3                 |       | Hours                |

| $I_{TS}$                                  | Current Source from TS Pin                                       |                                                                 | 69    | 75                | 79    | μA                   |

| TC                                        | TC II . T                                                        | Falling Threshold                                               | 318   | 331               | 346   | mV                   |

| $TS_1$                                    | TS Hot Temperature Fault                                         | Hysteresis                                                      |       | 25                |       | mV                   |

| TC                                        | TO CALLE                                                         | Rising Threshold                                                | 2.30  | 2.39              | 2.48  | V                    |

| $TS_2$                                    | TS Cold Temperature Fault                                        | Hysteresis                                                      |       | 25                |       | mV                   |

| T <sub>LOOP_IN</sub>                      | Thermal Loop Entering Threshold                                  |                                                                 |       | 115               |       | °C                   |

| T <sub>LOOP OUT</sub>                     | Thermal Loop Exiting Threshold                                   |                                                                 |       | 85                |       | °C                   |

| T <sub>REG</sub>                          | Thermal Loop Regulation                                          |                                                                 |       | 100               |       | °C                   |

| 1120                                      | ches / SYSOUT LDO                                                |                                                                 |       |                   |       | *                    |

| R <sub>DS(ON)</sub> ,<br>BAT-SYSOUT       | On-Resistance of BAT-SYSOUT Load Switch                          |                                                                 |       | 100               | 150   | mΩ                   |

| R <sub>DS(ON)</sub> , PWR_IN-SYSOUT       | On-Resistance of PWR_IN-SYSOUT Load Switch                       |                                                                 |       | 0.2               | 0.3   | Ω                    |

|                                           | PWR_IN-SYSOUT Current Limit                                      |                                                                 |       | 2                 |       | А                    |

|                                           | PWR_IN-SYSOUT Current Limit                                      | USBSEL = High, PWR_ID = L<br>USBSEL = Low, PWR_ID = L           | 400   | 450<br>100        | 500   | mA<br>mA             |

|                                           | BAT-SYSOUT Current Limit                                         | OSBSEL - LOW, I WK_ID - L                                       |       | 2                 |       | A                    |

|                                           | DAT-313001 CUITEIL LIIIL                                         |                                                                 |       |                   | 1     | _ A                  |

<sup>1.</sup> Specification over the -40°C to +85°C operating temperature range is assured by design, characterization and correlation with statistical process controls.

## Electrical Characteristics (continued)<sup>1</sup>

$V_{PWR\_IN} = 5V$ ,  $V_{PWR\_ID} = 5V$ ,  $V_{BAT} = 3.6V$ , -40°C  $\leq T_A \leq +85$ °C, unless noted otherwise. Typical values are  $T_A = 25$ °C.

| Symbol                                     | Description                               | Conditions                                                                                                                 | Min   | Тур       | Max                 | Units   |

|--------------------------------------------|-------------------------------------------|----------------------------------------------------------------------------------------------------------------------------|-------|-----------|---------------------|---------|

| Step-Dowi                                  | n Buck Regulator (Buck1)                  |                                                                                                                            |       |           |                     |         |

| V <sub>INBUCK</sub>                        | Input Voltage Range                       |                                                                                                                            | 2.7   |           | 5.5                 | V       |

| V <sub>OUT</sub>                           | Output Voltage Programmable Range         | Using External Feedback Resistors, No Load                                                                                 | 0.6   |           | V <sub>INBUCK</sub> | V       |

| $V_{REG}$                                  | Output Voltage Accuracy                   | $I_{OUT} = 10 \text{mA}$                                                                                                   | 0.582 | 0.600     | 0.618               | V       |

| I <sub>LIM</sub>                           | P-Channel Current Limit                   |                                                                                                                            |       | 2600      |                     | mA      |

| R <sub>DS(ON)H</sub>                       | High-Side Switch On-Resistance            |                                                                                                                            |       | 450       |                     | mΩ      |

| R <sub>DS(ON)L</sub>                       | Low-Side Switch On-Resistance             |                                                                                                                            |       | 400       |                     | mΩ      |

| $\Delta V_{OUT} / (V_{OUT} \Delta V_{IN})$ | Line Regulation                           |                                                                                                                            |       | 0.2       |                     | %/V     |

| Fosc                                       | Oscillator Frequency                      |                                                                                                                            |       | 1.5       |                     | MHz     |

|                                            | n Buck Regulator (Buck2)                  |                                                                                                                            |       |           |                     |         |

| $V_{INBUCK}$                               | Input Voltage Range                       |                                                                                                                            | 2.7   |           | 5.5                 | V       |

| V <sub>FB</sub>                            | Feedback Voltage Programmable<br>Range    | Using I <sup>2</sup> C, with Default FB = 0.6V                                                                             | 0.5   |           | 0.7                 | V       |

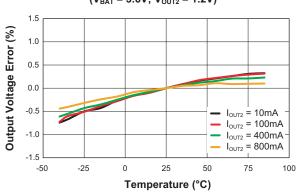

| $V_{REG}$                                  | Output Voltage Accuracy                   | $I_{OUT} = 10$ mA                                                                                                          | -3    |           | +3                  | %       |

| I <sub>LIM</sub>                           | P-Channel Current Limit                   | 2001 201111                                                                                                                |       | 2600      | 1.5                 | mA      |

| R <sub>DS(ON)H</sub>                       | High-Side Switch On-Resistance            |                                                                                                                            |       | 450       |                     | mΩ      |

| R <sub>DS(ON)L</sub>                       | Low-Side Switch On-Resistance             |                                                                                                                            |       | 400       |                     | mΩ      |

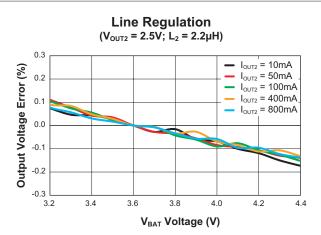

| $\Delta V_{OUT}$                           | Line Regulation                           |                                                                                                                            |       | 0.2       |                     | %/V     |

| $(V_{OUT} \Delta V_{IN})$ $F_{OSC}$        | Oscillator Frequency                      |                                                                                                                            |       | 1.5       |                     | MHz     |

|                                            | out Regulator (LDO1)                      |                                                                                                                            |       | 1.5       |                     | 11112   |

| V <sub>INLDO</sub>                         | Input Voltage Range                       |                                                                                                                            | 2.7   |           | 5.5                 | V       |

| V INLDO                                    | Input voitage Kange                       | $I_{LDO} = 1$ mA to 300mA, S1 = 0, S2 = 0                                                                                  | 2.91  | 3.00      | 3.09                | V       |

| $V_{\scriptscriptstyle LDO}$               | LDO Output Voltage                        | $I_{LDO} = 1 \text{ mA to } 300 \text{ mA}, S1 = 0, S2 = 0$<br>$I_{LDO} = 1 \text{ mA to } 300 \text{ mA}, S1 = 0, S2 = 1$ | 3.20  | 3.30      | 3.40                | V       |

| V LDO                                      | LDO Output Voltage                        | $I_{LDO} = 1 \text{mA to } 300 \text{mA}, S1 = 0, S2 = 1$<br>$I_{LDO} = 1 \text{mA to } 300 \text{mA}, S1 = 1, S2 = 0$     | 2.71  | 2.80      | 2.89                | V       |

| $I_Q$                                      | LDO Quiescent Current                     | V <sub>INLDO</sub> = 5V, added quiescent current when LDO is enabled                                                       | 2.71  | 50        | 90                  | μΑ      |

|                                            | Line Regulation                           | $I_{LDO} = 10 \text{mA}$                                                                                                   |       | 0.09      |                     | %/V     |

|                                            | Dropout Voltage                           | $I_{LDO} = 300 \text{mA}$                                                                                                  |       | 100       | 170                 | mV      |

| $I_{LDO}$                                  | LDO Maximum Load Current                  | 1LD0 - 300111A                                                                                                             | 500   | 100       | 170                 | mA      |

| I <sub>LDO(LIM)</sub>                      | LDO Current Limit                         |                                                                                                                            | 300   | 800       |                     | mA      |

|                                            | out Regulator (LDO2)                      |                                                                                                                            |       | 800       |                     | IIIA    |

| V <sub>INLDO</sub>                         | Input Voltage Range                       |                                                                                                                            | 2.7   |           | 5.5                 | V       |

|                                            | ·                                         | I 1 A t- 00 A                                                                                                              |       | 1.2       |                     |         |

| $V_{LDO}$ $I_{O}$                          | LDO Output Voltage  LDO Quiescent Current | $I_{LDO}$ = 1mA to 80mA<br>$V_{INLDO}$ = 5V, added quiescent current when                                                  | 1.164 | 1.2<br>35 | 1.236               | V<br>μA |

| ±Q                                         |                                           | LDO is enabled                                                                                                             |       |           | 00                  | · .     |

|                                            | Line Regulation                           | $I_{LDO} = 10 \text{mA}$                                                                                                   |       | 0.09      |                     | %/V     |

| ${ m I}_{\sf LDO}$                         | LDO Maximum Load Current                  |                                                                                                                            | 200   |           |                     | mA      |

| $I_{\text{LDO(LIM)}}$                      | LDO Current Limit                         |                                                                                                                            |       | 800       |                     | mA      |

|                                            | out Regulator (LDO3)                      |                                                                                                                            | ,     |           |                     |         |

| $V_{\text{INLDO}}$                         | Input Voltage Range                       |                                                                                                                            | 2.7   |           | 5.5                 | V       |

|                                            | Output Voltage Range                      | Using I <sup>2</sup> C. Default=1.2V                                                                                       | 0.8   |           | 1.4                 | V       |

| V <sub>LDO</sub>                           | LDO Output Voltage                        | $I_{\text{LDO}} = 1 \text{mA to } 80 \text{mA}$                                                                            | -3    |           | +3                  | %       |

| $I_Q$                                      | LDO Quiescent Current                     | $V_{\text{INLDO}} = 5V$ , added quiescent current when LDO is enabled                                                      |       | 35        | 80                  | μΑ      |

|                                            | Line Regulation                           | $I_{LDO} = 10 \text{mA}$                                                                                                   |       | 0.09      |                     | %/V     |

| $I_{LDO}$                                  | LDO Maximum Load Current                  |                                                                                                                            | 200   |           |                     | mA      |

| $I_{LDO(LIM)}$                             | LDO Current Limit                         |                                                                                                                            |       | 800       |                     | mA      |

<sup>1.</sup> Specification over the -40°C to +85°C operating temperature range is assured by design, characterization and correlation with statistical process controls.

# **AAT3608**

# Compact Seven-Channel Regulator with Li+/Polymer Linear Battery Charger and I2C Interface

## **Electrical Characteristics (continued)**<sup>1</sup>

$V_{PWR\_IN} = 5V$ ,  $V_{PWR\_ID} = 5V$ ,  $V_{BAT} = 3.6V$ , -40°C  $\leq T_A \leq +85$ °C, unless noted otherwise. Typical values are  $T_A = 25$ °C.

| Symbol                | Description                                    | Conditions                                                         | Min   | Тур  | Max   | Units |

|-----------------------|------------------------------------------------|--------------------------------------------------------------------|-------|------|-------|-------|

| Low-Dropo             | out Regulator (LDO4)                           |                                                                    |       |      |       |       |

| $V_{INLDO}$           | Input Voltage Range                            |                                                                    | 2.7   |      | 5.5   | V     |

| $V_{\text{LDO}}$      | LDO Output Voltage                             | I <sub>LDO</sub> = 1mA to 50mA                                     | 2.425 | 2.5  | 2.575 | V     |

| $I_Q$                 | LDO Quiescent Current                          | $V_{INLDO}$ = 5V, added quiescent current when LDO is enabled      |       | 50   | 80    | μΑ    |

|                       | Line Regulation                                | $I_{LDO} = 10 \text{mA}$                                           |       | 0.09 |       | %/V   |

| $I_{LDO}$             | LDO Maximum Load Current                       |                                                                    | 200   |      |       | mA    |

| $I_{\text{LDO(LIM)}}$ | LDO Current Limit                              |                                                                    |       | 800  |       | mA    |

| Low-Dropo             | out Regulator (LDO5)                           |                                                                    |       |      |       |       |

| $V_{INLDO}$           | Input Voltage Range                            |                                                                    | 2.7   |      | 5.5   | V     |

| $V_{LDO}$             | LDO Output Voltage                             | $I_{LDO} = 1 \text{mA to } 50 \text{mA}$                           | 3.2   | 3.3  | 3.4   | V     |

| $I_Q$                 | LDO Quiescent Current                          | $V_{INLDO}$ = 5V, added quiescent current when LDO is enabled      |       | 50   | 80    | μA    |

|                       | Line Regulation                                | $I_{LDO} = 10 \text{mA}$                                           |       | 0.09 |       | %/V   |

| $I_{LDO}$             | LDO Maximum Load Current                       |                                                                    | 200   |      |       | mA    |

| I <sub>LDO(LIM)</sub> | LDO Current Limit                              |                                                                    |       | 800  |       | mA    |

| Reset and             | Low-Battery Comparator                         |                                                                    | ·     |      |       |       |

|                       | Buck2 Power OK Threshold                       | Rising threshold                                                   |       |      | 91    | %     |

|                       | Buckz Power OK Tiffeshold                      | Hysteresis                                                         |       | 3    |       | %     |

|                       | Reset Time                                     | From Power OK of BUCK <sub>2</sub> output to RESET pin rising edge |       | 200  |       | ms    |

|                       | Law Dattery Threehold Veltage                  | Falling Edge                                                       | 0.96  | 1.0  | 1.04  | V     |

|                       | Low-Battery Threshold Voltage                  | Hysteresis                                                         |       | 50   |       | mV    |

| Thermal               |                                                |                                                                    |       |      |       |       |

| T <sub>SD</sub>       | Over-Temperature Shutdown Threshold            | Rising                                                             |       | 140  |       | °C    |

| T <sub>HYS</sub>      | Over-Temperature Shutdown Hysteresis           |                                                                    |       | 15   |       | °C    |

| SCL, SDA (            | I <sup>2</sup> C Interface)                    |                                                                    |       |      |       |       |

| $F_{SCL}$             | Clock Frequency                                |                                                                    | 0     |      | 400   | kHz   |

| $T_{LOW}$             | Clock Low Period                               |                                                                    | 1.3   |      |       | μs    |

| $T_{HIGH}$            | Clock High Period                              |                                                                    | 0.6   |      |       | μs    |

| $T_{HD\_STA}$         | Hold Time for START Condition                  |                                                                    | 0.6   |      |       | μs    |

| T <sub>SU_STA</sub>   | Set-up Time for Repeated START Condition       |                                                                    | 0.6   |      |       | μs    |

| $T_{SU\_DAT}$         | Data Setup Time                                |                                                                    | 100   |      |       | ns    |

| $T_{HD\_DAT}$         | Data Hold Low Time                             |                                                                    |       |      | 0.9   | μs    |

| $T_{SU\_STO}$         | Setup Time for STOP Condition                  |                                                                    | 0.6   |      |       | μs    |

| $T_{BUF}$             | Bus Free Time Between STOP and START Condition |                                                                    | 1.3   |      |       | μs    |

| $V_{IL}$              | Input Threshold Low                            | $2.7V \le V_{IN} \le 5.5V$                                         |       |      | 0.3   | V     |

| V <sub>IH</sub>       | Input Threshold High                           | $2.7V \le V_{IN} \le 5.5V$                                         | 1.4   |      |       | V     |

| I <sub>I</sub>        | Input Leakage Current                          |                                                                    | -1.0  |      | 1.0   | μA    |

| V <sub>OL</sub>       | Output Logic Low (SDA)                         | $I_{PULLUP} = 3mA$                                                 |       |      | 0.3   | V     |

<sup>1.</sup> Specification over the -40°C to +85°C operating temperature range is assured by design, characterization and correlation with statistical process controls.

## **Typical Characteristics-Charger**

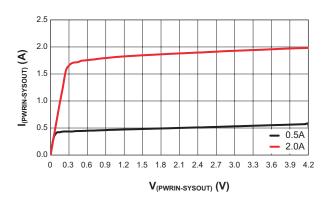

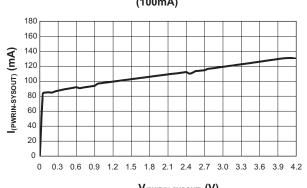

#### **Power-In to SYSOUT Switch Current Limit**

# Power-In to SYSOUT Switch Current Limit (100mA)

V<sub>(PWRIN-SYSOUT)</sub> (V)

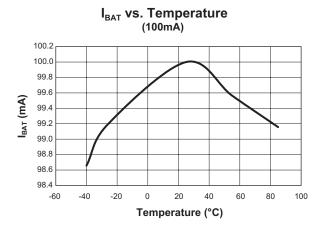

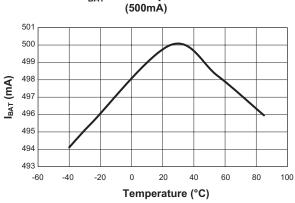

I<sub>BAT</sub> vs. Temperature

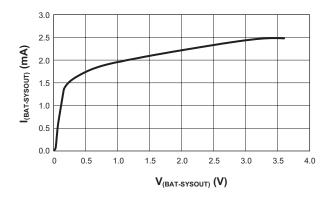

### Ideal Diode Load Switch between $V_{BAT}$ and $V_{SYSOUT}$

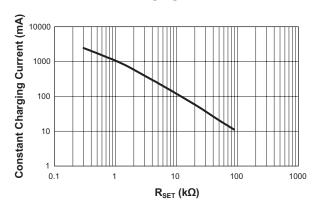

### Constant Charging Current vs. R<sub>SET</sub>

## **Typical Characteristics-Charger**

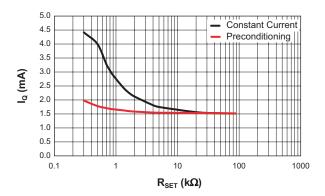

Adapter Mode Supply Current vs. R<sub>SET</sub> Resistor

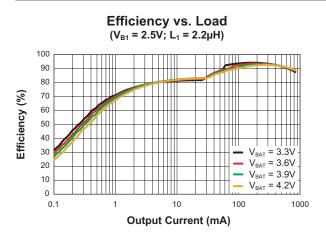

## Typical Characteristics-Buck1

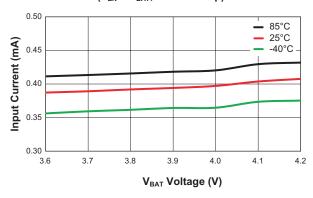

# No Load Total Input Current vs. $V_{BAT}$ Voltage $(V_{EN} = V_{BAT}; Closed Loop)$

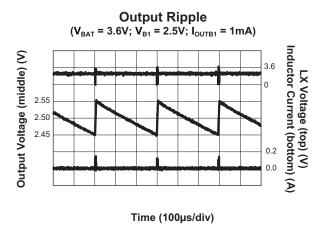

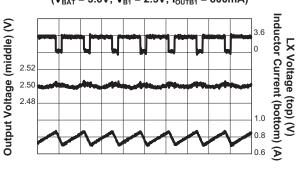

## Output Ripple (V<sub>BAT</sub> = 3.6V; V<sub>B1</sub> = 2.5V; I<sub>OUTB1</sub> = 800mA)

Time (500ns/div)

Time (200µs/div)

## Typical Characteristics-Buck1 (continued)

2.3 2.1

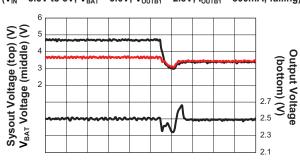

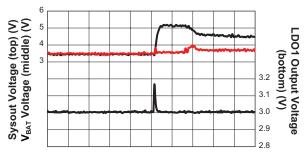

### System Line Transient Response $(V_{IN} = 3.5V \text{ to } 5V; V_{BAT} = 3.6V; V_{OUTB1} = 2.5V; I_{OUTB1} = 800\text{mA}; rising)$

Sysout Voltage (top) (V) V<sub>BAT</sub> Voltage (middle) (V) 5 Output Voltage (bottom) (V)

Time (200µs/div)

### **System Load Transient Response** $(I_{OUTB1} = 80 \text{mA} \text{ to } 800 \text{mA}; V_{BAT} = 3.6 \text{V}; C_{OUTB1} = 4.7 \mu\text{F}; C_{FF1} = 0 \text{pF})$

-800mA 1.0 0.5 **Output Current Output Voltage** (N) (mottom) 2.7 80m/ (top) (A) 2.5 2.1

Time (100µs/div)

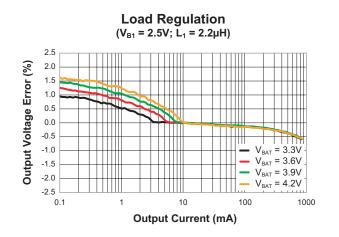

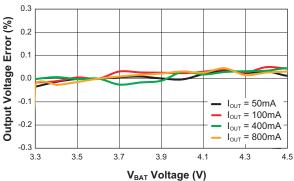

### **Line Regulation** $(V_{OUT1} = 2.5V; L_1 = 2.2\mu H)$

## **Output Voltage Error vs. Temperature**

$(V_{BAT} = 3.6V; V_{OUT1} = 2.5V)$

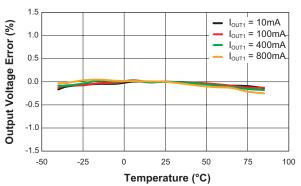

#### **Switching Frequency vs. Temperature** $(V_{IN} = 3.6V; V_{OUT1} = 2.5V; I_{OUT1} = 800mA)$

### Switching Frequency vs. V<sub>BAT</sub> Voltage $(V_{OUT1} = 2.5V; I_{OUT1} = 800mA)$

## Typical Characteristics-Buck1 (continued)

###

Time (100µs/div)

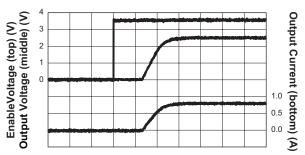

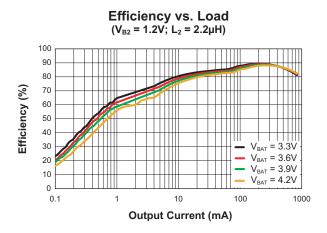

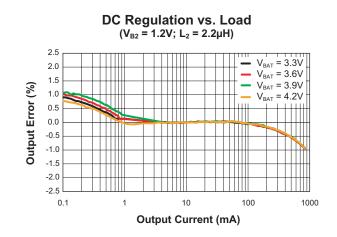

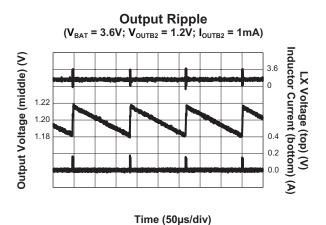

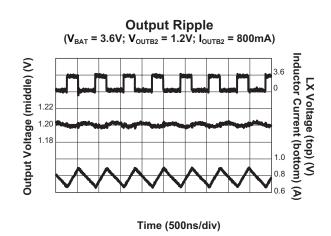

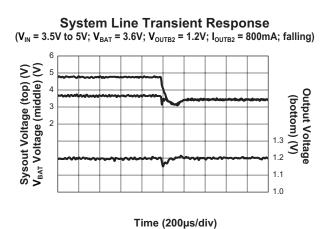

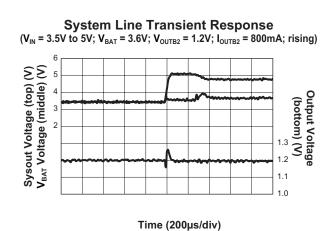

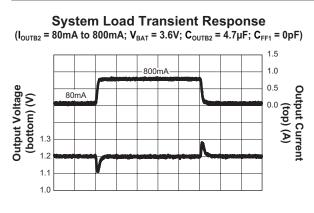

## **Typical Characteristics-Buck2**

## Typical Characteristics-Buck2 (continued)

Time (100µs/div)

# Output Voltage Error vs. Temperature $(V_{BAT} = 3.6V; V_{OUT2} = 1.2V)$

Output Current (bottom) (A)

Output Current (bottom) (A)

Output Current (bottom) (A)

Time (100µs/div)

## **Typical Characteristics-LD01**

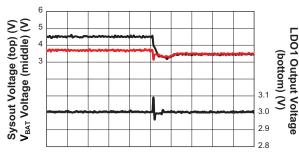

### System Line Transient Response

$(V_{IN} = 3.5V \text{ to 5V}; V_{BAT} = 3.6V; V_{LDO1} = 3V; I_{LDO1} = 300\text{mA}; rising)$

Time (200µs/div)

### System Line Transient Response

$(V_{IN} = 3.5V \text{ to 5V}; V_{BAT} = 3.6V; V_{LDO1} = 3V; I_{LDO1} = 300\text{mA}; falling)$

Time (200µs/div)

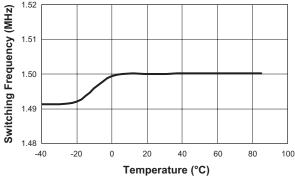

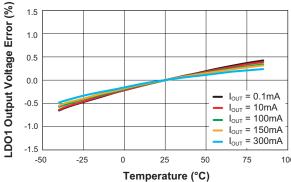

## Output Voltage Error vs. Temperature

$(V_{BAT} = 3.6V; V_{LDO1} = 3.0V)$

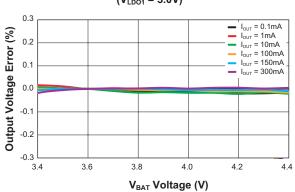

## Line Regulation

$(V_{LDO1} = 3.0V)$

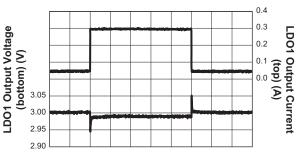

#### Load Transient Response

$(I_{LDO1} = 30 \text{mA to } 300 \text{mA}; V_{BAT} = 3.6 \text{V}; V_{LDO1} = 3 \text{V}; C_{LDO1} = 4.7 \mu\text{F})$

Time (200µs/div)

## Load Regulation (V<sub>BAT</sub> = 3.6V; V<sub>LDO1</sub> = 3.0V)

10 Output Current (mA)

100

0.1

1000

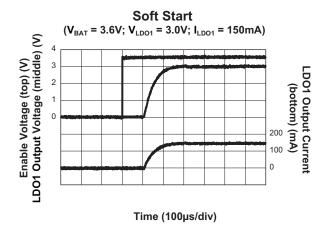

## **Typical Characteristics-LDO1 (continued)**

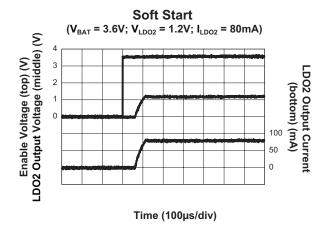

## **Typical Characteristics-LD02**

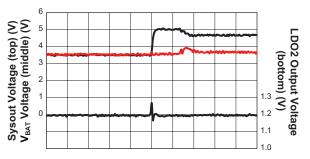

### System Line Transient Response

$(V_{IN} = 3.5V \text{ to } 5V; V_{BAT} = 3.6V; V_{LDO2} = 1.2V; I_{LDO2} = 80\text{mA}; \text{ rising})$

Time (200µs/div)

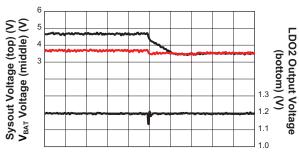

### System Line Transient Response

$(V_{IN} = 3.5V \text{ to 5V}; V_{BAT} = 3.6V; V_{LDO2} = 1.2V; I_{LDO2} = 80\text{mA}; falling)$

Time (200µs/div)

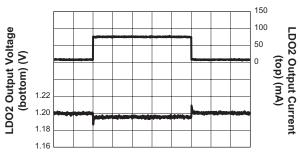

### **Load Transient Response**

$(I_{LDO2} = 8mA \text{ to } 80mA; V_{BAT} = 3.6V; V_{LDO2} = 1.2V; C_{LDO2} = 4.7\mu\text{F})$

Time (200µs/div)

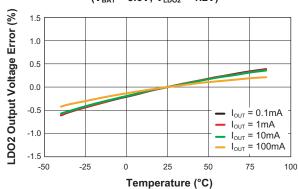

## **Output Voltage Error vs. Temperature**

$(V_{BAT} = 3.6V; V_{LDO2} = 1.2V)$

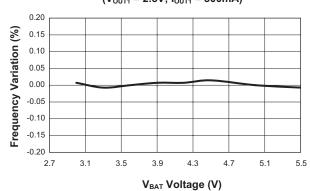

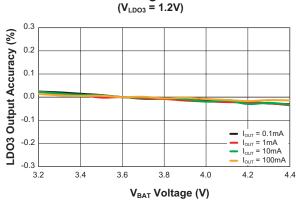

### Line Regulation (V<sub>LDO2</sub> = 1.2V)

0.2

0.1

0.0

-0.1

-0.2

-0.2

-0.1

-0.2

-0.0

-0.1

-0.2

-0.0

-0.1

-0.0

-0.1

-0.0

-0.1

-0.0

-0.1

-0.0

-0.1

-0.0

-0.1

-0.0

-0.1

-0.0

-0.1

-0.0

-0.1

-0.0

-0.1

-0.0

-0.0

-0.0

-0.0

-0.0

-0.0

-0.0

-0.0

-0.0

-0.0

-0.0

-0.0

-0.0

-0.0

-0.0

-0.0

-0.0

-0.0

-0.0

-0.0

-0.0

-0.0

-0.0

-0.0

-0.0

-0.0

-0.0

-0.0

-0.0

-0.0

-0.0

-0.0

-0.0

-0.0

-0.0

-0.0

-0.0

-0.0

-0.0

-0.0

-0.0

-0.0

-0.0

-0.0

-0.0

-0.0

-0.0

-0.0

-0.0

-0.0

-0.0

-0.0

-0.0

-0.0

-0.0

-0.0

-0.0

-0.0

-0.0

-0.0

-0.0

-0.0

-0.0

-0.0

-0.0

-0.0

-0.0

-0.0

-0.0

-0.0

-0.0

-0.0

-0.0

-0.0

-0.0

-0.0

-0.0

-0.0

-0.0

-0.0

-0.0

-0.0

-0.0

-0.0

-0.0

-0.0

-0.0

-0.0

-0.0

-0.0

-0.0

-0.0

-0.0

-0.0

-0.0

-0.0

-0.0

-0.0

-0.0

-0.0

-0.0

-0.0

-0.0

-0.0

-0.0

-0.0

-0.0

-0.0

-0.0

-0.0

-0.0

-0.0

-0.0

-0.0

-0.0

-0.0

-0.0

-0.0

-0.0

-0.0

-0.0

-0.0

-0.0

-0.0

-0.0

-0.0

-0.0

-0.0

-0.0

-0.0

-0.0

-0.0

-0.0

-0.0

-0.0

-0.0

-0.0

-0.0

-0.0

-0.0

-0.0

-0.0

-0.0

-0.0

-0.0

-0.0

-0.0

-0.0

-0.0

-0.0

-0.0

-0.0

-0.0

-0.0

-0.0

-0.0

-0.0

-0.0

-0.0

-0.0

-0.0

-0.0

-0.0

-0.0

-0.0

-0.0

-0.0

-0.0

-0.0

-0.0

-0.0

-0.0

-0.0

-0.0

-0.0

-0.0

-0.0

-0.0

-0.0

-0.0

-0.0

-0.0

-0.0

-0.0

-0.0

-0.0

-0.0

-0.0

-0.0

-0.0

-0.0

-0.0

-0.0

-0.0

-0.0

-0.0

-0.0

-0.0

-0.0

-0.0

-0.0

-0.0

-0.0

-0.0

-0.0

-0.0

-0.0

-0.0

-0.0

-0.0

-0.0

-0.0

-0.0

-0.0

-0.0

-0.0

-0.0

-0.0

-0.0

-0.0

-0.0

-0.0

-0.0

-0.0

-0.0

-0.0

-0.0

-0.0

-0.0

-0.0

-0.0

-0.0

-0.0

-0.0

-0.0

-0.0

-0.0

-0.0

-0.0

-0.0

-0.0

-0.0

-0.0

-0.0

-0.0

-0.0

-0.0

-0.0

-0.0

-0.0

-0.0

-0.0

-0.0

-0.0

-0.0

-0.0

-0.0

-0.0

-0.0

-0.0

-0.0

-0.0

-0.0

-0.0

-0.0

-0.0

-0.0

-0.0

-0.0

-0.0

-0.0

-0.0

-0.0

-0.0

-0.0

-0.0

-0.0

-0.0

-0.0

-0.0

-0.0

-0.0

-0.0

-0.0

-0.0

-0.0

-0.0

-0.0

-0.0

-0.0

-0.0

-0.0

-0.0

-0.0

-0.0

-0.0

-0.0

-0.0

-0.0

-0.0

-0.0

-0.0

-0.0

-0.0

-0.0

-0.0

-0.0

-0.0

-0.0

-0.0

-0.

LDO2 Output Accuracy (%)

3.2

3.4

V<sub>BAT</sub> Voltage (V)

- I<sub>OUT</sub> = 100mA

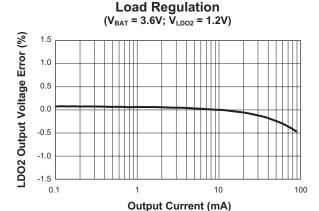

## **Typical Characteristics-LDO2 (continued)**

## **Typical Characteristics-LD03**

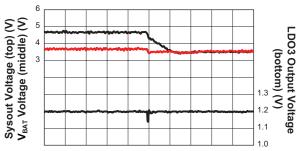

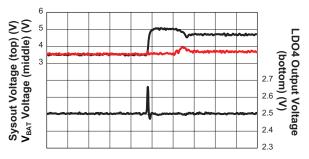

### **System Line Transient Response** $(V_{IN} = 3.5V \text{ to } 5V; V_{BAT} = 3.6V; V_{LDO3} = 1.2V; I_{LDO3} = 80\text{mA}; rising)$

Sysout Voltage (top) (V) V<sub>BAT</sub> Voltage (middle) (V) LDO3 Output Voltage (bottom) (V)

Time (200µs/div)

1.0

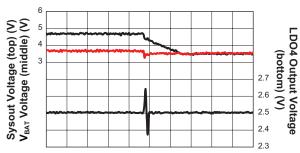

### **System Line Transient Response**

$(V_{IN} = 3.5V \text{ to } 5V; V_{BAT} = 3.6V; V_{LDO3} = 1.2V; I_{LDO3} = 80\text{mA}; \text{ falling})$

Time (200µs/div)

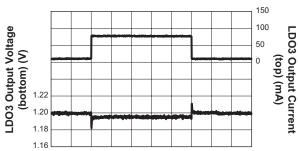

## **Load Transient Response**

$(I_{LDO3} = 8mA \text{ to } 80mA; V_{BAT} = 3.6V; C_{LDO3} = 4.7\mu\text{F})$

Time (200µs/div)

## **Line Regulation**

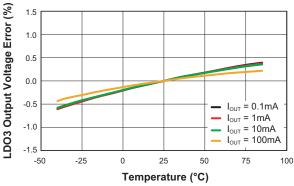

## **Output Voltage Error vs. Temperature**

$(V_{BAT} = 3.6V; V_{LDO3} = 1.2V)$

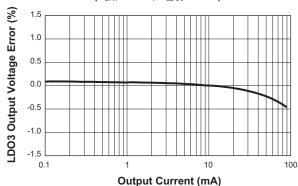

## **Load Regulation**

$(V_{BAT} = 3.6V; V_{LDO3} = 1.2V)$

## **Typical Characteristics-LDO3 (continued)**

## Typical Characteristics-LDO4

### **System Line Transient Response**

$(V_{IN} = 3.5V \text{ to 5V}; V_{BAT} = 3.6V; V_{LDO4} = 2.5V; I_{LDO4} = 50\text{mA}; \text{ rising})$

Time (200µs/div)

### **System Line Transient Response**

$(V_{IN} = 3.5V \text{ to 5V}; V_{BAT} = 3.6V; V_{LDO4} = 2.5V; I_{LDO4} = 50\text{mA}; \text{ falling})$

Time (200µs/div)

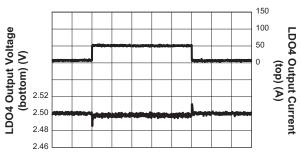

### **Load Transient Response**

$(I_{LDO4} = 5mA \text{ to } 50mA; V_{BAT} = 3.6V; V_{LDO4} = 2.5V; C_{LDO4} = 4.7\mu\text{F})$

Time (200µs/div)

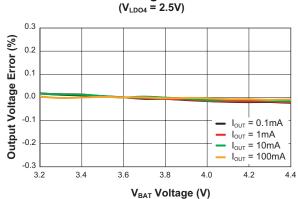

## **Line Regulation**

## **Output Voltage Error vs. Temperature**

$(V_{BAT} = 3.6V; V_{LDO4} = 2.5V)$

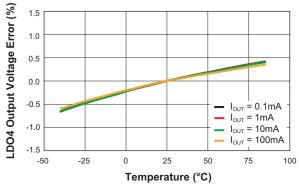

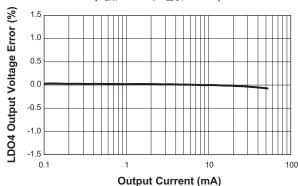

## **Load Regulation**

$(V_{BAT} = 3.6V; V_{LDO4} = 2.5V)$

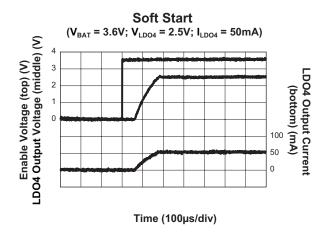

## **Typical Characteristics-LD04 (continued)**

## **Typical Characteristics-LD05**

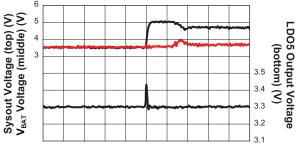

## **System Line Transient Response**

$(V_{IN} = 3.5V \text{ to } 5V; V_{BAT} = 3.6V; V_{LDO5} = 3.3V; I_{LDO5} = 50\text{mA}; \text{ rising})$

Time (200µs/div)

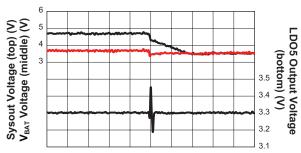

## **System Line Transient Response**

$(V_{IN} = 3.5V \text{ to 5V}; V_{BAT} = 3.6V; V_{LDO5} = 3.3V; I_{LDO5} = 50\text{mA}; \text{ falling})$

Time (200µs/div)

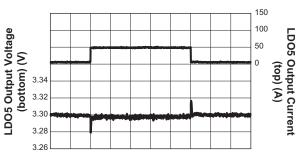

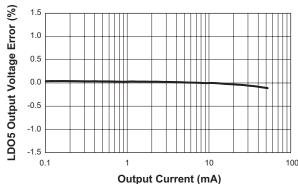

## **Load Transient Response**

$(I_{LDO5} = 5mA \text{ to } 50mA; V_{BAT} = 3.9V; C_{LDO5} = 4.7\mu\text{F})$

Time (200µs/div)

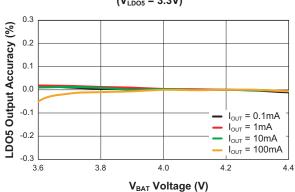

## **Line Regulation**

$(V_{LDO5} = 3.3V)$

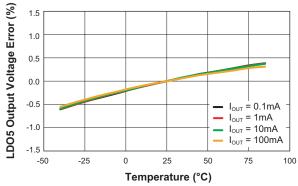

## **Output Voltage Error vs. Temperature**

$(V_{BAT} = 3.6V; V_{LDO4} = 3.3V)$

## **Load Regulation**

$(V_{BAT} = 3.6V; V_{LDO5} = 3.3V)$

## **Typical Characteristics-LDO5 (continued)**

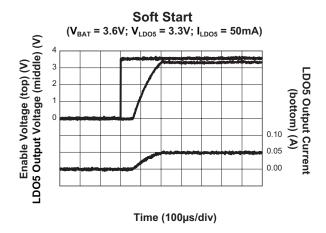

## **Functional Block Diagram**

## **Functional Description**

The AAT3608 is a complete power management solution. It seamlessly integrates a battery charger with two step-down converters and five low-dropout regulators to provide power from either an external power source or a single-cell Lithium Ion/Polymer battery. Internal load switches allow the converters to operate from the best available power source.

If only the battery is available, then the voltage converters are powered directly from the battery through a 100 m $\Omega$  load switch (BAT to SYSOUT). During this condition, the charger is put into sleep mode and draws less than 1 $\mu$ A quiescent current. If the system is connected to a wall adapter, then the voltage converters are powered directly from the adapter through a 200m $\Omega$  load-switch (PWR\_IN to SYSOUT) and the battery is disconnected from the voltage converter inputs. This allows the sys-

tem to operate regardless of the state of the battery. It can even operate with no battery.

## System Output (SYSOUT)

Intelligent control of the integrated load switches is managed by the switch control circuitry. If the voltage across PWR\_IN and GND pin is above the UVLO typical threshold voltage of 4.5, then the switch control will automatically short the load switch connecting PWR\_IN to SYSOUT. Additionally, the charging switch will be enabled and switch connecting BAT and SYSOUT will be turned off. The location of the two switches and the battery charging switch allows the step-down converter and LDO to always have the best available source of power. Furthermore, AAT3806 control logic allows the voltage converters to operate with no battery, or with a battery voltage below the trickle charge threshold.

## **Battery Charging**

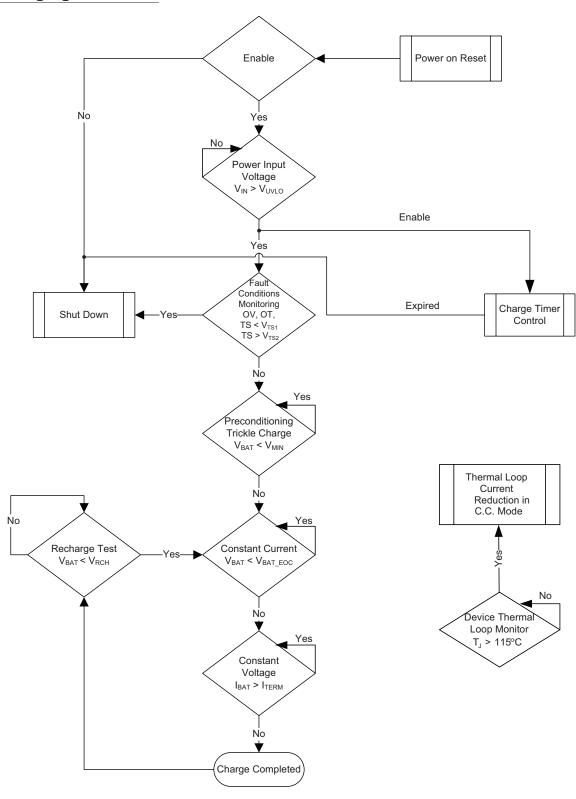

Battery charging commences only after the AAT3608 battery charger checks several conditions in order to maintain a safe charging environment. When an adapter input is connected to PWR\_IN and is greater than 4.5V, the  $\rm EN_{CHG}$  bit is set (default) and the PWR\_HOLD signal is high, the charger is enabled. The charger can be disabled by clearing the  $\rm EN_{CHG}$  bit through the  $\rm I^2C$  interface.

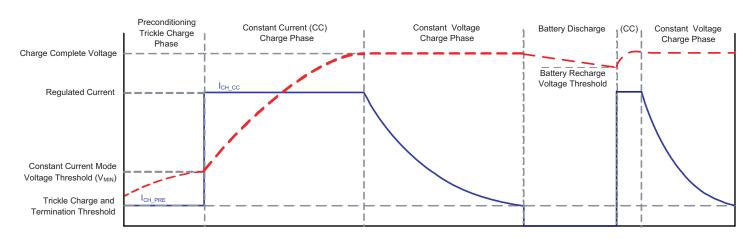

Figure 1 illustrates the entire battery charging profile or operation, which consists of three phases:

- 1. Preconditioning (Trickle) Charge

- 2. Constant Current Charge

- 3. Constant Voltage Charge

During battery charging, the battery charger initially checks the condition of the battery and determines which charging mode to apply. If the battery voltage is below  $V_{\text{MIN}}$ , then the battery charger initiates trickle charge mode and charges the battery at 12% of the programmed constant-current magnitude. For example, if the programmed current ( $I_{\text{SETA}}$ ) is 500mA, then the trickle charge current will be 60mA. Trickle charge is a safety precaution for a deeply discharged cell. It is intended to reduce stress on the battery, but also reduces the power dissipation in the internal series pass MOSFET when the input-output voltage differential is at its highest.

Trickle charge continues until the battery voltage reaches 2.8V. At this point the battery charger begins constant-current charging. The current level for this mode is programmed using a resistor from the ISETA pin to ground, or can be selected through the USBSEL pin with

settings of 100mA or 500mA; refer to the logic settings in Table 2. Constant-current charging continues until the voltage reaches the charge voltage regulation point.

$V_{\text{BAT\_REG}}$  is factory programmed to 4.2V (nominal). Charging in constant-voltage mode will continue until the charge current has reduced to the charge termination current threshold. After the charge cycle is complete, the battery charger turns off the series pass device and automatically goes into a power saving sleep mode. During this time, the series pass device will block current in both directions to prevent the battery from discharging through the battery charger.

The battery charger will remain in sleep mode even if the charger source is disconnected. It will come out of sleep mode when either the battery terminal voltage drops below the  $V_{\text{RCH}}$  threshold, or the charging source is removed and reconnected. In all cases, the battery charger will monitor all parameters and resume charging in the most appropriate mode.

### **Battery Temperature Fault Monitoring**

The TS pin is available to monitor the battery temperature. Connect a 10k NTC resistor from the TS pin to ground. The TS pin outputs a  $75\mu\text{A}$  constant current into the resistor and monitors the voltage to ensure that the battery temperature does not fall outside the operating limits depending on the temperature coefficient of the resistor used. When the voltage goes above 2.39V or goes below 0.331V, the charging will be suspended. A Beta range of 3300 to 4000 will place the typical charging temperature between -4°C and 48°C.

Figure 1: Current vs. Voltage Profile During Charging Phases.

## **Battery Charging Flowchart**

## **Buck Regulators**

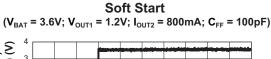

The AAT3608 step-down converters are peak current mode PWM converters operating at 1.5MHz frequency. The input voltage range is 2.7V to 5.5V. The converters provide internal compensation. Power devices are sized for 800mA output current while maintaining over 85% efficiency at full load. Peak efficiency is above 90%. Light load efficiency is maintained at greater than 80% down to 85% of full load current. Soft start limits the current surge seen at the input and eliminates output voltage overshoot.

The input pin, INBUCK (Pin 24) must be connected to the SYSOUT output pin. The Buck1 output voltage is adjustable from 0.6V to 5.5V and is programmed through an external resistor divider. Buck2 output default value is set by external resistor feedback and then the feedback voltage can be dynamically adjusted via I<sup>2</sup>C in 12.5mV increments from 0.5V to 0.7V.

For overload conditions, the peak input current is limited. Also, thermal protection completely disables switching if internal dissipation becomes excessive, thus protecting the device from damage. The junction overtemperature threshold is 140°C with 15°C of hysteresis. Under-voltage lockout (UVLO) guarantees sufficient  $V_{\rm IN}$  bias and proper operation of all internal circuits prior to activation.

The current through the P-channel MOSFET (high side) is sensed for current loop control, as well as short circuit and overload protection. A fixed slope compensation signal is added to the sensed current to maintain stability for duty cycles greater than 50%. The peak current mode loop appears as a voltage-programmed current source in parallel with the output capacitor. The output of the voltage error amplifier programs the current mode loop for the necessary peak switch current to force a constant output voltage for all load and line conditions. Internal loop compensation terminates the transconductance voltage error amplifier output. The reference voltage is internally set to program the converter output voltage greater than or equal to 0.6V.

For conditions where the input voltage drops to the output voltage level, the converter duty cycle increases to 100%. As the converter approaches the 100% duty cycle, the minimum off-time initially forces the high side on-time to exceed the 1.5MHz clock cycle and reduces the effective switching frequency. Once the input drops

below the level where the converter can regulate the output, the high side P-channel MOSFET is enabled continuously for 100% duty cycle. At 100% duty cycle the output voltage tracks the input voltage minus the I\*R drop of the high side P-channel MOSFET.

For overload conditions, the peak input current is limited. The bucks use a cycle-by-cycle current limit to protect itself and the load from an external fault condition. Thermal protection completely disables switching when internal dissipation becomes excessive. The junction over-temperature threshold is 140°C with 15°C of hysteresis. Once an over-temperature or over-current fault conditions is removed, the output voltage automatically recovers.

### **Low-Dropout Regulators**

The advanced circuit design of the linear regulators has been specifically optimized for very fast start-up and shutdown timing. These proprietary LDOs are tailored for superior transient response characteristics. These traits are particularly important for applications which require fast power supply timing.

The high-speed turn-on capability is enabled through the implementation of a fast start control circuit, which accelerates the power up behavior of fundamental control and feedback circuits within the LDO regulator. For fast turn-off time response is achieved by an active output pull down circuit, which is enabled when the LDO regulator is placed in the shutdown mode. This active fast shutdown circuit has no adverse effect on normal device operation.

There are two LDO input pins, INLDO (pins 6 and 9), which must be connected to the SYSOUT output pin. The LDO1 output voltage is selectable using pins S1 and S2 as shown in Table 1. LDO2 is fixed at 1.2V, LDO4 is fixed at 2.5V and LDO5 is fixed at 3.3V. LDO3 output default value is 1.2V and then can be dynamically adjusted via  $\rm I^2C$  in 25mV increments from 1.0V to 1.4V.

| S1 | S2 | LD01     |  |

|----|----|----------|--|

| 0  | 0  | 3.0V     |  |

| 0  | 1  | 3.3V     |  |

| 1  | 0  | 2.8V     |  |

| 1  | 1  | Reserved |  |

Table 1: LDO1 Output Voltages.

### **Controlling the System Outputs**

The AAT3608 has a specific startup and shutdown conditions depending on its mode of operation.

#### **Shutdown Mode**

"Shutdown Mode" is defined as the mode where the entire PMU (Power Management Unit) is shut down. This is a state that normally happens after all power has been disconnected from PWR\_IN and BAT. Typically, after power has been applied and the part has been turned on, it will normally never need to be turned off. For GPS applications, the amount of time required for the SOC to start up from shutdown is prohibitively long, so the only time that it will go into Shutdown Mode (from any other mode) is when PWR\_IN is disconnected and the BAT is below the Low-Battery comparator threshold.

#### **Normal Mode**

"Normal Mode" is defined as the mode where all regulators are active. Once the part is in Normal Mode, it will typically go into Sleep or Deep-Sleep Mode when trying to save current.

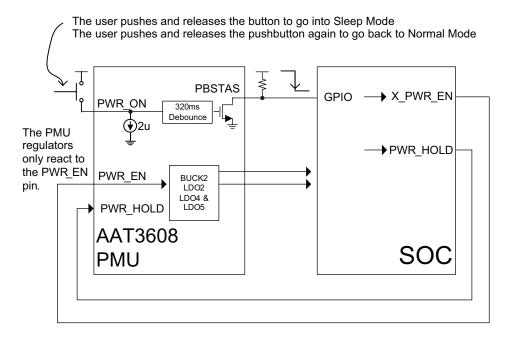

#### **SOC Sleep Mode**

"Sleep Mode" is an SOC-defined mode which simply means that all regulators are shut down except SYSOUT, Buck1, LDO1, and LDO3. To get into this mode from Normal, the SOC will pull the PWR\_EN pin low to turn off LDO2, LDO4, and LDO5. Buck2 can also be controlled by PWR\_EN only if the SOC masks PWR\_EN through I<sup>2</sup>C. From a PMU point of view, it is no different from Normal Mode except for the regulators that have been switched off by pulling PWR EN low.

### **Deep Sleep Mode**

"Deep Sleep Mode" is both an SOC and PMU-defined mode where all regulators have been turned off except for SYSOUT and Buck1. Data is backed up by the SOC and Buck1 stays alive to maintain the memory. LDO4 and LDO5 would be turned off separately by I<sup>2</sup>C, but the DS\_RDY and PWR\_DS I<sup>2</sup>C bits are used to get into and out of Deep Sleep Mode. See the flowchart diagrams for more detail.

### PWR\_ID Pin

The PWR\_ID pin is an input logic pin which determines the current limits and fast charge currents that will be used by PMU. PWR ID settings are listed in Table 2.

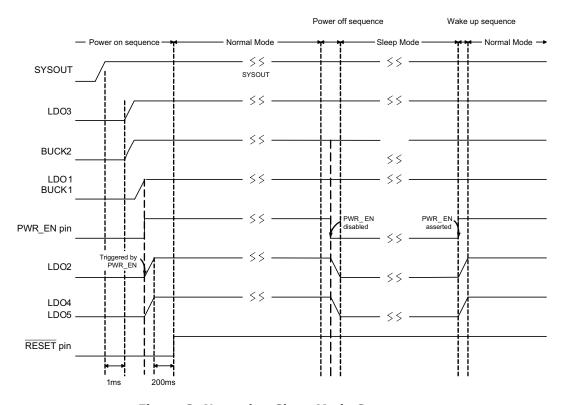

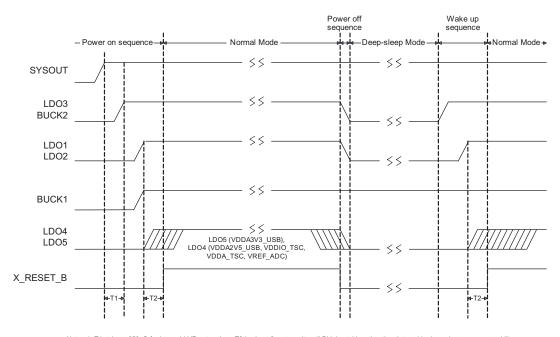

## **Timing Sequences**

The AAT3608 has a specific startup sequence when the device is activated. See the timing diagrams in Figures 2 through 7.

#### RESET

The  $\overline{\text{RESET}}$  pin is an open drain active low output signal for system reset. Connect a pull-up resistor from the  $\overline{\text{RESET}}$  pin to SYSOUT pin with a recommended resistance value of  $100k\Omega$ . After Buck2 and LDO2 reach their target nominal output voltage, a delay of 200ms exists before  $\overline{\text{RESET}}$  goes high; refer to the timing diagram in Figure 2.

| PWR_ID Pin | USBSEL Pin | PWR_IN - SYSOUT Switch Current Limit | Battery Fast Charge Current           |

|------------|------------|--------------------------------------|---------------------------------------|

| L          | L          | 100mA (typical)                      | 100mA (typical)                       |

| L          | Н          | 500mA (typical)                      | 500mA (typical)                       |

| Н          | X          | Up to 1.2A (typical)                 | Set by the resistor at the ISETA pin. |

Table 2: PWR\_ID Settings.

Figure 2: Normal ⇔ Sleep Mode Sequence.

Figure 3: Normal ⇔ Sleep Mode Block Diagram.

# **AAT3608**

# Compact Seven-Channel Regulator with Li+/Polymer Linear Battery Charger and I2C Interface

Notes 1: T1 at least 650µS for internal LVR setup time; T2 is about 2ms to wait until PLL is stable; other time interval is dependent on power stability. Notes 2: After wake-up sequence from Deep-sleep Mode, the power on sequence to Normal Mode is similar to when powering on initially.

Figure 4: Normal  $\Leftrightarrow$  Deep-Sleep Mode Sequence.

Figure 5: Normal Mode → Deep-Sleep Mode → Normal Mode Flowchart.

Figure 6: Normal Mode ⇔ Sleep Mode Flowchart.

Figure 7: System Shutdown ⇔ Normal Mode (Initial Start-Up) Flowchart.

### I<sup>2</sup>C Serial Interface and Programmability

#### **Serial Interface**

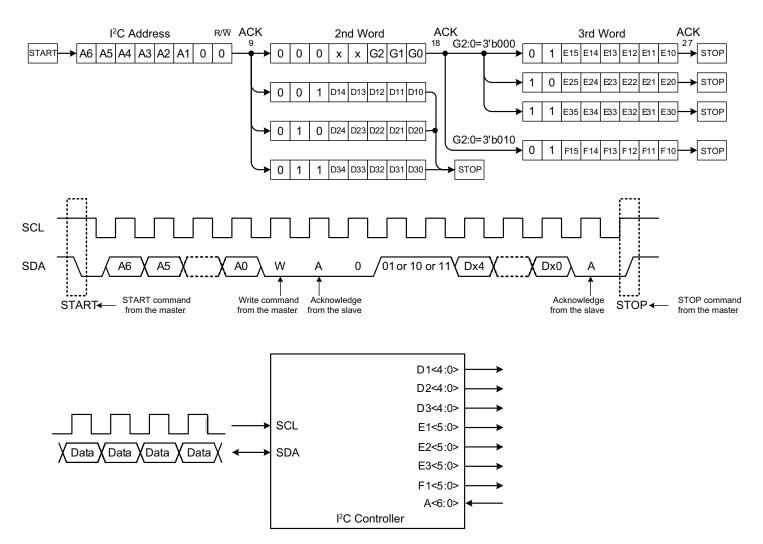

Many of the features of the AAT3608 can be controlled via the  $\rm I^2C$  serial interface. The  $\rm I^2C$  serial interface is a widely used interface where it requires a master to initiate all the communications with the slave devices. The  $\rm I^2C$  protocol consists of 2 active wires, SDA (serial data line) and SCL (serial clock line). Both wires are open drain and require an external pull up resistor to  $\rm Vcc$  (SYSOUT may be used as  $\rm Vcc$ ). The SDA pin serves I/O function, and the SCL pin controls and references the  $\rm I^2C$  bus.  $\rm I^2C$  protocol is a bidirectional bus which allows both read and write actions to take place. The timing diagram in Figure 8 depicts the transmission protocol.

### **START and STOP Conditions**

START and STOP conditions are always generated by the master. Prior to initiating a START condition, both the SDA and SCL pin are idle mode (idle mode is when there is no activity on the bus and SDA and SCL are pulled to Vcc via external resistor). As depicted in Figure 9, a START condition is defined to be when the master pulls the SDA line low and after a short period pulls the SCL line low. A START condition acts as a signal to all ICs that something is about to be transmitted on the BUS. A STOP condition, also shown in Figure 9, is when the master releases the bus and SCL changes from low to high followed by SDA low to high transition. The master does not issue an ACKNOWLEDGE and releases the SCL and SDA pins.

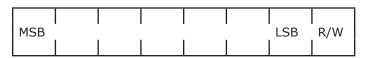

### **Transferring Data**

Every byte on the bus must be 8 bits long. A byte is always sent with the most significant bit first (see Figure 8).

Figure 8: Bit Order.

### **Acknowledge Bit**

The acknowledge bit is the ninth bit of data. It is used to send back a confirmation to the master that the data has been received properly. For acknowledge to take place, the MASTER must first release the SDA line, then the SLAVE will pull the data line low as shown in Figure 9.

The address is embedded in the first seven bits of the byte. The eighth bit is reserved for the direction of the information flow for the next byte of information. For the AAT3608, this bit must be set to "0" when writing and "1" when reading. The full 8-bit address including the R/W bit is 0x9C (hex) or 10011100 in binary for writing and 0x9D(hex) or 10011101 in binary for reading.

#### I<sup>2</sup>C Write Code

After sending the chip address, the master should send an 8-bit data stream (" $2^{ND}$  Word"). The " $2^{ND}$  Word" can consist of any one of the four sets of data listed in Table 3.

The "3<sup>RD</sup> Word" should be entered into the I<sup>2</sup>C only if  $(Bit_7, Bit_6, Bit_5) = (0,0,0)$  in the "2<sup>ND</sup> Word". In this case, the bits (G2,G1,G0) are used to set the bit assignments as shown in Tables 4 and 5.

Figure 9: I<sup>2</sup>C Protocol.

| Bit7 | Bit6 | Bit5 | Bit4               | Bit3               | Bit2              | Bit1                                     | Bit0                                     |

|------|------|------|--------------------|--------------------|-------------------|------------------------------------------|------------------------------------------|

| 0    | 0    | 0    | 0                  | 0                  | G2                | G1                                       | G0                                       |

| 0    | 0    | 1    | EN <sub>LDO5</sub> | EN <sub>LDO4</sub> | DS_RDY            | PWR_DS                                   | Reserved                                 |

| 0    | 1    | 0    | LDO5 <sub>1</sub>  | LDO5₀              | LDO4 <sub>1</sub> | LDO4 <sub>0</sub>                        | EN <sub>CHG</sub>                        |

| 0    | 1    | 1    | BUCK24 and LDO34   | BUCK23 and LDO33   | BUCK2, and LDO3,  | BUCK2 <sub>1</sub> and LDO3 <sub>1</sub> | BUCK2 <sub>0</sub> and LDO3 <sub>0</sub> |

Table 3: I<sup>2</sup>C "2nd Word" Bit Assignments.

| Bit7 | Bit6 | Bit5               | Bit4               | Bit3               | Bit2                | Bit1                | Bit0          |

|------|------|--------------------|--------------------|--------------------|---------------------|---------------------|---------------|

| 0    | 1    | EN <sub>LDO3</sub> | EN <sub>LDO2</sub> | EN <sub>LDO1</sub> | EN <sub>BUCK1</sub> | EN <sub>BUCK2</sub> | PWR_EN Mask   |

| 1    | 0    | PWR_IN IN Mask     | PWR_IN OUT Mask    | Reserved           | LBO Mask            | TIME OUT Mask       | CHG DONE Mask |

Table 4:  $I^2C$  "3rd Word" Bit Assignments for (G2,G1,G0) = (0,0,0)

| Bit7 | Bit6 | Bit5 | Bit4       | Bit3 | Bit2 | Bit1 | Bit0 |  |

|------|------|------|------------|------|------|------|------|--|

| 0    | 1    |      | Test Modes |      |      |      |      |  |

Table 5:  $I^2C$  "3rd Word" Bit Assignments for (G2,G1,G0) = (0,1,0).