# Product Datasheet

# MB86697A

April 2000 Version 2.3

# FireStream<sup>TM</sup>155 ATM 155Mbps SAR Device

/FML/NPD/FS155/DS/1973

The **FireStream<sup>™</sup>155** is a high performance ATM protocol controller which autonomously terminates ATM Adaptation Layer standard Type 5 (AAL5). ATM cells are received through a UTOPIA v2.01 compliant interface. Simultaneous segmentation and reassembly can be achieved at an average rate in excess of 155Mbps.

All ATM Forum traffic classes (ABR, VBR, CBR, UBR) are supported with traffic management to ATM Forum TM4.0 specification on up to 65536 virtual circuits (VCs).

The device is ideally suited to many ATM applications including ATM switches, access units, adaptor cards and multi-protocol hubs, bridges and routers.

#### **Features**

- Broadband ISDN Adaptation Layer standard Type 5 (AAL5)

- Simultaneous segmentation and reassembly on up to 64K VCs

- ABR, VBR, UBR and CBR traffic classes with traffic management compliant to TM4.0

- Autonomous Resource Management (RM) cell handling

- 33MHz 32-bit PCI interface compliant to Revision 2.1

- Write-only interface for PDU handling with copy of SAR registers maintained in host memory

- Configuration through PCI slave port, PCI configuration optionally through serial EEPROM interface

- Transparent ATM cell and cell payload modes (AAL0) with support for Operations and Maintenance (OAM) cells

- 8/16-bit, up to 52MHz UTOPIA v2.01 level 1 and level 2 compliant cell stream interface with master/slave modes and optional HEC checking on receive

- Flexible routing tag append / remove mode for direct ATM Switch connection

- 32-bit Local memory port connects directly to SRAM

- JTAG compliant to IEEE1149.1

- Fabricated in CMOS technology with CMOS/TTL compatible 5V tolerant I/O and a 3.3V power supply

# LEFT BLANK

#### **Table of Contents**

| 1 | Introduction |                                          |     |  |

|---|--------------|------------------------------------------|-----|--|

| 2 | Exte         | ernal Interfaces                         | 15  |  |

|   | 2.1          | Logical Outline                          | 15  |  |

|   | 2.2          | Pin Descriptions                         | 16  |  |

| 3 | Fund         | Functional Description                   |     |  |

|   | 3.1          | Traffic Management Controller            | 22  |  |

|   | 3.2          | PCI Master DMA Controller                | 22  |  |

|   | 3.3          | PCI Slave Interface                      | 23  |  |

|   | 3.4          | Segmentation and Reassembly              | 23  |  |

|   | 3.5          | Local Memory Controller                  | 23  |  |

|   | 3.6          | UTOPIA (Multi-PHY) Interface             | 24  |  |

| 4 | Devi         | ice Operation                            | 27  |  |

|   | 4.1          | Device Configuration and Start-up        | 27  |  |

|   | 4.2          | Test Modes                               | 29  |  |

|   | 4.3          | Clocks                                   | 29  |  |

| 5 | Traff        | ic Management                            | 31  |  |

|   | 5.1          | Calendar Algorithm                       | 31  |  |

|   | 5.2          | VBR & CBR Implementation                 | 32  |  |

|   | 5.3          | ABR Implementation                       | 33  |  |

|   | 5.4          | UBR Implementation                       | 35  |  |

|   | 5.5          | Overall Traffic Shaping                  | 35  |  |

|   | 5.6          | Configuration and Performance Monitoring | 35  |  |

|   | 5.7          | GFC Support                              | 35  |  |

|   | 5.8          | Rate Parameters                          | 36  |  |

| 6 | Prog         | gramming Interface                       | 37  |  |

|   | 6.1          | Concepts                                 | 37  |  |

|   | 6.2          | FireStream155 Modes of Operation         | 40  |  |

|   | 6.3          | Control Functions                        | 42  |  |

|   | 6.4          | Data Buffer Management                   | 47  |  |

|   | 6.5          | Descriptor Format                        | 49  |  |

|   | 6.6          | Command Management                       | 53  |  |

|   | 6.7          | Host -> FireStream155 Queue Formats      | 56  |  |

|   | 6.8          | FireStream155 -> Host Queues             | 59  |  |

|   | 6.9          | Command Descriptions                     | 65  |  |

| 7 | Loca         | al Memory Organisation                   | 109 |  |

|   | 7.1          | Memory Organisation                      | 109 |  |

|   | 7.2          | Transmit Buffer Manager LRAM Format      | 111 |  |

|   |              |                                          |     |  |

|   | 7.3             | Segmentation / Routing Tag LRAM Format | 115 |

|---|-----------------|----------------------------------------|-----|

|   | 7.4             | Traffic Manager LRAM Format            | 117 |

|   | 7.5             | Reassembly LRAM Format                 | 124 |

|   | 7.6             | Receive Buffer Manager LRAM Format     | 126 |

| Α | Regi            | ster Map                               | 131 |

|   | A.1             | PCI Configuration Registers            | 131 |

|   | A.2             | Internal Registers                     | 132 |

| В | Regi            | ster Descriptions                      | 137 |

| С | Ratii           | ngs                                    | 197 |

|   | C.1             | DC Characteristics                     | 197 |

|   | C.2             | Recommended Operating Conditions       | 198 |

|   | C.3             | Absolute Maximum Ratings               | 198 |

| D | AC 7            | Fiming Characteristics                 | 199 |

|   | D.1             | PCI Interface                          | 199 |

|   | D.2             | UTOPIA Interface                       | 200 |

|   | D.3             | Local Interface                        | 201 |

|   | D.4             | SRAM Interface                         | 202 |

|   | D.5             | EEPROM Interface                       | 204 |

|   | D.6             | JTAG Interface                         | 205 |

| Е | JTAC            | §                                      | 207 |

| F | Pin Assignments |                                        | 209 |

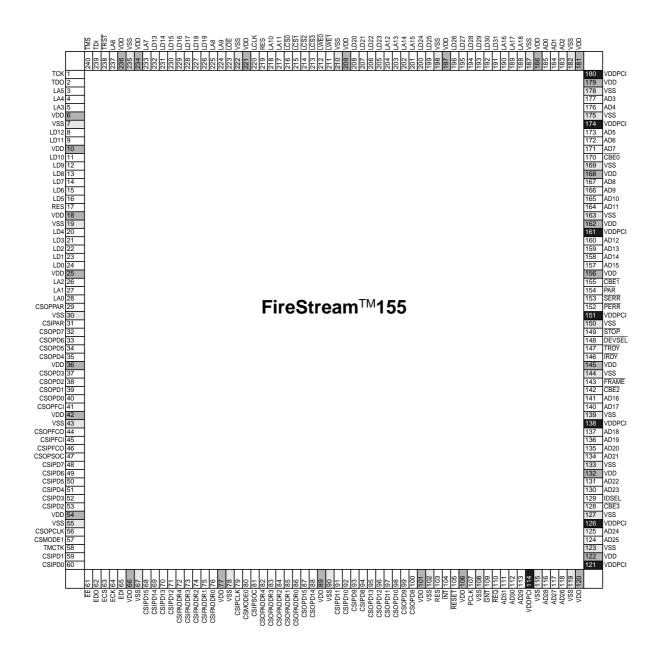

|   | F.1             | Pin Diagram                            | 209 |

|   | F.2             | Pin Assignments                        | 210 |

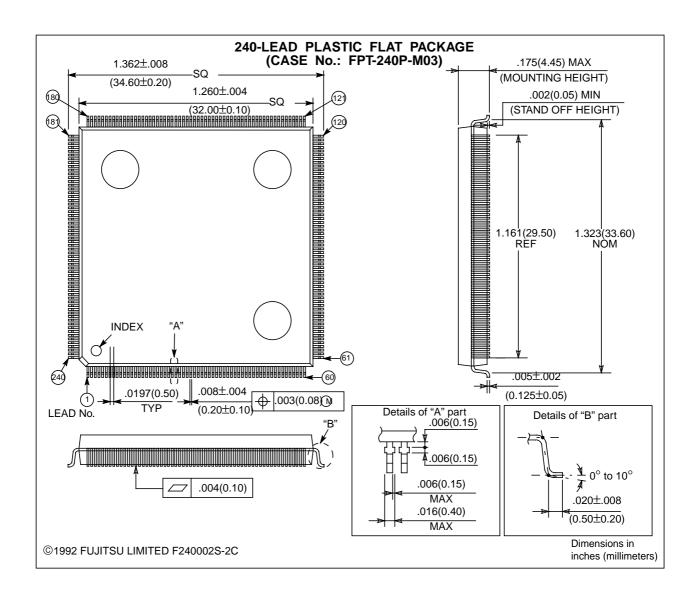

| G | Pack            | age Dimensions                         | 217 |

| н | Glos            | sary of Terms                          | 219 |

## **List of Figures**

| Figure 1  | ATM Switch Port designed around the FireStream155     |     |  |

|-----------|-------------------------------------------------------|-----|--|

| Figure 2  | ATM Terminal Equipment based around the FireStream155 | 13  |  |

| Figure 3  | FireStream155 External Interfaces                     | 15  |  |

| Figure 4  | FireStream155 Block Diagram                           | 21  |  |

| Figure 5  | FireStream155 Loopback Mode                           | 29  |  |

| Figure 6  | Calendar Algorithm                                    | 32  |  |

| Figure 7  | Calendar Priority Mechanism                           | 33  |  |

| Figure 8  | Firestream155 Basic Data Structures overview          | 38  |  |

| Figure 9  | Transmit Path Overview                                | 39  |  |

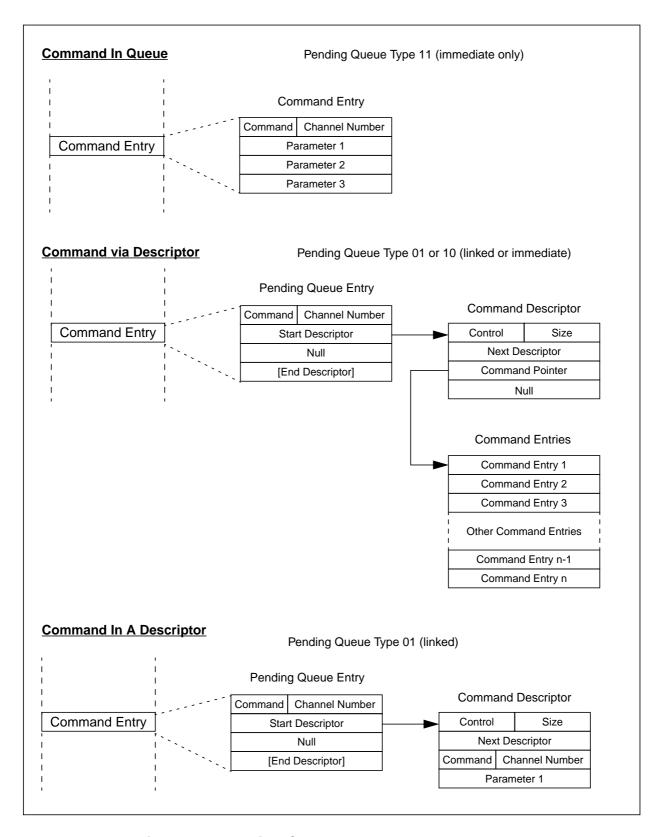

| Figure 10 | Passing Commands to the FireStream155                 | 54  |  |

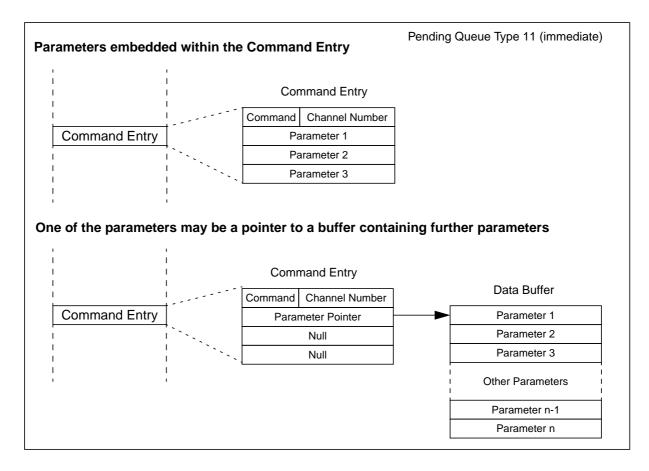

| Figure 11 | Passing Parameters to the FireStream155               | 55  |  |

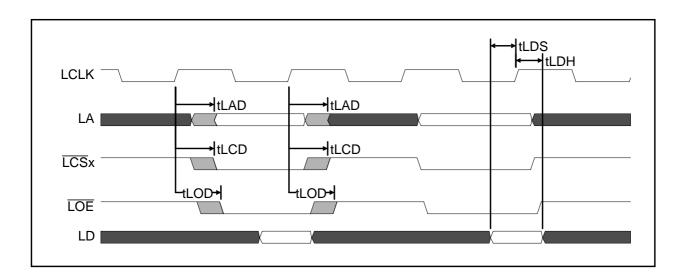

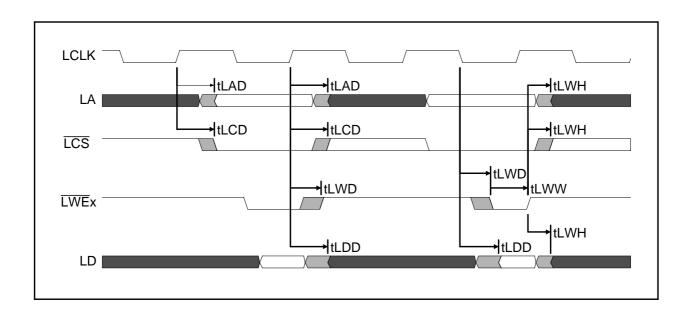

| Figure 12 | Local Interface Timings                               | 201 |  |

| Figure 13 | SRAM Read Timing                                      | 202 |  |

| Figure 14 | SRAM Write Timing                                     | 202 |  |

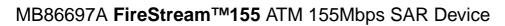

| Figure 15 | EEPROM Interface Timings                              | 204 |  |

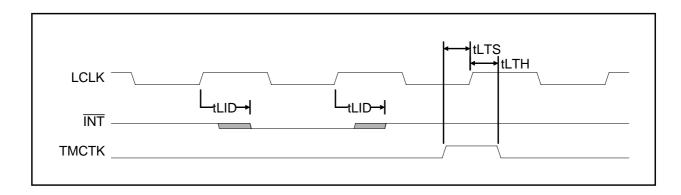

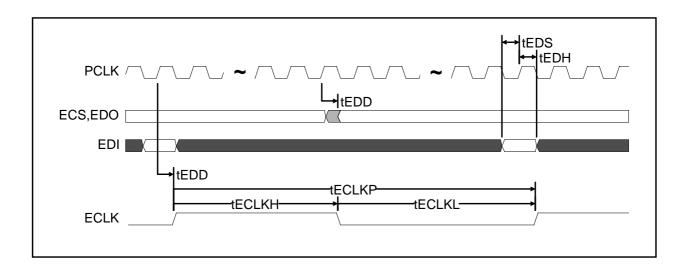

| Figure 16 | JTAG Interface Timings                                | 205 |  |

| Figure 17 | Pin Assignments                                       | 209 |  |

| Figure 18 | Package Dimensions                                    | 217 |  |

# LEFT BLANK

#### **List of Tables**

| Table 1  | FireStream155 UTOPIA modes                                 | 19 |

|----------|------------------------------------------------------------|----|

| Table 2  | Shadowed Registers (Shadow Select = 0)                     | 44 |

| Table 3  | Shadowed Registers (Shadow Select = 1)                     | 44 |

| Table 4  | Descriptor Format                                          | 49 |

| Table 5  | CM Coding                                                  | 49 |

| Table 6  | Command-In-A-Descriptor Format                             | 51 |

| Table 7  | Receive Descriptor Write Accesses                          | 52 |

| Table 8  | Common Transmit Pending Queue Format                       | 56 |

| Table 9  | Transmit Pending Queue Entry Type and Type Specific Coding | 57 |

| Table 10 | Common Status Queue Format                                 | 59 |

| Table 11 | Status Queue Entry Type and Type Specific Coding           | 60 |

| Table 12 | Transmit Buffer Release Queue Entry Status                 | 62 |

| Table 13 | Receive Buffer Ready Queue Status Codes                    | 63 |

| Table 14 | Firestream155 Command List                                 | 65 |

| Table 15 | Null Command Pending Format                                | 67 |

| Table 16 | Null Command Status Format                                 | 67 |

| Table 17 | Register Read Command Pending Format                       | 68 |

| Table 18 | Register Read Command Status Format                        | 68 |

| Table 19 | Register Read Multiple Command Pending Format              | 69 |

| Table 20 | Register Read Multiple Command Status Format               | 69 |

| Table 21 | Register Write Command Pending Format                      | 70 |

| Table 22 | Register Write Command Status Format                       | 70 |

| Table 23 | Register Write Multiple Command Pending Format             | 71 |

| Table 24 | Register Write Multiple Command Pending Format             | 71 |

| Table 25 | Transmit Configuration Command Pending Format              | 72 |

| Table 26 | Transmit Configuration Data Buffer Format                  | 72 |

| Table 27 | Transmit Configuration Parameters                          | 72 |

| Table 28 | Transmit Configuration Command Status Format               | 75 |

| Table 29 | Receive Configuration Command Pending Format               | 76 |

| Table 30 | Receive Configuration Parameters                           | 76 |

| Table 31 | BPS Coding                                                 | 77 |

| Table 32 | Receive Configuration Command Status Format                | 78 |

| Table 33 | Read Peripheral Command Pending Format                     | 79 |

| Table 34 | Read Peripheral Command Status Format                      | 79 |

| Table 35 | Read Peripheral Multiple Command Pending Format            | 80 |

| Table 36 | Read Peripheral Multiple Command Status Format             | 80 |

| Table 37 | Write Peripheral Command Pending Format                    | 81 |

|          |                                                            |    |

| Table 38 | Write Peripheral Command Status Format            | 81 |

|----------|---------------------------------------------------|----|

| Table 39 | Write Peripheral Command Pending Format           | 82 |

| Table 40 | Write Peripheral Command Status Format            | 82 |

| Table 41 | Receive Enable Command Pending Format             | 83 |

| Table 42 | Receive Enable Command Status Format              | 83 |

| Table 43 | Receive Purge and Inhibit Command Pending Format  | 84 |

| Table 44 | Receive Purge and Inhibit Command Status Format   | 84 |

| Table 45 | Receive Purge Command Pending Format              | 85 |

| Table 46 | Receive Purge Command Status Format               | 85 |

| Table 47 | Transmit Enable Command Pending Format            | 86 |

| Table 48 | Transmit Enable Command Status Format             | 86 |

| Table 49 | Transmit Purge and Inhibit Command Pending Format | 87 |

| Table 50 | Transmit Purge and Inhibit Command Status Format  | 87 |

| Table 51 | Transmit Purge Command Pending Format             | 88 |

| Table 52 | Transmit Purge Command Status Format              | 88 |

| Table 53 | Reset Congestion Command Pending Format           | 89 |

| Table 54 | Reset Congestion Command Status Format            | 89 |

| Table 55 | Set Congestion Command Pending Format             | 90 |

| Table 56 | Set Congestion Command Status Format              | 90 |

| Table 57 | Reset CLP Command Pending Format                  | 91 |

| Table 58 | Reset CLP Command Status Format                   | 91 |

| Table 59 | Set CLP Command Pending Format                    | 92 |

| Table 60 | Set CLP Command Status Format                     | 92 |

| Table 61 | Override Length Command Pending Format            | 93 |

| Table 62 | Override Length Command Status Format             | 93 |

| Table 63 | Add Buffers to Free Pool Command Pending Format   | 94 |

| Table 64 | Add Buffers to Free Pool Parameters               | 94 |

| Table 65 | Add Buffers to Free Pool Command Status Format    | 94 |

| Table 66 | Dump Transmit Channel Command Pending Format      | 95 |

| Table 67 | Dump Transmit Channel Command Status Format       | 95 |

| Table 68 | Dump Receive Channel Command Pending Format       | 96 |

| Table 69 | Dump Receive Channel Command Status Format        | 96 |

| Table 70 | Read LRAM Command Pending Format                  | 97 |

| Table 71 | Read LRAM Command Status Format                   | 97 |

| Table 72 | Read LRAM Multiple Command Pending Format         | 98 |

| Table 73 | Read LRAM Multiple Command Status Format          | 98 |

| Table 74 | Write LRAM Command Pending Format                 | 99 |

| Table 75 | Write LRAM Command Status Format                  | 99 |

| Table 78  | LRAM Bit Set Command Pending Format                      | 101 |

|-----------|----------------------------------------------------------|-----|

| Table 79  | LRAM Bit Set Command Status Format                       | 101 |

| Table 80  | LRAM Bit Clear Command Pending Format                    | 102 |

| Table 81  | LRAM Bit Clear Command Status Format                     | 102 |

| Table 82  | Configure Segmentation Command Pending Format            | 103 |

| Table 83  | Configure Segmentation Command Status Format             | 103 |

| Table 84  | Configure Routing Tag Command Pending Format             | 104 |

| Table 85  | Configure Routing Tag Command Status Format              | 104 |

| Table 86  | Configure TM Command Pending Format                      | 105 |

| Table 87  | Configure TM Command Status Format                       | 105 |

| Table 88  | Configure Transmit Buffer Manager Command Pending Format | 106 |

| Table 89  | Configure Transmit Buffer Manager Command Status Format  | 106 |

| Table 90  | Configure Receive Buffer Manager Command Pending Format  | 107 |

| Table 91  | Configure Receive Buffer Manager Command Status Format   | 107 |

| Table 92  | Configure Reassembly Command Pending Format              | 108 |

| Table 93  | Configure Reassembly Command Status Format               | 108 |

| Table 94  | LRAM Organisation                                        | 109 |

| Table 95  | Mapping of Areas to Stored Parameters                    | 110 |

| Table 96  | Transmit Buffer Manager LRAM Format                      | 111 |

| Table 97  | STATUS Coding                                            | 112 |

| Table 98  | AAL Coding                                               | 112 |

| Table 99  | Segmentation LRAM Format                                 | 115 |

| Table 100 | Routing Tag LRAM Format                                  | 115 |

| Table 101 | Extended Routing Tag LRAM Format                         | 116 |

| Table 102 | Traffic Manager LRAM Format: ABR parameters.             | 117 |

| Table 103 | Traffic Manager LRAM Format: Additional ABR parameters   | 117 |

| Table 104 | TTYPE encoding                                           | 117 |

| Table 105 | TRM Encoding                                             | 118 |

| Table 106 | NRM Encoding                                             | 119 |

| Table 107 | MRM Encoding                                             | 119 |

| Table 108 | RDF Encoding                                             | 120 |

| Table 109 | CDF encoding                                             | 120 |

| Table 110 | BMODE Encoding                                           | 121 |

| Table 111 | Traffic Manager LRAM Format: CBR/VBR/UBR traffic         | 122 |

| Table 112 | cr_ratio coding example                                  | 122 |

| Table 113 | Reassembly LRAM Format                                   | 124 |

| Table 114 | Receive Buffer Manager LRAM Format                       | 126 |

| Table 115 | Receive Modes Of Operation                               | 127 |

|           |                                                          |     |

| Table 116 | PCI Configuration Registers | 131 |

|-----------|-----------------------------|-----|

| Table 117 | FireStream155 Register Map  | 132 |

| Table 118 | MOD Coding                  | 164 |

| Table 119 | PCI Interface Timings       | 199 |

| Table 120 | UTOPIA Interface Timings    | 200 |

| Table 121 | Local Interface Timings     | 201 |

| Table 122 | SRAM Interface Timings      | 203 |

| Table 123 | EEPROM Interface Timings    | 204 |

| Table 124 | JTAG Interface Timings      | 205 |

| Table 125 | Pin Assignments             | 210 |

### 1 Introduction

#### General

The **FireStream155** simultaneously supports autonomous segmentation and reassembly of user data packets on up to 64K virtual circuits (VCs). User data packets are transferred to and from shared data structure memory using a high speed 32-bit PCI bus and transferred to and from the network using a 8/16-bit UTOPIA interface.

### **Adaptation Layer Support**

The **FireStream155** autonomously terminates the protocols involved in segmenting and reassembling data streams conforming to ATM Adaptation Layer (AAL) type5 to I.363. Streaming and Message Modes as defined for AAL5 are supported. In Message Mode, the Convergence Sublayer payload (Service Data Unit) is considered to be the user data transmitted from or received into a single entity - a single entity being regarded as one user data buffer or linked chain of user data buffers. In Streaming Mode, the Convergence Sublayer payload is considered to be the user data transmitted from or received into multiple entities separated in time. This allows a partial segmentation or reassembly. The device recognises OAM and RM cells and separates them from the data stream.

The **FireStream155** device supports two transparent modes (AAL0) with optional CRC-10 generation and checking. In transparent payload mode the 48 byte ATM cell payload is received or transmitted transparently into or from SAR Memory. In transparent cell mode the complete ATM cell, excluding the HEC, is received or transmitted transparently into or from SAR Memory.

# **Traffic Shaping**

The **FireStream155** supports autonomous traffic shaping functions for ABR, VBR, UBR and CBR traffic. Traffic parameters are stored on a per-circuit basis in local memory. A calendar algorithm is used for traffic scheduling and has four priority levels which are independent of traffic type. ABR support includes autonomous handling of RM cells. Transmitted FRM cells are dropped into the data stream at the correct rate. Received BRM cells modify the associated VC's traffic parameters. Received FRM cells are stored locally and automatically rescheduled for transmission.

# **Local Memory**

Control structures are initialised by the host and then copied by the **FireStream155** into local memory. These include circuit information such as VP/VC values and descriptor information such as data pointers and buffer lengths. The **FireStream155** then works on the local copy of these structures and hence does not consume any further system bandwidth. The local memory also contains static and dynamic traffic parameters and pointers for the traffic scheduling algorithm.

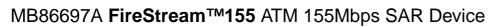

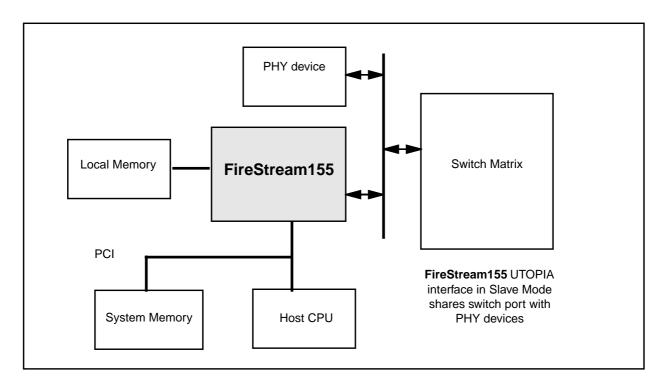

#### Cell Stream Interface

The **FireStream155** interfaces via a standard UTOPIA level 1 or level 2 interface. This 16-bit interface which operates at up to 52MHz can be configured as an ATM or a PHY (master or slave) device depending on the application. In routing tag modes the **FireStream155** adds a programmable length routing tag to the start of each ATM cell to allow connection to a switch matrix. The HEC is inserted on transmit and checked on receive. A 52-byte cell option is provided where the HEC is omitted.

#### **PCI Master Interface**

The **FireStream155** has a high performance 32-bit PCI master interface, conforming to v2.1 of the PCI specification. The programming interface has a "write-only" mode which minimizes PCI bus occupancy by removing the need for the Host to make slave read accesses.

#### **PCI Slave Interface**

A simple PCI slave control/status port is used to configure the device. Its function includes the initialization of the queue structures and the monitoring of cell and packet loss. An interrupt mechanism is implemented to indicate queue updates and exception conditions.

#### **Circuit Initialization**

Circuits are initialized for both transmit and receive by placing an entry on a high or low priority Transmit Pending Queue or onto an on-chip queue. This entry points to configuration information. A Status Queue is used to inform the user that the operation has been completed.

## **Transmit Operation**

Transmit operation is initiated using a simple queue structure. A buffer containing part or all of a packet's data is scheduled by placing a Transmit Descriptor pointer on the high or low priority Transmit Pending Queue. The **FireStream155** links queued descriptors for the same VC into a list. Data is then assembled under the control of the traffic scheduler into packets. The data pointer is contained in the Transmit Descriptor. When a buffer is exhausted it is returned to the host by putting the Transmit Descriptor pointer on a Release Queue.

## **Receive Operation**

On receiving ATM cells the **FireStream155** takes a buffer from one of eight simple Buffer Free Pools. Each pool forms a linked list and buffers are allocated to the device by linking Receive Descriptors onto the list. Each pool may use a different buffer size. Receive Circuits can be allocated to one of these pools. Alternatively the device may be configured so that Receive Circuits use an initial buffer from one pool followed by subsequent buffers from another pool to reassemble a packet. This maximizes memory efficiency. Receive Circuits can have a low-priority discard mode where free buffers will not be allocated while the number of free entries is below a programmable threshold. This improves robustness of the system under heavy receive traffic loading by preventing the free pools under running. When buffers are completed they are returned to the host by putting the Receive Descriptor identifier on one of four Buffer Ready Queues.

#### **JTAG**

The **FireStream155** provides boundary scan test circuitry compliant with IEEE 1149.1 (JTAG). The **FireStream155** JTAG circuitry permits easier board level testing to be carried out by allowing the signal pins on the device to form a serial scan chain around the device. JTAG test modes are controlled by accessing an internal test access port controller via a standard JTAG test port.

Figure 1 ATM Switch Port designed around the FireStream155

Figure 2 ATM Terminal Equipment based around the FireStream155

# LEFT BLANK

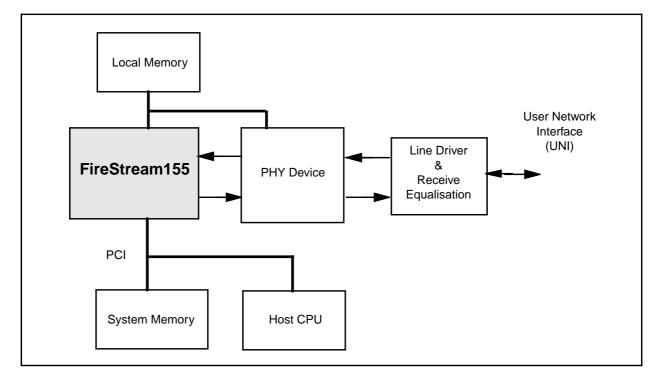

## 2 External Interfaces

# 2.1 Logical Outline

Figure 3 FireStream155 External Interfaces

# 2.2 Pin Descriptions

#### 2.2.1 PCI Interface

This interface provides the FireStream155 DMA controller with access to external system memory.

#### AD[31:0]

Bi-directional multiplexed address / data bus.

#### C/BE[3:0]

Command / Byte Enables.

#### PAR

Even parity over AD[31:0] and C/BE[3:0] buses.

#### **FRAME**

Transaction frame signal.

#### **IRDY**

Initiator ready to complete transfer.

#### TRDY

Target ready to complete transfer.

#### **STOP**

Transaction termination.

#### **DEVSEL**

Slave device acknowledge.

#### IDSEL

Initialization device select.

#### **REQ**

Bus request.

#### **GNT**

Bus grant.

#### INT

Interrupt output.

#### **PERR**

Parity error.

#### **SERR**

System error.

#### **PCLK**

PCI clock.

#### 2.2.2 UTOPIA Interface

#### CSM[1:0]

UTOPIA mode pins.

#### CSOPD[15:0]

8/16-bit parallel output data.

#### **CSOPPAR**

Output parity.

#### **CSOPSOC**

Output start of cell signal.

#### CSOPADR[4:0]

Output address.

#### **CSOPCLK**

This signal is used to clock data out of the FireStream155.

#### CSOPFC I/O

See table 1 for the meaning of these flow control signals in the different UTOPIA configurations.

#### CSIPFC I/O

See table 1 for the meaning of these flow control signals in the different UTOPIA configurations.

#### CSIPD[15:0]

8/16-bit parallel input data.

#### **CSIPPAR**

Input parity.

#### **CSIPSOC**

Input start of cell signal.

#### CSIPADR[4:0]

Input address.

#### **CSIPCLK**

This signal is used to clock data into the **FireStream155**.

# 2.2.3 Local Memory Interface

#### LD[31:0]

Local Memory Data.

#### LA[18:0]

Local Memory address.

#### l OF

Local Memory output enable.

#### **LWE[1:0]**

Local Memory upper and lower word write enables.

#### LCS[3:0]

Local Memory / Peripheral chip selects.

#### **LCLK**

Local Memory clock.

## 2.2.4 Miscellaneous Signals

#### **RESET**

FireStream155 master reset (including PCI reset).

#### **TMCTK**

Traffic Manager calendar interval tick input.

#### **TEST**

Test input (tie to Vss for normal operation).

#### 2.2.5 JTAG Test Port

#### **TCK**

JTAG test clock input.

#### **TMS**

JTAG test mode input.

#### **TDI**

JTAG test data input.

#### **TDO**

JTAG test data output.

#### **TRST**

JTAG reset.

#### 2.2.6 Serial EEPROM Port

#### **ECK**

EEPROM clock output.

#### **ECS**

EEPROM chip select output.

#### **EDI**

Serial data in from EEPROM.

#### **EDO**

Serial data out to EEPROM.

#### EE

EEPROM enable.

| Pin Name     | Direction     |                          | UTOPIA Interface Modes       |                              |

|--------------|---------------|--------------------------|------------------------------|------------------------------|

|              |               | Level 1<br>CSM[1:0] = 01 | Level 2 ATM<br>CSM[1:0] = 11 | Level 2 PHY<br>CSM[1:0] = 10 |

| CSOPD[7:0]   | Output        | TXD[7:0]                 | TXD[7:0]                     | RXD[7:0]                     |

| CSOPD[15:8]  | Output        |                          | TXD[15:8]                    | RXD[15:8]                    |

| CSOPSOC      | Output        | TXSOC                    | TXSOC                        | RXSOC                        |

| CSOPPAR      | Output        | TXPRTY                   | TXPRTY                       | RXPRTY                       |

| CSOPADR[4:0] | Bidirectional |                          | TXADDR[4:0] (out)            | RXADDR[4:0] (in)             |

| CSOPFCO      | Output        | TXEN                     | TXEN                         | RXCLAV                       |

| CSOPFCI      | Input         | TXFULL                   | TXCLAV                       | RXEN                         |

| CSOPCLK      | Input         | TXCLK                    | TXCLK                        | RXCLK                        |

| CSIPD[7:0]   | Input         | RXD[7:0]                 | RXD[7:0]                     | TXD[7:0]                     |

| CSIPD[15:8]  | Input         |                          | RXD[15:8]                    | TXD[15:8]                    |

| CSIPSOC      | Input         | RXSOC                    | RXSOC                        | TXSOC                        |

| CSIPPAR      | Input         | RXPRTY                   | RXPRTY                       | TXPRTY                       |

| CSIPADR[4:0] | Bidirectional |                          | RXADDR[4:0] (out)            | TXADDR[4:0] (in)             |

| CSIPFCO      | Output        | RXEN                     | RXEN                         | TXCLAV                       |

| CSIPFCI      | Input         | RXEMPTY                  | RXCLAV                       | TXEN                         |

| CSIPCLK      | Input         | RXCLK                    | RXCLK                        | TXCLK                        |

Table 1 FireStream155 UTOPIA modes

# LEFT BLANK

# **3 Functional Description**

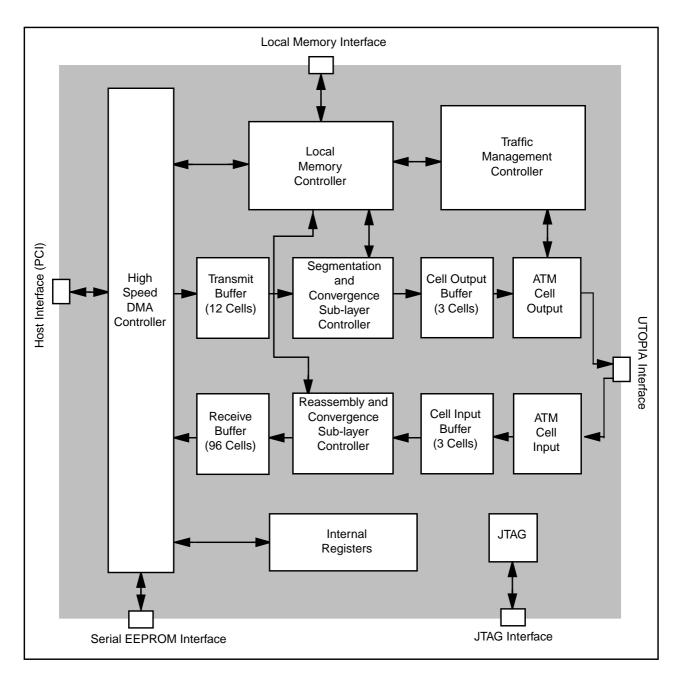

Figure 4 FireStream155 Block Diagram

# 3.1 Traffic Management Controller

The Traffic Management Controller communicates with the Reassembly Process, the Segmentation Process and the Local RAM (LRAM) interface. It is responsible for ensuring that the **FireStream155** conforms to the Traffic Management Specification v4.0 as devised by the ATM Forum, by managing the times at which cells are enabled to be sent. This process includes monitoring the traffic type (ABR, VBR, UBR or CBR) and the priority of the cells.

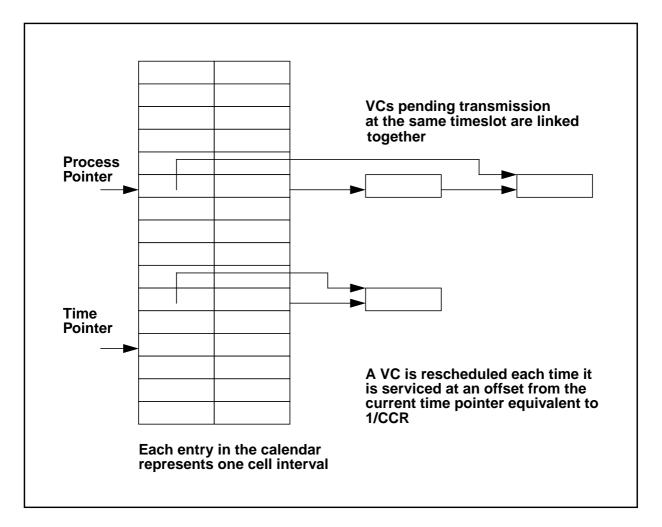

A cell scheduling process maintains a Calendar of locations representing a list of Virtual Circuits (VC) to be serviced in the order that they are to be processed. A Process Pointer keeps track of which location is being processed at any given time, and a Time Pointer keeps track of the current time. The Time Pointer is incremented by a pre-scaled version of either the Local clock or the TMCTK input. Both pointers step down the calendar and once the end is reached they return to the top. New cells which are to be scheduled are entered into the calendar with reference to the Time Pointer. Once a VC is serviced, the time it should be serviced next is calculated and a new entry is made in the calendar. Up to four calendars can be used each with a different priority. This feature can be used to allow CBR traffic to be sent in preference to other traffic types for example.

The overall traffic output of the **FireStream155** can be controlled by an additional leaky bucket traffic shaper.

RM cell handling is triggered by the Reassembly Interface once a Forward Resource Management (FRM) cell is received from the destination entity. The key elements of the FRM cell required to produce a Backward RM cell are stored in LRAM for the appropriate VC. A signal in the LRAM is set to indicate to the Scheduling Process that a BRM cell should be sent on this VC. After a BRM cell is received and before an FRM cell can be sent, the Traffic Manager triggers the Rate Calculation Process to determine the new rate for the VC. The new rate is used by the Traffic Manager to determine when the next cell should be scheduled. To control local congestion, the Host can program the **FireStream155** to behave as a congested destination and request the remote source to reduce its rate by adjusting the outgoing BRM cells.

GFC is implemented to ITU Specification I.361 section 4.1. Additionally the Host can program the **FireStream155** to report changes in GFC on a per circuit basis.

#### 3.2 PCI Master DMA Controller

The PCI Master DMA Controller is responsible for enabling access to system memory. Within the DMA Controller accesses are shared between Transmit and Receive Buffer Managers. The **FireStream155** data-structures are defined to be highly efficient and keep the PCI bandwidth consumed to a minimum. A write-only interface for PDU handling may be implemented using registers shadowed in Host memory.

On transmit the Transmit Buffer Manager receives instructions to assemble cells from the Traffic Manager. It then makes a request to the DMA interface to transfer control information and ATM payload data. An example of control information might be to fetch, update or release a Transmit Descriptor. The Transmit Buffer Manager also processes the Transmit Pending Queues, the Status Queue and the Transmit Buffer Release Queue. It passes parameters from newly queued buffers to be stored in Local Memory.

The Receive Buffer Manager services requests for data transfer to memory for cells stored in the Rx DMA Cell Buffer. It also updates the Receive Buffer Ready queues on buffer completion and fetches

free buffers from the Buffer Free Pools for use with new data as required. Packet and Channel ageing functions are implemented in this module.

### 3.3 PCI Slave Interface

The **FireStream155** PCI Slave interface provides access to all the device's internal registers. It is also used to generate PCI interrupts.

### 3.3.1 Interrupts

Various sources of interrupt are generated by the **FireStream155** and can be signalled to PCI by asserting the PCI INT signal. The interrupt sources include:

- Transmit / Receive completion event

- Queue low fill level warning and queue underrun

- Statistics events / counter overflow

- Initialisation complete

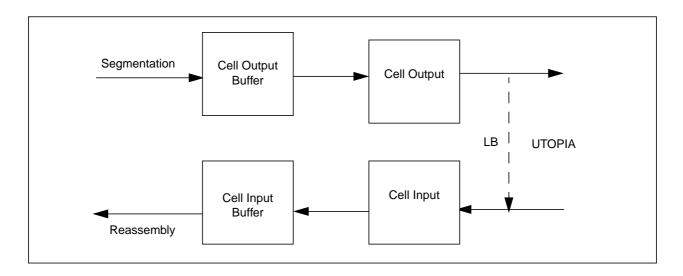

# 3.4 Segmentation and Reassembly

The Segmentation Process receives user data from the Tx DMA Cell Buffer and circuit information from the Local Memory Interface. The circuit information includes the ATM header, any SAR-layer or Convergence-Sublayer information and possibly a routing tag. It carries out the appropriate SAR/CS processing on the data, appends the routing tag and ATM header and stores the cell in the ATM Cell Output Buffer. When the cell write is complete the Segmentation Process signals to the ATM Cell Output process that a cell is available for sending on the UTOPIA interface.

The Reassembly Process receives ATM cells from the UTOPIA Interface section via the Cell Input Buffer. A combination of bits from the UTOPIA address and the VP/VC fields are then used to identify the appropriate Receive Circuit Reference. Any selection of bits can be used from these fields. The data is stripped out by first removing the cell header (SAR layer) and then removing the data trailer (CS sublayer). The CRC32 check and the packet length measurement are computed at this point. The circuit information is stored in the local memory via the Local Memory Interface and the user data is sent to the system memory via the 96 Cell Receive Buffer.

# 3.5 Local Memory Controller

The Local Memory Controller module forms the interface between the local memory and the sections of the device requiring access to the memory. The data stored within the local memory comprises the traffic management parameters including the calendar table, cell headers, buffer parameters and other circuit information, used by both the Segmentation and Reassembly Processes. The interface also provides access via the Pending / Status Queue to enable circuit information to be accessed externally. Different numbers of VCs can be supported dependent on the amount of SRAM provided externally. For example 4x32Kx8 is enough SRAM to support 1K VCs full duplex and 4x128Kx8 is enough SRAM to support 4K VCs full duplex.

Peripherals, such as framers, which do not support PCI but can accept the SRAM interface timing, can be mapped into the LRAM address space and accessed using the Pending / Status Queue mechanism.

## 3.6 UTOPIA (Multi-PHY) Interface

The UTOPIA Multi-PHY interface implements the ATM Forum UTOPIA Level 1 and Level 2 interface specification with an 8/16-bit datapath. Refer to the UTOPIA Level 1/2 Specification for a detailed description of the UTOPIA interface operation and example timing diagrams. The optional TX/RXClav[3:1] signals are not supported by the **FireStream155**. The device can be configured as an ATM layer or PHY layer (master or slave) device and for level 1/2 operation by 2 mode pins.

## 3.6.1 ATM Layer (Master) Operation Transmit Direction

The **FireStream155** assembles cells for transmission in the Cell Output Buffer. These cells are tagged with the port address of the destination PHY device. When the **FireStream155** polls the PHY device (via the UTOPIA interface) the Cell Output Process transmits the complete cell on the UTOPIA interface if the PHY device indicates there is space for it. If no space is indicated, then the device does not transmit a cell but will continue to poll the device until such time that the cell can be accepted. The cumulative traffic queued for a given PHY port should not exceed its capacity to accept data or other PHY ports may suffer data starvation.

### 3.6.2 ATM Layer (Master) Operation Receive Direction

The **FireStream155** polls, selects and services enabled PHY devices on a "round-robin" basis (via the UTOPIA interface). When a selection has been made the **FireStream155** accepts a complete cell from the PHY device and stores it in the Cell Input Buffer. The Cell Input Buffer signals to the SAR/CS Receive Process block whenever there is a complete cell available. Once the SAR/CS Receive Process is ready to receive data, it empties the buffer.

# 3.6.3 PHY Layer (Slave) Operation Transmit Direction

When the **FireStream155** PHY port is polled by the ATM Layer (via the UTOPIA interface) the Cell Input Process signals back to the UTOPIA interface if there is space for a complete cell to be stored in its Cell Input Buffer. If no space is indicated, then it is the responsibility of the ATM layer not to transmit a cell. If a cell is erroneously sent under these conditions, it will be lost (no data will be over written in the Cell Input Buffer, and no indication is made via statistics or interrupts). The Cell Input Buffer signals to the SAR/CS Receive Process whenever there is a complete cell available. Once the SAR/CS Receive Process is ready to receive data, it empties the buffer.

# 3.6.4 PHY Layer (Slave) Operation Receive Direction

The SAR/CS Transmit Process waits until the Cell Output Buffer has room to accept a complete cell. It is therefore able to wait for the ATM layer device to poll, select and service the Cell Output Buffer (via the UTOPIA interface) - so this buffer will not overrun. On the UTOPIA side, if the Cell Output Buffer contains a cell ready for transfer, the Cell Output Process indicates this to the UTOPIA interface when polled.

# 3.6.5 Level 1 Operation

The **FireStream155** defaults to an ATM Layer device in level 1 operation. Octet level flow control is permitted during cell transmission from the PHY device. The **FireStream155** asserts its output flow

control signals on a cell boundary enabling interworking with devices implementing both cell and octet level flow control.

# LEFT BLANK

# 4 Device Operation

## 4.1 Device Configuration and Start-up

### 4.1.1 Device Reset Sequence

On power-up (hard-reset) or after the application of a soft-reset, the **FireStream155** will carry out a reset of all control logic and internal registers and is able to execute both internal and external RAM tests. A serial EEPROM may be used to program appropriate sections of the PCI configuration space.

## 4.1.2 Device Configuration

Firstly the PCI configuration is completed. Then the **FireStream155** can be configured for operation by setting the appropriate bits in various control registers using the PCI slave interface. Static parameters, such as queue start and end pointers should be initialised followed by initial values of queue pointers.

#### 4.1.3 Circuit Initialisation

Before data can be sent or received, circuit parameters for transmit and receive must be configured. These parameters are stored in Local Memory. The Pending Queues or the on-chip queue allow the user to pass parameters to the **FireStream155** using Commands. An initialisation command contains a Circuit Reference number, indicates the category of control access required and optionally points to an area of host memory where the parameters are stored or are required to be stored.

Commands are used for all control initialisation for both transmit and receive as well as setting up and modifying Traffic Management parameters and tearing down receive connections. The Status Queue provides an indication to the host that the commands placed on the control queue have been executed. An interrupt is available to flag the update of this queue.

#### 4.1.4 Transmit Data Flow

A packet is passed to the **FireStream155** for segmentation by using the high or low priority Transmit Pending Queues. An entry on the queue points to a Transmit Descriptor and contains a Circuit Reference identifier which links it to an entry in the Local Memory. The Transmit Descriptor is associated with user data for a particular VC in host memory. The user data may form part of a packet (Chaining or Streaming modes) or an entire packet (Message mode). When a Transmit Descriptor is entered on the Transmit Pending Queue the Traffic Manager is informed that data exists for that circuit.

The Traffic Manager enters a marker for the data into one of its Calendars using the Circuit Reference identifier. When the calendar advances it searches for valid markers and, when it sees such a marker, it updates the calendar slot where the next cell should be sent using the appropriate traffic shaping parameters and requests to the Transmit Buffer Manager for a cell's worth of data for that circuit. The Transmit Buffer Manager fetches the data via the PCI DMA interface and performs any necessary buffer management, such as releasing a used buffer to the Transmit Buffer Release Queue or a chaining or streaming operation. The data is stored in the Transmit DMA buffer and is tagged with the

Circuit Reference. When a whole cell has been assembled in the buffer and there is also room for a cell's worth of data in the ATM Cell Output Buffer, the segmentation process fetches the ATM header, any SAR-layer or Convergence-Sublayer information and possibly a routing tag. It carries out the appropriate SAR/CS processing on the data, appends the routing tag and ATM header and stores the cell in the ATM Cell Output Buffer.

When the cell write is complete the Segmentation Process signals to the ATM Cell Output process that a cell is available. The cell is then output on the UTOPIA interface under the control of the UTOPIA flow control mechanisms with the HEC inserted and the CRC10 calculated as required.

#### 4.1.5 Receive Data Flow

A cell arriving at the ATM Input Process is processed according to the UTOPIA flow control mechanisms. As it arrives it is buffered in the Cell Input Buffer. The cell is accepted if it passes the HEC and CRC10 checks as appropriate. The cell is then handed to the Reassembly Process. This process firstly maps the VP/VC onto a Receive Circuit Reference. This Circuit Reference is used as an address to look up circuit parameters in local memory. These parameters include SAR-layer and Convergence-Sublayer values and circuit status.

If the circuit is not activated, it may optionally be tagged as unknown and forwarded to the Host. If not, or if the packet is in discard mode after a protocol error or "packet too long detected", the cell will be dropped at this point. Otherwise the cell is stored in the Receive DMA Cell buffer with its Circuit Reference. When the Receive Buffer Manager sees a complete cell in the buffer it reads the appropriate buffer status information from Local Memory. If packet ageing is enabled and the packet is too old, reception is aborted and the host notified. If the circuit is active but no buffer is indicated and, for low priority circuits, enough free buffers are available, the Receive Buffer Manager will fetch a new buffer via the PCI DMA Interface from one of the pools of free buffers maintained by the Host.

The choice of which pool to use is determined by the mode of the circuit which is programmed by the Host. If the cell is the first in a packet then it might choose a buffer from a pool of small buffers, otherwise from a pool of large buffers. Alternatively there may be a fixed association between a VC and one of the pools. The cell is then transferred to host memory using the data pointer provided.

#### 4.2 Test Modes

### 4.2.1 Loopback

A loopback path can be enabled within the **FireStream155**, as shown in Figure 5. This is a loopback path between the Utopia output path, and the Utopia input path. CSOPCLK and CSIPLCK do not need to be running during loopback testing and the UTOPIA interface will be idle.

Figure 5 FireStream155 Loopback Mode

## 4.2.2 Local Memory

The **FireStream155** will automatically test the local memory on initialisation. Parameters in this memory are initialised by the Host and maintained by the device. For debugging purposes the user may use commands to obtain a dump of the contents of the local memory.

#### 4.3 Clocks

The **FireStream155** requires up to 4 separate external clocks, PCLK, LCLK, CSOPCLK and CSIPCLK.

PCLK provides a clock for the PCI Interface. This Interface can run at any frequency up to 33MHz. LCLK provides a clock for the Local Memory Interface and can run at up to 33MHz. The CSOPCLK and CSIPCLK pins provide the clocks for the UTOPIA interface. The UTOPIA specification characterises the interface for clock speed of 25, 33 and 50MHz, but the interface may also be run at any frequency, up to 52MHz maximum for Level2 and 33MHz for Level1. The transmit and receive parts of the UTOPIA interface do not have to run at the same clock speed.

# LEFT BLANK

# 5 Traffic Management

# 5.1 Calendar Algorithm

### 5.1.1 Principle of Operation

The calendar controller maintains a list of locations in LRAM representing calendars of channels to be serviced according to the time at which they are to be processed. A Process Pointer keeps track of which location is being processed at any given time, and a Time Pointer keeps track of the current time. Both pointers step down the calendar and once the end is reached they return to the top. New cells which are to be scheduled are entered into the calendar with reference to the Time Pointer, and ahead of the Time Pointer. If two or more channels should be scheduled in one location, then a linked list is formed in order to maintain the correct scheduling order.

Every cell period the Time Pointer always moves to the next location in the list but the progress of the Process Pointer depends on the entry at the current location. Where there are many operations scheduled in one location, the Process Pointer waits until all the channels for that location have been serviced and therefore falls behind the Time Pointer. However, any empty locations will be skipped by the Process Pointer and hence it will catch up with the Time Pointer.

Once a channel is serviced, the time it should be serviced next is calculated and a new entry is made in the calendar. The range of the calendar scheme is between 6 and 365,000 cells/sec or 2.37Kbits/sec to 155 Mbits/sec at a resolution of 1.56%.

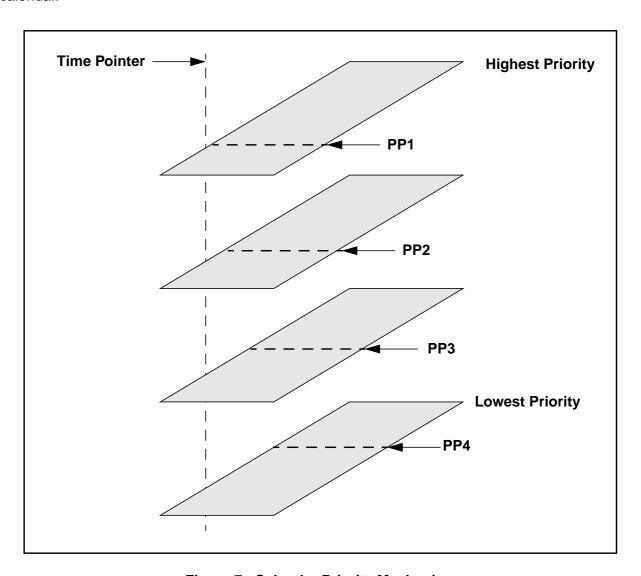

## 5.1.2 Multiple Calendars

The Traffic Management module can maintain up to 4 calendars of descending priority. Therefore, different channels or traffic types can be prioritised by associating them to different calendars.

If the Process Pointer on a higher priority calendar should catch up with the Time Pointer on that calendar, then the Traffic Manager will service channels on the calendar of immediately lower priority. This process is illustrated in Figure 6 and Figure 7.

# 5.1.3 Controlling the calendars

The calendars are initialised by the **FireStream155** on power-up. The calendar entries are all cleared and the process pointer and time pointer are aligned. The calendars are enabled for operation by setting the calendar enable bits in the Traffic Management Configuration register.

The rate of processing for each calendar (cell interval) can be individually controlled by selecting between a programmably divided version of either the local clock (LCLK) or an asynchronous external calendar tick input (TMCTK).

#### 5.1.4 Behaviour Under Extreme Traffic Overload

The process pointer will lag behind the current time pointer on the calendar if too much traffic is scheduled or if DMA bandwidth is insufficient to sustain the programmed bandwidth.

In this case the difference between the process pointer and the current time pointer is limited. This causes the time pointer to slow down. When process pointer catches up, the time pointer can advance at its usual rate.

Figure 6 Calendar Algorithm

# 5.2 VBR & CBR Implementation

# 5.2.1 Leaky Bucket Algorithm

The VBR and CBR traffic types are dealt with using a leaky bucket algorithm. When a circuit is encountered in the calendar, the number of new tokens is computed, When tokens are available the next cell is scheduled at 1/PCR interval. If no tokens are available then the next cell is scheduled at 1/SCR interval.

CBR circuits are programmed in a similar way to VBR, but with PCR only defined. However, CBR circuits modify the calendar algorithm slightly. Instead of being rescheduled relative to the current time pointer, they are scheduled relative to the time when they should have been sent (subject to this

not being less than the current time). This ensures that the rate is maintained. Assigning these circuits to the highest priority calendar will ensure that the CDV is kept to a minimum.

When no further data is available on a VBR channel, the time of sending the last data cell is recorded and no new entry made in the calendar. If new data is queued at a later time, the current time and timestamp are compared to compute any new tokens and the circuit is scheduled back into the calendar.

Figure 7 Calendar Priority Mechanism

# 5.3 ABR Implementation

#### 5.3.1 Source Behaviour

The source behaviour conforms to the specification in TM 4.0 section 5.10.4. Cells are scheduled in the calendar using the current interval 1/CCR.

#### 5.3.2 Transmission of FRM cells

The first cell to be transmitted on an ABR circuit is an FRM cell. FRM cells are composed autonomously by the **FireStream155** using the channel's parameters stored in local memory. FRM cells are then sent every Nrm cells or at Trm (typically10) cells/sec - whichever is the greater. The **FireStream155** keeps a count of data cells between FRM cells and also timestamps the last FRM transmission to make sure these rules are obeyed. Every time an FRM cell is sent the count of FRM cells since last BRM is incremented. If the circuit's CCR becomes zero then the FRM cells may be optionally sent out of rate with the CLP bit set. If the channel runs out of data, no further FRM cells are sent.

### 5.3.3 Reception of BRM cells

When a BRM cell is received it is examined to see if the NI or CI are set or if the ER is programmed. The transmission rate is adjusted accordingly. Also if BN = 0, the count of FRM cells sent on this ABR channel since the last BRM cell was received is reset.

#### 5.3.4 No Data To Send

If a channel's data source is exhausted, the **FireStream155** marks the channel as being in a waiting state. During this period the ADTF timeout is monitored. If it expires then the channel becomes idle and returns to its initial state (the rate is reset to ICR). Otherwise if new data arrives it continues to be processed using existing parameters.

#### 5.3.5 Destination Behaviour

The destination behaviour confirms to the specification in TM 4.0 section 5.10.5.

### 5.3.6 Reception of FRM cells

FRM cells received by the **FireStream155** are processed and the relevant parameters stored in local memory. FRM turnaround strategies 1, 2, 3 and 4 are supported.

Note that the **FireStream155** does not store the SN and QL fields of the RM cell. These fields are set to zero on outgoing FRM cells. However, the user can program the **FireStream155** to pass RM cells in Transparent Cell buffers to allow access to the received SN and QL fields.

### 5.3.7 Transmission of BRM cells

BRM cells are constructed from the parameters stored from a previous FRM cell reception but may be modified if the congested destination behaviour is enabled.

## 5.3.8 Congested Destination

The system environment of the **FireStream155** may be such that from time to time resources to handle receive traffic become scarce. In this case the Host can instruct the **FireStream155** to modify the BRM cells it sends out - either by use of the NI and CI bits or by modifying the Explicit Cell Rate by a factor of 1/2<sup>n</sup>. Each ABR channel can be assigned to one of eight groups so that only an

appropriate selection of channels are affected. This assignment may correspond with the association of channels with the 8 Buffer Free Pools.

#### 5.3.9 Uni-directional Channel

The **FireStream155** may receive RM cells on a channel where there is no corresponding transmit channel. In this case the RM cell will be turned round immediately and sent back out-of-rate.

## 5.4 UBR Implementation

UBR traffic is implemented in a similar way to CBR in that it is always scheduled at its peak rate. It is recommended that the lowest priority calendar be used for this traffic type.

# 5.5 Overall Traffic Shaping

The overall rate of ATM cell transmission can be controlled by an additional leaky bucket process. The peak and average rates and the bucket size are all programmable via the Cell Output Shaping Configuration register.

# 5.6 Configuration and Performance Monitoring

#### 5.6.1 Channel Initialisation

The **FireStream155** traffic management parameters are stored in local memory rather than host memory. As for all parameter initialisation, the Transmit Pending Queues or on chip queue are used to allow the user to pass the necessary values to the **FireStream155**.

#### 5.6.2 Channel Parameter Modification

The **FireStream155** Pending Queues can be used during normal operation to pass commands to the device to modify the Traffic Management Parameters. This process can be immediate or linked to a particular place in the data stream (e.g. at the end of a packet).

# **5.6.3** Performance Monitoring

The **FireStream155** Commands can also be used during normal operation to report the status of the Traffic Management Parameters. The entire Traffic Management local storage can be dumped to Host memory.

# 5.7 GFC Support

Generic Flow Control (GFC) is a mechanism allowing a Controlling function to control the Traffic Output from a controlled device, using the 4-bit GFC field in ATM cell headers (GFC is applicable to UNI interfaces only). The GFC algorithm may be applied independently to each calendar. Each calendar may be 'assigned' to the GFC algorithm and may be 'controlled' or 'uncontrolled'. (refer to ITU specification I.361).

A counter is set by the GFC fields of incoming cells and decremented when a cell is sent on a 'controlled' calendar.

In certain circumstances, a user may wish to be informed of changes in the GFC field, for example, when the GFC field is being used within a system to convey other status information. The **FireStream155** can optionally inform the Host via an RBRQ entry, of any change in the GFC field on a per channel basis.

### 5.8 Rate Parameters

The various rate parameters (e.g. PCR, SCR) are programmed using the binary floating point representation as described in TM 4.0 section 5.10.3.2. For example, a rate of 155Mbps equates to a PCR setting of 0x64C9.

# 6 Programming Interface

### 6.1 Concepts

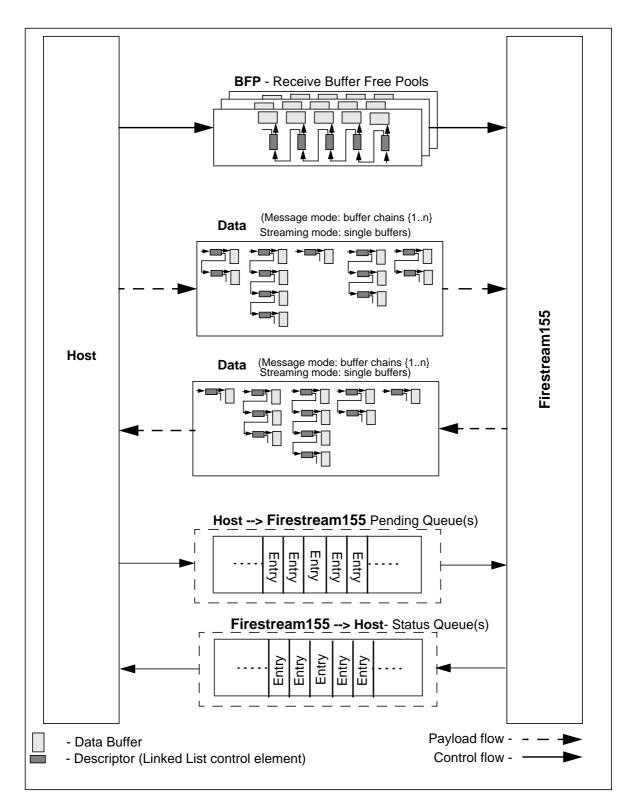

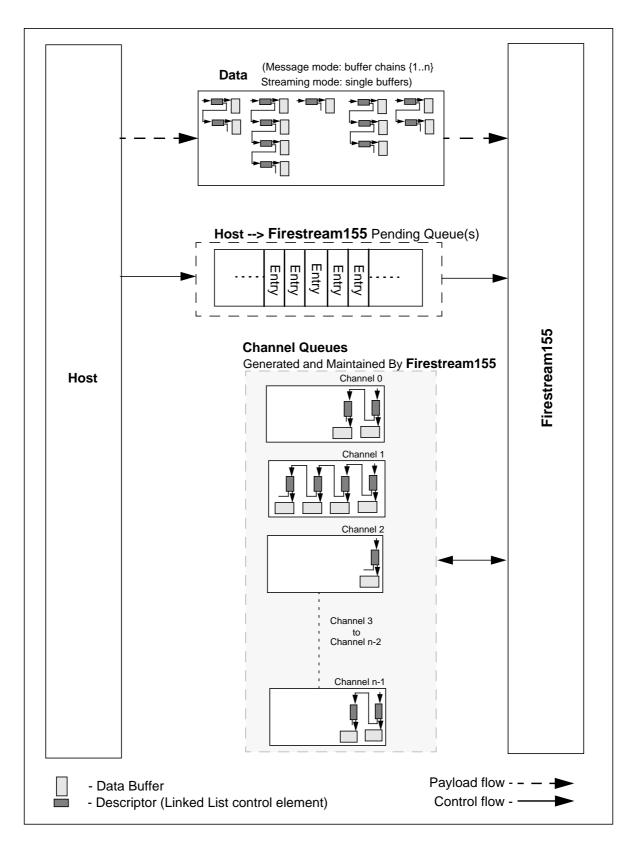

The Programming (Hardware-Software) Interface defines the bi-directional interface between the Host Processor Software and the **Firestream155**. Figure 8 shows the basic data structures used by the **Firestream155**. Communication between the Host and the device is achieved via **Firestream155**->Host and Host->**Firestream155** queue structures in an area of memory accessible by both the Host and the **Firestream155** (Shared Memory).

Payload data is transferred between the Host and the **Firestream155** via data buffers. Each data buffer has an associated descriptor. The descriptor contains a pointer to the data buffer, and may additionally provide limited control information about the data buffer. A descriptor is an area of memory containing the linked list control information associated with a data buffer.

#### 6.1.1 Transmit Path

When data is to be transmitted an entry is placed on an appropriate Pending Queue. This entry contains a pointer to a single descriptor or pointers to the beginning and end of a linked list of descriptors, that in turn point to the buffers containing the data to be transmitted.

The **Firestream155** maintains a linked list of data to be transmitted for each channel, using descriptors. This is called the Channel Queue. When the Host passes new data for transmission, the **Firestream155** adds the linked list onto the end of the appropriate Channel Queue. The Channel Queue concept is shown in Figure 9. When the **Firestream155** has completed transmission of the User Data, used descriptors will be returned to the Host via a Transmit Buffer Release Queue entry.

#### 6.1.2 Receive Path

When the **Firestream155** receives the first cell of a packet, it will obtain a new Receive Descriptor from a Buffer Free Pool. A Buffer Free Pool is a linked list of descriptors in Shared Memory which is constructed and maintained by the Host.

The **Firestream155** places the user data in the buffer pointed to by that descriptor. When a termination event (usually end of buffer or end of packet) is recognised by the **Firestream155**, an entry is placed upon an appropriate Buffer Ready Queue. This entry contains a pointer to the beginning (and optionally the end) of a linked list of descriptors, which in turn point to the received packet data. The Buffer Ready Queue entry also contains status information regarding the received data.

Figure 8 Firestream155 Basic Data Structures overview

Figure 9 Transmit Path Overview

## 6.2 FireStream155 Modes of Operation

Four major modes of operation are supported by the **FireStream155**. Packet (Message) Mode, Streaming Mode, Store & Forward Mode and Position Mode. The latter two modes are derived from Streaming Mode and are used to maintain the position of OAM cells within a received cell stream.

### 6.2.1 Packet (Message) Mode

In Packet (Message) Mode, a complete AAL PDU is stored in one or more data buffers. The complete AAL PDU is passed between the Host and **FireStream155** in a linked list (or chain) of buffers.

In the transmit direction, pointers to the head and the tail of the chain of buffers are passed to the **FireStream155** using a Pending Queue entry.

In the Receive direction, data is only returned to the Host when a complete AAL PDU has been received into one (or more) buffers. A linked list (chain) of receive data buffers is formed in Shared Memory by the **FireStream155** as data is received. When a complete packet has been received, the linked list is passed to the Host via a Receive Buffer Ready Queue (RBRQ) entry. If OAM cells are mixed within the received cell stream, they are passed from the **FireStream155** to the Host via separate RBRQ entries.

Two distinct types of Packet (Message) Mode are specified: Packet Mode (Single Buffer) and Packet Mode (Multiple Buffers). In the former, a single buffer contains the whole AAL PDU, and in the latter the AAL PDU may be stored in one or more buffers. If a receive channel is programmed as packet Mode (Single Buffer) and the AAL PDU is too large to fit into a single buffer, packet re-assembly is aborted and the buffer is returned to the Host via a Buffer Ready Queue entry, which indicates the error status.

# 6.2.2 Streaming Mode

Streaming mode allows incomplete AAL PDU payload data to be transferred between the Host and **FireStream155**. On transmit, data can be passed to the **FireStream155** for transmission as part of an AAL PDU before the Host has compiled and buffered the complete AAL PDU.

Similarly on receive, data buffers can be passed to the Host for processing before the end of the AAL PDU is detected. When a data buffer becomes full, it is immediately passed to the Host via an RBRQ entry. No linked lists are formed by the **FireStream155** in Shared Memory.

Note that an OAM cell's position in the receive cell stream is not maintained in Streaming Mode but is provided on a separate queue entry.

#### 6.2.3 Store & Forward Mode

The Store & Forward operation allows the **FireStream155** to be used as part of a simple switch or uplink station. Receive data may be passed from the RBRQ to a Transmit Pending Queue with minimal Host intervention.

Store & Forward mode is a modified form of Streaming Mode. The only difference is in the way Store & Forward Mode treats non-payload cells (e.g. OAM cells) in the receive cell stream. The position of OAM cells in the receive data stream is maintained by immediately terminating the current data buffer and placing the entry on the RBRQ followed by the OAM cell in a separate buffer. Note that in certain

circumstances, the number of payload bytes in a data buffer reported by the **FireStream155** may include pad bytes.

#### 6.2.4 Position Mode

In certain applications, for example OAM based encryption or Cells in Frames, other than Store & Forward Mode, it is important to maintain the position of control cells (e.g. OAM cells) within a data stream. This is achieved using Position Mode. This mode is similar to Store & Forward Mode except that the current data buffer is not returned to the Host until the next data cell is received, The ensures that the correct packet length is always reported to the Host.

### 6.2.5 Transparent Payload

The Host or FireStream155 provides multiple cell payloads (48 bytes) in data buffers.

In the transmit direction, the Host provides the data via a descriptor in a Transmit Pending Queue entry. Each 48 byte payload data has an ATM header added by the **FireStream155**, before being transmitted. No further AAL processing is performed. A CRC10 calculation may be performed on the cell payload. This 10-bit result overwrites the last 10-bits of each ATM cell payload.

In the receive direction, the **FireStream155** removes the ATM header from received data cells, prior to writing the 48 bytes of payload data to a data buffer. The **FireStream155** may also perform a CRC10 check on each incoming cell payload. If a CRC10 error occurs, the current buffer is returned to the Host via a Receive Buffer Ready Queue entry, which indicates the CRC10 failure. Further received data is placed in a new buffer.

## 6.2.6 Transparent Cell

The Host or **FireStream155** provide multiple ATM cells (48 payload bytes, plus default ATM header, but excluding the HEC byte). This 52 byte data is contiguous in the data buffer.

In the transmit direction, the Host provides the data via descriptors in a Transmit Pending Queue entry. As in Transparent Payload mode, an optional CRC10 calculation may be performed, with the 10-bit result overwriting the last 10 bits of each ATM cell payload.

In the receive direction, the **FireStream155** writes the complete cell (48 byte data plus ATM header, excluding HEC byte) into a data buffer. An optional CRC10 check may be performed, as in Transparent Payload mode.

Note that in the transmit data buffer, the ATM cell header must be written in little endian format. i.e. the first header byte of the cell should be in the most significant address. Similarly, the header will appear in this format for received data buffers.

### 6.2.7 OAM Cell Support

Any active receive channel may receive F4 or F5 OAM cells. The **FireStream155** does not autonomously process OAM cells. However there is a mechanism to allow the **FireStream155** to pass OAM cells to the Host using transparent cell mode. Each OAM cell uses a separate buffer and reception is indicated using special Receive Buffer Ready Queue entries. The forwarding of OAM cells to the Host can be configured on a per-channel basis. Alternatively, the **FireStream155** is able to extract and discard these cells.

#### 6.3 Control Functions

#### 6.3.1 Channel and Packet Ageing

#### **Receive Packet Ageing**

The **FireStream155** implements Receive Packet ageing. This is a mechanism by which the Host can specify a maximum time between receiving the first and last cell of a packet. The Receive Packet Ageing threshold value is programmable between 1ms and 30s. The Receive Packet Ageing function can be enabled or disabled independently for each receive channel. When a packet exceeds the maximum age, the **FireStream155** passes the existing data buffer(s) to the Host via a Receive Buffer Ready Queue entry with the Receive Packet Ageing Status code. All further data for that packet is discarded.

#### **Receive Channel Ageing**

The **FireStream155** implements Receive Channel ageing. This is a mechanism by which the Host can specify a maximum time between receiving packets. The Receive Channel Ageing threshold value is programmable between 4ms and 120s. The Receive Channel Ageing function can be enabled or disabled independently for each receive channel. When an idle period between packets exceeds the maximum age, the **FireStream155** passes a message to the Host via a Receive Buffer Ready Queue entry with the Receive Channel Ageing Status code. The Host may than take whatever action it deems necessary.

### 6.3.2 Interrupts

The **FireStream155** can generate an external interrupt in order to inform the Host of events. For example, the **FireStream155** may interrupt the Host when a write, or a number of writes, to a Receive Buffer Ready Queue takes place. This allows the Host to be designed to poll status/pointer registers in the **FireStream155**, or to be interrupt driven. Each interrupt event can be independently maskable and a global interrupt enable is provided.

There are several mechanisms defined for accessing the **FireStream155** Interrupt Status register and Re-Enabling Interrupts during interrupt servicing.

These mechanisms are:

- Read and Clear: when the Host reads the FireStream155 Interrupt Status Register (ISR), the interrupt flags are cleared at completion of the bus read cycle.

- Read and No Clear: when the Host reads the FireStream155 ISR, the interrupt flags are not cleared. Clearing the flags requires an separate write to the Interrupt Under Service Register (IUSR). Any bit set in the IUSR by the Host write, will clear the corresponding interrupt from the ISR.

- Read, Clear and Inhibit: when the Host reads the FireStream155 ISR, the interrupt flags are

cleared at completion of the bus read cycle. Additionally, FireStream155 interrupt reporting is

globally disabled. A write to the FireStream155 is required to globally re-enable interrupt

generation.

- Read, No Clear and Inhibit: when the Host reads the FireStream155 ISR, the interrupt flags are

not cleared, and FireStream155 interrupt reporting is globally disabled. Clearing interrupt

conditions requires a separate write to the IUSR. Any bit set in the IUSR by the Host write, will

clear the corresponding interrupt from the ISR. A separate write to the **FireStream155** is required to globally re-enable interrupt generation.

#### 6.3.3 Register Access and Register Shadowing

All registers within the FireStream155 are readable.

In Addition, the **FireStream155** can be configured to shadow queue pointers and status information in Host memory. This information is updated at a programmable interval provided that some change has occurred in one or more of the shadowed registers. This mechanism eliminates unnecessary PCI slave reads which are inefficient and reduce system performance.

The shadowing function is configured by programming a Shadow Base Address, a Shadow Update Period and the Shadow Select bit in the Shadow Configuration Register and by setting the value of INTMODE in SAR Mode Register 0. The shadowing function is enabled by setting the SHADEN bit in SAR Mode 0 Register.

All Shadowed registers are written to system memory when the programmed time interval expires provided that a change has occurred in at least one of the shadowed registers. If no change has occurred at this point then the next change immediately triggers an update. The hardware interrupt will not be driven until the shadow register update has been completed and must be explicitly cleared using the Interrupt Under Service Register (INTMODE 00 is not supported if using shadowing).

Further shadow updates may be inhibited until the IUSR has been accessed by setting the INTMODE field in SAR Mode Register 0 to Read, No Clear mode (01).

The registers that are shadowed are shown in Table 2 and Table 3.

| Offset From<br>Shadow Base<br>Address (Hex) | Register                              | Register Offset<br>(Hex) |

|---------------------------------------------|---------------------------------------|--------------------------|

| 00                                          | Rx Buffer Ready Queue 3 Write Pointer | 17C                      |

| 04                                          | Rx Buffer Ready Queue 2 Write Pointer | 168                      |

| 08                                          | Rx Buffer Ready Queue 1 Write Pointer | 154                      |

| 0C                                          | Rx Buffer Ready Queue 0 Write Pointer | 140                      |

| 10                                          | Tx Buffer Release Queue Write Pointer | 02C                      |

| 14                                          | HP Tx Pending Queue Read Pointer      | 008                      |

| 18                                          | LP Tx Pending Queue Read Pointer      | 018                      |

| 1c                                          | Status Queue Write Pointer            | 054                      |

| 20                                          | Buffer Free Pool Status               | 130                      |

| 24                                          | Interrupt Status Register             | 064                      |

Table 2 Shadowed Registers (Shadow Select = 0)

| Offset From<br>Shadow Base<br>Address (Hex) | Register                             | Register Offset<br>(Hex) |

|---------------------------------------------|--------------------------------------|--------------------------|

| 00                                          | Rx Buffer Ready Queue 3 Read Pointer | 178                      |

| 04                                          | Rx Buffer Ready Queue 2 Read Pointer | 164                      |

| 08                                          | Rx Buffer Ready Queue 1 Read Pointer | 150                      |

| 0C                                          | Rx Buffer Ready Queue 0 Read Pointer | 13C                      |

| 10                                          | Tx Buffer Release Queue Read Pointer | 028                      |

| 14                                          | HP Tx Pending Queue Write Pointer    | 00C                      |

| 18                                          | LP Tx Pending Queue Write Pointer    | 01C                      |

| 1c                                          | Status Queue Read Pointer            | 050                      |

| 20                                          | Buffer Free Pool Status              | 130                      |

| 24                                          | Interrupt Status Register            | 064                      |

Table 3 Shadowed Registers (Shadow Select = 1)

#### 6.3.4 Low Priority Discard Modes

The **FireStream155** provides two mechanisms to allow graceful degradation of receive performance under heavy system loading and are designed to prevent loss of critical data.

#### **Receive Buffer Manager LPD**

If there is a scarcity of free receive buffers, this mechanism allows low priority traffic to be discarded. Each receive channel can be marked as low priority by clearing the Buffer Free Pool Priority bit if the receive configuration. A receive descriptor will only be allocated to a low priority channel if there is a minimum number of buffers available on the associated Buffer Free Pool. This minimum value is programmed by the host, and is the same value as that used for the Buffer Free Pool Nearly Empty interrupt (specified in the Buffer Free Pool Configuration registers). If a channel does not get a requested buffer, then the user is notified by an entry on the associated Receive Buffer Ready Queue and the rest of the packet is discarded.

#### Reassembly LPD

If the host PCI bus is saturated and the 96-cell receive buffer begins to fill, this mechanism allows low priority packets to be dropped at the ingress to this buffer. Each receive channel can be marked as low priority by setting the PRI bit in the receive configuration. The setting of the PRI\_MODE bits in the Receive Address Select 0 register determines the discard behaviour based on the fill level of the buffer. This allows the user to tune the system to minimize cell loss.

#### 6.3.5 Software Reset

The FireStream155 implements two levels of Software Reset.

- Software Reset 0 has the same effect as a Hard Reset. All LRAM configuration data is lost.

- Software Reset 1 resets all FireStream155 internal logic but leaves the LRAM data structures untouched.

# 6.3.6 Cell Loss Priority Control and Reporting

The Cell Loss Priority (CLP) bit within the ATM Cell header indicates the relative priority of the Cell. In the Transmit direction, the Host device has control over this bit (per channel) using the Set CLP and Reset CLP commands. By linking this command into the transmit data stream, the Host can control the CLP bit on a per buffer basis. The CLP of received data is reported via the CLP bit of the Receive Buffer Ready Queue. This bit is set if any of the cells within the packet associated with data buffer(s) for the queue entry were received with CLP=1.

# 6.3.7 Congestion Control and Reporting

Congestion within an ATM network is indicated via bit 1 of the PTI field in ATM cell header. In the Transmit direction, the Host device has control over this bit (per channel) using the Set Congestion and Reset Congestion commands. By linking this command into the transmit data stream, the Host can control the CLP bit on a per buffer basis. The Congestion state of received data is reported via the CI and CIL bits of the Receive Buffer Ready Queue. The CI bit is set if any of the cells within the data buffer(s) for the queue entry were received with PTI[1]=1, and the CIL bit reports the Congestion status of the last received cell of the packet.

### 6.3.8 Cells In Frames (CIF) Support

Position Mode can be used to aid the host in implementing Cells-In-Frames. On receive, any change in the cell header, or the reception of an OAM/RM cell can be used to terminate packet reception. On transmit, data and OAM/RM cells can be interleaved in the per-channel queue as can commands to alter the cell header.

## 6.3.9 LAN Emulation (LANE) Support

The Encapsulated Header function can be used to support LAN Emulation. This allows the Host to add a fixed header (of 1 to 12 bytes) onto each transmitted packet.

# 6.4 Data Buffer Management

Data buffers are used to transfer payload and control data between the Host and the **FireStream155**. Each data buffer has a descriptor associated with it. The descriptor formats are defined in paragraph 6.5 below.

#### 6.4.1 Transmit Path Data Buffers

The Host may have limited control over transmit data buffers, therefore, there are few limitations placed upon these buffers. The minimum size of transmit data buffers is 1 byte and the maximum size is 65536 bytes.

There is no restriction on the memory alignment of Transmit data buffers (other than alignment on a byte boundary). Similarly there is no restriction on the size of data buffers other than those imposed on the AAL Packet length. This means that a single cell payload can straddle several buffers (up to a single buffer per byte). Note that a small buffer size will lead to a reduction in system performance, as will using buffers that are not D-Word aligned.

#### 6.4.2 Receive Path Data Buffers