- Single-Chip EtherLoop Modem

- Optimized for Client and Server Modem Applications

- Glueless Interface to EtherLoop Processor Interface, Analog-to-Digital Converter (ADC), and Digital-to-Analog Converter (DAC)

- Implements 6-Mbit/s Modem Algorithms

- Supports Wide Range of Symbol Rates, Allowing Adaptation to Line Conditions

- Operates in Presence of Bridge Taps

- Industrial Operating Free-Air Temperature to Support Central Office and Distributed Server Applications

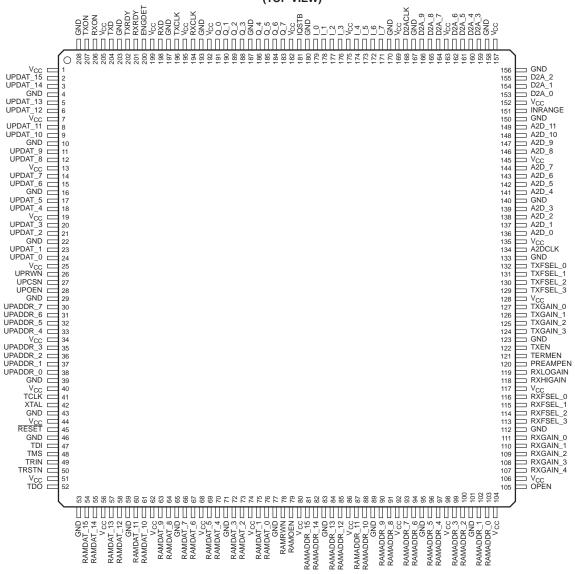

- Packaged in 208-Pin Plastic Quad Flatpack

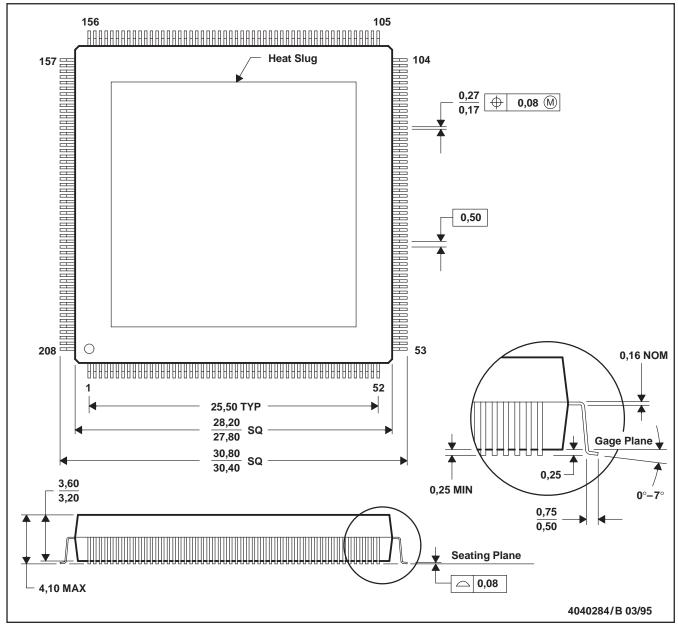

# PPB PACKAGE<sup>†</sup> (TOP VIEW)

†Thermally enhanced molded plastic package with a heat slug (HSL)

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

EtherLoop is a trademark of Elastic Networks.

#### description

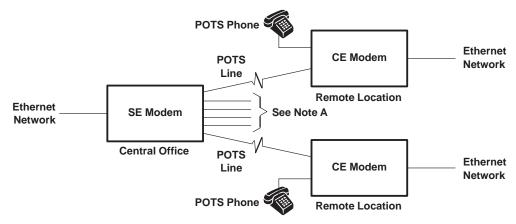

The TNETEL1200 is an EtherLoop modem. EtherLoop technology enables simultaneous voice and Ethernet communication over local-loop plain old telephone service (POTS) wiring. The TNETEL1200 supports data rates of up to 6 Mbit/s and POTS wire lengths of up to 21,000 feet. Figure 1 shows a typical system with an EtherLoop modem located at each end of the POTS line. Each EtherLoop modem has a 10Base-T Ethernet interface and is responsible for buffering Ethernet data before sending it over the POTS wire. The server-end (SE) EtherLoop modem is located in a central switching office and can communicate with several client-end (CE) EtherLoop modems, based on a round-robin arbitration scheme. The CE EtherLoop modem typically is located at a remote site.

NOTE A: Flexible multiplexing scheme allows one SE modem to interface with many CE modems.

Figure 1. Typical EtherLoop System

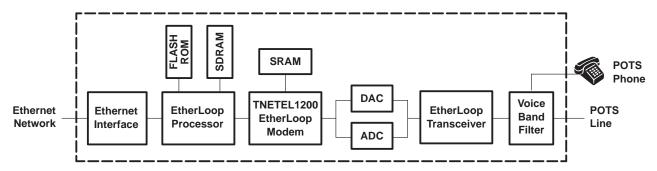

Figure 2 shows a block diagram of a typical CE EtherLoop modem. Ethernet data destined for the POTS wire is received via 10Base-T interface and presented to the EtherLoop processor. The EtherLoop processor performs Ethernet frame processing and buffer management. The EtherLoop processor sends buffered Ethernet frames to the TNETEL1200 EtherLoop modem (via an HDLC interface). The TNETEL1200 performs data modulation before passing the modulated digital data to a digital-to-analog converter (DAC). The resulting analog signal passes to the EtherLoop transceiver, which acts as the line interface. The modem uses a half-duplex communication protocol over the POTS wire, and data received from the POTS wire follows the reverse path back to the Ethernet framer.

Figure 2. Typical CE EtherLoop Modem

## description (continued)

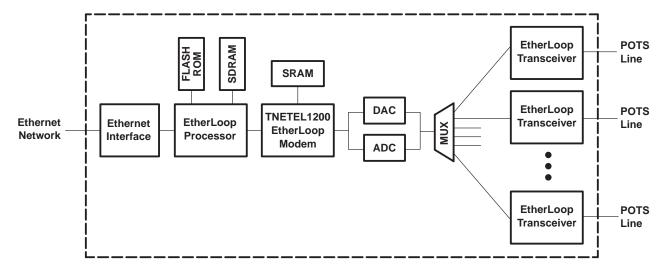

Figure 3 shows a block diagram of a typical SE EtherLoop modem. Data flow follows the same path as in the CE EtherLoop modem. In the SE application, the EtherLoop processor also performs round-robin arbitration between each of the attached EtherLoop transceiver devices.

Figure 3. Typical SE EtherLoop Modem

#### summary of TNETEL1200 EtherLoop modem

- Modulates serial HDLC data stream and presents results to DAC

- Demodulates data from analog-to-digital converter (ADC) and presents results as an HDLC data stream

- Supports wide range of data symbol rates to accommodate a range of line conditions

#### transmitter and receiver

The TNETEL1200 performs modulation of the digital data stream transmitted from the EtherLoop modem and demodulation of the digital data stream received by the EtherLoop modem. The TNETEL1200 supports a variety of modulation schemes and symbol rates. This flexibility allows the modem to adapt to changing conditions on the POTS line. The modem is designed to compensate for the presence of bridge taps on the POTS line, allowing for easy service deployment.

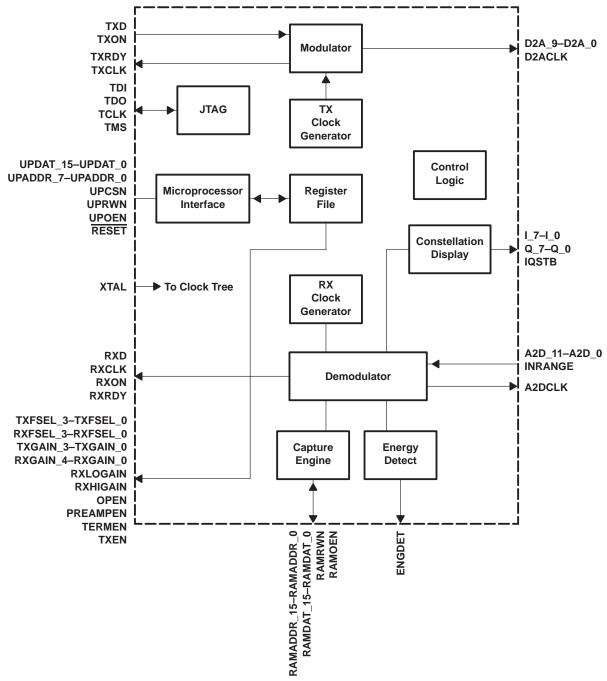

Figure 4 shows the EtherLoop modem block diagram.

Figure 4. EtherLoop Modem Block Diagram

## **Terminal Functions**

# microprocessor

| TERMINAL                                                                                                                                              |                                                                                        | +    | DESCRIPTION                                                                                                   |  |  |

|-------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------|------|---------------------------------------------------------------------------------------------------------------|--|--|

| NAME                                                                                                                                                  | NO.                                                                                    | 1/0† | DESCRIPTION                                                                                                   |  |  |

| UPADDR_7<br>UPADDR_6<br>UPADDR_5<br>UPADDR_4<br>UPADDR_3<br>UPADDR_2<br>UPADDR_1                                                                      | 30<br>31<br>32<br>33<br>35<br>36<br>37                                                 | I    | Bits 7–0 of the microprocessor address bus; used to address the register file.                                |  |  |

| UPADDR_0                                                                                                                                              | 38                                                                                     |      |                                                                                                               |  |  |

| UPCSN                                                                                                                                                 | 27                                                                                     | I    | Microprocessor chip-select line (active low). UPCSN is used to initiate an access to the register file.       |  |  |

| UPDAT_15 UPDAT_14 UPDAT_13 UPDAT_12 UPDAT_11 UPDAT_10 UPDAT_9 UPDAT_8 UPDAT_7 UPDAT_6 UPDAT_5 UPDAT_5 UPDAT_4 UPDAT_3 UPDAT_3 UPDAT_2 UPDAT_1 UPDAT_1 | 2<br>3<br>5<br>6<br>8<br>9<br>11<br>12<br>14<br>15<br>17<br>18<br>20<br>21<br>23<br>24 | I/O  | Bits 15–0 of the microprocessor data bus; used to communicate with the register file.                         |  |  |

| UPOEN                                                                                                                                                 | 28                                                                                     | I    | Microprocessor output-enable line (active low). UPOEN enables the output onto the data bus.                   |  |  |

| UPRWN                                                                                                                                                 | 26                                                                                     | I    | Microprocessor read/write line. UPRWN is used to differentiate between reads and writes to the register file. |  |  |

$<sup>\</sup>dagger$  I = input, O = output

## system

| TERMINAL |     | +    | DESCRIPTION                                                                 |  |  |

|----------|-----|------|-----------------------------------------------------------------------------|--|--|

| NAME     | NO. | 1/0† | DESCRIPTION                                                                 |  |  |

| RESET    | 45  | Ι    | System reset. If RESET is set low, it sets all flip-flops to initial state. |  |  |

| XTAL     | 42  | I    | System clock. Frequency is 80 MHz, 50% duty cycle.                          |  |  |

<sup>†</sup> I = input, O = output

# serial loop communications

| TERMIN | NAL | +    | DESCRIPTION                                                                                                                                  |  |

|--------|-----|------|----------------------------------------------------------------------------------------------------------------------------------------------|--|

| NAME   | NO. | 1/0† | DESCRIPTION                                                                                                                                  |  |

| RXCLK  | 194 | 0    | Receive clock. RXCLK is driven by the TNETEL1200 to clock receive data into the microprocessor.                                              |  |

| RXD    | 198 | 0    | Receive data. RXD is the data from the TNETEL1200 from the loop being sent to the microprocessor.                                            |  |

| RXON   | 206 | I    | Receive on. RXON is driven by the microprocessor to enable the TNETEL1200 loop receiver.                                                     |  |

| RXRDY  | 201 | 0    | Receive ready. RXRDY is driven by the TNETEL1200 to inform the microprocessor that the TNETEL1200 is ready for receiving data from the loop. |  |

| TXCLK  | 196 | 0    | Transmit clock. TXCLK is driven by the TNETEL1200 to clock transmit data out of the microprocessor.                                          |  |

| TXD    | 204 | I    | Transmit data. TXD is the data from the microprocessor to be driven onto the loop by the TNETEL1200.                                         |  |

| TXON   | 207 | I    | Transmit on. TXON is driven by the microprocessor to enable the TNETEL1200 loop transmitter.                                                 |  |

| TXRDY  | 202 | 0    | Transmit ready. TXRDY is driven by the TNETEL1200 to inform the microprocessor that the TNETEL1200 is ready for transmitting onto the loop.  |  |

$<sup>\</sup>dagger$  I = input, O = output

## signal data

| TERMINAL |     | +    | DESCRIPTION                                                                       |  |  |  |

|----------|-----|------|-----------------------------------------------------------------------------------|--|--|--|

| NAME     | NO. | 1/0† | DESCRIPTION                                                                       |  |  |  |

| A2D_11   | 149 |      |                                                                                   |  |  |  |

| A2D_10   | 148 |      |                                                                                   |  |  |  |

| A2D_9    | 147 |      |                                                                                   |  |  |  |

| A2D_8    | 146 |      |                                                                                   |  |  |  |

| A2D_7    | 144 |      |                                                                                   |  |  |  |

| A2D_6    | 143 |      | Bits 11–0 of the data signal values sent from the ADC in the analog loop receiver |  |  |  |

| A2D_5    | 142 | l '  | Bits 11 of the data signal values sent from the 7De in the dinalog loop received  |  |  |  |

| A2D_4    | 141 |      |                                                                                   |  |  |  |

| A2D_3    | 139 |      |                                                                                   |  |  |  |

| A2D_2    | 138 |      |                                                                                   |  |  |  |

| A2D_1    | 137 |      |                                                                                   |  |  |  |

| A2D_0    | 136 |      |                                                                                   |  |  |  |

| A2DCLK   | 134 | 0    | Clock. A2DCLK is used to clock the data out of the ADC.                           |  |  |  |

| D2A_9    | 166 |      |                                                                                   |  |  |  |

| D2A_8    | 165 |      |                                                                                   |  |  |  |

| D2A_7    | 164 |      |                                                                                   |  |  |  |

| D2A_6    | 162 |      |                                                                                   |  |  |  |

| D2A_5    | 161 | 0    | Bits 9–0 of the data signal values sent to the DAC in the analog loop transmitter |  |  |  |

| D2A_4    | 160 |      | bits 5 of the data signal values sent to the BAO in the analog loop transmitted   |  |  |  |

| D2A_3    | 159 |      |                                                                                   |  |  |  |

| D2A_2    | 155 |      |                                                                                   |  |  |  |

| D2A_1    | 154 |      |                                                                                   |  |  |  |

| D2A_0    | 153 |      |                                                                                   |  |  |  |

| D2ACLK   | 168 | 0    | Clock. D2ACLK is used to clock the data into the DAC.                             |  |  |  |

| INRANGE  | 151 | I    | Data overflow signal from the ADC                                                 |  |  |  |

$<sup>\</sup>dagger I = input, O = output$

# capture buffer

| TERMINAL                                                                                                                                                                                            |                                                                                                 | +    | DESCRIPTION                                                                                                  |  |  |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------|------|--------------------------------------------------------------------------------------------------------------|--|--|

| NAME                                                                                                                                                                                                | NO.                                                                                             | 1/0† | DESCRIPTION                                                                                                  |  |  |

| RAMADDR_15 RAMADDR_14 RAMADDR_13 RAMADDR_12 RAMADDR_11 RAMADDR_10 RAMADDR_9 RAMADDR_8 RAMADDR_7 RAMADDR_6 RAMADDR_6 RAMADDR_5 RAMADDR_4 RAMADDR_4 RAMADDR_3 RAMADDR_1 RAMADDR_1 RAMADDR_1 RAMADDR_1 | 81<br>82<br>84<br>85<br>87<br>88<br>90<br>91<br>93<br>94<br>96<br>97<br>99<br>100<br>102<br>103 | 0    | Bits 15–0 of the address path from the TNETEL1200 and the capture buffer SRAM                                |  |  |

| RAMDAT_15 RAMDAT_14 RAMDAT_13 RAMDAT_12 RAMDAT_11 RAMDAT_10 RAMDAT_9 RAMDAT_9 RAMDAT_7 RAMDAT_6 RAMDAT_6 RAMDAT_5 RAMDAT_4 RAMDAT_3 RAMDAT_4 RAMDAT_3 RAMDAT_1 RAMDAT_1 RAMDAT_1 RAMDAT_1           | 54<br>55<br>57<br>58<br>60<br>61<br>63<br>64<br>66<br>67<br>69<br>70<br>72<br>73<br>75<br>76    | I/O  | Bits15–0 of the data path between the TNETEL1200 and the capture buffer SRAM                                 |  |  |

| RAMOEN                                                                                                                                                                                              | 79                                                                                              | 0    | SRAM output enable (active low). RAMOEN is the output enable from the TNETEL1200 to the capture buffer SRAM. |  |  |

| RAMRWN                                                                                                                                                                                              | 78                                                                                              | 0    | SRAM read/write. RAMRWN is the read/write signal from the TNETEL1200 to the capture buffer SRAM.             |  |  |

<sup>†</sup> I = input, O = output

## analog loop control

| TERMINA                                                  | TERMINAL                        |      | DESCRIPTION                                                                    |  |  |  |

|----------------------------------------------------------|---------------------------------|------|--------------------------------------------------------------------------------|--|--|--|

| NAME                                                     | NO.                             | 1/0† | DESCRIPTION                                                                    |  |  |  |

| OPEN                                                     | 105                             | 0    | Open. Control signal to open and close link between line driver and line load. |  |  |  |

| PREAMPEN                                                 | 120                             | 0    | Preamplifier enable. PREAMPEN enables the preamplifier.                        |  |  |  |

| RXFSEL_3<br>RXFSEL_2<br>RXFSEL_1<br>RXFSEL_0             | 113<br>114<br>115<br>116        | 0    | Receiver filter. Bits 3–0 enable the receiver filter sections.                 |  |  |  |

| RXGAIN_4<br>RXGAIN_3<br>RXGAIN_2<br>RXGAIN_1<br>RXGAIN_0 | 107<br>108<br>109<br>110<br>111 | 0    | Receiver gain. Bits 4–0 enable the receiver gain sections (1, 2, 4, 8, 16 dB). |  |  |  |

| RXHIGAIN                                                 | 118                             | 0    | Receiver high gain. RXHIGAIN controls a preamplifier in the receiver.          |  |  |  |

| RXLOGAIN                                                 | 119                             | 0    | Receiver low gain. RXHIGAIN controls a preamplifier in the receiver.           |  |  |  |

| TERMEN                                                   | 121                             | 0    | Termination enable. TERMEN enables the line termination.                       |  |  |  |

| TXEN                                                     | 122                             | 0    | Transmitter enable. TXEN enables the output transmitter sections.              |  |  |  |

| TXFSEL_3<br>TXFSEL_2<br>TXFSEL_1<br>TXFSEL_0             | 129<br>130<br>131<br>132        | 0    | Transmitter filter. Bits 3–0 enable the transmitter filter sections.           |  |  |  |

| TXGAIN_3<br>TXGAIN_2<br>TXGAIN_1<br>TXGAIN_0             | 124<br>125<br>126<br>127        | 0    | Transmitter gain. Bits 3–0 enable transmitter gain sections.                   |  |  |  |

<sup>†</sup> I = input, O = output

## debug

|                                                      | TERMINAL                                             |   | DESCRIPTION                                                       |

|------------------------------------------------------|------------------------------------------------------|---|-------------------------------------------------------------------|

| NAME<br>ENGDET                                       | <b>NO.</b> 200                                       | 0 | Energy detect                                                     |

| I_7<br>I_6<br>I_5<br>I_4<br>I_3<br>I_2<br>I_1        | 171<br>172<br>173<br>174<br>176<br>177<br>178<br>179 | 0 | Bits 7–0 of the I component of the demodulated signal (test only) |

| IQSTB                                                | 181                                                  | 0 | IQSTB is used to clock out the I and Q data (test only).          |

| Q_7<br>Q_6<br>Q_5<br>Q_4<br>Q_3<br>Q_2<br>Q_1<br>Q_0 | 183<br>184<br>185<br>186<br>188<br>189<br>190        | 0 | Bits 7–0 of the Q component of the demodulated signal (test only) |

$<sup>\</sup>dagger I = input, O = output$

# design for test

| TERMII | TERMINAL |      | DESCRIPTION                                  |  |  |  |  |  |

|--------|----------|------|----------------------------------------------|--|--|--|--|--|

| NAME   | NO.      | 1/0† | DESCRIPTION                                  |  |  |  |  |  |

| TDI    | 47       | I    | Test data input                              |  |  |  |  |  |

| TDO    | 52       | 0    | Test data output                             |  |  |  |  |  |

| TCLK   | 41       | I    | Test clock                                   |  |  |  |  |  |

| TMS    | 48       | I    | Test mode select                             |  |  |  |  |  |

| TRIN   | 49       | I    | Asynchronous output pad 3-state (active low) |  |  |  |  |  |

| TRSTN  | 50       | I    | Asynchronous TAP reset (active low)          |  |  |  |  |  |

<sup>†</sup> I = input, O = output

# power supply

|      | TERMINAL                                                                                                                                         | DESCRIPTION              |  |

|------|--------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------|--|

| NAME | NO.                                                                                                                                              |                          |  |

| GND  | 4, 10, 16, 22, 29, 39, 43, 46, 53, 59, 65, 71, 83, 89, 95, 101, 112, 123, 133, 140, 150, 156, 158, 167, 170, 180, 187, 193, 197, 203, 208        | Digital supply return    |  |

| VCC  | 1, 7, 13, 19, 25, 34, 40, 44, 51, 56, 62, 68, 74, 80, 86, 92, 98, 104, 106, 117, 128, 135, 145, 152, 157, 163, 169, 175, 182, 192, 195, 199, 205 | 3.3-V core and I/O power |  |

**Table 1. Processor Interface Signal List**

| TERMINAL NAME   | 1/0† | SIGNAL                                    |

|-----------------|------|-------------------------------------------|

| UPDAT15-UPDAT0  | I/O  | Microprocessor data bus                   |

| UPADDR7-UPADDR0 | I    | Microprocessor address bus                |

| UPRWN           | I    | Microprocessor read/write enable          |

| UPCSN           | I    | Microprocessor chip select (active low)   |

| UPOEN           | i    | Microprocessor output enable (active low) |

$<sup>\</sup>dagger$  I = input, O = output

## **Table 2. Operating Conditions (I/O Terminals)**

#### MICROPROCESSOR

| TERMINAL NAME   | ı/o† | HYSTERESIS | 5-V<br>TOLERANT | 3.6-V<br>FAILSAFE |

|-----------------|------|------------|-----------------|-------------------|

| UPDAT15-UPDAT0  | I/O  | Υ          | N               | Υ                 |

| UPADDR7-UPADDR0 | - 1  | Υ          | N               | N                 |

| UPRWN           | - 1  | Υ          | N               | N                 |

| UPCSN           | - 1  | Υ          | N               | N                 |

$<sup>\</sup>dagger I = input, O = output$

#### SYSTEM

| TERMINAL<br>NAME | TYPE‡ | HYSTERESIS | 5-V<br>TOLERANT | 3.6-V<br>FAILSAFE |

|------------------|-------|------------|-----------------|-------------------|

| XTAL             | Ι     | Υ          | N               | N                 |

| RESET            | I     | Y          | N               | N                 |

<sup>‡</sup>I = input

#### SERIAL LOOP COMMUNICATIONS

| TERMINAL<br>NAME | 1/0† | HYSTERESIS | 5-V<br>TOLERANT | 3.6-V<br>FAILSAFE |

|------------------|------|------------|-----------------|-------------------|

| TXRDY            | 0    |            | N               |                   |

| TXCLK            | 0    |            | N               |                   |

| TXON             | I    | Υ          | N               | N                 |

| TXD              | Ι    | Y          | N               | N                 |

| RXRDY            | 0    |            | N               |                   |

| RXCLK            | 0    |            | N               |                   |

| RXON             | I    | Υ          | N               | N                 |

| RXD              | 0    |            | N               | ·                 |

<sup>†</sup> I = input, O = output

# Table 2. Operating Conditions (I/O Terminals) (Continued)

#### SIGNAL DATA

| TERMINAL<br>NAME | ı/o† | HYSTERESIS | 5-V<br>TOLERANT | 3.6-V<br>FAILSAFE |

|------------------|------|------------|-----------------|-------------------|

| D2A9-D2A0        | 0    |            | Y               |                   |

| D2ACLK           | 0    |            | Υ               |                   |

| A2D11-A2D0       | I    | Υ          | Y               |                   |

| A2DCLK           | 0    |            | Y               |                   |

| INRANGE          | 1    | Y          | Υ               |                   |

$<sup>\</sup>dagger I = input, O = output$

#### **CAPTURE BUFFER**

| TERMINAL NAME      | ı/o† | HYSTERESIS | 5-V<br>TOLERANT | 3.6-V<br>FAILSAFE |

|--------------------|------|------------|-----------------|-------------------|

| RAMDAT15-RAMDAT0   | I/O  | Υ          | N               | Y                 |

| RAMADDR15-RAMADDR0 | 0    |            | N               |                   |

| RAMRDN             | 0    |            | N               |                   |

| RAMOEN             | 0    |            | N               |                   |

$<sup>\</sup>dagger$  I = input, O = output

#### **ANALOG LOOP CONTROL**

| TERMINAL NAME   | TYPE‡ | HYSTERESIS | 5-V<br>TOLERANT | 3.6-V<br>FAILSAFE |

|-----------------|-------|------------|-----------------|-------------------|

| RXGAIN4-RXGAIN0 | 0     |            | Y               |                   |

| RXFSEL3-RXFSEL0 | 0     |            | Y               |                   |

| RXHIGAIN        | 0     |            | Υ               |                   |

| RXLOGAIN        | 0     |            | Y               |                   |

| PREAMPEM        | 0     |            | Υ               |                   |

| TERMEN          | 0     |            | Y               |                   |

| TXGAIN3-TXGAIN0 | 0     |            | Y               |                   |

| TXFSEL3-TXFSEL0 | 0     |            | Υ               |                   |

| RXEN            | 0     |            | Y               |                   |

<sup>‡</sup>O = output

#### **DEBUG**

| TERMINAL<br>NAME | түре‡ | HYSTERESIS | 5-V<br>TOLERANT | 3.6-V<br>FAILSAFE |

|------------------|-------|------------|-----------------|-------------------|

| I_7-I_0          | 0     |            | N               |                   |

| Q_7-Q_0          | 0     |            | N               |                   |

| IQSTB            | 0     |            | N               |                   |

<sup>‡</sup>O = output

Table 2. Operating Conditions (I/O Terminals) (Continued)

#### **DESIGN FOR TEST**

| TERMINAL<br>NAME | ı/o† | HYSTERESIS | 5-V<br>TOLERANT | 3.6-V<br>FAILSAFE |

|------------------|------|------------|-----------------|-------------------|

| TDI              | I    | Υ          | N               | N                 |

| TDO              | 0    |            | N               |                   |

| TCLK             | Ι    | Υ          | N               | N                 |

| TMS              | I    | Y          | N               | N                 |

$<sup>\</sup>dagger$  I = input, O = output

Table 3. Power Consumption (V<sub>CC</sub> = 3.3 V, T<sub>A</sub> = 25°C, R<sub>L</sub> = 500  $\Omega$ )<sup>‡</sup>

| SYMBOL             | DESCRIPTION | POWER<br>(W)§ |

|--------------------|-------------|---------------|

| P <sub>total</sub> | Total power | 1.7           |

$<sup>^{\</sup>ddagger}$  All I/Os have a resistive load of 75  $\Omega$ , and the source and sink current is set to 0 mA.

<sup>§</sup> DFT circuitry is inactive.

### absolute maximum ratings over operating free-air temperature (unless otherwise noted)†

| Core supply-voltage range, V <sub>CC</sub>                                                  | 0.5 V to 4.0 V                            |

|---------------------------------------------------------------------------------------------|-------------------------------------------|

| Input-voltage range, V <sub>I</sub> : Standard TTL/LVCMOS                                   | $\dots$ -0.5 V to V <sub>CC</sub> + 0.5 V |

| 3.6-V fail-safe TTL/LVCMOS                                                                  | 0.5 V to 3.6 V                            |

| 5-V tolerant TTL/LVCMOS                                                                     |                                           |

| Output-voltage range, Vo: Standard TTL/LVCMOS                                               | $\dots$ -0.5 V to V <sub>CC</sub> + 0.5 V |

| 3.6-V fail-safe TTL/LVCMOS                                                                  | –0.5 V to 3.6 V                           |

| 5-V tolerant TTL/LVCMOS                                                                     |                                           |

| Input clamp current for TTL/LVCMOS ( $V_I < 0$ or $V_I > V_{CC}$ ) (see Note 1)             | ±20 mA                                    |

| Output clamp current (V <sub>O</sub> < 0 or V <sub>O</sub> > V <sub>CC</sub> ) (see Note 2) | ±20 mA                                    |

| Electrostatic discharge (100 pF, 1.5 kΩ)                                                    | 4.0 kV                                    |

| Latchup immunity                                                                            | >250 mA at 25°C                           |

| Storage temperature range, T <sub>stq</sub>                                                 | –65°C to 150°C                            |

<sup>†</sup> Stresses beyond those listed under "absolute maximum ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated under "recommended operating conditions" is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

NOTES: 1. Applies to external input and bidirectional buffers (for 5-V tolerant, used  $V_I >$ )

## recommended operating conditions

|                  |                                                                         |                         | MIN | MAX | UNIT |

|------------------|-------------------------------------------------------------------------|-------------------------|-----|-----|------|

| Vcc              | Supply voltage                                                          |                         | 3   | 3.6 | V    |

| \/.              | Input voltage                                                           | TTL/LVCMOS              | 0   | VCC | V    |

| VI               | Input voltage                                                           | 5-V tolerant TTL/LVCMOS |     |     | V    |

| \/a              | Output voltogo                                                          | TTL/LVCMOS              | 0   | VCC | V    |

| VO               | Output voltage                                                          | 5-V tolerant TTL/LVCMOS |     |     | V    |

| \/               | High-level input voltage                                                | TTL/LVCMOS              | 2   | VCC | V    |

| VIH              | riigii-levei iriput voitage                                             | 5-V tolerant TTL/LVCMOS |     |     | V    |

| \/               | Low level input veltore                                                 | TTL/LVCMOS              | 0   | 0.8 | V    |

| VIL              | Low-level input voltage                                                 | 5-V tolerant TTL/LVCMOS |     | 0.8 | V    |

| t <sub>r</sub>   | Input transition (t <sub>r</sub> and t <sub>f</sub> ) time (10% to 90%) |                         | T   | 6   | ns   |

| T <sub>A</sub> ‡ | Ambient temperature                                                     |                         | -40 | 85  | °C   |

| TJ               | Junction temperature (commercial specification)                         |                         | -40 | 125 | °C   |

$<sup>^{\</sup>ddagger}$  T<sub>A</sub> is measured at the surface of the package. No airflow or heatsink is assumed. The maximum ambient temperature is calculated considering  $P_{MAX}$ ,  $R_{\theta JA}$ , and  $T_{J}$ .

#### electrical characteristics over recommended operating conditions

|                   | PARAMETER                                                        | TEST CONDITIONS         | MIN                  | TYP | MAX | UNIT |

|-------------------|------------------------------------------------------------------|-------------------------|----------------------|-----|-----|------|

| Vон               | High-level output voltage                                        | IOH = rated             | V <sub>CC</sub> -0.6 |     |     | V    |

| VOL               | High-level output voltage                                        | I <sub>OL</sub> = rated |                      |     | 0.5 | V    |

| V <sub>hys</sub>  | Hysteresis ( $V_{T+} - V_{T-}$ )                                 |                         |                      | 0.4 |     | V    |

| l                 | Low-level input current (V <sub>in</sub> = V <sub>II</sub> min)  | 3.6-V failsafe          |                      |     | ±1  | μΑ   |

| '  _              | Low-level input current (VIN = VIL min)                          | 5-V tolerant            |                      |     | ±20 | μΑ   |

| I                 | High level input current (\(\lambda = \lambda \tau \max \rangle) | 3.6-V failsafe          |                      |     | ±1  |      |

| L IH              | High-level input current (V <sub>in</sub> = V <sub>IH</sub> max) | 5-V tolerant            |                      |     | ±20 | μΑ   |

| I <sub>IZ</sub> § | 3-state output high-impedance current                            |                         |                      |     | ±20 | μΑ   |

<sup>§ 3-</sup>state or open-drain output must be in high-impedance state.

<sup>2.</sup> Applies to external output and bidirectional buffers (for 5-V tolerant, used  $V_{O}$  >)

# timing requirements over recommended ranges of supply voltage and operating free-air temperature

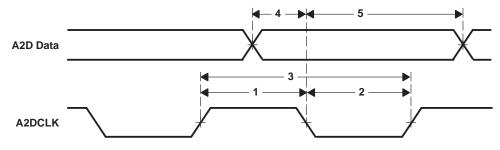

#### A2D interface (see Figure 5)

| NO. |                                                     | MIN N | VIAX | UNIT |

|-----|-----------------------------------------------------|-------|------|------|

| 1   | t <sub>W</sub> Pulse duration, A2DCLK high          | 70    |      | ns   |

| 2   | t <sub>W</sub> Pulse duration, A2DCLK low           | 70    |      | ns   |

| 3   | t <sub>C</sub> Cycle time, A2DCLK                   | 150   |      | ns   |

| 4   | t <sub>SU</sub> Setup time, A2D data before A2DCLK↓ | 10    |      | ns   |

| 5   | t <sub>h</sub> Hold time, A2D data after A2DCLK↓    | 15    |      | ns   |

Figure 5. A2D Interface

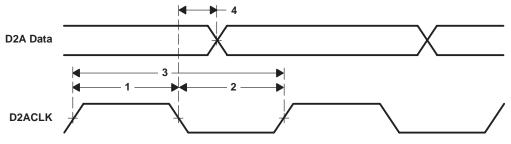

## D2A interface (see Figure 6)

| NO. |                                                     | MIN | MAX | UNIT |

|-----|-----------------------------------------------------|-----|-----|------|

| 1   | t <sub>W</sub> Pulse duration, D2ACLK high          | 75  |     | ns   |

| 2   | t <sub>W</sub> Pulse duration, D2ACLK low           | 25  |     | ns   |

| 3   | t <sub>C</sub> Cycle time, D2ACLK                   | 100 |     | ns   |

| 4   | t <sub>pd</sub> Propagation delay time from D2ACLK↓ |     | 5   | ns   |

Figure 6. D2A Interface

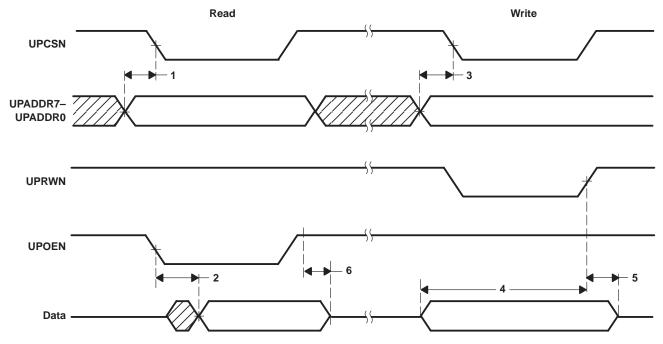

## microprocessor interface (see Figure 7)

| NO. |                                                                                                | MIN | MAX | UNIT |

|-----|------------------------------------------------------------------------------------------------|-----|-----|------|

| 1   | t <sub>SU</sub> Setup time, UPADDR before UPCSN low – address is latched by UPCSN falling edge | 2   |     | ns   |

| 2   | t <sub>d</sub> Delay time, read data valid after last of UPCSN and UPOEN low                   |     | 20  | ns   |

| 3   | t <sub>SU</sub> Setup time, address before UPCSN low                                           | 2   |     | ns   |

| 4   | t <sub>SU</sub> Setup time, write data valid before UPWRN high                                 | 15  |     | ns   |

| 5   | th Hold time, write data valid after UPWRN high                                                | 5   |     | ns   |

| 6   | t <sub>d</sub> Delay time, data high Z after UPOEN high                                        |     | 20  | ns   |

Figure 7. Microprocessor Interface

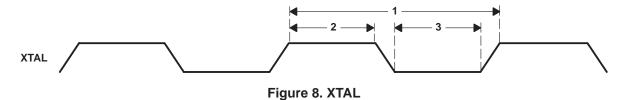

## XTAL (see Figure 8)

| NO. |                                                 | MIN  | MAX | UNIT |

|-----|-------------------------------------------------|------|-----|------|

| 1   | t <sub>C(XTAL)</sub> Cycle time, XTAL           | 12.5 |     | ns   |

| 2   | t <sub>w(XTALH)</sub> Pulse duration, XTAL high | 5    |     | ns   |

| 3   | t <sub>w(XTALL)</sub> Pulse duration, XTAL low  | 5    |     | ns   |

#### **HDLC INTERFACE**

switching characteristics over recommended ranges of supply voltage and operating free-air temperature

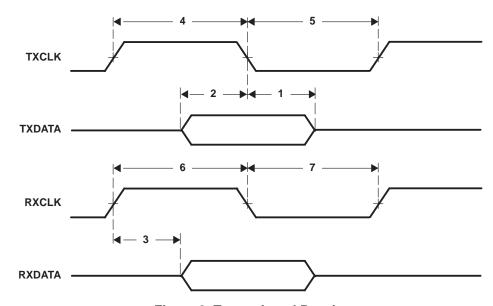

## transmit and receive (see Figure 9)

| NO. | PARAMETER                                        | MIN | MAX | UNIT |

|-----|--------------------------------------------------|-----|-----|------|

| 1   | t <sub>h</sub> Hold time, TXDATA after TXCLK↓    | 0   |     | ns   |

| 2   | t <sub>SU</sub> Setup time, TXDATA before TXCLK↓ | 15  |     | ns   |

| 3   | t <sub>d</sub> Delay time, RXDATA after RXCLK    |     | 0   | ns   |

| 4   | t <sub>W</sub> Pulse duration, TXCLK high        | 75  |     | ns   |

| 5   | t <sub>W</sub> Pulse duration, TXCLK low         | 75  |     | ns   |

| 6   | t <sub>W</sub> Pulse duration, RXCLK high        | 100 |     | ns   |

| 7   | t <sub>W</sub> Pulse duration, RXCLK low         | 50  |     | ns   |

Figure 9. Transmit and Receive

#### **CAPTURE RAM INTERFACE**

switching characteristics over recommended ranges of supply voltage and operating free-air temperature

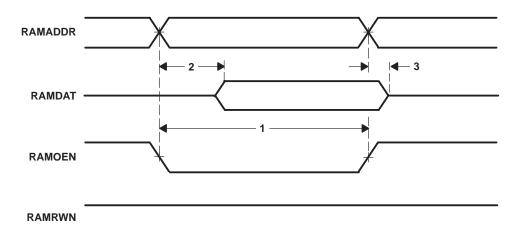

## read cycle (see Figure 10)

| NO. | PARAMETER                                  | MIN | MAX | UNIT |

|-----|--------------------------------------------|-----|-----|------|

| 1   | t <sub>a</sub> Read access time            | 45  |     | ns   |

| 2   | t <sub>d</sub> Data delay time from RAMOEN |     | 30  | ns   |

| 3   | t <sub>h</sub> Data hold time after RAMOEN | 0   |     | ns   |

Figure 10. Read Cycle

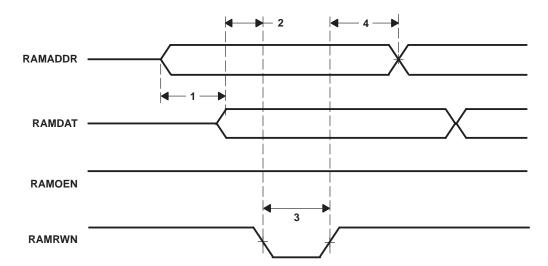

## write cycle (see Figure 11)

| NO. |                       | PARAMETER                               |    |  |    |  |

|-----|-----------------------|-----------------------------------------|----|--|----|--|

| 1   | t <sub>su(ADDR)</sub> | Address setup time                      | 70 |  | ns |  |

| 2   | t <sub>su(DATA)</sub> | Data setup time to RAMRWN               | 12 |  | ns |  |

| 3   | t <sub>W</sub>        | Pulse width, RAMRWN low                 | 22 |  | ns |  |

| 4   | th                    | Data and address hold time after RAMRWN | 30 |  | ns |  |

Figure 11. Write Cycle

#### **MECHANICAL DATA**

#### PPB (S-PQFP-G208)

#### PLASTIC QUAD FLATPACK (DIE-DOWN)

NOTES: A. All linear dimensions are in millimeters.

- B. This drawing is subject to change without notice.

- C. Thermally enhanced molded plastic package with a heat slug (HSL)

- D. Falls within JEDEC MO-143

ti.com 24-Jun-2005

#### **PACKAGING INFORMATION**

| Orderable Device | Status <sup>(1)</sup> | Package<br>Type | Package<br>Drawing | Pins Package<br>Qty | Eco Plan <sup>(2)</sup> | Lead/Ball Finish | MSL Peak Temp <sup>(3)</sup> |

|------------------|-----------------------|-----------------|--------------------|---------------------|-------------------------|------------------|------------------------------|

| TNETEL1200PPB    | OBSOLETE              | HQFP            | PPB                | 208                 | TBD                     | Call TI          | Call TI                      |

<sup>(1)</sup> The marketing status values are defined as follows:

ACTIVE: Product device recommended for new designs.

LIFEBUY: TI has announced that the device will be discontinued, and a lifetime-buy period is in effect.

**NRND:** Not recommended for new designs. Device is in production to support existing customers, but TI does not recommend using this part in a new design.

PREVIEW: Device has been announced but is not in production. Samples may or may not be available.

**OBSOLETE:** TI has discontinued the production of the device.

(2) Eco Plan - The planned eco-friendly classification: Pb-Free (RoHS) or Green (RoHS & no Sb/Br) - please check http://www.ti.com/productcontent for the latest availability information and additional product content details.

TBD: The Pb-Free/Green conversion plan has not been defined.

**Pb-Free** (RoHS): TI's terms "Lead-Free" or "Pb-Free" mean semiconductor products that are compatible with the current RoHS requirements for all 6 substances, including the requirement that lead not exceed 0.1% by weight in homogeneous materials. Where designed to be soldered at high temperatures, TI Pb-Free products are suitable for use in specified lead-free processes.

Green (RoHS & no Sb/Br): TI defines "Green" to mean Pb-Free (RoHS compatible), and free of Bromine (Br) and Antimony (Sb) based flame retardants (Br or Sb do not exceed 0.1% by weight in homogeneous material)

(3) MSL, Peak Temp. -- The Moisture Sensitivity Level rating according to the JEDEC industry standard classifications, and peak solder temperature.

Important Information and Disclaimer: The information provided on this page represents TI's knowledge and belief as of the date that it is provided. TI bases its knowledge and belief on information provided by third parties, and makes no representation or warranty as to the accuracy of such information. Efforts are underway to better integrate information from third parties. TI has taken and continues to take reasonable steps to provide representative and accurate information but may not have conducted destructive testing or chemical analysis on incoming materials and chemicals. TI and TI suppliers consider certain information to be proprietary, and thus CAS numbers and other limited information may not be available for release.

In no event shall TI's liability arising out of such information exceed the total purchase price of the TI part(s) at issue in this document sold by TI to Customer on an annual basis.

#### **IMPORTANT NOTICE**

Texas Instruments Incorporated and its subsidiaries (TI) reserve the right to make corrections, modifications, enhancements, improvements, and other changes to its products and services at any time and to discontinue any product or service without notice. Customers should obtain the latest relevant information before placing orders and should verify that such information is current and complete. All products are sold subject to TI's terms and conditions of sale supplied at the time of order acknowledgment.

TI warrants performance of its hardware products to the specifications applicable at the time of sale in accordance with TI's standard warranty. Testing and other quality control techniques are used to the extent TI deems necessary to support this warranty. Except where mandated by government requirements, testing of all parameters of each product is not necessarily performed.

TI assumes no liability for applications assistance or customer product design. Customers are responsible for their products and applications using TI components. To minimize the risks associated with customer products and applications, customers should provide adequate design and operating safeguards.

TI does not warrant or represent that any license, either express or implied, is granted under any TI patent right, copyright, mask work right, or other TI intellectual property right relating to any combination, machine, or process in which TI products or services are used. Information published by TI regarding third-party products or services does not constitute a license from TI to use such products or services or a warranty or endorsement thereof. Use of such information may require a license from a third party under the patents or other intellectual property of the third party, or a license from TI under the patents or other intellectual property of TI.

Reproduction of information in TI data books or data sheets is permissible only if reproduction is without alteration and is accompanied by all associated warranties, conditions, limitations, and notices. Reproduction of this information with alteration is an unfair and deceptive business practice. TI is not responsible or liable for such altered documentation.

Resale of TI products or services with statements different from or beyond the parameters stated by TI for that product or service voids all express and any implied warranties for the associated TI product or service and is an unfair and deceptive business practice. TI is not responsible or liable for any such statements.

Following are URLs where you can obtain information on other Texas Instruments products and application solutions:

| Products         |                        | Applications       |                           |

|------------------|------------------------|--------------------|---------------------------|

| Amplifiers       | amplifier.ti.com       | Audio              | www.ti.com/audio          |

| Data Converters  | dataconverter.ti.com   | Automotive         | www.ti.com/automotive     |

| DSP              | dsp.ti.com             | Broadband          | www.ti.com/broadband      |

| Interface        | interface.ti.com       | Digital Control    | www.ti.com/digitalcontrol |

| Logic            | logic.ti.com           | Military           | www.ti.com/military       |

| Power Mgmt       | power.ti.com           | Optical Networking | www.ti.com/opticalnetwork |

| Microcontrollers | microcontroller.ti.com | Security           | www.ti.com/security       |

|                  |                        | Telephony          | www.ti.com/telephony      |

|                  |                        | Video & Imaging    | www.ti.com/video          |

|                  |                        | Wireless           | www.ti.com/wireless       |

Mailing Address: Texas Instruments

Post Office Box 655303 Dallas, Texas 75265

Copyright © 2005, Texas Instruments Incorporated