## LMH6672 Dual, High Output Current, High Speed Op Amp

### 1 Features

- **High Output Drive**

- 19.2 V<sub>PP</sub> Differential Output Voltage,  $R_L = 50 \Omega$

- 9.6 V<sub>PP</sub> Single-ended Output Voltage,  $R_L = 25 \Omega$

- **High Output Current**

- $\pm 200 \text{ mA}$  @  $V_O = 9 \text{ V}_{PP}$ ,  $V_S = 12 \text{ V}$

- **Low Distortion**

- 105 dB SFDR @ 100 kHz,  $V_O = 8.4 \text{ V}_{PP}$ ,  $R_L = 25 \Omega$

- 98 dB SFDR @ 1MHz,  $V_O = 2 \text{ V}_{PP}$ ,  $R_L = 100 \Omega$

- **High Speed**

- 90 MHz 3 dB Bandwidth ( $G = 2$ )

- 135 V/ $\mu\text{s}$  Slew Rate

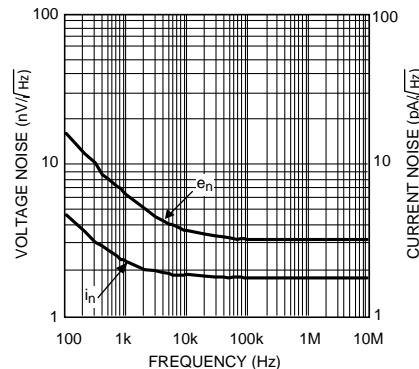

- **Low Noise**

- 3.1 nV/ $\sqrt{\text{Hz}}$ : Input Noise Voltage

- 1.8 pA/ $\sqrt{\text{Hz}}$ : Input Noise Current

- Low Supply Current: 7.2mA/amp

- Single-supply Operation: 5 V to 12 V

- Stable for Gain of +2V/V or Higher

- Available in 8-pin SOIC and SO PowerPAD (DDA)

### 2 Applications

- ADSL PCI Modem Cards

- xDSL External Modems

- Line Drivers

### 3 Description

The LMH6672 is a low cost, dual high speed op amp capable of driving signals to within 1 V of the power supply rails. It features the high output drive with low distortion required for the demanding application of a single supply xDSL line driver.

When connected as a differential output driver, the LMH6672 can drive a 50- $\Omega$  load to 16.8 V<sub>PP</sub> swing with only -98 dBc distortion, fully supporting the peak upstream power levels for upstream full-rate ADSL. The LMH6672 is fully specified for operation with 5-V and 12-V supplies. Ideal for PCI modem cards and xDSL modems.

### Device Information<sup>(1)</sup>

| PART NUMBER | PACKAGE  | BODY SIZE (NOM)   |

|-------------|----------|-------------------|

| LMH6672     | SOIC (8) | 4.89 mm x 3.90 mm |

(1) For all available packages, see the orderable addendum at the end of the datasheet.

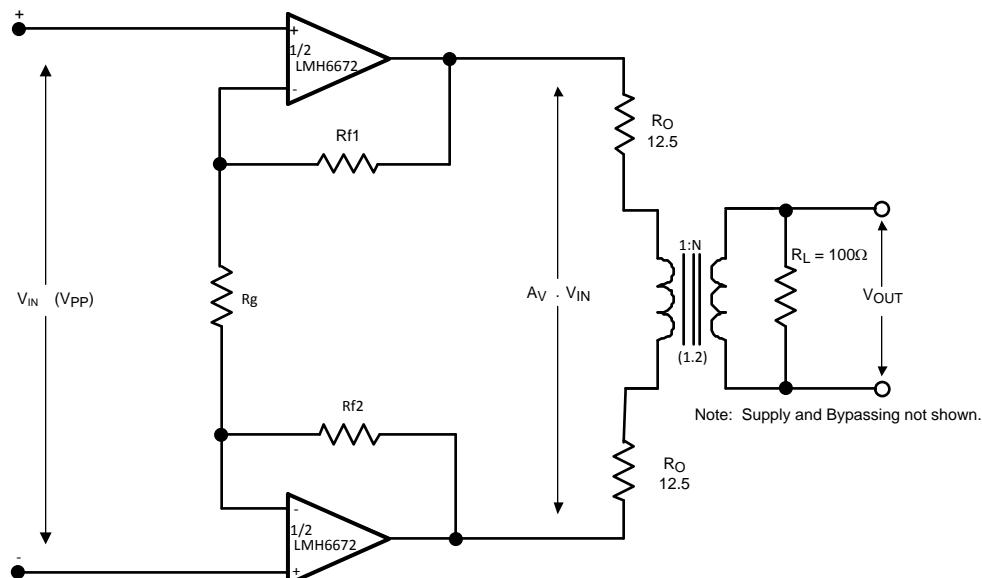

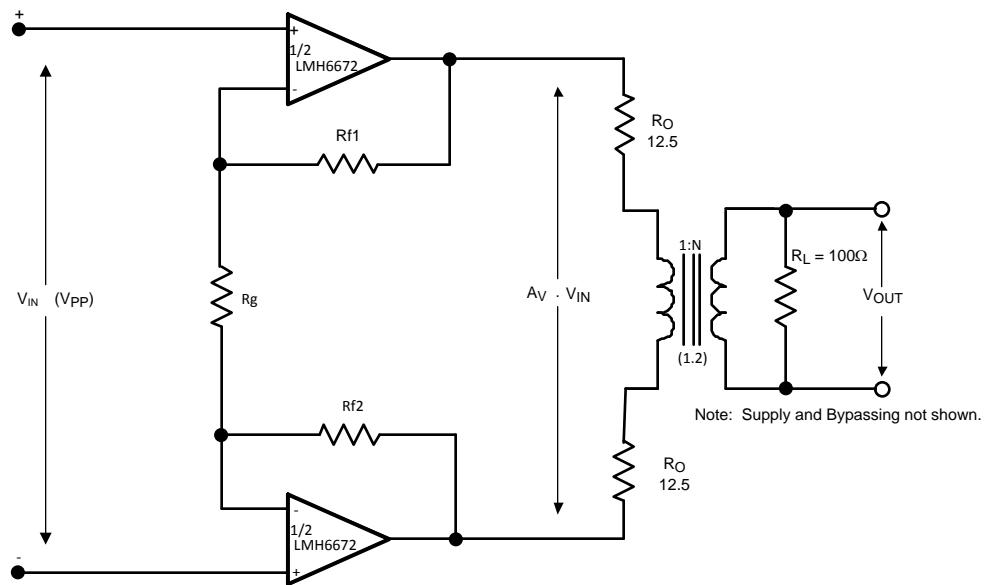

### Typical Application

An IMPORTANT NOTICE at the end of this data sheet addresses availability, warranty, changes, use in safety-critical applications, intellectual property matters and other important disclaimers. PRODUCTION DATA.

## Table of Contents

|                                                |   |                                                                  |    |

|------------------------------------------------|---|------------------------------------------------------------------|----|

| <b>1 Features</b> .....                        | 1 | 6.6 $\pm 2.5V$ Electrical Characteristics .....                  | 6  |

| <b>2 Applications</b> .....                    | 1 | 6.7 Typical Performance Characteristics .....                    | 7  |

| <b>3 Description</b> .....                     | 1 | <b>7 Detailed Description</b> .....                              | 15 |

| <b>4 Revision History</b> .....                | 2 | 7.1 Functional Block Diagram .....                               | 15 |

| <b>5 Pin Configuration and Functions</b> ..... | 3 | <b>8 Power Supply Recommendations</b> .....                      | 16 |

| <b>6 Specifications</b> .....                  | 4 | 8.1 Thermal Management .....                                     | 16 |

| 6.1 Absolute Maximum Ratings .....             | 4 | <b>9 Device and Documentation Support</b> .....                  | 18 |

| 6.2 Handling Ratings .....                     | 4 | 9.1 Trademarks .....                                             | 18 |

| 6.3 Recommended Operating Conditions .....     | 4 | 9.2 Electrostatic Discharge Caution .....                        | 18 |

| 6.4 Thermal Information .....                  | 4 | 9.3 Glossary .....                                               | 18 |

| 6.5 Electrical Characteristics .....           | 5 | <b>10 Mechanical, Packaging, and Orderable Information</b> ..... | 18 |

## 4 Revision History

NOTE: Page numbers for previous revisions may differ from page numbers in the current version.

| Changes from Revision G (March 2013) to Revision H                                                                                                                                                                                                     | Page |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| • Changed data sheet flow and layout to conform with new TI standards. Added the following sections: Device Information Table, Application and Implementation; Device and Documentation Support; Mechanical, Packaging, and Ordering Information ..... | 1    |

| • Added "Stable for Gain of +2V/V or Higher" in <a href="#">Features</a> .....                                                                                                                                                                         | 1    |

| • Changed from "Junction Temperature Range" to "Operating Temperature Range" in <a href="#">Recommended Operating Conditions</a> .....                                                                                                                 | 4    |

| • Deleted $T_J = 25^\circ\text{C}$ in <a href="#">Electrical Characteristics</a> .....                                                                                                                                                                 | 5    |

| • Deleted $T_J = 25^\circ\text{C}$ and "Slew Rate" in <a href="#">±2.5V Electrical Characteristics</a> .....                                                                                                                                           | 6    |

| • Added condition "Av = + 2V/V" in <a href="#">Typical Performance Characteristics</a> .....                                                                                                                                                           | 7    |

| • Added "Vs= +/-2.5V" and "Vs=+/-6V" as curve labels for <a href="#">Figure 36</a> .....                                                                                                                                                               | 11   |

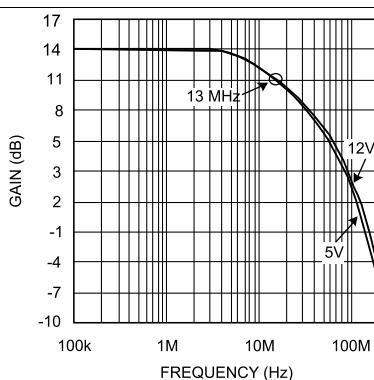

| • Changed curve label from 31 MHz to 13 MHz. Changed title from +5V to +5V/V in <a href="#">Figure 37</a> .....                                                                                                                                        | 12   |

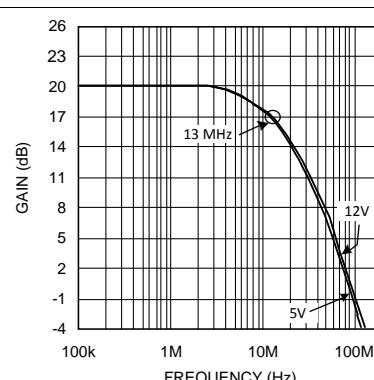

| • Changed "10V" to + "10V/V" in caption title for <a href="#">Figure 38</a> .....                                                                                                                                                                      | 12   |

| • Added "Vs = 12V" to <a href="#">Figure 39</a> caption title .....                                                                                                                                                                                    | 13   |

| • Added "Vs = 5V" to <a href="#">Figure 40</a> caption title .....                                                                                                                                                                                     | 13   |

| • Changed from "40 = 346 mW" to "40 mW lower or 346 mW" in <a href="#">Thermal Management</a> .....                                                                                                                                                    | 17   |

| • Changed from 41 mW to 17 mW .....                                                                                                                                                                                                                    | 17   |

| • Added "from ambient" .....                                                                                                                                                                                                                           | 17   |

| • Changed sentence beginning with "Using the same $P_{\text{DRIVER}}$ as above..." .....                                                                                                                                                               | 17   |

| • Added caution note .....                                                                                                                                                                                                                             | 17   |

| Changes from Revision F (March 2013) to Revision G         | Page |

|------------------------------------------------------------|------|

| • Changed layout of National Data Sheet to TI format ..... | 17   |

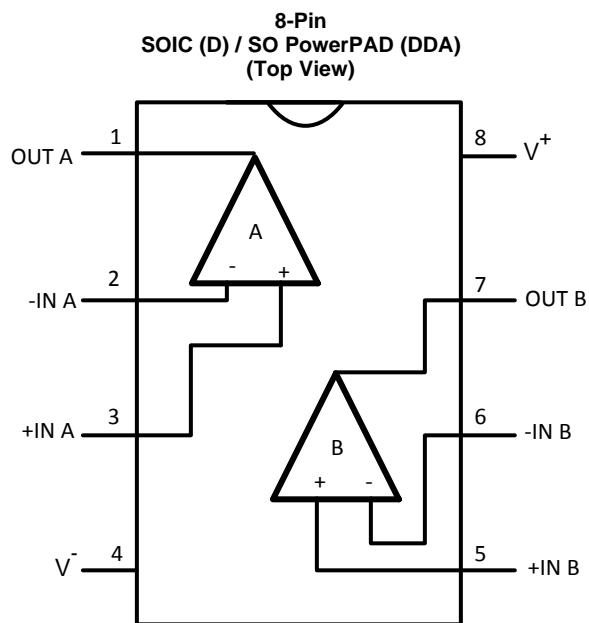

## 5 Pin Configuration and Functions

### Pin Functions

| PIN    |                | I/O | DESCRIPTION             |

|--------|----------------|-----|-------------------------|

| NUMBER | NAME           |     |                         |

| 1      | OUT A          | O   | ChA Output              |

| 2      | -IN A          | I   | ChA Inverting Input     |

| 3      | +IN A          | I   | ChA Non-inverting Input |

| 4      | V <sup>-</sup> | I   | Negative Supply         |

| 5      | +IN B          | I   | ChB Non-inverting Input |

| 6      | -IN B          | I   | ChB Inverting Input     |

| 7      | OUT B          | O   | ChB Output              |

| 8      | V <sup>+</sup> | I   | Positive Supply         |

## 6 Specifications

### 6.1 Absolute Maximum Ratings<sup>(1)</sup>

over operating free-air temperature range (unless otherwise noted)

|                                                   |                                 | MIN                                        | MAX                 | UNIT |

|---------------------------------------------------|---------------------------------|--------------------------------------------|---------------------|------|

| V <sub>IN</sub> Differential                      |                                 |                                            | ±1.2                | V    |

| Output Short Circuit Duration                     |                                 | See <sup>(2)</sup>                         |                     |      |

| Supply Voltage (V <sup>+</sup> – V <sup>-</sup> ) |                                 |                                            | 13.2                | V    |

| Voltage at Input/Output pins                      |                                 | V <sup>+</sup> +0.8<br>V <sup>-</sup> –0.8 |                     | V    |

| Junction Temperature                              |                                 |                                            | +150 <sup>(3)</sup> | °C   |

| Soldering Information                             | Infrared or Convection (20 sec) |                                            | 235                 | °C   |

|                                                   | Wave Soldering (10 sec)         |                                            | 260                 | °C   |

(1) Stresses beyond those listed under *Absolute Maximum Ratings* may cause permanent damage to the device. These are stress ratings only, which do not imply functional operation of the device at these or any other conditions beyond those indicated under *Recommended Operating Conditions*. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

(2) Shorting the output to either supply or ground will exceed the absolute maximum T<sub>J</sub> and can result in failure.

(3) The maximum power dissipation is a function of T<sub>J(MAX)</sub>, R<sub>θJA</sub> and T<sub>A</sub>. The maximum allowable power dissipation at any ambient temperature is P<sub>D</sub> = (T<sub>J(MAX)</sub> – T<sub>A</sub>)/R<sub>θJA</sub>. All numbers apply for packages soldered directly onto a PC board.

### 6.2 Handling Ratings

|                    |                                        | MIN                                                                         | MAX  | UNIT |

|--------------------|----------------------------------------|-----------------------------------------------------------------------------|------|------|

| T <sub>stg</sub>   | Storage temperature range              | –65                                                                         | +150 | °C   |

| V <sub>(ESD)</sub> | Electrostatic discharge <sup>(1)</sup> | Human body model (HBM), per ANSI/ESDA/JEDEC JS-001, all pins <sup>(2)</sup> | 2    | 2000 |

|                    |                                        | Machine Model (MM) <sup>(3)</sup>                                           | 200  | V    |

(1) Human body model, 1.5 kΩ in series with 100 pF. Machine model, 200 Ω in series with 100 pF.

(2) JEDEC document JEP155 states that 2000-V HBM allows safe manufacturing with a standard ESD control process.

(3) JEDEC document JEP157 states that 200-V MM allows safe manufacturing with a standard ESD control process.

### 6.3 Recommended Operating Conditions

over operating free-air temperature range (unless otherwise noted)

|                                                   |  | MIN  | MAX  | UNIT |

|---------------------------------------------------|--|------|------|------|

| Supply Voltage (V <sup>+</sup> - V <sup>-</sup> ) |  | ±2.5 | ±6.5 | V    |

| Operating Temperature Range                       |  | –40  | 150  | °C   |

### 6.4 Thermal Information

| THERMAL METRIC <sup>(1)</sup>                           | SOIC<br>Package D | SO PowerPAD<br>Package DDA | UNIT |

|---------------------------------------------------------|-------------------|----------------------------|------|

|                                                         | 8 PINS            | 8 PINS                     |      |

| R <sub>θJA</sub> Junction-to-ambient thermal resistance | 172               | 58.6                       | °C/W |

(1) For more information about traditional and new thermal metrics, see the *IC Package Thermal Metrics* application report, [SPRA953](#).

## 6.5 Electrical Characteristics

Unless otherwise specified, all limits are ensured for  $G = +2$ ,  $V_S = \pm 2.5$  to  $\pm 6V$ ,  $R_F = R_{IN} = 470\Omega$ ,  $R_L = 100\Omega$ .

| PARAMETER                            | TEST CONDITIONS                                      | MIN <sup>(1)</sup>                                                                    | TYP <sup>(2)</sup> | MAX <sup>(1)</sup> | UNIT                   |

|--------------------------------------|------------------------------------------------------|---------------------------------------------------------------------------------------|--------------------|--------------------|------------------------|

| <b>DYNAMIC PERFORMANCE</b>           |                                                      |                                                                                       |                    |                    |                        |

| –3dB Bandwidth                       |                                                      | 90                                                                                    |                    |                    | MHz                    |

| 0.1dB Bandwidth                      | $V_S = \pm 6V$                                       | 12                                                                                    |                    |                    | MHz                    |

| Slew Rate                            | $V_S = \pm 6V$ , 4V Step, 10-90%                     | 135                                                                                   |                    |                    | V/ $\mu$ s             |

| Rise and Fall Time                   | $V_S = 6V$ , 4V Step, 10-90%                         | 23.5                                                                                  |                    |                    | ns                     |

| <b>DISTORTION and NOISE RESPONSE</b> |                                                      |                                                                                       |                    |                    |                        |

| 2 <sup>nd</sup> Harmonic Distortion  | $V_O = 8.4 V_{PP}$ , $f = 100$ kHz, $R_L = 25\Omega$ | –105                                                                                  |                    |                    | dBc                    |

|                                      | $V_O = 8.4 V_{PP}$ , $f = 1$ MHz, $R_L = 100\Omega$  | –90                                                                                   |                    |                    | dBc                    |

| 3 <sup>rd</sup> Harmonic Distortion  | $V_O = 8.4 V_{PP}$ , $f = 100$ kHz, $R_L = 25\Omega$ | –110                                                                                  |                    |                    | dBc                    |

|                                      | $V_O = 8.4 V_{PP}$ , $f = 1$ MHz, $R_L = 100\Omega$  | –87                                                                                   |                    |                    | dBc                    |

| Input Noise Voltage                  | $f = 100$ kHz                                        | 3.1                                                                                   |                    |                    | nV/ $\sqrt{\text{Hz}}$ |

| Input Noise Current                  | $f = 100$ kHz                                        | 1.8                                                                                   |                    |                    | pA/ $\sqrt{\text{Hz}}$ |

| <b>INPUT CHARACTERISTICS</b>         |                                                      |                                                                                       |                    |                    |                        |

| $V_{OS}$                             | Input Offset Voltage                                 | $T_J = -40^\circ\text{C}$ to $125^\circ\text{C}$                                      | –5.5               | 0.1                | 5.5                    |

|                                      |                                                      |                                                                                       | –4                 | –0.2               | 4                      |

| $I_B$                                | Input Bias Current                                   | $T_J = -40^\circ\text{C}$ to $125^\circ\text{C}$                                      | 8                  | 16                 | $\mu\text{A}$          |

| $I_{OS}$                             | Input Offset Current                                 | $T_J = -40^\circ\text{C}$ to $125^\circ\text{C}$                                      | –2.1               | 0                  | 2.1                    |

| CMVR                                 | Common Voltage Range                                 | $V_S = \pm 6V$                                                                        | –6.0               | –5.7 to 4.5        | 4.5                    |

| CMRR                                 | Common-Mode Rejection Ratio                          | $V_S = \pm 6V$ , $T_J = -40^\circ\text{C}$ to $125^\circ\text{C}$                     | 150                | 7.5                | $\mu\text{V/V}$        |

| <b>TRANSFER CHARACTERISTICS</b>      |                                                      |                                                                                       |                    |                    |                        |

| $A_{VOL}$                            | Voltage Gain                                         | $R_L = 1\text{k}$ , $T_J = -40^\circ\text{C}$ to $125^\circ\text{C}$                  | 1.0                | 5                  | $\text{V/mV}$          |

|                                      |                                                      | $R_L = 25\Omega$ , $T_J = -40^\circ\text{C}$ to $125^\circ\text{C}$                   | 0.67               | 3.4                | $\text{V/mV}$          |

| $V_O$                                | Output Swing                                         | $R_L = 25\Omega$ , $V_S = \pm 6V$                                                     | –4.5               | ±4.8               | 4.5                    |

|                                      |                                                      | $R_L = 25\Omega$ , $T_J = -40^\circ\text{C}$ to $125^\circ\text{C}$ , $V_S = \pm 6V$  | –4.4               | ±4.8               | 4.4                    |

| $V_O$                                | Output Swing                                         | $R_L = 1\text{k}$ , $V_S = \pm 6V$                                                    | –4.8               | ±4.8               | 4.8                    |

|                                      |                                                      | $R_L = 1\text{k}$ , $T_J = -40^\circ\text{C}$ to $125^\circ\text{C}$ , $V_S = \pm 6V$ | –4.7               | ±4.8               | 4.7                    |

| $I_{SC}$                             | Output Current <sup>(3)</sup>                        | $V_O = 0$ , $V_S = \pm 6V$                                                            | 350                | 525                | $\text{mA}$            |

|                                      |                                                      | $V_O = 0$ , $V_S = \pm 6V$ , $T_J = -40^\circ\text{C}$ to $125^\circ\text{C}$         | 260                | 600                | $\text{mA}$            |

| <b>POWER SUPPLY</b>                  |                                                      |                                                                                       |                    |                    |                        |

| $I_S$                                | Supply Current/Amp                                   | $V_S = \pm 6V$                                                                        |                    | 8                  | $\text{mA}$            |

|                                      |                                                      | $V_S = \pm 6V$ , $T_J = -40^\circ\text{C}$ to $125^\circ\text{C}$                     | 7.2                | 9                  |                        |

| PSRR                                 | Power Supply Rejection Ratio                         | $V_S = \pm 2.5V$ to $\pm 6V$ , $T_J = -40^\circ\text{C}$ to $125^\circ\text{C}$       | 72                 | 88.5               | $\text{dB}$            |

(1) All limits are specified by testing, characterization or statistical analysis.

(2) Typical values represent the most likely parametric norm.

(3) Shorting the output to either supply or ground will exceed the absolute maximum  $T_J$  and can result in failure.

## 6.6 $\pm 2.5V$ Electrical Characteristics

Unless otherwise specified, all limits are ensured for  $G = +2$ ,  $V_S = \pm 2.5$  to  $\pm 6V$ ,  $R_F = R_{IN} = 470\Omega$ ,  $R_L = 100\Omega$ .

| PARAMETER                            | TEST CONDITIONS                                                                     | MIN <sup>(1)</sup> | TYP <sup>(2)</sup> | MAX <sup>(1)</sup> | UNIT            |

|--------------------------------------|-------------------------------------------------------------------------------------|--------------------|--------------------|--------------------|-----------------|

| <b>DYNAMIC PERFORMANCE</b>           |                                                                                     |                    |                    |                    |                 |

| –3 dB Bandwidth                      |                                                                                     | 80                 |                    |                    | MHz             |

| 0.1 dB Bandwidth                     |                                                                                     | 12                 |                    |                    | MHz             |

| Rise and Fall Time                   | 2V Step, 10-90%                                                                     | 14                 |                    |                    | ns              |

| <b>DISTORTION and NOISE RESPONSE</b> |                                                                                     |                    |                    |                    |                 |

| 2 <sup>nd</sup> Harmonic Distortion  | $V_O = 2 V_{PP}$ , $f = 100$ kHz, $R_L = 25\Omega$                                  | –96                |                    |                    | dBc             |

|                                      | $V_O = 2 V_{PP}$ , $f = 1$ MHz, $R_L = 100\Omega$                                   | –85                |                    |                    | dBc             |

| 3 <sup>rd</sup> Harmonic Distortion  | $V_O = 2 V_{PP}$ , $f = 100$ kHz, $R_L = 25\Omega$                                  | –98                |                    |                    | dBc             |

|                                      | $V_O = 2 V_{PP}$ , $f = 1$ MHz, $R_L = 100\Omega$                                   | –87                |                    |                    | dBc             |

| <b>INPUT CHARACTERISTICS</b>         |                                                                                     |                    |                    |                    |                 |

| $V_{OS}$                             | Input Offset Voltage<br>$T_J = -40^\circ\text{C}$ to $125^\circ\text{C}$            | –5.5               |                    | 5.5                | mV              |

|                                      |                                                                                     | –4.0               | 0.02               | 4.0                |                 |

| $I_B$                                | Input Bias Current<br>$T_J = -40^\circ\text{C}$ to $125^\circ\text{C}$              |                    | 8.0                | 16                 | $\mu\text{A}$   |

| CMVR                                 | Common-Mode Voltage Range                                                           | –2.5               |                    | 1.0                | V               |

| CMRR                                 | Common-Mode Rejection Ratio<br>$T_J = -40^\circ\text{C}$ to $125^\circ\text{C}$     | 150                | 8                  |                    | $\mu\text{V/V}$ |

| <b>TRANSFER CHARACTERISTICS</b>      |                                                                                     |                    |                    |                    |                 |

| $A_{VOL}$                            | Voltage Gain<br>$R_L = 25\Omega$ , $T_J = -40^\circ\text{C}$ to $125^\circ\text{C}$ | 0.67               | 3                  |                    | V/mV            |

|                                      |                                                                                     | 1.0                | 4                  |                    |                 |

| <b>OUTPUT CHARACTERISTICS</b>        |                                                                                     |                    |                    |                    |                 |

| $V_O$                                | Output Voltage Swing<br>$R_L = 25\Omega$                                            | 1.20               | 1.45               |                    | V               |

|                                      |                                                                                     | 1.10               | 1.35               |                    |                 |

|                                      |                                                                                     | 1.30               | 1.60               |                    |                 |

|                                      |                                                                                     | 1.25               | 1.50               |                    |                 |

| <b>POWER SUPPLY</b>                  |                                                                                     |                    |                    |                    |                 |

| $I_S$                                | Supply Current/Amp<br>$T_J = -40^\circ\text{C}$ to $125^\circ\text{C}$              |                    |                    | 8.0                | mA              |

|                                      |                                                                                     |                    | 6.7                | 9.0                |                 |

(1) All limits are specified by testing, characterization or statistical analysis.

(2) Typical values represent the most likely parametric norm.

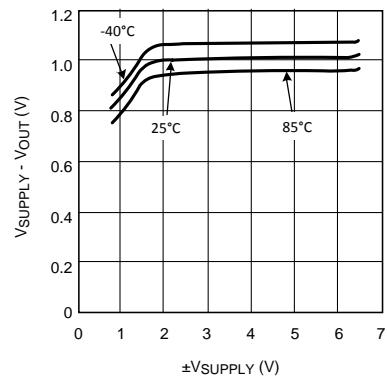

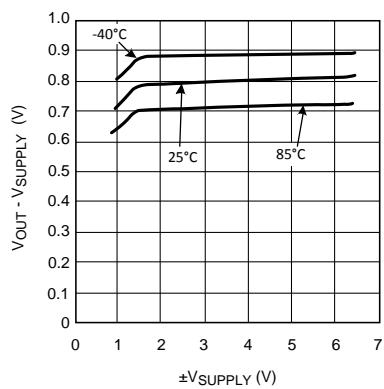

## 6.7 Typical Performance Characteristics

$A_v = +2V/V$

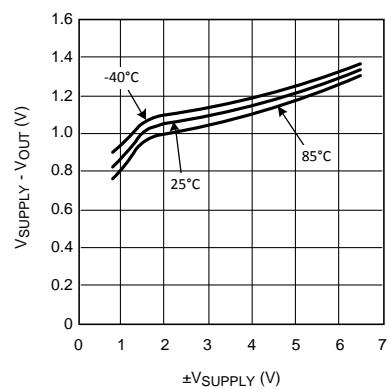

**Figure 1. Output Swing  $R_L = 25\Omega$ ,  $1\text{ k}\Omega$  @  $-40^\circ\text{C}$ ,  $25^\circ\text{C}$ ,  $85^\circ\text{C}$**

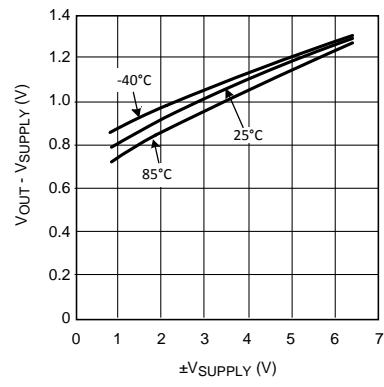

**Figure 2. Positive Output Swing into  $1\text{k}\Omega$**

**Figure 3. Negative Output Swing into  $1\text{k}\Omega$**

**Figure 4. Positive Output Swing into  $25\Omega$**

**Figure 5. Negative Output Swing into  $25\Omega$**

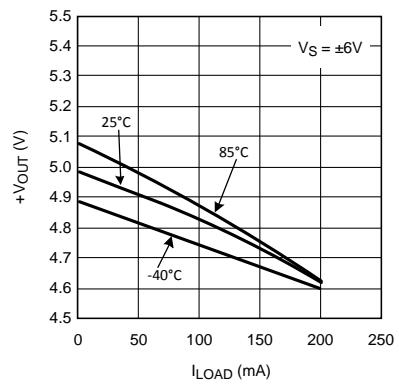

**Figure 6.  $+V_{\text{OUT}}$  vs.  $I_{\text{LOAD}}$**

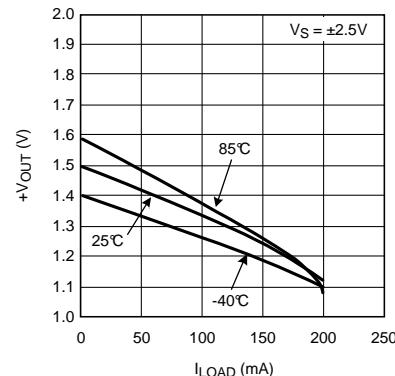

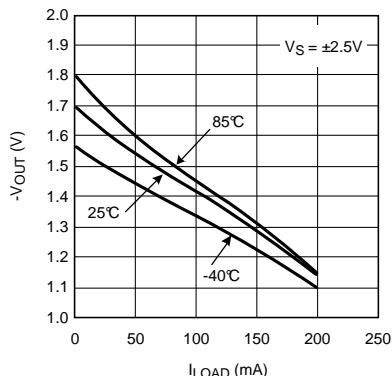

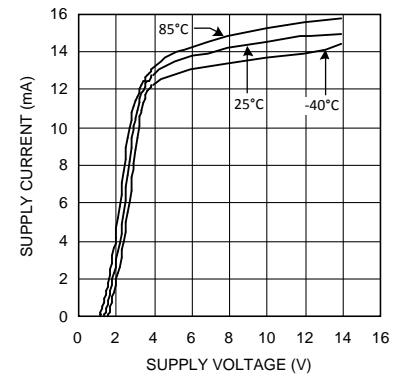

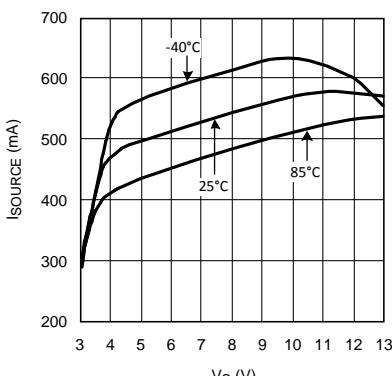

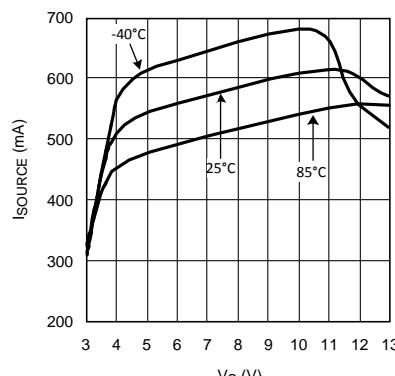

## Typical Performance Characteristics (continued)

$A_v = + 2V/V$

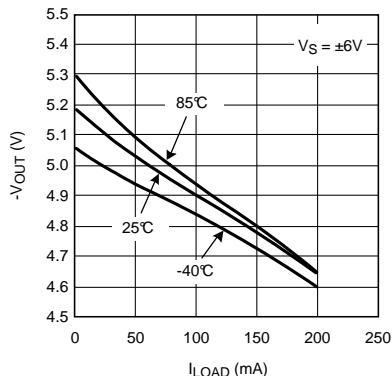

Figure 7.  $-V_{OUT}$  vs.  $I_{LOAD}$

Figure 8.  $+V_{OUT}$  vs.  $I_{LOAD}$

Figure 9.  $-V_{OUT}$  vs.  $I_{LOAD}$

Figure 10. Supply Current vs. Supply Voltage

Figure 11. Sourcing Current vs. Supply Voltage

Figure 12. Sinking Current vs. Supply Voltage

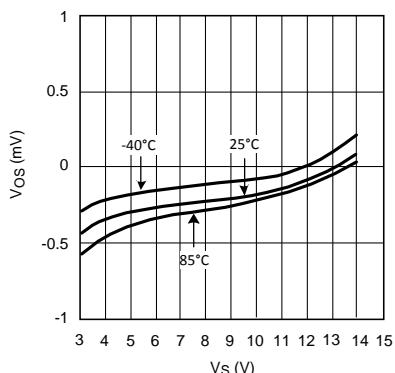

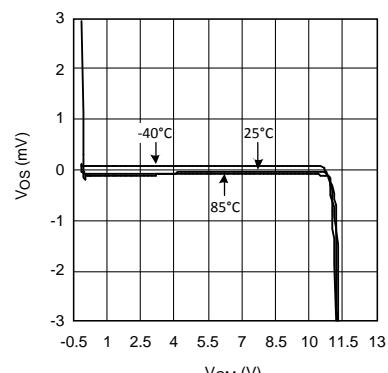

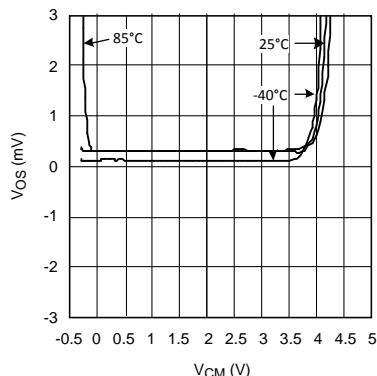

## Typical Performance Characteristics (continued)

$A_v = +2V/V$

Figure 13.  $V_{OS}$  vs.  $V_S$

Figure 14.  $V_{OS}$  vs.  $V_{CM}$ ,  $V_S = 12V$

Figure 15.  $V_{OS}$  vs.  $V_{CM}$ ,  $V_S = 5V$

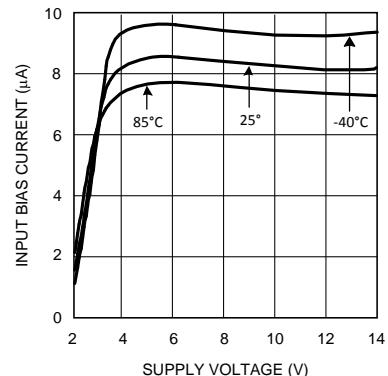

Figure 16. Bias Current vs.  $V_{SUPPLY}$

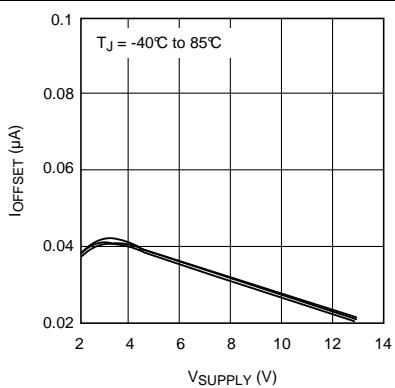

Figure 17. Offset Current vs.  $V_{SUPPLY}$

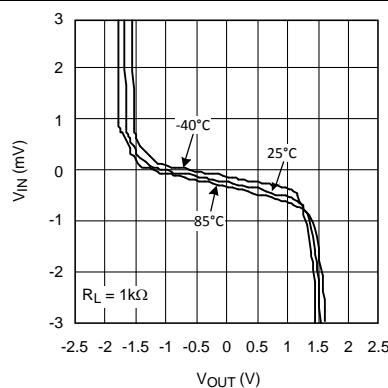

Figure 18.  $V_{OUT}$  vs.  $V_{IN}$

## Typical Performance Characteristics (continued)

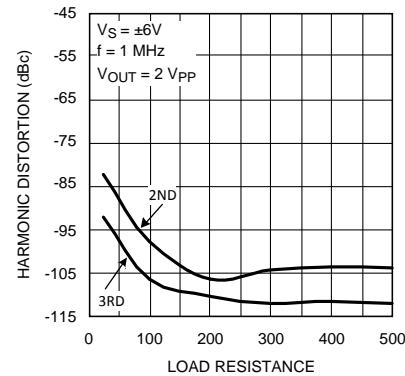

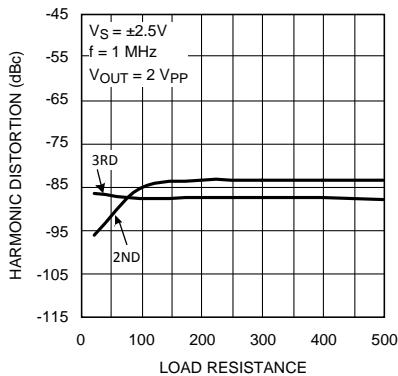

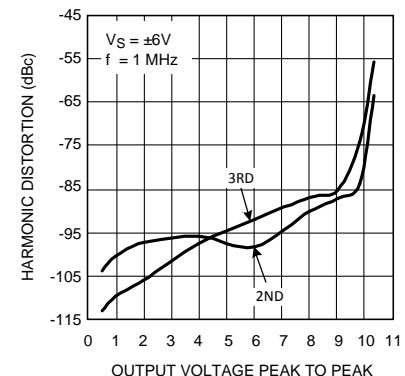

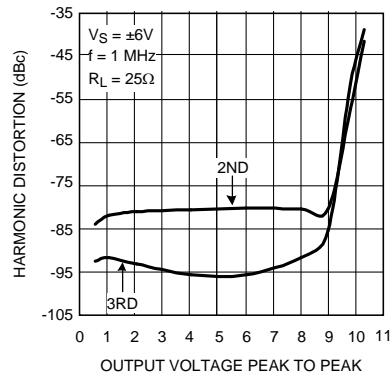

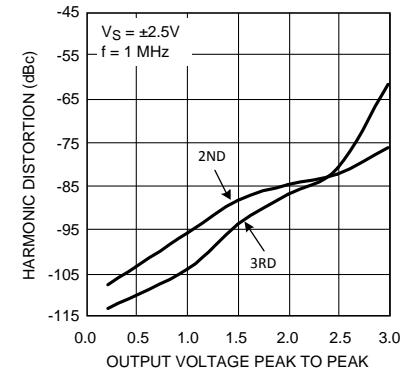

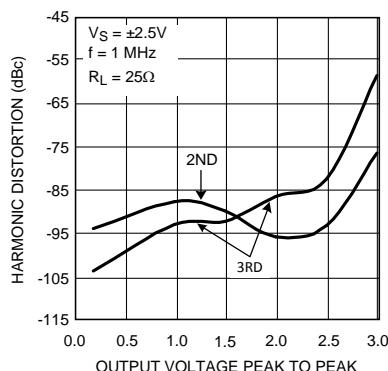

$A_v = +2V/V$

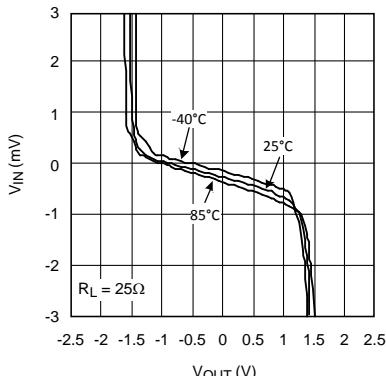

Figure 19.  $V_{OUT}$  vs.  $V_{IN}$

Figure 20. Harmonic Distortion vs. Load

Figure 21. Harmonic Distortion vs. Load

Figure 22. Harmonic Distortion vs. Output Voltage

Figure 23. Harmonic Distortion vs. Output Voltage

Figure 24. Harmonic Distortion vs. Output Voltage

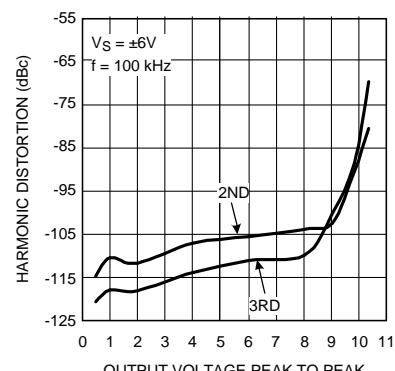

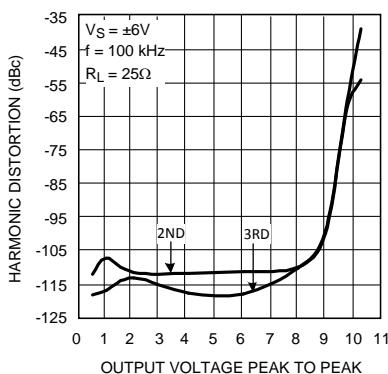

## Typical Performance Characteristics (continued)

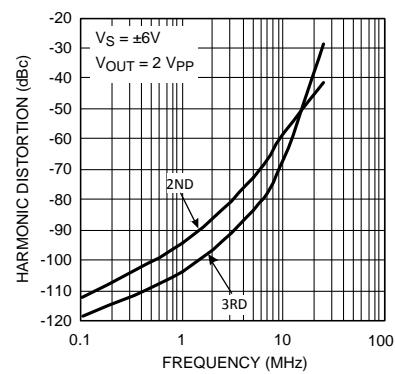

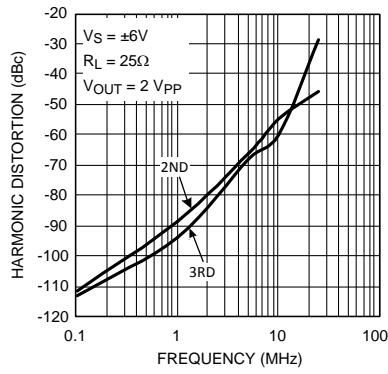

$A_v = +2V/V$

Figure 25. Harmonic Distortion vs. Output Voltage

Figure 26. Harmonic Distortion vs. Output Voltage

Figure 27. Harmonic Distortion vs. Output Voltage

Figure 28. Harmonic Distortion vs. Frequency

Figure 29. Harmonic Distortion vs. Frequency

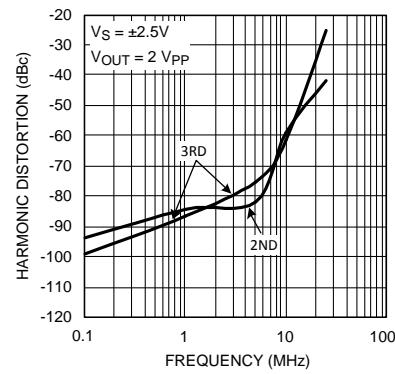

Figure 30. Harmonic Distortion vs. Frequency

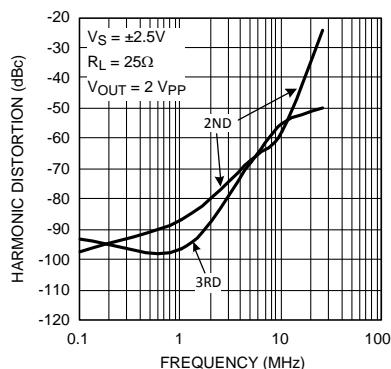

## Typical Performance Characteristics (continued)

$A_v = +2V/V$

Figure 31. Harmonic Distortion vs. Frequency

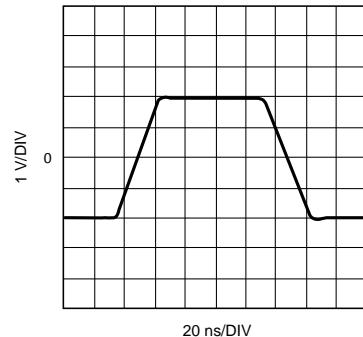

Figure 32. Pulse Response,  $V_S = \pm 6V$

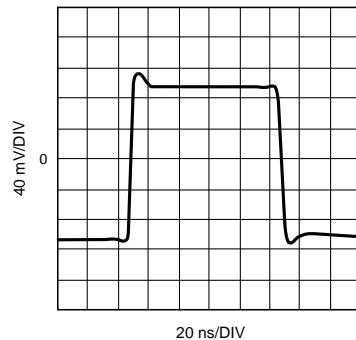

Figure 33. Pulse Response,  $V_S = \pm 2.5V, \pm 6V$

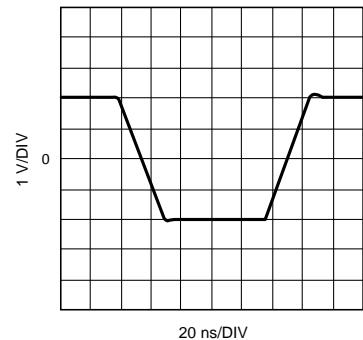

Figure 34. Pulse Response,  $A_{VCL} = -1, V_S = \pm 6V$

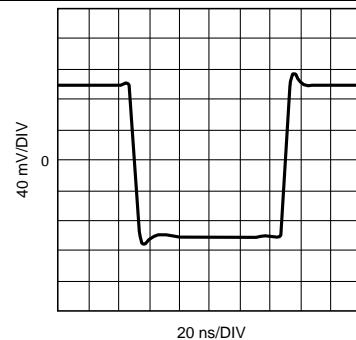

Figure 35. Pulse Response,  $A_{VCL} = -1, V_S = \pm 2.5V, \pm 6V$

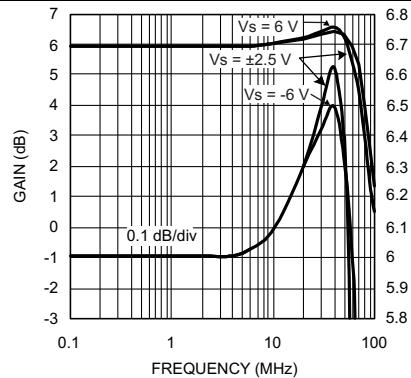

Figure 36. Frequency Response

## Typical Performance Characteristics (continued)

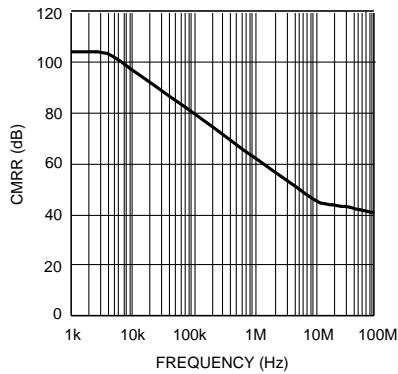

$A_v = +2V/V$

Figure 37. Frequency Response,  $A_{vCL} = +5V/V$

Figure 38. Frequency Response,  $A_{vCL} = +10V/V$

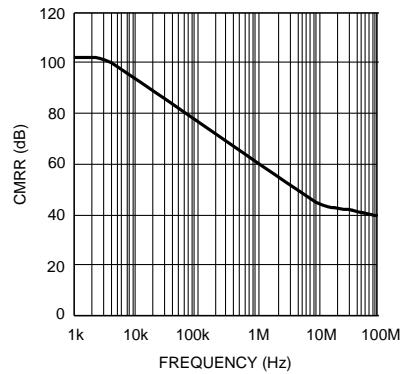

Figure 39. CMRR vs. Frequency,  $V_s = 12V$

Figure 40. CMRR vs. Frequency,  $V_s = 5V$

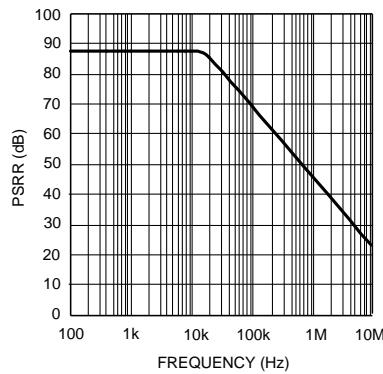

Figure 41. PSRR+ vs. Frequency,  $V_s = 5V$  and  $12V$

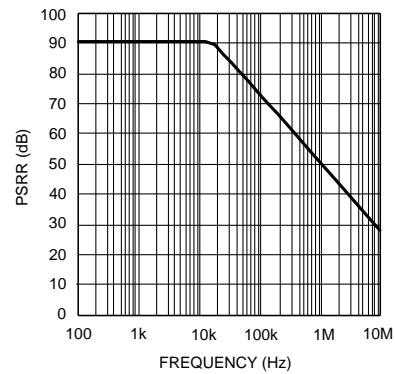

Figure 42. PSRR- vs. Frequency  $V_s = 5V$  and  $12V$

**Typical Performance Characteristics (continued)** $A_v = + 2V/V$ **Figure 43.  $e_n$  &  $i_n$  vs. Frequency,  $V_S = 5V$  and  $12V$**

## 7 Detailed Description

### 7.1 Functional Block Diagram

**Figure 44. LMH6672 Block Diagram**

## 8 Power Supply Recommendations

### 8.1 Thermal Management

The LMH6672 is a high-speed, high power, dual operational amplifier with a very high slew rate and very low distortion. For ease of use, it uses conventional voltage feedback. These characteristics make the LMH6672 ideal for applications where driving low impedances of 25 to 100  $\Omega$  such as xDSL and active filters.

A class AB output stage allows the LMH6672 to deliver high currents to low impedance loads with low distortion while consuming low quiescent supply current. For most op-amps, class AB topology means that internal power dissipation is rarely an issue, even with the trend to smaller surface mount packages. However, the LMH6672 has been designed for applications where high levels of power dissipation may be encountered.

Several factors contribute to power dissipation and consequently higher junction temperatures. These factors need to be well understood if the LMH6672 is to perform to specifications in all applications. This section will examine the typical application shown in [Figure 44](#) as an example. Because both amplifiers are in a single package, the calculations are for the total power dissipated by both amplifiers.

There are two separate contributors to the internal power dissipation:

1. The product of the supply voltage and the quiescent current when no signal is being delivered to the external load.

2. The additional power dissipated while delivering power to the external load.

The first of these components appears easy to calculate simply by inspecting the data sheet. The typical quiescent supply current for this part is 7.2 mA per amplifier. Therefore, with a  $\pm 6$  volt supply, the total power dissipation is:

$$P_D = V_S \times 2 \times I_Q = 12 \times (14.4 \times 10^{-3}) = 173 \text{ mW}$$

where

$$\bullet \quad (V_S = V_{CC} + V_{EE}) \quad (1)$$

With a thermal resistance of  $172^\circ\text{C}/\text{W}$  for the SOIC package, this level of internal power dissipation will result in a junction temperature ( $T_J$ ) of  $30^\circ\text{C}$  above ambient.

Using the worst-case maximum supply current of 18 mA and an ambient of  $85^\circ\text{C}$ , a similar calculation results in a power dissipation of 216 mW, or a  $T_J$  of  $122^\circ\text{C}$ .

This is approaching the maximum allowed  $T_J$  of  $150^\circ\text{C}$  before a signal is applied. Fortunately, in normal operation, this term is reduced, for reasons that will soon be explained.

The second contributor to high  $T_J$  is the power dissipated internally when power is delivered to the external load. This cause of temperature rise is more difficult to calculate, even when the actual operating conditions are known.

To maintain low distortion, in a Class AB output stage, an idle current,  $I_Q$ , is maintained through the output transistors when there is little or no output signal. In the LMH6672, about 4.8 mA of the total quiescent supply current of 14.4 mA flows through the output stages.

Under normal large signal conditions, as the output voltage swings positive, one transistor of the output pair will conduct the load current, while the other transistor shuts off, and dissipates no power. During the negative signal swing this situation is reversed, with the lower transistor sinking the load current while the upper transistor is cut off. The current in each transistor will approximate a half wave rectified version of the total load current.

Because the output stage idle current is now routed into the load, 4.8 mA can be subtracted from the quiescent supply current when calculating the quiescent power when the output is driving a load.

## Thermal Management (continued)

The power dissipation caused by driving a load in a DSL application, using a 1:2 turns ratio transformer driving 20 mW into the subscriber line and 20 mW into the back termination resistors, can be calculated as follows:

$$P_{\text{DRIVER}} = P_{\text{TOT}} - (P_{\text{TERM}} + P_{\text{LINE}})$$

Where

- $P_{\text{DRIVER}}$  is the LMH6672 power dissipation

- $P_{\text{TOT}}$  is the total power drawn from the power supply

- $P_{\text{TERM}}$  is the power dissipated in the back termination resistors

- $P_{\text{LINE}}$  is the power sent into the subscriber line

- At full specified power,  $P_{\text{TERM}} = P_{\text{LINE}} = 20 \text{ mW}$ ,  $P_{\text{TOT}} = V_S \times I_S$  (2)

In this application,  $V_S = 12V$ .

$$I_S = I_Q + A_{VG} |I_{OUT}| \quad (3)$$

$I_Q$  = the LMH6672 quiescent current minus the output stage idle current. (4)

$$I_Q = 14.4 - 4.8 = 9.6 \text{ mA} \quad (5)$$

Average ( $A_{VG}$ )  $|I_{OUT}|$  for a full-rate ADSL CPE application, using a 1:2 turns ratio transformer, is  $\sqrt{40 \text{ mW}/50\Omega} = 28.28 \text{ mA RMS}$ .

For a Gaussian signal, which the DMT ADSL signal approximates,  $A_{VG} |I_{OUT}| = \sqrt{2/\pi} \times I_{RMS} = 22.6 \text{ mA}$ . Therefore,  $P_{\text{TOT}} = (22.6 \text{ mA} + 9.6 \text{ mA}) \times 12V = 386 \text{ mW}$  and  $P_{\text{DRIVER}}$  is 40 mW lower or 346 mW.

In the SOIC package, with a  $\theta_{JA}$  of  $172^{\circ}\text{C/W}$ , this causes a temperature rise of  $60^{\circ}\text{C}$ . With an ambient temperature at the maximum recommended  $85^{\circ}\text{C}$ , the  $T_J$  is at  $145^{\circ}\text{C}$ , which is below the specified  $150^{\circ}\text{C}$  maximum.

Even if it is assumed that the absolute maximum  $I_S$  over temperature of 18 mA, when the  $I_Q$  is scaled up proportionally to 7 mA, the  $P_{\text{DRIVER}}$  only goes up by 17 mW causing a  $62^{\circ}\text{C}$  rise from ambient to  $147^{\circ}\text{C}$ .

Although very few CPE applications will ever operate in an environment as hot as  $85^{\circ}\text{C}$ , if a lower  $T_J$  is desired or the LMH6672 is to be used in an application where the power dissipation is higher, the SO PowerPAD (DDA) package provides a much lower  $R_{\theta JA}$  of only  $58.6^{\circ}\text{C/W}$ . Using the same  $P_{\text{DRIVER}}$  as above, we find that the temperature rise is only about  $21^{\circ}\text{C}$ , resulting in  $T_J$  of  $106^{\circ}\text{C}$  with  $85^{\circ}\text{C}$  ambient.

### NOTE

Since the exposed PAD (or DAP) of the SO PowerPAD (DDA) package is internally floating, the footprint for DAP could be connected to ground plane in PCB for better heat dissipation.

## 9 Device and Documentation Support

### 9.1 Trademarks

All trademarks are the property of their respective owners.

### 9.2 Electrostatic Discharge Caution

These devices have limited built-in ESD protection. The leads should be shorted together or the device placed in conductive foam during storage or handling to prevent electrostatic damage to the MOS gates.

### 9.3 Glossary

[SLYZ022](#) — *TI Glossary*.

This glossary lists and explains terms, acronyms, and definitions.

## 10 Mechanical, Packaging, and Orderable Information

The following pages include mechanical, packaging, and orderable information. This information is the most current data available for the designated devices. This data is subject to change without notice and revision of this document. For browser-based versions of this data sheet, refer to the left-hand navigation.

**PACKAGING INFORMATION**

| Orderable part number | Status<br>(1) | Material type<br>(2) | Package   Pins           | Package qty   Carrier | RoHS<br>(3) | Lead finish/<br>Ball material<br>(4) | MSL rating/<br>Peak reflow<br>(5) | Op temp (°C) | Part marking<br>(6) |

|-----------------------|---------------|----------------------|--------------------------|-----------------------|-------------|--------------------------------------|-----------------------------------|--------------|---------------------|

| LMH6672MA/NOPB        | Active        | Production           | SOIC (D)   8             | 95   TUBE             | Yes         | SN                                   | Level-1-260C-UNLIM                | -40 to 150   | LMH66<br>72MA       |

| LMH6672MA/NOPB.A      | Active        | Production           | SOIC (D)   8             | 95   TUBE             | Yes         | SN                                   | Level-1-260C-UNLIM                | -40 to 150   | LMH66<br>72MA       |

| LMH6672MAX/NOPB       | Active        | Production           | SOIC (D)   8             | 2500   LARGE T&R      | Yes         | SN                                   | Level-1-260C-UNLIM                | -40 to 150   | LMH66<br>72MA       |

| LMH6672MAX/NOPB.A     | Active        | Production           | SOIC (D)   8             | 2500   LARGE T&R      | Yes         | SN                                   | Level-1-260C-UNLIM                | -40 to 150   | LMH66<br>72MA       |

| LMH6672MR/NOPB        | Active        | Production           | SO PowerPAD<br>(DDA)   8 | 95   TUBE             | Yes         | SN                                   | Level-3-260C-168 HR               | -40 to 150   | LMH66<br>72MR       |

| LMH6672MR/NOPB.A      | Active        | Production           | SO PowerPAD<br>(DDA)   8 | 95   TUBE             | Yes         | SN                                   | Level-3-260C-168 HR               | -40 to 150   | LMH66<br>72MR       |

| LMH6672MRX/NOPB       | Active        | Production           | SO PowerPAD<br>(DDA)   8 | 2500   LARGE T&R      | Yes         | SN                                   | Level-3-260C-168 HR               | -40 to 150   | LMH66<br>72MR       |

| LMH6672MRX/NOPB.A     | Active        | Production           | SO PowerPAD<br>(DDA)   8 | 2500   LARGE T&R      | Yes         | SN                                   | Level-3-260C-168 HR               | -40 to 150   | LMH66<br>72MR       |

<sup>(1)</sup> **Status:** For more details on status, see our [product life cycle](#).

<sup>(2)</sup> **Material type:** When designated, preproduction parts are prototypes/experimental devices, and are not yet approved or released for full production. Testing and final process, including without limitation quality assurance, reliability performance testing, and/or process qualification, may not yet be complete, and this item is subject to further changes or possible discontinuation. If available for ordering, purchases will be subject to an additional waiver at checkout, and are intended for early internal evaluation purposes only. These items are sold without warranties of any kind.

<sup>(3)</sup> **RoHS values:** Yes, No, RoHS Exempt. See the [TI RoHS Statement](#) for additional information and value definition.

<sup>(4)</sup> **Lead finish/Ball material:** Parts may have multiple material finish options. Finish options are separated by a vertical ruled line. Lead finish/Ball material values may wrap to two lines if the finish value exceeds the maximum column width.

<sup>(5)</sup> **MSL rating/Peak reflow:** The moisture sensitivity level ratings and peak solder (reflow) temperatures. In the event that a part has multiple moisture sensitivity ratings, only the lowest level per JEDEC standards is shown. Refer to the shipping label for the actual reflow temperature that will be used to mount the part to the printed circuit board.

<sup>(6)</sup> **Part marking:** There may be an additional marking, which relates to the logo, the lot trace code information, or the environmental category of the part.

---

Multiple part markings will be inside parentheses. Only one part marking contained in parentheses and separated by a "~" will appear on a part. If a line is indented then it is a continuation of the previous line and the two combined represent the entire part marking for that device.

**Important Information and Disclaimer:** The information provided on this page represents TI's knowledge and belief as of the date that it is provided. TI bases its knowledge and belief on information provided by third parties, and makes no representation or warranty as to the accuracy of such information. Efforts are underway to better integrate information from third parties. TI has taken and continues to take reasonable steps to provide representative and accurate information but may not have conducted destructive testing or chemical analysis on incoming materials and chemicals. TI and TI suppliers consider certain information to be proprietary, and thus CAS numbers and other limited information may not be available for release.

In no event shall TI's liability arising out of such information exceed the total purchase price of the TI part(s) at issue in this document sold by TI to Customer on an annual basis.

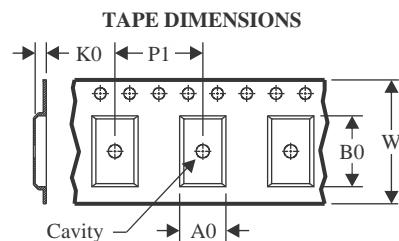

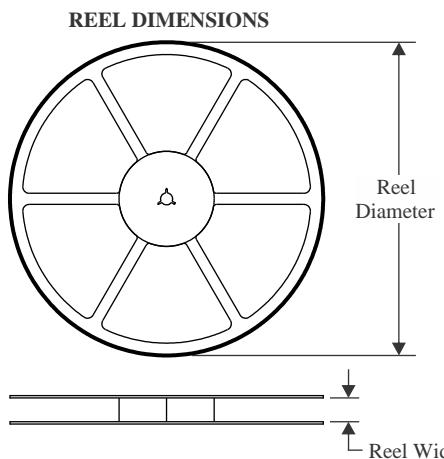

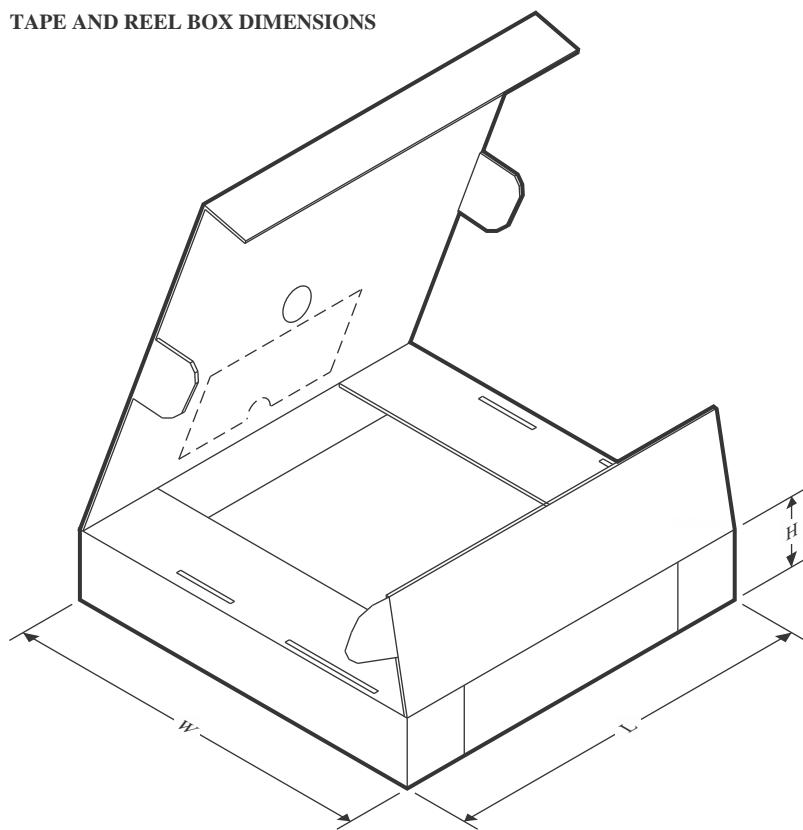

**TAPE AND REEL INFORMATION**

|    |                                                           |

|----|-----------------------------------------------------------|

| A0 | Dimension designed to accommodate the component width     |

| B0 | Dimension designed to accommodate the component length    |

| K0 | Dimension designed to accommodate the component thickness |

| W  | Overall width of the carrier tape                         |

| P1 | Pitch between successive cavity centers                   |

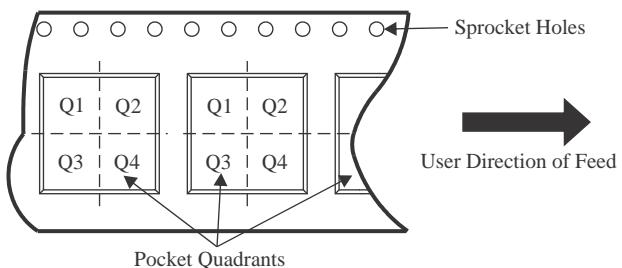

**QUADRANT ASSIGNMENTS FOR PIN 1 ORIENTATION IN TAPE**

\*All dimensions are nominal

| Device          | Package Type | Package Drawing | Pins | SPQ  | Reel Diameter (mm) | Reel Width W1 (mm) | A0 (mm) | B0 (mm) | K0 (mm) | P1 (mm) | W (mm) | Pin1 Quadrant |

|-----------------|--------------|-----------------|------|------|--------------------|--------------------|---------|---------|---------|---------|--------|---------------|

| LMH6672MAX/NOPB | SOIC         | D               | 8    | 2500 | 330.0              | 12.4               | 6.5     | 5.4     | 2.0     | 8.0     | 12.0   | Q1            |

| LMH6672MRX/NOPB | SO PowerPAD  | DDA             | 8    | 2500 | 330.0              | 12.4               | 6.5     | 5.4     | 2.0     | 8.0     | 12.0   | Q1            |

**TAPE AND REEL BOX DIMENSIONS**

\*All dimensions are nominal

| Device          | Package Type | Package Drawing | Pins | SPQ  | Length (mm) | Width (mm) | Height (mm) |

|-----------------|--------------|-----------------|------|------|-------------|------------|-------------|

| LMH6672MAX/NOPB | SOIC         | D               | 8    | 2500 | 367.0       | 367.0      | 35.0        |

| LMH6672MRX/NOPB | SO PowerPAD  | DDA             | 8    | 2500 | 356.0       | 356.0      | 36.0        |

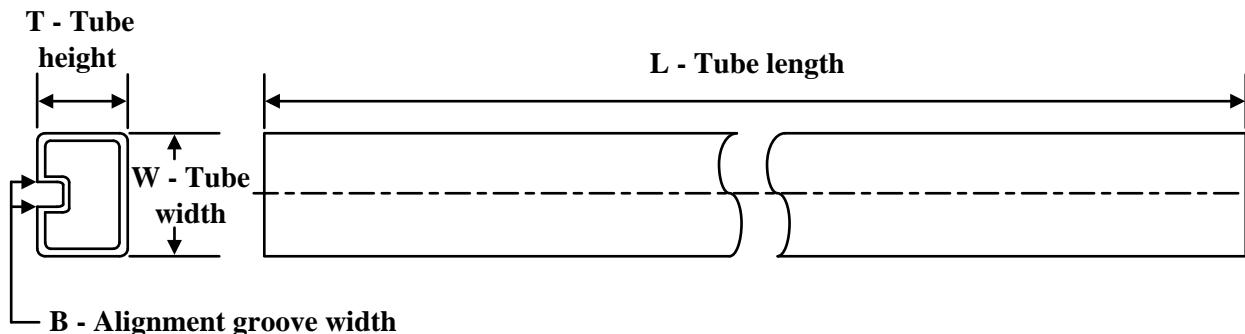

**TUBE**

\*All dimensions are nominal

| Device           | Package Name | Package Type | Pins | SPQ | L (mm) | W (mm) | T ( $\mu$ m) | B (mm) |

|------------------|--------------|--------------|------|-----|--------|--------|--------------|--------|

| LMH6672MA/NOPB   | D            | SOIC         | 8    | 95  | 495    | 8      | 4064         | 3.05   |

| LMH6672MA/NOPB.A | D            | SOIC         | 8    | 95  | 495    | 8      | 4064         | 3.05   |

| LMH6672MR/NOPB   | DDA          | HSOIC        | 8    | 95  | 495    | 8      | 4064         | 3.05   |

| LMH6672MR/NOPB.A | DDA          | HSOIC        | 8    | 95  | 495    | 8      | 4064         | 3.05   |

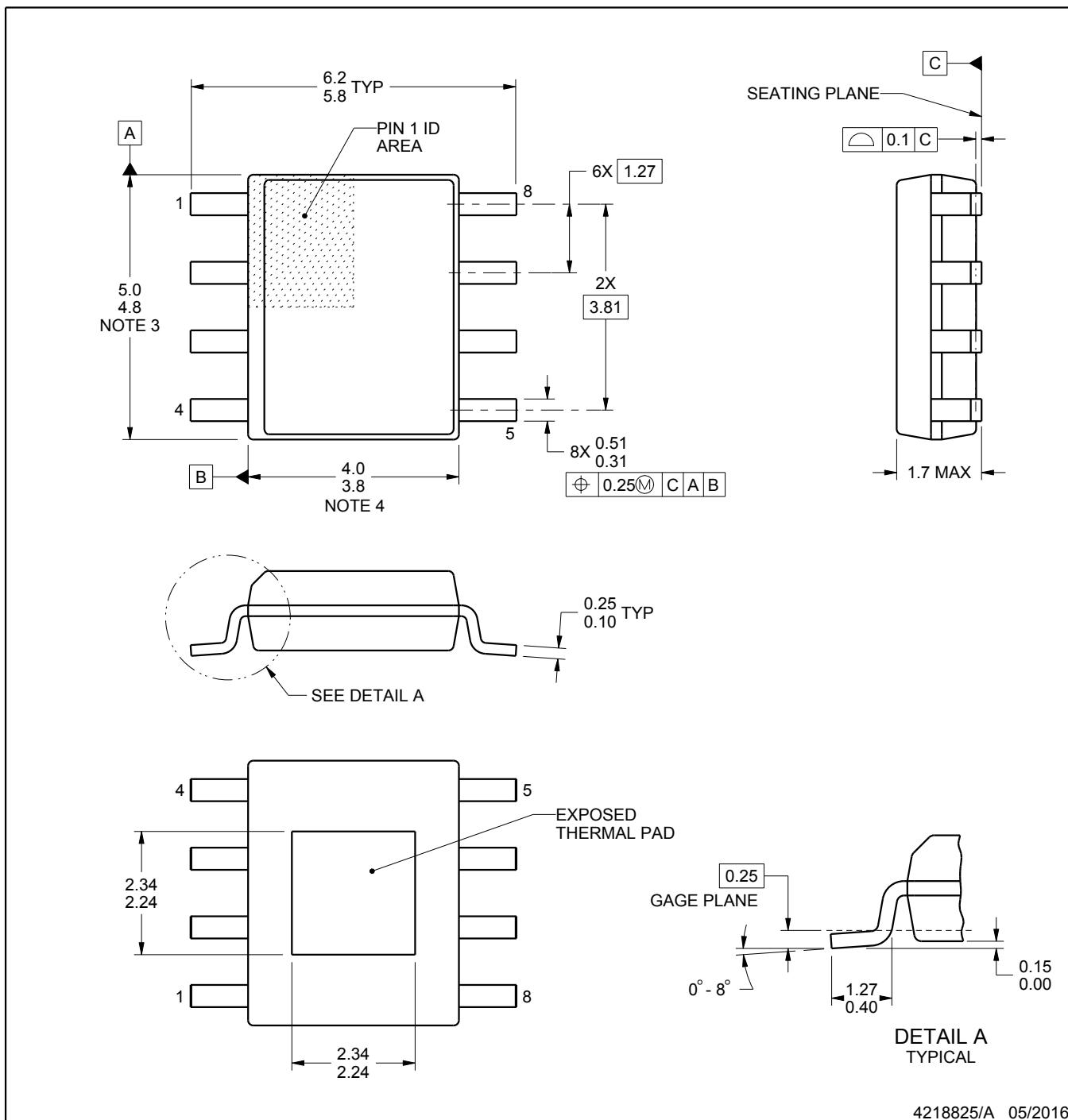

# PACKAGE OUTLINE

DDA0008A

PowerPAD™ SOIC - 1.7 mm max height

PLASTIC SMALL OUTLINE

4218825/A 05/2016

PowerPAD is a trademark of Texas Instruments.

## NOTES:

1. All linear dimensions are in millimeters. Any dimensions in parenthesis are for reference only. Dimensioning and tolerancing per ASME Y14.5M.

2. This drawing is subject to change without notice.

3. This dimension does not include mold flash, protrusions, or gate burrs. Mold flash, protrusions, or gate burrs shall not exceed 0.15 mm per side.

4. This dimension does not include interlead flash. Interlead flash shall not exceed 0.25 mm per side.

5. Reference JEDEC registration MS-012.

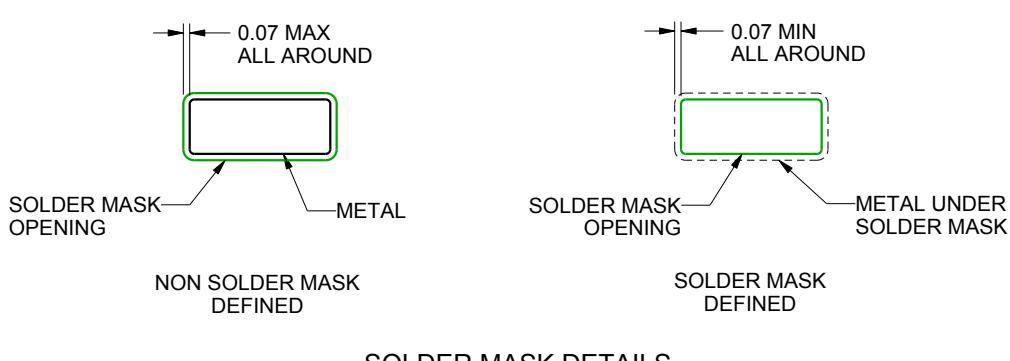

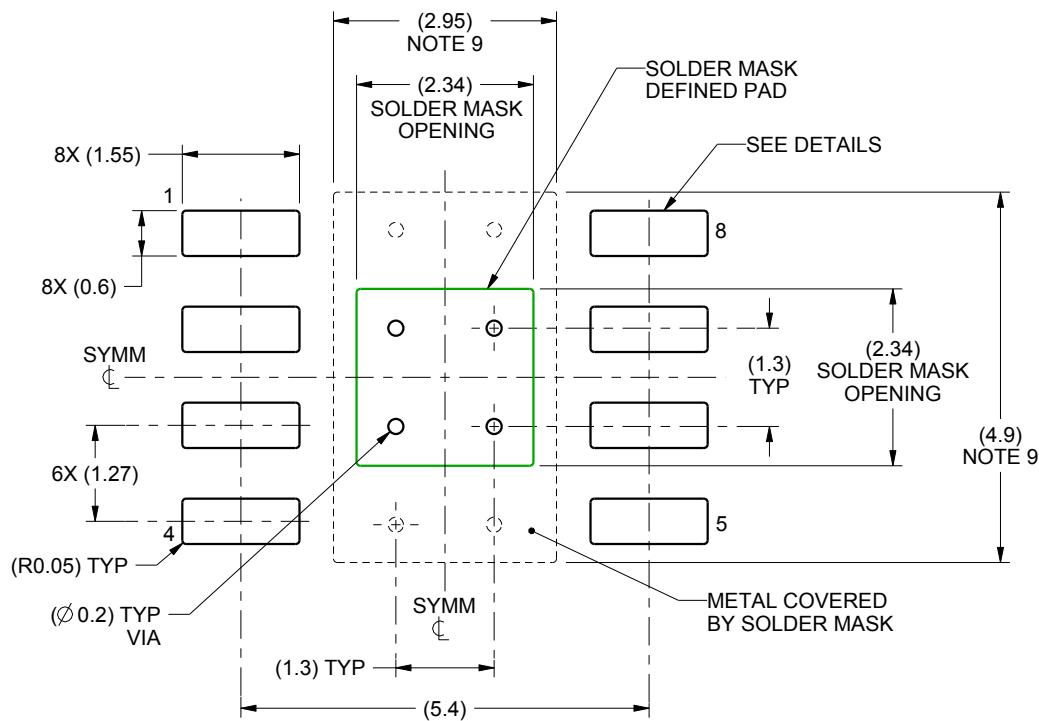

# EXAMPLE BOARD LAYOUT

DDA0008A

PowerPAD™ SOIC - 1.7 mm max height

PLASTIC SMALL OUTLINE

4218825/A 05/2016

NOTES: (continued)

6. Publication IPC-7351 may have alternate designs.

7. Solder mask tolerances between and around signal pads can vary based on board fabrication site.

8. This package is designed to be soldered to a thermal pad on the board. For more information, see Texas Instruments literature numbers SLMA002 ([www.ti.com/lit/slma002](http://www.ti.com/lit/slma002)) and SLMA004 ([www.ti.com/lit/slma004](http://www.ti.com/lit/slma004)).

9. Size of metal pad may vary due to creepage requirement.

10. Vias are optional depending on application, refer to device data sheet. If any vias are implemented, refer to their locations shown on this view. It is recommended that vias under paste be filled, plugged or tented.

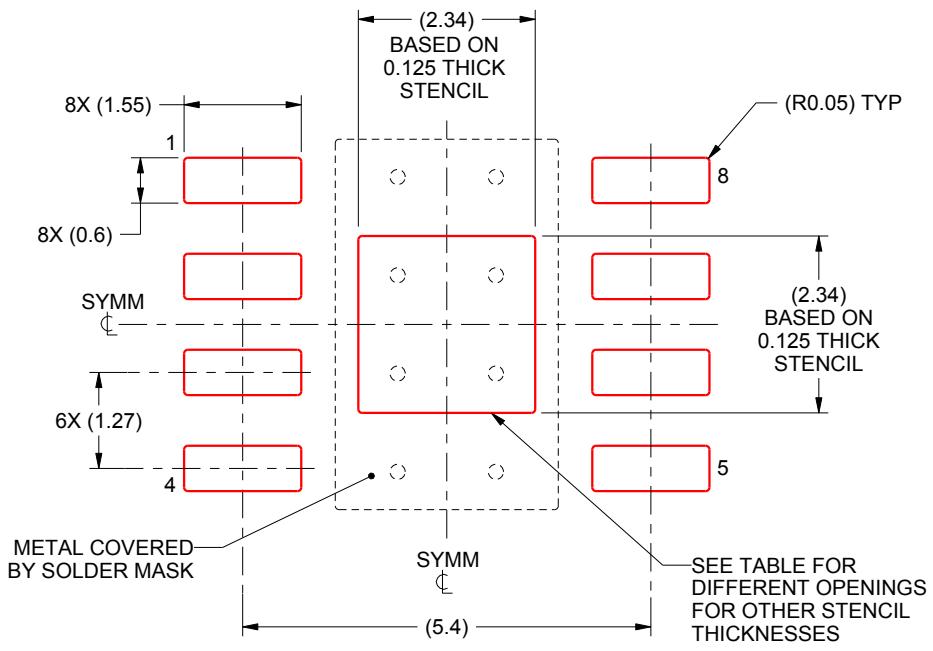

# EXAMPLE STENCIL DESIGN

DDA0008A

PowerPAD™ SOIC - 1.7 mm max height

PLASTIC SMALL OUTLINE

SOLDER PASTE EXAMPLE

EXPOSED PAD

100% PRINTED SOLDER COVERAGE BY AREA

SCALE:10X

| STENCIL THICKNESS | SOLDER STENCIL OPENING |

|-------------------|------------------------|

| 0.1               | 2.62 X 2.62            |

| 0.125             | 2.34 X 2.34 (SHOWN)    |

| 0.150             | 2.14 X 2.14            |

| 0.175             | 1.98 X 1.98            |

4218825/A 05/2016

NOTES: (continued)

11. Laser cutting apertures with trapezoidal walls and rounded corners may offer better paste release. IPC-7525 may have alternate design recommendations.

12. Board assembly site may have different recommendations for stencil design.

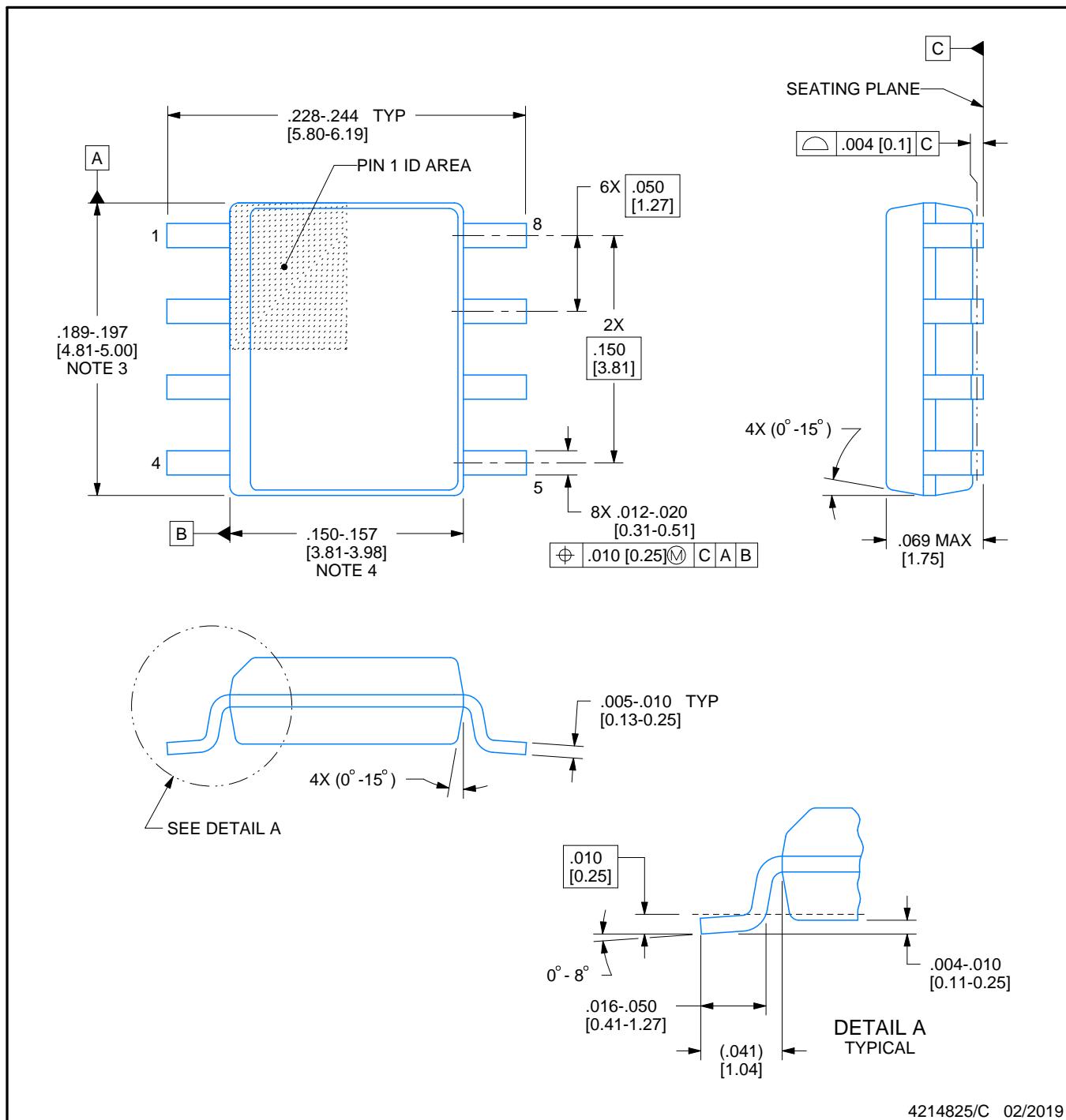

## PACKAGE OUTLINE

**D0008A**

**SOIC - 1.75 mm max height**

## SMALL OUTLINE INTEGRATED CIRCUIT

4214825/C 02/2019

## NOTES:

1. Linear dimensions are in inches [millimeters]. Dimensions in parenthesis are for reference only. Controlling dimensions are in inches. Dimensioning and tolerancing per ASME Y14.5M.

2. This drawing is subject to change without notice.

3. This dimension does not include mold flash, protrusions, or gate burrs. Mold flash, protrusions, or gate burrs shall not exceed .006 [0.15] per side.

4. This dimension does not include interlead flash.

5. Reference JEDEC registration MS-012, variation AA.

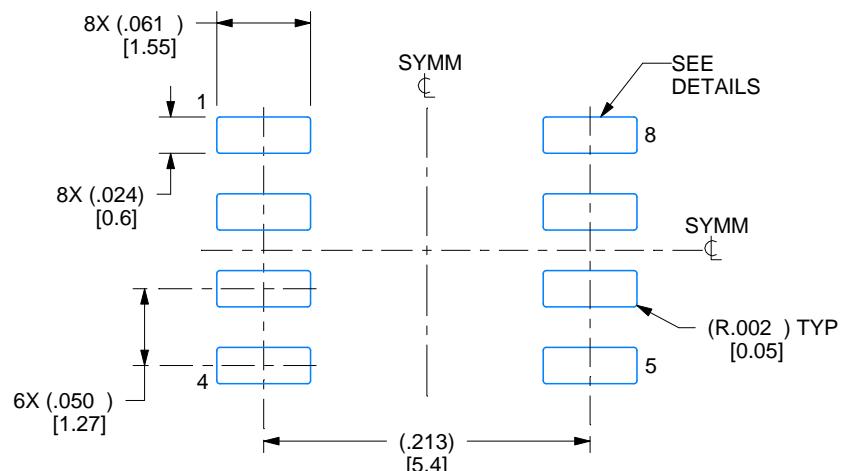

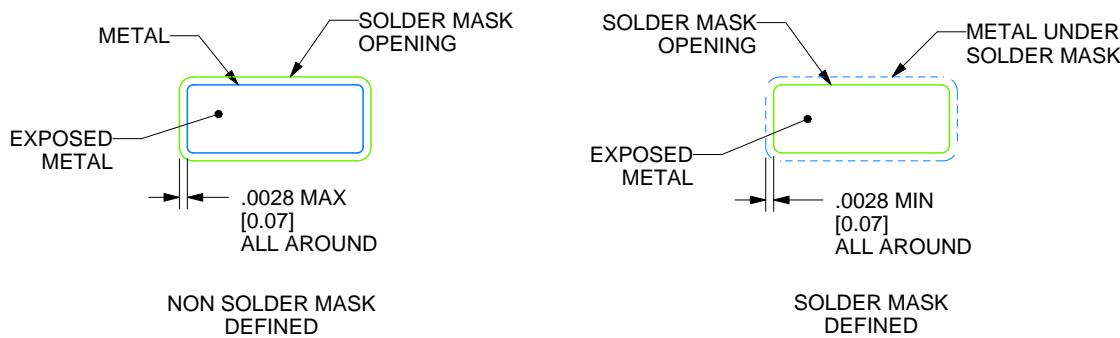

# EXAMPLE BOARD LAYOUT

D0008A

SOIC - 1.75 mm max height

SMALL OUTLINE INTEGRATED CIRCUIT

LAND PATTERN EXAMPLE

EXPOSED METAL SHOWN

SCALE:8X

SOLDER MASK DETAILS

4214825/C 02/2019

NOTES: (continued)

6. Publication IPC-7351 may have alternate designs.

7. Solder mask tolerances between and around signal pads can vary based on board fabrication site.

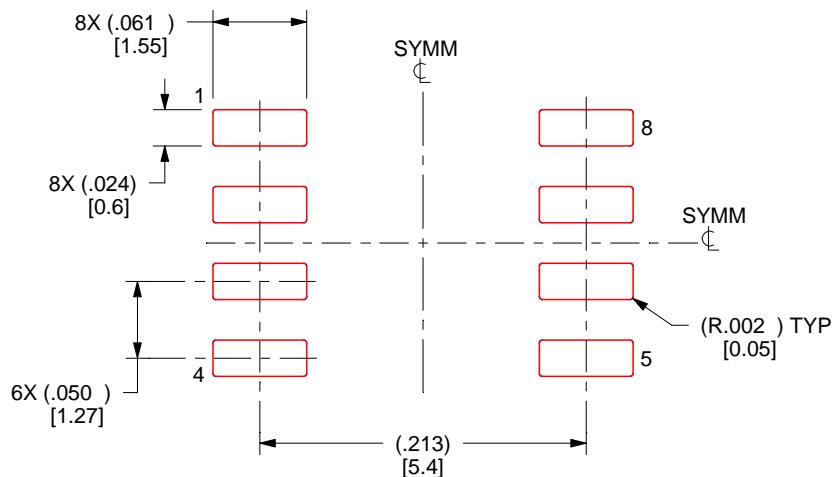

## EXAMPLE STENCIL DESIGN

**D0008A**

### **SOIC - 1.75 mm max height**

## SMALL OUTLINE INTEGRATED CIRCUIT

**SOLDER PASTE EXAMPLE

BASED ON .005 INCH [0.125 MM] THICK STENCIL

SCALE:8X**

4214825/C 02/2019

#### NOTES: (continued)

8. Laser cutting apertures with trapezoidal walls and rounded corners may offer better paste release. IPC-7525 may have alternate design recommendations.

9. Board assembly site may have different recommendations for stencil design.

## IMPORTANT NOTICE AND DISCLAIMER

TI PROVIDES TECHNICAL AND RELIABILITY DATA (INCLUDING DATA SHEETS), DESIGN RESOURCES (INCLUDING REFERENCE DESIGNS), APPLICATION OR OTHER DESIGN ADVICE, WEB TOOLS, SAFETY INFORMATION, AND OTHER RESOURCES "AS IS" AND WITH ALL FAULTS, AND DISCLAIMS ALL WARRANTIES, EXPRESS AND IMPLIED, INCLUDING WITHOUT LIMITATION ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE OR NON-INFRINGEMENT OF THIRD PARTY INTELLECTUAL PROPERTY RIGHTS.

These resources are intended for skilled developers designing with TI products. You are solely responsible for (1) selecting the appropriate TI products for your application, (2) designing, validating and testing your application, and (3) ensuring your application meets applicable standards, and any other safety, security, regulatory or other requirements.

These resources are subject to change without notice. TI grants you permission to use these resources only for development of an application that uses the TI products described in the resource. Other reproduction and display of these resources is prohibited. No license is granted to any other TI intellectual property right or to any third party intellectual property right. TI disclaims responsibility for, and you will fully indemnify TI and its representatives against, any claims, damages, costs, losses, and liabilities arising out of your use of these resources.

TI's products are provided subject to [TI's Terms of Sale](#) or other applicable terms available either on [ti.com](#) or provided in conjunction with such TI products. TI's provision of these resources does not expand or otherwise alter TI's applicable warranties or warranty disclaimers for TI products.

TI objects to and rejects any additional or different terms you may have proposed.

Mailing Address: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265

Copyright © 2025, Texas Instruments Incorporated