### MC100ES6210

**NRND**

### NRND - Not Recommend for New Designs

**DATA SHEET**

#### **Product Discontinuance Notice – Last Time Buy Expires on (12/23/2013)**

The MC100ES6210 is a bipolar monolithic differential clock fanout buffer. Designed for most demanding clock distribution systems, the MC100ES6210 supports various applications that require to distribute precisely aligned differential clock signals. Using SiGe technology and a fully differential architecture, the device offers very low clock skew outputs and superior digital signal characteristics. Target applications for this clock driver is high performance clock distribution in computing, networking and telecommunication systems.

LOW VOLTAGE DUAL

1:5 DIFFERENTIAL PECL/ECL/HSTL

CLOCK FANOUT BUFFER

#### **Features**

- Dual 1:5 differential clock distribution

- · 30 ps maximum device skew

- · Fully differential architecture from input to all outputs

- · SiGe technology supports near-zero output skew

- Supports DC to 3GHz operation of clock or data signals

- · ECL/PECL compatible differential clock outputs

- ECL/PECL compatible differential clock inputs

- Single 3.3V, -3.3V, 2.5V or -2.5V supply

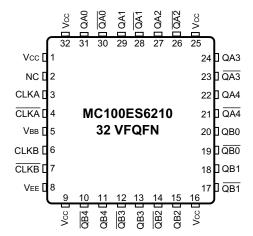

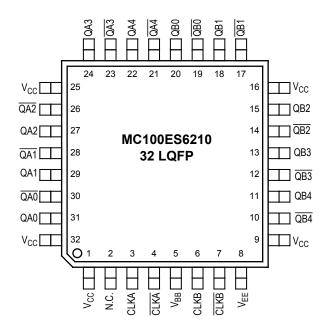

- Standard 32 lead LQFP and VFQFN packages

- Industrial temperature range

- Pin and function compatible to the MC100EP210

- · 32-lead Pb-free Package

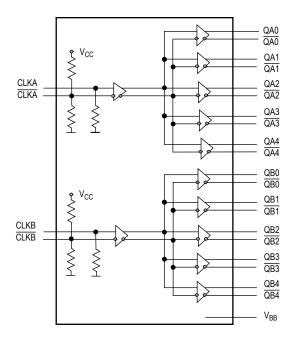

#### **Functional Description**

The MC100ES6210 is designed for low skew clock distribution systems and supports clock frequencies up to 3GHz. The device consists of two independent 1:5 clock fanout buffers. The input signal of each fanout buffer is distributed to five identical, differential ECL/PECL outputs. Both CLKA and CLKB inputs can be driven by ECL/PECL compatible signals.

If  $V_{BB}$  is connected to the CLKA or CLKB input and bypassed to GND by a 10nF capacitor, the MC100ES6210 can be driven by single-ended ECL/PECL signals utilizing the  $V_{BB}$  bias voltage output.

In order to meet the tight skew specification of the device, both outputs of a differential output pair should be terminated, even if only one output is used. In the case where not all ten outputs are used, the output pairs on the same package side as the parts being used on that side should be terminated.

The MC100ES6210 can be operated from a single 3.3V or 2.5V supply. As most other ECL compatible devices, the MC100ES6210 supports positive (PECL) and negative (ECL) supplies. The is function and pin compatible to the MC100EP210.

1

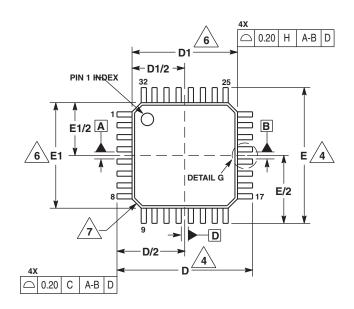

AC SUFFIX 32-LEAD LQFP PACKAGE Pb-FREE PACKAGE CASE 873A-03

K SUFFIX 32-LEAD VFQFN PACKAGE Pb-FREE PACKAGE

| ORDERING INFORMATION |                    |  |  |  |  |

|----------------------|--------------------|--|--|--|--|

| Device Package       |                    |  |  |  |  |

| MC100ES6210AC        | LQFP-32 (Pb-Free)  |  |  |  |  |

| MC100ES6210ACR2      | LQFP-32 (Pb-Free)  |  |  |  |  |

| MC100ES6210KLF       | VFQFN-32 (Pb-Free) |  |  |  |  |

Figure 1. MC100ES6210 Logic Diagram

Figure 3. 32-Lead VFQFN Package Pinout (Top View)

Figure 3. 32-Lead VFQFN Package Pinout (Top View)

Figure 2. 32-Lead LQFP Package Pinout (Top View)

**Table 1. Pin Configuration**

| Pin                            | I/O    | Туре     | Function                                                                                                                     |

|--------------------------------|--------|----------|------------------------------------------------------------------------------------------------------------------------------|

| CLKA, CLKA                     | Input  | ECL/PECL | Differential reference clock signal input (fanout buffer A)                                                                  |

| CLKB, CLKB                     | Input  | ECL/PECL | Differential reference clock signal input (fanout buffer B)                                                                  |

| QA[0-4], QA[0-4]               | Output | ECL/PECL | Differential clock outputs (fanout buffer A)                                                                                 |

| QB[0-4], QB[0-4]               | Output | ECL/PECL | Differential clock outputs (fanout buffer B)                                                                                 |

| V <sub>EE</sub> <sup>(1)</sup> | Supply |          | Negative power supply                                                                                                        |

| V <sub>CC</sub>                | Supply |          | Positive power supply. All $V_{\rm CC}$ pins must be connected to the positive power supply for correct DC and AC operation. |

| V <sub>BB</sub>                | Output | DC       | Reference voltage output for single ended ECL or PECL operation                                                              |

<sup>1.</sup> In ECL mode (negative power supply mode),  $V_{EE}$  is either -3.3V or -2.5V and  $V_{CC}$  is connected to GND (0 V). In PECL mode (positive power supply mode),  $V_{EE}$  is connected to GND (0V) and  $V_{CC}$  is either +3.3V or +2.5V. In both modes, the input and output levels are referenced to the most positive supply ( $V_{CC}$ )

Table 2. Absolute Maximum Ratings<sup>(1)</sup>

| Symbol           | Characteristics     | Characteristics Min Max |                       | Unit | Condition |

|------------------|---------------------|-------------------------|-----------------------|------|-----------|

| V <sub>CC</sub>  | Supply Voltage -0.3 |                         | 3.6                   | V    |           |

| V <sub>IN</sub>  | DC Input Voltage    | -0.3                    | V <sub>CC</sub> + 0.3 | V    |           |

| V <sub>OUT</sub> | DC Output Voltage   | -0.3                    | V <sub>CC</sub> + 0.3 | V    |           |

| I <sub>IN</sub>  | DC Input Current    |                         | ±20                   | mA   |           |

| I <sub>OUT</sub> | DC Output Current   |                         | ±50                   | mA   |           |

| T <sub>S</sub>   | Storage temperature | -65                     | 125                   | °C   |           |

<sup>1.</sup> Absolute maximum continuous ratings are those maximum values beyond which damage to the device may occur. Exposure to these conditions or conditions beyond those indicated may adversely affect device reliability. Functional operation at absolute-maximum-rated conditions is not implied.

**Table 3. General Specifications**

| Symbol            | Characteristics                                                                       | Min  | Тур                                  | Max                                  | Unit                         | Condition                                                                  |

|-------------------|---------------------------------------------------------------------------------------|------|--------------------------------------|--------------------------------------|------------------------------|----------------------------------------------------------------------------|

| V <sub>TT</sub>   | Output Termination Voltage                                                            |      | V <sub>CC</sub> - 2 <sup>(1)</sup>   |                                      | V                            |                                                                            |

| MM                | ESD Protection (Machine Model)                                                        | 200  |                                      |                                      | V                            |                                                                            |

| HBM               | ESD Protection (Human Body Model)                                                     | 2000 |                                      |                                      | V                            |                                                                            |

| CDM               | ESD Protection (Charged Device Model)                                                 |      |                                      |                                      | V                            |                                                                            |

| LU                | Latch-Up Immunity                                                                     | 200  |                                      |                                      | mA                           |                                                                            |

| C <sub>IN</sub>   | Input Capacitance                                                                     |      | 4.0                                  |                                      | pF                           | Inputs                                                                     |

| $\theta_{\sf JA}$ | Thermal Resistance Junction to Ambient 32 LQFP JESD 51-3, single layer test board     |      | 83.1<br>73.3<br>68.9<br>63.8<br>57.4 | 86.0<br>75.4<br>70.9<br>65.3<br>59.6 | °C/W<br>°C/W<br>°C/W<br>°C/W | Natural convection<br>100 ft/min<br>200 ft/min<br>400 ft/min<br>800 ft/min |

|                   | JESD 51-6, 2S2P multilayer test board                                                 |      | 59.0<br>54.4<br>52.5<br>50.4<br>47.8 | 60.6<br>55.7<br>53.8<br>51.5<br>48.8 | °C/W<br>°C/W<br>°C/W<br>°C/W | Natural convection<br>100 ft/min<br>200 ft/min<br>400 ft/min<br>800 ft/min |

|                   | Thermal Resistance Junction to Ambient 32 VFQFN                                       |      | 53.3<br>46.6<br>41.8                 |                                      | °C/W<br>°C/W                 | 0 meters per second<br>1 meters per second<br>2.5 meters per second        |

| θЈС               | Thermal Resistance Junction to Case 32 LQFP                                           |      | 23.0                                 | 26.3                                 | °C/W                         | MIL-SPEC 883E<br>Method 1012.1                                             |

| T <sub>J</sub>    | Operating Junction Temperature <sup>(2)</sup> (continuous operation) MTBF = 9.1 years |      |                                      | 110                                  | °C                           |                                                                            |

<sup>1.</sup> Output termination voltage V<sub>TT</sub> = 0V for V<sub>CC</sub> = 2.5V operation is supported but the power consumption of the device will increase.

Table 4. PECL DC Characteristics ( $V_{CC}$  = 2.5V  $\pm$  5% or  $V_{CC}$  = 3.3V  $\pm$  5%,  $V_{EE}$  = GND,  $T_J$  = 0°C to +110°C)

| Symbol           | Characteristics                                                     | Min                                          | Тур                                              | Max                                          | Unit | Condition                              |  |  |  |

|------------------|---------------------------------------------------------------------|----------------------------------------------|--------------------------------------------------|----------------------------------------------|------|----------------------------------------|--|--|--|

| Clock Input      | Clock Input Pair CLKA, CLKA, CLKB, CLKB (PECL differential signals) |                                              |                                                  |                                              |      |                                        |  |  |  |

| V <sub>PP</sub>  | Differential Input Voltage <sup>(1)</sup>                           | 0.1                                          |                                                  | 1.3                                          | V    | Differential operation                 |  |  |  |

| V <sub>CMR</sub> | Differential Cross Point Voltage <sup>(2)</sup>                     | 1.0                                          |                                                  | V <sub>CC</sub> - 0.3                        | V    | Differential operation                 |  |  |  |

| I <sub>IN</sub>  | Input Current <sup>(1)</sup>                                        |                                              |                                                  | ±100                                         | μА   | $V_{IN} = V_{IL}$ or $V_{IN} = V_{IH}$ |  |  |  |

| PECL Clock       | Outputs (QA0-4, QA0-4, QB0-4, QB0-4)                                |                                              |                                                  |                                              |      | •                                      |  |  |  |

| V <sub>OH</sub>  | Output High Voltage                                                 | V <sub>CC</sub> -1.2                         | V <sub>CC</sub> -1.005                           | V <sub>CC</sub> -0.7                         | V    | $I_{OH} = -30 \text{ mA}^{(3)}$        |  |  |  |

| V <sub>OL</sub>  | Output Low Voltage $V_{CC}$ = 3.3V±5% $V_{CC}$ = 2.5V±5%            | V <sub>CC</sub> -1.9<br>V <sub>CC</sub> -1.9 | V <sub>CC</sub> –1.705<br>V <sub>CC</sub> –1.705 | V <sub>CC</sub> -1.5<br>V <sub>CC</sub> -1.3 | V    | $I_{OL} = -5 \text{ mA}^{(3)}$         |  |  |  |

| Supply Curr      | ent and V <sub>BB</sub>                                             |                                              |                                                  |                                              |      |                                        |  |  |  |

| I <sub>EE</sub>  | Maximum Quiescent Supply Current without Output Termination Current |                                              | 60                                               | 100                                          | mA   | V <sub>EE</sub> pin                    |  |  |  |

| V <sub>BB</sub>  | Output Reference Voltage                                            | V <sub>CC</sub> -1.38                        | V <sub>CC</sub> -1.26                            | V <sub>CC</sub> –1.14                        | V    | I <sub>BB</sub> = 0.2 mA               |  |  |  |

<sup>1.</sup> V<sub>PP</sub> (DC) is the minimum differential input voltage swing required to maintain device functionality.

<sup>2.</sup> Operating junction temperature impacts device life time. Maximum continuous operating junction temperature should be selected according to the application life time requirements (See application note AN1545 for more information). The device AC and DC parameters are specified up to 110°C junction temperature allowing the MC100ES6210 to be used in applications requiring industrial temperature range. It is recommended that users of the MC100ES6210 employ thermal modeling analysis to assist in applying the junction temperature specifications to their particular application.

<sup>2.</sup> V<sub>CMR</sub> (DC) is the crosspoint of the differential input signal. Functional operation is obtained when the crosspoint is within the V<sub>CMR</sub> (DC) range and the input swing lies within the V<sub>PP</sub> (DC) specification.

<sup>3.</sup> Equivalent to a termination of 50  $\Omega$  to V  $_{TT}$

Table 5. ECL DC Characteristics (V<sub>EE</sub> = -2.5V  $\pm$  5% or V<sub>EE</sub> = -3.3V  $\pm$  5%, V<sub>CC</sub> = GND, T<sub>J</sub> = 0°C to +110°C)

| Symbol           | Characteristics                                                        | Min                   | Тур              | Max          | Unit | Condition                                                              |

|------------------|------------------------------------------------------------------------|-----------------------|------------------|--------------|------|------------------------------------------------------------------------|

| Clock Input      | Pair CLKA, CLKA, CLKB, CLKB (ECL differen                              | tial signals)         | I                |              | 1    | 1                                                                      |

| V <sub>PP</sub>  | Differential Input Voltage <sup>(1)</sup>                              | 0.1                   |                  | 1.3          | V    | Differential operation                                                 |

| V <sub>CMR</sub> | Differential Cross Point Voltage <sup>(2)</sup>                        | V <sub>EE</sub> + 1.0 |                  | -0.3         | V    | Differential operation                                                 |

| I <sub>IN</sub>  | Input Current <sup>(1)</sup>                                           |                       |                  | ±100         | μА   | V <sub>IN</sub> = V <sub>IL</sub> or V <sub>IN</sub> = V <sub>IH</sub> |

| ECL Clock (      | Outputs (QA0–4, QA0–4, QB0–4, QB0–4)                                   |                       |                  |              | •    |                                                                        |

| V <sub>OH</sub>  | Output High Voltage                                                    | -1.2                  | -1.005           | -0.7         | V    | $I_{OH} = -30 \text{ mA}^{(3)}$                                        |

| V <sub>OL</sub>  | Output Low Voltage $V_{CC}$ = 3.3V $\pm 5\%$ $V_{CC}$ = 2.5V $\pm 5\%$ |                       | -1.705<br>-1.705 | -1.5<br>-1.3 | V    | $I_{OL} = -5 \text{ mA}^{(3)}$                                         |

| Supply Curr      | ent and V <sub>BB</sub>                                                |                       |                  |              | •    |                                                                        |

| I <sub>EE</sub>  | Maximum Quiescent Supply Current without Output Termination Current    |                       | 60               | 100          | mA   | V <sub>EE</sub> pin                                                    |

| $V_{BB}$         | Output Reference Voltage                                               | -1.38                 | -1.26            | -1.14        | V    | I <sub>BB</sub> = 0.2 mA                                               |

<sup>1.</sup>  $V_{PP}$  (DC) is the minimum differential input voltage swing required to maintain device functionality.

<sup>2.</sup>  $V_{CMR}$  (DC) is the crosspoint of the differential input signal. Functional operation is obtained when the crosspoint is within the  $V_{CMR}$  (DC) range and the input swing lies within the  $V_{PP}$  (DC) specification.

<sup>3.</sup> Equivalent to a termination of 50  $\Omega$  to V  $_{TT}\!.$

| <b>Table 6. AC Characteristics</b> (ECL: $V_{EE}$ = -3.3V $\pm$ 5% or $V_{EE}$ = -2.5V $\pm$ 5%, $V_{CC}$ = GND) or |   |

|---------------------------------------------------------------------------------------------------------------------|---|

| (PECL: $V_{CC}$ = 3.3V ± 5% or $V_{CC}$ = 2.5V ± 5%, $V_{EE}$ = GND, $T_J$ = 0°C to +110°C) <sup>(1)</sup> (2)      | ) |

| Symbol                          | Characteristics                                                                              | Min                          | Тур                  | Max                            | Unit        | Condition                                          |

|---------------------------------|----------------------------------------------------------------------------------------------|------------------------------|----------------------|--------------------------------|-------------|----------------------------------------------------|

| Clock Input                     | Pair CLKA, CLKA, CLKB, CLKB (PECL or ECL diff                                                | erential signals)            |                      |                                | <b>'</b>    | 1                                                  |

| V <sub>PP</sub>                 | Differential Input Voltage <sup>(3)</sup> (peak-to-peak)                                     | 0.3                          | 0.3                  | 1.3                            | V           |                                                    |

| V <sub>CMR</sub>                | Differential Input Crosspoint Voltage <sup>(4)</sup> PECL ECL                                | 1.2<br>V <sub>EE</sub> + 1.2 |                      | V <sub>CC</sub> - 0.3<br>-0.3V | V           |                                                    |

| ECL Clock (                     | Outputs (Qx0–4, Qx0–4)                                                                       |                              |                      |                                |             |                                                    |

| f <sub>CLK</sub>                | Input Frequency                                                                              | 0                            |                      | 3000                           | MHz         | Differential                                       |

| t <sub>PD</sub>                 | Propagation Delay<br>CLKA to QAx or CLKB to QBx                                              | 175                          | 260                  | 350                            | ps          | Differential                                       |

| $V_{O(P-P)}$                    | Differential Output Voltage (peak-to-peak) $f_O < 1.1 GHz \\ f_O < 2.5 GHz \\ f_O < 3.0 GHz$ | 0.45<br>0.35<br>0.20         | 0.70<br>0.55<br>0.35 |                                | V<br>V<br>V |                                                    |

| t <sub>sk(O)</sub>              | Output-to-Output Skew (per bank)                                                             |                              | 13                   | 30                             | ps          | Differential                                       |

| t <sub>sk(PP)</sub>             | Output-to-Output Skew (part-to-part)                                                         |                              |                      | 175                            | ps          | Differential                                       |

| t <sub>JIT(CC)</sub>            | Output Cycle-to-Cycle Jitter                                                                 |                              |                      | 1                              | ps          |                                                    |

| t <sub>jit</sub>                | Buffer Additive Phase Jitter, RMS 3.3V±5% 2.5V±5%                                            |                              |                      | 0.45<br>0.96                   | ps<br>ps    |                                                    |

| t <sub>SK(P)</sub>              | Output Pulse Skew <sup>(5)</sup>                                                             |                              |                      | 50                             | ps          |                                                    |

| $DC_Q$                          | Output Duty Cycle $ f_{REF} < 0.1 GHz \\ f_{REF} < 1.0 GHz $                                 | 49.5<br>45.0                 | 50<br>50             | 50.5<br>55.0                   | %<br>%      | DC <sub>REF</sub> = 50%<br>DC <sub>REF</sub> = 50% |

| t <sub>r</sub> , t <sub>f</sub> | Output Rise/Fall Time                                                                        | 30                           |                      | 250                            | ps          | 20% to 80%                                         |

- 1. AC characteristics are design targets and pending characterization.

- 2. AC characteristics apply for parallel output termination of 50  $\Omega$  to V $_{TT}$

- 3. V<sub>PP</sub> (AC) is the minimum differential ECL/PECL input voltage swing required to maintain AC characteristics including t<sub>PD</sub> and device-to-device skew.

- 4. V<sub>CMR</sub> (AC) is the crosspoint of the differential ECL/PECL input signal. Normal AC operation is obtained when the crosspoint is within the V<sub>CMR</sub> (AC) range and the input swing lies within the V<sub>PP</sub> (AC) specification. Violation of V<sub>CMR</sub> (AC) or V<sub>PP</sub> (AC) impacts the device propagation delay, device and part-to-part skew.

- 5. Output pulse skew is the absolute difference of the propagation delay times: | t<sub>PLH</sub> t<sub>PHL</sub> |.

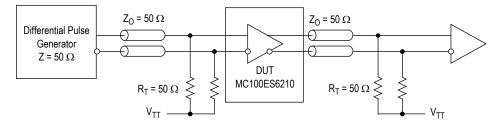

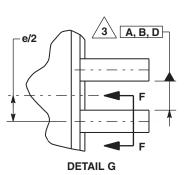

Figure 4. MC100ES6210 AC Test Reference

## **Package Outline and Package Dimensions**

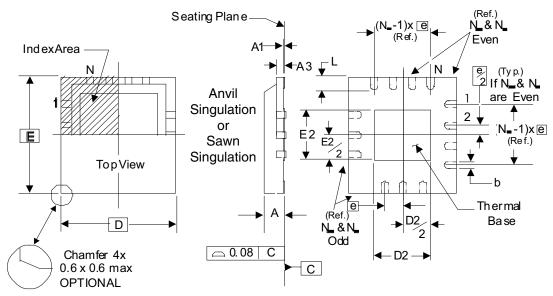

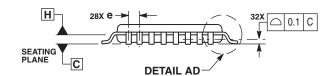

### Package Outline - K Suffix for 32 Lead VFQFN

NOTE: The following package mechanical drawing is a generic drawing that applies to any pin count VFQFN package. This drawing is not intended to convey the actual pin count or pin layout of this device. The pin count and pinout are shown on the front page. The package dimensions are in Table 7 below.

**Table 7. Package Dimensions**

| JEDEC Variation: VHHD-2/-4 All Dimensions in Millimeters |         |                |         |  |  |  |  |

|----------------------------------------------------------|---------|----------------|---------|--|--|--|--|

| Symbol                                                   | Minimum | Nominal        | Maximum |  |  |  |  |

| N                                                        |         | 32             |         |  |  |  |  |

| Α                                                        | 0.80    |                | 1.00    |  |  |  |  |

| A1                                                       | 0       |                | 0.05    |  |  |  |  |

| А3                                                       |         | 0.25 Ref.      |         |  |  |  |  |

| b                                                        | 0.18    | 0.25           | 0.30    |  |  |  |  |

| N <sub>D</sub> & N <sub>E</sub>                          |         |                | 8       |  |  |  |  |

| D&E                                                      |         | 5.00 Basic     |         |  |  |  |  |

| D2 & E2                                                  | 3.0     |                | 3.3     |  |  |  |  |

| е                                                        |         | 0.50 Basic     |         |  |  |  |  |

| L                                                        | 0.30    | 0.30 0.40 0.50 |         |  |  |  |  |

Reference Document: JEDEC Publication 95, MO-220

#### **PACKAGE DIMENSIONS**

#### NOTES:

- NOTES:

1. DIMENSIONS ARE IN MILLIMETERS.

2. INTERPRET DIMENSIONS AND TOLERANCES PER ASME Y14.5M, 1994.

3. DATUMS A, B, AND D TO BE DETERMINED AT DATUM PLANE H.

4. DIMENSIONS D AND E TO BE DETERMINED AT SEATING PLANE C.

5. DIMENSION & DOES NOT INCLUDE DAMBAR PROTRUSION. ALLOWABLE DAMBAR PROTRUSION SHALL NOT CAUSE THE LEAD WIDTH TO EXCEED THE MAXIMUM & DIMENSION BY MORE THAN 0.08-mm. DAMBAR CANNOT BE LOCATED ON THE LOWER RADIUS OR THE FOOT MINIMUM SPACE BETWEEN PROTRUSION AND ADJACENT LEAD OR PROTRUSION. ALLOWABLE PROTRUSION IS 0.25-mm PER SIDE. D1 AND E1 ARE MAXIMUM PLASTIC BODY SIZE DIMENSIONS INCLUDING MOLD MISMATCH.

A. EXACT SHAPE OF EACH CORNER IS OPTIONAL.

8. THESE DIMENSIONS APPLY TO THE FLAT SECTION OF THE LEAD BETWEEN 0.1-mm AND 0.25-mm FROM THE LEAD BETWEEN 0.1-mm AND 0.25-mm FROM THE LEAD BETWEEN 0.1-mm AND 0.25-mm FROM THE LEAD TIP.

- 0.25-mm FROM THE LEAD TIP.

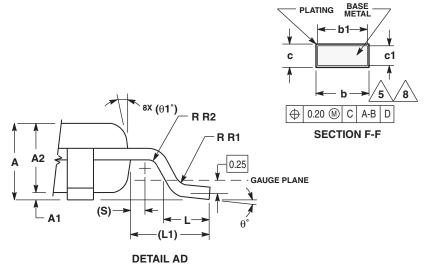

|     | MILLIMETERS |      |  |  |  |

|-----|-------------|------|--|--|--|

| DIM | MIN         | MAX  |  |  |  |

| Α   | 1.40        | 1.60 |  |  |  |

| A1  | 0.05        | 0.15 |  |  |  |

| A2  | 1.35        | 1.45 |  |  |  |

| b   | 0.30        | 0.45 |  |  |  |

| b1  | 0.30        | 0.40 |  |  |  |

| С   | 0.09        | 0.20 |  |  |  |

| c1  | 0.09        | 0.16 |  |  |  |

| D   | 9.00        | BSC  |  |  |  |

| D1  | 7.00        | BSC  |  |  |  |

| е   | 0.80        | BSC  |  |  |  |

| Ε   | 9.00        | BSC  |  |  |  |

| E1  | 7.00        | BSC  |  |  |  |

| L   | 0.50        | 0.70 |  |  |  |

| L1  | 1.00        | REF  |  |  |  |

| q   | 0° 7°       |      |  |  |  |

| q1  | 12 REF      |      |  |  |  |

| R1  | 0.08        | 0.20 |  |  |  |

| R2  | 0.08        |      |  |  |  |

| S   | 0.20        | REF  |  |  |  |

**CASE 873A-03 ISSUE B** 32-LEAD LQFP PACKAGE

# **Revision History Sheet**

| Rev | Table | Page | Description of Change                                                 | Date       |

|-----|-------|------|-----------------------------------------------------------------------|------------|

| 7   |       | 1    | NRND – Not Recommend for New Designs                                  | 12/19/2012 |

| 6   |       | 1    | Product Discontinuance Notice – Last Time Buy Expires on (12/23/2013) | 2/5/2013   |

# We've Got Your Timing Solution

6024 Silver Creek Valley Road San Jose, California 95138

800-345-7015 (inside USA) +408-284-8200 (outside USA) Fax: 408-284-2775 www.IDT.com/go/contactIDT Technical Support netcom@idt.com +480-763-2056

DISCLAIMER Integrated Device Technology, Inc. (IDT) and its subsidiaries reserve the right to modify the products and/or specifications described herein at any time and at IDT's sole discretion. All information in this document, including descriptions of product features and performance, is subject to change without notice. Performance specifications and the operating parameters of the described products are determined in the independent state and are not guaranteed to perform the same way when installed in customer products. The information contained herein is provided without representation or warranty of any kind, whether express or implied, including, but not limited to, the suitability of IDT's products for any particular purpose, an implied warranty of merchantability, or non-infringement of the intellectual property rights of others. This document is presented only as a guide and does not convey any license under intellectual property rights of IDT's products for any particular purpose.

IDT's products are not intended for use in applications involving extreme environmental conditions or in life support systems or similar devices where the failure or malfunction of an IDT product can be reasonably expected to significantly affect the health or safety of users. Anyone using an IDT product in such a manner does so at their own risk, absent an express, written agreement by IDT.

Integrated Device Technology, IDT and the IDT logo are registered trademarks of IDT. Other trademarks and service marks used herein, including protected names, logos and designs, are the property of IDT or their respective third party owners.

# **Mouser Electronics**

**Authorized Distributor**

Click to View Pricing, Inventory, Delivery & Lifecycle Information:

IDT (Integrated Device Technology): MC100ES6210ACR2 MC100ES6210AC