N PACKAGE (TOP VIEW)

SLLS260B - NOVEMBER 1996 - REVISED AUGUST 1997

- Universal Serial Bus (USB) Version 1.0 Compliant

- **Integrated USB Transceivers**

- **Four Downstream Ports**

- **Two Power Source Modes**

- **Self-powered Mode**

- **Bus-powered Mode**

- **Power Switching and Overcurrent** Reporting is Provided Per Port or Ganged

- **Suspend Status Terminal Avaliable for External Logic Power Down**

- All Downstream Ports Support Full-Speed and Low-Speed Operations

- **Supports Suspend and Resume Operations**

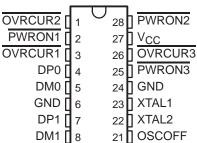

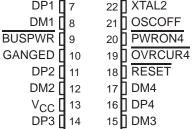

- Available in 28-Pin DIP Package and a 48-Pin TQFP<sup>†</sup> Package

- 3.3-V Operation

## description

The TUSB2040 hub is a CMOS device that provides up to four downstream ports in conformance with the USB specification, version 1.0. It supports two power source modes: bus-powered and self-powered. The hub and downstream ports share the same power source. The TUSB2040 hub powers down to 20 nA during the suspend operation by powering down the internal oscillator.

The TUSB2040 hub supports power switching to the downstream ports either individually or ganged. An external device or devices are required to switch power and to detect overcurrent conditions. The TUSB2040 provides outputs to control power switching and inputs to monitor any overcurrent conditions. In the ganged operation, all PWRON signals transition simultaneously, and any OVRCUR input may be used.

#### PT PACKAGE (TOP VIEW)

† JEDEC descriptor S-PQFP-G for thin quad flatpack (TQFP)

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

SLLS260B - NOVEMBER 1996 - REVISED AUGUST 1997

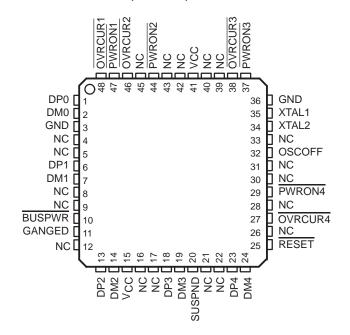

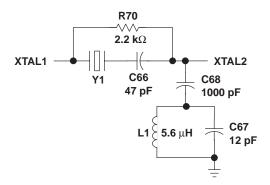

The hub requires a 48-MHz clock signal to sample data from the upstream port and generate a synchronized 12-MHz USB clock signal. The hub supports the flexibility to use either a 48-MHz oscillator or a crystal tuned to 48-MHz. If an oscillator is used, connect its output to the XTAL1 terminal and leave the XTAL2 terminal open. An oscillator with TTL output may be used if the output does not exceed 3.6 V. For a crystal implementation, use the XTAL1 terminal as the input and the XTAL2 terminal as the feedback path to the crystal. Because the crystal is required to resonate at 48-MHz, a tuning circuit as shown in Figure 6 may be required.

USB-compliant transceivers are provided for the upstream port and all downstream ports. Every downstream port supports both full- and low-speed connection by automatically setting the slew rate according to the speed of the device attached to the port.

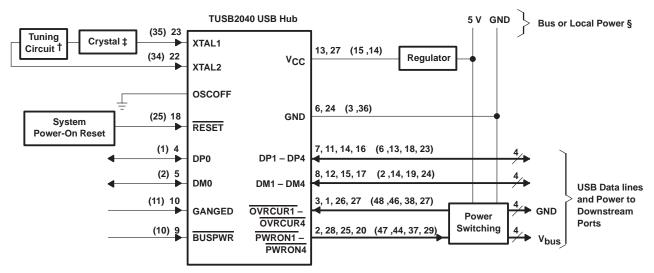

## functional block diagram

NOTES: A. Pins in parentheses are for TQFP package

B. SUSPND output only available in TQFP package

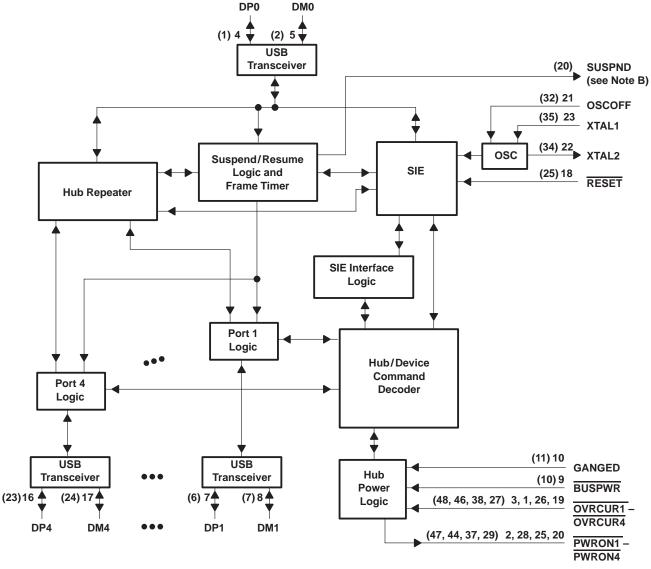

# **Terminal Functions**

| TERMINAL             |                  | 1,,               | DESCRIPTION |                                                                                                                                                                                                                                                                                                                              |  |

|----------------------|------------------|-------------------|-------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| NAME                 | N NO.            | PT NO.            | 1/0         | DESCRIPTION                                                                                                                                                                                                                                                                                                                  |  |

| BUSPWR               | 9                | 10                | I           | Power source indicator. BUSPWR is an active low input that indicates whether the ports and the hub derive power from the bus or are self-powered by the local supply. This standard TTL input must not change dynamically during operation.                                                                                  |  |

| DM0                  | 5                | 2                 | I/O         | Root port USB differential data minus. DM0 paired with DP0 constitutes the upstream USB port.                                                                                                                                                                                                                                |  |

| DM1 – DM4            | 8, 12,<br>15, 17 | 7, 14,<br>19, 24  | I/O         | USB differential data minus. DM1 – DM4 paired with DP1 – DP4 support up to four downstream USB ports.                                                                                                                                                                                                                        |  |

| DP0                  | 4                | 1                 | I/O         | Root port USB differential data plus. DP0 paired with DM0 constitutes the upstream USB port.                                                                                                                                                                                                                                 |  |

| DP1 – DP4            | 7, 11,<br>14, 16 | 6, 13,<br>18, 23  | I/O         | USB differential data plus. DP1 – DP4 paired with DM1 – DM4 support up to four downstream USB ports.                                                                                                                                                                                                                         |  |

| GANGED               | 10               | 11                | I           | Power switching/overcurrent detection mode. GANGED selects between gang or per port switching and overcurrent detection for downstream ports. This standard TTL input must not change dynamically during operation.                                                                                                          |  |

| GND                  | 6, 24            | 3, 36             |             | Ground. GND terminals must be tied to ground for proper operation.                                                                                                                                                                                                                                                           |  |

| OSCOFF               | 21               | 32                | I           | Oscillator off. OSCOFF disables the internal oscillator for quiesent current draw (ICCQ) testing. It must be tied low for proper operation.                                                                                                                                                                                  |  |

| OVRCUR1 –<br>OVRCUR4 | 3, 1,<br>26, 19  | 48, 46,<br>38, 27 | I           | Overcurrent indicators. OVRCUR1 – OVRCUR4 are active low, standard TTL inputs. One overcurrent indicator is available for each of the four downstream ports. In GANGED mode, one implementation is to tie these inputs together. Alternatively, one OVRCUR input pin may be used with the remaining OVRCUR pins tied to VCC. |  |

| PWRON1 –<br>PWRON4   | 2, 28,<br>25, 20 | 47, 44,<br>37, 29 | 0           | Power-on/-off control signals. PWRON1 – PWRON4 are active low, open-drain outputs. One power on/off control switch is used for each of the four downstream ports. In GANGED mode, all outputs are switched together.                                                                                                         |  |

| RESET                | 18               | 25                | I           | Reset. RESET is an active low TTL input with hysteresis and must be asserted at power up. When RESET is asserted it initializes all logic.                                                                                                                                                                                   |  |

| SUSPND               | _                | 20                | 0           | Suspend status. SUSPND is an active high output that is available for external logic power down operations. During the SUSPEND mode, SUSPND is high. SUSPND is low for normal operation.                                                                                                                                     |  |

| Vcc                  | 13, 27           | 15, 41            |             | 3.3-V supply voltage                                                                                                                                                                                                                                                                                                         |  |

| XTAL1                | 23               | 35                | Ι           | Crystal 1. XTAL1 is a 48-MHz crystal input with 50 % duty cycle. Operation at 48-MHz is four times the USB full-speed bit rate of 12-Mbps.                                                                                                                                                                                   |  |

| XTAL2                | 22               | 34                | 0           | Crystal 2. XTAL2 is a 48-MHz crystal output. Operation at 48-MHz is four times the USB full-speed bit rate of 12-Mbps. This terminal is left open when using an oscillator.                                                                                                                                                  |  |

## absolute maximum ratings over operating free-air temperature range (unless otherwise noted)†

| Supply voltage range, V <sub>CC</sub> (see Note 1)                                                                                             | $\dots \dots -0.5 \ V$ to 3.8 V                       |

|------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------|

| Input voltgage range, V <sub>I</sub>                                                                                                           |                                                       |

| Input clamp current, $I_{IK}$ , $(V_I < 0 \text{ V or } V_I > V_{CC})$ Output clamp current, $I_{OK}$ , $(V_O < 0 \text{ V or } V_O > V_{CC})$ | $ \begin{array}{cccccccccccccccccccccccccccccccccccc$ |

<sup>†</sup> Stresses beyond those listed under "absolute maximum ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated under "recommended operating conditions" is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

NOTE 1: All voltage levels are with respect to GND.

# TUSB2040 4-PORT HUB FOR THE UNIVERSAL SERIAL BUS

SLLS260B - NOVEMBER 1996 - REVISED AUGUST 1997

## recommended operating conditions

|                                                                   | MIN      | NOM | MAX      | UNIT |

|-------------------------------------------------------------------|----------|-----|----------|------|

| Supply voltage, V <sub>CC</sub>                                   | 3        | 3.3 | 3.6      | V    |

| Input voltage, TTL/LVCMOS, VI                                     | 0        |     | Vcc      | V    |

| Output voltage, TTL/LVCMOS, VO                                    | 0        |     | Vcc      | V    |

| High-level input voltage, signal-ended receiver, VIH(REC)         | 2        |     | Vcc      | V    |

| Low-level input voltage, signal-ended receiver, VIL(REC)          |          |     | 0.8      | V    |

| High-level input voltage, TTL/LVCMOS, VIH(TTL)                    | 2        |     | Vcc      | V    |

| Low-level input voltage, TTL/LVCMOS, VIL(TTL)                     |          |     | 0.8      | V    |

| Operating free-air temperature, T <sub>A</sub>                    | 0        |     | 70       | °C   |

| External series, differential driver resistor, R <sub>(DRV)</sub> | 22 (-5%) | 2   | 22 (+5%) | Ω    |

| Operating (dc differential driver) high speed mode, f(OPRH)       |          |     | 12       | Mb/s |

| Operating (dc differential driver) low speed mode, f(OPRL)        |          |     | 1.5      | Mb/s |

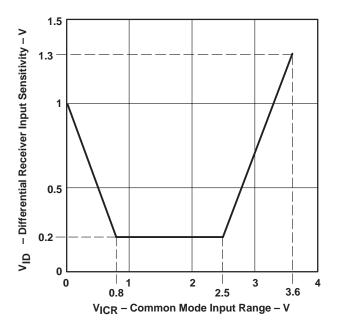

| Common mode, input range, differential receiver, V(ICR)           | 0.8      |     | 2.5      | V    |

| Input transition times, t <sub>t</sub> , TTL/LVCMOS               | 0        |     | 6        | ns   |

# electrical characteristics over recommended ranges of operating free-air temperature and supply voltage (unless otherwise noted)

|                      | PARAMETER                               |                | TEST CONDITIONS                                               | MIN       | MAX  | UNIT |

|----------------------|-----------------------------------------|----------------|---------------------------------------------------------------|-----------|------|------|

| VOH                  | High-level output voltage               | USB data lines | $R(DRV) = 15 k\Omega$ , to GND                                | 2.8       | 3.6  | V    |

|                      |                                         |                | $I_{OH} = -12 \text{ mA (without R}_{(DRV)})$                 | VCC - 0.5 |      |      |

| VOL                  | Low-level output voltage                | TTL/LVCMOS     | I <sub>OL</sub> = 4 mA                                        |           | 0.5  |      |

|                      |                                         | USB data lines | $R_{(DRV)} = 1.5 \text{ k } \Omega \text{ to } 3.6 \text{ V}$ |           | 0.3  | ٧    |

|                      |                                         |                | $I_{OL} = 12 \text{ mA (without R}_{(DRV)})$                  |           | 0.5  |      |

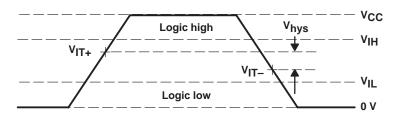

| V <sub>IT+</sub>     | Positive input threshold voltage        | TTL/LVCMOS     |                                                               |           | 2    | V    |

|                      |                                         | Single-ended   | $0.8 \text{ V} \leq \text{V}_{\text{ICR}} \leq 2.5 \text{ V}$ |           | 1.8  | V    |

| \/                   | Negative-input threshold voltage        | TTL/LVCMOS     |                                                               | 0.8       |      | V    |

| V <sub>IT</sub> _    |                                         | Single-ended   | $0.8 \text{ V} \leq \text{V}_{\text{ICR}} \leq 2.5 \text{ V}$ | 1         |      | V    |

| \/.                  | Input hysteresis† ( $V_{T+} - V_{T-}$ ) | TTL/LVCMOS     |                                                               | 0.25      | 0.7  | V    |

| V <sub>hys</sub>     |                                         | Single-ended   | $0.8 \text{ V} \leq \text{V}_{\text{ICR}} \leq 2.5 \text{ V}$ | 300       | 500  | mV   |

| 10-                  | High-impedance output current           | TTL/LVCMOS     | $V = V_{CC}$ or GND‡                                          |           | ±10  | μΑ   |

| loz                  |                                         | USB data lines | $0 \text{ V} \leq \text{V}_{O} \leq \text{V}_{CC}$            |           | ±10  | μΑ   |

| I <sub>IL</sub>      | Low-level input current                 | TTL/LVCMOS     | V <sub>I</sub> = GND                                          |           | -1   | μΑ   |

| lН                   | High-level input current                | TTL/LVCMOS     | VI = VCC                                                      |           | 1    | μΑ   |

| Z <sub>O</sub> (DRV) | Driver output impedance                 | USB data lines | Static VOH or VOL                                             | 7.1       | 19.9 | Ω    |

| VID                  | Differential input voltage              | USB data lines | 0.8 V ≤ V <sub>ICR</sub> ≤ 2.5 V                              | 0.2       |      | V    |

| laa                  | Input cumply current                    |                | Normal operation                                              |           | 100  | mA   |

| ICC                  | Input supply current                    |                | Suspend mode                                                  |           | 1    | μА   |

<sup>†</sup> Applies for input buffers with hysteresis

<sup>‡</sup> Applies for open drain buffers

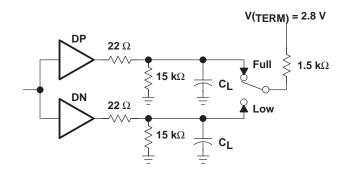

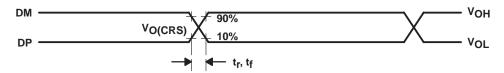

differential driver switching characteristics over recommended ranges of operating free-air temperature and supply voltage,  $C_L = 50$  pF unless otherwise noted (see Figures 1 and 2)

## full speed mode

|                | PARAMETER                         | TEST CONDITIONS           | MIN | MAX | UNIT |

|----------------|-----------------------------------|---------------------------|-----|-----|------|

| t <sub>r</sub> | Transition rise time for DP or DM | See Figure 1 and Figure 2 | 4   | 20  | ns   |

| t <sub>f</sub> | Transition fall time for DP or DM | See Figure 1 and Figure 2 | 4   | 20  | ns   |

| t(RFM)         | Rise/fall time matching           | $(t_f/t_f) \times 100$    | 90  | 110 | %    |

| VO(CRS)        | Signal crossover output voltage   |                           | 1.3 | 2.0 | V    |

## low speed mode

| PARAMETER      |                                   | TEST CONDITIONS                                             | MIN | MAX | UNIT |

|----------------|-----------------------------------|-------------------------------------------------------------|-----|-----|------|

| t <sub>r</sub> | Transition rise time for DP to DM | C <sub>L</sub> = 50 pF to 350 pF, See Figure 1 and Figure 2 | 75  | 300 | ns   |

| tf             | Transition fall time for DP to DM | C <sub>L</sub> = 50 pF to 350 pF, See Figure 1 and Figure 2 | 75  | 300 | ns   |

| t(RFM)         | Rise/fall time matching           | $(t_f/t_f) \times 100$                                      | 80  | 120 | %    |

| VO(CRS)        | Signal crossover output voltage   | C <sub>L</sub> = 50 pF to 350 pF                            | 1.3 | 2.0 | V    |

Figure 1. Differential Driver Switching Load

Figure 2. Differential Driver Timing Waveforms

Figure 3. Differential Receiver Input Sensitivity vs. Common Mode Input Range

Figure 4. Single-Ended Receiver Input Signal Parameter Definitions

## **USB** design notes

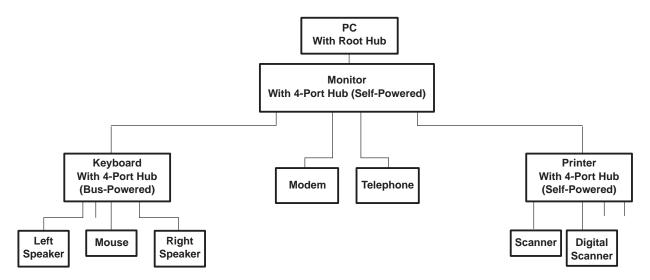

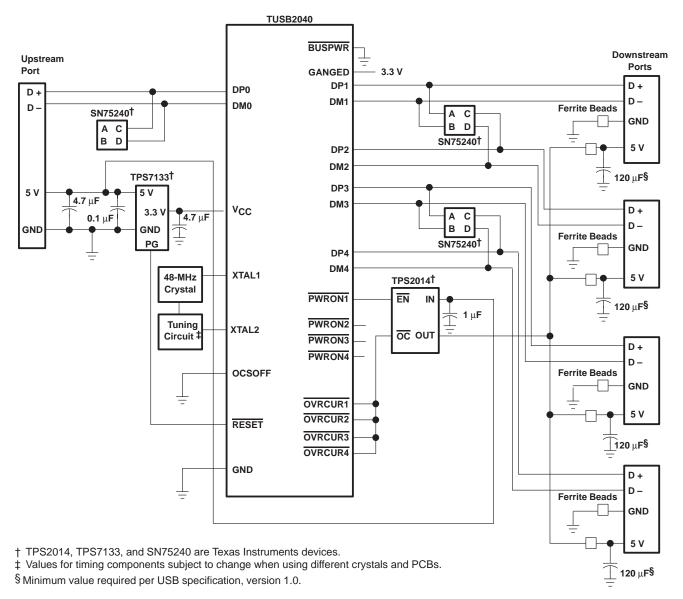

The USB is a serial bus interface providing power and data to peripheral functions that include printers, monitors, joysticks, mice, keyboards and hubs. The USB specifies three power modes for functions: low-power, high-power, and self-powered. Low-power functions may draw a maximum current of 100 mA from the USB 5-V line. High-power functions may draw a maximum current of 500 mA from the USB 5-V line and may only be connected to self-powered hubs. Self-powered functions contain their own power supply, but are permitted a maximum current draw of 100 mA from the USB 5-V line for communication purposes. (A typical application of the TUSB2040 universal serial bus hub is shown in Figure 5).

All USB data lines must be terminated with 22- $\Omega$  resistors. All downstream port data lines (DM1 – DM4, DP1 – DP4) must be pulled down with 15-k $\Omega$  resistors. DP0 must be pulled up with a 1.5-k $\Omega$  resistor (see Figure 1).

<sup>†</sup> Values for timing components are subject to change when using different crystals and PCBs-

Figure 5. Typical Application of the TUSB2040 USB Hub

NOTES: C. When tuning the crystal (Y1) for different board implementations, the capacitor (C67) is subject to change. Other components should remain the same. **Figure 6. Tuning Circuit**

<sup>&</sup>lt;sup>‡</sup> The crystal in this application is a 48–MHz US Crystal, P/N HC–18/U 48MHZ.

<sup>§</sup> BUSPWR input should be set according to the system power source. If self-powered, the local ground is tied to the USB ground.

<sup>¶</sup> Pin numbers in parentheses are for TQFP package only.

A major advantage of USB is the ability to connect 127 functions configured in up to 6 logical layers (tiers) to a single personal computer (See Figure 7).

Figure 7. USB Tiered Configuration Example

Another advantage of USB is that all peripherals are connected using a standardized 4-wire cable which provides both communication and power distribution. The three power configurations are Bus-Powered, Self-Power and High-Power mode. For all three configurations, 100 mA is the maximum current that may be drawn from the USB 5 V line during power-up. For Bus-Power mode, a hub can draw a maximum of 500 mA from the 5 V line of the USB cable. A Bus-Powered hub must always be connected downstream to a Self-Powered hub unless it is the only hub connected to the PC and there are no High-Powered functions connected downstream. In the Self-Power mode, the hub is connected to its own power supply and can supply up to 500 mA to each downstream port. High-Powered functions may draw a maximum of 500 mA and may only be connected downstream to Self-Powered hubs.

Both Bus-Powered and Self-Powered hubs require over-current protection for all downstream ports. The two types of protection are individual port management (individual port basis) or ganged port management (multiple port basis). Individual port management requires power management devices for each individual downstream port, but adds robustness to your USB system because, in the event of an over-current condition, the USB Host will only power-down the port that has the condition. The ganged configuration uses fewer power management devices and thus has lower system costs, but in the event of an over-current condition on any of the downstream ports, all the ganged ports will be disabled by the USB Host.

Using a combination of the BUSPWR and GANGED inputs, the TUSB2140 supports four modes of power management: Bus-Powered hub with either individual port power management or ganged port power management and the Self-Powered hub with either individual port power management or ganged port power management. Texas Instruments supplies the complete hub solution because we offer this TUSB2040, the TUSB2070 (7–port) and the TUSB2140 (4-port with I<sup>2</sup>C) hubs along with the power management chips needed to implement a fully USB Specification 1.0 compliant system. See Figure 8, 9 and 10 for example configurations.

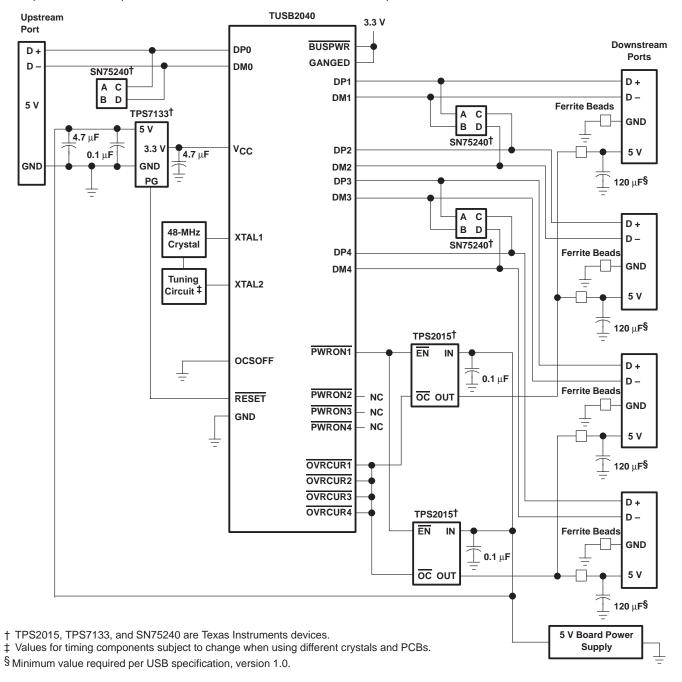

## bus-powered hub, ganged port power management

A bus-powered TUSB2040 supports up to four downstream ports (operation shown in Figure 8) and is capable of supplying 100 mA of current for low-power device class functions to each downstream port. Bus-powered hubs must implement power switching. Ganged power management (see Figure 8) utilizes the TPS2014 power switch device and provides overcurrent protection for downstream ports. Individual SN75240 transient suppressors reduce in-rush current and voltage spikes. The TPS7133 low-dropout voltage regulator provides a Power Good (PG) signal for reset at power-up.  $\overline{\text{OVRCUR1}} - \overline{\text{OVRCUR4}}$  inputs may be tied together for ganged mode operation.

Figure 8. TUSB2040 Bus-Powered Hub, Ganged Port Power Management Application

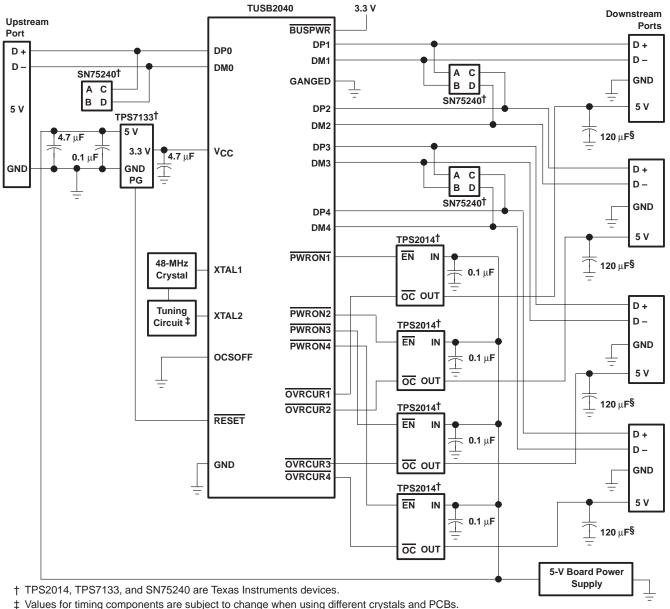

## self-powered hub, ganged port power management

A self-powered TUSB2040 can also be implemented using ganged port power management. This implementation is similiar to the individual power management except one TPS2015 provides power switching and overcurrent protection for two ports. Although this is a more economical solution, a fault on one downstream port will cause power to be removed from both downstream ports.

Figure 9. TUSB2040 Self-Powered Hub, Ganged Port Power Management Application

## self-powered hub, individual port power management

A self-powered TUSB2040 is capable of supplying 500 mA of current for low-power or high-power device class functions to each downstream port. Self-powered hubs are required to implement overcurrent protection. Individual-port power management (see Figure 10) utilizes the TPS2014 power switching and overcurrent protection that provide maximum robustness to the hub system. When the hub detects a downstream port fault, power is removed from the faulty port only, thus allowing other ports to continue normal operation. Individual SN75240 transient suppressors reduce in-rush current and voltage spikes. The TPS7133 Low-Dropout regulator provides a Power-Good (PG) signal for reset at power-up.

§ Minimum value required per USB specification, version 1.0.

Figure 10. TUSB2040 Self-Powered Hub, Individual-Port Power Management Application

SLLS260B - NOVEMBER 1996 - REVISED AUGUST 1997

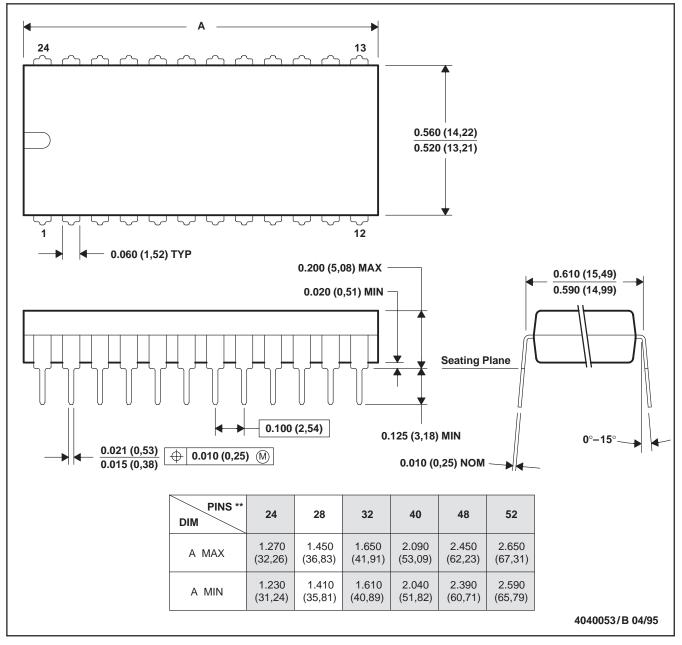

#### **MECHANICAL DATA**

## N (R-PDIP-T\*\*)

#### 24 PIN SHOWN

## PLASTIC DUAL-IN-LINE PACKAGE

NOTES: A. All linear dimensions are in inches (millimeters).

- B. This drawing is subject to change without notice.

- C. Falls within JEDEC MS-011

- D. Falls within JEDEC MS-015 (32-pin only)

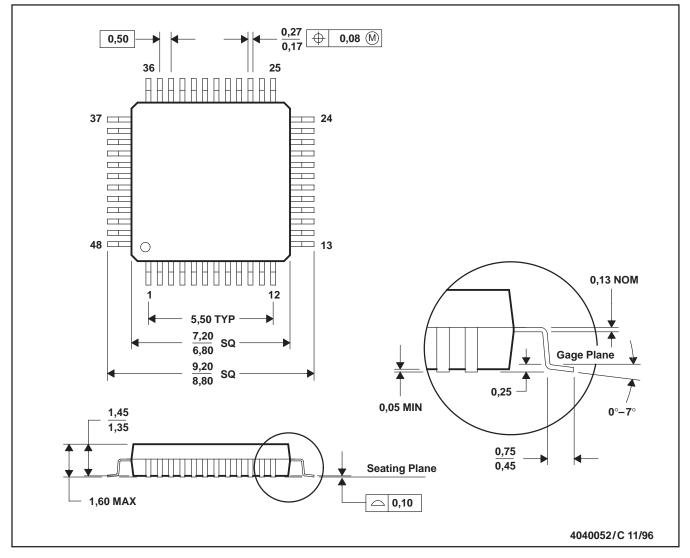

## **MECHANICAL DATA**

## PT (S-PQFP-G48)

#### PLASTIC QUAD FLATPACK

NOTES: A. All linear dimensions are in millimeters.

- B. This drawing is subject to change without notice.

- C. Falls within JEDEC MS-026

- D. This may also be a thermally enhanced plastic package with leads conected to the die pads.

#### **IMPORTANT NOTICE**

Texas Instruments (TI) reserves the right to make changes to its products or to discontinue any semiconductor product or service without notice, and advises its customers to obtain the latest version of relevant information to verify, before placing orders, that the information being relied on is current and complete.

TI warrants performance of its semiconductor products and related software to the specifications applicable at the time of sale in accordance with TI's standard warranty. Testing and other quality control techniques are utilized to the extent TI deems necessary to support this warranty. Specific testing of all parameters of each device is not necessarily performed, except those mandated by government requirements.

Certain applications using semiconductor products may involve potential risks of death, personal injury, or severe property or environmental damage ("Critical Applications").

TI SEMICONDUCTOR PRODUCTS ARE NOT DESIGNED, INTENDED, AUTHORIZED, OR WARRANTED TO BE SUITABLE FOR USE IN LIFE-SUPPORT APPLICATIONS, DEVICES OR SYSTEMS OR OTHER CRITICAL APPLICATIONS.

Inclusion of TI products in such applications is understood to be fully at the risk of the customer. Use of TI products in such applications requires the written approval of an appropriate TI officer. Questions concerning potential risk applications should be directed to TI through a local SC sales office.

In order to minimize risks associated with the customer's applications, adequate design and operating safeguards should be provided by the customer to minimize inherent or procedural hazards.

TI assumes no liability for applications assistance, customer product design, software performance, or infringement of patents or services described herein. Nor does TI warrant or represent that any license, either express or implied, is granted under any patent right, copyright, mask work right, or other intellectual property right of TI covering or relating to any combination, machine, or process in which such semiconductor products or services might be or are used.

Copyright © 1998, Texas Instruments Incorporated