# 82540EP Gigabit Ethernet Controller

#### **Networking Silicon**

#### **Datasheet**

#### **Product Features**

- PCI Bus

- PCI Revision 2.3 support for 32-bit wide interface at 33 MHz and 66 MHz

- Algorithms that optimally use advanced PCI, MWI, MRM, and MRL commands

- CardBus Information Services (CIS) Pointer

- CLK\_RUN# Signal

- MAC Specific

- Low-latency transmit and receive queues

- IEEE 802.3x-compliant flow-control support with software-controllable thresholds

- Caches up to 64 packet descriptors in a single burst

- Programmable host memory receive buffers (256 B to 16 KB) and cache line size (16 B to 256 B)

- Wide, optimized internal data path architecture

- 64 KB configurable Transmit and Receive FIFO buffers

- PHY Specific

- Integrated for 10/100/1000 Mb/s operation

- IEEE 802.3ab Auto-Negotiation support

- IEEE 802.3ab PHY compliance and compatibility. State-of-the-art DSP architecture implements digital adaptive equalization, echo cancellation, and crosstalk cancellation

- Automatic detection of cable lengths and MDI vs. MDI-X cable at all speeds

- Host Off-Loading

- Transmit and receive IP, TCP, and UDP checksum off-loading capabilities

- Transmit TCP segmentation

- Advanced packed filtering

- —Jumbo frame support up to 16 KB

- IEEE 802.1q VLAN support with VLAN tag insertion, stripping and packet filtering for up to 4096 VLAN tags

- Descriptor ring management hardware for transmit and receive

- Interrupt coalescing (multiple packets per interrupt)

- Manageability

- Manageability features: Onboard SMB port, ASF 1.0, ACPI, Wake on LAN, and PXE

- Compliance with PCI Power Management 1.1 and ACPI 2.0 register set compliant

- SNMP and RMON statistic counters

- SDG 3.0, WfM 2.0, and PC2001 compliance

- Additional Device

- Four activity and link indication outputs that directly drive LEDs

- JTAG (IEEE 1149.1) Test Access Port built in silicon

- Internal PLL for clock generation can use a 25 MHz crystal

- Programmable LED functionality

- Industrial temperature support (-40 to +85 °C)

INFORMATION IN THIS DOCUMENT IS PROVIDED IN CONNECTION WITH INTEL PRODUCTS. NO LICENSE, EXPRESS OR IMPLIED, BY ESTOPPEL OR OTHERWISE, TO ANY INTELLECTUAL PROPERTY RIGHTS IS GRANTED BY THIS DOCUMENT. EXCEPT AS PROVIDED IN INTEL'S TERMS AND CONDITIONS OF SALE FOR SUCH PRODUCTS, INTEL ASSUMES NO LIABILITY WHATSOEVER, AND INTEL DISCLAIMS ANY EXPRESS OR IMPLIED WARRANTY, RELATING TO SALE AND/OR USE OF INTEL PRODUCTS INCLUDING LIABILITY OR WARRANTIES RELATING TO FITNESS FOR A PARTICULAR PURPOSE, MERCHANTABILITY, OR INFRINGEMENT OF ANY PATENT, COPYRIGHT OR OTHER INTELLECTUAL PROPERTY RIGHT.

Intel products are not intended for use in medical, life saving, or life sustaining applications.

Intel may make changes to specifications and product descriptions at any time, without notice.

Designers must not rely on the absence or characteristics of any features or instructions marked "reserved" or "undefined." Intel reserves these for future definition and shall have no responsibility whatsoever for conflicts or incompatibilities arising from future changes to them.

The Intel products referenced in this document may contain design defects or errors known as errata which may cause the product to deviate from published specifications. Current characterized errata are available on request.

Contact your local Intel sales office or your distributor to obtain the latest specifications and before placing your product order.

Copies of documents which have an ordering number and are referenced in this document, or other Intel literature, may be obtained from:

Intel Corporation P.O. Box 5937 Denver, CO 80217-9808

or call in North America 1-800-548-4725, Europe 44-0-1793-431-155, France 44-0-1793-421-777, Germany 44-0-1793-421-333, other Countries 708-

Intel® is a trademark or registered trademark of Intel Corporation or its subsidiaries in the United States and other countries.

\*Other names and brands may be claimed as the property of others.

Copyright © Intel Corporation, 2002-2007

# Revision History

| Date      | Revision | Notes                                                                                                                                                                            |

|-----------|----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Apr 2002  | 0.25     | Initial Release                                                                                                                                                                  |

| Nov 2002  | 1.0      | Changed document status to Intel Confidential.                                                                                                                                   |

| Jan 2003  | 1.1      | Section 1.0. Replaced Block Diagram                                                                                                                                              |

|           |          | Section 2.6. Added Table footnote                                                                                                                                                |

|           |          | Section 4.1, 4.2, 4.3. Replaced tables                                                                                                                                           |

|           |          | Section 5.1. Added Visual Pin Reference                                                                                                                                          |

|           |          | Section 4.4 Removed Power Supply Characteristics; added note to I/O Characteristics                                                                                              |

|           |          | Section 5.0 Replaced Pinout Diagram                                                                                                                                              |

| Apr 2003  | 1.2      | Removed confidential status.                                                                                                                                                     |

|           |          | Section 1.0. Added product ordering code.                                                                                                                                        |

| Oct 2003  | 1.3      | Updated Table 8 to reflect correct values for internal pull-up impedance.                                                                                                        |

| Nov 2004  | 1.4      | Added product features to cover.                                                                                                                                                 |

|           |          | Updated signal names to match design guide and reference schematics.                                                                                                             |

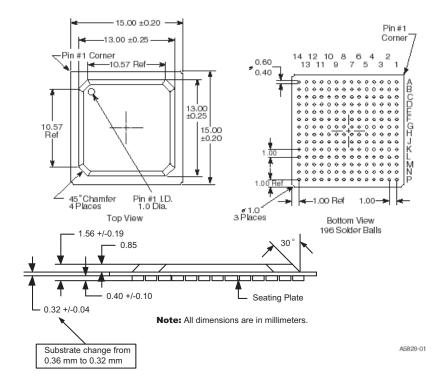

| Nov 2004  | 1.5      | Added information about migrating from a 2-layer 0.36 mm wide-trace substrate to a 2-layer 0.32 mm wide-trace substrate. Refer to the section on Package and Pinout Information. |

|           |          | Added statement that no changes to existing soldering processes are needed for the 2-layer 0.32 mm wide-trace substrate change in the section describing "Package Information".  |

|           |          | Corrected pinout discrepancies between Tables 35 and 36.                                                                                                                         |

| July 2006 | 1.6      | Added LAN-disable description to the FLSH_SO signal description in Section 3.                                                                                                    |

| Sept 2006 | 1.7      | Added industrial temperature values to "Product Features" and Table 2.                                                                                                           |

|           |          | Added a note to Figure 12 clarifying the device pin 1 location.                                                                                                                  |

| Feb 2007  | 1.8      | Updated Section 5.3 "Thermal Specifications".                                                                                                                                    |

| Sept 2007 | 1.9      | Updated ball G13 description to 1.5V. Updated Figure 12 (changed G13 description to 1.5V).                                                                                       |

#### 82540EP — Networking Silicon

Note: This page intentionally left blank.

# Contents

| 1.0        | Intro   | duction                                         | 1                |

|------------|---------|-------------------------------------------------|------------------|

| 1.1        | Docum   | nent Scope                                      | 1                |

| 1.2        |         | ence Documents                                  |                  |

| 1.3        | Block [ | Diagram                                         | 3                |

| 2.0        | Produ   | uct Code                                        | 5                |

| 3.0        | Signa   | al Descriptions                                 | 7                |

| 3.1        | Signal  | Type Definitions                                | 7                |

| 3.2        |         | us Interface                                    |                  |

| 0.2        | 3.2.1   | PCI Address, Data and Control Signals           |                  |

|            | 3.2.2   | Arbitration Signals                             |                  |

|            | 3.2.3   | Interrupt Signal                                |                  |

|            | 3.2.4   | System Signals                                  |                  |

|            | 3.2.5   | Error Reporting Signals                         |                  |

|            | 3.2.6   | Power Management Signals                        |                  |

|            | 3.2.7   | Impedance Compensation Signals                  |                  |

|            | 3.2.8   | SMB Signals                                     |                  |

| 3.3        | EEPR(   | OM and Serial FLASH Interface Signals           |                  |

| 3.4        |         | llaneous Signals                                |                  |

|            | 3.4.1   | LED Signals                                     |                  |

|            | 3.4.2   | Other Signals                                   | 11               |

| 3.5        | PHY S   | Signals                                         | 12               |

|            | 3.5.1   | Crystal Signals                                 | 12               |

|            | 3.5.2   | Analog Signals                                  | 12               |

| 3.6        | Test In | nterface Signals                                | 13               |

| 3.7        | Power   | Supply Connections                              |                  |

|            | 3.7.1   | Digital Supplies                                |                  |

|            | 3.7.2   | Analog Supplies                                 | 13               |

|            | 3.7.3   | Ground and No Connects                          |                  |

|            | 3.7.4   | Control Signals                                 | 14               |

| 4.0        | Volta   | ge, Temperature, and Timing Specifications      | 15               |

| 4.1        | ∧ boolu | uto Mayimum Datinga                             | 15               |

| 4.1<br>4.2 | Poson   | ute Maximum Ratingsnmended Operating Conditions | 15<br>1 <i>5</i> |

| 4.2<br>4.3 |         | pecifications                                   |                  |

| 4.3<br>4.4 |         | paracteristics                                  |                  |

| 4.4<br>4.5 |         | g Specifications                                | _                |

| ٦.٥        | 4.5.1   | PCI Bus Interface                               |                  |

|            | 4.5.1   | Link Interface Timing                           |                  |

|            | 4.5.2   | EEPROM Interface                                |                  |

|            | 4.3.3   | LLF NOW INCHASE                                 | ∠5               |

### 82540EP — Networking Silicon

| 5.0 | Package and Pinout Information | 27 |

|-----|--------------------------------|----|

| 5.1 | Device Identification          | 27 |

| 5.2 | Package Information            | 28 |

| 5.3 | Thermal Specifications         | 29 |

|     | Pinout Information             |    |

| 5.5 | Visual Pin Reference           | 39 |

#### 1.0 Introduction

The Intel® 82540EP Gigabit Ethernet Controller is a single, compact component with an integrated Gigabit Ethernet Media Access Control (MAC) and physical layer (PHY) functions. For desktop, workstation and mobile PC Network designs with critical space constraints, the Intel® 82540EP allows for a Gigabit Ethernet implementation in a very small area that is footprint compatible with current generation 10/100 Mbps Fast Ethernet designs

The Intel<sup>®</sup> 82540EP integrates Intel's fourth generation gigabit MAC design with fully integrated, physical layer circuitry to provide a standard IEEE 802.3 Ethernet interface for 1000BASE-T, 100BASE-TX, and 10BASE-T applications (802.3, 802.3u, and 802.3ab). The controller is capable of transmitting and receiving data at rates of 1000 Mbps, 100 Mbps, or 10 Mbps. In addition to managing MAC and PHY layer functions, the controller provides a 32-bit wide direct Peripheral Component Interconnect (PCI) 2.2 compliant interface capable of operating at 33 or 66 MHz.

The 82540EP also incorporates the CLK\_RUN# protocol and hardware supported downshift capability to two or three-pair 100 Mb/s operation. These features optimize mobile applications.

The Intel® 82540EP's on-board System Management Bus (SMB) port enables network manageability implementations required by information technology personnel for remote control and alerting via the LAN. With SMB, management packets can be routed to or from a management processor. The SMB port enables industry standards, such as Intelligent Platform Management Interface (IPMI) and Alert Standard Forum (ASF), to be implemented using the 82540EP. In addition, on chip ASF 1.0 circuitry provides alerting and remote control capabilities with standardized interfaces.

The 82540EP Gigabit Ethernet Controller architecture is designed to deliver high performance and PCI bus efficiency. Wide internal data paths eliminate performance bottlenecks by efficiently handling large address and data words. The 82540EP controller includes advanced interrupt handling features to limit PCI bus traffic and a PCI interface that maximizes the use of bursts for efficient bus usage. The 82540EP caches up to 64 packet descriptors in a single burst for efficient PCI bandwidth use. A large 64 KByte on-chip packet buffer maintains superior performance as available PCI bandwidth changes. In addition, using hardware acceleration, the controller offloads tasks from the host controller, such as TCP/UDP/IP checksum calculations and TCP segmentation.

The 82540EP is packaged in a 15 mm<sup>2</sup> 196-ball grid array and is pin compatible with both the 82551QM 10/100 Mbps Fast Ethernet Multifunction PCI/CardBus Controller and the 82540EM Gigabit Ethernet Controller (which does not have added power saving features like CLK\_RUN#).

### 1.1 Document Scope

This document contains datasheet specifications for the 82540EP Gigabit Ethernet Controller, including signal descriptions, DC and AC parameters, packaging data, and pinout information.

#### 1.2 Reference Documents

This application assumes that the designer is acquainted with high-speed design and board layout techniques. The following documents provide additional information:

- 82544EI/82544GC Gigabit Ethernet Controller Software Developer's Manual, Revision 0.25, Intel Corporation.

- PCI Local Bus Specification, Revision 2.3, PCI Special Interest Group.

- PCI Bus Power Management Interface Specification, Rev. 1.1, PCI Special Interest Group.

- IEEE Standard 802.3, 1996 Edition, Institute of Electrical and Electronics Engineers (IEEE).

- IEEE Standard 802.3u, 1995 Edition, Institute of Electrical and Electronics Engineers (IEEE).

- IEEE Standard 802.3x, 1997 Edition, Institute of Electrical and Electronics Engineers (IEEE).

- IEEE Standard 802.3z, 1998 Edition, Institute of Electrical and Electronics Engineers (IEEE).

- IEEE Standard 802.3ab, 1999 Edition, Institute of Electrical and Electronics Engineers (IEEE).

- Intel Ethernet Controllers Timing Device Selection Guide, AP-419, Intel Corporation.

- PCI Mobile Design Guide, Rev. 1.1, PCI Special Interest Group

- 82540EP/82541(PI/GI/EI) & 82562EZ(EX) Dual Footprint Design Guide, AP-444. Intel Corporation.

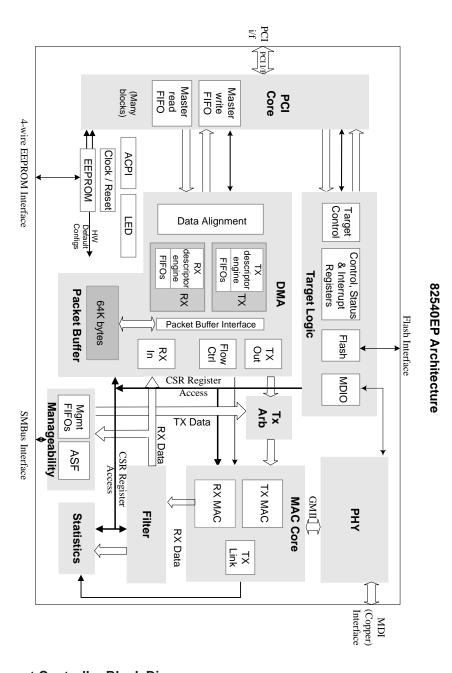

# 1.3 Block Diagram

Figure 1. Gigabit Ethernet Controller Block Diagram

### 82540EP — Networking Silicon

*Note:* This page is intentionally left blank.

# 2.0 Product Code

The product ordering code for the 82540EP is: RC82540EP.

### 82540EP — Networking Silicon

*Note:* This page intentionally left blank.

# 3.0 Signal Descriptions

**Note:** The targeted signal names are subject to change without notice. Verify with your local Intel sales office that you have the latest information before finalizing a design.

### 3.1 Signal Type Definitions

The signals of the 82540EP controller are electrically defined as follows:

| Name | Definition                                                                                                                                                                                                                                                                                                                        |

|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| I    | Input. Standard input only digital signal.                                                                                                                                                                                                                                                                                        |

| 0    | Output. Standard output only digital signal.                                                                                                                                                                                                                                                                                      |

| TS   | Tri-state. Bi-directional three-state digital input/output signal.                                                                                                                                                                                                                                                                |

| STS  | Sustained Tri-state. Sustained digital three-state signal driven by one agent at a time.  An agent driving the STS pin low must actively drive it high for at least one clock before letting it float. The next agent of the signal cannot drive the pin earlier than one clock after it has been released by the previous agent. |

| OD   | Open Drain. Wired-OR with other agents.  The signaling agent asserts the OD signal, but the signal is returned to the inactive state by a weak pull-up resistor. The pull-up resistor may require two or three clock periods to fully restore the signal to the de-asserted state.                                                |

| Α    | Analog. PHY analog data signal.                                                                                                                                                                                                                                                                                                   |

| Р    | Power. Power connection, voltage reference, or other reference connection.                                                                                                                                                                                                                                                        |

#### 3.2 PCI Bus Interface

When the Reset signal (RST#) is asserted, the 82540EP will not drive any PCI output or bidirectional pins except the Power Management Event signal (PME#).

#### 3.2.1 PCI Address, Data and Control Signals

| Туре | Name and Function                                                                                                                                                                                                                                                                                     |

|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| TS   | Address and Data. Address and data signals are multiplexed on the same PCI pins. A bus transaction includes an address phase followed by one or more data phases.                                                                                                                                     |

|      | The address phase is the clock cycle when the Frame signal (FRAME#) is asserted low. During the address phase AD[31:0] contain a physical address (32 bits). For I/O, this is a byte address, and for configuration and memory, a DWORD address. The 82540EP device uses little endian byte ordering. |

|      | During data phases, AD[7:0] contain the least significant byte (LSB) and AD[31:24] contain the most significant byte (MSB).                                                                                                                                                                           |

|      |                                                                                                                                                                                                                                                                                                       |

| Symbol     | Туре | Name and Function                                                                                                                                                                                                                                                                                                                                                                                                                  |

|------------|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| C/BE#[3:0] | TS   | Bus Command and Byte Enables. Bus command and byte enable signals are multiplexed on the same PCI pins. During the address phase of a transaction, C/BE#[3:0] define the bus command. In the data phase, C/BE#[3:0] are used as byte enables. The byte enables are valid for the entire data phase and determine which byte lanes contain meaningful data.  C/BE#[0] applies to byte 0 (LSB) and C/BE#[3] applies to byte 3 (MSB). |

|            |      | Parity. The Parity signal is issued to implement even parity across AD[31:0] and C/                                                                                                                                                                                                                                                                                                                                                |

| PAR        | TS   | BE#[3:0]. PAR is stable and valid one clock after the address phase. During data phases, PAR is stable and valid one clock after either IRDY# is asserted on a write transaction or TRDY# is asserted after a read transaction. Once PAR is valid, it remains valid until one clock after the completion of the current data phase.                                                                                                |

|            |      | When the 82540EP controller is a bus master, it drives PAR for address and write data phases, and as a slave device, drives PAR for read data phases.                                                                                                                                                                                                                                                                              |

| FRAME#     | STS  | <b>Cycle Frame.</b> The Frame signal is driven by the 82540EP device to indicate the beginning and length of an access and indicate the beginning of a bus transaction. While FRAME# is asserted, data transfers continue. FRAME# is de-asserted when the transaction is in the final data phase.                                                                                                                                  |

| IRDY#      | STS  | Initiator Ready. Initiator Ready indicates the ability of the 82540EP controller (as bus master device) to complete the current data phase of the transaction. IRDY# is used in conjunction with the Target Ready signal (TRDY#). The data phase is completed on any clock when both IRDY# and TRDY# are asserted.                                                                                                                 |

| INDT#      |      | During the write cycle, IRDY# indicates that valid data is present on AD[31:0]. For a read cycle, it indicates the master is ready to accept data. Wait cycles are inserted until both IRDY# and TRDY# are asserted together. The 82540EP controller drives IRDY# when acting as a master and samples it when acting as a slave.                                                                                                   |

| TRDY#      | STS  | Target Ready. The Target Ready signal indicates the ability of the 82540EP controller (as a selected device) to complete the current data phase of the transaction. TRDY# is used in conjunction with the Initiator Ready signal (IRDY#). A data phase is completed on any clock when both TRDY# and IRDY# are sampled asserted.                                                                                                   |

|            |      | During a read cycle, TRDY# indicates that valid data is present on AD[31:0]. For a write cycle, it indicates the target is ready to accept data. Wait cycles are inserted until both IRDY# and TRDY# are asserted together. The 82540EP device drives TRDY# when acting as a slave and samples it when acting as a master.                                                                                                         |

| STOP#      | STS  | <b>Stop.</b> The Stop signal indicates the current target is requesting the master to stop the current transaction. As a slave, the 82540EP controller drives STOP# to request the bus master to stop the transaction. As a master, the 82540EP controller receives STOP# from the slave to stop the current transaction.                                                                                                          |

| IDSEL#     | I    | Initialization Device Select. The Initialization Device Select signal is used by the 82540EP as a chip select signal during configuration read and write transactions.                                                                                                                                                                                                                                                             |

| DEVSEL#    | STS  | <b>Device Select.</b> When the Device Select signal is actively driven by the 82540EP, it signals notifies the bus master that it has decoded its address as the target of the current access. As an input, DEVSEL# indicates whether any device on the bus has been selected.                                                                                                                                                     |

| VIO        | Р    | <b>VIO.</b> The VIO signal is a voltage reference for the PCI interface (3.3 V or 5 V PCI signaling environment). It is used as the clamping voltage.                                                                                                                                                                                                                                                                              |

| VIO        | P    | Note: An external resistor is required between the voltage reference and the VIO pin. The target resistor value is 100 K $\Omega$                                                                                                                                                                                                                                                                                                  |

# 3.2.2 Arbitration Signals

| Symbol | Туре | Name and Function                                                                                                                                                                                           |

|--------|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| REQ#   | TS   | <b>Request Bus.</b> The Request Bus signal is used to request control of the bus from the arbiter. This signal is point-to-point.                                                                           |

| GNT#   | I    | <b>Grant Bus.</b> The Grant Bus signal notifies the 82540EP that bus access has been granted. This is a point-to-point signal.                                                                              |

| LOCK#  | I    | <b>Lock Bus.</b> The Lock Bus signal is asserted by an initiator to require sole access to a target memory device during two or more separate transfers. The 82540EP device does not implement bus locking. |

# 3.2.3 Interrupt Signal

| Symbol | Туре | Name and Function                                                                                                                                |

|--------|------|--------------------------------------------------------------------------------------------------------------------------------------------------|

| INTA#  | TS   | <b>Interrupt A.</b> Interrupt A is used to request an interrupt by port 1 of the 82540EP. It is an active low, level-triggered interrupt signal. |

# 3.2.4 System Signals

| Symbol   | Туре      | Name and Function                                                                                                                                                                                                                                                                                                              |

|----------|-----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CLK      | 1         | <b>PCI Clock.</b> The PCI Clock signal provides timing for all transactions on the PCI bus and is an input to the 82540EP device. All other PCI signals, except the Interrupt A (INTA#) and PCI Reset signal (RST#), are sampled on the rising edge of CLK. All other timing parameters are defined with respect to this edge. |

| M66EN    | I         | 66 MHz Enable. M66EN indicates whether the system bus is enabled for 66 MHz.                                                                                                                                                                                                                                                   |

| RST#     | 1         | PCI Reset. When the PCI Reset signal is asserted, all PCI output signals, except the Power Management Event signal (PME#), are floated and all input signals are ignored. The PME# context is preserved, depending on power management settings.                                                                               |

|          |           | Most of the internal state of the 82540EP is reset on the de-assertion (rising edge) of RST#.                                                                                                                                                                                                                                  |

| CLK_RUN# | I/O<br>OD | Clock Run. This signal is used by the system to pause the PCI clock signal. It is used by the 82540EP controller to request the PCI clock. When the CLK_RUN# feature is disabled, leave this pin unconnected.                                                                                                                  |

# 3.2.5 Error Reporting Signals

| Symbol | Туре | Name and Function                                                                                                                                                                                                                                                                                                                                                                                  |

|--------|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SERR#  | OD   | <b>System Error.</b> The System Error signal is used by the 82540EP controller to report address parity errors. SERR# is open drain and is actively driven for a single PCI clock when reporting the error.                                                                                                                                                                                        |

| PERR#  | STS  | Parity Error. The Parity Error signal is used by the 82540EP controller to report data parity errors during all PCI transactions except by a Special Cycle. PERR# is sustained tri-state and must be driven active by the 82540EP controller two data clocks after a data parity error is detected. The minimum duration of PERR# is one clock for each data phase a data parity error is present. |

# 3.2.6 Power Management Signals

| Symbol               | Туре | Name and Function                                                                                                                                                                                                                                                                |

|----------------------|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| LAN_<br>PWR_<br>GOOD | 1    | <b>Power Good (Power-on Reset).</b> The Power Good signal is used to indicate that stable power is available for the 82540EP. When the signal is low, the 82540EP holds itself in reset state and floats all PCI signals.                                                        |

| PME#                 | OD   | Power Management Event. The 82540EP device drives this signal low when it receives a wake-up event and either the PME Enable bit in the Power Management Control/Status Register or the Advanced Power Management Enable (APME) bit of the Wake-up Control Register (WUC) is 1b. |

| AUX_PWR              | I    | <b>Auxiliary Power.</b> If the Auxiliary Power signal is high, then auxiliary power is available and the 82540EP device should support the D3cold power state.                                                                                                                   |

# 3.2.7 Impedance Compensation Signals

| Symbol  | Туре | Name and Function                                                                                                                                                                                                                                                               |

|---------|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ZN_COMP | I/O  | N Device Impedance Compensation. This signal should be connected to an external precision resistor (to VDD) that is indicative of the PCI trace load. This cell is used to dynamically determine the drive strength required on the N-channel transistors in the PCI I/O cells. |

| ZP_COMP | I/O  | P Device Impedance Compensation. This signal should be connected to an external precision resistor (to VSS) that is indicative of the PCI trace load. This cell is used to dynamically determine the drive strength required on the P-channel transistors in the PCI I/O cells. |

### 3.2.8 SMB Signals

| Symbol         | Туре | Name and Function                                                                 |

|----------------|------|-----------------------------------------------------------------------------------|

| SMBCLK         | I/O  | SMB Clock. The SMB Clock signal is an open drain signal for serial SMB interface. |

| SMBDATA        | I/O  | SMB Data. The SMB Data signal is an open drain signal for serial SMB interface.   |

| SMB_<br>ALERT# | 0    | SMB Alert. The SMB Alert signal is open drain for serial SMB interface.           |

# 3.3 EEPROM and Serial FLASH Interface Signals

| Symbol | Туре | Name and Function                                                                                                                                |

|--------|------|--------------------------------------------------------------------------------------------------------------------------------------------------|

| EEDI   | 0    | <b>EEPROM Data Input.</b> The EEPROM Data Input pin is used for output to the memory device.                                                     |

| EEDO   | I    | <b>EEPROM Data Output.</b> The EEPROM Data Output pin is used for input from the memory device. The EE_DO includes an internal pull-up resistor. |

| EECS   | 0    | <b>EEPROM Chip Select.</b> The EEPROM Chip Select signal is used to enable the device.                                                           |

| EESK   | 0    | <b>EEPROM Serial Clock.</b> The EEPROM Shift Clock provides the clock rate for the EEPROM interface, which is approximately 1 MHz.               |

| Symbol  | Туре | Name and Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|---------|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| FL_CE#  | 0    | FLASH Chip Enable Output. Used to enable FLASH device.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| FL_SCK  | 0    | FLASH Serial Clock Output. The clock rate of the serial FLASH interface is approximately 1 MHz.                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| FL_SI   | 0    | FLASH Serial Data Input. This pin is an output to the memory device.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| FLSH_SO | I    | <b>FLASH Serial Data Output.</b> This pin is an input from the FLASH memory. <b>Note:</b> The 82540EP LAN-disable mechanism is implemented using this pin. It is generally used when no Flash device is present (Flash disabled). If this pin is 1b (Vcc) then the 82540EP is enabled. If the pin is 0b (Vss) then the 82540EP is disabled. This signal should be sampled within 1μs of the rising edge of LAN_PWR_GOOD and PCI_RST_N. Note that this pin also has an internal pull-up that is sufficient enough to enable the 82540EP if no Flash device is present. |

**Note:** If the LAN-disable feature is used when a Flash device is present, then care must be taken by system designers not to drive the FLSH\_SO pin while the Flash device is driving it.

# 3.4 Miscellaneous Signals

# 3.4.1 LED Signals

| Symbol    | Туре | Name and Function                                                                                                |

|-----------|------|------------------------------------------------------------------------------------------------------------------|

| LINK_UP#  | 0    | <b>LED0 / LINK Up.</b> Programmable LED indication. Defaults to indicate link connectivity.                      |

| ACTIVITY# | 0    | <b>LED1 / Activity.</b> Programmable LED indication. Defaults to flash to indicate transmit or receive activity. |

| LINK100#  | 0    | <b>LED2 / LINK 100.</b> Programmable LED indication. Defaults to indicate link at 100 Mbps.                      |

| LINK1000# | 0    | <b>LED3 / LINK 1000.</b> Programmable LED indication. Defaults to indicate link at 1000 Mbps.                    |

### 3.4.2 Other Signals

| Symbol               | Туре | Name and Function                                                                                                                                                                                                                                                                                                                                                                                             |

|----------------------|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SDP[7:6]<br>SDP[1:0] | TS   | Software Defined Pins. The Software Defined Pins are reserved and programmable with respect to input and output capability. These default to input signals upon power-up but may be configured differently by the EEPROM. The upper four bits may be mapped to the General Purpose Interrupt bits if they are configured as input signals.  Note: SDP5 is not included in the group of Software Defined Pins. |

# 3.5 PHY Signals

# 3.5.1 Crystal Signals

| Symbol | Туре | Name and Function                                                                                                                                                                                      |

|--------|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| XTAL1  | 1    | <b>Crystal One.</b> The Crystal One pin is a 25 MHz +/- 30 ppm input signal. It can be connected to either an oscillator or crystal. If a crystal is used, Crystal Two (XTAL2) must also be connected. |

| XTAL2  | 0    | <b>Crystal Two.</b> Crystal Two is the output of an internal oscillator circuit used to drive a crystal into oscillation. If an external oscillator is used in the design, XTAL2 must be disconnected. |

# 3.5.2 Analog Signals

| Symbol    | Туре | Name and Function                                                                                                                                      |

|-----------|------|--------------------------------------------------------------------------------------------------------------------------------------------------------|

| REF       | Р    | <b>Reference.</b> This Reference signal should be connected to VSS through an external 2.49 K $\Omega$ resistor.                                       |

|           |      | Media Dependent Interface [0].                                                                                                                         |

|           |      | 1000BASE-T: In MDI configuration, MDI[0]+/- corresponds to BI_DA+/-, and in MDI-X configuration, MDI[0]+/- corresponds to BI_DB+/                      |

| MDI[0]+/- | Α    | <b>100BASE-TX</b> : In MDI configuration, MDI[0]+/- is used for the transmit pair, and in MDI-X configuration, MDI[0]+/- is used for the receive pair. |

|           |      | <b>10BASE-T</b> : In MDI configuration, MDI[0]+/- is used for the transmit pair, and in MDI-X configuration, MDI[0]+/- is used for the receive pair.   |

|           |      | Media Dependent Interface [1].                                                                                                                         |

|           |      | <b>1000BASE-T</b> : In MDI configuration, MDI[1]+/- corresponds to BI_DB+/-, and in MDI-X configuration, MDI[1]+/- corresponds to BI_DA+/              |

| MDI[1]+/- | А    | <b>100BASE-TX</b> : In MDI configuration, MDI[1]+/- is used for the receive pair, and in MDI-X configuration, MDI[1]+/- is used for the transit pair.  |

|           |      | <b>10BASE-T</b> : In MDI configuration, MDI[1]+/- is used for the receive pair, and in MDI-X configuration, MDI[1]+/- is used for the transit pair.    |

|           |      | Media Dependent Interface [2].                                                                                                                         |

| MDI[2]+/- | A    | 1000BASE-T: In MDI configuration, MDI[2]+/- corresponds to BI_DC+/-, and in MDI-X configuration, MDI[2]+/- corresponds to BI_DD+/                      |

|           |      | 100BASE-TX: Unused.                                                                                                                                    |

|           |      | 10BASE-T: Unused.                                                                                                                                      |

|           |      | Media Dependent Interface [3].                                                                                                                         |

| MDI[3]+/- | A    | <b>1000BASE-T</b> : In MDI configuration, MDI[3]+/- corresponds to BI_DD+/-, and in MDI-X configuration, MDI[3]+/- corresponds to BI_DC+/              |

|           |      | 100BASE-TX: Unused.                                                                                                                                    |

|           |      | 10BASE-T: Unused.                                                                                                                                      |

# 3.6 Test Interface Signals

| Symbol         | Туре | Name and Function                                                                                                                                                |

|----------------|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| JTAG_TCK       | I    | JTAG Clock.                                                                                                                                                      |

| JTAG_TDI       | I    | JTAG TDI.                                                                                                                                                        |

| JTAG_TDO       | 0    | JTAG TDO.                                                                                                                                                        |

| JTAG_TMS       | I    | JTAG TMS.                                                                                                                                                        |

| JTAG_<br>TRST# | I    | JTAG Reset. This is an active low reset signal for JTAG. This signal should be terminated using a pull-down resistor to ground. It must not be left unconnected. |

| TEST           | I    | Factory Test Pin.                                                                                                                                                |

| CLK_VIEW       | 0    | Clock View. Output for GTX_CLK and RX_CLK during IEEE PHY conformance testing. The clock is selected by register programming.                                    |

| ALTCLK 125     | I    | Alternate CLK125 Input. Factory use only.                                                                                                                        |

| ALTOLK_125     |      | For normal component operation, connect to VSS.                                                                                                                  |

| CLK BYP#       |      | Clock Bypass Enable. Factory use only.                                                                                                                           |

| OLIC_BIT#      |      | For normal component operation, no connect.                                                                                                                      |

| HSDACP         |      | PHY High Speed Test Interface. Factory use only.                                                                                                                 |

| TIODAOI        | '    | For normal component operation, no connect.                                                                                                                      |

| HSDACN         |      | PHY High Speed Test Interface. Factory use only.                                                                                                                 |

| TIODACIV       | '    | For normal component operation, no connect.                                                                                                                      |

| PHY TSTPT      |      | PHY Test Point. Factory use only.                                                                                                                                |

| FIII_ISIFI     | '    | For normal component operation, no connect.                                                                                                                      |

# 3.7 Power Supply Connections

# 3.7.1 Digital Supplies

| Symbol | Туре | Name and Function                |

|--------|------|----------------------------------|

| VDDO   | Р    | 3.3 V I/O Power Supply.          |

| DVDD   | Р    | 1.5 V Digital Core Power Supply. |

# 3.7.2 Analog Supplies

| Symbol | Туре | Name and Function          |

|--------|------|----------------------------|

| AVDDH  | Р    | 3.3 V Analog Power Supply. |

| AVDDL  | Р    | 2.5 V Analog Power Supply. |

### 3.7.3 Ground and No Connects

|   | Symbol | Туре | Name and Function                                                                                                                    |

|---|--------|------|--------------------------------------------------------------------------------------------------------------------------------------|

| ( | GND    | Р    | Ground.                                                                                                                              |

| 1 | NC     | Р    | <b>No Connect.</b> Do not connect any circuitry to these pins. Pull-up or pull-down resistors should not be connected to these pins. |

# 3.7.4 Control Signals

| Symbol | Туре | Name and Function                                                                                                                                                                                                                                                                                   |

|--------|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CTRL15 | А    | <b>1.5V Control.</b> LDO voltage regulator output to drive external pass transistor. If 1.5 V is already present in the system, leave output unconnected. To achieve optimal $D_3$ power consumption (<50 mw), leave the output unconnected and use a high-efficiency external switching regulator. |

| CTRL25 | Α    | <b>2.5V Control.</b> LDO voltage regulator output to drive external pass transistor. If 2.5 V is already present in the system, leave output unconnected. To achieve optimal $D_3$ power consumption (<50 mw), leave the output unconnected and use a high-efficiency external switching regulator. |

# 4.0 Voltage, Temperature, and Timing Specifications

**Note:** The specification values listed in this section are subject to change without notice. Verify with your local Intel sales office that you have the latest information before finalizing a design.

### 4.1 Absolute Maximum Ratings

Table 1. Absolute Maximum Ratings<sup>a</sup>

| Symbol           | Parameter              | Min  | Max                   | Unit |

|------------------|------------------------|------|-----------------------|------|

| V <sub>DD</sub>  | DC supply voltage      | -0.3 | 7                     | V    |

| V <sub>IN</sub>  | Input voltage          | -1   | V <sub>DD</sub> + 0.3 | V    |

| I <sub>IN</sub>  | DC input pin current   | -10  | 10                    | mA   |

| T <sub>STG</sub> | Storage<br>temperature | -40  | 125                   | °C   |

a. Maximum ratings are referenced to ground (VSS). Permanent device damage is likely to occur if the ratings in this table are exceeded. These values should not be used as the limits for normal device operations.

# 4.2 Recommended Operating Conditions

Table 2. Recommended Operating Conditions<sup>a</sup> (Sheet 1 of 2)

| Symbol          | Parameter                     | Condition   | Min | Тур | Max  | Unit |

|-----------------|-------------------------------|-------------|-----|-----|------|------|

| T <sub>OP</sub> | Operating<br>Temperature      |             | -40 |     | 85   | °C   |

| V <sub>IO</sub> | VIO Voltage<br>Range          |             | 3   |     | 5.25 | V    |

| V <sub>DD</sub> | Periphery<br>Voltage<br>Range | 3.3 V ± 10% | 3   | 3.3 | 3.6  | V    |

Table 2. Recommended Operating Conditions<sup>a</sup> (Sheet 2 of 2)

| Symbol          | Parameter                        | Condition   | Min   | Тур | Max   | Unit |

|-----------------|----------------------------------|-------------|-------|-----|-------|------|

| V <sub>AH</sub> | Analog High<br>VDD Range         | 3.3 V ± 10% | 3     | 3.3 | 3.6   | V    |

| V <sub>D</sub>  | Core Digital<br>Voltage<br>Range | 1.5 V ± 5%  | 1.425 | 1.5 | 1.575 | V    |

| V <sub>AL</sub> | Analog Low<br>VDD Range          | 2.5 V ± 5%  | 2.375 | 2.5 | 2.625 | V    |

a. Sustained operation of the device at conditions exceeding these values, even if they are within the absolute maximum rating limits, might result in permanent damage.

# 4.3 DC Specifications

Table 3. DC Characteristics

| Symbol                | Parameter                          | Min  | Тур | Max  | Units |

|-----------------------|------------------------------------|------|-----|------|-------|

| V <sub>DD</sub> (3.3) | DC supply voltage on VDDO or AVDDH | 3.00 | 3.3 | 3.60 | V     |

| V <sub>DD</sub> (2.5) | DC supply voltage on AVDDL         | 2.38 | 2.5 | 2.62 | V     |

| V <sub>DD</sub> (1.5) | DC supply voltage on DVDD          | 1.43 | 1.5 | 1.57 | V     |

Table 4. Power Specifications - D0a

|                          |                   | D0a             |                 |                 |                 |                |                 |                |  |  |  |  |

|--------------------------|-------------------|-----------------|-----------------|-----------------|-----------------|----------------|-----------------|----------------|--|--|--|--|

|                          | unplugged/no link |                 | @10 Mbps        |                 | @100Mbps        |                | @1000Mbps       |                |  |  |  |  |

|                          | TypIcc<br>(mA)    | Max Icc<br>(mA) | Typ Icc<br>(mA) | Max Icc<br>(mA) | Typ Icc<br>(mA) | MaxIcc<br>(mA) | Typ Icc<br>(mA) | MaxIcc<br>(mA) |  |  |  |  |

| 3.3 V                    | 40                | 40              | 55              | 65              | 65              | 80             | 125             | 125            |  |  |  |  |

| 2.5 V                    | 20                | 20              | 30              | 35              | 55              | 60             | 145             | 150            |  |  |  |  |

| 1.5 V                    | 100               | 120             | 95              | 100             | 115             | 125            | 400             | 425            |  |  |  |  |

| Total<br>Device<br>Power | 325 mW            |                 | 400 mW          |                 | 525 mW          |                | 1.38 W          | 1.5 W          |  |  |  |  |

Table 5. Power Specifications - D3cold

|                          |                | D3cold - wake-up enabled unplugged/no link @10 Mbps @100Mbps |                |                |                 |                |                 | - wake<br>d - max<br>avings | D3cold - wake<br>disabled - max<br>power savings |                |

|--------------------------|----------------|--------------------------------------------------------------|----------------|----------------|-----------------|----------------|-----------------|-----------------------------|--------------------------------------------------|----------------|

|                          | unplugg        | ed/no link                                                   | @10            | Mbps           | @1001           | /lbps          | mode disabled   |                             | mode enabled <sup>a</sup>                        |                |

|                          | Typicc<br>(mA) | MaxIcc<br>(mA)                                               | TypIcc<br>(mA) | MaxIcc<br>(mA) | Typ Icc<br>(mA) | MaxIcc<br>(mA) | Typ Icc<br>(mA) | MaxIcc<br>(mA)              | Typ Icc<br>(mA)                                  | MaxIcc<br>(mA) |

| 3.3 V                    | 40             | 40                                                           | 55             | 55             | 50              | 50             | 40              | 40                          | 6                                                | 8              |

| 2.5 V                    | 20             | 20                                                           | 30             | 30             | 55              | 55             | 20              | 20                          | 0.1                                              | 0.1            |

| 1.5 V                    | 40             | 40                                                           | 30             | 35             | 55              | 60             | 10              | 10                          | 1                                                | 1              |

| Total<br>Device<br>Power | 240 mW         |                                                              | 300 mW         |                | 385 mW          |                | 195 mW          |                             | 20 mW                                            |                |

a. Special Note: To obtain the benefit of max power savings mode, do not use the internal voltage regulator control circuit and external pass transistors. Use external switching regulators for highest efficiency.

Table 6. Power Specifications D(r) Uninitialized

|                       | D(r) Uninitialized<br>(LAN_PWR_GOOD=0) |                 |  |  |  |  |

|-----------------------|----------------------------------------|-----------------|--|--|--|--|

|                       | Typ Icc<br>(mA)                        | Max Icc<br>(mA) |  |  |  |  |

| 3.3 V                 | 40                                     | 45              |  |  |  |  |

| 2.5 V                 | 40                                     | 45              |  |  |  |  |

| 1.5 V                 | 190                                    | 200             |  |  |  |  |

| Total Device<br>Power | 520 mW                                 |                 |  |  |  |  |

Table 7. Power Specifications - Complete Subsystem

|       |                                                                   | Complete Subsystem (Reference Design) Including Magnetics, LED, Regulator Circuits |                                 |                |                                  |                |                        |                 |                                                                  |                |

|-------|-------------------------------------------------------------------|------------------------------------------------------------------------------------|---------------------------------|----------------|----------------------------------|----------------|------------------------|-----------------|------------------------------------------------------------------|----------------|

|       | D3cold - wake<br>disabled - max<br>power savings<br>mode disabled |                                                                                    | D3cold wake-<br>enabled @10Mbps |                | D3cold wake-<br>enabled @100Mbps |                | D0 @1000Mbps<br>active |                 | D3cold - wake<br>disabled - max<br>power savings<br>mode enabled |                |

|       | Typicc (mA)                                                       | MaxIcc<br>(mA)                                                                     | Typ Icc<br>(mA)                 | MaxIcc<br>(mA) | Typ Icc<br>(mA)                  | MaxIcc<br>(mA) | Typ<br>Icc<br>(mA)     | Max Icc<br>(mA) | Typicc<br>(mA)                                                   | MaxIcc<br>(mA) |

| 3.3 V | 40                                                                | 40                                                                                 | 60                              | 60             | 60                               | 60             | 130                    | 130             | 6                                                                | 8              |

Table 7. Power Specifications - Complete Subsystem

| 2.5 V                      | 20 | 20    | 40 | 40     | 80 | 80     | 240 | 245    | 0.1 | 0.1   |

|----------------------------|----|-------|----|--------|----|--------|-----|--------|-----|-------|

| 1.5 V                      | 10 | 10    | 30 | 35     | 55 | 60     | 400 | 425    | 1   | 1     |

| Subsystem<br>3.3 V current |    | 70 mA |    | 135 mA |    | 200 mA |     | 800 mA |     | 10 mA |

Table 8. I/O Characteristics

| Symbol                       | Parameter                                                                                  | Condition                                                               | Min                | Тур | Max                     | Unit           |

|------------------------------|--------------------------------------------------------------------------------------------|-------------------------------------------------------------------------|--------------------|-----|-------------------------|----------------|

| V <sub>IL</sub>              | Voltage input LOW                                                                          |                                                                         | -0.5               |     | 0.8                     | V              |

| V <sub>IH</sub>              | Voltage input HIGH                                                                         |                                                                         | 2                  |     | V <sub>DD</sub><br>+0.3 | V              |

| V <sub>OL</sub>              | Voltage output LOW                                                                         |                                                                         |                    |     | 0.4                     | V              |

| V <sub>OH</sub>              | Voltage output HIGH                                                                        |                                                                         | 2.4                |     |                         | V              |

| V <sub>SH</sub>              | Schmitt Trigger Hysterysis                                                                 |                                                                         | 0.1                |     |                         | V              |

| l <sub>OL</sub> <sup>a</sup> | Output current LOW 3mA drivers (TTL3) 6mA drivers (TTL6) 12mA drivers (TTL12)              | V <sub>OL</sub><br>V <sub>OL</sub><br>V <sub>OL</sub>                   | 3<br>6<br>12       |     |                         | mA<br>mA<br>mA |

| I <sub>OH</sub> <sup>a</sup> | Output current HIGH 3mA drivers (TTL3) 6mA drivers (TTL6) 12mA drivers (TTL12)             | V <sub>OH</sub><br>V <sub>OH</sub><br>V <sub>OH</sub>                   | -3<br>-6<br>-12    |     |                         | mA<br>mA<br>mA |

| I <sub>IN</sub>              | Input Current TTL inputs Inputs with pull-down resistors TTL inputs with pull-up resistors | $V_{IN} = V_{DD}$ or $V_{SS}$<br>$V_{IN} = V_{DD}$<br>$V_{IN} = V_{SS}$ | -10<br>150<br>-150 | ±1  | 10<br>480<br>-480       | μΑ<br>μΑ<br>μΑ |

| I <sub>OZ</sub>              | 3-state output leakage current                                                             | $V_{OH} = V_{DD}$ or $V_{SS}$                                           | -10                | ±1  | 10                      | μΑ             |

| C <sub>IN</sub>              | Input capacitance                                                                          | Any input and bi-directional buffer                                     |                    | 2.5 |                         | pF             |

| C <sub>OUT</sub>             | Output capacitance                                                                         | Any output<br>buffer                                                    |                    | 2   |                         | pF             |

| C <sub>PUD</sub>             | Pull-up/down Resistor value                                                                |                                                                         | 15                 | 20  | 30                      | kΩ             |

a. TTL3 signals include: EE\_DI, EE\_SK, EE\_CS, and JTAG\_TDO.

TTL6 signals include: CLKRUN#, FL\_CE#, FL\_SCK, FL\_SI, and CLK\_VIEW.

TTL12 signals include: LED0 / LINK #, LED1 / ACT #, LED2 / LINK100 #, LED3 / LINK1000 #, SDP0, SDP1, SDP6, and SDP7.

### 4.4 AC Characteristics

#### Table 9. AC Characteristics: 3.3 V Interfacing

| Symbol | Parameter                   | Min | Тур | Max | Unit |

|--------|-----------------------------|-----|-----|-----|------|

| CLK    | Clock frequency in PCI mode |     |     | 66  | MHz  |

#### Table 10. 25 MHz Clock Input Requirements

| Symbol    | Parameter <sup>a</sup> | Min         | Тур | Max            | Unit |

|-----------|------------------------|-------------|-----|----------------|------|

| fi_TX_CLK | TX_CLK_IN frequency    | 25 - 50 ppm | 25  | 25 + 50<br>ppm | MHz  |

a. This parameter applies to an oscillator connected to the Crystal One (XTAL1) input. Alternatively, a crystal may be connected to XTAL1 and XTAL2 as the frequency source for the internal oscillator.

#### **Table 11. Link Interface Clock Requirements**

| Symbol            | Parameter         | Min | Тур | Max | Unit |  |

|-------------------|-------------------|-----|-----|-----|------|--|

| fGTX <sup>a</sup> | GTX_CLK frequency |     | 125 |     | MHz  |  |

a.  $\mathsf{GTX}\_\mathsf{CLK}$  is used externally for test purposes only.

#### **Table 12. EEPROM Interface Clock Requirements**

| Symbol | Parameter | Min | Тур | Max | Unit |

|--------|-----------|-----|-----|-----|------|

| fSK    |           |     |     | 1   | MHz  |

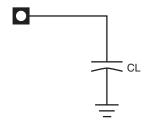

#### Table 13. AC Test Loads for General Output Pins

| Symbol | Signal Name                       | Value | Units |

|--------|-----------------------------------|-------|-------|

| CL     | TDO                               | 10    | pF    |

| CL     | PME#, SDP[7:0]                    | 16    | pF    |

| CL     | EEDI, EESK                        | 18    | pF    |

| CL     | RX_ACTIVITY, TX_ACTIVITY, LINK_UP | 20    | pF    |

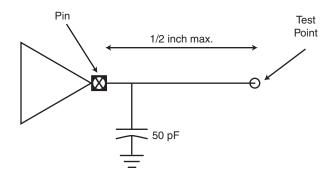

Figure 1. AC Test Loads for General Output Pins

#### 4.5 **Timing Specifications**

Timing specifications are subject to change. Verify with your local Intel sales office that you have the latest information before finalizing a design.

#### 4.5.1 **PCI Bus Interface**

#### 4.5.1.1 **PCI Bus Interface Clock**

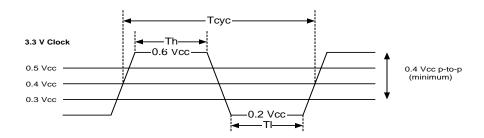

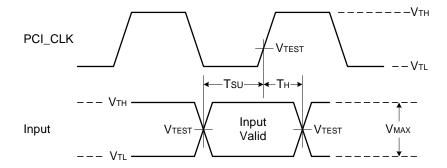

Table 14. PCI Bus Interface Clock Parameters

| Symbol | Parameter <sup>a</sup>      | PCI 66 MHz |     | PCI 33 MHz |     | Units  |

|--------|-----------------------------|------------|-----|------------|-----|--------|

| Symbol | Faranietei                  | Min        | Max | Min        | Max | Offics |

| TCYC   | CLK cycle time              | 15         | 30  | 30         |     | ns     |

| TH     | CLK high time               | 6          |     | 11         |     | ns     |

| TL     | CLK low time                | 6          |     | 11         |     | ns     |

|        | CLK slew rate               | 1.5        | 4   | 1          | 4   | V/ns   |

|        | RST# slew rate <sup>b</sup> | 50         |     | 50         |     | mV/ns  |

a. Rise and fall times are specified in terms of the edge rate measured in V/ns. This slew rate must be met across the

minimum peak-to-peak portion of the clock waveform as shown.

b. The minimum RST# slew rate applies only to the rising (de-assertion) edge of the reset signal and ensures that system noise cannot render a monotonic signal to appear bouncing in the switching range.

Figure 2. PCI Clock Timing

#### 4.5.1.2 PCI Bus Interface Timing

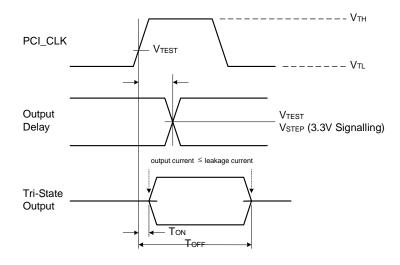

Table 15. PCI Bus Interface Timing Parameters

| Symbol    | Parameter                                         | PCI 6   | 6MHz | PCI 3   | 3 MHz | Units  |

|-----------|---------------------------------------------------|---------|------|---------|-------|--------|

| Symbol    | raiametei                                         | Min     | Max  | Min     | Max   | Offics |

| TVAL      | CLK to signal valid delay: bussed signals         | 2       | 6    | 2       | 11    | ns     |

| TVAL(ptp) | CLK to signal valid delay: point-to-point signals | 2       | 6    | 2       | 12    | ns     |

| TON       | Float to active delay                             | 2       |      | 2       |       | ns     |

| TOFF      | Active to float delay                             |         | 14   |         | 28    | ns     |

| TSU       | Input setup time to CLK: bussed signals           | 3       |      | 7       |       | ns     |

| TSU(ptp)  | Input setup time to CLK: point-to-point signals   | 5       |      | 10, 12  |       | ns     |

| TH        | Input hold time from CLK                          | 0       |      | 0       |       | ns     |

| TRRSU     | REQ64# to RST# setup time                         | 10*TCYC |      | 10*TCYC |       | ns     |

| TRRH      | RST# to REQ64# hold time                          | 0       |      | 0       |       | ns     |

#### NOTES:

- 1. Output timing measurements are as shown.

- 2. REQ# and GNT# signals are point-to-point and have different output valid delay and input setup times than bussed signals. GNT# has a setup of 10 ns; REQ# has a setup of 12 ns. All other signals are bussed.

- 3. Input timing measurements are as shown.

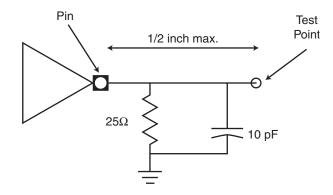

Figure 3. PCI Bus Interface Output Timing Measurement

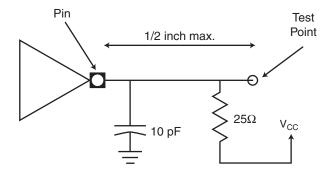

Figure 4. PCI Bus Interface Input Timing Measurement Conditions

**Table 16. PCI Bus Interface Timing Measurement Conditions**

| Symbol | Parameter                             | PCI 66 MHz<br>3.3 v | Unit |

|--------|---------------------------------------|---------------------|------|

| VTH    | Input measurement test voltage (high) | 0.6*VCC             | V    |

| VTL    | Input measurement test voltage (low)  | 0.2*VCC             | V    |

| VTEST  | Output measurement test voltage       | 0.4*VCC             | V    |

|        | Input signal slew rate                | 1.5                 | V/ns |

Figure 5. TVAL (max) Rising Edge Test Load

Figure 6. TVAL (max) Falling Edge Test Load

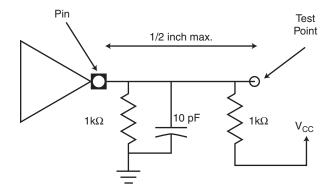

Figure 7. TVAL (min) Test Load

Figure 8. TVAL Test Load (PCI 5 V Signaling Environment)

**NOTE:** Note: 50 pF load used for maximum times. Minimum times are specified with 0 pF load.

### 4.5.2 Link Interface Timing

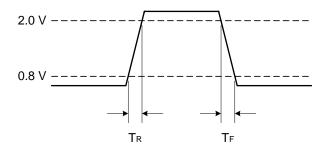

Table 17. Rise and Fall Times

| Symbol | Parameter       | Condition      | Min | Max | Unit |

|--------|-----------------|----------------|-----|-----|------|

| TR     | Clock rise time | 0.8 V to 2.0 V | 0.7 |     | ns   |

| TF     | Clock fall time | 2.0 V to 0.8 V | 0.7 |     | ns   |

| TR     | Data rise time  | 0.8 to 2.0 V   | 0.7 |     | ns   |

| TF     | Data fall time  | 2.0 V to 0.8 V | 0.7 |     | ns   |

Figure 9. Link Interface Rise/Fall Timing

#### 4.5.3 EEPROM Interface

#### **Table 18. Link Interface Clock Requirements**

| Symbol | Parameter        | Min | Тур         | Max | Unit |

|--------|------------------|-----|-------------|-----|------|

| TPW    | EESK pulse width |     | TPERIOD*128 |     | ns   |