# CP3BT13 Reprogrammable Connectivity Processor with Bluetooth® and CAN Interfaces

### 1.0 General Description

The CP3BT13 connectivity processor combines high performance with the massive integration needed for embedded Bluetooth applications. A powerful RISC core with on-chip SRAM and Flash memory provides high computing bandwidth, communications peripherals provide high I/O bandwidth, and an external bus provides system expandability.

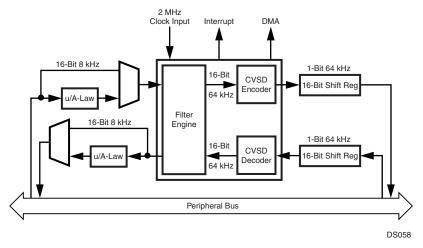

On-chip communications peripherals include: Bluetooth Lower Link Controller, CAN, ACCESS.bus, Microwire/Plus, SPI, UART, and Advanced Audio Interface (AAI). Additional on-chip peripherals include DMA controller, CVSD/PCM conversion module, Timing and Watchdog Unit, Versatile Timer Unit, Multi-Function Timer, and Multi-Input Wakeup.

Bluetooth hand-held devices can be both smaller and lower in cost for maximum consumer appeal. The low voltage and advanced power-saving modes achieve new design points in the trade-off between battery size and operating time for handheld and portable applications.

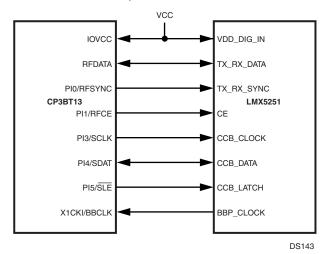

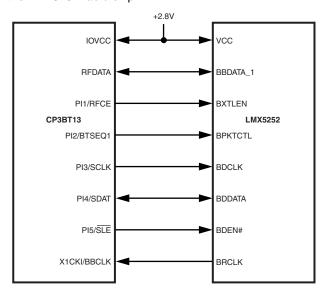

In addition to providing the features needed for the next generation of embedded Bluetooth products, the CP3BT13 is backed up by the software resources designers need for rapid time-to-market, including an operating system, Bluetooth protocol stack implementation, reference designs, and an integrated development environment. Combined with National's LMX5252 Bluetooth radio transceiver, the CP3BT13 provides a complete Bluetooth system solution.

National Semiconductor offers a complete and industry-proven application development environment for CP3BT13 applications, including the IAR Embedded Workbench, iSYSTEM winIDEA and iC3000 Active Emulator, Bluetooth Development Board, Bluetooth Protocol Stack, and Application Software.

|      | Table                                    | of     | Con  | tents                                                                                        |

|------|------------------------------------------|--------|------|----------------------------------------------------------------------------------------------|

| 1.0  | General Description                      | . 1    |      | 15.3 LMX5251 Power-Up Sequence                                                               |

| 2.0  | Features                                 |        |      | 15.4 LMX5252 Power-Up Sequence                                                               |

| 3.0  | Device Overview                          |        |      | 15.5 Bluetooth Sleep Mode                                                                    |

| 0.0  | 3.1 CR16C CPU Core                       |        |      | 15.7 Bluetooth Sequencer RAM                                                                 |

|      | 3.2 Memory                               |        |      | 15.8 Bluetooth Shared Data RAM                                                               |

|      | 3.3 Input/Output Ports                   | 4      | 16.0 | CAN Module                                                                                   |

|      | 3.4 Bus Interface Unit                   |        |      | 16.1 Functional Description                                                                  |

|      | 3.6 Bluetooth LLC                        |        |      | 16.2 Basic CAN Concepts                                                                      |

|      | 3.7 Multi-Input Wake-up                  | 4      |      | 16.4 Acceptance Filtering                                                                    |

|      | 3.8 Triple Clock and Reset               |        |      | 16.5 Receive Structure                                                                       |

|      | 3.9 Power Management                     | o<br>5 |      | 16.6 Transmit Structure                                                                      |

|      | 3.11 Versatile Timer Unit                |        |      | 16.7         Interrupts         92           16.8         Time Stamp Counter         93      |

|      | 3.12 Timing and Watchdog Module          | 5      |      | 16.9 Memory Organization                                                                     |

|      | 3.13 UART                                |        |      | 16.10 CAN Controller Registers95                                                             |

|      | 3.15 CAN Interface                       |        |      | 16.11 System Start-Up and Multi-Input Wake-Up                                                |

|      | 3.16 ACCESS.bus Interface                |        | 17.0 | Advanced Audio Interface                                                                     |

|      | 3.17 DMA Controller                      |        |      | 17.1 Audio Interface Signals                                                                 |

|      | 3.19 CVSD/PCM Conversion Module          |        |      | 17.2 Audio Interface Modes                                                                   |

|      | 3.20 Serial Debug Interface              | 6      |      | 17.3 Bit Clock Generation                                                                    |

|      | 3.21 Development Support                 |        |      | 17.4 Frame Clock Generation                                                                  |

| 4.0  | Device Pinouts                           |        |      | 17.6 Communication Options                                                                   |

| E 0  | 4.1 Pin DescriptionS                     |        |      | 17.7 Audio Interface Registers                                                               |

| 5.0  | CPU Architecture                         |        | 40.0 | 17.8 Usage Hints                                                                             |

|      | 5.1 General-Purpose Registers            |        | 18.0 | CVSD/PCM Conversion Module                                                                   |

|      | 5.3 Processor Status Register (PSR)      | . 18   |      | 18.1       Operation       125         18.2       PCM Conversions       125                  |

|      | 5.4 Configuration Register (CFG)         | . 19   |      | 18.3 CVSD Conversion                                                                         |

|      | 5.5 Addressing Modes                     |        |      | 18.4 PCM to CVSD Conversion                                                                  |

|      | 5.7 Instruction Set                      |        |      | 18.5 CVSD to PCM Conversion                                                                  |

| 6.0  | Memory                                   | 26     |      | 18.7 DMA Support                                                                             |

|      | 6.1 Operating Environment                | . 26   |      | 18.8 Freeze                                                                                  |

|      | 6.2 Bus Interface Unit (BIU)             |        |      | 18.9 CVSD/PCM Converter Registers                                                            |

|      | 6.3 Bus Cycles                           |        | 19.0 | UART Module                                                                                  |

|      | 6.5 Wait and Hold States                 |        |      | 19.1       Functional Overview       130         19.2       UART Operation       130         |

| 7.0  | System Configuration Registers           | 31     |      | 19.3 UART Registers                                                                          |

|      | 7.1 Module Configuration Register (MCFG) | . 31   |      | 19.4 Baud Rate Calculations                                                                  |

|      | 7.2 Module Status Register (MSTAT)       |        | 20.0 | Microwire/SPI Interface                                                                      |

| 8.0  | Flash Memory                             |        |      | 20.1 Microwire Operation                                                                     |

|      | 8.1 Flash Memory Protection              |        |      | 20.2       Master Mode       144         20.3       Slave Mode       145                     |

|      | 8.2 Flash Memory Organization            |        |      | 20.4 Interrupt Generation                                                                    |

|      | 8.4 Information Block Words              | . 35   |      | 20.5 Microwire Interface Registers                                                           |

|      | 8.5 Flash Memory Interface Registers     |        | 21.0 | ACCESS.bus Interface                                                                         |

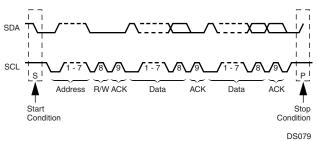

| 9.0  | DMA Controller                           |        |      | 21.1 ACB Protocol Overview                                                                   |

|      | 9.1 Channel Assignment                   |        |      | 21.2 ACB Functional Description                                                              |

|      | 9.3 Operation Modes                      |        |      | 21.4 Usage Hints                                                                             |

|      | 9.4 Software DMA Request                 | . 44   | 22.0 | Timing and Watchdog Module 157                                                               |

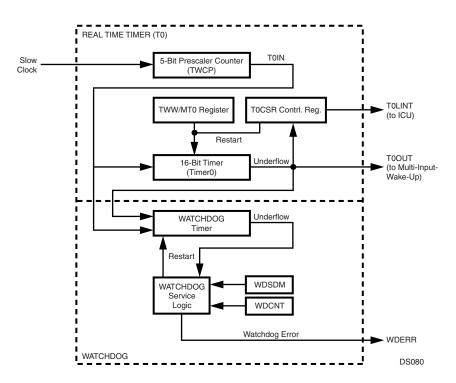

|      | 9.5 Debug Mode                           |        |      | 22.1 TWM Structure                                                                           |

| 10.0 | 9.6 DMA Controller Register Set          |        |      | 22.2 Timer T0 Operation                                                                      |

| 10.0 | 10.1 Non-Maskable Interrupts             |        |      | 22.3         Watchdog Operation         158           22.4         TWM Registers         158 |

|      | 10.2 Maskable Interrupts                 |        |      | 22.5 Watchdog Programming Procedure                                                          |

|      | 10.3 Interrupt Controller Registers      | . 48   | 23.0 | Multi-Function Timer                                                                         |

|      | 10.4 Maskable Interrupt Sources          |        |      | 23.1 <u>Timer Structure</u>                                                                  |

| 11.0 | 10.5 Nested Interrupts                   |        |      | 23.2 Timer Operating Modes                                                                   |

| 11.0 | 11.1 External Crystal Network            |        |      | 23.3 Timer Interrupts                                                                        |

|      | 11.2 Main Clock                          |        |      | 23.5 Timer Registers                                                                         |

|      | 11.3 Slow Clock                          |        | 24.0 | Versatile Timer Unit (VTU)                                                                   |

|      | 11.4 PLL Clock                           |        |      | 24.1 VTU Functional Description                                                              |

|      | 11.6 Auxiliary Clocks.                   |        |      | 24.2 VTU Registers                                                                           |

|      | 11.7 Power-Ón Reset                      | . 54   | 25.0 | Register Map                                                                                 |

|      | 11.8 External Reset                      |        | 26.0 | Register Bit Fields                                                                          |

| 10.0 | 11.9 Clock and Reset Registers           |        | 27.0 | Electrical Characteristics 201                                                               |

| 12.0 | Power Management                         |        |      | 27.1 Absolute Maximum Ratings                                                                |

|      | 12.2 Power Save Mode                     |        |      | 27.2 DC Electrical Characteristics                                                           |

|      | 12.3 Idle Mode                           | . 58   |      | 27.4 Output Signal Levels                                                                    |

|      | 12.4 Halt Mode                           |        |      | 27.5 Clock and Reset Timing                                                                  |

|      | 12.5 Hardware Clock Control              |        |      | 27.6 UART Timing                                                                             |

|      | 12.7 Switching Between Power Modes       |        |      | 27.7 I/O Port Timing                                                                         |

| 13.0 | Multi-Input Wake-Up                      |        |      | 27.9 Microwire/SPI Timing                                                                    |

|      | 13.1 Multi-Input Wake-Up Registers       |        |      | 27.10 ACCESS.bus Timing                                                                      |

|      | 13.2 Programming Procedures              |        |      | 27.11 Multi-Function Timer (MFT) Timing                                                      |

| 14.0 | Input/Output Ports                       |        |      | 27.12 Versaule Firming Offit (VTO) Firming                                                   |

|      | 14.1 Port Registers                      |        | 28.0 |                                                                                              |

|      | 14.2 Open Drain Operation                |        |      | Pin Assignments 226                                                                          |

| 15 N | 14.2 Open-Drain Operation                |        | 29.0 |                                                                                              |

| 15.0 | 14.2 Open-Drain Operation                | 69     |      | Revision History                                                                             |

### 2.0 Features

#### **CPU Features**

- Fully static RISC processor core, capable of operating from 0 to 24 MHz with zero wait/hold states

- Minimum 41.7 ns instruction cycle time with a 24-MHz internal clock frequency, based on a 12-MHz external input

- 30 independently vectored peripheral interrupts

### **On-Chip Memory**

- 256K bytes reprogrammable Flash program memory

- 8K bytes Flash data memory

- 10K bytes of static RAM data memory

- Addresses up to 8 Mbytes of external memory

### **Broad Range of Hardware Communications Peripherals**

- Bluetooth Lower Link Controller (LLC) including a shared 4.5K byte Bluetooth RAM and 1K byte Bluetooth Sequencer RAM

- Full CAN interface with 15 message buffers conforming to CAN specification 2.0B active

- ACCESS.bus serial bus (compatible with Philips I<sup>2</sup>C bus)

- 8/16-bit SPI, Microwire/Plus serial interface

- Universal Asynchronous Receiver/Transmitter (UART)

- Advanced Audio Interface (AAI) to connect to external 8/ 13-bit PCM Codecs as well as to ISDN-Controllers through the IOM-2 interface (slave only)

- CVSD/PCM converter supporting one bidirectional audio connection

### **General-Purpose Hardware Peripherals**

- Dual 16-bit Multi-Function Timer

- Versatile Timer Unit with four subsystems (VTU)

- Four channel DMA controller

- Timing and Watchdog Unit

### Flexible I/O

- Up to 40 general-purpose I/O pins (shared with on-chip peripheral I/O pins)

- Programmable I/O pin characteristics: TRI-STATE output, push-pull output, weak pull-up input, high-impedance input

- Schmitt triggers on general purpose inputs

- Multi-Input Wakeup

### **Extensive Power and Clock Management Support**

- On-chip Phase Locked Loop

- Support for multiple clock options

- Dual clock and reset

- Power-down modes

### **Power Supply**

- I/O port operation at 2.5V to 3.3V

- Core logic operation at 2.5V

- On-chip power-on reset

### **Temperature Range**

■ -40°C to +85°C (Industrial)

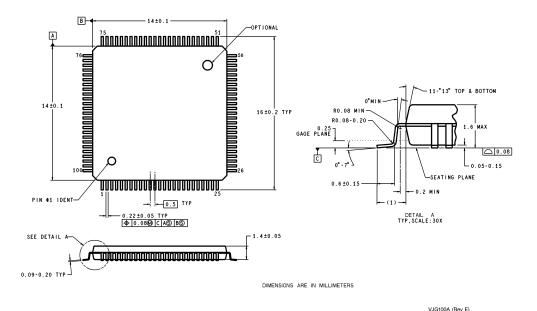

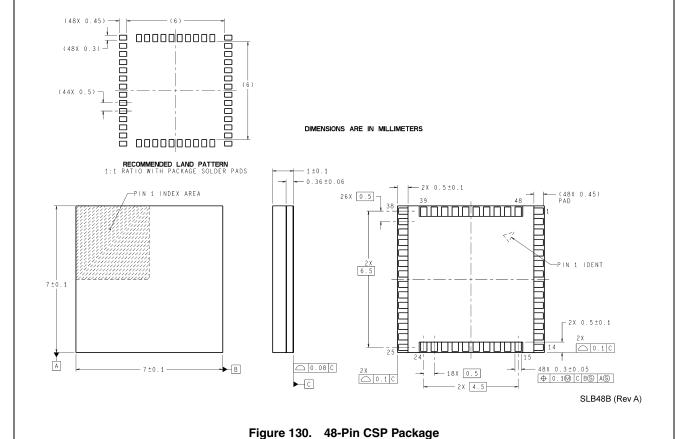

### **Packages**

■ CSP-48, LQFP-100

#### **Complete Development Environment**

- Pre-integrated hardware and software support for rapid prototyping and production

- Integrated environment

- Project manager

- Multi-file C source editor

- High-level C source debugger

- Comprehensive, integrated, one-stop technical support

#### **Bluetooth Protocol Stack**

- Applications can interface to the high-level protocols or directly to the low-level Host Controller Interface (HCI)

- Transport layer support allows HCI command-based interface over UART port

- Baseband (Link Controller) minimizes the performance demand on the CPU

- Link Manager (LM)

- Logical Link Control and Adaptation Protocol (L2CAP)

- Service Discovery Protocol (SDP)

- RFCOMM Serial Port Emulation Protocol

- All packet types, piconet, and scatternet functionality supported

### **CP3BT13 Connectivity Processor Selection Guide**

| NSID        | Speed<br>(MHz) | Temp. Range   | Program<br>Flash<br>(kBytes) | Data<br>Flash<br>(kBytes) | SRAM<br>(kBytes) | External<br>Address<br>Lines | I/Os | Package<br>Type | Pack<br>Method |

|-------------|----------------|---------------|------------------------------|---------------------------|------------------|------------------------------|------|-----------------|----------------|

| CP3BT13G38  | 24             | -40° to +85°C | 256                          | 8                         | 10               | 23                           | 40   | LQFP-100        | Tray           |

| CP3BT13G38X | 24             | -40° to +85°C | 256                          | 8                         | 10               | 23                           | 40   | LQFP-100        | 1000-T&R       |

| CP3BT13K38X | 24             | -40° to +85°C | 256                          | 8                         | 10               | 0                            | 23   | CSP-48          | 2500-T&R       |

| CP3BT13K38Y | 24             | -40° to +85°C | 256                          | 8                         | 10               | 0                            | 23   | CSP-48          | 250-T&R        |

T&R = Tape and Reel

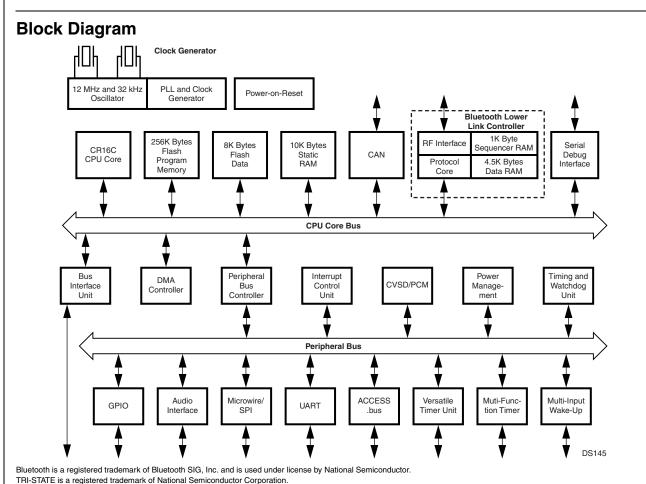

### 3.0 Device Overview

The CP3BT13 connectivity processor is a complete microcomputer with all system timing, interrupt logic, program memory, data memory, I/O ports included on-chip, making them well-suited to a wide range of embedded applications. The block diagram on page 1 shows the major on-chip components of the CP3BT13.

### 3.1 CR16C CPU CORE

The CP3BT13 implements the CR16C CPU core module. The high performance of the CPU core results from the implementation of a pipelined architecture with a two-bytesper-cycle pipelined system bus. As a result, the CPU can support a peak execution rate of one instruction per clock cycle.

For more information, please refer to the CR16C Programmer's Reference Manual (document number 424521772-101, which may be downloaded from National's web site at http://www.national.com).

### 3.2 MEMORY

The CP3BT13 supports a uniform linear address space of up to 16 megabytes. Three types of on-chip memory occupy specific regions within this address space:

- 256K bytes of Flash program memory

- 8K bytes of Flash data memory

- 10K bytes of static RAM

- Up to 8M bytes of external memory (100-pin devices)

The 256K bytes of Flash program memory are used to store the application program, Bluetooth protocol stack, and real-time operating system. The Flash memory has security features to prevent unintentional programming and to prevent unauthorized access to the program code. This memory can be programmed with an external programming unit or with the device installed in the application system (in-system programming).

The 8K bytes of Flash data memory are used for non-volatile storage of data entered by the end-user, such as configuration settings.

The 10K bytes of static RAM are used for temporary storage of data and for the program stack and interrupt stack. Read and write operations can be byte-wide or word-wide, depending on the instruction executed by the CPU.

Up to 8M bytes of external memory can be added on an external bus. The external bus is only available on devices in 100-pin packages.

For Flash program and data memory, the device internally generates the necessary voltages for programming. No additional power supply is required.

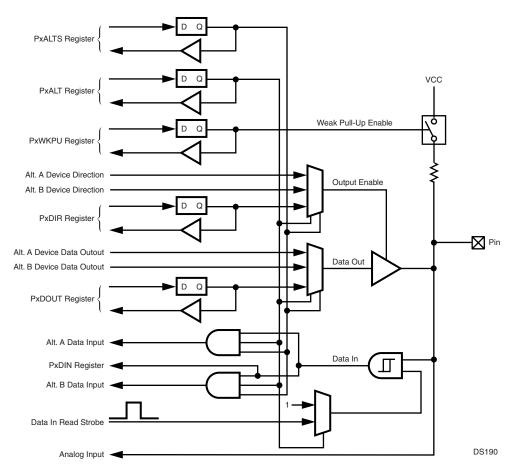

#### 3.3 INPUT/OUTPUT PORTS

The device has up to 40 software-configurable I/O pins, organized into five 8-pin ports called Port B, Port C, Port G, Port H, and Port I. Each pin can be configured to operate as a general-purpose input or general-purpose output. In addition, many I/O pins can be configured to operate as inputs or outputs for on-chip peripheral modules such as the UART, timers, or Microwire/SPI interface.

The I/O pin characteristics are fully programmable. Each pin can be configured to operate as a TRI-STATE output, push-pull output, weak pull-up input, or high-impedance input.

#### 3.4 BUS INTERFACE UNIT

The Bus Interface Unit (BIU) controls access to internal/external memory and I/O. It determines the configured parameters for bus access (such as the number of wait states for memory access) and issues the appropriate bus signals for each requested access.

The BIU uses a set of control registers to determine how many wait states and hold states are used when accessing Flash program memory, and the I/O area (Port B and Port C). At start-up, the configuration registers are set for slowest possible memory access. To achieve fastest possible program execution, appropriate values must be programmed. These settings vary with the clock frequency and the type of off-chip device being accessed.

### 3.5 INTERRUPT CONTROL UNIT (ICU)

The ICU receives interrupt requests from internal and external sources and generates interrupts to the CPU. An interrupt is an event that temporarily stops the normal flow of program execution and causes a separate interrupt handler to be executed. After the interrupt is serviced, CPU execution continues with the next instruction in the program following the point of interruption.

Interrupts from the timers, UART, Microwire/SPI interface, and Multi-Input Wake-Up, are all maskable interrupts; they can be enabled or disabled by software. There are 32 maskable interrupts, assigned to 32 linear priority levels.

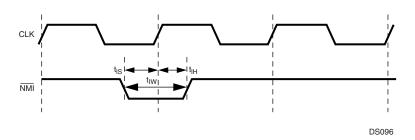

The highest-priority interrupt is the Non-Maskable Interrupt  $(\overline{\text{NMI}})$ , which is generated by a signal received on the  $\overline{\text{NMI}}$  input pin.

### 3.6 BLUETOOTH LLC

The integrated hardware Bluetooth Lower Link Controller (LLC) complies to the Bluetooth Specification Version 1.1 and integrates the following functions:

- 4.5K-byte dedicated Bluetooth data RAM

- 1K-byte dedicated Bluetooth Sequencer RAM

- Support of all Bluetooth 1.1 packet types

- Support for fast frequency hopping of 1600 hops/s

- Access code correlation and slot timing recovery circuit

- Power Management Control Logic

- BlueRF-compatible interface to connect with National's LMX5252 and other RF transceiver chips

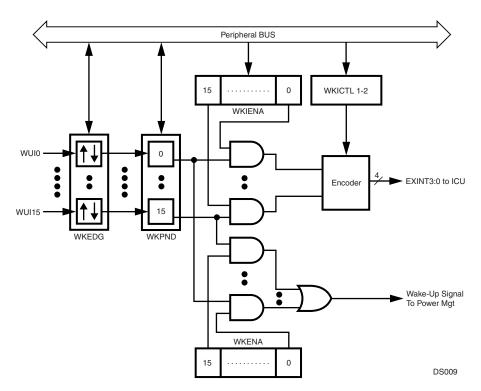

### 3.7 MULTI-INPUT WAKE-UP

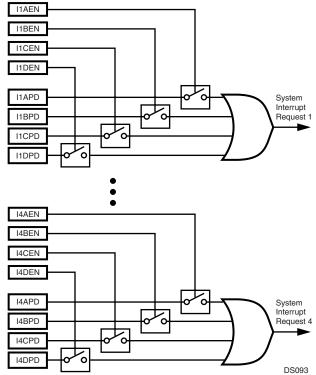

The Multi-Input Wake-Up (MIWU) module can be used for either of two purposes: to provide inputs for waking up (exiting) from the Halt, Idle, or Power Save mode; or to provide general-purpose edge-triggered maskable interrupts from external sources. This 16-channel module generates four programmable interrupts to the CPU based on the signals received on its 16 input channels. Channels can be individually enabled or disabled, and programmed to respond to positive or negative edges.

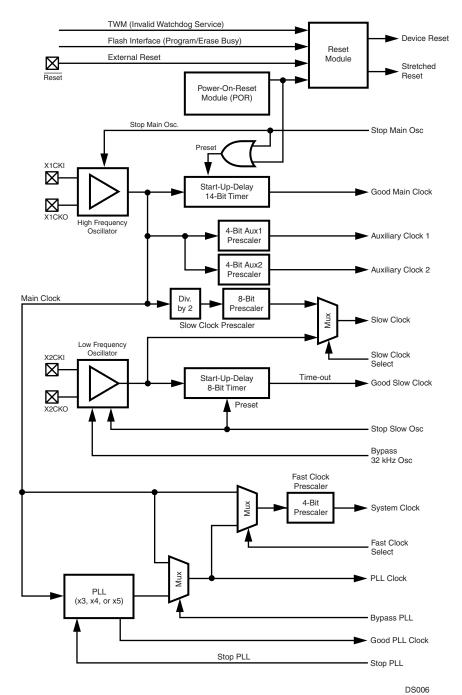

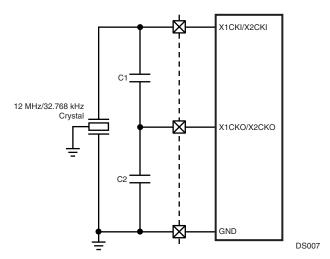

### 3.8 TRIPLE CLOCK AND RESET

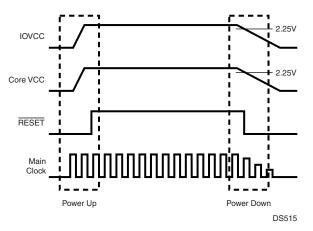

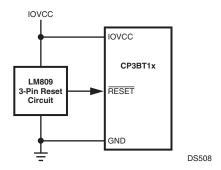

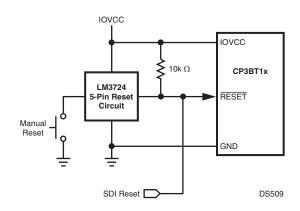

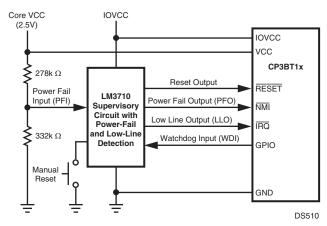

The Triple Clock and Reset module generates a high-speed System Clock from an external crystal network. It also provides the system reset signal and a power-on reset function.

This module generates a slow System Clock (32.768 kHz) from an optional external crystal network. The Slow Clock is used for operating the device in power-save mode. The 32.768 kHz external crystal network is optional, because the Slow Clock can be derived from the high-speed clock by a prescaler. Also, two independent clocks divided down from the high speed clock are available on output pins.

The Triple Clock and Reset module provides the clock signals required for the operation of the various CP3BT13 onchip modules. From external crystal networks, it generates the Main Clock, which can be scaled up to 24 MHz from an external 12 MHz input clock, and a 32.768 kHz secondary System Clock. The 12 MHz external clock is primarily used as the reference frequency for the on-chip PLL. Also the clock for modules which require a fixed clock rate (e.g. the Bluetooth LLC and the CVSD/PCM transcoder) is generated through prescalers from the 12 MHz clock. The PLL may be used to drive the high-speed System Clock through a prescaler. Alternatively, the high speed System Clock can be derived directly from the 12 MHz Main Clock.

In addition, this module generates the device reset by using reset input signals coming from an external reset and various on-chip modules.

### 3.9 POWER MANAGEMENT

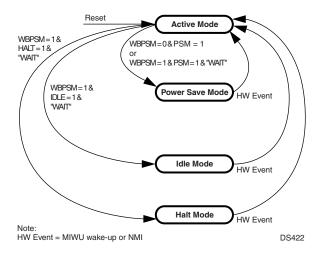

The Power Management Module (PMM) improves the efficiency of the device by changing the operating mode and power consumption to match the required level of activity.

The device can operate in any of four power modes:

- Active—The device runs at full speed using the high-frequency clock. All device functions are fully operational.

- Power Save—The device operates at reduced speed using the Slow Clock. The CPU and some modules can continue to operate at this low speed.

- *Idle*—The device is inactive except for the Power Management Module and Timing and Watchdog Module, which continue to operate using the Slow Clock.

- Halt—The device is inactive but still retains its internal state (RAM and register contents).

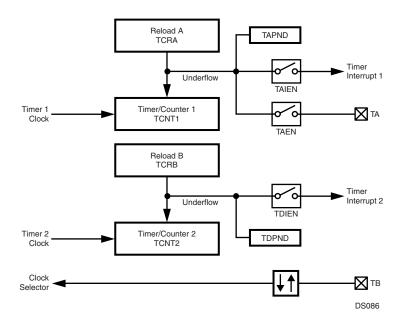

#### 3.10 MULTI-FUNCTION TIMER

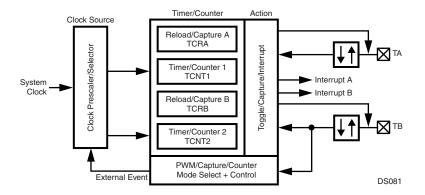

The Multi-Function Timer (MFT) module contains a pair of 16-bit timer/counter registers. Each timer/counter unit can be configured to operate in any of the following modes:

- Processor-Independent Pulse Width Modulation (PWM) mode—Generates pulses of a specified width and duty cycle and provides a general-purpose timer/counter.

- Dual Input Capture mode—Measures the elapsed time between occurrences of external event and provides a general-purpose timer/counter.

- Dual Independent Timer mode—Generates system timing signals or counts occurrences of external events.

- Single Input Capture and Single Timer mode—Provides one external event counter and one system timer.

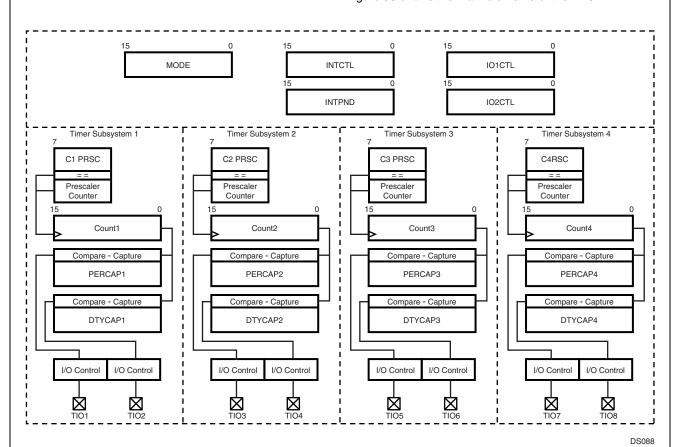

#### 3.11 VERSATILE TIMER UNIT

The Versatile Timer Unit (VTU) module contains four independent timer subsystems, each operating in either dual 8-bit PWM configuration, as a single 16-bit PWM timer, or a 16-bit counter with two input capture channels. Each of the four timer subsystems offer an 8-bit clock prescaler to accommodate a wide range of frequencies.

### 3.12 TIMING AND WATCHDOG MODULE

The Timing and Watchdog Module (TWM) contains a Real-Time timer and a Watchdog unit. The Real-Time Clock Timing function can be used to generate periodic real-time based system interrupts. The timer output is one of 16 inputs to the Multi-Input-Wake-Up module which can be used to exit from a power-saving mode. The Watchdog unit is designed to detect the application program getting stuck in an infinite loop resulting in loss of program control or "runaway" programs. When the watchdog triggers, it resets the device. The TWM is clocked by the low-speed System Clock.

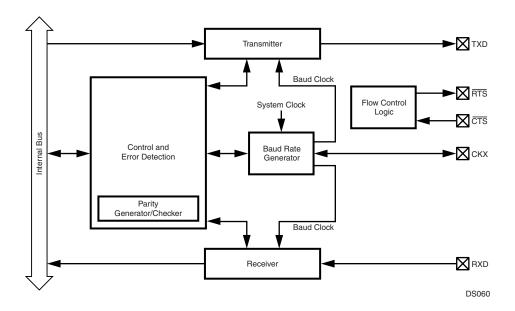

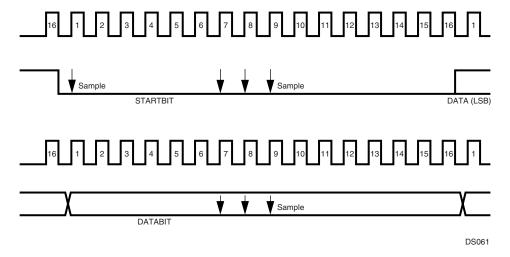

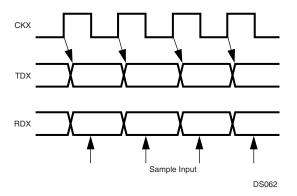

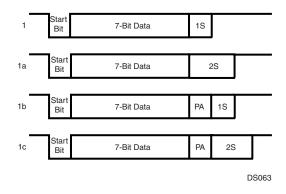

#### 3.13 **UART**

The UART supports a wide range of programmable baud rates and data formats, parity generation, and several error detection schemes. The baud rate is generated on-chip, under software control.

The UART offers a wake-up condition from the power-save mode using the Multi-Input Wake-Up module.

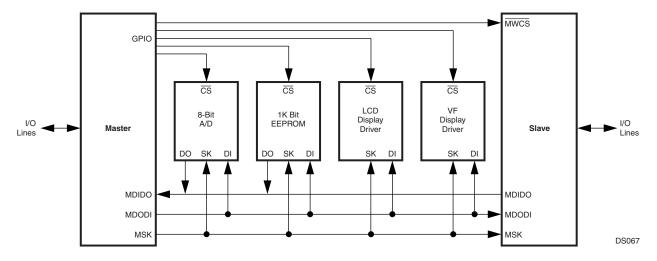

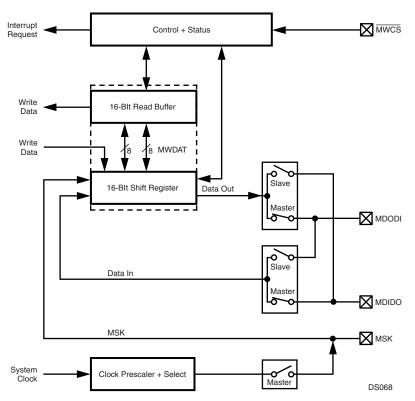

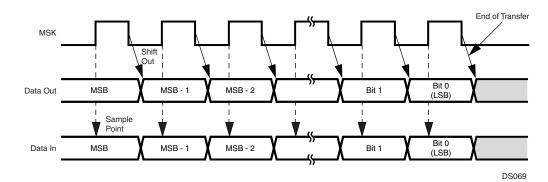

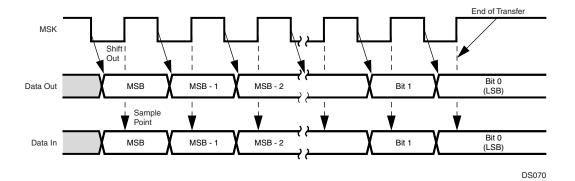

### 3.14 MICROWIRE/SPI

The Microwire/SPI (MWSPI) interface module supports synchronous serial communications with other devices that conform to Microwire or Serial Peripheral Interface (SPI) specifications. It supports 8-bit and 16-bit data transfers.

The Microwire interface allows several devices to communicate over a single system consisting of four wires: serial in, serial out, shift clock, and slave enable. At any given time, the Microwire interface operates as the master or a slave. The Microwire interface supports the full set of slave select for multi-slave implementation.

In master mode, the shift clock is generated on chip under software control. In slave mode, a wake-up out of power-save mode is triggered using the Multi-Input Wake-Up module.

### 3.15 CAN INTERFACE

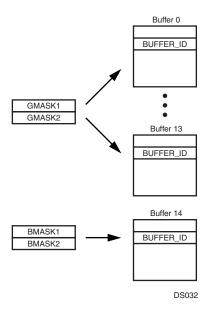

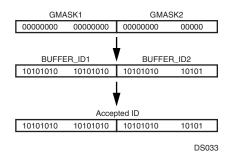

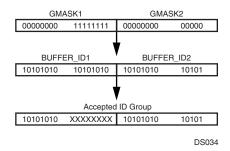

The CAN module contains a Full CAN 2.0B class, CAN serial bus interface for applications that require a high-speed (up to 1Mbits per second) or a low-speed interface with CAN bus master capability. The data transfer between CAN and the CPU is established by 15 memory-mapped message buffers, which can be individually configured as receive or transmit buffers. An incoming message is filtered by two masks, one for the first 14 message buffers and another one for the 15th message buffer to provide a basic CAN path. A priority decoder allows any buffer to have the highest or lowest transmit priority. Remote transmission requests can be processed automatically by automatic reconfiguration to a receiver after transmission or by automated transmit scheduling upon reception. In addition, a time stamp counter (16-bits wide) is provided to support real time applications.

The CAN module is a fast core bus peripheral, which allows single cycle byte or word read/write access. A set of diagnostic features (such as loopback, listen only, and error identification) support the development with the CAN module and provide a sophisticated error management tool.

The CAN receiver can trigger a wake-up condition out of the low-power modes through the Multi-Input Wake-Up module.

#### 3.16 ACCESS.BUS INTERFACE

The ACCESS.bus interface module (ACB) is a two-wire serial interface with the ACCESS.bus physical layer. It is also compatible with Intel's System Management Bus (SMBus) and Philips' I<sup>2</sup>C bus. The ACB module can be configured as a bus master or slave, and can maintain bidirectional communications with both multiple master and slave devices.

The ACCESS.bus receiver can trigger a wake-up condition out of the low-power modes using the Multi-Input Wake-Up module.

### 3.17 DMA CONTROLLER

The Direct Memory Access Controller (DMAC) can speed up data transfer between memory and I/O devices or between two memories, relative to data transfers performed directly by the CPU. A method called cycle-stealing allows the CPU and the DMAC to use the core bus in parallel. The DMAC implements four independent DMA channels. DMA requests from a primary and a secondary source are recognized for each DMA channel, as well as a software DMA request issued directly by the CPU. Table 1 shows the DMA channel assignment on the CP3BT13 architecture. The following on-chip modules can assert a DMA request to the DMAC:

- CR16C (Software DMA request)

- UART

- Advanced Audio Interface

- CVSD/PCM Converter

Table 1 shows how the four DMA channels are assigned to the modules listed above.

Table 1 DMA Channel Assignment

| Channel | Primary/<br>Secondary | Peripheral | Transaction |

|---------|-----------------------|------------|-------------|

| 0       | Primary               | Reserved   | Read/Write  |

| 0       | Secondary             | UART       | Read        |

| _       | Primary               | UART       | Write       |

| 1       | Secondary             | Unused     | N/A         |

| 0       | Primary               | AAI        | Read        |

| 2       | Secondary             | CVSD/PCM   | Read        |

| •       | Primary               | AAI        | Write       |

| 3       | Secondary             | CVSD/PCM   | Write       |

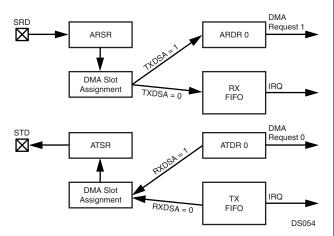

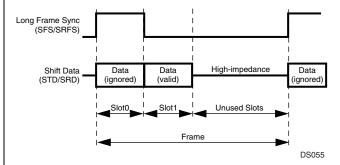

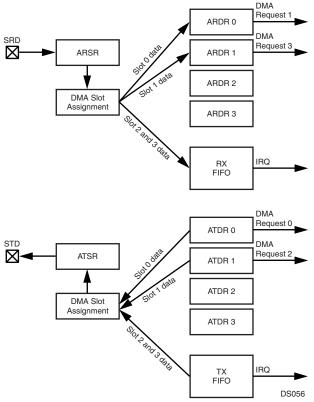

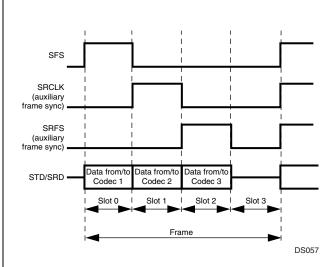

#### 3.18 ADVANCED AUDIO INTERFACE

The audio interface provides a serial synchronous, full-duplex interface to codecs and similar serial devices. Transmit and receive paths operate asynchronously with respect to each other. Each path uses three signals for communication: shift clock, frame synchronization, and data.

In case receive and transmit use separate shift clocks and frame sync signals, the interface operates in its asynchronous mode. Alternatively, the transmit and receive path can share the same shift clock and frame sync signals for synchronous mode operation.

The interface can handle data words of either 8- or 16-bit length and data frames can consist of up to four slots.

In the normal mode of operation, the interface only transfers one word at a periodic rate. In the network mode, the interface transfers multiple words at a periodic rate. The periodic rate is also called a data frame and each word within one frame is called a slot. The beginning of each new data frame is marked by the frame sync signal.

### 3.19 CVSD/PCM CONVERSION MODULE

The CVSD/PCM module performs conversion between CVSD and PCM data, in which the CVSD encoding is as defined in the Bluetooth specification 1.0 and the PCM data can be 8-bit  $\mu$ -Law, 8-bit A-Law, or 13-bit to 16-bit Linear.

#### 3.20 SERIAL DEBUG INTERFACE

The Serial Debug Interface module (SDI module) provides a JTAG-based serial link to an external debugger, for example running on a PC. In addition, the SDI module integrates an on-chip debug module, which allows the user to set up to four hardware breakpoints on instruction execution and data transfer. The SDI module can act as a CPU bus master to access all memory mapped resources, such as RAM and peripherals. It also provides fast program download into the on-chip Flash program memory using the JTAG interface.

**Note:** The SDI module may assert Freeze mode to gather information, which may cause periodic fluctuations in response (bus availability, interrupt latency, etc.). Anomalous behavior often may be traced to SDI activity.

### 3.21 DEVELOPMENT SUPPORT

In addition to providing the features needed for the next generation of embedded Bluetooth products, the CP3BT13 is backed up by the software resources designers need for rapid time-to-market, including an operating system, Bluetooth protocol stack implementation, peripheral drivers, reference designs, and an integrated development environment. Combined with National's LMX5252 Bluetooth radio transceiver, the CP3BT13 provides a total Bluetooth system solution.

National Semiconductor offers a complete and industry-proven application development environment for CP3BT13 applications, including the IAR Embedded Workbench, iSYSTEM winIDEA and iC3000 Active Emulator, Bluetooth Development Board, Bluetooth Protocol Stack, and Application Software. See your National Semiconductor sales representative for current information on availability and features of emulation equipment and evaluation boards.

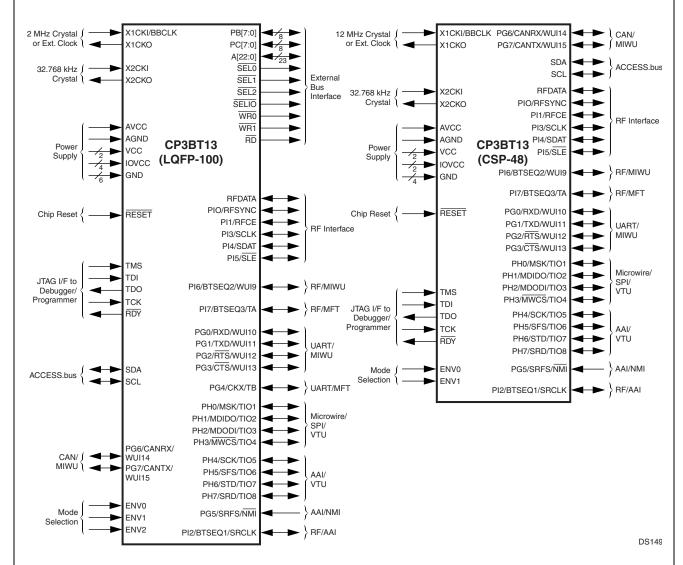

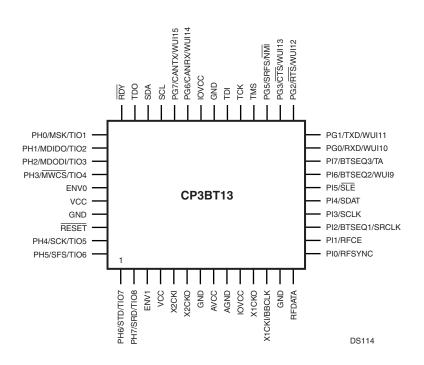

### 4.0 Device Pinouts

Table 2 Pin Assignments for 100-Pin Package

| Pin Name | Alternate Function(s) | Pin Numbers | Туре |

|----------|-----------------------|-------------|------|

| A14      |                       | 1           | 0    |

| A13      |                       | 2           | 0    |

| A12      |                       | 3           | 0    |

| A11      |                       | 4           | 0    |

| A10      |                       | 5           | 0    |

| PH6      | STD/TIO7              | 6           | GPIO |

| PH7      | SRD/TIO8              | 7           | GPIO |

| ENV1     |                       | 8           | I/O  |

| A9       |                       | 9           | 0    |

| A8       |                       | 10          | 0    |

| A7       |                       | 11          | 0    |

| A6       |                       | 12          | 0    |

| A5       |                       | 13          | 0    |

Table 2 Pin Assignments for 100-Pin Package

| Pin Name | Alternate Function(s) | Pin Numbers | Type |

|----------|-----------------------|-------------|------|

| A4       |                       | 14          | 0    |

| VCC      |                       | 15          | PWR  |

| X2CKI    |                       | 16          | I    |

| X2CKO    |                       | 17          | 0    |

| GND      |                       | 18          | PWR  |

| AVCC     |                       | 19          | PWR  |

| AGND     |                       | 20          | PWR  |

| IOVCC    |                       | 21          | PWR  |

| X1CKO    |                       | 22          | 0    |

| X1CKI    | BBCLK                 | 23          | I    |

| GND      |                       | 24          | PWR  |

| RFDATA   |                       | 25          | I/O  |

| A3       |                       | 26          | 0    |

| A2       |                       | 27          | 0    |

| A1       |                       | 28          | 0    |

| A0       |                       | 29          | 0    |

| PI0      | RFSYNC                | 30          | GPIO |

| PI1      | RFCE                  | 31          | GPIO |

| PI2      | BTSEQ1/SRCLK          | 32          | GPIO |

| PB0      | D0                    | 33          | GPIO |

| PB1      | D1                    | 34          | GPIO |

| PB2      | D2                    | 35          | GPIO |

| PB3      | D3                    | 36          | GPIO |

| PB4      | D4                    | 37          | GPIO |

| PB5      | D5                    | 38          | GPIO |

| PB6      | D6                    | 39          | GPIO |

| PB7      | D7                    | 40          | GPIO |

| GND      | <del></del>           | 41          | PWR  |

| IOVCC    |                       | 42          | PWR  |

| PI3      | SCLK                  | 43          | GPIO |

| PI4      | SDAT                  | 44          | GPIO |

| PI5      | SLE                   | 45          | GPIO |

| PI6      | WUI9                  | 46          | GPIO |

| PI7      | TA                    | 47          | GPIO |

| PG0      | RXD/WUI10             | 48          | GPIO |

| PG1      | TXD/WUI11             | 49          | GPIO |

| PC0      | D8                    | 50          | GPIO |

| PG2      | RTS/WUI12             | 51          | GPIO |

| PG3      | CTS/WUI13             | 52          | GPIO |

| PC1      | D9                    | 53          | GPIO |

| PC2      | D10                   | 54          | GPIO |

| PC3      | D11                   | 55          | GPIO |

| PC4      | D12                   | 56          | GPIO |

Table 2 Pin Assignments for 100-Pin Package

| Pin Name | Alternate Function(s) | Pin Numbers | Туре |

|----------|-----------------------|-------------|------|

| PC5      | D13                   | 57          | GPIO |

| PC6      | D14                   | 58          | GPIO |

| PC7      | D15                   | 59          | GPIO |

| PG5      | SRFS/NMI              | 60          | GPIO |

| TMS      |                       | 61          | I    |

| TCK      |                       | 62          | I    |

| TDI      |                       | 63          | I    |

| GND      |                       | 64          | PWR  |

| IOVCC    |                       | 65          | PWR  |

| ENV2     |                       | 66          | I/O  |

| SEL0     |                       | 67          | 0    |

| PG4      | CKX/TB                | 68          | GPIO |

| PG6      | CANRX/WUI14           | 69          | GPIO |

| PG7      | CANTX/WUI15           | 70          | GPIO |

| SCL      |                       | 71          | I/O  |

| SDA      |                       | 72          | I/O  |

| TDO      |                       | 73          | 0    |

| A22      |                       | 74          | 0    |

| RDY      |                       | 75          | 0    |

| SEL1     |                       | 76          | 0    |

| SEL2     |                       | 77          | 0    |

| SELIO    |                       | 78          | 0    |

| A21      |                       | 79          | 0    |

| A20      |                       | 80          | 0    |

| PH0      | MSK/TIO1              | 81          | GPIO |

| PH1      | MDIDO/TIO2            | 82          | GPIO |

| PH2      | MDODI/TIO3            | 83          | GPIO |

| PH3      | MWCS/TIO4             | 84          | GPIO |

| ENV0     |                       | 85          | I/O  |

| IOVCC    |                       | 86          | PWR  |

| GND      |                       | 87          | PWR  |

| VCC      |                       | 88          | PWR  |

| GND      |                       | 89          | PWR  |

| RESET    |                       | 90          | ı    |

| RD       |                       | 91          | 0    |

| WR0      |                       | 92          | 0    |

| WR1      |                       | 93          | 0    |

| A19      |                       | 94          | 0    |

| A18      |                       | 95          | 0    |

| A17      |                       | 96          | 0    |

| A16      |                       | 97          | 0    |

| A15      |                       | 98          | 0    |

### Table 2 Pin Assignments for 100-Pin Package

| Pin Name | Alternate Function(s) | Pin Numbers | Туре |

|----------|-----------------------|-------------|------|

| PH4      | SCK/TIO5              | 99          | GPIO |

| PH5      | SFS/TIO6              | 100         | GPIO |

Note 1: The ENV0, ENV1, ENV2, TCK, TDI, and TMS pins each have a weak pull-up to keep the input from floating.

Note 2: The RESET input has a weak pulldown.

Note 3: These functions are always enabled, due to the direct low-impedance path to these pins.

Table 3 Pin Assignments for 48-Pin Package

| Pin Name | Alternate Function(s) | Pin Number | Туре     |

|----------|-----------------------|------------|----------|

| PH6      | STD/TIO7              | 1          | GPIO     |

| PH7      | SRD/TIO8              | 2          | GPIO     |

| ENV1     |                       | 3          | I/O      |

| VCC      |                       | 4          | PWR      |

| X2CKI    |                       | 5          | I        |

| X2CKO    |                       | 6          | 0        |

| GND      |                       | 7          | PWR      |

| AVCC     |                       | 8          | PWR      |

| AGND     |                       | 9          | PWR      |

| IOVCC    |                       | 10         | PWR      |

| X1CKO    |                       | 11         | 0        |

| X1CKI    | BBCLK                 | 12         | 1        |

| GND      |                       | 13         | PWR      |

| RFDATA   |                       | 14         | I/O      |

| PI0      | RFSYNC                | 15         | GPIO     |

| PI1      | RFCE                  | 16         | GPIO     |

| PI2      | BTSEQ1/SRCLK          | 17         | GPIO     |

| PI3      | SCLK                  | 18         | GPIO     |

| PI4      | SDAT                  | 19         | GPIO     |

| PI5      | SLE                   | 20         | GPIO     |

| PI6      | BTSEQ2/WUI9           | 21         | GPIO     |

| PI7      | BTSEQ3/TA             | 22         | GPIO     |

| PG0      | RXD/WUI10             | 23         | GPIO     |

| PG1      | TXD/WUI11             | 24         | GPIO     |

| PG2      | RTS/WUI12             | 25         | GPIO     |

| PG3      | CTS/WUI13             | 26         | GPIO     |

| PG5      | SRFS/NMI              | 27         | GPIO     |

| TMS      |                       | 28         | I        |

| TCK      |                       | 29         | I        |

| TDI      |                       | 30         | 1        |

| GND      |                       | 31         | PWR      |

| IOVCC    |                       | 32         | PWR      |

| PG6      | CANRX/WUI14           | 33         | O, GPIO  |

| PG7      | CANTX/WUI15           | 34         | O, GPIO  |

| SCL      |                       | 35         | I/O      |

| SDA      |                       | 36         | PWR, I/O |

| Pin Name | Alternate Function(s) | Pin Number | Туре   |

|----------|-----------------------|------------|--------|

| TDO      |                       | 37         | PWR, O |

| RDY      |                       | 38         | 0      |

| PH0      | MSK/TIO1              | 39         | GPIO   |

| PH1      | MDIDO/TIO2            | 40         | GPIO   |

| PH2      | MDODI/TIO3            | 41         | GPIO   |

| PH3      | MWCS/TIO4             | 42         | GPIO   |

| ENV0     |                       | 43         | I/O    |

| VCC      |                       | 44         | PWR    |

| GND      |                       | 45         | PWR    |

| RESET    |                       | 46         | 1      |

| PH4      | SCK/TIO5              | 47         | GPIO   |

| PH5      | SFS/TIO6              | 48         | GPIO   |

### 4.1 PIN DESCRIPTIONS

Some pins may be enabled as general-purpose I/O-port pins or as alternate functions associated with specific peripheral or interface is enabled. Table 4 lists the device pins.

Table 4 CP3BT13 Pin Descriptions for the 100-Pin LQFP Package

| Name  | Pins | I/O    | Primary Function                                      | Alternate<br>Name | Alternate Function                      |

|-------|------|--------|-------------------------------------------------------|-------------------|-----------------------------------------|

| X1CKI | 1    | Input  | 12 MHz Oscillator Input                               | BBCLK             | BB reference clock for the RF Interface |

| X1CKO | 1    | Output | 12 MHz Oscillator Output                              | None              | None                                    |

| X2CKI | 1    | Input  | 32 kHz Oscillator Input                               | None              | None                                    |

| X2CKO | 1    | Output | 32 kHz Oscillator Output                              | None              | None                                    |

| AVCC  | 1    | Input  | PLL Analog Power Supply                               | None              | None                                    |

| IOVCC | 4    | Input  | 2.5V - 3.3V I/O Power Supply                          | None              | None                                    |

| VCC   | 2    | Input  | 2.5V Core Logic<br>Power Supply                       | None              | None                                    |

| GND   | 6    | Input  | Reference Ground                                      | None              | None                                    |

| AGND  | 1    | Input  | PLL Analog Ground                                     | None              | None                                    |

| RESET | 1    | Input  | Chip general reset                                    | None              | None                                    |

| TMS   | 1    | Input  | JTAG Test Mode Select<br>(with internal weak pull-up) | None              | None                                    |

| TDI   | 1    | Input  | JTAG Test Data Input<br>(with internal weak pull-up)  | None              | None                                    |

| TDO   | 1    | Output | JTAG Test Data Output                                 | None              | None                                    |

| TCK   | 1    | Input  | JTAG Test Clock Input<br>(with internal weak pull-up) | None              | None                                    |

| RDY   | 1    | Output | NEXUS Ready Output                                    | None              | None                                    |

| DO0   | _    | 1/0    | O arrania I/O                                         | RXD               | UART Receive Data Input                 |

| PG0   | 1    | I/O    | Generic I/O                                           | WUI10             | Multi-Input Wake-Up Channel 10          |

| DC1   | 4    | 1/0    | Canadia I/O                                           | TXD               | UART Transmit Data Output               |

| PG1   | 1    | I/O    | Generic I/O                                           | WUI11             | Multi-Input Wake-Up Channel 11          |

| DO0   | _    | 1/0    | O arrania I/O                                         | RTS               | UART Ready-To-Send Output               |

| PG2   | 1    | I/O    | Generic I/O                                           | WUI12             | Multi-Input Wake-Up Channel 12          |

| DCO   | 4    | 1/0    | Canada I/O                                            | CTS               | UART Clear-To-Send Input                |

| PG3   | 1    | I/O    | Generic I/O                                           | WUI13             | Multi-Input Wake-Up Channel 13          |

| DO4   | _    | 1/0    | O arrania I/O                                         | CKX               | UART Clock Input                        |

| PG4   | 1    | I/O    | Generic I/O                                           | ТВ                | Multi Function Timer Port B             |

| DOF   | _    | 1/0    | Conorio I/O                                           | SRFS              | AAI Receive Frame Sync                  |

| PG5   | 1    | I/O    | Generic I/O                                           | NMI               | Non-Maskable Interrupt Input            |

| DC6   | 4    | 1/0    | Conorio I/O                                           | CANRX             | CAN Receive Pin                         |

| PG6   | 1    | I/O    | Generic I/O                                           | WUI14             | Multi-Input Wake-Up Channel 14          |

| DC7   | 4    | 1/0    | Canaria I/O                                           | CANTX             | CAN Transmit Pin                        |

| PG7   | 1    | I/O    | Generic I/O                                           | WUI15             | Multi-Input Wake-Up Channel 15          |

| Name    | Pins | I/O    | Primary Function                    | Alternate<br>Name | Alternate Function                 |

|---------|------|--------|-------------------------------------|-------------------|------------------------------------|

| PH0     | 1    | I/O    | Generic I/O                         | MSK               | SPI Shift Clock                    |

| ГПО     | !    | 1/0    | Generic i/O                         | TIO1              | Versatile Timer Channel 1          |

| PH1     | 4    | I/O    | Canaria I/O                         | MDIDO             | SPI Master In Slave Out            |

| РПІ     | 1    | 0      | Generic I/O                         | TIO2              | Versatile Timer Channel 2          |

| PH2     | 1    | I/O    | Generic I/O                         | MDODI             | SPI Master Out Slave In            |

| FUZ     |      | 1/0    | Generic i/O                         | TIO3              | Versatile Timer Channel 3          |

| PH3     | 1    | I/O    | Generic I/O                         | MWCS              | SPI Slave Select Input             |

| PHS     | 1    | 1/0    | Generic i/O                         | TIO4              | Versatile Timer Channel 4          |

| DUIA    | 4    | -2     | Canadia I/O                         | SCK               | AAI Clock                          |

| PH4     | 1    | I/O    | Generic I/O                         | TIO5              | Versatile Timer Channel 5          |

| DUE     | 4    | 1/0    | Caravia I/O                         | SFS               | AAI Frame Synchronization          |

| PH5     | 1    | I/O    | Generic I/O                         | TIO6              | Versatile Timer Channel 6          |

| DUIG    | 4    |        | 0 : 1/0                             | STD               | AAI Transmit Data Output           |

| PH6     | 1    | I/O    | Generic I/O                         | TIO7              | Versatile Timer Channel 7          |

| D. 15   |      |        | 0 : 1/0                             | SRD               | AAI Receive Data Input             |

| PH7     | 1    | I/O    | Generic I/O                         | TIO8              | Versatile Timer Channel 8          |

| RFDATA  | 1    | I/O    | Bluetooth RX/TX Data Pin            | None              | None                               |

| PI0     | 1    | I/O    | Generic I/O                         | RFSYNC            | BT AC Correlation/TX Enable Output |

| PI1     | 1    | I/O    | Generic I/O                         | RFCE              | BT RF Chip Enable Output           |

| Die     |      |        | 0 1 1/0                             | BTSEQ1            | Bluetooth Sequencer Status         |

| PI2     | 1    | I/O    | Generic I/O                         | SRCLK             | AAI Receive Clock                  |

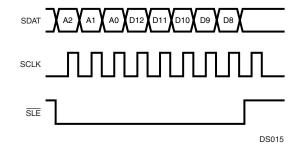

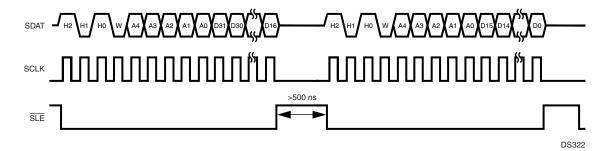

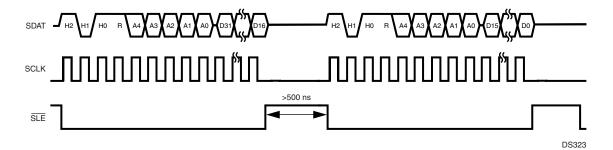

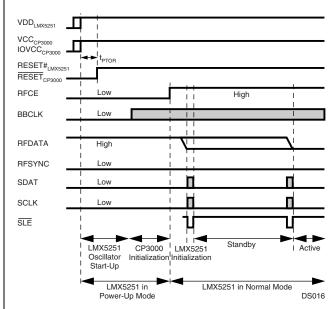

| PI3     | 1    | I/O    | Generic I/O                         | SCLK              | BT Serial I/F Shift Clock Output   |

| PI4     | 1    | I/O    | Generic I/O                         | SDAT              | BT Serial I/F Data                 |

| PI5     | 1    | I/O    | Generic I/O                         | SLE               | BT Serial I/F Load Enable Output   |

| Die     |      |        | 0 1 1/0                             | WUI9              | Multi-Input Wake-Up Channel 9      |

| PI6     | 1    | I/O    | Generic I/O                         | BTSEQ2            | Bluetooth Sequencer Status         |

|         | _    |        |                                     | TA                | Multi Function Timer Port A        |

| PI7     | 1    | I/O    | Generic I/O                         | BTSEQ3            | Bluetooth Sequencer Status         |

| SDA     | 1    | I/O    | ACCESS.bus Serial Data              | None              | None                               |

| SCL     | 1    | I/O    | ACCESS.bus Clock                    | None              | None                               |

| PB[7:0] | 8    | I/O    | Generic I/O                         | D[7:0]            | External Data Bus Bit 0 to 7       |

| PC[7:0] | 8    | I/O    | Generic I/O                         | D[15:8]           | External Data Bus Bit 8 to 15      |

| A[22:0] | 23   | Output | External Address Bus<br>Bit 0 to 22 | None              | None                               |

| SEL0    | 1    | Output | Chip Select for Zone 0              | None              | None                               |

| SEL1    | 1    | Output | Chip Select for Zone 1              | None              | None                               |

| SEL2    | 1    | Output | Chip Select for Zone 2              | None              | None                               |

| SELIO   | 1    | Output | Chip Select for Zone I/O Zone       | None              | None                               |

| Name            | Pins | I/O    | Primary Function                                             | Alternate<br>Name | Alternate Function |

|-----------------|------|--------|--------------------------------------------------------------|-------------------|--------------------|

| WR0             | 1    | Output | External Memory Write Low Byte                               | None              | None               |

| WR1             | 1    | Output | External Memory Write High Byte                              | None              | None               |

| $\overline{RD}$ | 1    | Output | External Memory Read                                         | None              | None               |

| ENV0            | 1    | I/O    | Special mode select input with internal pull-up during reset | PLLCLK            | PLL Clock Output   |

| ENV1            | 1    | I/O    | Special mode select input with internal pull-up during reset | CPUCLK            | CPU Clock Output   |

| ENV2            | 1    | I/O    | Special mode select input with internal pull-up during reset | SLOWCLK           | Slow Clock Output  |

Table 5 CP3BT13 Pin Descriptions for the 48-Pin CSP

| Name  | Pins | I/O    | Primary Function                                      | Alternate<br>Name | Alternate Function                      |

|-------|------|--------|-------------------------------------------------------|-------------------|-----------------------------------------|

| X1CKI | 1    | Input  | 12 MHz Oscillator Input                               | BBCLK             | BB reference clock for the RF Interface |

| X1CKO | 1    | Output | 12 MHz Oscillator Output                              | None              | None                                    |

| X2CKI | 1    | Input  | 32 kHz Oscillator Input                               | None              | None                                    |

| X2CKO | 1    | Output | 32 kHz Oscillator Output                              | None              | None                                    |

| AVCC  | 1    | Input  | PLL Analog Power Supply                               | None              | None                                    |

| IOVCC | 2    | Input  | 2.5V - 3.3V I/O Power Supply                          | None              | None                                    |

| VCC   | 2    | Input  | 2.5V Core Logic<br>Power Supply                       | None              | None                                    |

| GND   | 4    | Input  | Reference Ground                                      | None              | None                                    |

| AGND  | 1    | Input  | PLL Analog Ground                                     | None              | None                                    |

| RESET | 1    | Input  | Chip general reset                                    | None              | None                                    |

| TMS   | 1    | Input  | JTAG Test Mode Select<br>(with internal weak pull-up) | None              | None                                    |

| TDI   | 1    | Input  | JTAG Test Data Input<br>(with internal weak pull-up)  | None              | None                                    |

| TDO   | 1    | Output | JTAG Test Data Output                                 | None              | None                                    |

| TCK   | 1    | Input  | JTAG Test Clock Input<br>(with internal weak pull-up) | None              | None                                    |

| RDY   | 1    | Output | NEXUS Ready Output                                    | None              | None                                    |

| DOO   | _    |        | Ormania I/O                                           | RXD               | UART Receive Data Input                 |

| PG0   | 1    | I/O    | Generic I/O                                           | WUI10             | Multi-Input Wake-Up Channel 10          |

| DO4   | _    |        | 0 : 1/0                                               | TXD               | UART Transmit Data Output               |

| PG1   | 1    | I/O    | Generic I/O                                           | WUI11             | Multi-Input Wake-Up Channel 11          |

| DOG   |      | 1/0    | 0 : 1/0                                               | RTS               | UART Ready-To-Send Output               |

| PG2   | 1    | I/O    | Generic I/O                                           | WUI12             | Multi-Input Wake-Up Channel 12          |

| DOG   |      | 1/0    | 0 : 1/0                                               | CTS               | UART Clear-To-Send Input                |

| PG3   | 1    | I/O    | Generic I/O                                           | WUI13             | Multi-Input Wake-Up Channel 13          |

| Name   | Pins        | I/O | Primary Function         | Alternate<br>Name | Alternate Function                 |

|--------|-------------|-----|--------------------------|-------------------|------------------------------------|

| DOF    | 1 I/O Ge    |     | Canaria I/O              | SRFS              | AAI Receive Frame Sync             |

| PG5    |             |     | Generic I/O              | NMI               | Non-Maskable Interrupt Input       |

| DCC    | 4           | 2   | Canaria I/O              | CANRX             | CAN Receive Pin                    |

| PG6    | 1           | I/O | Generic I/O              | WUI14             | Multi-Input Wake-Up Channel 14     |

| PG7    | 4           | I/O | Generic I/O              | CANTX             | CAN Transmit Pin                   |

| PG/    | 1           | 1/0 | Generic I/O              | WUI15             | Multi-Input Wake-Up Channel 15     |

| DLIO   | 4           | -/- | Canaria I/O              | MSK               | SPI Shift Clock                    |

| PH0    | 1           | I/O | Generic I/O              | TIO1              | Versatile Timer Channel 1          |

| DUIA   | _           |     | 0                        | MDIDO             | SPI Master In Slave Out            |

| PH1    | 1           | I/O | Generic I/O              | TIO2              | Versatile Timer Channel 2          |

| DLIO   | 4           | -/- | Canaria I/O              | MDODI             | SPI Master Out Slave In            |

| PH2    | 1           | I/O | Generic I/O              | TIO3              | Versatile Timer Channel 3          |

| DUIG   | _           |     | 0                        | MWCS              | SPI Slave Select Input             |

| PH3    | 1           | I/O | Generic I/O              | TIO4              | Versatile Timer Channel 4          |

| DUIA   | _           |     | 0                        | SCK               | AAI Clock                          |

| PH4    | 1           | I/O | Generic I/O              | TIO5              | Versatile Timer Channel 5          |

| DUE    | 4           | 1/0 | Cararia I/O              | SFS               | AAI Frame Synchronization          |

| PH5    | 1           | I/O | Generic I/O              | TIO6              | Versatile Timer Channel 6          |

| DLIC   | 4           | 1/0 | Cararia I/O              | STD               | AAI Transmit Data Output           |

| PH6    | 1           | I/O | Generic I/O              | TIO7              | Versatile Timer Channel 7          |

| DUZ    | 4           | -/- | Cararia I/O              | SRD               | AAI Receive Data Input             |

| PH7    | 1           | I/O | Generic I/O              | TIO8              | Versatile Timer Channel 8          |

| RFDATA | 1           | I/O | Bluetooth RX/TX Data Pin | None              | None                               |

| PI0    | 1           | I/O | Generic I/O              | RFSYNC            | BT AC Correlation/TX Enable Output |

| PI1    | 1           | I/O | Generic I/O              | RFCE              | BT RF Chip Enable Output           |

| DIO    | 4           | -/- | Canaria I/O              | BTSEQ1            | Bluetooth Sequencer Status         |

| PI2    | 1           | I/O | Generic I/O              | SRCLK             | AAI Receive Clock                  |

| PI3    | 1           | I/O | Generic I/O              | SCLK              | BT Serial I/F Shift Clock Output   |

| PI4    | 1           | I/O | Generic I/O              | SDAT              | BT Serial I/F Data                 |

| PI5    | 1           | I/O | Generic I/O              | SLE               | BT Serial I/F Load Enable Output   |

| DIC    | PI6 1 I/O   |     | Canaria I/O              | WUI9              | Multi-Input Wake-Up Channel 9      |

| PIO    |             |     | Generic I/O              | BTSEQ2            | Bluetooth Sequencer Status         |

| DIZ    | 4           | 1/0 | Conorio I/O              | TA                | Multi Function Timer Port A        |

| F1/    | PI7 1 I/O G |     | Generic I/O              | BTSEQ3            | Bluetooth Sequencer Status         |

| SDA    | 1           | I/O | ACCESS.bus Serial Data   | None              | None                               |

| SCL    | 1           | I/O | ACCESS.bus Clock         | None              | None                               |

| Name | Pins | I/O | Primary Function                                             | Alternate<br>Name | Alternate Function |  |

|------|------|-----|--------------------------------------------------------------|-------------------|--------------------|--|

| ENV0 | 1    | I/O | Special mode select input with internal pull-up during reset | PLLCLK            | PLL Clock Output   |  |

| ENV1 | 1    | I/O | Special mode select input with internal pull-up during reset | CPUCLK            | CPU Clock Output   |  |

### 5.0 CPU Architecture

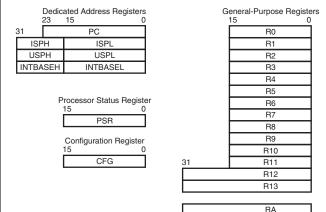

The CP3BT13 uses the CR16C third-generation 16-bit CompactRISC processor core. The CPU implements a Reduced Instruction Set Computer (RISC) architecture that allows an effective execution rate of up to one instruction per clock cycle. For a detailed description of the CPU16C architecture, see the *CompactRISC CR16C Programmer's Reference Manual* which is available on the National Semiconductor web site (http://www.nsc.com).

The CR16C CPU core includes these internal registers:

- General-purpose registers (R0-R13, RA, and SP)

- Dedicated address registers (PC, ISP, USP, and INT-BASE)

- Processor Status Register (PSR)

- Configuration Register (CFG)

The R0-R11, PSR, and CFG registers are 16 bits wide. The R12, R13, RA, SP, ISP and USP registers are 32 bits wide. The PC register is 24 bits wide. Figure 1 shows the CPU registers.

DS004

Figure 1. CPU Registers

Some register bits are designated as "reserved." Software must write a zero to these bit locations when it writes to the register. Read operations from reserved bit locations return undefined values.

### 5.1 GENERAL-PURPOSE REGISTERS

The CompactRISC CPU features 16 general-purpose registers. These registers are used individually as 16-bit operands or as register pairs for operations on addresses greater than 16 bits.

- General-purpose registers are defined as R0 through R13, RA, and SP.

- Registers are grouped into pairs based on the setting of the Short Register bit in the Configuration Register (CFG.SR). When the CFG.SR bit is set, the grouping of register pairs is upward-compatible with the architecture of the earlier CR16A/B CPU cores: (R1,R0), (R2,R1) ... (R11,R10), (R12\_L, R11), (R13\_L, R12\_L), (R14\_L, R13\_L) and SP. (R14\_L, R13\_L) is the same as (RA,ERA).

■ When the CFG.SR bit is clear, register pairs are grouped in the manner used by native CR16C software: (R1,R0), (R2,R1) ... (R11,R10), (R12\_L, R11), R12, R13, RA, SP. R12, R13, RA, and SP are 32-bit registers for holding addresses greater than 16 bits.

With the recommended calling convention for the architecture, some of these registers are assigned special hardware and software functions. Registers R0 to R13 are for general-purpose use, such as holding variables, addresses, or index values. The SP register holds a pointer to the program runtime stack. The RA register holds a subroutine return address. The R12 and R13 registers are available to hold base addresses used in the index addressing mode.

If a general-purpose register is specified by an operation that is 8 bits long, only the lower byte of the register is used; the upper part is not referenced or modified. Similarly, for word operations on register pairs, only the lower word is used. The upper word is not referenced or modified.

#### 5.2 DEDICATED ADDRESS REGISTERS

The CR16C has four dedicated address registers to implement specific functions: the PC, ISP, USP, and INTBASE registers.

### 5.2.1 Program Counter (PC) Register

The 24-bit value in the PC register points to the first byte of the instruction currently being executed. CR16C instructions are aligned to even addresses, therefore the least significant bit of the PC is always 0. At reset, the PC is initialized to 0 or an optional predetermined value. When a warm reset occurs, value of the PC prior to reset is saved in the (R1,R0) general-purpose register pair.

### 5.2.2 Interrupt Stack Pointer (ISP)

The 32-bit ISP register points to the top of the interrupt stack. This stack is used by hardware to service exceptions (interrupts and traps). The stack pointer may be accessed as the ISP register for initialization. The interrupt stack can be located anywhere in the CPU address space. The ISP cannot be used for any purpose other than the interrupt stack, which is used for automatic storage of the CPU registers when an exception occurs and restoration of these registers when the exception handler returns. The interrupt stack grows downward in memory. The least significant bit and the 8 most significant bits of the ISP register are always 0.

### 5.2.3 User Stack Pointer (USP)

The USP register points to the top of the user-mode program stack. Separate stacks are available for user and supervisor modes, to support protection mechanisms for multitasking software. The processor mode is controlled by the U bit in the PSR register (which is called PSR.U in the shorthand convention). Stack grow downward in memory. If the USP register points to an illegal address (any address greater than 0x00FF\_FFFF) and the USP is used for stack access, an IAD trap is taken.

U

### 5.2.4 Interrupt Base Register (INTBASE)

The INTBASE register holds the address of the dispatch table for exceptions. The dispatch table can be located anywhere in the CPU address space. When loading the INTBASE register, bits 31 to 24 and bit 0 must written with 0.

### 5.3 PROCESSOR STATUS REGISTER (PSR)

Ν

The PSR provides state information and controls operating modes for the CPU. The format of the PSR is shown below.

| 15 12    | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|----------|----|----|---|---|---|---|---|---|---|---|---|---|

| Reserved | Ι  | Р  | Ε | 0 | Ν | Z | F | 0 | U | L | Т | С |

C The Carry bit indicates whether a carry or borrow occurred after addition or subtraction.

0 - No carry or borrow occurred.

1 - Carry or borrow occurred.

T The Trace bit enables execution tracing, in which a Trace trap (TRC) is taken after every instruction. Tracing is automatically disabled during the execution of an exception handler.

0 - Tracing disabled.

1 - Tracing enabled.

L The Low bit indicates the result of the last comparison operation, with the operands interpreted as unsigned integers.

Second operand greater than or equal to first operand.

1 — Second operand less than first operand. The User Mode bit controls whether the CPU is in user or supervisor mode. In supervisor mode, the SP register is used for stack operations. In user mode, the USP register is used instead. User mode is entered by executing the Jump USR instruction. When an exception is taken, the exception handler automatically begins execution in supervisor mode. The USP register is accessible using the Load Processor Register (LPR/LPRD) instruction in supervisor mode. In user mode, an attempt to access the USP register generates a UND

0 - CPU is executing in supervisor mode.

1 – CPU is executing in user mode.

F The Flag bit is a general condition flag for signalling exception conditions or distinguishing the results of an instruction, among other thing uses. For example, integer arithmetic instructions use the F bit to indicate an overflow condition after an addition or subtraction operation.

Z The Zero bit is used by comparison operations. In a comparison of integers, the Z bit is set if the two operands are equal. If the operands are unequal, the Z bit is cleared.

0 – Source and destination operands unequal.

1 – Source and destination operands equal.

The Negative bit indicates the result of the last comparison operation, with the operands interpreted as signed integers.

Second operand greater than or equal to first operand.

1 — Second operand less than first operand. The Local Maskable Interrupt Enable bit enables or disables maskable interrupts. If this bit and the Global Maskable Interrupt Enable (I) bit are both set, all interrupts are enabled. If either of these bits is clear, only the non-maskable interrupt is enabled. The E bit is set by the Enable Interrupts (EI) instruction and cleared by the Disable Interrupts (DI) instruction

0 - Maskable interrupts disabled.

1 - Maskable interrupts enabled.

The Trace Trap Pending bit is used together with the Trace (T) bit to prevent a Trace (TRC) trap from occurring more than once for one instruction. At the beginning of the execution of an instruction, the state of the T bit is copied into the P bit. If the P bit remains set at the end of the instruction execution, the TRC trap is taken.

0 - No trace trap pending.

1 - Trace trap pending.

The Global Maskable Interrupt Enable bit is used to enable or disable maskable interrupts. If this bit and the Local Maskable Interrupt Enable (E) bit are both set, all maskable interrupts are taken. If either bit is clear, only the non-maskable interrupt is taken. Unlike the E bit, the I bit is automatically cleared when an interrupt occurs and automatically set upon completion of an interrupt handler.

0 - Maskable interrupts disabled.

1 – Maskable interrupts enabled.

Bits Z, C, L, N, and F of the PSR are referenced from assembly language by the condition code in conditional branch instructions. A conditional branch instruction may cause a branch in program execution, based on the value of one or more of these PSR bits. For example, one of the Bcond instructions, BEQ (Branch EQual), causes a branch if the PSR.Z bit is set.

On reset, bits 0 through 11 of the PSR are cleared, except for the PSR.E bit, which is set. On warm reset, the values of each bit before reset are copied into the R2 general-purpose register. Bits 4 and 8 of the PSR have a constant value of 0. Bits 12 through 15 are reserved. In general, status bits are modified only by specific instructions. Otherwise, status bits maintain their values throughout instructions which do not implicitly affect them.

### 5.4 CONFIGURATION REGISTER (CFG)

The CFG register is used to enable or disable various operating modes and to control optional on-chip caches. Because the CP3BT13 does not have cache memory, the cache control bits in the CFG register are reserved. All CFG bits are cleared on reset.

| 15  | 1      | 0 | 9  | 8  | 7 | 6 | 5     | 2   | 1 | 0 |

|-----|--------|---|----|----|---|---|-------|-----|---|---|

| Res | served |   | SR | ED | 0 | 0 | Reser | ved | 0 | 0 |

ED

SR

The Extended Dispatch bit selects whether the size of an entry in the interrupt dispatch table (IDT) is 16 or 32 bits. Each entry holds the address of the appropriate exception handler. When the IDT has 16-bit entries, and all exception handlers must reside in the first 128K of the address space. The location of the IDT is held in the INTBASE register, which is not affected by the state of the ED bit.

0 - Interrupt dispatch table has 16-bit entries.

1 — Interrupt dispatch table has 32-bit entries. The Short Register bit enables a compatibility mode for the CR16B large model. In the CR16C core, registers R12, R13, and RA are extended to 32 bits. In the CR16B large model, only the lower 16 bits of these registers are used, and these "short registers" are paired together for 32-bit operations. In this mode, the (RA, R13) register pair is used as the extended RA register, and address displacements relative to a single register are supported with offsets of 0 and 14 bits in place of the index addressing with these displacements.

0-32-bit registers are used.

1 – 16-bit registers are used (CR16B mode).

www.national.com

19

#### 5.5 **ADDRESSING MODES**

The CR16C CPU core implements a load/store architecture, in which arithmetic and logical instructions operate on register operands. Memory operands are made accessible in registers using load and store instructions. For efficient implementation of I/O-intensive embedded applications, the architecture also provides a set of bit operations that operate on memory operands.

The load and store instructions support these addressing modes: register/pair, immediate, relative, absolute, and index addressing. When register pairs are used, the lower bits are in the lower index register and the upper bits are in the higher index register. When the CFG.SR bit is clear, the 32bit registers R12, R13, RA, and SP are also treated as register pairs.

References to register pairs in assembly language use parentheses. With a register pair, the lower numbered register pair must be on the right. For example,

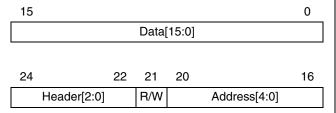

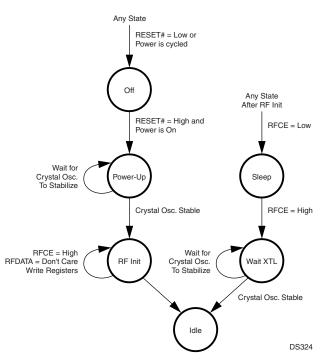

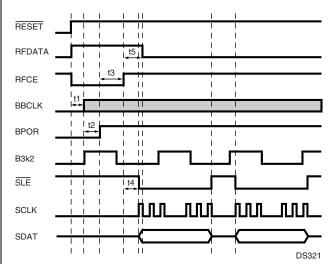

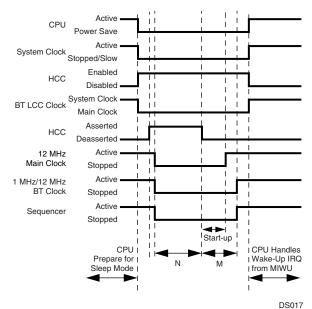

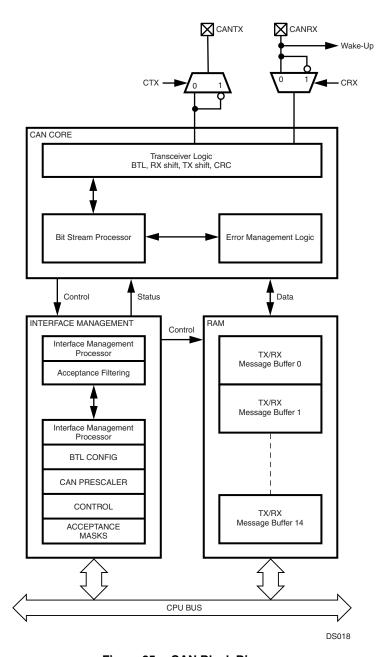

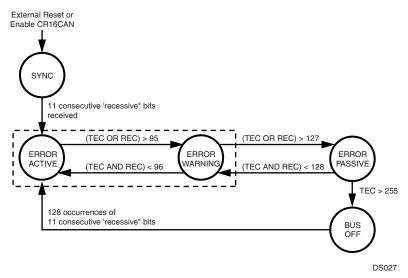

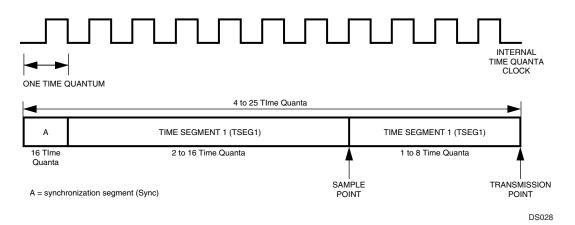

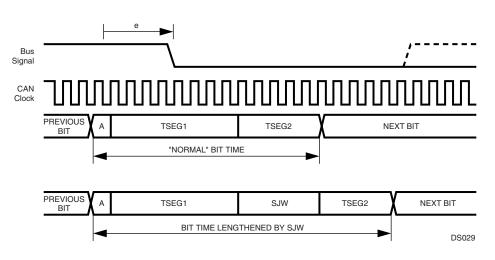

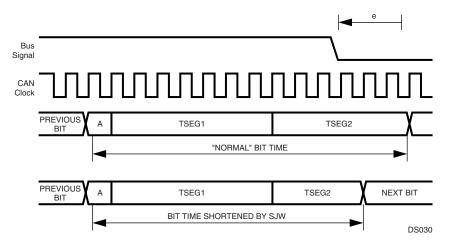

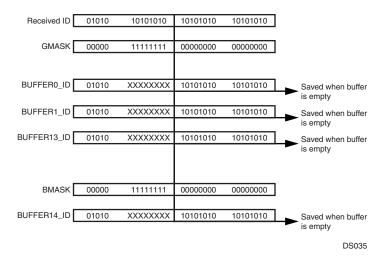

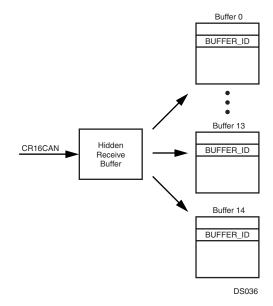

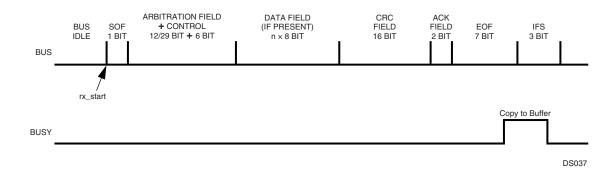

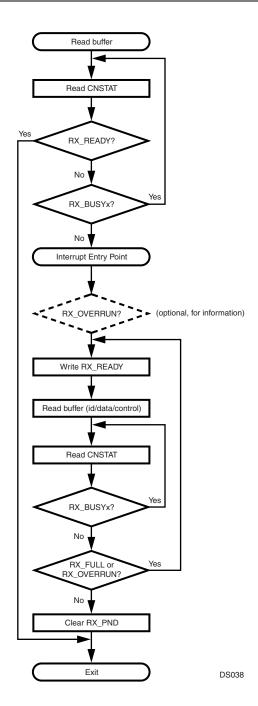

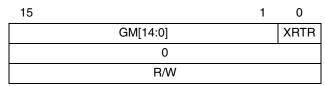

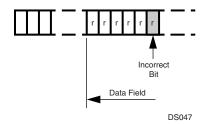

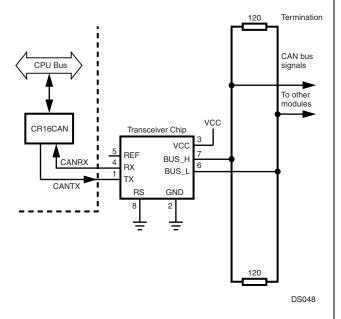

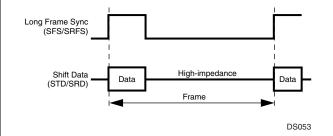

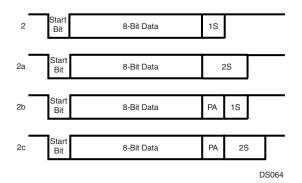

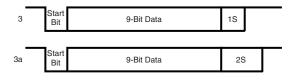

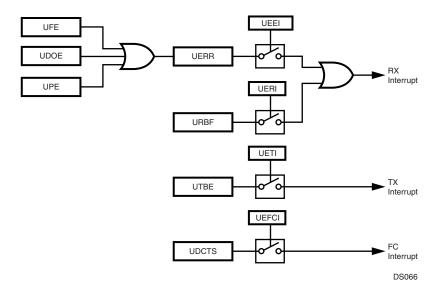

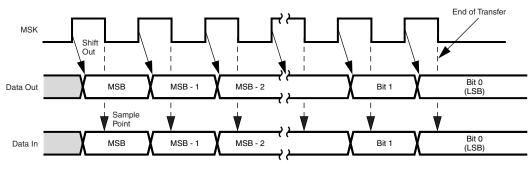

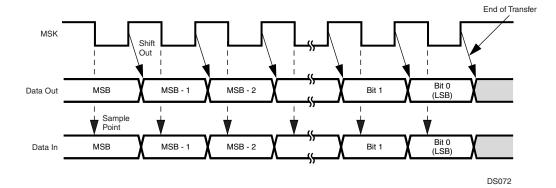

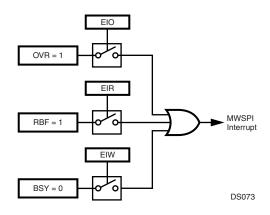

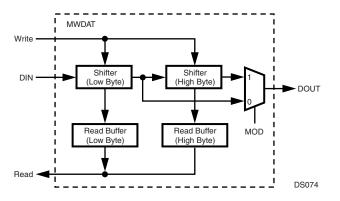

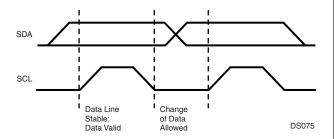

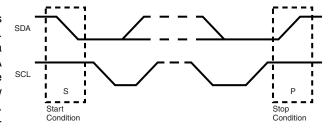

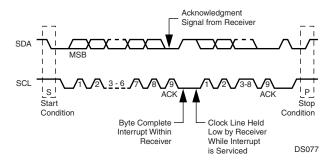

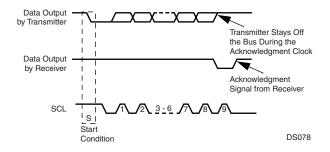

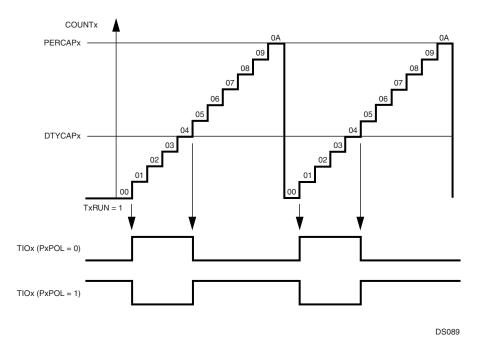

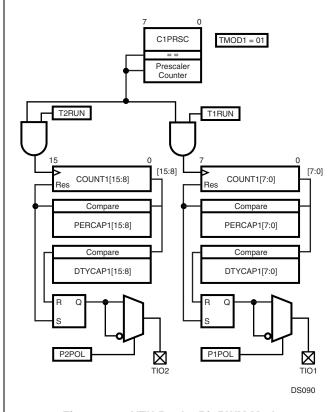

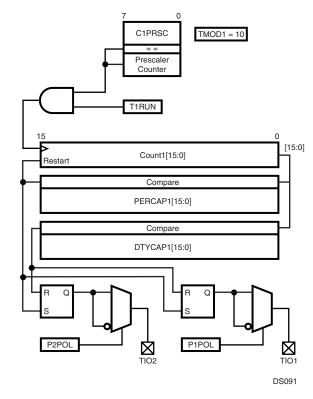

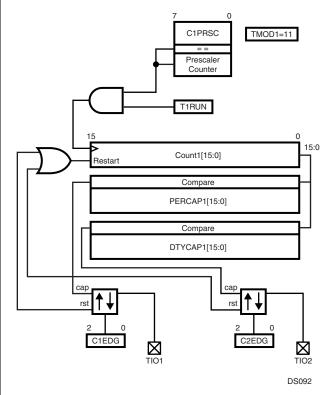

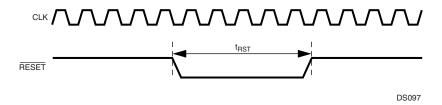

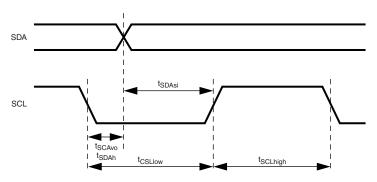

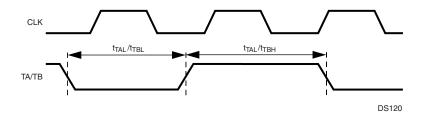

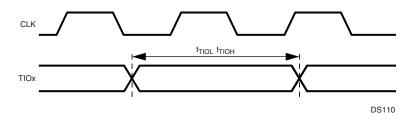

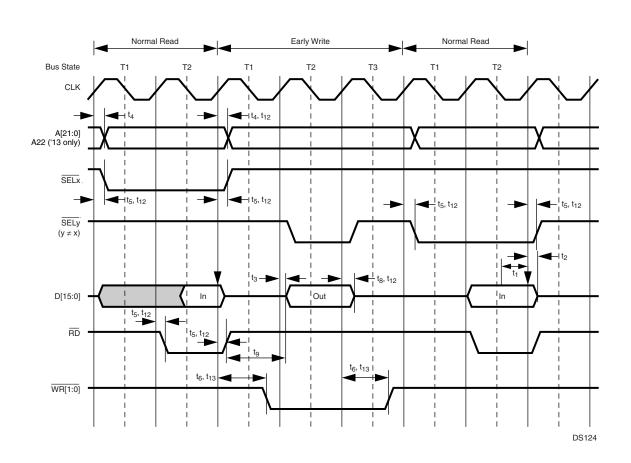

jump (r5, r4) load \$4(r4,r3), (r6,r5) load \$5(r12), (r13)