# nanoSmart® Ultra-Low-Power Linear Regulator

### **DESCRIPTIONS**

The TS14001 linear regulator is an ultra-low-power circuit which draws low nA level quiescent current at light load, but has the capability to regulate current loads as high as 200mA.

## **APPLICATIONS**

- Portable electronics

- RFID

- Industrial

- Medical

- Energy harvesting systems

- SmartCard

### **FEATURES**

- Ultra-low nA operating current at light load

- Best-in-class quiescent current of 20nA at I<sub>load</sub>=0

- Best-in-class quiescent current of 100pA in disable mode

- Output voltage options of 1.2V 4.2V in 100mV steps (programmed at manufacturing)

- Accurate output regulation

- Over-current protection

### **SUMMARY SPECIFICATIONS**

- Low input operating voltage of 2.5V to 5.5V

- Packaged in a 8pin VDFN (2x2)

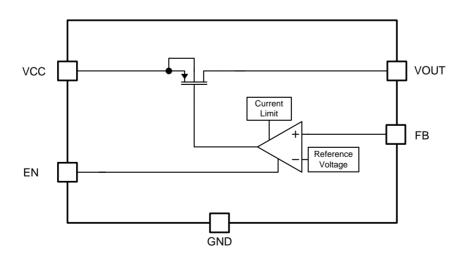

## **Block Diagram**

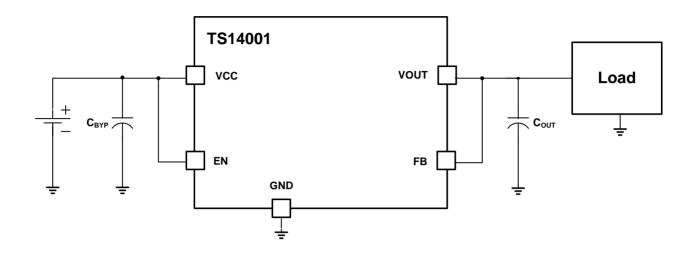

### TYPICAL APPLICATION

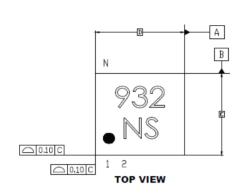

### **PIN-OUT CONFIGURATION**

| PIN# | NAME      | I/O/P | DESCRIPTION                          |

|------|-----------|-------|--------------------------------------|

| 1    | GND       | Р     | Ground                               |

| 2    | $V_{OUT}$ | 0     | Regulated Output Voltage             |

| 3    | NC        |       | No Connect (connect to GND or float) |

| 4    | NC        |       | No Connect (connect to GND or float) |

| 5    | NC        |       | No Connect (connect to GND or float) |

| 6    | FB        | 1     | Feedback Input                       |

| 7    | $V_{CC}$  | Р     | Input Power                          |

| 8    | EN        | I     | Enable Input                         |

### ABSOLUTE MAXIMUM RATINGS

Over operating free-air temperature range unless otherwise noted (1,2,3)

| PIN / PARAMETER                                      | VALUE       | UNIT |

|------------------------------------------------------|-------------|------|

| $V_{CC}$ , $V_{OUT}$ , EN, FB                        | -0.3 to 6.0 | V    |

| Electrostatic Discharge (Human Body Model)           | 2           | kV   |

| Operating Junction Temperature Range, T <sub>J</sub> | -20 to 85   | °C   |

| Storage Temperature Range, T <sub>STG</sub>          | -65 to 150  | °C   |

| Lead Temperature (soldering, 10 seconds)             | 260         | °C   |

Note 1: Stresses beyond those listed under "absolute maximum ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated under "recommended operating conditions" is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

Note 2: All voltage values are with respect to network ground terminal.

Note 3: ESD testing is performed according to the respective JESD22 JEDEC standard.

### THERMAL CHARACTERISTICS

| Package | θ <sub>JA</sub> (°C/W) | θ <sub>JC</sub> (°C/W) |

|---------|------------------------|------------------------|

| DFN     | (See Note 4)           | (See Note 5)           |

| 8 pin   | 73.1                   | 10.7                   |

Note 4: This assumes a FR4 board only.

Note 5: This assumes a 1oz. Copper JEDEC standard board with thermal vias. See Exposed Pad section and application note for more information.

### RECOMMENDED OPERATING CONDITIONS

| Parameter                                                   | Min | Тур | Max | Unit |

|-------------------------------------------------------------|-----|-----|-----|------|

| Unregulated Supply Input Voltage (V <sub>CC</sub> )         | 2.5 |     | 5.5 | V    |

| Enable Input (EN)                                           | 0   |     | 5   | V    |

| Regulated Supply Output Voltage (V <sub>OUT</sub> ) typical | 1.2 |     | 4.2 | V    |

| Operating Ambient Temperature, T <sub>A</sub> (Note 6)      | -40 |     | 55  | °C   |

| Operating Junction Temperature, T <sub>J</sub>              | -40 |     | 85  | °C   |

| Input Bypass Capacitor (C <sub>BYP</sub> )                  |     | 2.2 |     | uF   |

| Output Bypass Capacitor (C <sub>OUT</sub> )                 | 1   | 2.2 | 4.7 | uf   |

Note 6: TA Max shown here is a guideline. Higher TA can be tolerated if TJ does not exceed the Absolute Maximum Rating.

### **CHARACTERISTICS**

Electrical characteristics,  $V_{CC} = 2.5V$  to 5V,  $T_{J} = 25C$ , unless otherwise noted

| Symbol                  | Parameter                          | Condition                                                | Min     | Тур | Max     | Unit |

|-------------------------|------------------------------------|----------------------------------------------------------|---------|-----|---------|------|

| VBAT                    | Input Supply Voltage               |                                                          | 2.5     |     | 5.5     | V    |

| Vil <sub>EN</sub>       | Input Low Logic Level              |                                                          |         |     | 0.3*VCC | V    |

| Vih <sub>EN</sub>       | Input High Logic Level             |                                                          | 0.7*VCC |     |         | V    |

| l <sub>qq</sub>         | Quiescent Current                  | $V_{CC} = 2.5V$ to 5.5V, $I_{OUT} = 0$                   |         | 20  |         | nA   |

| I <sub>qq-disable</sub> | Quiescent Current:<br>Disable Mode | I <sub>OUT</sub> = 0, EN = 0                             |         | 100 |         | рА   |

|                         |                                    | $V_{CC} = V_{CC\_MIN}, I_{OUT} = 200mA$ (Note 7)         |         | 200 |         | uA   |

| I <sub>op-gnd</sub>     | Operating Current                  | $V_{CC} = V_{CC\_NOM}, I_{OUT} = 200mA$ (Note 7)         |         | 200 |         | uA   |

|                         |                                    | $V_{CC} = V_{CC\_MAX}, I_{OUT} = 200 \text{mA}$ (Note 7) |         | 200 |         | uA   |

| 1 .                     | Load Capability                    | Vout <sub>nominal</sub> from 1.2V to 3.5V                | 0       |     | 200     | mA   |

| l <sub>out</sub>        | Load Capability                    | $Vout_{nominal} > 3.5V$                                  | 0       |     | 100     | 1117 |

Note 7: If  $Vout_{nominal} < 2.5V$ , then  $V_{CC\_MIN} = 2.5V$ , otherwise  $V_{CC\_MIN} = Vout + 0.3V$ .  $V_{CC\_MAX}$  is always 5.5V.  $V_{CC\_NOM}$  is the average of  $V_{CC\_MAX}$  and  $V_{CC\_MIN}$ .

## **CHARACTERISTICS CONTINUED**

Electrical characteristics,  $V_{CC} = 2.5V$  to 5V,  $T_J = 25C$ , unless otherwise noted

| Symbol             | Parameter            | Condition                                                                                     | Min | Тур | Max | Unit |

|--------------------|----------------------|-----------------------------------------------------------------------------------------------|-----|-----|-----|------|

| V                  | DC Line Describation | $V_{CC} = V_{CC\_MIN}$ to $V_{CC\_MAX}$ ,<br>$V_{OUT} = 1.8V$ to $4.2V$ ,<br>$I_{OUT} = 50mA$ |     | 0.5 | 4   | %    |

| $V_{Line}$         | DC Line Regulation   | $V_{CC} = V_{CC\_MIN}$ to $V_{CC\_MAX}$ ,<br>$V_{OUT} < 1.8V$ ,<br>$I_{OUT} = 50$ mA          |     |     | 4   | %    |

| $V_{Load}$         | DC Load Regulation   | $V_{CC} = V_{CC\_NOM}$ , $I_{OUT} = 0.02$ mA to 200mA,                                        |     | 1   | 3   | %    |

| 1                  | Current Limit        | $I_{OUT}$ measured at $V_{OUT} = 0.9*Vout_{nominal}$ ; $Vout_{nominal}$ from 1.2V to 3.5V     |     | 250 |     | - mA |

| I <sub>limit</sub> |                      | $I_{OUT}$ measured at $V_{OUT} = 0.9*Vout_{nominal}$ ; $Vout_{nominal} > 3.5V$                |     | 175 |     |      |

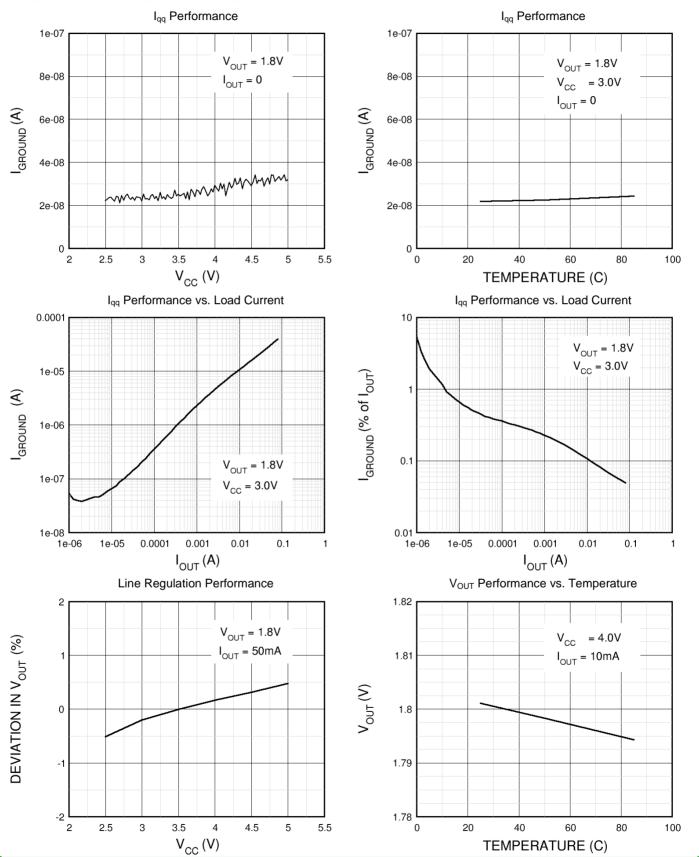

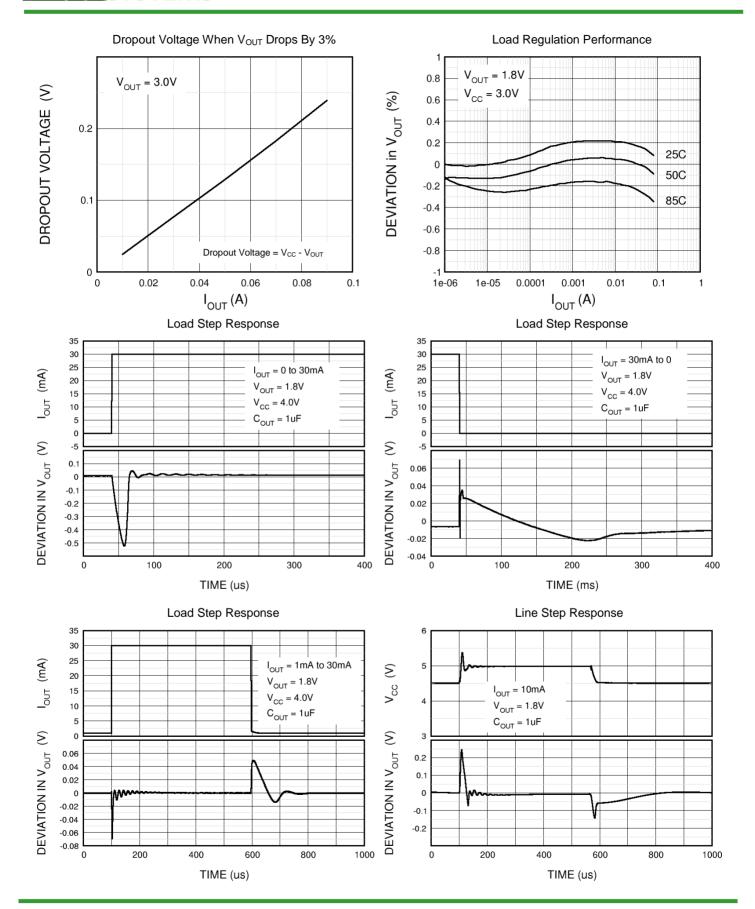

### TYPICAL CHARACTERISTICS

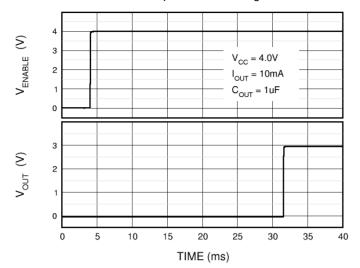

### Output Enable Timing

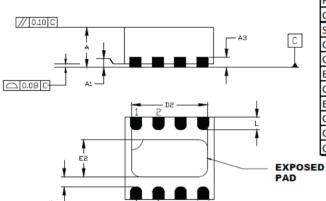

### PACKAGE MECHANICAL DRAWINGS

**BOTTOM VIEW**

⊕ 0.10 M C A B 0.05 M C

|                        | MILLIMETERS                 |          |          |      |

|------------------------|-----------------------------|----------|----------|------|

| D                      | Dimensions Limits           |          | NOM      | MAX  |

| Number of Pins         | 8                           |          |          |      |

| Pitch                  | е                           |          | 0.50 BSC |      |

| Overall Height         | Α                           | 0.80     | 0.90     | 1.00 |

| Standoff               | A1                          | 0.00     | 0.02     | 0.05 |

| Contact Thickness      | ntact Thickness A3 0.20 REF |          |          |      |

| Overall Length         | D                           | 2.00 BSC |          |      |

| Exposed Pad Width      | E2                          | 0.75     | 0.90     | 1.00 |

| Overall Width          | E                           | 2.00 BSC |          |      |

| Exposed Pad Length     | D2                          | 1.55     | 1.70     | 1.80 |

| Contact Width          | b                           | 0.18     | 0.25     | 0.30 |

| Contact Length         | L                           | 0.20     | 0.30     | 0.40 |

| Contact-to-Exposed Pad | K                           | 0.20     | -        | -    |

#### Notes:

Dimensions and tolerancing per ASME Y14.5M

BSC: Basic Dimension. Theoretically exact value shown without tolerances. REF: Refernce Dimension, usually without tolerance, for information only.

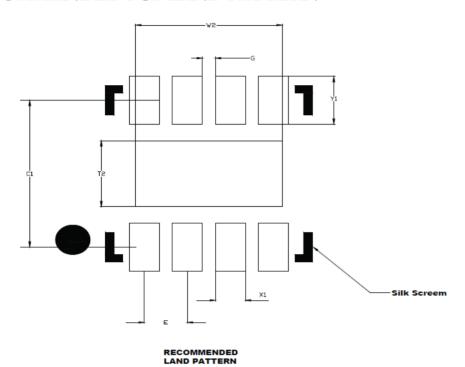

## RECOMMENDED PCB LAND PATTERN

|                            | 1  | MILLIMETER | RS       |      |

|----------------------------|----|------------|----------|------|

| Dimension Limits           |    | MIN        | NOM      | MAX  |

| Contact Pitch E            |    |            | 0.50 BSC |      |

| Optional Center Pad Width  | W2 | -          | -        | 1.70 |

| Optional Center Pad Length | T2 | -          | -        | 0.90 |

| Contact Pad Spacing        | C1 | -          | 2.00     | -    |

| Contact Pad Width (X8)     | X1 | -          | -        | 0.35 |

| Contact Pad Length (X8)    | Y1 | -          | -        | 0.65 |

| Distance Between Pads      | G  | 0.15       | -        | -    |

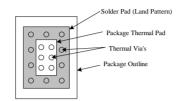

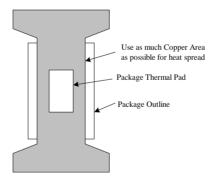

### APPLICATION USING A MULTI-LAYER PCB

To maximize the efficiency of this package for application on a single layer or multi-layer PCB, certain guidelines must be followed when laying out this part on the PCB.

The following are guidelines for mounting the exposed pad IC on a Multi-Layer PCB with ground a plane.

Package and PCB Land Configuration For a Multi-Layer PCB

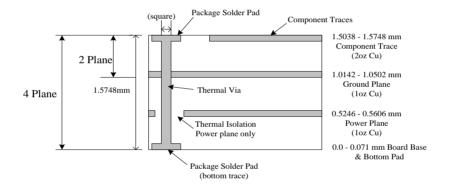

#### **JEDEC standard FR4 PCB Cross-section:**

Multi-Layer Board (Cross-sectional View)

In a multi-layer board application, the thermal vias are the primary method of heat transfer from the package thermal pad to the internal ground plane. The efficiency of this method depends on several factors, including die area, number of thermal vias, thickness of copper, etc.

Note: NOT to Scale

The above drawing is a representation of how the heat can be conducted away from the die using an exposed pad package. Each application will have different requirements and limitations and therefore the user should use sufficient copper to dissipate the power in the system. The output current rating for the linear regulators may have to be de-rated for ambient temperatures above 85C. The de-rate value will depend on calculated worst case power dissipation and the thermal management implementation in the application.

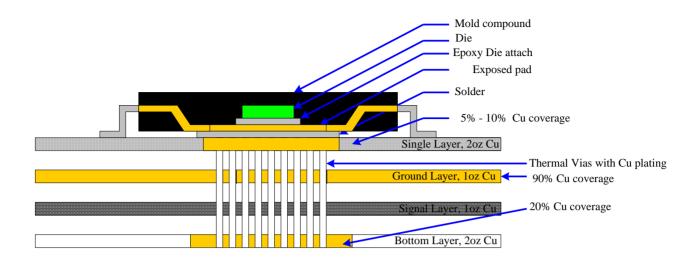

### APPLICATION USING A SINGLE LAYER PCB

Layout recommendations for a Single Layer PCB: utilize as much Copper Area for Power Management. In a single layer board application the thermal pad is attached to a heat spreader (copper areas) by using low thermal impedance attachment method (solder paste or thermal conductive epoxy).

In both of the methods mentioned above it is advisable to use as much copper traces as possible to dissipate the heat.

#### **IMPORTANT:**

If the attachment method is NOT implemented correctly, the functionality of the product is not guaranteed. Power dissipation capability will be adversely affected if the device is incorrectly mounted onto the circuit board.

## **ORDERING INFORMATION**

### TS14001-CvvvDFNR

| vvv | Output Voltage* |

|-----|-----------------|

| 012 | 1.2 V           |

| 018 | 1.8 V           |

| 025 | 2.5 V           |

| 033 | 3.3 V           |

| 042 | 4.2 V           |

<sup>\*</sup> Custom values also available (1.2V - 4.2V typical in 100mV increments)

#### **Legal Notices**

Information contained in this publication regarding device applications and the like is provided only for your convenience and may be superseded by updates. It is your responsibility to ensure that your application meets with your specifications. "Typical" parameters which may be provided in Triune Systems data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for your application by your technical experts. TRIUNE SYSTEMS MAKES NO REPRESENTATIONS OR WARRANTIES OF ANY KIND WHETHER EXPRESS OR IMPLIED, WRITTEN OR ORAL, STATUTORY OR OTHERWISE, RELATED TO THE INFORMATION, INCLUDING BUT NOT LIMITED TO ITS CONDITION, QUALITY, PERFORMANCE, MERCHANTABILITY OR FITNESS FOR PURPOSE. Triune Systems disclaims all liability arising from this information and its use. Triune System products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other applications intended to support or sustain life, or for any other application in which the failure of the Triune Systems product could create a situation where personal injury or death may occur. Should the Buyer purchase or use Triune Systems products for any such unintended or unauthorized application, the Buyer shall indemnify and hold Triune Systems, and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that Triune Systems was negligent regarding the design or manufacture of the part. No licenses are conveyed, implicitly or otherwise, under any Triune Systems intellectual property rights.

#### **Trademarks**

The Triune Systems® name and logo, MPPT-lite™, and nanoSmart® are trademarks of Triune Systems, LLC. in the U.S.A..

All other trademarks mentioned herein are property of their respective companies.

© 2012 Triune Systems, LLC. All Rights Reserved.

# **Mouser Electronics**

**Authorized Distributor**

Click to View Pricing, Inventory, Delivery & Lifecycle Information:

# Triune Systems:

TS14001-C012DFNR TS14001-C018DFNR TS14001-C025DFNR TS14001-C033DFNR