# True Single Chip Multi-Mode Wireless Power Receiver IC

### **Preliminary Datasheet Short Form**

### **Features**

- Single Chip Solution for Wireless Power Consortium (WPC)

"Qi" compliant wireless power receiver designs

- Designed to meet WPC specifications, with up to 7.5W power delivery in proprietary mode

- Integrated Synchronous Full-Bridge Rectifier

- Integrated Synchronous Buck Converter

- Embedded MCU, ROM, RAM, & ADC

- Integrated USB Adaptor Switches for USB charging

- Supports proprietary power transmission protocols in addition to Qi with dynamic switching capability

- Closed Loop Power Transfer control between Base Station and Mobile Device

- Proprietary Base to Mobile Communication for Authentication

- Programmable option for added security and encryption up to 64 bit for 2-way authentication

- Multi-layer advanced Foreign Object Detection (FOD) for safety

- Over Temperature, Voltage, Current Protection

- Thermal Loop Control

- Compatible with all WPC receiver coils including proprietary and PCB based coils

- Power Good Status Pin

- Open Drain Coupling LED indicator Outputs

- I2C Interface

- Packages 7x7-56 TQFN, 4.6 x 4.9 WLCSP

|                | WPC Mode | Proprietary Modes |

|----------------|----------|-------------------|

| Output Power   | 5W       | 7.5W              |

| Authentication | OFF      | ON                |

| Foreign Object | 1,2      | 1,2,3,4           |

| Detection      |          | K A '             |

| Channel        | RX→TX    | RX→TX & TX→RX     |

| Communication  |          |                   |

### **Description**

The IDTP9020 is a highly-integrated single-chip, multi-mode wireless power receiver IC. The device enables conversion of AC power provided via an inductively coupled coil (from a compatible wireless transmitter) into a regulated 5V output voltage, which can be used to power devices or supply the charger input in mobile applications. The IDTP9020 integrates a high-efficiency synchronous full bridge rectifier, high efficiency synchronous buck converter, and control circuits used to modulate the load to transmit WPC compliant message packets to the transmitter station to optimize power delivery. In WPC mode, power delivery is limited to 5W in accordance with the Qi specification, while up 7.5W power may be delivered in proprietary modes.

The IDTP9020 may be operated in proprietary modes where additional enhanced functions such as multi layered Foreign Object Detection (FOD), 2-way secure authentication, and higher-efficiency control algorithms may be employed.

The device includes over temperature/voltage/current protection and up to four levels of advanced Foreign Object Detection (FOD) (when used with IDT's IDTP9030 transmitter) to ensure safety of the base station and mobile device from over-heating in the presence of a metallic foreign objects. Power transfer fault conditions are managed by the embedded MCU and controls status LEDs indicate operating and fault modes.

### **Applications**

- WPC Compliant or Non-WPC Wireless Receiver Solutions for Mobile Applications

- Mobile and Smart Phones

- Tablets, MIDs

- Digital Camera, MP3 Player

- Remote controls

- GPS, and more....

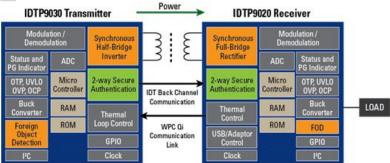

Figure 1 - IDT Power Transfer/Data Communication System Block Diagram

### **ABSOLUTE MAXIMUM RATINGS**

**Table 1: Absolute Maximum Ratings Summary**

| Symbol                                                                                | Description                              | Value      | Units |

|---------------------------------------------------------------------------------------|------------------------------------------|------------|-------|

| INP, INM, Z <sub>REFP</sub> , Z <sub>REFM</sub> , A <sub>CMP</sub> , A <sub>CMM</sub> | Input voltage                            | -1 to 24V  | V     |

| T <sub>J</sub>                                                                        | Junction Temperature Range               | -40 to 150 | °C    |

| T <sub>LEAD</sub>                                                                     | Maximum Soldering Temperature (at Leads) | 300        | °C    |

| ESD                                                                                   | ESD rating, Human Body Model             | +/- 2000   | ٧     |

Stresses greater than those listed under Absolute Maximum Ratings may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect reliability.

The maximum power dissipation is  $P_{D(MAX)} = (T_{J(MAX)}-T_A)/\theta_{JA}$  where  $T_{J(MAX)}$  is 125°C. Exceeding the maximum allowable power dissipation will result in excessive die temperature, and the device will enter thermal shutdown.

**Table 2: Package Thermal Resistivity**

| Symbol        | Description                             | Value | Units |

|---------------|-----------------------------------------|-------|-------|

| $\Theta_{JA}$ | Maximum Thermal Resistance (TQFN 7 x 7) | TBD   | °C/W  |

| $\Theta_{JA}$ | Maximum Thermal Resistance (WLCSP-TBD)  | TBD   | °C/W  |

This thermal rating was calculated based on a JEDEC standard 4-layer board with dimensions 4in x 4.5in in still air conditions. Actual thermal resistance will be affected by PCB size, solder joint quality, PCB layer count, copper thickness, air flow, altitude, and other unlisted variables.

# **SPECIFICATION TABLE**

$T_J$  = -40 to +125°C, unless otherwise noted.

| Symbol                  | Description                                    | Conditions                    | Min | Тур | Max | Units |

|-------------------------|------------------------------------------------|-------------------------------|-----|-----|-----|-------|

| Synchronous             | Full Bridge Rectifier (SFBR)                   | )                             |     |     | 4   |       |

| $V_{\text{IN,AC}}$      | Input voltage to SFBR                          | f <sub>PWM</sub> = 110-205kHz |     |     | +24 | V     |

| I <sub>RECT</sub>       | Current from rectified voltage pin             |                               |     |     | 1.5 | Α     |

| $V_{DSMAX}$             | Maximum drain to source voltage on SFBR switch | 24                            | V   |     |     |       |

| R <sub>LOAD,MIN</sub>   | Minimum on-chip load                           | f <sub>PWM</sub> = 110-205kHz | 1   |     | 5   | kΩ    |

| Modulation              |                                                |                               |     |     |     |       |

| ····oualatioii          |                                                | RX Coil A                     |     |     |     |       |

| C <sub>MOD AC</sub>     | AC modulation capacitor                        |                               |     | 47  |     | nF    |

| R <sub>DS</sub> -       | Mosfet on resistance                           |                               | 0.5 |     | 4   |       |

| ON,CMOD AC              | driving C <sub>MOD</sub>                       |                               | 0.5 | 2   | 4   | Ω     |

|                         |                                                |                               |     |     |     |       |

|                         |                                                | RX Coil B                     |     |     | 1   |       |

| C <sub>MOD AC</sub>     | AC modulation capacitor                        |                               | A   | 47  |     | nF    |

| R <sub>DS</sub> -       | Mosfet on resistance                           |                               | 0.5 | 2   | 4   | Ω     |

| ON,CMOD AC              | driving C <sub>MOD</sub>                       |                               |     |     |     |       |

|                         |                                                | RX Coil C                     |     |     |     |       |

| C <sub>MOD</sub>        | AC modulation capacitor                        | RX con c                      |     | 47  |     | nF    |

| R <sub>DS-ON,CMOD</sub> | Mosfet on resistance driving C <sub>MOD</sub>  |                               | 0.5 | 2   | 4   | Ω     |

|                         | T GIVING OMOD                                  |                               |     |     |     |       |

|                         |                                                | RX Coil D                     |     |     |     |       |

| C <sub>MOD</sub>        | AC modulation capacitor                        |                               |     | 22  |     | nF    |

| R <sub>DS-ON,CMOD</sub> | Mosfet on resistance                           | *                             | 0.5 | 2   | 4   | Ω     |

| - 103-011,01100         | driving C <sub>MOD</sub>                       |                               |     |     |     |       |

|                         |                                                |                               |     |     |     |       |

| Analog to Dig           | ital Converter                                 |                               |     |     |     |       |

| N                       | Resolution                                     |                               |     | 12  |     | Bit   |

| fSAMPLE                 | Sampling Rate                                  |                               |     | ·   | 125 | kSPS  |

| Channel                 | # of Channel                                   |                               | 8   |     | -   |       |

| ADC <sub>CLK</sub>      | Sampling Rate                                  |                               | -   |     | 2   | MHz   |

| INL                     | Integral Non Linearity                         |                               |     |     | ±2  | LSB   |

| DNL                     | Differential Non Linearity                     |                               |     |     | ±2  | LSB   |

| V <sub>IN,FS</sub>      | Full scale Input voltage                       |                               | 0   |     | TBD | V     |

| I <sub>QUIESENT</sub>   | Quiesent current                               |                               |     |     | 600 | μΑ    |

| V <sub>REF</sub>        | Reference voltage                              |                               |     | TBD |     | V     |

| PSRR                    | Power Supply Rejection                         |                               | TBD |     |     | dB    |

# **SPECIFICATION TABLE (CONTINUED)**

$T_J$  = -40 to +125°C, unless otherwise noted.

| Symbol                              | Description                                   | Conditions                   | Min               | Тур | Max | Units |

|-------------------------------------|-----------------------------------------------|------------------------------|-------------------|-----|-----|-------|

| OVP/OCP/UVL                         |                                               |                              |                   |     |     |       |

| $V_{RECT,OVP}$                      | Over voltage protection for rectified voltage | I <sub>RECT</sub> =0 to 1.5A |                   |     | 20  | V     |

| 1                                   |                                               |                              |                   |     |     | V     |

| $V_{RECT,UVLO}$                     | Rising                                        |                              |                   |     | 6.5 | V     |

|                                     | Falling                                       |                              | 6                 |     |     | V     |

|                                     |                                               |                              |                   |     |     |       |

|                                     |                                               |                              |                   |     |     |       |

|                                     |                                               |                              |                   |     |     | 7     |

| DCDC Convert                        |                                               | <u> </u>                     |                   |     |     |       |

| V <sub>IN</sub>                     | Input voltage                                 |                              |                   |     | 20  | V     |

| V <sub>OUT</sub>                    | Output voltage                                |                              |                   | 5   |     | V     |

| $\Delta V_{OUT} / V_{OUT}$          | Output voltage accuracy                       |                              | -5                |     | 5   | %     |

| I <sub>OUT</sub>                    | Output current                                |                              |                   |     | 1.5 | Α     |

| Fsw                                 | Switching frequency                           |                              |                   | 3   |     | MHz   |

|                                     |                                               |                              |                   |     |     |       |

| <u> </u>                            |                                               |                              |                   |     |     |       |

| Low Drop Out                        | Regulator                                     |                              |                   |     |     |       |

| LDO2P5V                             | 1                                             |                              | 1                 | 1   | 1   |       |

| V <sub>IN</sub>                     | Input voltage                                 |                              |                   | 5   |     | V     |

| V <sub>OUT</sub>                    | Output voltage                                |                              |                   | 2.5 |     | V     |

| I <sub>OUT</sub>                    | Output current                                |                              |                   |     | 200 | mA    |

| $\Delta V_{OUT} / V_{OUT}$          | Output voltage accuracy                       |                              | -5                |     | +5  | %     |

| LDO5V                               |                                               |                              | 1                 | ı   |     |       |

| V <sub>IN</sub>                     | Input voltage                                 |                              |                   |     | 20  | V     |

| V <sub>OUT</sub>                    | Output voltage                                |                              |                   | 5   |     | V     |

| ΔV <sub>OUT</sub> /V <sub>OUT</sub> | Output voltage accuracy                       | <del></del>                  | -5                |     | +5  | %     |

| I <sub>OUT</sub>                    | Output current                                |                              |                   | 30  | 90  | mA    |

| Thermal Shutd                       | lown                                          |                              |                   | ı   |     |       |

| T <sub>SD</sub>                     | Thermal shutdown                              |                              | Threshold Rising  | 140 |     | оС    |

|                                     |                                               |                              | Threshold Falling | 110 |     | оС    |

|                                     |                                               |                              | <u> </u>          |     |     |       |

| Microcontrolle                      | or .                                          |                              |                   |     |     |       |

| FCLOCK                              | Clock frequency                               |                              |                   |     | 40  | MHz   |

| F <sub>CLOCK</sub><br>Accuracy      | Clock accuracy                                |                              | TBD               |     |     | %     |

| V <sub>IN</sub>                     | Input voltage                                 |                              |                   | 2.5 |     | V     |

# **SPECIFICATION TABLE (CONTINUED)**

$T_J$  = -40 to +125°C, unless otherwise noted.

| Symbol              | Description                                          | Conditions                                       | Min                        | Тур | Max | Units |

|---------------------|------------------------------------------------------|--------------------------------------------------|----------------------------|-----|-----|-------|

| SCL, SDA (I         | <sup>2</sup> C Interface)                            |                                                  |                            |     |     |       |

| f <sub>SCL</sub>    | Clock Frequency                                      |                                                  | 0                          | (   | 400 | kHz   |

| t <sub>LOW</sub>    | Clock Low Period                                     |                                                  | 1.3                        | 1   |     | μS    |

| t <sub>HIGH</sub>   | Clock High Period                                    |                                                  | 0.6                        | A-  |     | μS    |

| t <sub>HD,STA</sub> | Hold Time (Repeated) for START Condition             |                                                  | 0.6                        |     |     | μS    |

| t <sub>SU:STA</sub> | Set-up Time for Repeated START Condition             |                                                  | 0.6                        |     |     | μs    |

| t <sub>SU:DAT</sub> | Data Setup Time                                      |                                                  | 100                        |     | 4   | ns    |

| t <sub>HD:DAT</sub> | Data Hold Time                                       | A.                                               |                            |     | 0.9 | μs    |

| t <sub>SU:STO</sub> | Setup Time for STOP Condition                        |                                                  | 0.6                        |     |     | μs    |

| t <sub>BUF</sub>    | Bus Free Time Between<br>STOP and START<br>Condition |                                                  | 1.3                        |     |     | μs    |

| t <sub>R</sub>      | Rise Time of Both SDA and SCL Signals                |                                                  | 20 + 0.1<br>C <sub>B</sub> |     | 300 | ns    |

| t <sub>F</sub>      | Fall Time of Both SDA and SCL Signals                |                                                  | 20 + 0.1<br>C <sub>B</sub> |     | 300 | ns    |

| $T_SP$              | Spike Pulse Widths Suppressed by Input Filter        |                                                  | 0                          |     | 50  | ns    |

| Св                  | Capacitive Load for Each<br>Bus Line                 |                                                  |                            |     | 400 | pF    |

| C <sub>BIN</sub>    | SCL, SDA Input<br>Capacitance                        |                                                  |                            |     | 60  | pF    |

| V <sub>IL</sub>     | Input Threshold Low                                  | (Note 1)                                         |                            |     | 0.4 | V     |

| V <sub>IH</sub>     | Input Threshold High                                 | (Note 1)                                         | 1.4                        |     |     | V     |

| I <sub>I</sub>      | Input Leakage Current                                |                                                  | -1.0                       |     | 1.0 | μΑ    |

| V <sub>OL</sub>     | Output Logic Low (SDA)                               | I <sub>PD</sub> = 4mA (Note 1)                   |                            |     | 0.4 | V     |

| I <sub>PD</sub>     | SCL, SDA Pull-down<br>Current                        | V <sub>BAT</sub> =4.2V<br>V <sub>PIN</sub> =0.4V |                            | 0.2 |     | uA    |

| tsleep              | Bus Low Timeout                                      | (Note 3)                                         | 1.5                        |     | 2.2 | S     |

# **PIN CONFIGURATION & DESCRIPTION**

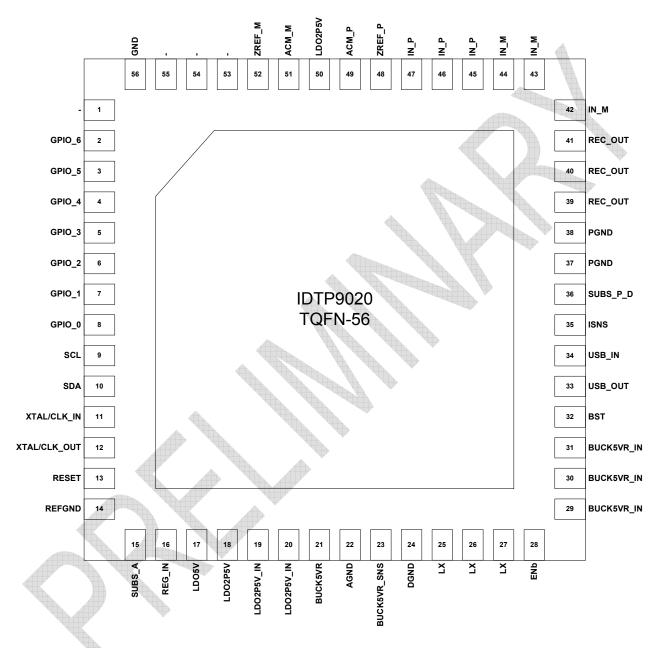

Figure 2: IDTP9020 Pin Configuration

| Pin #  |              | <b>Absolute</b> |          |                                                                                                 |

|--------|--------------|-----------------|----------|-------------------------------------------------------------------------------------------------|

| (TQFN) | Name         | Max (V)         | Туре     | Function                                                                                        |

| 1      | NC           |                 | -        |                                                                                                 |

| 2      | GPIO_6       |                 | I/O      | General purpose input/output.                                                                   |

| 3      | GPIO_5       |                 | I/O      | General purpose input/output.                                                                   |

| 4      | GPIO 4       |                 | I/O      | General purpose input/output.                                                                   |

| 5      | GPIO_3       |                 | I/O      | General purpose input/output.                                                                   |

| 6      | GPIO_2       |                 | I/O      | General purpose input/output.                                                                   |

| 7      | GPIO_2       |                 | I/O      | General purpose input/output.                                                                   |

| 8      |              |                 | I/O      | General purpose input/output.                                                                   |

|        | GPIO_0       |                 |          | System Clock                                                                                    |

| 9      | SCL          |                 | I        |                                                                                                 |

| 10     | SDA          |                 | I/O      | Data bus                                                                                        |

| 11     | XTAL/CLK_IN  |                 | I        | Crystal or clock input.                                                                         |

| 12     | XTAL/CLK_OUT |                 | 0        | Crystal or clock output.                                                                        |

| 13     | RESET        |                 | I        | Chip reset, active high.                                                                        |

| 14     | REFGND       |                 | I        | Signal ground connection.                                                                       |

| 15     | SUBS_A       |                 | I        | Analog substrate ground                                                                         |

| 16     | REG_IN       |                 | I        | Regulator power supply Input. Connect 1µF capacitor between this pin and ground.                |

| 17     | LDO5V        |                 | 0        | Regulated output.                                                                               |

| 18     | LDO2P5V      |                 | 0        | Regulated output.                                                                               |

| 19     | LDO2P5V_IN   |                 | I        | Regulator power supply input. Share 1µF input cap with LDO2P5V_IN.                              |

| 20     | LDO2P5V_IN   |                 | I        | Regulator power supply input. Share 1µF input cap with LDO2P5V_IN.                              |

| 21     | BUCK5VR      |                 | I        | Power and Digitlal supply input.                                                                |

| 22     | AGND         |                 | I        | Analog ground connection.                                                                       |

| 23     | DGND         |                 | I        | Digital ground connection.                                                                      |

| 24     | BUCK5VR_SNS  |                 | I        | Feedback from output capacitor of buck converter.                                               |

| 25     | LX           |                 | 0        | Switch Node of buck converter. Connects to one of the inductor's terminals.                     |

| 26     | LX           |                 | 0        | Switch Node of buck converter. Connects to one of the inductor's terminals.                     |

| 27     | LX           |                 | 0        | Switch Node of buck converter. Connects to one of the inductor's terminals.                     |

| 21     | LA           |                 | _        | Active-Low charger Enable pin. Charger is suspended and placed in low current (sleep) mode when |

| 28     | ENb          |                 | I        | pulled high. Tie low for stand alone mode.                                                      |

| 29     | BUCK5VR_IN   |                 | I        | Buck converter power supply input.                                                              |

| 30     | BUCK5VR_IN   |                 | 1        | Buck converter power supply input.                                                              |

| 31     | BUCK5VR_IN   |                 | I        | Buck converter power supply input.                                                              |

| 32     | BST          | A               | I        | Bootstrap cap for BUCK converter gate drive supply.                                             |

| 33     | USB OUT      |                 | 0        | USB or 5V adaptor output.                                                                       |

| 34     | USB IN       |                 | I        | USB or 5V adaptor input.                                                                        |

| 35     | _            |                 | /0000    | Current sense.                                                                                  |

|        | ISNS         |                 | ?        |                                                                                                 |

| 36     | SUBS_P       |                 | I        | Power substrate ground                                                                          |

| 37     | SUBS_D       |                 | I        | Digital substrate ground                                                                        |

| 38     | NC           |                 | -        |                                                                                                 |

| 39     | REC_OUT      | 450             | 0        | Rectified output.                                                                               |

| 40     | REC_OUT      |                 | 0        | Rectified output.                                                                               |

| 41     | REC_OUT      |                 | 0        | Rectified output.                                                                               |

| 42     | IN_M         |                 | I        | Negative inductor input.                                                                        |

| 43     | IN_M         |                 | I        | Negative inductor input.                                                                        |

| 44     | IN_M         |                 | I        | Negative inductor input.                                                                        |

| 45     | IN_P         |                 | I        | Positive inductor input.                                                                        |

| 46     | IN_P         |                 | I        | Positive inductor input.                                                                        |

| 47     | IN_P         |                 | I        | Positive inductor input.                                                                        |

| 48     | ZREF_M       |                 | I        | AC clamp, negative end                                                                          |

| 49     | ACM_M        |                 | I        | AC modulation input, negative end.                                                              |

| 50     | ACM_P        |                 | I        | AC modulation input, positive end.                                                              |

| 51     |              |                 | I        | AC clamp, positive end.                                                                         |

|        | ZREF_P       |                 | <b>i</b> | 2.5V output (Do not load).                                                                      |

| 52     | LDO2P5V      |                 | I        | 2.3ν ομέρας (100 που ισαμ).                                                                     |

| 53     | NC<br>NC     |                 | -        |                                                                                                 |

| 54     | NC           |                 | -        |                                                                                                 |

| 55     | NC           |                 | -        |                                                                                                 |

| 56     | GND          | I               | I        | Signal ground connection.                                                                       |

## **APPLICATION DIAGRAMS**

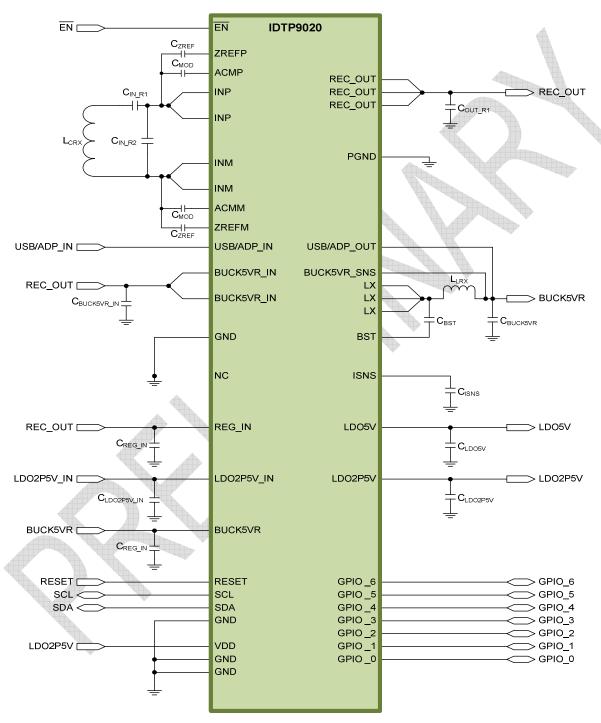

Figure 3: IDTP9020 Applications Diagram

# **SYSTEM DIAGRAM**

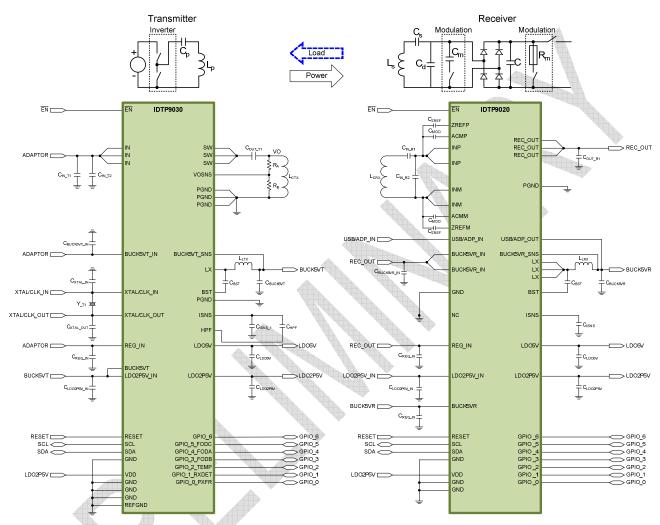

Figure 4: IDTP9030/IDTP9020 Systems Applications Diagram.

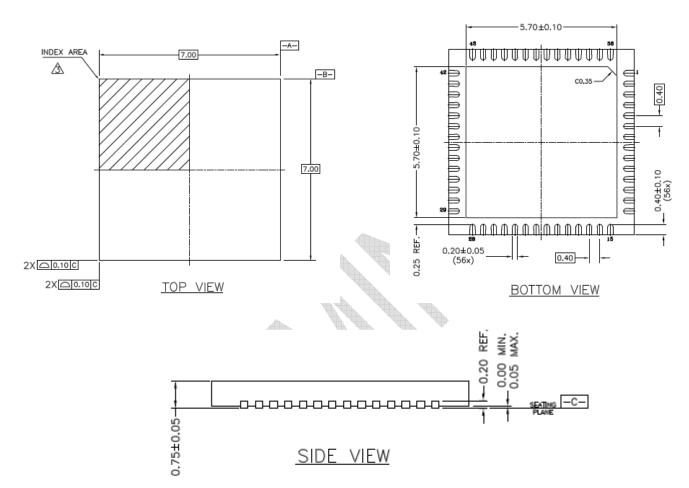

# PACKAGE OUTLINE DRAWING (QFN)

### NOTES:

- ALL DIMENSIONING AND TOLERANCING CONFORM TO ANSI Y14.5M-1982

- 2 ALL DIMENSIONS ARE IN MILLIMETERS.

- INDEX AREA (PIN1 IDENTIFIER)

Figure 5: Package Outline Drawing (NDG QFN-56 7x7x0.75mm 56-ld)

## **ORDERING GUIDE**

**Table 3: Ordering Summary**

| PART NUMBER  | MARKING | PACKAGE           | AMBIENT TEMP.<br>RANGE | SHIPPING CARRIER | QUANTITY |

|--------------|---------|-------------------|------------------------|------------------|----------|

| P9020-0NTGI  |         | QFN-56 7x7x0.75mm | -40°C to +85°C         | Tube or Tray     | 260      |

| P9020-0NTGI8 |         | QFN-56 7x7x0.75mm | -40°C to +85°C         | Tape and Reel    | 2,000    |

6024 Silver Creek Valley Road San Jose, California 95138

Tel: 800-345-7015

DISCLAIMER Integrated Device Technology, Inc. (IDT) and its subsidiaries reserve the right to modify the products and/or specifications described herein at any time and at IDT's sole discretion. All information in this document, including descriptions of product features and performance, is subject to change without notice. Performance specifications and the operating parameters of the described products are determined in the independent state and are not guaranteed to perform the same way when installed in customer products. The information contained herein is provided without representation or warranty of any kind, whether express or implied, including, but not limited to, the suitability of IDT's products for any particular purpose, an implied warranty of merchantability, or non-infringement of the intellectual property rights of others. This document is presented only as a guide and does not convey any license under intellectual property rights of IDT or any third parties. IDT's products are not intended for use in life support systems or similar devices where the failure or malfunction of an IDT product can be reasonably expected to significantly affect the health or safety of users. Anyone using an IDT product in such a manner does so at their own risk, absent an express, written agreement by IDT.

Integrated Device Technology, IDT and the IDT logo are registered trademarks of IDT. Other trademarks and service marks used herein, including protected names, logos and designs, are the property of IDT or their respective third party owners.

© Copyright 2012. All rights reserved.

# **Mouser Electronics**

**Authorized Distributor**

Click to View Pricing, Inventory, Delivery & Lifecycle Information:

IDT (Integrated Device Technology): P9020-EVK