## **Advanced Video Decoder with 10-Bit ADC** and Component Input Support

## **ADV7183**

**FEATURES**

Analog Video to Digital YCrCb Video Decoder:

NTSC-(M/N), PAL-(B/D/G/H/I/M/N)

ADV®7183 Integrates Two 10-Bit Accurate ADCs

Clocked from a Single 27 MHz Crystal

**Dual Video Clocking Schemes:**

Line-Locked Clock Compatible (LLC)

Adaptive Digital Line Length Tracking (ADLLT™)

Three-Line Chroma Comb Filter

Real-Time Clock and Status Information Output

Integrated AGC (Automatic Gain Control) and Clamping

**Multiple Programmable Analog Input Formats:**

CVBS (Composite Video)

SVHS (Y/C)

YCrCb Component (VESA, MII, SMPTE, and BetaCom)

6 Analog Input Video Channels

**Automatic NTSC/PAL Identification**

**Differential Mode Video Input**

Digital Output Formats 16-Bit Wide Bus):

YCrCb (4:2:2 or 4:1:1)

CCIR601/CCIR656 8-Bit or 16-Bit

0.5 V to 2.0 V p-p Input Range

Differential Gain, 0.4% Typ

Differential Phase, 0.6° Typ

**Programmable Video Controls:**

Peak White/Hue/Brightness/Saturation/Contrast

**APPLICATIONS**

**Security Systems**

**Projectors**

**Digital Televisions**

**DVD-RAM Recorders and Players**

**PDP Displays**

Video Decoders

Hybrid Analog/Digital Set-Top Boxes

(continued on page 9)

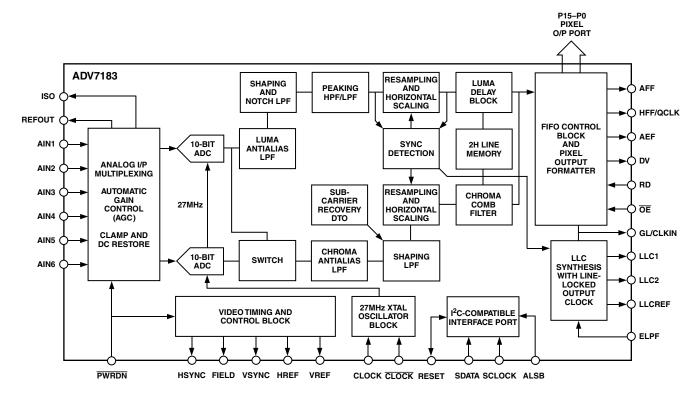

#### FUNCTIONAL BLOCK DIAGRAM

ADLLT is a trademark and ADV is a registered trademark of Analog Devices, Inc.

### REV. 0

Information furnished by Analog Devices is believed to be accurate and reliable. However, no responsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other rights of third parties that may result from its use. No license is granted by implication or otherwise under any patent or patent rights of Analog Devices.

One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A. Tel: 781/329-4700 www.analog.com Fax: 781/326-8703

© Analog Devices, Inc., 2002

# $\textbf{ADV7183-SPECIFICATIONS}^{1} \text{ (V}_{AA} = 4.75 \text{ V to } 5.25 \text{ V, V}_{DD} = 3.2 \text{ V to } 3.5 \text{ V, V}_{DDIO} = 3.15 \text{ V to } 3.5 \text{ V, T}_{MIN} \text{ to T}_{MAX}^{2}, \text{ unless otherwise noted.)}$

| Parameter                                                                                                                                                                                                                                                                           | Min                 | Тур                                  | Max                       | Unit                                   | Test Conditions                                           |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------|--------------------------------------|---------------------------|----------------------------------------|-----------------------------------------------------------|

| STATIC PERFORMANCE Resolution (each ADC) Accuracy (each ADC)                                                                                                                                                                                                                        |                     |                                      | 10                        | Bits                                   |                                                           |

| Integral Nonlinearity <sup>3</sup> Differential Nonlinearity <sup>3</sup>                                                                                                                                                                                                           |                     | ±0.25<br>±0.08                       | ±0.5<br>±0.17             | LSB<br>LSB                             | BSL, 2 V Input Range to ADC<br>2 V Input Range to ADC     |

| DIGITAL INPUTS <sup>3</sup> Input High Voltage, $V_{INH}$ Input Low Voltage, $V_{INL}$ Input Current, $I_{IN}$ Input Capacitance, $C_{IN}$                                                                                                                                          | 2 -10               |                                      | 0.8<br>+10<br>10          | V<br>V<br>μA<br>pF                     |                                                           |

| DIGITAL OUTPUTS <sup>3</sup> Output High Voltage, V <sub>OH</sub> Output Low Voltage, V <sub>OL</sub> High Impedance Leakage Current Output Capacitance                                                                                                                             | 2.4                 |                                      | 0.4<br>10<br>30           | V<br>V<br>μΑ<br>pF                     | $I_{SOURCE} = 3.2 \text{ mA}$ $I_{SINK} = 0.4 \text{ mA}$ |

| VOLTAGE REFERENCE <sup>3</sup> Reference Range, V <sub>REFOUT</sub>                                                                                                                                                                                                                 | 2.15                | 2.2                                  | 2.25                      | V                                      | $I_{VREFOUT} = 0 \mu A$                                   |

| POWER REQUIREMENTS  Digital Power Supply, V <sub>DD</sub> Digital IO Power Supply, V <sub>DDIO</sub> Analog Power Supply, V <sub>AA</sub> Digital Supply Current, I <sub>DD</sub> Digital IO Supply Current, I <sub>DDIO</sub> Analog Supply Current, I <sub>AA</sub> Power-Up Time | 3.2<br>3.15<br>4.75 | 3.3<br>3.3<br>5.0<br>125<br>7<br>150 | 3.5<br>3.5<br>5.25<br>165 | V<br>V<br>V<br>mA<br>mA<br>mA<br>Field | Sleep Mode until Powered Up                               |

-2-REV. 0

NOTES

NOTES

The max/min specifications are guaranteed over this range. The max/min values are typical over  $V_{AA} = 4.75 \text{ V}$  to 5.25 V,  $V_{DD} = 3.2 \text{ to } 3.5 \text{ V}$ , and  $V_{DDIO} = 3.15 \text{ V}$  to 3.5 V range.

$<sup>^2</sup> Temperature$  range  $T_{MIN}$  to  $T_{MAX}$  =  $0^{\circ} C$  to  $70^{\circ} C$

<sup>&</sup>lt;sup>3</sup>Guaranteed by characterization.

$<sup>^4\</sup>mathrm{I}_{AA}$  is total analog current taken by AVDD supply pins.

Specifications subject to change without notice.

##

| Parameter                                                | Min | Тур        | Max | Unit     | Test Conditions                     |

|----------------------------------------------------------|-----|------------|-----|----------|-------------------------------------|

| NONLINEAR SPECIFICATIONS <sup>2</sup> Differential Phase |     | 0.6        |     | Decree   | CVDC Comb No Comb                   |

| Differential Phase Differential Gain                     |     | 0.6<br>0.7 |     | Degree % | CVBS, Comb/No Comb                  |

|                                                          |     |            |     | %<br>%   | CVBS, Comb/No Comb                  |

| Luma Nonlinearity                                        |     | 1.0        |     | %0       |                                     |

| NOISE SPECIFICATIONS <sup>2</sup>                        |     |            |     |          |                                     |

| SNR (Ramp)                                               | 61  | 54         |     | dB       | CVBS                                |

| Analog Front End Channel Crosstalk                       |     | 63         |     | dB       | S-Video/YUV, Single-Ended           |

| Analog Front End Channel Crosstalk                       |     | 63         |     | dB       | S-Video/YUV, Differential-Ended     |

| LOCK TIME AND JITTER                                     |     |            |     |          |                                     |

| SPECIFICATIONS <sup>2</sup>                              |     |            |     |          |                                     |

| Horizontal Lock Time                                     |     | 50         |     | Lines    | TV/VCR mode                         |

| Horizontal Recovery Time                                 |     | 50         |     | Lines    |                                     |

| Horizontal Lock Range                                    |     | ±5         |     | %        |                                     |

| Line Length Variation Over Field                         |     | $\pm 1$    |     | %        | VCR Mode/Surveillance Mode          |

| Line Length Variation Over Field                         |     | ±1         |     | %        | TV Mode                             |

| HLock Lost Declared                                      | 10  |            |     | HSync    | TV Mode, Number of Missing HSyncs   |

| HLock Lost Declared                                      |     | 20         |     | HSync    | VCR/Surveillance Mode, Number of    |

|                                                          |     |            |     |          | Missing HSyncs                      |

| Vertical Lock Time                                       |     | 2          |     | VSync    | First Lock into Video Signal        |

| VLock Lost Declared                                      |     | 1          |     | VSync    | All Modes, Number of Missing VSyncs |

| F <sub>SC</sub> Subcarrier Lock Range                    |     | $\pm 400$  |     | Hz       | NTSC/PAL                            |

| Color Lock Time                                          |     | 50         |     | Lines    | HLock to Color Lock Time            |

| LLC Clock Jitter (Short Time Jitter)                     |     | 1          |     | ns       | RMS Clock Jitter                    |

| LLC Clock Jitter (Frame Jitter)                          |     | 37         |     | ns       | RMS Clock Jitter                    |

| CHROMA-SPECIFIC                                          |     |            |     |          |                                     |

| SPECIFICATIONS <sup>2</sup>                              |     |            |     |          |                                     |

| Hue Accuracy                                             |     | 1.0        |     | Degree   |                                     |

| Color Saturation Accuracy                                |     | 1.0        |     | %        |                                     |

| Color Gain Control Range                                 | -6  |            | +18 | dB       | S-Video, YUV, Overall CGC Range     |

| Ç                                                        |     |            |     |          | (Analog and Digital)                |

| Analog Color Gain Range                                  | -6  |            | +6  | dB       | S-Video, YUV                        |

| Digital Color Gain Range                                 | 0   |            | 12  | dB       | CVBS, S-Video, YUV                  |

| Chroma Amplitude Error                                   |     | 0.1        |     | %        |                                     |

| Chroma Phase Error                                       |     | 0          |     | Degree   |                                     |

| Chroma Luma Intermodulation                              |     | 0.1        |     | %        |                                     |

| LUMA-SPECIFIC SPECIFICATIONS <sup>2</sup>                |     |            |     |          |                                     |

| Luma Brightness Accuracy                                 |     | 1.0        |     | %        | Video Input Range = 1.0 V p-p       |

|                                                          |     | 1.0        |     |          |                                     |

| Luma Contrast Accuracy                                   |     | 1.0        |     | %        | Video Input Range = 1.0 V p-p       |

### NOTES

Specifications subject to change without notice.

REV. 0 -3-

$<sup>^{1}</sup>$ The max/min specifications are guaranteed over this range. The max/min values are typical over  $V_{AA}$  = 4.75 V to 5.25 V,  $V_{DD}$  = 3.2 to 3.5 V, and  $V_{DDIO}$  = 3.15 V to 3.5 V range.

<sup>&</sup>lt;sup>2</sup>Guaranteed by characterization.

$<sup>^3</sup> Temperature$  range  $T_{MIN}$  to  $T_{MAX}$  = 0°C to 70°C

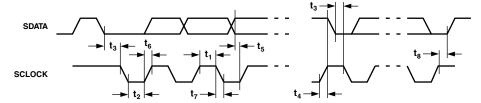

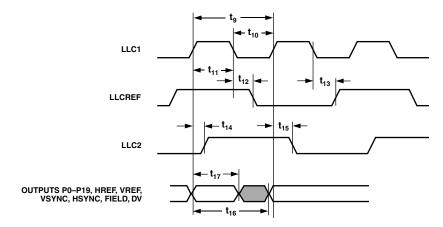

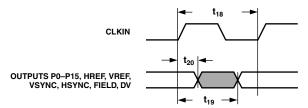

## TIMING SPECIFICATIONS $^{1}$ ( $V_{AA}=4.75$ V to 5.25 V, $V_{DD}=3.2$ V to 3.5 V, $V_{DDI0}=3.15$ V to 3.5 V, $T_{MIN}$ to $T_{MAX}^{2}$ , unless otherwise noted.)

| Parameter                                       | Min | Typ  | Max | Unit | Test Conditions                 |

|-------------------------------------------------|-----|------|-----|------|---------------------------------|

| SYSTEM CLOCK AND CRYSTAL                        |     |      |     |      |                                 |

| Nominal Frequency                               |     | 27   |     | MHz  |                                 |

| I <sup>2</sup> C PORT <sup>2</sup>              |     |      |     |      |                                 |

| SCL Clock Frequency                             | 0   |      | 400 | kHz  |                                 |

| SCL Min Pulsewidth High, t <sub>1</sub>         | 0.6 |      |     | μs   |                                 |

| SCL Min Pulsewidth Low, t <sub>2</sub>          | 1.3 |      |     | μs   |                                 |

| Hold Time (Start Condition), t <sub>3</sub>     | 0.6 |      |     | μs   |                                 |

| Setup Time (Start Condition), t <sub>4</sub>    | 0.6 |      |     | μs   |                                 |

| Data Setup Time, t <sub>5</sub>                 | 100 |      |     | ns   |                                 |

| SCL/SDA Rise Time, t <sub>6</sub>               |     |      | 300 | ns   |                                 |

| SCL/SDA Fall Time, t <sub>7</sub>               |     |      | 300 | ns   |                                 |

| Setup Time (Stop Condition), t <sub>8</sub>     |     | 0.6  |     | μs   |                                 |

| RESET FEATURE                                   |     |      |     |      |                                 |

| Reset Pulse Input Width                         | 74  |      |     | ns   |                                 |

| CLOCK OUTPUTS <sup>3</sup>                      |     |      |     |      |                                 |

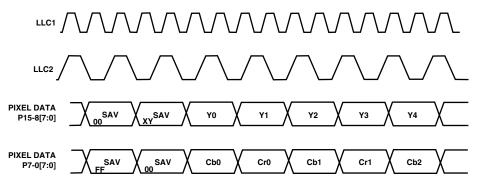

| LLC1 Cycle Time, t <sub>9</sub>                 |     | 37   |     | ns   | CCIR601 Mode 27 MHz             |

| LLC1 Cycle Time, t <sub>9</sub>                 |     | 33.9 |     | ns   | PAL Square Pixel Mode 29.5 MHz  |

| LLC1 Cycle Time, t <sub>9</sub>                 |     | 40.8 |     | ns   | NTSC Square Pixel Mode 24.5 MHz |

| LLC1 Min Low Period, t <sub>10</sub>            |     | 18   |     | ns   | CCIR601 Mode 27 MHz             |

| LLC1 Min High Period, t <sub>11</sub>           |     | 18   |     | ns   | CCIR601 Mode 27 MHz             |

| LLC1 Falling to LLCREF Falling, t <sub>12</sub> |     | 4    |     | ns   |                                 |

| LLC1 Falling to LLCREF Rising, t <sub>13</sub>  |     | 6    |     | ns   |                                 |

| LLC1 Rising to LLC2 Rising, t <sub>14</sub>     |     | 3    | 5   | ns   |                                 |

| LLC1 Rising to LLC2 Falling, t <sub>15</sub>    |     | 1    | 3   | ns   |                                 |

| CLKIN Cycle Time, t <sub>18</sub>               |     | 37   |     | ns   | SCAPI and CAPI Modes            |

| DATA AND CONTROL OUTPUT                         |     |      |     |      |                                 |

| Data Output Hold Time, t <sub>17</sub>          | 26  |      |     | ns   | LLC Mode                        |

| Data Output Access Time, t <sub>16</sub>        |     | 30   | 33  | ns   | LLC Mode                        |

| Data Output Access Time, t <sub>19</sub>        |     | 20   | 25  | ns   | SCAPI and CAPI Modes            |

| Data Output Hold Time, t <sub>20</sub>          | 6   | 11   |     | ns   | SCAPI and CAPI Modes            |

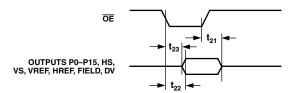

| Propagation Delay to High Z, t <sub>21</sub>    |     | 5    | 8   | ns   |                                 |

| Max Output Enable Access Time, t22              |     | 8    | 11  | ns   |                                 |

| Min Output Enable Access Time, t <sub>23</sub>  | 2   | 5    |     | ns   |                                 |

#### NOTES

Specifications subject to change without notice.

# ANALOG FRONT END SPECIFICATIONS $^{1}$ ( $V_{AA} = 4.75$ V to 5.25 V, $V_{DD} = 3.2$ V to 3.5 V, $V_{DDI0} = 3.15$ V to 3.5 V, $T_{MIN}$ to $T_{MAX}^{2}$ , unless otherwise noted.)

| Parameter                | Min | Typ  | Max | Unit | Test Conditions                        |

|--------------------------|-----|------|-----|------|----------------------------------------|

| CLAMP CIRCUITRY          |     |      |     |      |                                        |

| External Clamp Capacitor |     | 0.1  |     | μF   |                                        |

| Input Impedance          |     | 10   |     | MΩ   | Clamp Switched Off                     |

| Voltage Clamp Level      |     | 1.4  |     | V    | _                                      |

| Clamp Source Current     |     | 3    |     | μA   | Signal Already Clamped (Fine Clamping) |

| Sink Current             |     | -3   |     | μA   | Signal Already Clamped (Fine Clamping) |

| Source Current           |     | 0.9  |     | mA   | Acquire Mode (Fast Clamping)           |

| Clamp Sink Current       |     | -0.9 |     | mA   | Acquire Mode (Fast Clamping)           |

#### NOTES

-4- REV. 0

$<sup>^{1}</sup>$ The max/min specifications are guaranteed over this range. The max/min values are typical over  $V_{AA} = 4.75 \text{ V}$  to 5.25 V,  $V_{DD} = 3.2 \text{ to } 3.5 \text{ V}$ , and  $V_{DDIO} = 3.15 \text{ V}$  to 3.5 V range.

<sup>&</sup>lt;sup>2</sup>Temperature Range  $T_{MIN}$  to  $T_{MAX}$  = 0°C to 70°C

<sup>&</sup>lt;sup>3</sup>Guaranteed by characterization.

$<sup>^{1}</sup>$ The max/min specifications are guaranteed over this range. The max/min values are typical over  $V_{AA}$  = 4.75 V to 5.25 V,  $V_{DD}$  = 3.2 to 3.5 V, and  $V_{DDIO}$  = 3.15 V to 3.5 V range.

$<sup>^2</sup>$ Temperature range  $T_{MIN}$  to  $T_{MAX}$  = 0°C to 70°C

Specifications subject to change without notice.

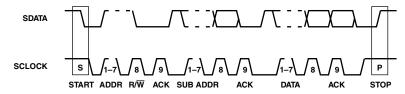

Figure 1. MPU Port Timing Diagram

Figure 2. LLC Clock, Pixel Port, and Control Outputs Timing Diagram

Figure 3. Pixel Port and Control Outputs in CAPI and SCAPI Mode Timing Diagram

Figure 4. OE Timing Diagram

REV. 0 -5-

## ABSOLUTE MAXIMUM RATINGS<sup>1</sup>

| V <sub>AA</sub> to GND 7 V                                                      |

|---------------------------------------------------------------------------------|

| V <sub>DD</sub> to GND                                                          |

| $V_{DDIO}$ to GND 4 V                                                           |

| Voltage on Digital Input Pins GND – $0.5 \text{ V}$ to $V_{AA} + 0.5 \text{ V}$ |

| Storage Temperature ( $T_S$ )65°C to +150°C                                     |

| Junction Temperature (T <sub>J</sub> ) 150°C                                    |

| Lead Temperature (Soldering, 10 sec) 260°C                                      |

| Analog Outputs to $GND^2$ $GND - 0.5 \ V$ to $V_{AA}$                           |

#### NOTES

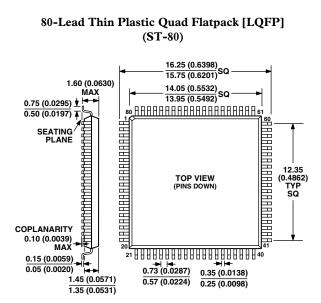

#### ORDERING GUIDE

| Model      | Temperature Range | Package |

|------------|-------------------|---------|

| ADV7183KST | 0°C to 70°C       | 80-LQFP |

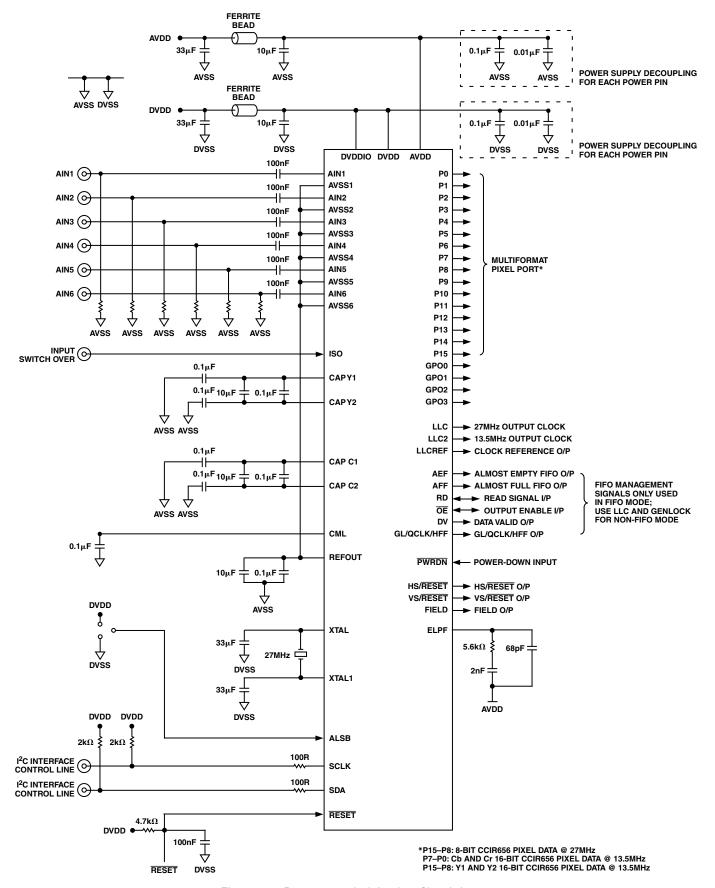

#### PIN CONFIGURATION

#### CAUTION

ESD (electrostatic discharge) sensitive device. Electrostatic charges as high as 4000 V readily accumulate on the human body and test equipment and can discharge without detection. Although the ADV7183 features proprietary ESD protection circuitry, permanent damage may occur on devices subjected to high energy electrostatic discharges. Therefore, proper ESD precautions are recommended to avoid performance degradation or loss of functionality.

<sup>&</sup>lt;sup>1</sup>Stresses above those listed under Absolute Maximum Ratings may cause permanent damage to the device. This is a stress rating only; functional operation of the device at these or any other conditions above those listed in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

<sup>&</sup>lt;sup>2</sup>Analog output short circuit to any power supply or common can be of an indefinite duration.

## PIN FUNCTION DESCRIPTIONS

| Pin                          | Mnemonic     | Input/Output | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|------------------------------|--------------|--------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1                            | VS/VACTIVE   | 0            | VS or Vertical Sync. A dual-function pin, (OM_SEL[1:0] = 0, 0) is an output signal that indicates a vertical sync with respect to the YUV pixel data. The active period of this signal is six lines of video long. The polarity of the VS signal is controlled by the PVS bit. VACTIVE (OM_SEL[1:0] = 1, 0 or 0, 1) is an output signal that is active during the active/viewable period of a video field. The polarity of VACTIVE is controlled by PVS bit.                                                              |

| 2                            | HS/HACTIVE   | O            | HS or Horizontal Sync. A dual-function pin, (OM_SEL[1:0] = 0, 0) is a programmable horizontal sync output signal. The rising and falling edges can be controlled by HSB[9:0] and HSE[9:0] in steps of 2 LLC1. The polarity of the HS signal is controlled by the PHS bit. HACTIVE (OM_SEL[1:0] = 1, 0 or 0, 1) is an output signal that is active during the active/viewable period of a video line. The active portion of a video line is programmable on the ADV7183. The polarity of HACTIVE is controlled by PHS bit. |

| 3, 14                        | DVSSIO       | G            | Digital I/O Ground                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 4, 15                        | DVDDIO       | P            | Digital I/O Supply Voltage (3.3 V)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 5–8, 19–24,<br>32, 33, 73–76 | P15-P0       | О            | Video Pixel Output Port. 8-bit multiplexed YCrCb pixel port (P15–P8), 16-bit YCrCb pixel port (P15–P8 = Y and P7–P0 = Cb,Cr).                                                                                                                                                                                                                                                                                                                                                                                             |

| 9, 31, 71                    | DVSS1-3      | G            | Ground for Digital Supply                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 10, 30, 72                   | DVDD1-3      | P            | Digital Supply Voltage (3.3 V)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 11                           | AFF          | 0            | Almost Full Flag. A FIFO control signal indicating when the FIFO has reached the almost full margin set by the user (use FFM[4:0]). The polarity of this signal is controlled by the PFF bit.                                                                                                                                                                                                                                                                                                                             |

| 12                           | HFF/QCLK/GL  | I/O          | Half Full Flag. A multifunction pin, (OM_SEL[1:0] = 1, 0) is a FIFO control signal that indicates when the FIFO is half full. The QCLK (OM_SEL[1:0] = 0, 1) pin function is a qualified pixel output clock when using FIFO SCAPI mode. The GL (OM_SEL[1:0] = 0, 0) function (Genlock output) is a signal that contains a serial stream of data that contains information for locking the subcarrier frequency. The polarity of HFF signal is controlled by PFF bit.                                                       |

| 13                           | AEF          | 0            | Almost Empty Flag. A FIFO control signal, it indicates when the FIFO has reached the almost empty margin set by the user (use FFM[4:0]). The polarity of this signal is controlled by PFF bit.                                                                                                                                                                                                                                                                                                                            |

| 16                           | CLKIN        | I            | Asynchronous FIFO Clock. This asynchronous clock is used to output data onto the P19-P0 bus and other control signals.                                                                                                                                                                                                                                                                                                                                                                                                    |

| 17, 18, 34, 35               | GPO[3:0]     | 0            | General-Purpose Outputs controlled via I <sup>2</sup> C                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 25                           | LLCREF       | 0            | Clock Reference Output. This is a clock qualifier distributed by the internal CGC for a data rate of LLC2. The polarity of LLCREF is controlled by the PLLCREF bit.                                                                                                                                                                                                                                                                                                                                                       |

| 26                           | LLC2         | 0            | Line-Locked Clock System Output Clock/2 (13.5 MHz)                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 27                           | LLC1/PCLK    | О            | Line-Locked Clock System Output Clock. A dual-function pin (27 MHz ± 5%) or a FIFO output clock ranging from 20 MHz to 35 MHz.                                                                                                                                                                                                                                                                                                                                                                                            |

| 28                           | XTAL1        | 0            | Second terminal for crystal oscillator; not connected if external clock source is used.                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 29                           | XTAL         | I            | Input terminal for 27 MHz crystal oscillator or connection for external oscillator with CMOS-compatible square wave clock signal                                                                                                                                                                                                                                                                                                                                                                                          |

| 36                           | <u>PWRDN</u> | I            | Power-Down Enable. A logical low will place part in a power-down status.                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 37                           | ELPF         | I            | This pin is used for the External Loop Filter that is required for the LLC PLL.                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 38                           | PVDD         | P            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 39                           | PVSS         | G            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

REV. 0 -7-

## PIN FUNCTION DESCRIPTIONS (continued)

| Pin                       | Mnemonic    | Input/Output | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|---------------------------|-------------|--------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 40, 47, 53, 56,<br>63     | AVSS        | G            | Ground for Analog Supply                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 41, 43, 45, 57,<br>59, 61 | AVSS1-6     | G            | Analog Input Channels. Ground if single-ended mode is selected. These pins should be connected directly to REFOUT when differential mode is selected.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 42, 44, 46, 58,<br>60, 62 | AIN1-6      | I            | Video Analog Input Channels                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 48, 49                    | CAPY1-2     | I            | ADC Capacitor Network                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 50                        | AVDD        | P            | Analog Supply Voltage (5 V)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 51                        | REFOUT      | O            | Internal Voltage Reference Output                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 52                        | CML         | О            | Common-Mode Level for ADC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 54, 55                    | CAPC1-2     | I            | ADC Capacitor Network                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 64                        | RESET       | I/O          | System Reset Input. Active Low.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 65                        | ISO         | I            | Input Switch Over. A low to high transition on this input indicates to the decoder core that the input video source has been changed externally and configures the decoder to reacquire the new timing information of the new source. This is useful in applications where external video muxes are used. This input gives the advantage of faster locking to the external muxed video sources. A low to high transition triggers this input.                                                                                                                                                                                                            |

| 66                        | ALSB        | I            | TTL Address Input. Selects the MPU address:  MPU address = 88h ALSB = 0, disables I <sup>2</sup> C filter  MPU address = 8Ah ALSB = 1, enables I <sup>2</sup> C filter                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 67                        | SDATA       | I/O          | MPU Port Serial Data Input/Output                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 68                        | SCLK        | I            | MPU Port Serial Interface Clock Input                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 69                        | VREF/VRESET | 0            | VREF or Vertical Reference Output Signal. Indicates start of next field.   VRESET or Vertical Reset Output is a signal that indicates the beginning of a new field. In SCAPI/CAPI mode this signal is one clock wide and active low relative to CLKIN. It immediately follows the HRESET pixel, and indicates that the next active pixel is the first active pixel of the next field.                                                                                                                                                                                                                                                                    |

| 70                        | HREF/HRESET | 0            | HREF or Horizontal Reference Output Signal. A dual-function pin (enabled when Line-Locked Interface is selected, OM_SEL[1:0] = 0,0), this signal is used to indicate data on the YUV output. The positive slope indicates the beginning of a new active line; HREF is always 720 Y samples long. HRESET or Horizontal Reset Output (enabled when SCAPI or CAPI is selected, OM_SEL[1:0] = 0, 1 or 1, 0) is a signal that indicates the beginning of a new line of video. In SCAPI/CAPI this signal is one clock cycle wide and is output relative to CLKIN. It immediately follows the last active pixel of a line. The polarity is controlled via PHVR. |

| 77                        | RD          | I            | Asynchronous FIFO Read Enable Signal. A logical high on this pin enables a read from the output of the FIFO.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 78                        | DV          | 0            | DV or Data Valid Output Signal. In SCAPI/CAPI mode, DV performs two functions, depending on whether SCAPI or CAPI is selected. It toggles high when the FIFO has reached the AFF margin set by the user, and remains high until the FIFO is empty. The alternative mode is where it can be used to control FIFO reads for bursting information out of the FIFO. In API mode DV indicates valid data in the FIFO, which includes both pixel information and control codes. The polarity of this pin is controlled via PDV.                                                                                                                                |

| 79                        | ŌĒ          | I            | Output Enable Controls Pixel Port Outputs. A logic high will three-state P19–P0.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 80                        | FIELD       | О            | ODD/EVEN Field Output Signal. An active state indicates that an even field is being digitized. The polarity of this signal is controlled by the PF bit.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

-8- REV. 0

(FEATURES continued from page 1)

CCIR/Square Pixel Operation

Integrated On-Chip Video Timing Generator

Synchronous or Asynchronous Output Timing

Line-Locked Clock Output

Closed Captioning Passthrough Operation

Vertical Blanking Interval Support

Power-Down Mode

2-Wire Serial MPU Interface (I<sup>2</sup>C-Compatible)

5 V Analog 3.3 V Digital Supply Operation

80-Lead LQFP Package

#### **GENERAL DESCRIPTION**

The ADV7183 is an integrated video decoder that automatically detects and converts a standard analog baseband television signal compatible with worldwide standards NTSC or PAL into 4:2:2 or 4:1:1 component video data compatible with 16-/8-bit CCIR601/CCIR656.

The advanced and highly flexible digital output interface enables performance video decoding and conversion in both frame-buffer-based and line-locked clock-based systems. This makes the device ideally suited for a broad range of applications with diverse analog video characteristics, including tape-based sources, broadcast sources, security/surveillance cameras, and professional systems.

Fully integrated line stores enable real-time horizontal and vertical scaling of captured video down to icon size. The 10-bit accurate A/D conversion provides professional quality SNR performance. This allows true 8-bit resolution in the 8-bit output mode.

The six analog input channels accept standard composite, S-video, and component YCrCb video signals in an extensive number of combinations. AGC and clamp restore circuitry allow an input video signal peak-to-peak range of 0.5 V up to 2 V. Alternatively, these can be bypassed for manual settings.

The fixed 27 MHz clocking of the ADCs and data path for all modes allows very precise and accurate sampling and digital filtering. The line-locked clock output allows the output data rate, timing signals, and output clock signals to be synchronous, asynchronous, or line-locked even with  $\pm 5\%$  line length variation. The output control signals allow glueless interface connection in almost any application.

The ADV7183 modes are set up over a 2-wire serial bidirectional port (I<sup>2</sup>C-compatible).

The ADV7183 is fabricated in a 5 V CMOS process. Its monolithic CMOS construction ensures greater functionality with lower power dissipation.

The ADV7183 is packaged in a small 80-pin LQFP package.

#### ANALOG INPUT PROCESSING

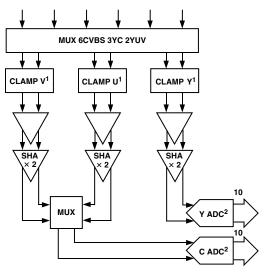

The ADV7183 has six analog video input channels. These six channels can be arranged in a variety of configurations to support up to six CVBS input signals, three S-video input signals, and two YCrCb component analog video input signals. The INSEL[3:0] bits control the input type and channel selected. The analog front end includes three clamp circuits for DC restore. There are three sample-and-hold amplifiers prior to the ADC which are used to enable simultaneous sampling of up to three channels in a YCrCb input mode. Two 10-bit ADCs are used for sampling. The entire analog front end is fully differential which ensures that the video is captured to the highest quality possible. This is very important in highly integrated systems such as video decoders. Figure 5 shows the analog front end section of the ADV7183.

NOTES

ANALOG SIGNAL PATH KEPT FULLY DIFFERENTIAL

ADCs: 10-BIT ACCURATE; 12dB GAIN RANGE

1CLAMP BLOCKS CONTAIN A SET OF CURRENT SOURCES FOR DC

RESTORATION; U AND V HAVE ONLY HALF BANDWIDTH (SAMPLED

SIMULTANEOUSLY, CONVERTED SEQUENTIALLY)

2PIPFI INFD

Figure 5. Analog Front End Block Diagram

## CLAMPING

The clamp control on the ADV7183 consists of a digitally controlled analog current and voltage clamp and a digitally controlled digital clamp circuit. The coupling capacitor on each channel is used to store and filter the clamping voltage. A digital controller controls the clamp up and down current sources that charge the capacitor on every line. Four current sources are used in the current clamp control, two large current sources are used for coarse clamping, and two small current sources are used for fine clamping. The voltage clamp, if enabled, is only used on startup or if a channel is switched. This clamp pulls the video into the midrange of the ADC, which results in faster clamping and faster lock-in time for the decoder. The fourth clamp controller is fully digital and clamps the ADC output data, which results in extremely accurate clamping. It also has the added advantage of being fully digital, which results in very fast clamp timing and makes the entire clamping process very robust in terms of handling large amounts of hum that can be present on real-world video signals.

REV. 0 –9–

In S-video mode there are two clamp controllers used to separately control the luminance clamping and the chrominance clamping. Also in YCrCb component input mode there are two clamp controllers used to control the luminance clamping and the CrCb clamping separately; there are, however, individual current clamps on the Cr and Cb inputs.

User programmability is built into the clamp controllers which enable the current and digital clamp controllers to be set up to user-defined conditions. Refer to analog clamp control register (14H), digital clamp control register (15H), and digital color clamp offset register (15H and 16H) for control settings.

#### ANALOG-TO-DIGITAL CONVERTERS

Two 10-bit ADCs are used in the ADV7183, and they run from a 27 MHz input clock. An integrated band gap generates the required reference voltages for the converters. If the decoder is configured in CVBS mode, the second ADC can be switched off to reduce power consumption, see PSC[1:0].

#### **AUTOMATIC GAIN CONTROL**

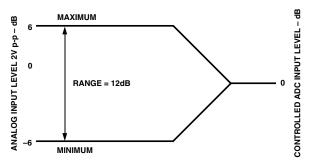

The AGC control block on the ADV7183 is a digitally based system. This controller ensures that the input video signal (CVBS, S-video, or YCrCb) is scaled to its correct value such that the YCrCb digital output data matches the correct gain of the video signal. The AGC has an analog input video range of 0.5 V p-p to 2.0 V p-p, which gives a -6 dB to +6 dB gain range. Figure 6 demonstrates this range. This AGC range will compensate for video signals that have been incorrectly terminated or have been attenuated due to cable loss or other factors.

There are two main control blocks: one for the luminance channel and one for the chrominance channel.

The luminance automatic gain control has eight modes of operation:

- 1. Manual AGC mode where gain for the luminance path is set manually using LGM[11:0].

- 2. Blank level to sync tip is used to set the luminance gain; manual MIRE[2:0] controls the maximum value through the luminance channel. There is no override of this mode when white peak mode is detected.

- 3. Blank level to sync tip is used to set luminance gain; manual MIRE[2:0] controls the maximum value through luminance channel. There is override of this mode when white peak mode is detected. White peak mode is activated when the input video exceeds the maximum luminance range for long periods; this mode is designed to prevent clipping of the input video signal.

- 4. Blank level to sync tip is used to set luminance gain; MIRE[2:0] is automatically controlled to set the maximum value through the luminance channel. There is no override of this mode when white peak mode is detected.

- 5. Blank level to sync tip is used to set luminance gain; manual MIRE[2:0] is automatically controlled to set the maximum value through the luminance channel. There is override of this mode when white peak mode is detected. White peak mode is activated when the input video exceeds the maximum luminance range for long periods; this mode is designed to prevent clipping of the input video signal.

- 6. Based on active video peak white. PW\_UPD sets the gain update frequency (once per field).

- Based on average active video. PW\_RES sets what lines are used; only relevant if the signal conforms to PAL 625 line standard.

- 8. The luminance channel gain is frozen at its present value.

Figure 6. Analog Input Range

The chrominance automatic gain control has four modes of operation:

- 1. Manual AGC mode where gain for chrominance path is set manually using CGM[11:0].

- 2. Luminance gain used for chrominance channel.

- 3. Chrominance automatic gain based on color burst amplitude.

- 4. Chrominance gain frozen at its present setting.

Both the luminance and chrominance AGC controllers have a programmable time constant that allows the AGC to operate in four modes: slow, medium, fast, and video quality controlled.

The maximum IRE (MIRE[2:0]) control can be used to set the maximum input video range that can be decoded. Table I shows the selectable range.

Table I. MIRE Control

|     |         | Fur       | Function   |  |  |  |  |  |

|-----|---------|-----------|------------|--|--|--|--|--|

| MIF | RE[2:0] | PAL (IRE) | NTSC (IRE) |  |  |  |  |  |

| 0   | 0 0     | 133       | 122        |  |  |  |  |  |

| 0   | 0 1     | 125       | 115        |  |  |  |  |  |

| 0   | 1 0     | 120       | 110        |  |  |  |  |  |

| 0   | 1 1     | 115       | 105        |  |  |  |  |  |

| 1   | 0 0     | 110       | 100        |  |  |  |  |  |

| 1   | 0 1     | 105       | 100        |  |  |  |  |  |

| 1   | 1 0     | 100       | 100        |  |  |  |  |  |

| 1   | 1 1     | 100       | 100        |  |  |  |  |  |

-10- REV. 0

#### **LUMINANCE PROCESSING**

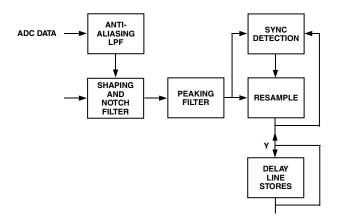

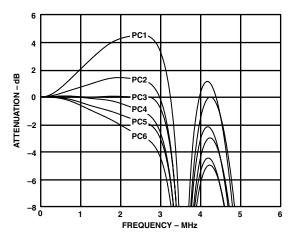

Figure 7 shows the luminance data path. The 10-bit data from the Y ADC is applied to an antialiasing low pass filter that is designed to band-limit the input video signal such that aliasing does not occur. This filter dramatically reduces the design on an external analog antialaising filter; this filter need only remove components in the input video signal above 22 MHz. The data then passes through a shaping or notch filter.

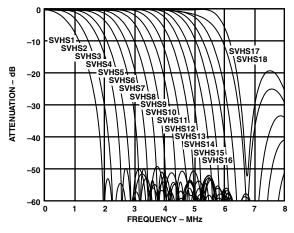

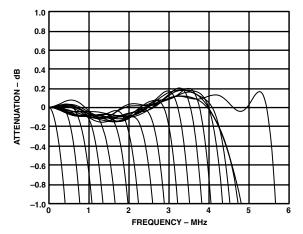

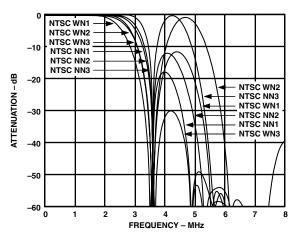

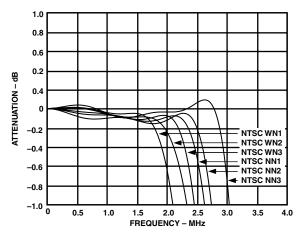

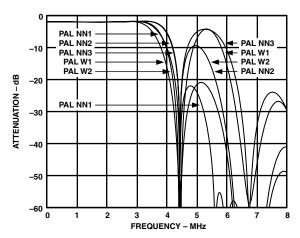

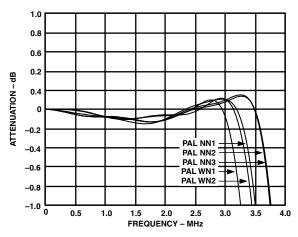

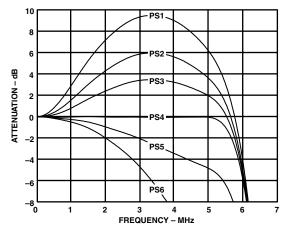

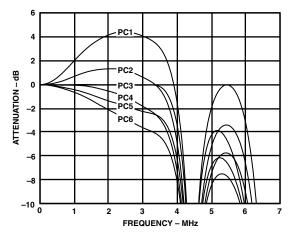

When in CVBS mode a notch filter must be used to remove the unwanted chrominance data that lies around the subcarrier frequency. A wide variety of programmable notch filters for both PAL and NTSC are available. The YSFM[4:0] control the selection of these filters; refer to Figures 8 to 16 for plots of these filters. If S-video or component mode is selected a notch filter is not required. The ADV7183 offers 18 possible shaping filters (SVHS1-18) with a range of low pass filter responses from 0.5 MHz up to 5.75 MHz. The YSFM[4:0] control the selection of these filters. Please refer to Figures 8 through 16 for filter plots.

The next stage in the luminance processing path is a peaking filter; this filter offers a sharpness function on the luminance path. The degree of sharpness can be selected using YPM[2:0]. If no sharpness is required, this filter can be bypassed.

The luminance data is then passed through a resampler to correct for line length variations in the input video. This resampler is designed to always output 720 pixels per line for standard PAL or NTSC. The resampler used on the ADV7183 is of very high quality as it uses 128 phases to resample the video, giving 1/128 pixel resolution. The resampler is controlled by a sync detection block that calculates line length variations on the input video.

The final stage in the luminance path, before it is applied to an output formatter block, is a two-line delay store that is used to compensate for delays in the chroma data path when chroma comb filter is selected.

Figure 7. Luminance Processing Path

Figure 8. Luminance SVHS1–18 Shaping Filter Responses

Figure 9. Luminance SVHS1–SVHS18 Shaping Filter Responses (Close-Up)

Figure 10. Luminance NTSC Narrow/Wide Notch Shaping Filter

REV. 0 –11–

Figure 11. Luminance NTSC Narrow/Wide Notch Shaping Filter (Close-Up)

Figure 12. Luminance PAL Narrow/Wide Notch Shaping Filter Responses

Figure 13. Luminance PAL Narrow/Wide Notch Shaping Filter Responses (Close-Up)

Figure 14. Luminance Peaking Filter Responses in S-Video (SVHS17 Selected)

Figure 15. Luminance Peaking Filter Responses in CVBS (PAL NN3 Selected)

Figure 16. Luminance Peaking Filter Responses in CVBS (NTSC NN3 Selected)

-12- REV. 0

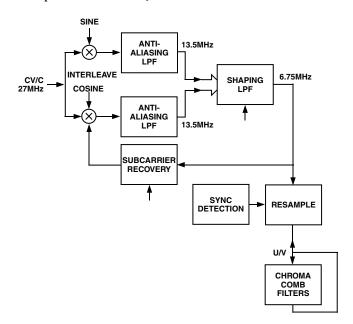

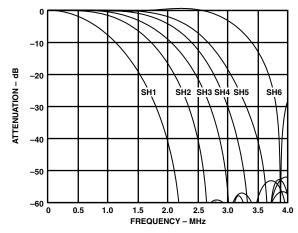

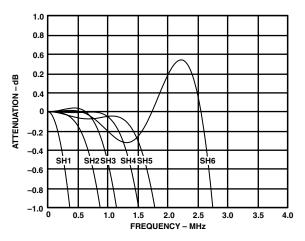

#### **CHROMINANCE PROCESSING**

Figure 17 shows the chrominance data path. The 10-bit data from the Y ADC (CVBS mode) or the C ADC (S-video) is first demodulated. The demodulation is achieved by multiplying by the locally generated quadrature subcarrier, where the sign of the cos subcarrier is inverted from line to line according to the PAL switch, and then low pass filtering is applied to removed components at twice the subcarrier frequency. For NTSC, the phase of the locally generated subcarrier during color burst is the same as the phase of the color burst. For PAL, the phase of the color burst changes from line to line, relative to the phase during active video, and the phase of the locally generated subcarrier is the average of these two values.

The chrominance data is then passed through an antialiasing filter which is a band-pass filter to remove the unwanted luminance data. This antialaising filter dramatically reduces the external antialaising filter requirements as it has only to filter components above 25 MHz. In component mode the demodulation block is bypassed.

The next stage of processing is a shaping filter that can be used to limit the chrominance bandwidth to between 0.5 MHz and 3 MHz; the CSFM[2:0] can be used to select these responses. It should be noted that in CVBS mode a filter of no greater than 1.5 MHz should be selected, as CVBS video is typically band-limited to below 1.5 MHz. In S-video mode a filter of up to 2 MHz can be used. In component mode a filter of up to 3 MHz can be used as component video has higher bandwidth than CVBS or S-video.

The chrominance data is then passed through a resampler to correct for line length variations in the input video. This resampler is designed to always output 720 pixels per line for standard PAL or NTSC. The resampler used on the ADV7183 is of very high quality as it uses 64 phases to resample the video, giving 1/64 pixel resolution. The resampler is controlled by a sync detection block that calculates line length variations on the input video.

The final stage in the chrominance path, before it is applied to an output formatter block, is chroma comb filter.

Figure 17. Chrominance Processing Path

Figure 18. Chrominance Shaping Filter Responses

Figure 19. Chrominance Shaping Filter Responses (Close-Up)

#### **OUTPUT INTERFACE**

#### **Mode Selection Overview**

The ADV7183 supports three output interfaces: LLC-compatible synchronous pixel interface, the CAPI interface, and the SCAPI interface. When the part is configured in the synchronous pixel interface mode, pixel and control data are output synchronous with LLC1 (8-bit mode) or LLC2 (16-bit mode). In this mode control and timing information for field, vertical blanking, and horizontal blanking identification may also be encoded as control codes.

When configured in CAPI or SCAPI mode only the active pixel data is output synchronous with the CLKIN (asynchronous FIFO clock). The pixels are output via a 512-pixel deep, 20-bit wide FIFO. HACTIVE and VACTIVE are output on independent pins. HACTIVE will be active during the active viewable period of a video line and VACTIVE will be active during the active

viewable period of a video field. CAPI and SCAPI modes will always output data in 16-bit, so this mode of operation cannot be used when an 8-bit or 10-bit output interface is required. After power-up, the ADV7183 will default to the LLC-compatible 8-bit CCIR656 4:2:2 @ LLC.

#### Synchronous Pixel Interface

When the output is configured for an 8-bit pixel interface, the data is output on the pixel output port P[15:8]. In this mode, 8 bits of chrominance data will precede 8 bits of luminance data. New pixel data is output on the pixel port after each rising edge of LLC1. When the output is configured for a 16-bit pixel interface, the luminance data is output on P[15:8] and the chrominance data on P[7:0]. In this mode the data is output with respect to LLC2. Figure 20 shows the basic timing relationship for this mode.

Figure 20. Synchronous Pixel Interface, 16-Bit Example

-14- REV. 0

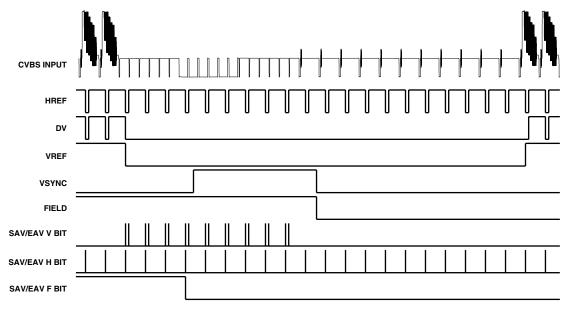

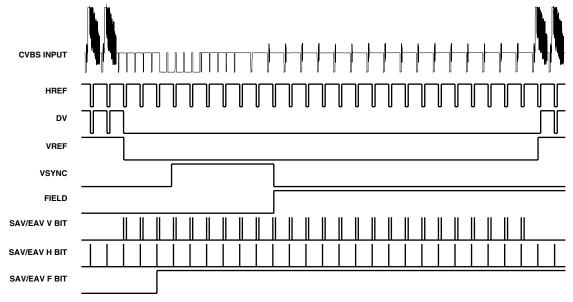

Figure 21. NTSC End Even Field (LLC Mode)

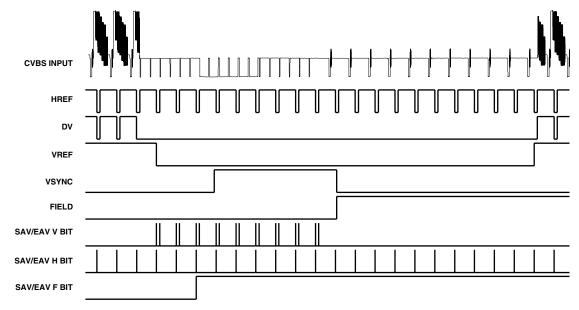

Figure 22. NTSC End Odd Field (LLC Mode)

REV. 0 -15-

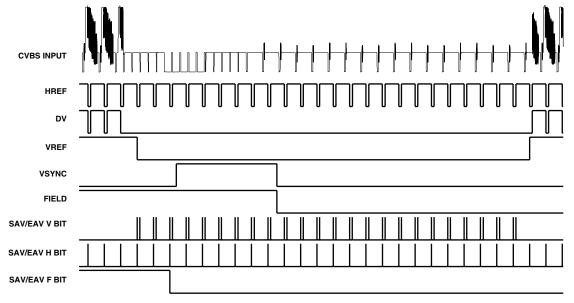

Figure 23. PAL End Even Field (LLC Mode)

Figure 24. PAL End Odd Field (LLC Mode)

-16- REV. 0

#### Control and Pixel Interface FIFO Modes

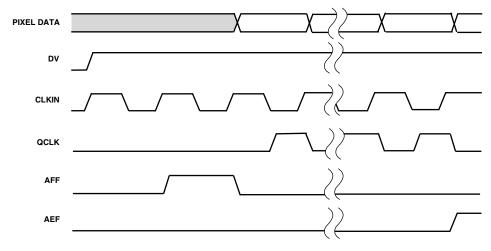

When the ADV7183 is configured to operate in this mode, pixel data generated within the part is buffered by a 512-pixel deep FIFO. Only active video pixels and control codes are written into the FIFO; the others have been dropped. In this mode the output is operating asynchronously and a CLKIN must be provided to clock pixels out of the FIFO. The CLKIN must operate faster than the effective data transfer rate into the FIFO. This rate will be determined by the number of active pixels per line. If the CLKIN is not above this, the FIFO may overflow. The ADV7183 controls the FIFO when set to operate in SCAPI mode. DV (data valid) is internally fed back to the RD (read enable), unlike the synchronous pixel mode where DV will not indicate the validity of the current pixel and only acts as an indication of how much data is stored in the FIFO. DV will go high at the same time as AFF and remain high until the FIFO is empty.

By internally setting DV to RD the system ensures that the FIFO never overflows. When using this mode the status of data on the pixel outputs can be determined by two indicators, DV and QCLK. DV will go active two clock cycles (LLC1) before valid data appears on the bus. QCLK is a qualified clock derived from CLKIN, but will only be present when valid pixel data is output from the FIFO. DV indicates valid pixel or control code data. Using these two control signals, the user can differentiate between pixel information and invalid data. Figure 25 shows the basic timing relationship for this mode.

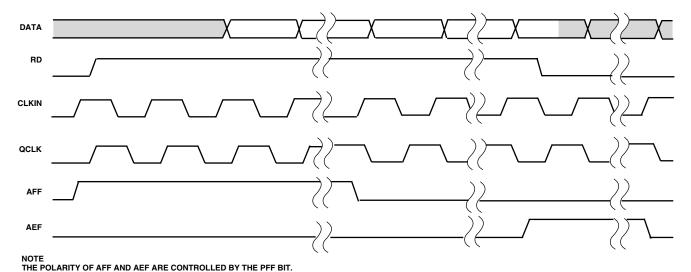

The operation of the ADV7183 in CAPI mode is similar to that of SCAPI mode with the exception that now the FIFO is controlled by the system; the system must monitor the almost full flag (AFF), the almost empty flag (AEF), and control the FIFO read enable (RD). Unlike SCAPI mode, the QCLK is not gated and is therefore continuous. Figure 26 shows the basic timing relationship of this mode.

NOTE

THE POLARITY OF AFF AND AEF ARE CONTROLLED BY THE PFF BIT.

DV POLARITY IS SET BY THE PDV BIT.

Figure 25. SCAPI Output Mode FIFO Operation

Figure 26. CAPI Output Mode FIFO Operation

REV. 0 -17-

#### **Manual Clock Control**

The ADV7183 offers several output clock mode options; the output clock frequency can be set by the input video line length, a fixed 27 MHz output, or by a user-programmable value. Information on the clock control register at 28h can be found in the register access map. When Bit 6 of this register (CLKMANE) is set to Logic "1," the output clock frequency will be determined by the user-programmable value (CLKVAL[15:0]). Using this mode the output clock frequency is calculated as:

$$LLC = \frac{CLKVAL[17:0]}{2^{20}} \times 28 \times \frac{3}{16} \times 27 MHz$$

For example, a required clock frequency of 25 MHz would yield a CLKVAL of 2D266h (184934).

### **Color Subcarrier Control**

The color subcarrier manual frequency control register (CSMF[27:0]) can be used to set the DDFS block to a user-defined frequency. This function can be useful if the color subcarrier frequency of the incoming video signal is outside the standard  $F_{SC}$  lock range. Setting Bit 4 Reg 23h (CSM) to a Logic "1" enables the manual frequency control, the frequency of which will be determined by CSMF[27:0]. The value of CSMF[27:0] can be calculated as:

$$CSMF[27:0] = F_{SC} \times \frac{2^{28}}{27 MHz}$$

\*Required

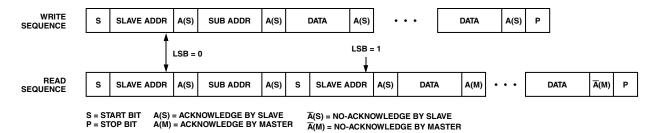

#### MPU PORT DESCRIPTION

The ADV7183 supports a 2-wire serial (I<sup>2</sup>C-compatible) microprocessor bus driving multiple peripherals. Two inputs, serial data (SDATA) and serial clock (SCLOCK) carry information between any device connected to the bus. Each slave device is recognized by a unique address. The ADV7183 has two possible slave addresses for both read and write operations. These are unique addresses for the device and are illustrated in Figure 27. The LSB sets either a read or write operation. Logic Level "1" corresponds to a read operation while Logic Level "0" corresponds to a write operation. A1 is set by setting the ALSB pin of the ADV7183 to Logic Level "0" or Logic Level "1."

| 1 | 0 | 0 | 0 | 1 | 0 | A11 | $\mathbf{X}^2$ | 1 |

|---|---|---|---|---|---|-----|----------------|---|

|---|---|---|---|---|---|-----|----------------|---|

<sup>&</sup>lt;sup>1</sup>Address Control. Set up by ALSB.

Figure 27. Slave Address

To control the device on the bus the following protocol must be followed. First the master initiates a data transfer by establishing a start condition, defined by a high to low transition on SDATA while SCLOCK remains high. This indicates that an address/data stream will follow. All peripherals respond to the start condition and shift the next 8 bits (7-bit address +  $R/\overline{W}$  bit). The bits are transferred from MSB down to LSB. The peripheral that recognizes the transmitted address responds by pulling the data line low during the ninth clock pulse. This is known as an acknowledge bit. All other devices withdraw from the bus at this point and maintain an idle condition. The idle condition is where the device monitors the SDATA and SCLOCK lines waiting for the start condition and the correct transmitted address. The  $R/\overline{W}$  bit determines the direction of the data. A Logic "0" on the LSB of the first byte means that the master will write information to the peripheral. A Logic "1" on the LSB of the first byte means that the master will read information from the peripheral.

The ADV7183 acts as a standard slave device on the bus. The data on the SDATA pin is 8 bits long, supporting the 7-bit addresses plus the  $R/\overline{W}$  bit. The ADV7183 has 71 subaddresses to enable access to the internal registers. It therefore interprets the first byte as the device address and the second byte as the starting subaddress. The subaddresses autoincrement, allowing data to be written to or read from the starting subaddress. A data transfer is always terminated by a stop condition. The user can also access any unique subaddress register on a one-by-one basis, without having to update all the registers.

Stop and start conditions can be detected at any stage during the data transfer. If these conditions are asserted out of sequence with normal read and write operations, they cause an immediate jump to the idle condition. During a given SCLOCK high period the user should only issue one start condition, one stop condition, or a single stop condition followed by a single start condition. If an invalid subaddress is issued by the user, the ADV7183 will not issue an acknowledge and will return to the idle condition. If the user exceeds the highest subaddress in autoincrement mode, the following action will be taken:

- In read mode, the highest subaddress register contents will continue to be output until the master device issues a no-acknowledge. This indicates the end of a read. A no-acknowledge condition is where the SDATA line is not pulled low on the ninth pulse.

- 2. In write mode, the data for the invalid byte will not be loaded into any subaddress register, a no-acknowledge will be issued by the ADV7183, and the part will return to the idle condition.

Figure 28. Write and Read Sequences

-18- REV. 0

<sup>&</sup>lt;sup>2</sup>Read/Write Control. Write = 0; Read = 1

Figure 29. Bus Data Transfer

Table II. Subaddress Register

| Register Name             | Addr (Hex) |

|---------------------------|------------|

| BASIC BLOCK               |            |

| Input Control             | 00         |

| Video Selection           | 01         |

| Video Enhancement Control | 02         |

| Output Control            | 03         |

| Extended Output Control   | 04         |

| General-Purpose Output    | 05         |

| Reserved                  | 06         |

| FIFO Control              | 07         |

| Contrast Control          | 08         |

| Saturation Control        | 09         |

| Brightness Control        | 0A         |

| Hue Control               | 0B         |

| Default Value Y           | 0C         |

| Default Value C           | 0D         |

| Temporal Decimation       | 0E         |

| Power Management          | 0F         |

| Status Register           | 10         |

| Info Register             | 11         |

#### **REGISTER ACCESSES**

The MPU can write to or read from all of the registers of the ADV7183 except the subaddress register, which is a write only register. The subaddress register determines which register the next read or write operation accesses. All communications with the part through the bus start with an access to the subaddress register. Then a read/write operation is performed from/to the target address which then increments to the next address until a stop command on the bus is performed.

### REGISTER PROGRAMMING

The following section describes each register in terms of its configuration.

#### Subaddress Register (SR7-SR0)

The communications register is an 8-bit write only register. After the part has been accessed over the bus and a read/write operation is selected, the subaddress is set up. The subaddress register determines to/from which register the operation takes place.

Table II shows the various operations under the control of the subaddress register. Zero should always be written to SR7–SR6.

#### Register Select (SR5-SR0)

These bits are set up to point to the required starting address.

| Register Name                | Addr (Hex) |

|------------------------------|------------|

| ADVANCED BLOCK               |            |

| Reserved                     | 12         |

| Analog Control (Internal)    | 13         |

| Analog Clamp Control         | 14         |

| Digital Clamp Control 1      | 15         |

| Digital Clamp Control 2      | 16         |

| Shaping Filter Control       | 17         |

| Reserved                     | 18         |

| Comb Filter Control          | 19         |

| Reserved                     | 1A         |

| Reserved                     | 1B         |

| Reserved                     | 1C         |

| Reserved                     | 1D         |

| Reserved                     | 1E         |

| Reserved                     | 1F         |

| Reserved                     | 20         |

| Reserved                     | 21         |

| Reserved                     | 22         |

| Color Subcarrier Control 1   | 23         |

| Color Subcarrier Control 2   | 24         |

| Color Subcarrier Control 3   | 25         |

| Color Subcarrier Control 4   | 26         |

| Pixel Delay Control          | 27         |

| Manual Clock Control 1       | 28         |

| Manual Clock Control 2       | 29         |

| Manual Clock Control 3       | 2A         |

| Auto Clock Control           | 2B         |

| AGC Mode Control             | 2C         |

| Chroma Gain Control 1        | 2D         |

| Chroma Gain Control 2        | 2E         |

| Luma Gain Control 1          | 2F         |

| Luma Gain Control 2          | 30         |

| Manual Gain Shadow Control 1 | 31         |

| Manual Gain Shadow Control 2 | 32         |

| Misc Gain Control            | 33         |

| HSync Position Control 1     | 34         |

| HSync Position Control 2     | 35         |

| HSync Position Control 3     | 36         |

| Polarity Control             | 37         |

| Reserved                     | 44         |

| Reserved                     | 45         |

| Reserved                     | F1         |

| Reserved                     | F2         |

|                              | <u> </u>   |

REV. 0 -19-

Table III. Basic Registers

| Register                     | Addr<br>(Hex) | <b>D</b> 7 | D6        | <b>D</b> 5 | D4        | <b>D</b> 3 | D2       | D1              | <b>D</b> 0     |

|------------------------------|---------------|------------|-----------|------------|-----------|------------|----------|-----------------|----------------|

| Input Control                | 00            | VID SEL.3  | VID SEL.2 | VID SEL.1  | VID SEL.0 | INSEL.3    | INSEL.2  | INSEL.1         | INSEL.0        |

| Video Selection              | 01            | ASE        |           | BETACAM    | 4FSC      | DIFFIN     | SQPE     | VID<br>QUAL.1   | VID<br>QUAL.0  |

| Video Enhancement<br>Control | 02            |            |           |            | COR.1     | COR.0      | YPM.2    | YPM.1           | YPM.0          |

| Output Control               | 03            | VBI EN     | TOD       | OF SEL.3   | OF SEL.2  | OF SEL.1   | OF SEL.O | OM SEL.1        | OMEL.O         |

| Extended Output<br>Control   | 04            | BT656-4    |           |            |           |            |          |                 | RANGE          |