# YAMAHAL 5 I

# YM3437C

# Digital Audio Interface Transmitter (DIT2)

#### OUTLINE

The YM3437C (DIT2) is a serial digital audio transmitter LSI. DIT2 can convert 4 different kinds of serial digital audio data into EIAJ CP-340 or AES/EBU digital audio interface format. It has capabilities of outputting with the 24-bit output and also setting the channel status, user data, etc.

#### **■ FEATURES**

- Operation synchronous with the external clock signals inputted through the MCLK terminal.

- Useable for either 24-bit output by using the auxiliary bit of the digital audio interface signal or 20-bit output.

- All of the validity flag, channel status and user data can be set as a control code.

- Synchronous mode; All bits of the validity flag, channel status and user data can be set syn-

chronous with the audio data.

Asynchronous mode; The first 32 bits of each of the channel status and user data can be set independently from the audio data timing.

- The output data can be muted according to the MUTE signal from outside.

- 5V power supply, Si-gate CMOS, 16-pin DIP and 16-pin SOP.

-YAMAHA CORPORATION

YM3437C CATALOG CATALOG No. : LSI-2134372

1994. 04

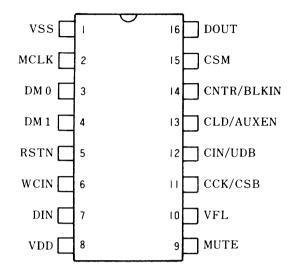

# ■ PIN CONFIGURATION

TOP VIEW (common to YM3437C-D and YM3437C-F)

# ■ PIN DESCRIPTION

| No. | Name       | I/O | Description                                                   |

|-----|------------|-----|---------------------------------------------------------------|

| 1   | VSS        |     | Ground                                                        |

| 2   | MCLK       | I   | Master clock input (128fs)                                    |

| 1   | 1          | _   | _                                                             |

| 3   | DM0        | Ι   | Data input mode select 0                                      |

| 4   | DM1        | I   | Data input mode select 1                                      |

| 5   | RSTN       | I   | System reset input ('L' active)                               |

| 6   | WCIN       | I   | Word clock input                                              |

| 7   | DIN        | I   | Audio data input                                              |

| 8   | VDD        |     | +5V power supply                                              |

| 9   | MUTE       | I   | DOUT output muting control input (when 'H', muted audio data) |

| 10  | VFL        | I   | Validity flag input                                           |

| 11  | CCK/CSB    | I   | CSM='L'; C, U bit data input, serial clock                    |

|     |            |     | CSM='H'; C bit data input                                     |

| 12  | CIN/UDB    | I   | CSM='L'; C, U bit data input, serial data                     |

|     |            |     | CSM='H'; U bit data input                                     |

| 13  | CLD/AUXEN  | I   | CSM='L'; C, U bit data input word clock                       |

|     |            |     | CSM='H'; 24-bit output at 'H' (AUX bit used)                  |

| 14  | CNTR/BLKIN | I   | CSM='L'; Local sample address reset input                     |

|     |            |     | CSM='H'; Block start clock                                    |

| 15  | CSM        | I   | Control code input mode select                                |

|     |            |     | ('L'; Asynchronous mode 'H'; Synchronous mode)                |

| 16  | DOUT       | O   | Digital audio interface signal output                         |

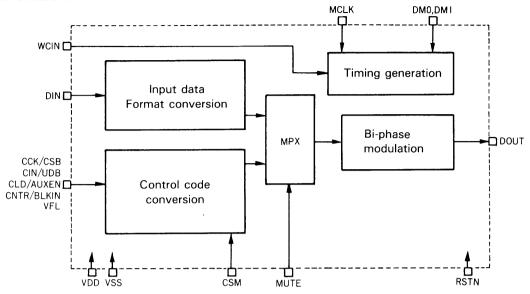

#### ■ BLOCK DIAGRAM

#### ■ FUNCTION DESCRIPTION

#### 1. Master clock MCLK

The 128fs master clock signal is inputted through the MCLK terminal.

#### 2. Audio data input DIN, WCIN, DM0, DM1

The audio data is inputted through the DIN terminal and the input format is selected by the DM0 or DM1 terminal.

# 3. Control code input CSM, VFL, CCK/CSB, CIN/UDB, CLD/AUXEN, CNTR/BLKIN

There are 2 types of the input mode for the control code and the CSM terminal is used for its selection.

(The function of each terminal of CIN/UDB, CCK/CSB, CLD/AUXEN and CNTR/BLKIN varies depending on the mode and the name is also indicated. Hereinafter, only the name corresponding to each mode is used.)

#### (1) CSM='H'; Parallel synchronous mode

V, U and C bit data are inputted through the VFL, UDB and CSB terminals respectively synchronized with the audio data.

It is possible to input the code for L and R independently.

When 'H' is inputted through the BLKIN terminal synchronized with the WCIN signal, the applicable frame comes to the head end (preamble "B") of the block. (Refer to the section describing the input format.)

Enter 'H' at every 192 frames. When 'H' is inputted to the AUXEN terminal in this mode, 24 bits of the audio data are output by using the AUX bit.

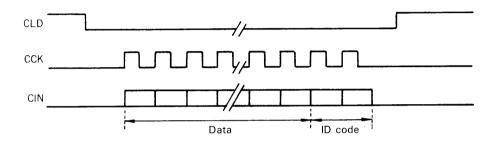

#### (2) CSM='L'; Serial asynchronous mode

From each terminal of CCK, CIN and CLD, the first 32 bits of the channel status and the user data can be set independently of the audio data timing.

Regarding the channel status, when the first bit is identified to be for the professional use format, 4 bytes of the local sample address, 1 byte of the reliability flag and 1 byte of the CRC are automatically generated internally. The same code is output at L and R.

The validity flag is inputted through the VFL terminal synchronized with the audio data as in the synchronous mode.

With the CLD set to 'L', the data is inputted to the CIN. The CIN data is taken in at the fall of the CCK. Two ID bits are placed after each data input in order to identify the serial data.

| ID code | Specified Bit No. | Content                                |

|---------|-------------------|----------------------------------------|

| ,00,    | 32 bits           | First 32 bits of channel status        |

| '10'    | 32 bits           | First 32 bits of user data (NOTE)      |

| '01'    | 4 bits            | Internal control                       |

|         |                   | 1st bit; Ubit ('1'=U bit data output)  |

|         |                   | 2nd bit; SMUTE ('1'=audio data muting) |

|         |                   | 3rd bit; AUXEN ('1'=AUX bit used)      |

|         |                   | 4th bit ; Enter '0'                    |

(NOTE) There is no specification to delimit the user data into the same blocks as the channel status, but in the asynchronous mode, the first 32 bits of the user data can be used in the same way as channel status.

In this mode, the 24-bit output is set by the 3rd bit of the internal control.

Also, setting the CNTR terminal to 'L' in this mode will reset all the local sample address codes for the professional use format to 'zero'.

#### 4. Data output DOUT, MUTE

The audio data and control code taken in are bi-phase modulated and output from the DOUT terminal. Whether to set the audio data processing length to 20 bits (or 16 bits for the DIN (4) of the input format) or 24 bits depends on the control code input mode. (Refer to the description in the previous section.)

Also, when the MUTE terminal is set to 'H', the audio data is all output as 'zero'. This does not affect the control code. When the CSM terminal is set to 'L', muting by the internal control bit is also possible.

#### 5. System reset RSTN

The internal register of the control code is initialized by setting the RSTN terminal to 'L' during the fs period.

The channel status data of the asynchronous mode is initialized to for consumer use, copy able, without emphasis and fs=48Hz.

The DOUT terminal becomes 'L' while the RSTN terminal is 'L'.

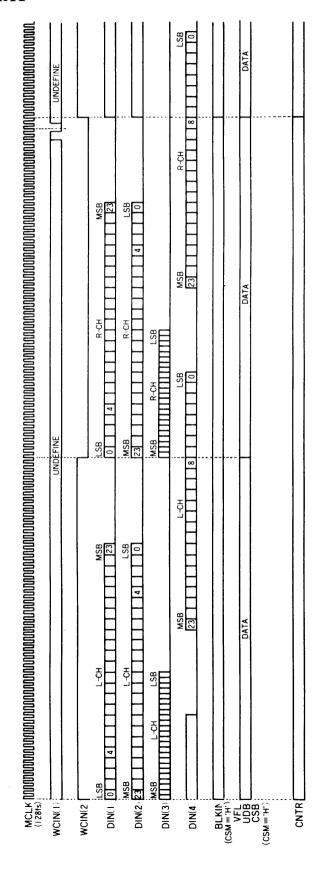

# ■ INPUT FORMAT

When the 20-bit input is used (AUXEN=L'), bits 0 to 3 of DIN (1), DIN (2) and DIN (3) and bits 0 to 7 of DIN (4) are invalid.

DIN (1), WCIN (1) DIN (2), WCIN (1) DIN (3), WCIN (1) DIN (4), WCIN (2)

3 2 3

ПППП

T H H H

DM0 | Input Mode

DM1

# ■ ELECTRICAL CHARACTERISTICS

#### • Absolute maximum ratings

| Parameter             | Symbol | Rating                           | Unit |

|-----------------------|--------|----------------------------------|------|

| Power supply voltage  | Vdd    | $-0.3 \sim 7.0$                  | V    |

| Input voltage         | Vı     | $V_{SS} - 0.3 \sim V_{DD} + 0.5$ | V    |

| Operating temperature | Top    | 0~+85                            | °C   |

| Storage temperature   | Tstg   | $-50 \sim +125$                  | °C   |

### • Recommended operating conditions

| Parameter             | Symbol            | Min. | Тур. | Max. | Unit |

|-----------------------|-------------------|------|------|------|------|

| Power supply voltage  | $V_{\mathrm{DD}}$ | 4.75 | 5.00 | 5.25 | V    |

| Operating temperature | Тор               | 0    | 25   | 85   | °C   |

### • DC characteristics (Conditions; $Ta=0 \sim 85$ °C, $V_{DD}=5.0 \pm 0.25$ V)

| Parameter              | Symbol | Condition                                          | Min. | Typ. | Max. | Unit |

|------------------------|--------|----------------------------------------------------|------|------|------|------|

| Power supply current   | Idd    | V <sub>DD</sub> =5.0V<br>f <sub>MC</sub> =6.144MHz |      |      | 5    | mA   |

| Input voltage H level  | Vih    |                                                    | 2.2  |      |      | V    |

| Input voltage L level  | VIL    |                                                    |      |      | 0.8  | V    |

| Input leakage current  | Ilk    |                                                    | -10  |      | 10   | μA   |

| Output voltage H level | Vон    | $I_{OH} = -0.4 \text{mA}$                          | 4.0  |      |      | V    |

| Output voltage L level | Vol    | IoL=2.0mA                                          |      |      | 0.4  | V    |

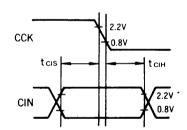

#### • AC characteristics (Conditions; $Ta=0 \sim 85$ °C, $V_{DD}=5.0 \pm 0.25$ V)

| Parameter        | Symbol       | Min.    | Typ. | Max. | Unit |

|------------------|--------------|---------|------|------|------|

| MCLK frequency   | fмc          |         |      | 6.4  | MHz  |

| MCLK duty        |              | 40      | 50   | 60   | %    |

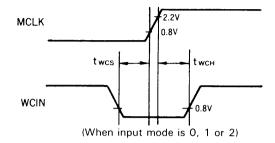

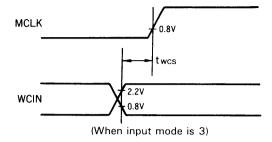

| WCIN setup time  | twcs         | 50      |      |      | ns   |

| WCIN hold time   | twch         | 0       |      |      | ns   |

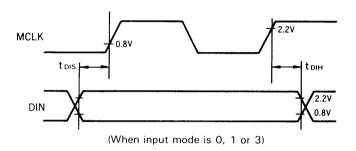

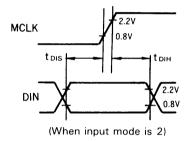

| DIN setup time   | tDIS         | 50      |      |      | ns   |

| DIN hold time    | tdin         | 0       |      |      | ns   |

| CIN setup time   | tcis         | 50      |      |      | ns   |

| CIN hold time    | <b>t</b> CIH | 0       |      |      | ns   |

| CLD ON time      |              | 5/fmc   |      |      |      |

| RSTN pulse width |              | 128/fмс |      |      |      |

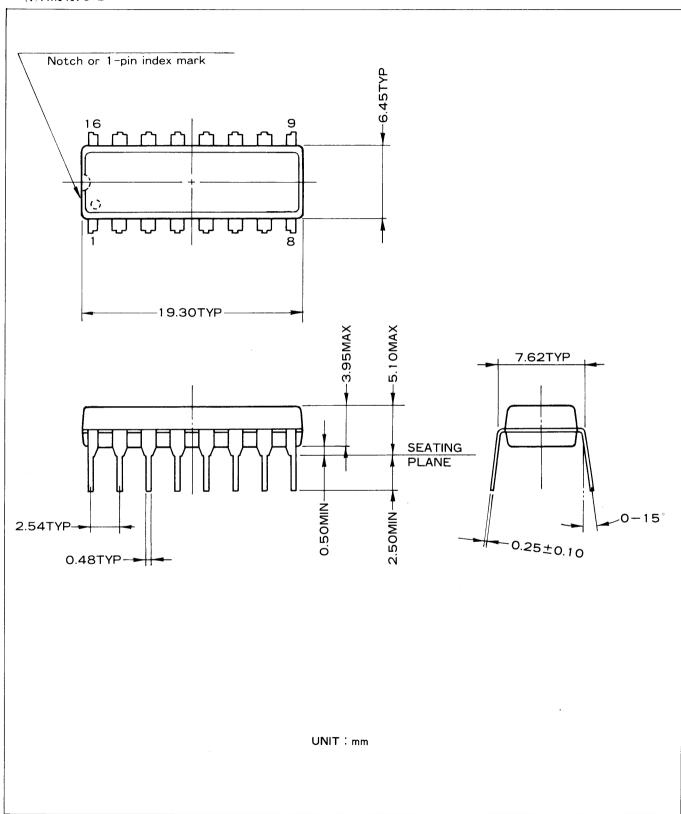

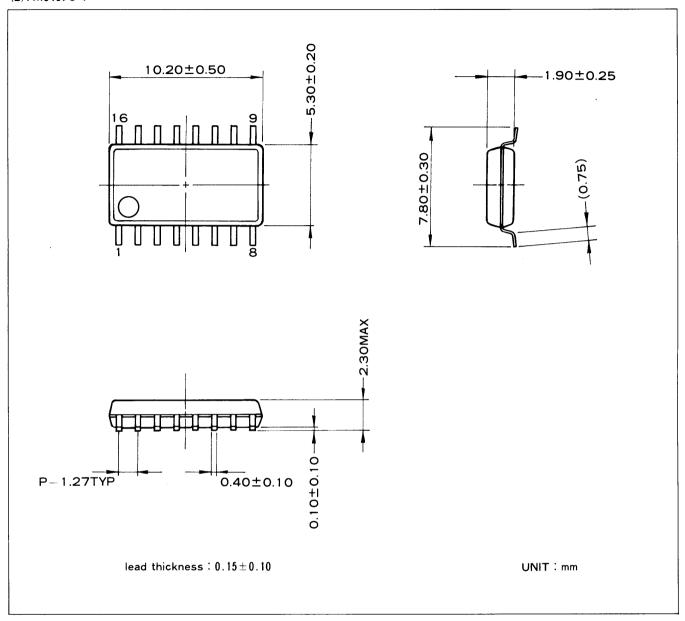

# ■ EXTERNAL DIMENSIONS

(1)YM3437C-D

#### (2)YM3437C-F

The specifications of this product are subject to improvement changes without prior notice.

### IMPORTANT NOTICE

- 1. Yamaha reserves the right to make changes to its Products and to this document without notice. The information contained in this document has been carefully checked and is believed to be reliable. However, Yamaha assumes no responsibilities for inaccuracies and makes no commitment to update or to keep current the information contained in this document.

- 2. These Yamaha Products are designed only for commercial and normal industrial applications, and are not suitable for other uses, such as medical life support equipment, nuclear facilities, critical care equipment or any other application the failure of which could lead to death, personal injury or environmental or property damage. Use of the Products in any such application is at the customer's sole risk and expense.

- 3. YAMAHA ASSUMES NO LIABILITY FOR INCIDENTAL, CONSEQUENTIAL OR SPECIAL DAMAGES OR INJURY THAT MAY RESULT FROM MISAPPLICATION OR IMPROPER USE OR OPERATION OF THE PRODUCTS.

- 4. YAMAHA MAKES NO WARRANTY OR REPRESENTATION THAT THE PRODUCTS ARE SUBJECT TO INTELLECTUAL PROPERTY LICENSE FROM YAMAHA OR ANYTHIRD PARTY, AND YAMAHA MAKES NO WARRANTY OR REPRESENTATION OF NON-INFRINGEMENT WITH RESPECT TO THE PRODUCTS. YAMAHA SPECIFICALLY EXCLUDES ANY LIABILITY TO THE CUSTOMER OR ANY THIRD PARTY ARISING FROM OR RELATED TO THE PRODUCTS' INFRINGEMENT OF ANY THIRD PARTY'S INTELLECTUAL PROPERTY RIGHTS, INCLUDING THE PATENT, COPYRIGHT, TRADEMARK OR TRADE SECRET RIGHTS OF ANY THIRD PARTY.

- 5. EXAMPLES OF USE DESCRIBED HEREIN ARE MERELY TO INDICATE THE CHARACTERISTICS AND PERFORMANCE OF YAMAHA PRODUCTS. YAMAHA ASSUMES NO RESPONSIBILITY FOR ANY INTELLECTUAL PROPERTY CLAIMS OR OTHER PROBLEMS THAT MAY RESULT FROM APPLICATIONS BASED ON THE EXAMPLES DESCRIBED HEREIN. YAMAHA MAKES NO WARRANTY WITH RESPECT TO THE PRODUCTS, EXPRESS OR IMPLIED, INCLUDING, BUT NOT LIMITED TO THE WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR USE AND TITLE.

The specifications of this product are subject to improvement changes without prior notice.

| — AGENCY — | <br> |

|------------|------|

|            |      |

|            |      |

|            |      |

|            |      |

|            |      |

## -YAMAHA CORPORATION

Address inquiries to:

Semiconductor Sales & Marketing Department

■ Head Office 203, Matsunokijima, Toyooka-mura, Iwata-gun, Shizuoka-ken, 438-0192

Tel. +81-539-62-4918 Fax. +81-539-62-5054

2-17-11, Takanawa, Minato-ku,

■ Tokyo Office

Tokyo, 108-8568

Tel. +81-3-5488-5431 Fax. +81-3-5488-5088

Namba Tsujimoto Nissei Bldg. 4F Osaka Office

1-13-17, Namba Naka, Naniwa-ku, Osaka City, Osaka, 556-0011

Tel. +81-6-6633-3690 Fax. +81-6-6633-3691

■ U.S.A. Office YAMAHA Systems Technology

100 Century Center Court, San Jose,

CA 95112

Tel. +1-408-467-2300 Fax. +1-408-437-8791