### INTEGRATED CIRCUITS

# DATA SHEET

# **GTL2002**

2-bit bi-directional low voltage translator

Product data sheet Supersedes data of 2003 Apr 01

### 2-bit bi-directional low voltage translator

**GTL2002**

#### **FEATURES**

- 2-bit bi-directional low voltage translator

- Allows voltage level translation between 1.0 V, 1.2 V, 1.5 V, 1.8 V, 2.5 V, 3.3 V, and 5 V buses which allows direct interface with GTL, GTL+, LVTTL/TTL and 5 V CMOS levels

- Provides bi-directional voltage translation with no direction pin

- Low 6.5  $\Omega$  RDS<sub>ON</sub> resistance between input and output pins (Sn/Dn)

- Supports hot insertion

- No power supply required Will not latch up

- 5 V tolerant inputs

- Low stand-by current

- Flow-through pinout for ease of printed circuit board trace routing

- ESD protection exceeds 2000 V HBM per JESD22-A114, 200 V MM per JESD22-A115, and 1000 V per JESD22-C101

- Packages offered: SO8, TSSOP8 (MSOP8), VSSOP8

#### **APPLICATIONS**

- Any application that requires bi-directional or unidirectional voltage level translation from any voltage between 1.0 V and 5.0 V to any voltage between 1.0 V and 5.0 V

- The open drain construction with no direction pin is ideal for bi-directional low voltage (e.g., 1.0 V, 1.2 V, 1.5 V, or 1.8 V) processor I<sup>2</sup>C port translation to the normal 3.3 V or 5.0 V I<sup>2</sup>C-bus signal levels or GTL/GTL+ translation to LVTTL/TTL signal levels.

#### **DESCRIPTION**

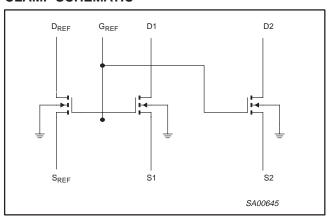

The Gunning Transceiver Logic — Transceiver Voltage Clamps (GTL–TVC) provide high-speed voltage translation with low ON-state resistance and minimal propagation delay. The GTL2002 provides 2 NMOS pass transistors (Sn and Dn) with a common gate (GREF) and a reference transistor (SREF and DREF). The device allows bi-directional voltage translations between 1.0 V and 5.0 V without use of a direction pin.

When the Sn or Dn port is LOW the clamp is in the ON-state and a low resistance connection exists between the Sn and Dn ports. Assuming the higher voltage is on the Dn port, when the Dn port is high, the voltage on the Sn port is limited to the voltage set by the reference transistor (SREF). When the Sn port is high, the Dn port is pulled to  $V_{CC}$  by the pull up resistors. This functionality allows a seamless translation between higher and lower voltages selected by the user, without the need for directional control.

All transistors have the same electrical characteristics and there is minimal deviation from one output to another in voltage or propagation delay. This is a benefit over discrete transistor voltage translation solutions, since the fabrication of the transistors is symmetrical. Because all transistors in the device are identical, S<sub>REF</sub> and D<sub>REF</sub> can be located on any of the other two matched Sn/Dn transistors, allowing for easier board layout. The translator's transistors provides excellent ESD protection to lower voltage devices and at the same time protect less ESD resistant devices.

### ORDERING INFORMATION

| PACKAGES                   | TEMPERATURE RANGE | ORDER CODE | TOPSIDE MARK | DWG NUMBER |

|----------------------------|-------------------|------------|--------------|------------|

| 8-Pin Plastic SO           | -40 °C to +85 °C  | GTL2002D   | GTL2002      | SOT96-1    |

| 8-Pin Plastic TSSOP (MSOP) | –40 °C to +85 °C  | GTL2002DP  | 2002         | SOT505-1   |

| 8-Pin Plastic VSSOP        | -40 °C to +85 °C  | GTL2002DC  | 2002         | SOT765-1   |

Standard packing quantities and other packaging data is available at www.standardproducts.philips.com/packaging.

2004 Sep 29 2

### 2-bit bi-directional low voltage translator

GTL2002

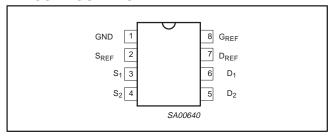

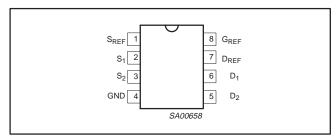

### PIN CONFIGURATION

Figure 1. SO8 and TSSOP8 pinning

Figure 2. VSSOP8 pinning

### PIN DESCRIPTION

| PIN NU            | IMBER               |                  |                                             |

|-------------------|---------------------|------------------|---------------------------------------------|

| SO8 and<br>TSSOP8 | VSSOP8              | SYMBOL           | NAME AND FUNCTION                           |

| 1                 | 4                   | GND              | Ground (0 V)                                |

| 2                 | 1                   | S <sub>REF</sub> | Source of reference transistor              |

| 3, 4              | 2, 3                | S <sub>n</sub>   | Port S <sub>1</sub> and Port S <sub>2</sub> |

| 5, 6              | 5, 6 D <sub>n</sub> |                  | Port D <sub>1</sub> and Port D <sub>2</sub> |

| 7                 | 7 D <sub>REF</sub>  |                  | Drain of reference transistor               |

| 8                 | 8                   | G <sub>REF</sub> | Gate of reference transistor                |

### **FUNCTION TABLE**

HIGH-to-LOW translation assuming Dn is at the higher voltage level

| G <sub>REF</sub> | D <sub>REF</sub> | S <sub>REF</sub>    | In-Dn | Out-Sn            | Transistor |

|------------------|------------------|---------------------|-------|-------------------|------------|

| Н                | Н                | 0 V                 | Х     | Х                 | Off        |

| Н                | Н                | V <sub>TT</sub>     | Н     | V <sub>TT</sub> 1 | On         |

| Н                | Н                | V <sub>TT</sub>     | L     | L <sup>2</sup>    | On         |

| L                | L                | 0 – V <sub>TT</sub> | Х     | Х                 | Off        |

H = HIGH voltage level

L = LOW voltage level

X = Don't Care

### NOTES:

1. Sn is not pulled up or pulled down.

2. Sn follows the Dn input LOW.

G<sub>REF</sub> should be at least 1.5 V higher than S<sub>REF</sub> for best translator operation.

4. V<sub>TT</sub> is equal to the S<sub>REF</sub> voltage.

### **FUNCTION TABLE**

LOW-to-HIGH translation assuming Dn is at the higher voltage level

| G <sub>REF</sub> | D <sub>REF</sub> | S <sub>REF</sub>    | In-Sn           | Out-Dn         | Transistor |

|------------------|------------------|---------------------|-----------------|----------------|------------|

| Н                | Н                | 0 V                 | Х               | Х              | Off        |

| Н                | Н                | V <sub>TT</sub>     | V <sub>TT</sub> | H <sup>1</sup> | nearly off |

| Н                | Н                | V <sub>TT</sub>     | L               | L <sup>2</sup> | On         |

| L                | L                | 0 – V <sub>TT</sub> | Х               | Х              | Off        |

H = HIGH voltage level

L = LOW voltage level

X = Don't Care

### NOTES:

- 1. Dn is pulled up to  $V_{CC}$  through an external resistor.

- 2. Dn follows the Sn input LOW.

- G<sub>REF</sub> should be at least 1.5 V higher than S<sub>REF</sub> for best translator operation.

- 4.  $V_{TT}$  is equal to the  $S_{REF}$  voltage.

### **CLAMP SCHEMATIC**

Figure 3. Clamp schematic

### 2-bit bi-directional low voltage translator

GTL2002

### **APPLICATIONS**

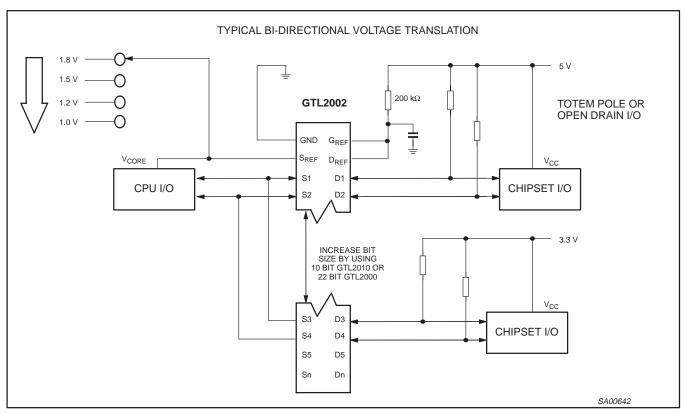

### Bi-directional translation

For the bi-directional clamping configuration, higher voltage to lower voltage or lower voltage to higher voltage, the  $G_{REF}$  input must be connected to  $D_{REF}$  and both pins pulled to HIGH side  $V_{CC}$  through a pull-up resistor (typically  $200~k\Omega$ ). A filter capacitor on  $D_{REF}$  is recommended. The processor output can be totem pole or open drain (pull-up resistors may be required) and the chipset output can be totem pole or open drain (pull-up resistors are required to pull the Dn outputs to  $V_{CC}$ ). However, if either output is totem pole, data must be uni-directional or the outputs must be 3-statable and the outputs must be controlled by some direction control mechanism to prevent HIGH-to-LOW contentions in either direction. If both outputs are open drain, no direction control is needed. The opposite side of the reference transistor ( $S_{REF}$ ) is connected to the processor core power supply voltage. When  $D_{REF}$  is connected through a 200  $k\Omega$  resistor to a 3.3 V to 5.5 V  $V_{CC}$  supply and  $S_{REF}$  is set between 1.0 V to  $V_{CC}$  – 1.5 V, the output of each Sn has a maximum output voltage equal to  $S_{REF}$  and the output of each Dn has a maximum output voltage equal to  $V_{CC}$ .

Figure 4. Bi-directional translation to multiple higher voltage levels such as an I2C-bus application

### 2-bit bi-directional low voltage translator

GTL2002

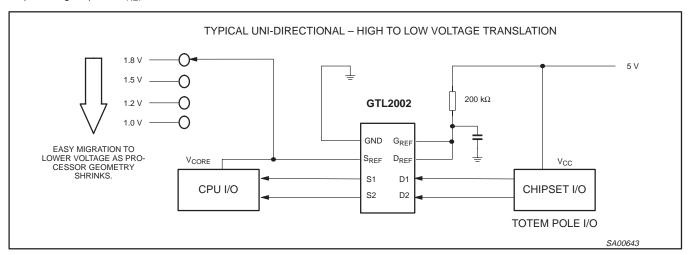

#### Uni-directional down translation

For uni-directional clamping, higher voltage to lower voltage, the  $G_{REF}$  input must be connected to  $D_{REF}$  and both pins pulled to the higher side  $V_{CC}$  through a pull-up resistor (typically 200 k $\Omega$ ). A filter capacitor on  $D_{REF}$  is recommended. Pull-up resistors are required if the chipset I/O are open drain. The opposite side of the reference transistor ( $S_{REF}$ ) is connected to the processor core supply voltage. When  $D_{REF}$  is connected through a 200 k $\Omega$  resistor to a 3.3 V to 5.5 V  $V_{CC}$  supply and  $S_{REF}$  is set between 1.0 V to  $V_{CC}$  – 1.5 V, the output of each Sn has a maximum output voltage equal to  $S_{REF}$ .

Figure 5. Uni-directional down translation, to protect low voltage processor pins

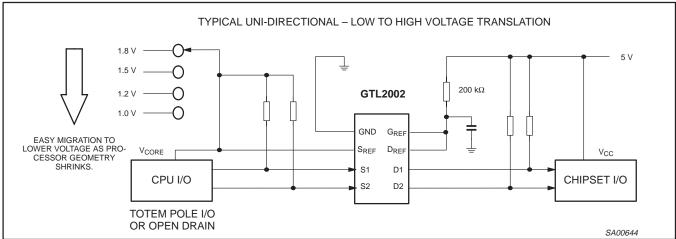

### Uni-directional up translation

For uni-directional up translation, lower voltage to higher voltage, the reference transistor is connected the same as for a down translation. A pull-up resistor is required on the higher voltage side (Dn or Sn) to get the full HIGH level, since the GTL-TVC device will only pass the reference source (S<sub>REF</sub>) voltage as a HIGH when doing an up translation. The driver on the lower voltage side only needs pull-up resistors if it is open drain.

Figure 6. Uni-directional up translation, to higher voltage chip sets

### 2-bit bi-directional low voltage translator

GTL2002

### Sizing pull-up resistor

The pull-up resistor value needs to limit the current through the pass transistor when it is in the "on" state to about 15 mA. This will guarantee a pass voltage of 260 mV to 350 mV. If the current through the pass transistor is higher than 15 mA, the pass voltage will also be higher in the "on" state. To set the current through each pass transistor at 15 mA, the pull-up resistor value is calculated as follows:

Resistor value (

$$\Omega$$

) =  $\frac{\text{Pull-up voltage (V)} - 0.35 \text{ V}}{0.015 \text{ A}}$

The table below summarizes resistor values for various reference voltages and currents at 15 mA and also at 10 mA and 3 mA. The resistor value shown in the +10 % column or a larger value should be used to ensure that the pass voltage of the transistor would be 350 mV or less. The external driver must be able to sink the total current from the resistors on both sides of the GTL-TVC device at 0.175 V, although the 15 mA only applies to current flowing through the GTL-TVC device. See Application Note AN10145-01 Bi-Directional Voltage Translators for more information.

### **PULL-UP RESISTOR VALUES**

|         | PULL-UP RESISTOR VALUE ( $\Omega$ ) |        |         |        |         |        |  |  |  |  |  |  |

|---------|-------------------------------------|--------|---------|--------|---------|--------|--|--|--|--|--|--|

| VOLTAGE | 15                                  | mA     | 10      | mA     | 3 n     | nA     |  |  |  |  |  |  |

| VOLTAGE | NOMINAL                             | + 10 % | NOMINAL | + 10 % | NOMINAL | + 10 % |  |  |  |  |  |  |

| 5.0 V   | 310                                 | 341    | 465     | 512    | 1550    | 1705   |  |  |  |  |  |  |

| 3.3 V   | 197                                 | 217    | 295     | 325    | 983     | 1082   |  |  |  |  |  |  |

| 2.5 V   | 143                                 | 158    | 215     | 237    | 717     | 788    |  |  |  |  |  |  |

| 1.8 V   | 97                                  | 106    | 145     | 160    | 483     | 532    |  |  |  |  |  |  |

| 1.5 V   | 77                                  | 85     | 115     | 127    | 383     | 422    |  |  |  |  |  |  |

| 1.2 V   | 57                                  | 63     | 85      | 94     | 283     | 312    |  |  |  |  |  |  |

#### NOTES:

- Calculated for V<sub>OL</sub> = 0.35 V

- Assumes output driver V<sub>OL</sub> = 0.175 V at stated current

+10 % to compensate for V<sub>DD</sub> range and resistor tolerance.

### ABSOLUTE MAXIMUM RATINGS<sup>1, 2, 3</sup>

| SYMBOL            | PARAMETER                            | CONDITIONS           | RATING       | UNIT |

|-------------------|--------------------------------------|----------------------|--------------|------|

| V <sub>SREF</sub> | DC source reference voltage          |                      | -0.5 to +7.0 | V    |

| $V_{DREF}$        | DC drain reference voltage           |                      | -0.5 to +7.0 | V    |

| V <sub>GREF</sub> | DC gate reference voltage            |                      | -0.5 to +7.0 | V    |

| V <sub>Sn</sub>   | DC voltage Port S <sub>n</sub>       |                      | -0.5 to +7.0 | V    |

| $V_{Dn}$          | DC voltage Port D <sub>n</sub>       |                      | -0.5 to +7.0 | V    |

| I <sub>REFK</sub> | DC diode current on reference pins   | V <sub>I</sub> < 0 V | -50          | mA   |

| I <sub>SK</sub>   | DC diode current Port S <sub>n</sub> | V <sub>I</sub> < 0 V | -50          | mA   |

| I <sub>DK</sub>   | DC diode current Port D <sub>n</sub> | V <sub>I</sub> < 0 V | -50          | mA   |

| I <sub>MAX</sub>  | DC clamp current per channel         | Channel in ON-state  | ±128         | mA   |

| T <sub>stg</sub>  | Storage temperature range            |                      | −65 to +150  | °C   |

- Stresses beyond those listed may cause permanent damage to the device. These are stress ratings only and functional operation of the device at these or any other conditions beyond those indicated under "recommended operating conditions" is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

- The performance capability of a high-performance integrated circuit in conjunction with its thermal environment can create junction temperatures which are detrimental to reliability. The maximum junction temperature of this integrated circuit should not exceed 150 °C.

- 3. The input and output negative voltage ratings may be exceeded if the input and output clamp current ratings are observed.

### 2-bit bi-directional low voltage translator

GTL2002

### **RECOMMENDED OPERATING CONDITIONS**

| SYMBOL            | PARAMETER                                | CONDITIONS  | LIM | UNIT |      |

|-------------------|------------------------------------------|-------------|-----|------|------|

| STWIBOL           | PARAMETER                                | CONDITIONS  | Min | Max  | UNIT |

| V <sub>I/O</sub>  | Input/output voltage (Sn, Dn)            |             | 0   | 5.5  | V    |

| V <sub>SREF</sub> | DC source reference voltage <sup>1</sup> |             | 0   | 5.5  | V    |

| V <sub>DREF</sub> | DC drain reference voltage               |             | 0   | 5.5  | V    |

| $V_{GREF}$        | DC gate reference voltage                |             | 0   | 5.5  | V    |

| I <sub>PASS</sub> | Pass transistor current                  |             | _   | 64   | mA   |

| T <sub>amb</sub>  | Operating ambient temperature range      | In free air | -40 | +85  | °C   |

### NOTE:

### **ELECTRICAL CHARACTERISTICS**

Over recommended operating free-air temperature range (unless otherwise noted)

| CVMDOL                       | DADAMETED                |                                                                  | FECT CONDITIONS                             |                         |      |                  |      |      |

|------------------------------|--------------------------|------------------------------------------------------------------|---------------------------------------------|-------------------------|------|------------------|------|------|

| SYMBOL                       | PARAMETER                |                                                                  | TEST CONDITIONS                             | •                       | MIN  | TYP <sup>1</sup> | MAX  | UNIT |

| V <sub>OL</sub>              | LOW-level output voltage | $V_{DD} = 3.0 \text{ V; } V_{SRE}$ $I_{clamp} = 15.2 \text{ mA}$ | <sub>EF</sub> = 1.365 V; V <sub>Sn</sub> or | $V_{Dn} = 0.175 V;$     | _    | 260              | 350  | mV   |

| V <sub>IK</sub>              | Input clamp voltage      | $I_{I} = -18 \text{ mA}$                                         | V <sub>GREF</sub> = 0 V                     |                         | _    | _                | -1.2 | V    |

| I <sub>IH</sub>              | Gate input leakage       | V <sub>I</sub> = 5 V                                             | V <sub>GREF</sub> = 0 V                     | _                       | _    | 5                | μΑ   |      |

| C <sub>I(GREF)</sub>         | Gate capacitance         | $V_I = 3 V \text{ or } 0 V$                                      |                                             | _                       | 19.4 | _                | pF   |      |

| C <sub>IO(OFF)</sub>         | Off capacitance          | $V_O = 3 \text{ V or } 0 \text{ V}$                              | V <sub>GREF</sub> = 0 V                     |                         | _    | 7.4              |      | pF   |

| C <sub>IO(ON)</sub>          | On capacitance           | $V_O = 3 \text{ V or } 0 \text{ V}$                              | V <sub>GREF</sub> = 3 V                     | V <sub>GREF</sub> = 3 V |      |                  | _    | pF   |

|                              |                          |                                                                  | V <sub>GREF</sub> = 4.5 V                   |                         | _    | 3.5              | 5    | Ω    |

|                              |                          |                                                                  | V <sub>GREF</sub> = 3 V                     | . 64 - 4                | _    | 4.4              | 7    |      |

|                              |                          | $V_I = 0 V$                                                      | V <sub>GREF</sub> = 2.3 V                   | I <sub>O</sub> = 64 mA  | _    | 5.5              | 9    |      |

|                              | On registeres            |                                                                  | V <sub>GREF</sub> = 1.5 V                   | 1                       | _    | 67               | 105  |      |

| r <sub>on</sub> <sup>2</sup> | On-resistance            |                                                                  | V <sub>GREF</sub> = 1.5 V                   | I <sub>O</sub> = 30 mA  | _    | 9                | 15   | Ω    |

|                              |                          | V 24V                                                            | V <sub>GREF</sub> = 4.5 V                   |                         | _    | 7                | 10   | Ω    |

|                              |                          | V <sub>I</sub> = 2.4 V                                           | V <sub>GREF</sub> = 3 V                     | I <sub>O</sub> = 15 mA  | _    | 58               | 80   |      |

|                              |                          | V <sub>I</sub> = 1.7 V                                           | V <sub>GREF</sub> = 2.3 V                   |                         |      | 50               | 70   |      |

### NOTES:

<sup>1.</sup>  $V_{SREF} \le V_{DREF} - 1.5 \text{ V}$  for best results in level shifting applications.

<sup>1.</sup> All typical values are measured at  $T_{amb}$  = 25 °C

Measured by the voltage drop between the Sn and the Dn terminals at the indicated current through the switch.

On-state resistance is determined by the lowest voltage of the two (Sn or Dn) terminals.

### 2-bit bi-directional low voltage translator

GTL2002

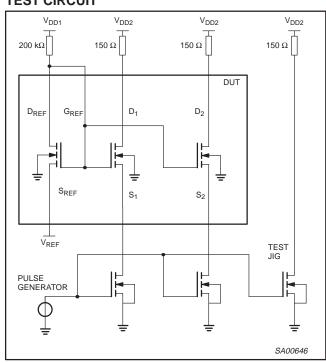

### AC CHARACTERISTICS FOR TRANSLATOR TYPE APPLICATIONS

$V_{REF} = 1.365 \text{ V to } 1.635 \text{ V; } V_{DD1} = 3.0 \text{ V to } 3.6 \text{ V; } V_{DD2} = 2.36 \text{ V to } 2.64 \text{ V; } GND = 0 \text{ V; } t_r = t_f \leq 3.0 \text{ ns. Refer to the Test Circuit diagram.}$

|                               |                                         |          |                    | UNIT             |     |    |

|-------------------------------|-----------------------------------------|----------|--------------------|------------------|-----|----|

| SYMBOL                        | PARAMETER                               | WAVEFORM | T <sub>amb</sub> = |                  |     |    |

|                               |                                         |          | MIN                | TYP <sup>1</sup> | MAX |    |

| t <sub>PLH</sub> <sup>2</sup> | Propagation delay<br>Sn to Dn; Dn to Sn |          | 0.5                | 1.5              | 5.5 | ns |

### NOTES:

- All typical values are measured at V<sub>DD1</sub> = 3.3 V, V<sub>DD2</sub> = 2.5 V, V<sub>REF</sub> = 1.5 V and T<sub>amb</sub> = 25 °C.

Propagation delay guaranteed by characterization.

C<sub>ON(max)</sub> of 30 pF and a C<sub>OFF(max)</sub> of 15 pF is guaranteed by design.

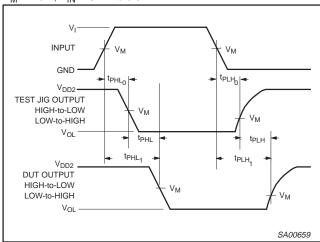

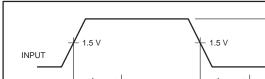

### **AC WAVEFORMS**

$V_{M} = 1.5 \text{ V}; V_{IN} = \text{GND to } 3.0 \text{ V}$

Waveform 1. The Input (S<sub>n</sub>) to Output (D<sub>n</sub>) propagation delays

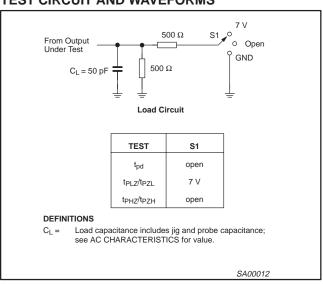

### **TEST CIRCUIT**

Waveform 2. Load circuit

### 2-bit bi-directional low voltage translator

GTL2002

### AC CHARACTERISTICS FOR CBT TYPE APPLICATION

$GND = 0 V; t_{R;} C_{L} = 50 pF$

|  | SYMBOL          | PARAMETER DESCRIPTION          | T <sub>amb</sub> :<br>G <sub>R</sub> | UNITS |     |    |

|--|-----------------|--------------------------------|--------------------------------------|-------|-----|----|

|  |                 |                                | Min                                  | Mean  | Max |    |

|  | t <sub>pd</sub> | Propagation delay <sup>1</sup> | _                                    | _     | 250 | ps |

### NOTES:

1. This parameter is warranted but not production tested. The propagation delay is based on the RC time constant of the typical on-state resistance of the switch and a load capacitance of 50 pF, when driven by an ideal voltage source (zero output impedance).

### **AC WAVEFORMS**

$V_M = 1.5 \text{ V}; V_{IN} = \text{GND to } 3.0 \text{ V}$

OUTPUT 0 V

1.5 V

VOL

SA00639

Waveform 3. Input (Sn) to Output (Dn) Propagation Delays

### **TEST CIRCUIT AND WAVEFORMS**

Waveform 4. Load circuit

### 2-bit bi-directional low voltage translator

GTL2002

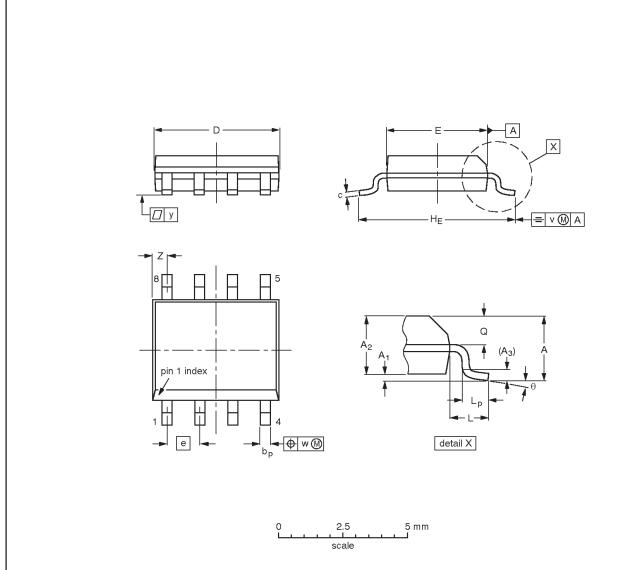

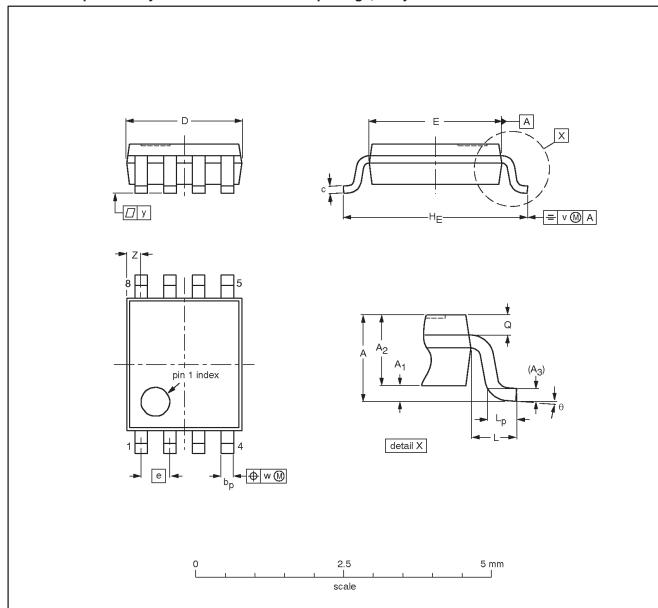

### SO8: plastic small outline package; 8 leads; body width 3.9 mm

SOT96-1

### DIMENSIONS (inch dimensions are derived from the original mm dimensions)

| UNIT   | A<br>max. | A <sub>1</sub> | A <sub>2</sub> | A <sub>3</sub> | bp           | С                | D <sup>(1)</sup> | E <sup>(2)</sup> | e    | HE             | L     | Lp             | œ              | v    | w    | у     | Z <sup>(1)</sup> | θ  |

|--------|-----------|----------------|----------------|----------------|--------------|------------------|------------------|------------------|------|----------------|-------|----------------|----------------|------|------|-------|------------------|----|

| mm     | 1.75      | 0.25<br>0.10   | 1.45<br>1.25   | 0.25           | 0.49<br>0.36 | 0.25<br>0.19     | 5.0<br>4.8       | 4.0<br>3.8       | 1.27 | 6.2<br>5.8     | 1.05  | 1.0<br>0.4     | 0.7<br>0.6     | 0.25 | 0.25 | 0.1   | 0.7<br>0.3       | 8° |

| inches | 0.069     | 0.010<br>0.004 | 0.057<br>0.049 | 0.01           |              | 0.0100<br>0.0075 | 0.20<br>0.19     | 0.16<br>0.15     | 0.05 | 0.244<br>0.228 | 0.041 | 0.039<br>0.016 | 0.028<br>0.024 | 0.01 | 0.01 | 0.004 | 0.028<br>0.012   | 0° |

### Notes

- 1. Plastic or metal protrusions of 0.15 mm (0.006 inch) maximum per side are not included.

- 2. Plastic or metal protrusions of 0.25 mm (0.01 inch) maximum per side are not included.

| OUTLINE<br>VERSION |        | REFER  | EUROPEAN | ISSUE DATE |                                 |

|--------------------|--------|--------|----------|------------|---------------------------------|

|                    | IEC    | JEDEC  | JEITA    | PROJECTION | ISSUE DATE                      |

| SOT96-1            | 076E03 | MS-012 |          |            | <del>99-12-27</del><br>03-02-18 |

2004 Sep 29 10

### 2-bit bi-directional low voltage translator

GTL2002

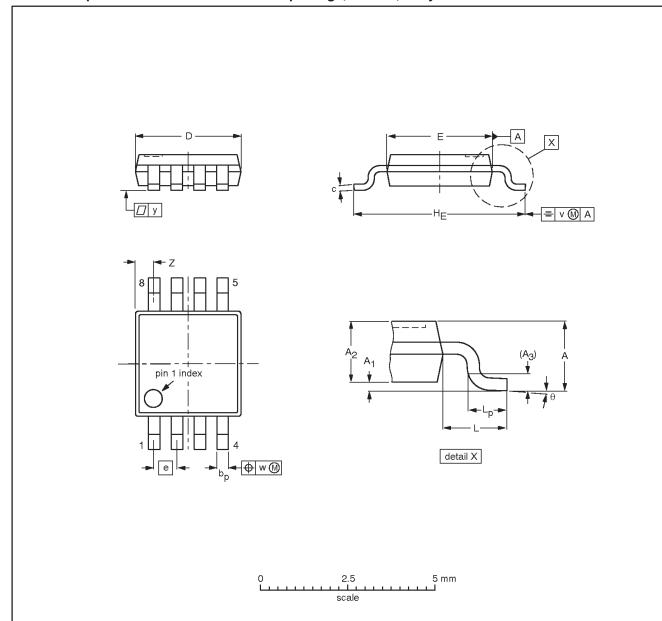

TSSOP8: plastic thin shrink small outline package; 8 leads; body width 3 mm

SOT505-1

### DIMENSIONS (mm are the original dimensions)

| UNIT | A<br>max. | A <sub>1</sub> | A <sub>2</sub> | A <sub>3</sub> | bp           | C            | D <sup>(1)</sup> | E <sup>(2)</sup> | e    | HE         | L    | Lp         | ٧   | w   | у   | Z <sup>(1)</sup> | θ        |

|------|-----------|----------------|----------------|----------------|--------------|--------------|------------------|------------------|------|------------|------|------------|-----|-----|-----|------------------|----------|

| mm   | 1.1       | 0.15<br>0.05   | 0.95<br>0.80   | 0.25           | 0.45<br>0.25 | 0.28<br>0.15 | 3.1<br>2.9       | 3.1<br>2.9       | 0.65 | 5.1<br>4.7 | 0.94 | 0.7<br>0.4 | 0.1 | 0.1 | 0.1 | 0.70<br>0.35     | 6°<br>0° |

#### Notes

- 1. Plastic or metal protrusions of 0.15 mm maximum per side are not included.

- 2. Plastic or metal protrusions of 0.25 mm maximum per side are not included.

| OUTLINE  |     | REFEF | EUROPEAN | ISSUE DATE |            |                                   |  |

|----------|-----|-------|----------|------------|------------|-----------------------------------|--|

| VERSION  | IEC | JEDEC | JEITA    |            | PROJECTION | ISSUE DATE                        |  |

| SOT505-1 |     |       |          |            |            | <del>-99-04-09-</del><br>03-02-18 |  |

### 2-bit bi-directional low voltage translator

GTL2002

### plastic very thin shrink small outline package; body width 2.3 mm

SOT765-1

### DIMENSIONS (mm are the original dimensions)

| UN | IT , | A<br>max. | A <sub>1</sub> | A <sub>2</sub> | A <sub>3</sub> | Ьp           | С            | D <sup>(1)</sup> | E <sup>(2)</sup> | е   | HE         | L   | Lp           | Q            | v   | w    | у   | Z <sup>(1)</sup> | θ  |

|----|------|-----------|----------------|----------------|----------------|--------------|--------------|------------------|------------------|-----|------------|-----|--------------|--------------|-----|------|-----|------------------|----|

| m  | m    | 1         | 0.15<br>0.00   | 0.85<br>0.60   | 0.12           | 0.27<br>0.17 | 0.23<br>0.08 | 2.1<br>1.9       | 2.4<br>2.2       | 0.5 | 3.2<br>3.0 | 0.4 | 0.40<br>0.15 | 0.21<br>0.19 | 0.2 | 0.13 | 0.1 | 0.4<br>0.1       | 8° |

- Plastic or metal protrusions of 0.15 mm maximum per side are not included.

Plastic or metal protrusions of 0.25 mm maximum per side are not included.

| OUTLINE  |     | REFER  | EUROPEAN | ISSUE DATE |            |            |

|----------|-----|--------|----------|------------|------------|------------|

| VERSION  | IEC | JEDEC  | JEITA    |            | PROJECTION | 1330E DATE |

| SOT765-1 |     | MO-187 |          |            |            | 02-06-07   |

## 2-bit bi-directional low voltage translator

GTL2002

### **REVISION HISTORY**

| Rev | Date     | Description                                                                                                                      |

|-----|----------|----------------------------------------------------------------------------------------------------------------------------------|

| _3  | 20040929 | Product data (9397 750 13058). Supersedes data of 2003 Apr 01 (9397 750 11349).                                                  |

|     |          | Modifications:                                                                                                                   |

|     |          | "Features" section on page 2, last bullet: add "(MSOP8)"                                                                         |

|     |          | ● "Ordering information" table on page 2: add "(MSOP)" to cell 8-Pin Plastic TSSOP in Packages column.                           |

|     |          | Add VSSOP8 package offering.                                                                                                     |

| _2  | 20030401 | Product data (9397 750 11349); ECN 853-2214 29603 Dated 28 February 2003.<br>Supersedes data dated 2000 Aug 16 (9397 750 07417). |

| _1  | 20000816 | Product data (9397 750 07417); ECN 853-2214 24367 dated 2000 Aug 16.                                                             |

2004 Sep 29 13

### 2-bit bi-directional low voltage translator

GTL2002

#### Data sheet status

| Level | Data sheet status [1]  | Product<br>status <sup>[2] [3]</sup> | Definitions                                                                                                                                                                                                                                                                                    |

|-------|------------------------|--------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| I     | Objective data sheet   | Development                          | This data sheet contains data from the objective specification for product development.  Philips Semiconductors reserves the right to change the specification in any manner without notice.                                                                                                   |

| II    | Preliminary data sheet | Qualification                        | This data sheet contains data from the preliminary specification. Supplementary data will be published at a later date. Philips Semiconductors reserves the right to change the specification without notice, in order to improve the design and supply the best possible product.             |

| III   | Product data sheet     | Production                           | This data sheet contains data from the product specification. Philips Semiconductors reserves the right to make changes at any time in order to improve the design, manufacturing and supply. Relevant changes will be communicated via a Customer Product/Process Change Notification (CPCN). |

<sup>[1]</sup> Please consult the most recently issued data sheet before initiating or completing a design.

### **Definitions**

Short-form specification — The data in a short-form specification is extracted from a full data sheet with the same type number and title. For detailed information see the relevant data sheet or data handbook.

Limiting values definition — Limiting values given are in accordance with the Absolute Maximum Rating System (IEC 60134). Stress above one or more of the limiting values may cause permanent damage to the device. These are stress ratings only and operation of the device at these or at any other conditions above those given in the Characteristics sections of the specification is not implied. Exposure to limiting values for extended periods may affect device reliability.

Application information — Applications that are described herein for any of these products are for illustrative purposes only. Philips Semiconductors make no representation or warranty that such applications will be suitable for the specified use without further testing or modification.

#### **Disclaimers**

Life support — These products are not designed for use in life support appliances, devices, or systems where malfunction of these products can reasonably be expected to result in personal injury. Philips Semiconductors customers using or selling these products for use in such applications do so at their own risk and agree to fully indemnify Philips Semiconductors for any damages resulting from such application.

Right to make changes — Philips Semiconductors reserves the right to make changes in the products—including circuits, standard cells, and/or software—described or contained herein in order to improve design and/or performance. When the product is in full production (status 'Production'), relevant changes will be communicated via a Customer Product/Process Change Notification (CPCN). Philips Semiconductors assumes no responsibility or liability for the use of any of these products, conveys no license or title under any patent, copyright, or mask work right to these products, and makes no representations or warranties that these products are free from patent, copyright, or mask work right infringement, unless otherwise specified.

#### **Contact information**

For additional information please visit

http://www.semiconductors.philips.com. Fax: +31 40 27 24825

For sales offices addresses send e-mail to: sales.addresses@www.semiconductors.philips.com.

© Koninklijke Philips Electronics N.V. 2004 All rights reserved. Printed in U.S.A.

Date of release: 09-04

Document order number: 9397 750 13058

Let's make things better.

Philips Semiconductors

<sup>[2]</sup> The product status of the device(s) described in this data sheet may have changed since this data sheet was published. The latest information is available on the Internet at URL http://www.semiconductors.philips.com.

<sup>[3]</sup> For data sheets describing multiple type numbers, the highest-level product status determines the data sheet status.