Data Sheet June 2001 File Number 4839.2

#### Wireless LAN Medium Access Controller

The Intersil HFA3842 Wireless LAN Medium Access Controller is part of the PRISM® 2.4GHz radio chip set. The HFA3842 directly interfaces with

the Intersil HFA386x family of Baseband Processors, offering a complete end-to-end chip set solution for wireless LAN products. Protocol and PHY support are implemented in firmware to allow custom protocol and different PHY transceivers.

The HFA3842 is designed to provide maximum performance with minimum power consumption. Package pin layout provides optimal PC board layout to all user interfaces.

Firmware implements the full IEEE 802.11 Wireless LAN MAC protocol. It supports BSS and IBSS operation under DCF, and operation under the optional Point Coordination Function (PCF). Low level protocol functions such as RTS/CTS generation and acknowledgement, fragmentation and de-fragmentation, and automatic beacon monitoring are handed without host intervention. Active scanning is performed autonomously once initiated by host command. Host interface command and status handshakes allow concurrent operations from multi-threaded I/O drivers. Additional firmware functions specific to access point applications are also available.

Designing wireless protocol systems using the HFA3842 is made easier with the availability of evaluation board, firmware, software device drivers, and complete documentation.

The HFA3842 is a WLAN MAC Controller IC, based on the HFA3841. Pin-for-pin upgrade replacement for the HFA3841.

#### **Features**

- New start up modes allow the PCMCIA Card Information Structure to be initialized from a serial EEPROM. This allows firmware to be downloaded from the host, eliminating the parallel Flash memory device.

- Firmware can be loaded from serial Flash memory.

- Direct attachment to a typical x16 SRAM using five control signals (RAMCS\_, MOE\_, MWEL\_, MLBE\_, and MUBE\_).

- Low frequency crystal oscillator to maintain time and allow baseband clock source to power off during sleep mode.

- Improved performance of internal WEP engine.

- On-chip execution can now be viewed while in debug mode.

- Independent programmable cycle timing for external chip selects allows attachment of slow memory devices without compromising higher speed instruction execution.

- · Pinout is backward compatible with HFA3841.

- IEEE802.11 Standard Data Rates: 1, 2, 5.5 and 11Mbps

- · Part of the Intersil PRISM Wireless LAN Chip Set

- Full Implementation of the MAC Protocol Specified in IEEE Standards 802.11-1999 and 802.11b

- PCMCIA Host Interface Supports Full 16-Bit Implementation of PC Card 16 (1995), also ISA PNP with Additional Chip

- · Host Interface Provides Dual Buffer Access Paths

- External Memory Interface Supports up to 4M bytes RAM

- Internal Encryption Engine Executes IEEE802.11 WEP

- Low Power Operation; 25mA Active, 8mA Doze, <1mA Sleep

- Operation at 2.7V to 3.6V Supply

- 5V Tolerant Host Interface Input/Outputs

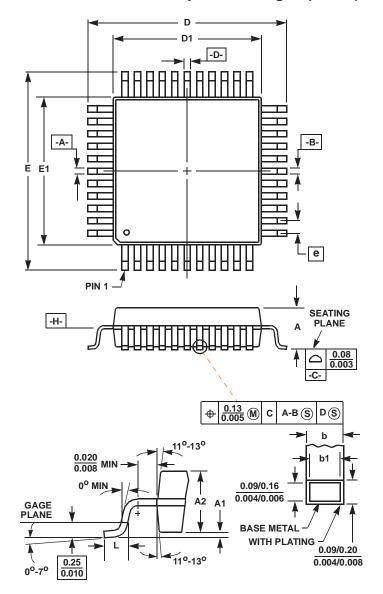

- 128 Pin LQFP Package Targeted for Type II PC Cards

- IEEE802.11 Wireless LAN MAC Protocol Firmware and Microsoft® Windows® Software Drivers

- Pin for Pin Replacement for the HFA3841 Supporting all Functions and operations of the HFA3841

# **Applications**

- High Data Rate Wireless LAN

- PC Card Wireless LAN Adapters

- PCI Wireless LAN Cards (Using Ext. Bridge Chip)

- · Wireless LAN Modules

- · Wireless LAN Access Points

- · Wireless Bridge Products

- · Wireless Point-to-Multipoint Systems

- · ISA, ISA PNP WLAN Cards

# Ordering Information

| PART<br>NUMBER | TEMP. RANGE<br>(°C) | PACKAGE       | PKG. NO.   |

|----------------|---------------------|---------------|------------|

| HFA3842IN      | -40 to 85           | 128 Ld LQFP   | Q128.14x20 |

| HFA3842IN96    | -40 to 85           | Tape and Reel |            |

Microsoft® and Windows® are registered trademarks of Microsoft Corporation.

PRISM® is a registered trademark of Intersil Americas Inc.

PRISM and design is a trademark of Intersil Americas Inc.

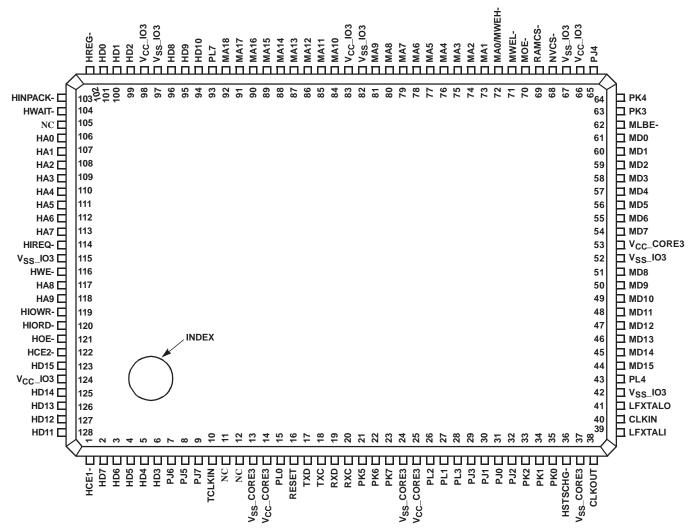

#### **Pinout**

#### 128 LEAD LQFP

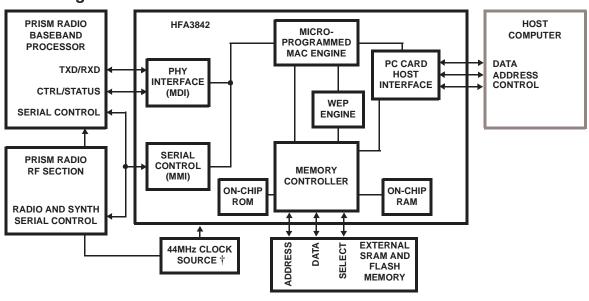

# Simplified Block Diagram

# **HFA3842 Pin Descriptions**

# **HOST INTERFACE PINS**

| PIN NAME    | PIN NUMBER                             | PIN I/O TYPE                        | DESCRIPTION                                                   |

|-------------|----------------------------------------|-------------------------------------|---------------------------------------------------------------|

| HA0-9       | 106-113, 117, 118                      | 5V Tol, CMOS, Input, 50K Pull Down  | PC Card Address Input, Bits 0 to 9                            |

| HCE1-       | 1                                      | 5V Tol, CMOS, Input, 50K Pull Up    | PC Card Select, Low Byte                                      |

| HCE2-       | 122                                    | 5V Tol, CMOS, Input, 50K Pull Up    | PC Card Select, High Byte                                     |

| HD0-15      | 101-99, 6-2,<br>96-94, 128-125,<br>123 | 5V Tol, BiDir, 2mA, 50K Pull Down   | PC Card Data Bus, Bit 0 to 15                                 |

| HINPACK-    | 103                                    | CMOS Output, 2mA                    | PC Card I/O Decode Confirmation                               |

| HIORD-      | 120                                    | 5V Tol, CMOS, Input, 50K Pull Up    | PC Card I/O Space Read                                        |

| HIOWR-      | 119                                    | 5V Tol, CMOS, Input, 50K Pull Up    | PC Card I/O Space Write                                       |

| HRDY/HIREQ- | 114                                    | CMOS Output, 4mA                    | PC Card interrupt Request (I/O Mode) Card Ready (Memory Mode) |

| HOE-        | 121                                    | 5V Tol, CMOS, Input, 50K Pull Up    | PC Card Memory Attribute Space Output Enable                  |

| HREG-       | 102                                    | 5V Tol, CMOS, Input, 50K Pull Up    | PC Card Attribute Space Select                                |

| HRESET      | 16                                     | 5V Tol, CMOS, ST Input, 50K Pull Up | Hardware Reset                                                |

| HSTSCHG-    | 36                                     | CMOS Output, 4mA                    | PC Card Status Change                                         |

| HWAIT-      | 104                                    | CMOS Output, 4mA                    | PC Card Not Ready (Force Host Wait State)                     |

| HWE-        | 116                                    | 5V Tol, CMOS Input, 50K Pull Up     | PC Card Memory Attribute Space Write Enable                   |

|             |                                        |                                     |                                                               |

|             |                                        |                                     |                                                               |

|             |                                        |                                     |                                                               |

### **TABLE 1. MEMORY INTERFACE PINS**

| PIN NAME               | PIN NUMBER   | PIN I/O TYPE                           | DESCRIPTION                                                                                                              |  |

|------------------------|--------------|----------------------------------------|--------------------------------------------------------------------------------------------------------------------------|--|

| MUBE- / MA0 /<br>MWEH- | 72           | CMOS TS Output, 2mA                    | MBUS Upper Byte Enable for x16 Memory; MBUS Address Bit 0 (byte) for x8 Memory; High Byte Write Enable for 2 x8 Memories |  |

| MA1-18                 | 73-81, 84-92 | CMOS TS Output, 2mA                    | MBUS Address Bits 1 to 18                                                                                                |  |

| PL4                    | 43           | CMOS BiDir, 2mA                        | MBUS Address Bit 19                                                                                                      |  |

| PL5                    | 12           | CMOS BiDir, 2mA, 50K Pull Up           | MBUS Address Bit 20                                                                                                      |  |

| PL6                    | 11           | CMOS BiDir, 2mA                        | MBUS Address Bit 21                                                                                                      |  |

| MLBE-                  | 62           | CMOS TS Output, 2mA, 50K Pull Up       | MBUS Lower Byte Enable, or I/O as PM2                                                                                    |  |

| MOE-                   | 70           | CMOS TS Output, 2mA                    | Memory Output Enable                                                                                                     |  |

| MWE- / MWEL-           | 71           | CMOS TS Output, 2mA                    | Low (or only) Byte Memory Write Enable                                                                                   |  |

| RAMCS-                 | 69           | CMOS TS Output, 2mA                    | RAM Select                                                                                                               |  |

| NVCS-                  | 68           | CMOS TS Output, 2mA                    | NV Memory Select                                                                                                         |  |

| MD0-7                  | 61-54        | 5V Tol, CMOS, BiDir, 2mA, 100K Pull Up | MBUS Low Data Byte, Bits 0 to 7                                                                                          |  |

| MD8-15                 | 51-44        | 5V Tol, CMOS, BiDir, 2mA 50K Pull Down | MBUS High Data Byte, Bits 8 to 15                                                                                        |  |

1

# TABLE 2. GENERAL PURPOSE AND EEPROM PORT PINS

| PIN NAME      | PIN NUMBER   | PIN I/O TYPE                   | DESCRIPTION OF FUNCTION<br>(IF OTHER THAN IO PORT) |

|---------------|--------------|--------------------------------|----------------------------------------------------|

| GENERAL PURPO | SE PORT PINS |                                |                                                    |

| TXD           | 17           | CMOS BiDir, 2mA, 50K Pull Down | Transmit Data Out                                  |

| TXC           | 18           | CMOS BiDir, 2mA                | Transmit Clock In/Out                              |

| RXD           | 19           | CMOS Input                     | Receive Data In                                    |

| RXC           | 20           | CMOS Input                     | Receive Clock In                                   |

#### HFA3842

TABLE 2. GENERAL PURPOSE AND EEPROM PORT PINS (Continued)

| PIN NAME      | PIN NUMBER | PIN I/O TYPE                       | DESCRIPTION OF FUNCTION<br>(IF OTHER THAN IO PORT) |

|---------------|------------|------------------------------------|----------------------------------------------------|

| PJ0           | 31         | CMOS BiDir, 2mA, 50K Pull Down     | MMI Clock (SCLK)                                   |

| PJ1           | 32         | CMOS BiDir, 2mA, 50K Pull Down     | MMI Serial Data (SD)                               |

| PJ3           | 29         | CMOS BiDir, 2mA                    | MMI Device Enable 0 (CS_BAR)                       |

| PJ4           | 65         | CMOS BiDir, 2mA                    | MMI Device Enable 1 (PE1)                          |

| PJ5           | 8          | CMOS BiDir, 2mA, 50K Pull Up       | MBUS Request (LE_IF)                               |

| PJ6           | 7          | CMOS BiDir, 2mA                    | MBUS Grant; LED                                    |

| PJ7           | 9          | CMOS BiDir, 2mA, 50K Pull Up       | (RADIO_PE)                                         |

| PK0           | 35         | CMOS BiDir, 2mA, ST, 50K Pull Down | MPSI Clock (LE_RF)                                 |

| PK1           | 34         | CMOS BiDir, 2mA, 50K Pull Down     | MPSI Data Out (SYNTHCLK)                           |

| PK2           | 33         | CMOS BiDir, 2mA, 50K Pull Down     | MPSI Data In (SYNTHDATA)                           |

| PK3           | 63         | CMOS BiDir, 2mA                    | MPSI Device Select 0 (PA_PE)                       |

| PK4           | 64         | CMOS BiDir, 2mA                    | MPSI Device Select 1 (PE2)                         |

| PK5           | 21         | CMOS BiDir, 2mA                    | PHY Data Available (MDREADY)                       |

| PK6           | 22         | CMOS BiDir, 2mA                    | PHY Medium Busy (CCA)                              |

| PK7           | 23         | CMOS BiDir, 2mA                    | PHY Energy Detect (CAL_EN)                         |

| PL0           | 15         | CMOS BiDir, 2mA                    | Transmitter Enable (TX_PE)                         |

| PL1           | 27         | CMOS BiDir, 2mA                    | Receiver Enable (or PHY Sleep Control) (RX_PE)     |

| PL2           | 26         | CMOS BiDir, 2mA                    | PHY Reset (RESET_BB)                               |

| PL3           | 28         | CMOS BiDir, 2mA                    | Antenna Select (T/R_SW_BAR)                        |

| PL4           | 43         | CMOS BiDir, 2mA                    | MBUS Address Bit 19 (MA19)                         |

| PL5           | 12         | CMOS BiDir, 2mA                    | MBUS Address Bit 20                                |

| PL6           | 11         | CMOS BiDir, 2mA                    | MBUS Address Bit 21                                |

| PL7           | 93         | CMOS BiDir, 2mA, Pull Down         | PHY Transmit Ready (T/R_SW)                        |

| SERIAL EEPROM | PORT PINS  |                                    |                                                    |

| PJ0           | 31         | CMOS BiDir                         | SCLK, Serial Clock                                 |

| PJ1           | 30         | CMOS BiDir, 50K Pull Down          | SD, Serial Data Out                                |

| PJ2           | 32         | CMOS BiDir, 50K Pull Down          | MISO, Serial Data IN                               |

| TCLKIN (CS_)  | 10         | CMOS BiDir                         | CS_, Chip Select                                   |

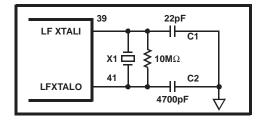

### TABLE 3. CLOCKS

| PIN NAME | PIN NUMBER | PIN I/O TYPE                   | DESCRIPTION                                                                |

|----------|------------|--------------------------------|----------------------------------------------------------------------------|

| CLKIN    | 40         | CMOS Input, ST Pull Down       | External Clock Input (at >= 2X Desired MCLK Frequency, Typically 44-48MHz) |

| LFXTALI  | 39         | Analog Input                   | 32.768kHz Crystal Input (Note 2)                                           |

| LFXTALO  | 41         | CMOS Output, 2mA               | 32.768kHz Crystal Output                                                   |

| CLKOUT   | 38         | CMOS, TS Output, 2mA           | Clock Output (Selectable as MCLK, TCLK, or TOUT0)                          |

| TCLKIN   | 10         | CMOS BiDir, 2mA, 50K Pull Down | Alternate clock input for timers                                           |

#### **TABLE 4. POWER**

| PIN NAME            | PIN NUMBER                          | PIN I/O TYPE        | DESCRIPTION |

|---------------------|-------------------------------------|---------------------|-------------|

| V <sub>CC</sub>     | 14, 25, 53, 66, 83, 98, 124         | 3.3V Supply         |             |

| V <sub>CC</sub> IO5 | 105                                 | 5V Tolerance Supply |             |

| V <sub>SS</sub>     | 13, 24, 37, 42, 52, 67, 82, 97, 115 | GND                 |             |

ST = Schmitt Trigger (Hysteresis), TS = Three-State. Signals ending with "-" are active low. NOTE:

3. Pin 39 (V<sub>CC</sub>\_CORE3 in 3841), has been reassigned as LFXTALI. For 3841 compatibility, it may be tied to V<sub>CC</sub>. Pin 62 (TRST- in 3841) has been reassigned as MLBE. For 3841 compatibility, it may be tied low through 1K. Pin 105 (V<sub>CC</sub>\_IO5 in 3841) has been reassigned. For 3841 compatibility, it may be tied to V<sub>CC</sub>. Output pins typically drive to positive voltage rail less 0.1V. Hence with a supply of 2.7V the output will just meet 5V TTL signal levels at rated loads.

# HFA3842

# TABLE 5. PORT PIN USES FOR PRISM APPLICATION

| PIN | NAME | PRISM I USE                                                                                                          | PRISM II USE                                                                           |  |

|-----|------|----------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------|--|

| 20  | RXC  | RXC - Receive Clock                                                                                                  | RXC - Receive Clock                                                                    |  |

| 19  | RXD  | RXD - Receive Data                                                                                                   | RXD - Receive Data                                                                     |  |

| 18  | TXC  | TXC - Transmit Clock                                                                                                 | TXC - Transmit Clock                                                                   |  |

| 17  | TXD  | TXD - Transmit Data                                                                                                  | TXD - Transmit Data                                                                    |  |

| 31  | PJ0  | SCLK - Clock for the SD Serial Bus                                                                                   | SCLK - Clock for the SD Serial Bus                                                     |  |

| 30  | PJ1  | SD - Serial Bidirectional Data Bus                                                                                   | SD - Serial Bi-Directional Data Bus                                                    |  |

| 32  | PJ2  | R/W - An input to the HFA3860A Used to Change the Direction of the SD Bus When Reading or Writing Data on the SD Bus | Not Used                                                                               |  |

| 29  | PJ3  | CS - A Chip Select for the Device to Activate the Serial Control Port (Active Low)                                   | CS_BAR - Chip Select for HFA3861 Baseband (Active Low)                                 |  |

| 65  | PJ4  | Not Used                                                                                                             | PE1 - Power Enable 1                                                                   |  |

| 8   | PJ5  | SYNTH_LE - Latches a Frame of 22 Bits After it has Been Shifted by the SCLK into the Synthesizer Registers           | LE_IF - Load Enable for HFA3783 Quad IF                                                |  |

| 7   | PJ6  | LED - Activity Indicator                                                                                             | LED - Activity Indicator                                                               |  |

| 9   | PJ7  | Not Used                                                                                                             | RADIO_PE - RF Power Enable                                                             |  |

| 35  | PK0  | Not Used                                                                                                             | LE_RF - Load Enable for HFA3683 RF Chip                                                |  |

| 34  | PK1  | Not Used                                                                                                             | SYNTHCLK - Serial Clock to Front End Chips                                             |  |

| 33  | PK2  | Not Used                                                                                                             | SYNTHDATA - Serial Data to Front End Chips                                             |  |

| 63  | PK3  | TX_PE_RF - Power Enable                                                                                              | PA_PE - Transmit PA Power Enable                                                       |  |

| 64  | PK4  | RX_PE_RF - Power Enable                                                                                              | PE2 - Power Enable 2                                                                   |  |

| 21  | PK5  | MD_RDY - Header Data and Data Packet are Ready to be Transferred From Baseband on RXD                                | MDREADY - Header Data and Data Packet are Ready to be Transferred from Baseband on RXD |  |

| 22  | PK6  | CCA - Signal that the Channel is Clear to Transmit                                                                   | CCA - Signal that the Channel is Clear to Transmit                                     |  |

| 23  | PK7  | RADIO_PE - Master Power Control for the RF Section                                                                   | CAL_EN - Calibration Mode Enable                                                       |  |

| 15  | PL0  | TX_PE and PA_PE - Transmit Enable to Baseband                                                                        | TX_PE - Transmit Enable to Baseband                                                    |  |

| 27  | PL1  | RX_PE - Receive Enable to Baseband                                                                                   | RX_PE - Receive Enable to Baseband                                                     |  |

| 26  | PL2  | RESET - Reset to Baseband                                                                                            | RESET_BB - Reset Baseband                                                              |  |

| 28  | PL3  | Not Used                                                                                                             | T/R-SW_BAR - Transient/Receive Control (Inverted)                                      |  |

| 43  | PL4  | MA19 (If Required)                                                                                                   | MA19 (If Required)                                                                     |  |

| 12  | PL5  | MA20 (If Required)                                                                                                   | MA20 (If Required)                                                                     |  |

| 11  | PL6  | MA21 (If Required)                                                                                                   | MA21 (If Required)                                                                     |  |

| 93  | PL7  | TX_RDY - Baseband Ready to Receive Data on TXD (Not Used By Firmware)                                                | T/R_SW - Transmit/Receive Control                                                      |  |

# **Absolute Maximum Ratings**

| <b>Operating Conditions</b>  |                             |

|------------------------------|-----------------------------|

| ESD Classification           |                             |

| Input, Output or I/O Voltage | GND -0.5V to $V_{CC}$ +0.5V |

| Supply Voltage               |                             |

| Voltage Range                | 3//        |

|------------------------------|------------|

|                              |            |

| Temperature Range40°C to 85° | 00         |

| Temperature Narige           | $^{\circ}$ |

# **Thermal Information**

| Thermal Resistance (Typical, Note 3)     | θ <sub>JA</sub> ( <sup>o</sup> C/W)  |

|------------------------------------------|--------------------------------------|

| LQFP Package                             | 50                                   |

| Maximum Storage Temperature Range65      | <sup>o</sup> C to 150 <sup>o</sup> C |

| Maximum Junction Temperature             | 100 <sup>o</sup> C                   |

| Maximum Lead Temperature (Soldering 10s) | 300°C                                |

| (Lead Tips Only)                         |                                      |

CAUTION: Stresses above those listed in "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress only rating and operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied.

4. θ<sub>JA</sub> is measured with the component mounted on a low effective thermal conductivity test board in free air. See Tech Brief TB379 for details.

# **Electrical Specifications**

| PARAMETER                   | SYMBOL           | TEST CONDITIONS                                                               | MIN                | TYP | MAX                | UNITS |

|-----------------------------|------------------|-------------------------------------------------------------------------------|--------------------|-----|--------------------|-------|

| Power Supply Current        | ICCOP            | V <sub>CC</sub> = 3.6V, CLK Frequency 44MHz                                   | -                  | 33  | 45                 | mA    |

| Input Leakage Current       | I <sub>I</sub>   | V <sub>CC</sub> = Max, Input = 0V or V <sub>CC</sub>                          | -10                | 1   | 10                 | μΑ    |

| Output Leakage Current      | IO               | V <sub>CC</sub> = Max, Input = 0V or V <sub>CC</sub>                          | -10                | 1   | 10                 | μΑ    |

| Logical One Input Voltage   | V <sub>IH</sub>  | V <sub>CC</sub> = Max, Min                                                    | 0.7V <sub>CC</sub> | -   | -                  | V     |

| Logical Zero Input Voltage  | V <sub>IL</sub>  | V <sub>CC</sub> = Min, Max                                                    | -                  | -   | 0.3V <sub>CC</sub> | V     |

| Logical One Output Voltage  | V <sub>OH</sub>  | I <sub>OH</sub> = -1mA, V <sub>CC</sub> = Min                                 | 0.9V <sub>CC</sub> | -   | -                  | V     |

| Logical Zero Output Voltage | V <sub>OL</sub>  | I <sub>OL</sub> = 2mA, V <sub>CC</sub> = Min                                  | -                  | 0.2 | 0.1V <sub>CC</sub> | V     |

| Input Capacitance           | C <sub>IN</sub>  | CLK Frequency 1MHz. All measurements referenced to GND. T <sub>A</sub> = 25°C | -                  | 5   | 10                 | pF    |

| Output Capacitance          | C <sub>OUT</sub> | CLK Frequency 1MHz. All measurements referenced to GND. T <sub>A</sub> = 25°C | -                  | 5   | 10                 | pF    |

#### NOTE:

# **AC Electrical Specifications**

| PARAMETER                                                     | SYMBOL          | MIN                      | TYP  | MAX                      | UNITS |

|---------------------------------------------------------------|-----------------|--------------------------|------|--------------------------|-------|

| CLOCK SIGNAL TIMING                                           |                 |                          |      | '                        |       |

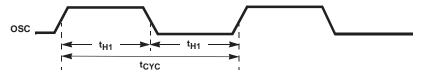

| OSC Clock Period (Typ. 44MHz)                                 | tcyc            | 20                       | 20.8 | 200                      | ns    |

| High Width                                                    | t <sub>H1</sub> | 10                       | 10.4 | -                        | ns    |

| Low Width                                                     | t <sub>L1</sub> | 10                       | 10.4 | -                        | ns    |

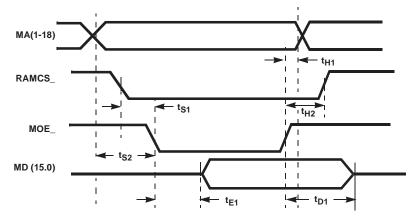

| EXTERNAL MEMORY INTERFACE                                     |                 |                          |      |                          |       |

| MOE_Setup Time From Ramcs                                     | t <sub>S1</sub> | 0                        | -    | -                        | ns    |

| MOE-Setup Time From MA (17.0)                                 | t <sub>S2</sub> | 0                        | -    | -                        | ns    |

| MA(18-1 Address Hold from MOE- Rising Edge                    | t <sub>H1</sub> | 20                       | -    | -                        | ns    |

| RAMCS Hold from MOE_ Rising Edge                              | t <sub>H2</sub> | 20                       | -    | -                        | ns    |

| MD(15:0) Enable from MOE-Falling                              | t <sub>E1</sub> | 5                        | -    | -                        | ns    |

| MD(15:0) Disable from MOE-Rising Edge                         | t <sub>D1</sub> | -                        | -    | 100                      | ns    |

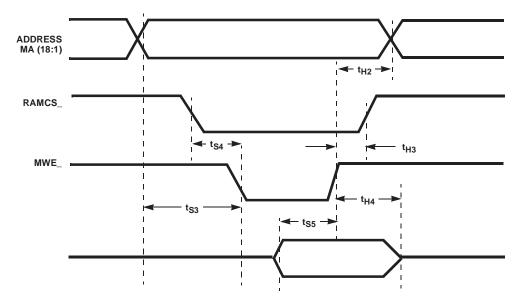

| EXTERNAL WRITE MEMORY INTERFACE                               |                 |                          |      |                          |       |

| MA (180) Address Setup Time to MWE Falling Edge               | t <sub>S3</sub> | 0                        | -    | -                        | ns    |

| RAMCS-Setup to MWE_                                           | t <sub>S4</sub> | 0                        | -    | -                        | ns    |

| MA (17.0) Hold From MWE_Rising Edge                           | t <sub>H2</sub> | 15                       | -    | -                        | ns    |

| RAMCS_Hold From MWE_Rising Edge                               | t <sub>H3</sub> | 15                       | -    | -                        | ns    |

| MD (15.0) Setup to MWE_Rising                                 | t <sub>S5</sub> | 40                       | -    | -                        | ns    |

| MD (15.0) Hold from MWE_Rising                                | t <sub>H4</sub> | 15                       | -    | -                        | ns    |

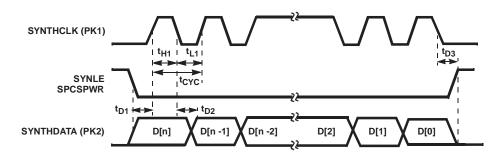

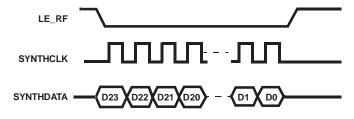

| SYNTHESIZER                                                   | ·               |                          |      |                          |       |

| SYNTHCLK (PK1) Period                                         | tcyc            | 83                       | -    | 4,000                    | ns    |

| SYNTHCLK (PK1) Width Hi                                       | t <sub>H1</sub> | t <sub>CYC</sub> /2 - 10 | -    | t <sub>CYC</sub> /2 + 10 | ns    |

| SYNTHCLK (PK1) Width Lo                                       | t <sub>L1</sub> | t <sub>CYC</sub> /2 - 10 | -    | t <sub>CYC</sub> /2 + 10 | ns    |

| SYNTHDATA (PK2) Hold Time from Falling Edge of SYNTHCLK (PK1) | t <sub>D2</sub> | 0                        | -    | -                        | ns    |

| SYNTHCLK (PK1) Falling Edge to SYNLE Inactive                 | t <sub>D3</sub> | 35                       | -    | -                        | ns    |

<sup>5.</sup> All values in this table have not been measured and are only estimates of the performance at this time.

### AC Electrical Specifications (Continued)

| PARAMETER                                            | SYMBOL                | MIN                  | TYP                   | MAX    | UNITS |

|------------------------------------------------------|-----------------------|----------------------|-----------------------|--------|-------|

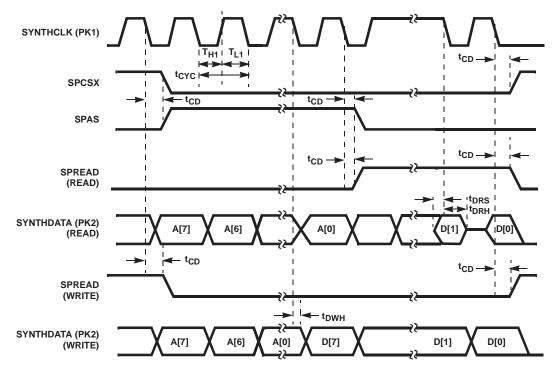

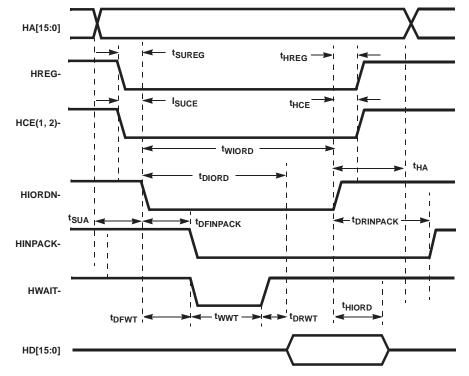

| SYSTEM INTERFACE - PC CARD IO READ 16                | 1                     |                      | -                     |        |       |

| Data Delay After HIORD-                              | tDIORD                | -                    | -                     | 100    | ns    |

| Data Hold Following HIORD-                           | tHIORD                | 0                    | -                     | -      | ns    |

| HIORD- Width Time                                    | twiord                | 165                  | -                     | -      | ns    |

| Address Setup Before HIORD-                          | tsua                  | 70                   | -                     | -      | ns    |

| Address Hold Following HIORD-                        | t <sub>HA</sub>       | 20                   | -                     | -      | ns    |

| HCE(1, 2)- Setup Before HIORD-                       | tsuce                 | 5                    | -                     | -      | ns    |

| HCE(1, 2)- Hold After HIORD-                         | tHCE                  | 20                   | -                     | -      | ns    |

| HREG- Setup Before HIORD-                            | tSUREG                | 5                    | -                     | -      | ns    |

| HREG- Hold Following HIORD-                          | tHREG                 | 0                    | -                     | -      | ns    |

| HINPACK- Delay Falling from HIORD-                   | t <sub>DFINPACK</sub> | 0                    | -                     | 45     | ns    |

| HINPACK- Delay Rising from HIORD-                    | d <sub>DRINPACK</sub> | 30                   | -                     | 45     | ns    |

| Data Delay from HWAIT- Rising                        | t <sub>DRWT</sub>     | -                    | -                     | 0      | ns    |

| HWAIT- Width Time                                    | t <sub>WWT</sub>      | -                    | -                     | 12,000 | ns    |

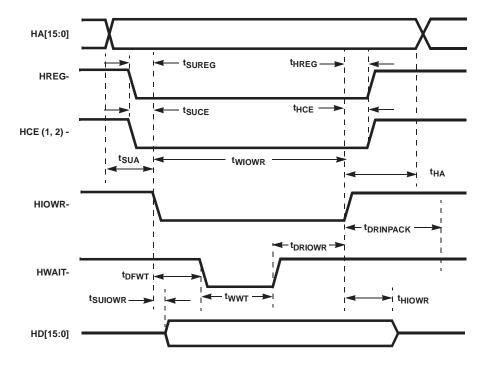

| SYSTEM INTERFACE - PC CARD IO WRITE 16               |                       |                      |                       |        |       |

| Data Setup Before HIORD-                             | tsulowr               | 30                   | -                     | 92     | ns    |

| Data Hold Following HIORD-                           | tHIOWR                | 20                   | -                     | -      | ns    |

| HIOWR- Width Time                                    | twiowr                | 165                  | -                     | -      | ns    |

| Address Setup Before HIORD-                          | tsua                  | 70                   | -                     | -      | ns    |

| Address Hold Following HIORD-                        | t <sub>HA</sub>       | 20                   | -                     | -      | ns    |

| HCE(1, 2)- Setup Before HIORD-                       | tsuce                 | 5                    | -                     | -      | ns    |

| HCE(1, 2)- Hold Following HIORD-                     | tHCE                  | 20                   | -                     | -      | ns    |

| HREG- Setup Before HIORD-                            | tSUREG                | 5                    | -                     | -      | ns    |

| HREG- Hold Following HIORD-                          | tHREG                 | 0                    | -                     | -      | ns    |

| HWAIT- Delay Falling from HIORD-                     | t <sub>DFWT</sub>     | -                    | -                     | 35     | ns    |

| HWAIT- Width Time                                    | t <sub>WWT</sub>      | -                    | -                     | 12,000 | ns    |

| HIOWR- High from HWAIT- High                         | t <sub>DRIOWR</sub>   | 0                    | -                     | -      | ns    |

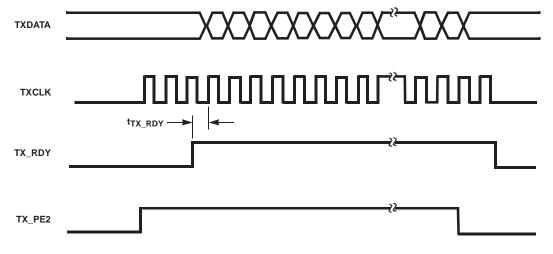

| RADIO TX DATA - TX PATH                              | ,                     |                      | -                     |        |       |

| TXC Period                                           | t <sub>TXC</sub>      | 4* t <sub>TMCK</sub> | -                     | -      | ns    |

| TXC Width Hi                                         | <sup>t</sup> CHM      | 31                   | -                     | -      | ns    |

| TXC Width Lo                                         | <sup>t</sup> CLM      | 31                   | -                     | -      | ns    |

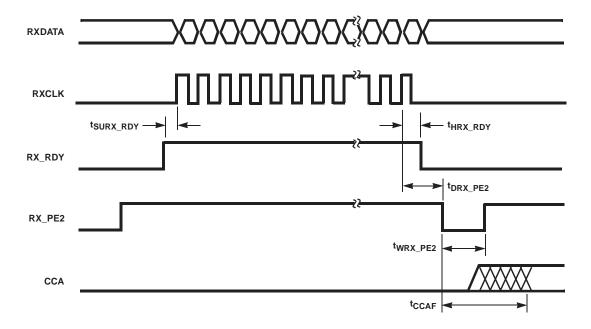

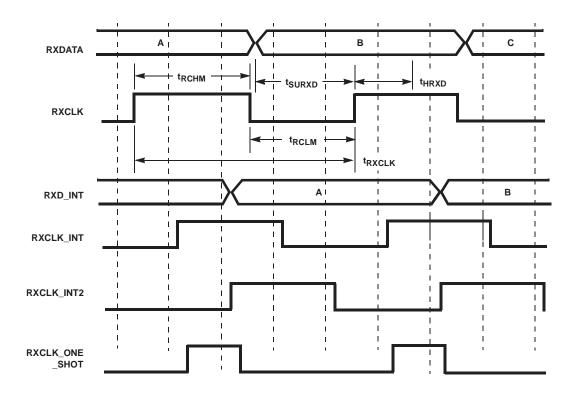

| RADIO RX DATA - RX PATH                              |                       |                      |                       |        |       |

| RX_RDY Setup Time to RXC Positive Edge (See Note 5)  | tsurx_rdy             | 10                   | -                     | -      | ns    |

| RX_RDY Hold Time from RXC Positive Edge (See Note 6) | tHRX_RDY              | 45                   | -                     | -      | ns    |

| RX_PE2 Delay from RX_RDY deAssert (See Note 10)      | t <sub>DRX_PE2</sub>  | -                    | 3 * t <sub>MCLK</sub> | -      | ns    |

| RX_PE2 Low Pulse Width (See Note 9)                  | t <sub>WRX_PE2</sub>  | -                    | 4 * t <sub>MCLK</sub> | -      | ns    |

| RXD Setup Time to RXC Positive Edge (See Note 7)     | tsurxd                | 10                   | -                     | -      | ns    |

| RXD Hold Time from RXC Positive Edge (See Note 7)    | tHRXD                 | 0                    | -                     | -      | ns    |

| RXC Period (See Note 12)                             | t <sub>RXC</sub>      | -                    | 3 * t <sub>MCLK</sub> | -      | ns    |

| RXC Width Hi                                         | t <sub>RCHM</sub>     | 31                   | -                     | -      | ns    |

| RXC Width Lo                                         | t <sub>RCLM</sub>     | 31                   | -                     | -      | ns    |

#### NOTES:

- 6. MD\_RDY is and'ed with RXC\_ONE\_SHOT (RXDAV) to shift data in shift register. RX\_RDY is not required to be valid until 1 MCLK after RXC is sampled high. Therefore, a negative setup time could be used. Since this is an unlikely scenario, we will leave it at a nominal 10ns setup time.

- 7. MD\_RDY is and'ed with RXC\_ONE\_SHOT (RXDAV) to shift data in shift register. Therefore, for the last data bit, the MD\_RDY must be held active until RXC\_ONE\_SHOT is sampled high by MAC's MCLK. However, it is assumed that BBP will be used in a mode that keeps RX\_RDY (MD\_RDY) and RXC running until RX\_PE2 is de-asserted. The MAC will stop processing data after the number of bits retrieved from the PLCP header length field are received. Therefore, the RX\_RDY hold time with respect to RXC does not matter. However, should the RX\_RDY signal be cleared when the last RXD bit is received the hold time w/r RXC must be honored.

- 8. RXC positive edge clocks a flop which stores the RXD for internal usage.

- 9. RXC period (and Hi/Lo times) must be long enough for flops clocked by MAC MCLK to see 1 RXC high and 1 RXC low.

- 10. RX\_PE inactive width at BBP is 3 BBP CLK's. Since BBP CLK and MAC CLK can be async minimum should be 4 MAC CLKs.

- 11. When RX\_RDY drops before expected number of RXD bits is received, then TX/RX FSM in mpctl.v signals timers which clear rx\_pe2\_int.

# Waveforms

FIGURE 1. CLOCK SIGNAL TIMING

FIGURE 2. EXTERNAL MEMORY READ TIMING

FIGURE 3. EXTERNAL MEMORY WRITE TIMING

FIGURE 4. SYNTHESIZER

# Waveforms (Continued)

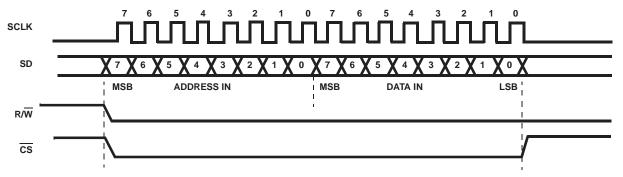

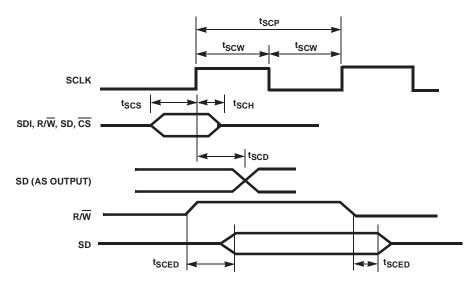

FIGURE 5. SERIAL PORT - HFA3824A/HFA3860B

FIGURE 6. PC CARD IO READ 16

# Waveforms (Continued)

FIGURE 7. PC CARD IO WRITE 16

FIGURE 8. TX PATH

# Waveforms (Continued)

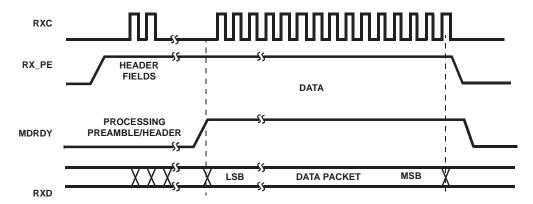

FIGURE 9. RX PATH

FIGURE 10. EXPANDED RX TIMING

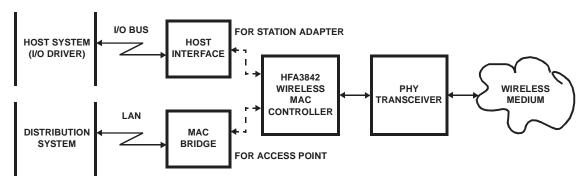

# HFA3842 System Overview

FIGURE 11. TYPICAL APPLICATION

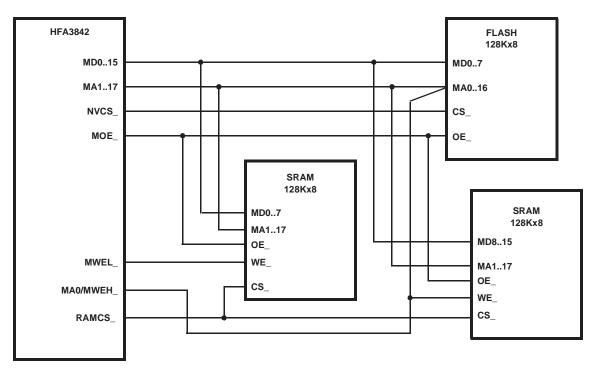

FIGURE 12. 8-BIT MEMORY INTERFACE

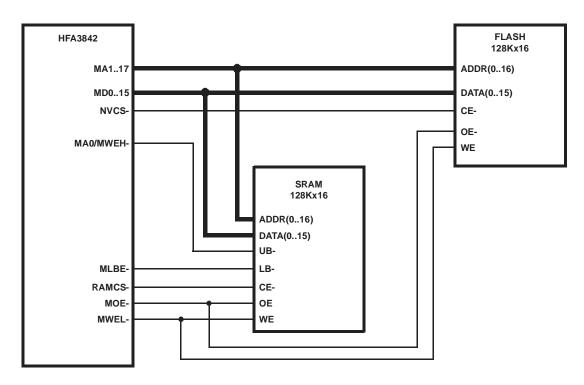

FIGURE 13. 16-BIT MEMORY INTERFACE

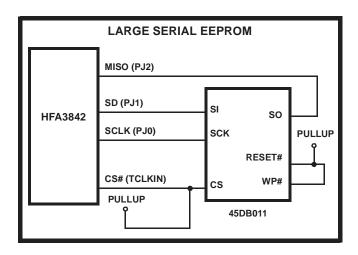

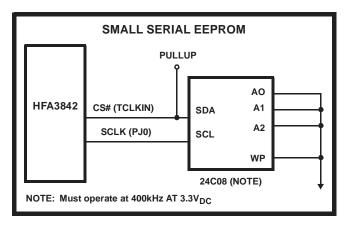

FIGURE 14. SERIAL EEPROM INTERFACE

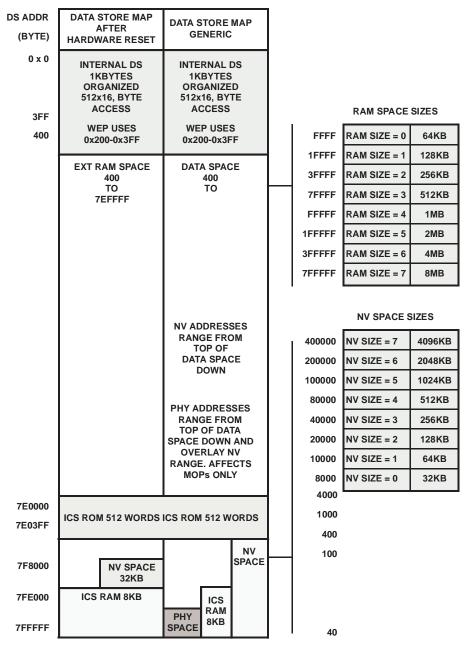

FIGURE 15. MEMORY MAP

# External Memory Interface

The HFA3842 provides separate external chip selects for code space and data storage space. Code space is accessible as data space through an overlay mechanism, except for an internal ROM. Refer to Figures 12, 13 and 14 for HFA3842 memory configuration details. Refer to Figure 15 for memory map.

The maximum possible memory space size is 4Mbytes.

Most of the data store space is reserved for storage of received and transmitted data, with some areas reserved for use by firmware. However, a portion of the data store may be

allocated as code store. This permits higher speed instruction execution, by using fast RAMs, than is possible from Flash memories. The maximum size of this overlay is the full code space address range, 128Kbytes, and is allocated in independent sections of 16KBytes each, on 16Kbyte boundaries, ranging from the highest address of the actual physical memory space and extending down.

Mapping code execution to RAM requires the RAM to have code written into it. Typically, this is done by placing code in a non-volatile memory such as a Flash in the code space. At initialization, the code in the non-volatile memory transfers itself to RAM, maps the appropriate blocks of the code space to the

RAM, and then branches to begin execution from RAM. This allows low cost, slow Flash devices to hold an entire code image, which can be executed much faster from RAM. If code is not placed in an external non-volatile memory as described here, it must be transferred to the RAM via the Host Interface.

Slow memories are not dynamically sensed. Following reset, the instruction clock operates with a slower cycle while the Flash is copied to RAM. Once code has been copied from Flash to RAM, execution transfers to RAM and the clock is raised to the normal operating frequency.

As mentioned above, it is feasible to operate without a code image in a non-volatile memory. In such a system, the firmware must be downloaded to RAM through the host interface before operation can commence.

The external SRAM memory must be organized in a 16-bit width to provide adequate performance to implement the 802.11 protocol at 11Mb/s rates. Systems designed for lower performance applications may be able to use 8-bit wide memory.

The minimum external memory is 128Kbytes of SRAM, organized 8 or 16 bits wide. Typical applications, including 802.11 station designs, use 256Kbytes organized 128K x 16. An access point application could make use of the full address space of the device with 4Mbytes organized a 2M x 16.

The HFA3842 supports 8 or 16 bit code space, and 8 or 16-bit data space. Code space is typically populated with the less expensive Flash memory available, usually an 8-bit device. Data space is usually populated with high-speed RAMs configured as a 16-bit space. This mixing of 8/16 bit spaces is fully supported, and may be done in any combination desired for code and data space.

The HFA3842 supports direct control of single chip 16-bit wide SRAMs with high/low byte enables, as well as direct control of a 16-bit space constructed from 8-bit wide SRAMs. The type of memory configuration is specified via the appropriate MD pin, sensed when the HFA3842 is reset.

HFA3842 pin MUBE-/MA0/MWEH- functions as Address 0 for 8-bit access, (such as Flash) as MWEH (High Byte Write Enable) when two x8 memories are configured as a single x16 space, and as the upper Byte Enable when a single x16 memory is used. No external logic is required to generate the required signals for both types of memory configurations, even when both exist together; all that is required is for the HFA3842 code to configure the HFA3842 memory controller to generate the proper signals for the particular address space being accessed.

For 8-bit spaces, the HFA3842 dynamically configures pin MUBE-/MA0/MWEH- cycle-by-cycle as the address LSB. MWEL-/MWE- is the only write control, and MOE- is the read output enable.

For 16-bit spaces constructed from 8-bit memories, the HFA3842 dynamically configures pin MUBE-/MA0/MWEH-cycle-by-cycle as the high byte write enable, MWEL- as the low write enable signal, and MOE- as the read output enable.

For 16-bit spaces constructed from single-chip x16 memories (such as SRAMs), the HFA3842 dynamically configures pin MUBE\_/MA0/MWEH- cycle-by-cycle as the upper byte enable. Pin MLBE- is connected as the low byte enable, MWEL-/MWE-is the write control, and MOE- is the read output enable.

These memory implementations require no external logic. The memory spaces may each be constructed from any type of memory desired. The only restriction is that a single memory space must be constructed from the same type of memory; for example, data space may not use both x8 and x16 memories, it must be all x8, or all x16. This restriction does not apply across memory spaces; e.g., code space may use a x8 memory and data space a single x16 memory, or code space two x8 memories and data space a single x8 memory.

Contact the factory for additional information in regards to HFA3842 to PRISM II MAC-less Connections.

#### Serial EEPROM Interface

The HFA3842 contains a small on-chip ROM Firmware which was added to allow the CIS or CIS plus firmware image to be transferred from an off-chip serial non-volatile memory device to RAM after a system Reset. This allows a system configuration without a parallel Flash Device. The operating frequency of the serial port is 400kHz with a voltage of 3.3V. Refer to Figure 14 for additional details on configuring the serial memory of the HFA3842. The Power On Reset Configuration section in this data sheet provides additional details on memory selection and control after a Reset condition.

#### Host Interface

#### PC Card Physical Interface

The Host interface is compatible to the PC Card 95 Standard (PCMCIA v2.1). The HFA3842 Host Interface pins connect directly to the correspondingly named pins on the PC Card connector with no external components (other than resistors) required. The HFA3842 operates as an I/O card using less than 64 octet locations. Reads and writes to internal registers and buffer memory are performed by I/O accesses. Attribute memory (256 octets) is provided for the CIS table which is located in external memory. Common memory is not used.

The following describes specific features of various pins:

#### HA[9:0]

Decoding of the system address space is performed by the HCEx-. During I/O accesses HA[5:0] decode the register. HA[9:6] are ignored when the internal HAMASK register is set to the defaults used by the standard firmware. During attribute memory accesses HA[9:1] are used.

#### HD[15:0]

The host interface is primarily designed for word accesses, although all byte access modes are fully supported. See HCE1-, HCE2- for a further description. Note that attribute memory is specified for and operates with even bytes accesses only.

### HCE1-, HCE2-

The PC Card cycle type and width are controlled with the CE signals. Word and Byte wide accesses are supported, using the combinations of HCE1-, HCE2-, and HA0 as specified in the PC Card standard.

#### HWE-, HOE-

HOE- and HWE- are only used to access attribute memory. Common Memory, as specified in the PC Card standard, is not used in the HFA3842. HOE- is the strobe that enables an attribute memory read cycle. HWE- is the corresponding strobe for the attribute memory write cycle. The attribute space contains the Card Information Structure (CIS) as well as the Function Configuration Registers (FCR).

#### HIORD-, HIOWR-

HIORD- and HIOWR- are the enabling strobes for register access cycles to the HFA3842. These cycles can only be performed once the initialization procedure is complete and the HFA3842 has been put into IO mode.

#### HREG-

This signal must be asserted for I/O or attribute cycles. A cycle with HREG- unasserted will be ignored as the HFA3842 does not support common memory.

#### HINPACK-

This signal is asserted by the HFA3842 whenever a valid I/O read cycle takes place. A valid cycle is when HCE1-, HCE2-, HREG-, and HIORD- are asserted, once the initialization procedure is complete.

### **HWAIT-**

Wait states are inserted in accesses using HWAIT-. The host interface synchronizes all PC Card cycles to the internal HFA3842 clock. The following wait states should be expected:

#### **Direct Read or Write to Hardware Register**

1/2 to 1 MCLK assertion of HWAIT- for internal synchronization.

# Write to Memory Mapped Register, Buffer Access Path, or Attribute Space (Post-Write)

- The data required for the write cycle will be latched and therefore only the synchronizing wait state will occur.

- Until the queued cycle has actually written to the memory, any subsequent access by the Host will result in a WAIT.

#### Read to Attribute Space and Memory Mapped Registers

WAIT will assert until the memory arbitration and access have completed.

#### **Buffer Access Paths, BAP0 and BAP1**

- An internal Pre-Read cycle to memory is initiated by a host Buffer Read cycle, after the internal address pointer has auto-incremented. If the next host cycle is a read to the same buffer, the data will be available without a memory arbitration delay.

- A single register holds the pre-read data. Thus, any read access to any other memory-mapped register (or the other buffer access path) will result in the pre-read data becoming invalidated.

- If another read cycle has invalidated the pre-read, then a memory arbitration delay will occur on the next buffer access path read cycle.

#### HIREQ-

Immediately after reset, the HIREQ- signal serves as the RDY/BSY (per the PC Card standard). Once the HFA3842 firmware initialization procedure is complete, HIREQ- is configured to operate as the interrupt to the PC Card socket controller. Both Level Mode and Pulse Mode interrupts are supported. By default, Level mode interrupts are used, so the interrupt source must be specifically acknowledged or disabled before the interrupt will be removed.

#### **HRESET**

When reset is removed, the CIS table is initialized and, once complete, HIREQ- is set high (HIREQ- acts as RDY/BSY from reset and is set high to indicate the card is ready for use). The CIS table resides in Flash memory and is copied to RAM during firmware initialization. The host system can then initialize the card by reading the CIS information and writing to the configuration register.

#### ISA PnP

The HFA3842 can be connected to the ISA bus and operate in a Plug and Play environment with an additional chip such as the Fujitsu MB86703, Texas Instruments TL16PNP200A, or Fairchild Semiconductor NM95MS15. See the Application Note AN9874, "ISA Plug and Play with the HFA3841" for more details.

#### Register Interface

The logical view of the HFA3842 from the host is a block of 32 word wide registers. These appear in IO space starting at the base address determined by the socket controller. There are three types of registers.

# HARDWARE REGISTERS (HW)

- 1 to 1 correspondence between addresses and registers.

- No memory arbitration delay, data transfer directly to/from registers.

- AUX base and offset are write-only, to set up access through AUX data port.

Note: All register cycles, including hardware registers, incur a short wait state on the PC Card bus to ensure the host cycle is synchronized with the HFA3842's internal MCLK.

#### **MEMORY MAPPED REGISTERS IN DATA RAM (MM)**

- 1 to 1 correspondence.

- Requires memory arbitration, since registers are actually locations in HFA3842 memory.

- Attribute memory access is mapped into RAM as Baseaddress + 0x400.

- AUX port provides host access to any location in HFA3842 RAM (reserved).

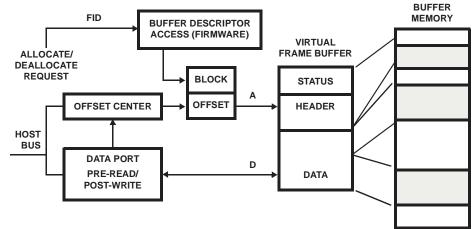

# **BUFFER ACCESS PATH (BAP)**

- No 1 to 1 correspondence between register address and memory address (due to indirect access through buffer address pointer registers).

- · Auto increment of pointer registers after each access.

- Require memory arbitration since buffers are located in HFA3842 memory.

- Buffer access may incur additional delay for Hardware Buffer Chaining.

**TABLE 6. MEMORY MAPPED REGISTER**

| I/O OFFSET | NAME        | TYPE       |

|------------|-------------|------------|

| 00         | Command     | MM         |

| 02         | Param0      | MM         |

| 04         | Param1      | MM         |

| 06         | Param2      | MM         |

| 08         | Status      | MM         |

| 0A         | Resp0       | MM         |

| 0C         | Resp1       | MM         |

| 0E         | Resp2       | MM         |

| 10         | InfoFID     | MM         |

| 20         | RxFID       | MM         |

| 22         | AllocFID    | MM         |

| 24         | TxComplFID  | MM         |

| 18         | BAP Select0 | MM         |

| 1C         | BAP Offset0 | MM         |

| 36         | BAP Data0   | BAP        |

| 1A         | BAP Select1 | MM         |

| 1E         | BAP Offset1 | MM         |

| 38         | BAP Data1   | BAP        |

| 30         | EvStat      | HW         |

| 32         | IntEn       | HW         |

| 34         | EvAck       | HW         |

| 14         | Control     | MM         |

| 28         | SwSupport0  | MM         |

| 2A         | SwSupport1  | MM         |

| 2C         | SwSupport2  | MM         |

| 3A         | AuxBase     | HW         |

| 3C         | AuxOffset   | HW         |

| 3E         | AuxData     | (Reserved) |

#### **Buffer Access Paths**

The HFA3842 has two independent buffer access paths, which permits concurrent read and write transfers. The firmware provides dynamic memory allocation between Transmit and Receive, allowing efficient memory utilization. On-the-fly allocation of (128-byte) memory blocks as needed for reception wastes minimal space when receiving fragments. The HFA3842 hides management of free memory from the driver, and allows fast response and minimum data copying for low latency. The firmware provides direct access to TX and RX buffers based on Frame ID (FID). This facilitates Power Management queuing, and allows dynamic fragmentation and defragmentation by controller. Simple Allocate/Deallocate commands ensure low host CPU overhead for memory management.

Hardware buffer chaining provides high performance while reading and writing buffers. Data is transferred between the host driver and the HFA3842 by writing or reading a single register location (The Buffer Access Path, or BAP). Each access increments the address in the buffer memory. Internally, the firmware allocates blocks of memory as needed to provide the requested buffer size. These blocks may not be contiguous, but the firmware builds a linked list of pointers between them. When the host driver is transferring data through a buffer access path and reaches the end of a physical memory block, hardware in the host interface follows the linked list so that the buffer access path points to the beginning of the next memory block. This process is completely transparent to the host driver, which simply writes or reads all buffer data to the same register. If the host driver attempts to access beyond the end of the allocated buffer, subsequent writes are ignored, and reads will be undefined.

#### PHY Interface

The HFA3842 is intended to support the PRISM family of Baseband processors with no additional components. This family currently includes the HFA3860B, HFA3861B, HFA3861 and HFA3863 baseband processors and the other ICs in the PRISM radio chip set. (Other baseband processors may be supported with custom firmware. See your sales representative for more information). The HFA3842 interfaces to the HFA386X baseband processors through two serial interfaces. The Modem Management Interface (MMI) is used to read and write internal registers in the baseband processor and access perpacket PLCP information. The Modem Data Interface (MDI) provides the receive and transmit data paths which transfer the actual MPDU data.

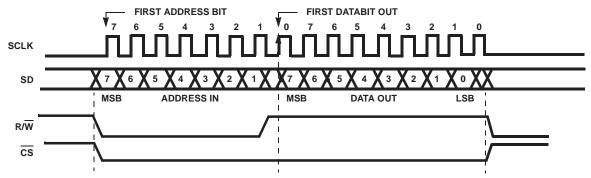

#### Serial Control Port (MMI)

The HFA3842 has a serial port that is used to program the baseband processor. There are individual chip selects and shared clock and data lines.

The MMI is used to program the registers and functionality of the PHY baseband processor.

#### PHY BASEBAND PROCESSOR

The PHY baseband processor is programmed by HFA3842 firmware.

The PRISM II baseband processor mode works as follows:

The Control Port consists of 3 signals: SD (serial data), SCLK (serial clock), and CS\_BAR (active-low chip select).

Control Port signaling for read and write operations is illustrated in Figures 17 and 18 respectively. Detailed timing relationships appear in Figure 19 and timing specifications are contained in Table 7.

The BBP always uses the rising edge when clocking data on the Control Port. This means that when the BBP is receiving data it uses the rising edge of clock to sample; when driving data, transitions occur on the rising edge.

Address bits 6 through 1 are significant for selecting configuration registers. Address bits 7 and 0 are unused. See the BBP Programming section for register addresses and suggested values.

For read operations, the rising edge of R/W must occur after the 7th but prior to the 8th rising edge of SCLK. This ensures that the first data bit is clocked out of the BBP prior to the edge used to clock it into the MAC.

For more detailed information on the Control Port and BBP register programming see the HFA386x data sheets.

FIGURE 16. BLOCK DIAGRAM OF A BUFFER ACCESS PATH

FIGURE 17. PRISM II BASEBAND PROCESSOR CONTROL PORT READ TIMING

FIGURE 18. PRISM II BASEBAND PROCESSOR SERIAL CONTROL PORT WRITE TIMING

FIGURE 19. BBP CONTROL PORT SIGNAL TIMING

TABLE 7. BBP CONTROL PORT AC ELECTRICAL SPECIFICATIONS

| PARAMETER                                        | SYMBOL | MIN | MAX | UNITS |

|--------------------------------------------------|--------|-----|-----|-------|

| SCLK Clock Period                                | tSCP   | 90  | -   | ns    |

| SCLK Width Hi or Low                             | tscw   | 20  | -   | ns    |

| Setup to SCLK + Edge<br>(SD, SDI, R/W, CS)       | tscs   | 30  | -   | ns    |

| Hold Time from SCLK +<br>Edge (SD, SDI, R/W, CS) | tsch   | 0   | -   | ns    |

| SD Out Delay from SCLK + Edge                    | tscd   | -   | 30  | ns    |

| SD Out Enable/Disable from R/W                   | tSCED  | -   | 15  | ns    |

#### **SYNTHESIZER**

For the PRISM II, the synthesizer is programmed by firmware using different pins than the MMI. The HFA3842 will exchange data with the baseband during transmit and receive operations over the MMI interface. If the MMI interface was connected to the front end chips, the transitions on SCLK and SD could couple noise into them. The synthesizer serial bus consists of SYNTHDATA, SYNTHCLK, LE\_IF and LE\_RF. SYNTHDATA is on pin PK2, SYNTHCLK is on PK1, LE\_IF is the enable for the HFA3783 Quad IF chip, and LE\_RF is the enable for the HFA3683 synthesizer.

Data is provided on SYNTHDATA and clock on SYNTHCLK. The data is updated the falling edge of SYNTHCLK and expected to be latched into the synthesizer on the rising edge. The enable signal LE\_RF is asserted while data is clocked out.

FIGURE 20. SYNTHESIZER DATA FORMAT

# PHY Data Interface (MDI)

The HFA3842 has a dedicated serial port to provide the data interface to the baseband processor. This is referred to as the Modem Data Interface (MDI). The MDI operates on the data being transferred to and from the baseband on a word by word basis. There are no FIFOs needed, since the firmware is able to control the protocol in real time.

The MDI performs the following functions:

- Serial to parallel conversion of received data from the baseband, with synchronization between the incoming RX clock to the internal HFA3842 clock.

- Generating CRCs (HEC and FCS) from the received data stream to verify correct reception.

- Decrypt the received data when WEP is enabled.

- Parallel to serial conversion of transmit data, with the serial timing synchronized with the TX clock.

- Insertion of the CRCs (HEC and FCS) at the appropriate point during transmission.

- Encrypt the transmitted data when WEP is enabled.

The receive data path uses RX\_RDY, RXC, RXD. The transmit data path uses TX\_RDY, TXC, TXD and the CCA input to determine (under the IEEE802.11 protocol) whether to transmit.

In transmit mode, the HFA386X is used in the mode where it generates the PLCP header internally and only the MPDU is passed from HFA3842. In receive, the HFA386X is used in the mode where it passes the PLCP header and the MPDU to the HFA3842.

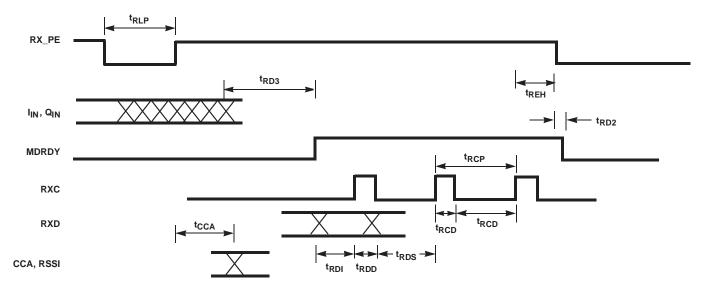

# **BBP Packet Reception**

There are 4 signals associated with the BBP Receive Port: RX\_PE (Receive Enable), MDRDY (Receive Ready), RXD (Receive Data), and RXCLK (Receive Clock). These connect to the HFA3842 on pins PL1, PK5, RXD, and RXC, respectively.

The receive demodulator in the BBP is activated via RX\_PE. When RX\_PE goes active the demodulator scrutinizes I and Q for packet activity. When a packet arrives at a valid signal level the demodulator acquires and tracks the incoming signal. It then sifts through the demodulator data for the Start Frame Delimiter (SFD). Normally, MDRDY is programmed to

go active after SFD is detected. This signals the HFA3842, allowing it to pick off the needed header fields from the real-time demodulated bitstream rather than having to read these fields through the BBP Control Port.

Assuming all is well with the header, the BBP decodes the signal field in the header and switches to the appropriate data rate. If the signal field is not recognized, or the CRC16 is in error, then MDRDY will go inactive shortly after CRC16 and the demodulator will return to acquisition mode looking for another packet. If all is well with the header, and after the demodulator has switched to the appropriate data rate, then the demodulator will continue to provide data to the HFA3842 indefinitely.

Receive Port exchange details are depicted in Figure 21. Detailed timing is related in Figure 22 and Table 8.

For more detailed information concerning BBP packet reception see the HFA386x data sheets.

FIGURE 21. BBP RECEIVE PORT TIMING

FIGURE 22. BBP RECEIVE PORT SIGNAL TIMING

NOTE: RXD, MDRDY is output two MCLK after RXC rising to provide hold time. RSSI output on TEST (5:0).

TABLE 8. BBP RECEIVE PORT AC ELECTRICAL SPECIFICATIONS

| PARAMETER                            | SYMBOL           | MIN  | MAX  | UNITS        |

|--------------------------------------|------------------|------|------|--------------|

| RX_PE Inactive Width                 | t <sub>RLP</sub> | 70   | -    | ns (Note 11) |

| RXC Period (11MBps Mode)             | t <sub>RCP</sub> | 77   | -    | ns           |

| RXC Width Hi or Low (11MBps Mode)    | t <sub>RCD</sub> | 31   | -    | ns           |

| RXC to RXD                           | t <sub>RDD</sub> | 20   | 60   | ns           |

| MD_RDY to 1st RXC                    | <sup>t</sup> RD1 | 940  | -    | ns (Note 12) |

| RXD to 1st RXC                       | t <sub>RD!</sub> | 940  | -    | ns           |

| Setup RXD to RXC                     | t <sub>RDS</sub> | 31   | -    | ns           |

| RXC to RX_PE Inactive (1MBps)        | t <sub>REH</sub> | 0    | 925  | ns (Note 13) |

| RXC to RX_PE Inactive (2MBps)        | t <sub>REH</sub> | 0    | 380  | ns (Note 13) |

| RXC to RX_PE Inactive (5.5MBps)      | t <sub>REH</sub> | 0    | 140  | ns (Note 13) |

| RXC to RX_PE Inactive (11MBps)       | t <sub>REH</sub> | 0    | 50   | ns (Note 13) |

| RX_PE inactive to MD_RDY Inactive    | t <sub>RD2</sub> | 5    | 30   | ns (Note 14) |

| Last Chip of SFD in to MD_RDY Active | t <sub>RD3</sub> | 2.77 | 2.86 | μs (Note 12) |

| RX Delay                             |                  | 2.77 | 2.86 | μs (Note 15) |

| RX_PE to CCA Valid                   | tCCA             | -    | 10   | μs (Note 16) |

| RX_PE to RSSI Valid                  | tCCA             | -    | 10   | μs (Note 16) |

#### NOTES:

- 12. RX\_PE must be inactive at least 3 MCLKs before going active to start a new CCA or acquisition.

- 13. MD\_RDY programmed to go active after SFD detect (measured from I<sub>IN</sub>, Q<sub>IN</sub>).

- 14. RX\_PE active to inactive delay to prevent next RXC.

- 15. Assumes RX\_PE inactive after last RXC.

- 16. MD\_RDY programmed to go active at MPDU start. Measured from first chip of first MPDU symbol at  $I_{IN}$ ,  $Q_{IN}$  to MD\_RDY active.

- 17. CCA and RSSI are measured once during the first 10μs interval following RX\_PE going active. RX\_PE must be pulsed to initiate a new measurement. RSSI may be read via serial port or from Test Bus.

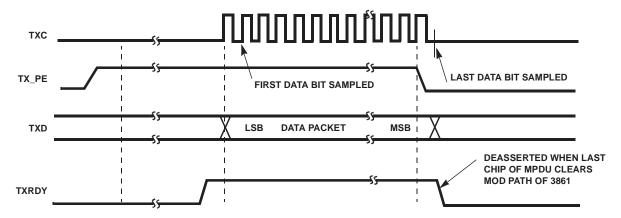

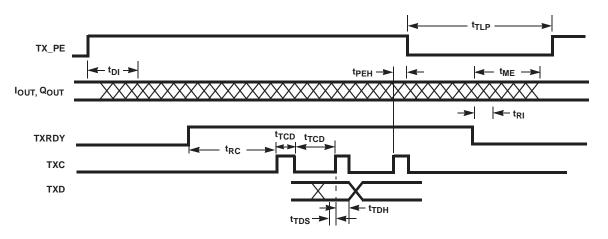

#### BBP Packet Transmission

There are 4 signals associated with the BBP Transmit Port: TX\_PE (Transmit Enable), TXRDY (Transmit Ready), TXD (Transmit Data), and TXCLK (Transmit Clock). These connect to the HFA3842 on PL0, PL7, TXD, and TXC, respectively.

State machines within the BBP control packet transmission and reception. In the case of a transmission, the MAC signals the BBP with the signal TX\_PE. The BBP forms the preamble and header and then signals the MAC to begin transferring data with the signal TXRDY. This sequence is illustrated in Figure 22 with detailed signal timing shown in Figure 23 and specified delays contained in Table 9. Note that if the MAC deactivates TX\_PE too early it may cut off modulation of the final symbol. For this reason, when TX\_PE is de-asserted the BBP will hold TXRDY active until the last symbol containing data is modulated. This is important for power sequencing and is discussed in more detail in that section.

For more detailed information concerning BBP packet transmission see the HFA3861 data sheet.

TABLE 9. BBP TRANSMIT PORT AC ELECTRICAL SPECIFICATIONS

| PARAMETER                                                    | SYMBOL           | MIN  | MAX | UNITS        |

|--------------------------------------------------------------|------------------|------|-----|--------------|

| TX_PE to I <sub>OUT</sub> /Q <sub>OUT</sub> (1st Valid Chip) | t <sub>D1</sub>  | 2.18 | 2.3 | μs (Note 17) |

| TX_PE Inactive Width                                         | t <sub>TLP</sub> | 2.22 | -   | μs (Note 18) |

| TXC Width Hi or Low                                          | t <sub>TCD</sub> | 40   | -   | ns           |

| TXRDY Active to 1st TX_CLK Hi                                | t <sub>RC</sub>  | 260  | -   | ns           |

| Setup TXD to TXC Hi                                          | t <sub>TDS</sub> | 30   | -   | ns           |

| Hold TXD to TXC Hi                                           | tTDH             | 0    | -   | ns           |

| TXC to TX_PE<br>Inactive (1MBps)                             | t <sub>PEH</sub> | 0    | 965 | ns (Note 20) |

| TXC to TX_PE<br>Inactive (2MBps)                             | tPEH             | 0    | 420 | ns (Note 20) |

| TXC to TX_PE<br>Inactive (5.5MBps)                           | tPEH             | 0    | 160 | ns (Note 20) |

| TXC to TX_PE<br>Inactive (11MBps)                            | t <sub>PEH</sub> | 0    | 65  | ns (Note 20) |

TABLE 9. BBP TRANSMIT PORT AC ELECTRICAL SPECIFICATIONS (Continued)

| PARAMETER                                     | SYMBOL          | MIN | MAX | UNITS        |

|-----------------------------------------------|-----------------|-----|-----|--------------|

| TXRDY Inactive To<br>Last Chip of MPDU<br>Out | t <sub>RI</sub> | -20 | 20  | ns           |

| TXD Modulation<br>Extension                   | t <sub>ME</sub> | 2   | -   | μs (Note 19) |

#### NOTES:

- I<sub>OUT</sub>/Q<sub>OUT</sub> are modulated before first valid chip of preamble is output to provide ramp up time for RF/IF circuits.

- TX\_PE must be inactive before going active to generate a new packet.

- 20.  $I_{OUT}/Q_{OUT}$  are modulated after last chip of valid data to provide ramp down time for RF/IF circuits.

- 21. Delay from TXC to inactive edge of TXPE to prevent next TXC. Because TXPE asynchronously stops TXC, TXPE going inactive within 40ns of TXC will cause TXC minimum hi time to be less than 40ns.

NOTE: Preamble/Header and Data is transmitted LSB first. TXD shown generated from rising edge of TXC.

FIGURE 23. BBP TRANSMIT PORT TIMING

FIGURE 24. BBP TRANSMIT PORT SIGNAL TIMING

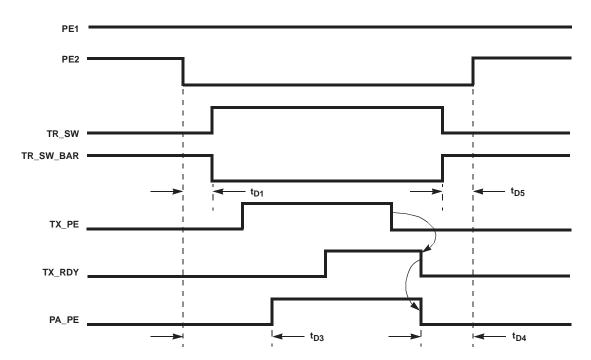

# **Power Sequencing**

The HFA3842 provides a number of firmware controlled port pins that are used for controlling the power sequencing and other functions in the front end components of the PHY.

Packet transmission requires precise control of the radio. Ideally, energy at the antenna ceases after the last symbol of information has been transmitted. Additionally, the transmit/receive switch must be controlled properly to protect the receiver. It's also important to apply appropriate modulation to the PA while it's active.

Signaling sequences for the beginning and end of normal transmissions are illustrated in Figure 25. Table 10 lists applicable delays.

A transmission begins with PE2 as shown in Figure 25. Next, the transmit/receive switch is configured for transmission via the differential pair TR\_SW and TR\_SW\_BAR. This is followed by TX\_PE which activates the transmit state machine in the BBP. Lastly, PA\_PE activates the PA. Delays for these signals related to the initiation of transmission are referenced to PE2.

Immediately after the final data bit has been clocked out of the HFA3842, TX\_PE is de-asserted. The HFA3842 then waits for TXRDY to go inactive, signaling that the BBP has modulated the final information-rich symbol. It then immediately de-asserts PA\_PE followed by placing the transmit/receive switch in the receive position and ending with PE2 going high. Delays for these signals related to the termination of transmission are referenced to the rising edge of PE2.

TABLE 10. TRANSMIT CONTROL TIMING SPECIFICATIONS

| PARAMETER        | SYMBOL          | DELAY | TOLERANCE | UNITS |

|------------------|-----------------|-------|-----------|-------|

| PE2 to TR Switch | t <sub>D1</sub> | 2     | ±0.1      | μs    |

| PE2 to PA_PE     | t <sub>D3</sub> | 3     | ±0.1      | μs    |

| PA_PE to PE2     | t <sub>D4</sub> | 3     | ±0.1      | μs    |

| TR Switch to PE2 | t <sub>D5</sub> | 2     | ±0.1      | μs    |

PE1 and PE2 encoding details are found in Table 11.

Note that during normal receive and transmit operation that PE1 is static and PE2 toggles for receive and transmit

FIGURE 25. TRANSMIT CONTROL SIGNAL SEQUENCING

**TABLE 11. POWER ENABLE STATES**

|                   | PE1 | PE2 | PLL_PE |

|-------------------|-----|-----|--------|

| Power Down State  | 0   | 0   | 1      |

| Receive State     | 1   | 1   | 1      |

| Transmit State    | 1   | 0   | 1      |

| PLL Active State  | 0   | 1   | 1      |

| PLL Disable State | Х   | Х   | 0      |

TABLE 11. POWER ENABLE STATES

|      | PE1 | PE2 | PLL_PE |

|------|-----|-----|--------|

| NOTE |     |     |        |

NOTE

22. PLL\_PE is controlled via the serial interface, and can be used to disable the internal synthesizer, the actual synthesizer control is an AND function of PLL\_PE, and a result of the OR function of PE1 and PE2. PE1 and PE2 will directly control the power enable functionality of the LO buffer(s)/phase shifter.

#### Master Clock

#### Prescaler

The HFA3842 contains a clock prescaler to provide flexibility in the choice of clock input frequencies. For 11Mb/s operation, the internal master clock, MCLK, must be between 11MHz and 16MHz. The clock generator itself requires an input from the prescaler that is twice the desired MCLK frequency. Thus the lowest oscillator frequency that can be used for an 11MHz MCLK is 22MHz. The prescaler can divide by integers and 1/2 steps (IE 1, 1.5, 2, 2.5). Another way to look at it is that the divisor ratio between the external clock source and the internal MCLK may be integers between 2 and 14.

Typically, the 44MHz baseband clock is used as the input, and the prescaler is set to divide by 2. Another useful configuration is to set the prescaler to divide by 1.5 (resulting in 44MHz ÷3) for an MCLK of 14.67MHz. Contact the factory for further details on setting the clock prescaler register in the HFA3842.

### Low-Frequency Crystal

The HFA3841 has an on-chip high-frequency oscillator that can be used to generate the internal master clock (MCLK). However, this on-chip high-frequency oscillator is almost never used because the MAC controller can accept the same clock signal as the PHY baseband processor (typically 44MHz), thereby avoiding the need for a separate, MAC-specific oscillator in close proximity to the PHY RF circuitry. Therefore, on the HFA3842 the high-frequency oscillator is replaced by a low-frequency oscillator. This low-frequency oscillator is intended for use with a 32.768KHz, tuning-fork type watch crystal to permit accurate timekeeping with very low power consumption during sleep state.

For the HFA3842 to achieve footprint compatibility with the HFA3841, pin 40 (OSCIN on the HFA3841) becomes CLKIN, which is the same function, when an external clock is provided to the MAC controller (as is recommended when using the HFA3842 with PRISM radios). The low-frequency crystal attaches between pin 39 (which is a 3.3V power input for the high-frequency oscillator on the HFA3841) and pin 41 (which is XTALO on the HFA3841, hence, unconnected if the on-chip oscillator is not being used). Refer to Figure 26 for additional details.

If a 32.768KHz crystal is connected, the resulting LF clock is supplied to an interval timer to permit measuring sleep intervals as well as providing a programmable wake-up time. In addition, the CHOICE-W clock generator can operate either from CLKIN or (very slowly) from the LF clock. Glitch-free switching between these two clock sources, under firmware control, is provided by two, non-architectural Strobe functions ("FAST" and "SLOW"). In addition, during hardware reset, the clock generator source is set to the LF clock if no edges are detected on CLKIN for two cycles of the LF clock (roughly 61 microseconds). This allows proper initialization

with omission of either clock source, since without the LF crystal attached there will not be cycles of the LF clock to activate the detection circuit. The ability to initialize the HFA3842 using the LF oscillator to generate MCLK allows the high-frequency (PHY) oscillator to be powered down during sleep state, which is not possible with the HFA3841. If this is done, firmware can turn on power to the PHY oscillator upon wakeup, and use the interval timer to measure the startup and stabilization period before switching to use CLKIN.

#### Clock Generator

The HFA3842 can operate with MCLK frequencies up to at least 25MHz and CLKIN frequencies of at least 50MHz. The MCLK prescaler generates MCLK (and QCLK) from the external clock provided at the CLKIN input, or from the output of the LF oscillator. The MCLK prescaler divides the selected input clock by any integer value between 2 and 16, inclusive.

- When using a 44MHz CLKIN, as is typical for 802.11 or 802.11b controllers with a PC Card Host Interface, common divisors are 3 (14.67MHz), 4 (11MHz), or 5 (8.8MHz)

- It is anticipated that a controller for the 802.11a, mandatory data rates will need to operate at an MCLK frequency of a least 24MHz, hence a CLKIN frequency of at least 48MHz.

The MCLK prescaler is set to divide by 16 at hardware reset to allow initialization firmware to be executed from slow memory devices at any CLKIN frequency. The MCLK prescaler generates glitch free output when the divisor is changed. This allows firmware to change the MCLK frequency during operation, which is especially useful to selectively reduce operating speed, thereby conserving power, when full speed processing is not required.

FIGURE 26. 32.768kHz CRYSTAL

# Power On Reset Configuration

The HFA3842 supports both hardware and software reset functions. Hardware reset is caused by assertion of the RESET input. When using the PC Card host interface, software reset is caused by setting the Sreset bit in the Configuration Option Register (COR[71]. Hardware and software reset leave the HFA3842 in the same state except in the case of soft reset from the PC Card Host Interface, in which case the COR and HCR registers come into play.

The MD[15:8] pin values are sampled during HRESET or SRESET. These pins have internal 50K pull-down resistors. External pull-up resistors (typically  $10k\Omega$ ) are used for bits that should be read as high at reset.

Table 12 summarizes the effect per pin. Table 13 provides the MD15 and MD14 bit values required by the HFA3842 to allow usage of Serial EEPROM Devices.

TABLE 12. INITIALIZATION STRAPPING OPTIONS ON MBUS DATA PINS