# 5-TAP, HCMOS-INTERFACED FIXED DELAY LINE (SERIES DDU4C)

#### **FEATURES**

- · Five equally spaced outputs

- Fits standard 8-pin DIP socket

- Low profile

- Auto-insertable

- Input & outputs fully CMOS interfaced & buffered

- 10 T<sup>2</sup>L fan-out capability

#### **PACKAGES**

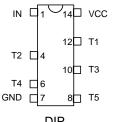

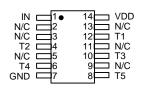

DDU4C-xx Comm. DDU4C-xxM Military

SMD

DDU4C-xxA2 Comm.

DDU4C-xxB2 Comm.

DDU4C-xxMC2 Military

#### **FUNCTIONAL DESCRIPTION**

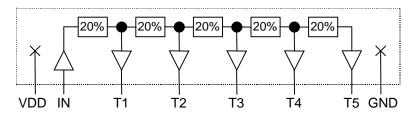

The DDU4C-series device is a 5-tap digitally buffered delay line. The signal input (IN) is reproduced at the outputs (T1-T5), shifted in time by an amount determined by the device dash number (See Table). The total delay of the line is measured from IN to T5. The nominal tap-to-tap delay increment is given by one-fifth of the total delay.

## **PIN DESCRIPTIONS**

IN Signal Input T1-T5 Tap Outputs VDD +5 Volts GND Ground

#### SERIES SPECIFICATIONS

• Minimum input pulse width: 20% of total delay

Output rise time: 8ns typical

Supply voltage: 5VDC ± 5%

Supply current: I<sub>CCL</sub> = 40μa typical

I<sub>CCH</sub> = 10ma typical

Operating temperature: 0° to 70° C

Temp. coefficient of total delay: 300 PPM/°C

#### DASH NUMBER SPECIFICATIONS

| Part       | Total          | Delay Per        |  |  |

|------------|----------------|------------------|--|--|

| Number     | Delay (ns)     | Tap (ns)         |  |  |

| DDU4C-5050 | $50 \pm 2.5$   | $10.0 \pm 3.0$   |  |  |

| DDU4C-5060 | $60 \pm 3.0$   | $12.0 \pm 3.0$   |  |  |

| DDU4C-5075 | $75 \pm 4.0$   | $15.0 \pm 3.0$   |  |  |

| DDU4C-5100 | $100 \pm 5.0$  | $20.0 \pm 3.0$   |  |  |

| DDU4C-5125 | $125 \pm 6.5$  | $25.0 \pm 3.0$   |  |  |

| DDU4C-5150 | $150 \pm 7.5$  | $30.0 \pm 3.0$   |  |  |

| DDU4C-5200 | 200 ± 10.0     | $40.0 \pm 4.0$   |  |  |

| DDU4C-5250 | $250 \pm 12.5$ | $50.0 \pm 5.0$   |  |  |

| DDU4C-5300 | $300 \pm 15.0$ | $60.0 \pm 6.0$   |  |  |

| DDU4C-5400 | $400 \pm 20.0$ | $80.0 \pm 8.0$   |  |  |

| DDU4C-5500 | $500 \pm 25.0$ | $100.0 \pm 10.0$ |  |  |

NOTE: Any dash number between 5050 and 5500

<del>net shewn is alse available</del>

**DDU4C Functional diagram**

©1997 Data Delay Devices

# **APPLICATION NOTES**

#### HIGH FREQUENCY RESPONSE

The DDU4C tolerances are guaranteed for input pulse widths and periods greater than those specified in the test conditions. Although the device will function properly for pulse widths as small as 20% of the total delay and periods as small as 40% of the total delay (for a symmetric input), the delays may deviate from their values at low frequency. However, for a given input condition, the deviation will be repeatable from pulse to pulse. Contact technical support at Data

Delay Devices if your application requires device testing at a specific input condition.

#### POWER SUPPLY BYPASSING

The DDU4C relies on a stable power supply to produce repeatable delays within the stated tolerances. A 0.1uf capacitor from VDD to GND, located as close as possible to the VDD pin, is recommended. A wide VDD trace and a clean ground plane should be used.

## **DEVICE SPECIFICATIONS**

**TABLE 1: ABSOLUTE MAXIMUM RATINGS**

| PARAMETER           | SYMBOL     | MIN  | MAX                  | UNITS | NOTES  |

|---------------------|------------|------|----------------------|-------|--------|

| DC Supply Voltage   | $V_{DD}$   | -0.3 | 7.0                  | V     |        |

| Input Pin Voltage   | $V_{IN}$   | -0.3 | V <sub>DD</sub> +0.3 | V     |        |

| Storage Temperature | $T_{STRG}$ | -55  | 150                  | С     |        |

| Lead Temperature    | $T_LEAD$   |      | 300                  | С     | 10 sec |

#### TABLE 2: DC ELECTRICAL CHARACTERISTICS

(0C to 70C, 4.75V to 5.25V)

| PARAMETER                 | SYMBOL          | MIN  | TYP  | MAX  | UNITS | NOTES                        |

|---------------------------|-----------------|------|------|------|-------|------------------------------|

| High Level Output Voltage | V <sub>OH</sub> | 3.98 | 4.4  |      | V     | $V_{DD} = 5.0, I_{OH} = MAX$ |

|                           |                 |      |      |      |       | $V_{IH} = MIN, V_{IL} = MAX$ |

| Low Level Output Voltage  | $V_{OL}$        |      | 0.15 | 0.26 | V     | $V_{DD} = 5.0, I_{OL} = MAX$ |

|                           |                 |      |      |      |       | $V_{IH} = MIN, V_{IL} = MAX$ |

| High Level Output Current | I <sub>OH</sub> |      |      | -4.0 | mA    |                              |

| Low Level Output Current  | I <sub>OL</sub> |      |      | 4.0  | mA    |                              |

| High Level Input Voltage  | $V_{IH}$        | 3.15 |      |      | V     |                              |

| Low Level Input Voltage   | $V_{IL}$        |      |      | 1.35 | V     |                              |

| Input Current             | I <sub>IH</sub> |      |      | 0.10 | μΑ    | $V_{DD} = 5.0$               |

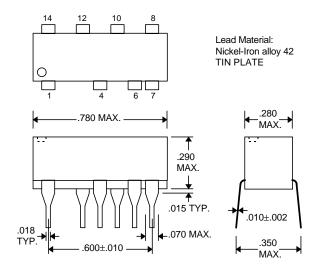

# **PACKAGE DIMENSIONS**

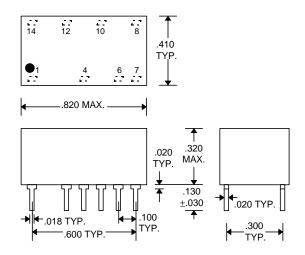

DDU4C-xx (Commercial DIP)

DDU4C-xxM (Military DIP)

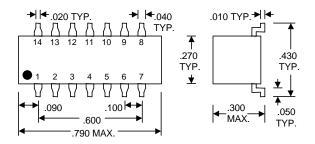

DDU4C-xxA2 (Commercial Gull-Wing)

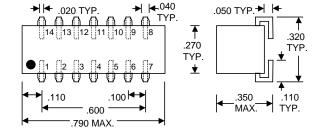

DDU4C-xxB2 (Commercial J-Lead)

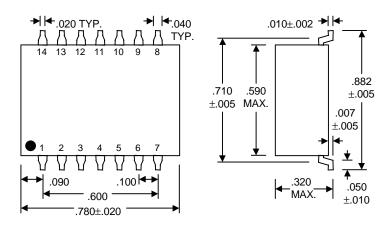

DDU4C-xxMC2 (Military SMD)

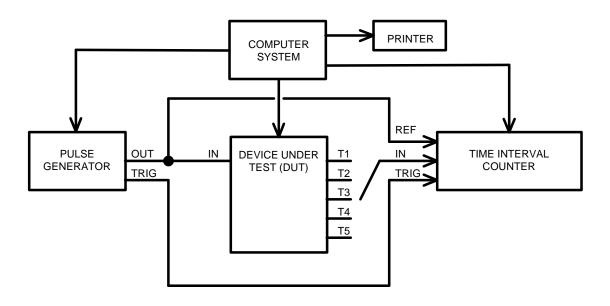

# **DELAY LINE AUTOMATED TESTING**

#### **TEST CONDITIONS**

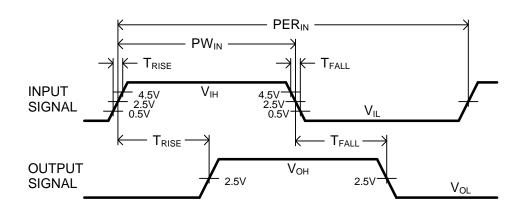

INPUT: OUTPUT:

**Ambient Temperature:**  $25^{\circ}\text{C} \pm 3^{\circ}\text{C}$  **Load:** 1 FAST-TTL Gate

Supply Voltage (VDD):  $5.0V \pm 0.1V$  C<sub>load</sub>:  $5pf \pm 10\%$  Input Pulse: High =  $5.0V \pm 0.1V$  Threshold: 2.5V (Rising & Falling)

Low =  $0.0V \pm 0.1V$

Source Impedance:  $50\Omega$  Max.

**Rise/Fall Time:** 5.0 ns Max. (measured

between 0.5V and 4.5V)

Pulse Width:  $PW_{IN} = 1.5 \times Total Delay$ Period:  $PER_{IN} = 10 \times Total Delay$

**NOTE:** The above conditions are for test only and do not in any way restrict the operation of the device.

**Test Setup**

**Timing Diagram For Testing**