SCAS323 - JULY 1990 - REVISED MARCH 1994

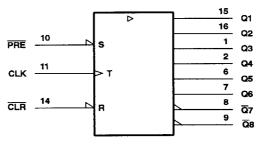

| Replaces SN74AS303     Maximum Output Skew Between Same     Phase Outputs of 1 ns     Maximum Pulse Skew of 1 ns              | D OR N PACKAGE (TOP VIEW)  Q3 1 16 Q2  |

|-------------------------------------------------------------------------------------------------------------------------------|----------------------------------------|

| TTL-Compatible Inputs and Outputs                                                                                             | Q4 [] 2 15 [] Q1<br>GND [] 3 14 [] CLR |

| Center-Pin V <sub>CC</sub> and GND Configurations     Minimize High-Speed Switching Noise     Paskers Ontions Include Pleatie | GND   4                                |

| <ul> <li>Package Options Include Plastic<br/>Small-Outline Package (D) and Standard<br/>Plastic 300-mil DIPs (N)</li> </ul>   | Q6 [ 7 10 ] PRE<br>Q7 [ 8 9 ] Q8       |

## description

The CDC303 contains eight flip-flops designed to have low skew between outputs. The eight outputs (six in-phase with CLK and two out-of-phase) toggle on successive CLK pulses. Preset ( $\overline{PRE}$ ) and clear ( $\overline{CLR}$ ) inputs are provided to set the Q and  $\overline{Q}$  outputs high or low independent of the clock (CLK) input.

The CDC303 has output and pulse-skew parameters  $t_{sk(o)}$  and  $t_{sk(p)}$  to ensure performance as a clock driver when a divide-by-two function is required.

The CDC303 is characterized for operation from 0°C to 70°C.

#### **FUNCTION TABLE**

| INPUTS |     |          | OUTPUTS          |                        |  |

|--------|-----|----------|------------------|------------------------|--|

| CLR    | PRE | CLK      | Q1-Q6            | <u>Q</u> 7− <u>Q</u> 8 |  |

| L      | Н   | X        | L                | Н                      |  |

| н      | L   | ×        | н                | L                      |  |

| L      | L   | ×        | L†               | L†                     |  |

| Н      | н   | <b>†</b> | $\overline{Q}_0$ | $Q_0$                  |  |

| н      | н   | L        | Qo               | $\overline{Q}_0$       |  |

† This configuration will not persist when PRE or CLR returns to its inactive (high) level.

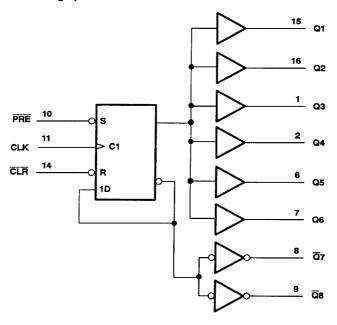

## logic symbol‡

<sup>‡</sup> This symbol is in accordance with ANSI/IEEE Std 91-1984 and IEC Publication 617-12.

PRODUCTION DATA information is current as of publication date. Products conform to specifications per the terms of Texas Instruments standard warranty. Production processing does not necessarily include teating of all parameters.

Copyright © 1994, Texas Instruments Incorporated

2-23

#### logic diagram (positive logic)

# absolute maximum ratings over operating free-air temperature range (unless otherwise noted)†

| Supply voltage, V <sub>CC</sub>        |

|----------------------------------------|

| input voltage, V <sub>I</sub>          |

| Operating free-air temperature range   |

| Storage temperature range65°C to 150°C |

<sup>†</sup> Stresses beyond those listed under "absolute maximum ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated under "recommended operating conditions" is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

#### recommended operating conditions

|        |                                | MIN | NOM | MAX | UNIT |

|--------|--------------------------------|-----|-----|-----|------|

| Vcc    | Supply voltage                 | 4.5 | 5   | 5.5 | V    |

| VIH    | High-level input voltage       | 2   |     |     | V    |

| VIL    | Low-level input voltage        |     |     | 0.8 | V    |

| ЮН     | High-level output current      |     |     | -24 | mA   |

| loL    | Low-level output current       |     |     | 48  | mA   |

| fclock | Input clock frequency          |     |     | 80  | MHz  |

| TA     | Operating free-air temperature | 0   |     | 70  | °C   |

2-24

8961723 0098455 T31 🖿

SCAS323 - JULY 1990 - REVISED MARCH 1994

# electrical characteristics over recommended operating free-air temperature range (unless otherwise noted)

| PARAMETER      | TEST CONDITIONS                   |                          | MIN                | TYP | MAX  | UNIT |

|----------------|-----------------------------------|--------------------------|--------------------|-----|------|------|

| VIK            | V <sub>CC</sub> = 4.5 V,          | l <sub>l</sub> = -18 mA  |                    |     | -1.2 | ٧    |

|                | V <sub>CC</sub> = 4.5 V to 5.5 V, | l <sub>OH</sub> = −2 mA  | V <sub>CC</sub> -2 |     |      | ٧    |

| VOH            | V <sub>CC</sub> = 4.5 V,          | I <sub>OH</sub> = -24 mA | 2                  | 2.8 |      | ٧    |

| VoL            | V <sub>CC</sub> = 4.5 V,          | I <sub>OL</sub> = 48 mA  |                    | 0.3 | 0.5  | >    |

| l <sub>l</sub> | V <sub>CC</sub> = 5.5 V,          | V <sub>I</sub> = 7 V     |                    |     | 0.1  | mA   |

| ήн             | V <sub>CC</sub> = 5.5 V,          | V <sub>I</sub> = 2.7 V   |                    |     | 20   | μΑ   |

| կլ             | V <sub>CC</sub> = 5.5 V,          | V <sub>i</sub> = 0.4 V   |                    |     | -0.5 | mA   |

| lo‡            | V <sub>CC</sub> = 5.5 V,          | V <sub>O</sub> = 2.25 V  | -50                |     | -150 | mA   |

| Icc            | V <sub>CC</sub> = 5.5 V,          | See Note 1               |                    | 40  | 70   | mA   |

<sup>†</sup> All typical values are at V<sub>CC</sub> = 5 V, T<sub>A</sub> = 25°C.

#### timing requirements

|                 |                               |                     | MIN | MAX | UNIT |

|-----------------|-------------------------------|---------------------|-----|-----|------|

| fclock          | Clock frequency               |                     | 0   | 80  | MHz  |

|                 | t <sub>w</sub> Pulse duration | CLR or PRE low      | 5   |     |      |

| tw              |                               | CLK high            | 4   |     | ns   |

|                 | CLK low                       | 6                   |     | i   |      |

| t <sub>su</sub> | Setup time before CLK†        | CLR or PRE inactive | 6   |     | ns   |

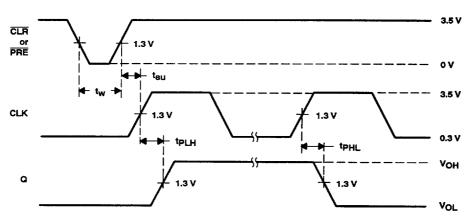

## switching characteristics over recommended operating free-air temperature range (see Figure 1)

| PARAMETER          | FROM<br>(INPUT) | TO<br>(OUTPUT)             | TEST CONDITIONS                                            | MIN | MAX | UNIT    |

|--------------------|-----------------|----------------------------|------------------------------------------------------------|-----|-----|---------|

| f <sub>max</sub> § |                 |                            |                                                            | 80  |     | MHz     |

| t <sub>PLH</sub>   | CLK             | Q, Q                       | R <sub>1</sub> = 500 Ω, C <sub>1</sub> = 50 pF             | 2   | 9   | –l ns l |

| <sup>t</sup> PHL   | OLK             | u, u                       | THE = 300 sz, OE = 30 pr                                   | 2   | 9   |         |

| t <sub>PLH</sub>   | PRE or CLR      | Q, <del>Q</del>            | R <sub>L</sub> = 500 Ω, C <sub>L</sub> = 50 pF             | 3   | 12  |         |

| <sup>t</sup> PHL   | PRE OF CLR      | <b>u</b> , u               | 71, 2 3 3 3 4 5 2 3 5 pr                                   | 3   | 12  |         |

|                    |                 | q                          |                                                            |     | 1   | ns      |

| t <sub>sk(o)</sub> | CLK             | ā                          | $R_L = 500 \Omega$ , $C_L = 10 pF to 30 pF$ , See Figure 2 |     | 1   |         |

|                    |                 | Q, $\overline{\mathbf{Q}}$ | - 000 Figuro 2                                             |     | 2   |         |

| <sup>t</sup> sk(p) | CLK             | a, <del>a</del>            | $R_L = 500 \Omega$ , $C_L = 10 pF to 30 pF$                |     | 1   | ns      |

| t <sub>r</sub>     |                 |                            |                                                            |     | 4.5 | ns      |

| tf                 |                 |                            |                                                            |     | 3.5 | ns      |

<sup>§</sup> f<sub>max</sub> minimum values are at C<sub>L</sub> = 0 to 30 pF.

<sup>‡</sup> The output conditions have been chosen to produce a current that closely approximates one half of the true short-circuit output current, IOS. NOTE 1: ICC is measured with CLK and PRE grounded, then with CLK and CLR grounded.

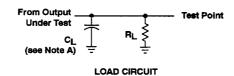

#### PARAMETER MEASUREMENT INFORMATION

NOTES: A. C<sub>L</sub> includes probe and jig capacitance.

B. Input pulses are supplied by generators having the following characteristics: PRR  $\leq$  10 MHz,  $t_f = 2.5$  ns,  $t_f = 2.5$  ns.

Figure 1. Load Circuit and Voltage Waveforms

2-26

8961723 0098457 804 🖿

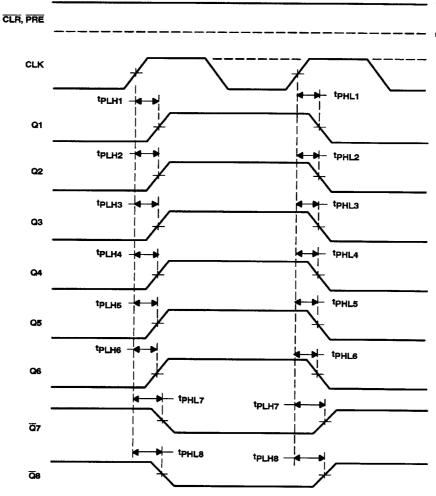

NOTES: A. t<sub>sk(o)</sub>, CLK to Q, is calculated as the greater of:

- The difference between the fastest and slowest of tpLHn (n = 1, 2, 3, 4, 5, 6)

- The difference between the fastest and slowest of tpHLn (n = 1, 2, 3, 4, 5, 6)

- B. t<sub>sk(o)</sub>, CLK to Q, is calculated as the greater of: | tpLH7 tpLH8 | and | tpHL7 tpHL8 |.

- C. tsk(o), CLK to Q and Q, is calculated as the greater of:

- The difference between the fastest and slowest of tpLHn (n = 1, 2, 3, 4, 5, 6), tpHL7, and tpHL8

- The difference between the fastest and slowest of tphln (n = 1, 2, 3, 4, 5, 6), tplh7, and tplh8

- D.  $t_{sk(p)}$  is calculated as the greater of  $|t_{PLHn} t_{PHLn}|$  ( n = 1, 2, 3, ..., 8 ).

Figure 2. Waveforms for Calculation of tsk(o)