## Am29C827A/Am29C828A

## Advanced Micro Devices

## **High-Performance CMOS Bus Buffers**

#### DISTINCTIVE CHARACTERISTICS

- High-speed CMOS buffers and inverters

D-Y delay = 4 ns typical

- Low standby power

- **■** JEDEC FCT-compatible specs

- Very high output drive

lo: = 48 mA Commercial, 32 mA Military

- Extra-wide (10-bit) data paths

- 200-mV typical hysteresis on data input ports

- Minimal speed degradation with multiple outputs switching

- Proprietary edge-rate controlled outputs dramatically reduce undershoots, overshoots, and ground bounce

- Power-up/down disable circuit provides for glitch-free power supply sequencing

- Ideal for driving 1Mblt x 1 and 1Mblt x 4 DRAM address inputs

- Can be powered off while in 3-state, ideal for card edge interface applications

- **■** JEDEC FCT-compatible specs

#### GENERAL DESCRIPTION

The Am29C827A and Am29C828A CMOS Bus Buffers provide high-performance bus interface buffering for wide address/data paths or buses carrying parity. Both devices feature 10-bit wide data paths and NORed output enables for maximum control flexibility. The Am29C827A has non-inverting outputs, while the Am29C828A has inverting outputs. Each device has data inputs with 200-mV typical input hysteresis to provide improved noise immunity. The Am29C827A and Am29C828A are produced with AMD's exclusive CS11SA CMOS process, and feature typical propagation delays of 4 ns, as well as an output current drive of 48 mA.

The 29C827A and Am29C828A incorporate AMD's proprietary edge-controlled outputs in order to minimize simultaneous switching noise (ground bounce). By con-

trolling the output transient currents, ground bounce and output ringing have been greatly reduced. A modified AMD output provides a stable, usable voltage level in less time than a non-controlled output.

Additionally, speed degradation due to increasing number of outputs switching is reduced. Together, these benefits or edge-rate control result in significant increase in system performance despite a minor increase in device propagation delay.\*

A unique I/O circuitry provides for high-impedance outputs during power-off and power-up/down sequencing, thus providing glitch-free operation for card-edge and other active bus applications.

The Am29C827A and Am29C828A are available in the standard package options: DIPs and SOICs.

\*For more details refer to a Minimization of Ground Bounce Through Output Edge-Rate Control Application Note (See Chapter 3).

Publication# 11228 Rev. D Amendment/0 Issue Date: August 1991

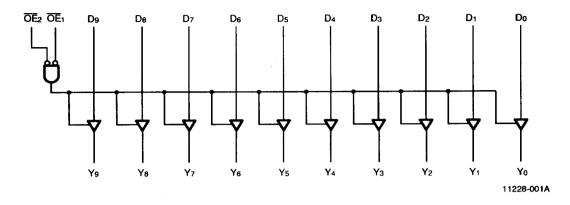

## BLOCK DIAGRAMS Am29C827A (Noninverting)

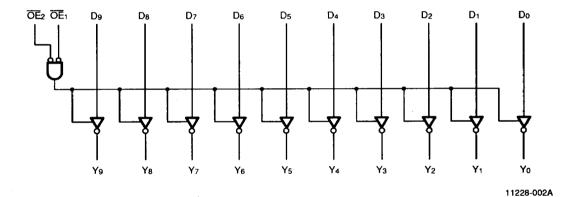

## Am29C828A (Inverting)

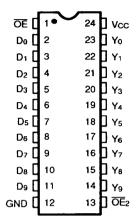

## CONNECTION DIAGRAMS (Top View)

DIPs\*

11228-003A

<sup>\*</sup>Also available in Small Outline package; pinout identical to DIPs.

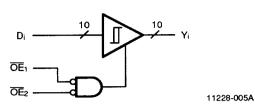

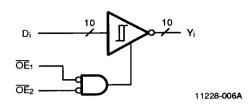

### **LOGIC SYMBOLS**

### Am29C827A

#### Am29C828A

## **FUNCTION TABLES**

### Am29C827A

| Inputs |            |   | Outputs |             |  |  |  |

|--------|------------|---|---------|-------------|--|--|--|

| ŌE₁    | OE₁ OE₂ Di |   | Yi      | Function    |  |  |  |

| L      | L          | Н | Н       | Transparent |  |  |  |

| L      | L          | L | L       | Transparent |  |  |  |

| Х      | Н          | Х | Z       | Hi-Z        |  |  |  |

| Н      | Х          | Х | Z       | Hi-Ż        |  |  |  |

## Am29C828A

| Inputs |            | Outputs |    |             |  |  |

|--------|------------|---------|----|-------------|--|--|

| ŌĒ1    | ŌĒ₁ ŌĒ₂ Di |         | Yi | Function    |  |  |

| L      | L          | Н       | L  | Transparent |  |  |

| L      | L          | L       | H  | Transparent |  |  |

| X      | Н          | Х       | Z  | Hi-Z        |  |  |

| H      | Х          | Х       | Z  | Hi-Z        |  |  |

H = HIGH

L = LOW

X = Don't Care Z = Hi-Z

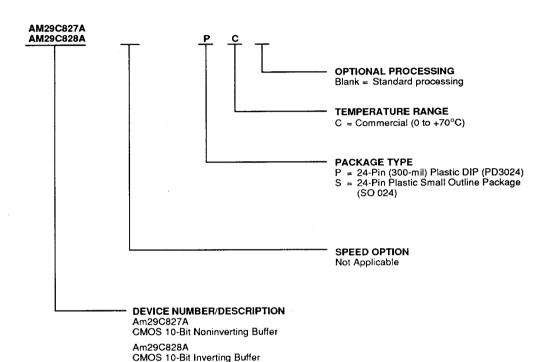

## ORDERING INFORMATION Standard Products

AMD standard products are available in several packages and operating ranges. The order number (Valid Combination) is formed by a combination of:

Device Number

Speed Option (if applicable)

Package Type

Temperature Range

Optional Processing

| Valid Combinations |        |  |  |  |  |

|--------------------|--------|--|--|--|--|

| AM29C827A          | 00.00  |  |  |  |  |

| AM29C828A          | PC, SC |  |  |  |  |

#### **Valid Combinations**

Valid Combinations list configurations planned to be supported in volume for this device. Consult the local AMD sales office to confirm availability of specific valid combinations or to check on newly released combinations, and to obtain additional data on AMD's standard military grade products.

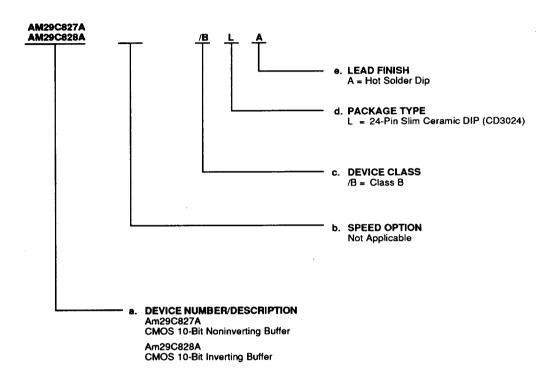

## MILITARY ORDERING INFORMATION **APL Products**

AMD products for Aerospace and Defense applications are available in several packages and operating ranges. APL (Approved Products List) products are fully compliant with MIL-STD-883C requirements. The order number (Valid Combination) is formed by a combination of: **Device Number**

- Speed Option (if applicable) b.

- Device Class

- Package Type Lead Finish

| Valid Combinations |              |  |  |  |  |

|--------------------|--------------|--|--|--|--|

| AM29C827A          | <b>6</b> 1 A |  |  |  |  |

| AM29C828A          | /BLA         |  |  |  |  |

#### Valid Combinations

Valid Combinations list configurations planned to be supported in volume for this device. Consult the local AMD sales office to confirm availability of specific valid combinations, or to check on newly released combinations.

#### **Group A Tests**

Group A tests consist of Subgroups 1, 2, 3, 7, 8, 9, 10, 11.

### PIN DESCRIPTION

<del>OE</del>i

### Output Enables (Input, Active LOW)

When the  $\overline{OE}_1$  and  $\overline{OE}_2$  are both LOW, the outputs are enabled. When either one or both are HIGH, the outputs are in the Hi-Z state.

D<sub>i</sub> Data Inputs (Input)

Di are the 10-bit data inputs.

Y<sub>i</sub> Data Outputs (Output)

Yi are the 10-bit data outputs.

#### **ABSOLUTE MAXIMUM RATINGS**

Storage Temperature -65 to +150°C Supply Voltage to Ground Potential Continuous -0.5 V to +7.0 V

DC Output Voltage -0.5 V to +6.0 V

DC Input Voltage -0.5 V to +6.0 V

DC Output Diode Current:

Into Output +50 mA

Out of Output -50 mA

DC Input Diode Current:

Into Input +20 mA

Out of Input -20 mA

DC Output Current per Pin:

Into Output +100 mA

Out of Output -100 mA

**Total DC Ground Current**

(n x lot + m x lcct) mA (Note 1)

Total DC Vcc Current

(n x loh + m x lcct) mA (Note 1)

#### Note:

1. n = number of outputs, m = number of inputs.

Stresses above those listed under Absolute Maximum Ratings may cause permanent device failure. Functionality at or above these limits is not implied. Exposure to absolute maximum ratings for extended periods may affect device reliability.

#### **OPERATING RANGES**

Commercial (C) Devices

Temperature (T<sub>A</sub>) 0 to +70°C Supply Voltage (Vcc) +4.5 V to +5.5 V

Military (M) Devices

Temperature (T<sub>A</sub>) -55 to +125°C Supply Voltage (Vcc) +4.5 V to +5.5 V

Operating ranges define those limits between which the functionality of the device is guaranteed.

## DC CHARACTERISTICS over operating ranges unless otherwise specified (for APL Products, Group A, Subgroups 1, 2, 3 are tested unless otherwise noted)

| Parameter<br>Symbol | Parameter Description        | Test Conditions                                                  |                                |              | Min. | Max.       | Unit        |

|---------------------|------------------------------|------------------------------------------------------------------|--------------------------------|--------------|------|------------|-------------|

| Vон                 | Output HIGH Voltage          | Vcc = 4.5 V<br>Vin = Vin or Vil                                  | I <sub>OH</sub> = -15 mA       |              | 2.4  |            | >           |

| Vol                 | Output LOW Voltage           | Vcc = 4.5 V                                                      | MIL lot = 3                    | 2 mA         |      | 0.5        | >           |

|                     |                              | VIN = VIHOT VIL                                                  | COM'L lou                      | = 48 mA      |      | 0.5        | ٧           |

| ViH                 | Input HIGH Voltage           | Guaranteed Input Logical HIGH<br>Voltage for All Inputs (Note 1) |                                |              | 2.0  |            | ٧           |

| ViL                 | Input LOW Voltage            | Guaranteed Input Logical LOW<br>Voltage for All Inputs (Note 1)  |                                |              |      | 0.8        | ٧           |

| Vı                  | Input Clamp Voltage          | Vcc = 4.5 V, I <sub>IN</sub> = -18 mA                            |                                |              |      | -1.2       | >           |

| lıL                 | Input LOW Current            | Vcc = 5.5 V, V <sub>IN</sub> = GND                               |                                |              |      | <b>-</b> 5 | μΑ          |

| lін                 | Input HIGH Current           | Vcc = 5.5 V, ViN = 5.5 V                                         |                                |              |      | 5          | μΑ          |

| lozн                | Output Off-State Current     | Vcc = 5.5 V, Vo = 5.5 V                                          |                                |              |      | +10        | μΑ          |

| lozL                | (High Impedance)             | Vcc = 5.5 V, Vo = or GND                                         |                                |              |      | -10        | μΑ          |

| Isc                 | Output Short-Circuit Current | Vcc = 5.5 V, Vc                                                  | Vcc = 5.5 V, Vo = 0 V (Note 2) |              |      |            | mA          |

| lcco                |                              |                                                                  | VIN = VCC or                   | MIL          |      | 1.5        | m A         |

|                     | Statio Summly Comment        | Vcc = 5.5 V                                                      | GND                            | COM'L        |      | 1.2        | mA          |

| Ісст                | Static Supply Current        | Outputs Open                                                     | VIN = 3.4 V                    | Data Input   |      | 1.5        | mA/         |

|                     |                              |                                                                  |                                | ŌĒ₁, ŌĒ₂     |      | 3.0        | Bit         |

| Iccot               | Dynamic Supply Current       | Vcc = 5.5 V (Note 3) Outputs                                     |                                | Outputs Open |      | 275        | μΑ/<br>MHz/ |

|                     | ·                            |                                                                  |                                |              |      | 400        | Bit         |

#### Notes:

- 1. Input thresholds are tested in combination with other DC parameters or by correlation.

- 2. Not more than one output shorted at a time. Duration should not exceed 100 milliseconds.

- 3. Measured at a frequency ≤ 10 MHz with 50% duty cycle.

- † Not included in Group A tests.

# SWITCHING CHARACTERISTICS for light capacitive loading over operating ranges unless otherwise specified (for APL Products, Group A, Subgroups 9, 10, 11 are tested unless otherwise noted)

| · · · · · · · · · · · · · · · · · · · |                                   |                                                                   | Commercial |      | Military |      |      |

|---------------------------------------|-----------------------------------|-------------------------------------------------------------------|------------|------|----------|------|------|

| Symbol                                | Parameter Description             | Test Conditions*                                                  | Min.       | Max. | Min.     | Max. | Unit |

| tplH                                  | Data (Di) to Output (Yi)          |                                                                   | · 1.0      | 7.5  | 1.0      | 8.5  | ns   |

| tphL                                  | Am29C827A (Noninverting) (Note 1) |                                                                   | 1.0        | 7.5  | 1.0      | 8.5  | ns   |

| t <sub>PLH</sub>                      | Data (Di) to Output (Yi)          | 0 50 5                                                            | 1.0        | 7.5  | 0.5      | 8.5  | ns   |

| tphL                                  | Am29C828A (Inverting ) (Note 1)   | $C_L = 50 \text{ pF}$<br>$R_1 = 500 \Omega$<br>$R_2 = 500 \Omega$ | 1.0        | 7.5  | 0.5      | 8.5  | ns   |

| tzн                                   | Output Enable Time OE to Yi       |                                                                   | 1.0        | 9    | 1.0      | 11   | ns   |

| tzL                                   |                                   | ]                                                                 | 3.0        | 12   | 3.0      | 14   | ns   |

| tHZ                                   | Control Disable Time OF to V      | ]                                                                 | 2.0        | 8    | 2.0      | 9    | ns   |

| tız                                   | Output Disable Time OE to Yi      |                                                                   | 3.0        | 8    | 2.0      | 9    | ns   |

## SWITCHING CHARACTERISTICS for heavy capacitive loading over operating ranges unless otherwise specified

|              |                                                                                                                        |                                                              | Commercial |      | Military |      |      |

|--------------|------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------|------------|------|----------|------|------|

| Symbol       | Parameter Description (Note 2)                                                                                         | Test Conditions*                                             | Min.       | Max. | Min.     | Max. | Unit |

| tplH         | Data (Di) to Output (Yi)                                                                                               |                                                              | 1.0        | 15.5 | 1.0      | 17.0 | ns   |

| tphL         | Am29C827A (Noninverting) (Note 1)  Data (D <sub>i</sub> ) to Output (Y <sub>i</sub> )  Am29C828A (Inverting ) (Note 1) | $C_L = 300 \text{ pF}$ $R_1 = 500 \Omega$ $R_2 = 500 \Omega$ | 1.0        | 15.5 | 1.0      | 17.0 | ns   |

| tрцн         |                                                                                                                        |                                                              | 1.0        | 13.5 | 0.5      | 15.0 | ns   |

| <b>t</b> PHL |                                                                                                                        |                                                              | 1.0        | 14   | 0.5      | 15.0 | ns   |

| tzн          | - · · · - · · · · · · · · · · · · · · ·                                                                                |                                                              | 1.0        | 13.5 | 1.0      | 15.0 | ns   |

| tzL          | Output Enable Time OE to Y                                                                                             |                                                              | 3.0        | 17   | 3.0      | 18.0 | ns   |

| tHZ          | O to A Bit able Time OF to V                                                                                           | C <sub>L</sub> = 5 pF                                        | 2.0        | 7    | 2.0      | 8    | ns   |

| tLZ          | Output Disable Time OE to Yi                                                                                           | $R_1 = 500 \Omega$ $R_2 = 500 \Omega$                        | 3.0        | 7    | 2.0      | 8    | ns   |

<sup>\*</sup>See Test Circuit and Waveforms listed in Chapter 2.

#### Notes:

For more details refer to a Minimization of Ground Bounce Through Output Edge-Rate Control Application Note (See Chapter 3).

<sup>2.</sup> These parameters are guaranteed by characterization but not production tested.