November 2012

# FSA801 — USB2.0 High-Speed (480 Mbps), UART, and Audio Switch with Negative Signal Capability

### **Features**

- 3:1 Switch Handles:

- Audio Headsets

- UART

- Up to Two High- and Low-Speed USB Data

- USB Charger Detection and Indication, Compliant with USB Battery Charging Specification, Rev 1.1

- Supports Data Contact Detect (DCD)

- Negative-Swing-Capable Audio Channel

- Built-in Termination Resistors for Audio Pop Reduction

- Simple Switch Control Using Three Select Pins

- 28 V Over-Voltage Tolerance on V<sub>BUS</sub>

# **Applications**

Cell Phones, MP3 Players, PDAs

### **Description**

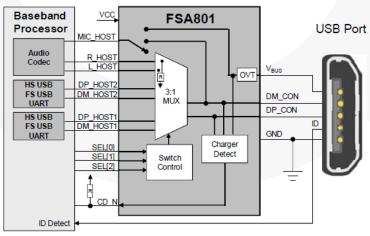

The FSA801 is a 3:1 USB accessory switch that enables USB data, stereo and mono audio, microphone, and UART data to share a common connector port. Two ports are designed for high-speed USB 2.0 signaling, while also capable of full-speed USB and UART communication. The architecture allows audio signals to swing below ground so a common USB and headphone jack can be used for personal media players and portable peripheral devices.

FSA801 detects wall chargers through a dedicated pin that provides the baseband with charger detection. The charger function is compliant with USB Battery Charging Specification, Rev 1.1, implementing Data Contact Detect (DCD) before detecting a charger. The FSA801 indicates if a Dedicated Charging Port (DCP) or a Charging Downstream Port (CDP) has been connected.

The FSA801 meets both USB Rev. 2.0 and micro-USB specifications.

# **Ordering Information**

| Part Number | Operating<br>Temperature Range | Top Mark | Package                                                                |

|-------------|--------------------------------|----------|------------------------------------------------------------------------|

| FSA801UMX   | -40 to +85°C                   | KL       | 16-Lead Quad, 1.8 x 2.6 mm Ultrathin Molded<br>Leadless Package (UMLP) |

Figure 1. Typical Application

### **Functional Description**

The FSA801 USB2.0 accessory switch is designed to consolidate wired accessories for portable devices, such as cellular telephones and portable audio players. The benefits of consolidation include reduced space requirements from a reduction of connectors and their size. The micro-USB connector, for example, reduces connector height and depth, allowing for slimmer overall designs. Using the USB industry standard and a common connector type for accessories such as chargers and headsets, greatly reduces the waste associated with new phone purchases by allowing re-use of the accessories.

Using just five wires for all connection types considerably reduces the cost of wired accessories and simplifies their construction. The FSA801 facilitates adopting this methodology because it is designed to redirect the DP/DM pins from the USB connector to one of three ports at the baseband's discretion. Additional flexibility is provided by the ability of the microphone line to be switched from either the DP CON or VBUS pin.

The VBUS pin is protected up to 28 V without damage to the FSA801.

### **USB Charger Detection / Data Contact Detect**

The FSA801 senses the presence of USB chargers per the USB Battery Charging Specification, Version 1.1. This specification uses  $V_{BUS}$  status and measurements on DP\_CON / DM\_CON pins to determine that a charging device might be attached. The 'CD\_N' pin goes to a low state, indicating the presence of a charger. The charger-detect algorithm executes when  $V_{BUS}$  is valid. The charger-detection algorithm detects both Dedicated Charging Ports (DCP) and Charging Downstream Ports (CDP).

In this implementation, per the *USB Battery Charging Specification, Version 1.1*, the FSA801 implements Data Contact Detect (DCD) to insure the D+ and D- pins have made contact before the dedicated charger detection is performed.

Since the BC1.1 charger detection algorithm applies and detects signals on the D+ and D- lines, any additional loading effects from portable device host side of the switch would cause the results to be invalid. To prevent interference due to any loading, the FSA801 only performs charger detection when all switches are open.

Additionally, if all switches are open and  $V_{BUS}$  is present, the FSA801 does not close any switch path until the DCD circuitry detects contact with the D+/D- pins and the charger detection is complete. If the D+/D- pins never contact, but  $V_{BUS}$  is present, the USB switches cannot be closed when configuring from SEL[2:0]='000' to SEL[2:0]='001' or SEL[2:0]='010'. To override this blocking, first switch to a non-USB mode (one of the audio modes, SEL[2:0]='011','100' or '101'), and then to the desired USB mode.

If the USB physical layer device that the FSA801 is connected to also performs DCD, it should not start until after the FSA801 has time to finish its detection function (since the delay between VBUS connection and D+/D-connection is not defined, this detection function time cannot be defined either).

Glitches on VBUS that occur when  $V_{\text{BUS}}$  is not driven (positive voltage spikes and on-off situations at the beginning of a cable attach) are automatically filtered by the DCD state machine timing.

To manually reset the FSA801 to search for a charger again, switch to SEL[2:0]='111' for a minimum of 30  $\mu$ s. After this state machine is reset, the next time that SEL[2:0]='000' (all switches open) for a minimum of 30  $\mu$ s, the FSA801 begins the charger detection sequence.

**PLEASE NOTE**: The FSA801 is guaranteed to operate down to 2.4 V. If the FSA801  $V_{\rm CC}$  is connected directly to a battery and falls below 2.4 V, the FSA801 may not correctly detect a charger. If a charger is applied, the  $V_{\rm CC}$  should start to rise above 2.4 V. In this situation, the FSA801 does not automatically check for a charger again, so the FSA801 should be placed in SEL[2:0]='111' for 30  $\mu$ s (min.), then SEL[2:0]='000' for 30  $\mu$ s (min.) to perform the charger detection again.

#### **Applications with Multiple USB Controllers**

When operating with two USB controllers, it is recommended to configure the switches to OPEN before switching to the other (second) USB interface. The OPEN setting duration should be long enough for the accessory to go to a SE0 state, so when the switch is set to the other (second) USB port, the new controller re-enumerates.

### **Mode Descriptions**

The FSA801 has three select pins to control the switching operations, SEL[0], SEL[1], and SEL[2] described in Table 1.

Table 1. Selection Truth Table

| SEL[2] | SEL[1] | SEL[0] | Switch Action                                   | Description                                                                                                                                                                                                                         |

|--------|--------|--------|-------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0      | 0      | 0      | OPEN                                            | Open all switch paths (device in low-power mode)                                                                                                                                                                                    |

| 0      | 0      | 1      | USB1, UART                                      | Closes USB1 path to D+/D-, default condition <sup>(1)</sup> - DP_CON connected to DP_HOST1 - DM_CON connected to DM_HOST1                                                                                                           |

| 0      | 1      | 0      | USB2, UART                                      | Closes USB2 path to D+/D DP_CON connected to DP_HOST2 - DM_CON connected to DM_HOST2                                                                                                                                                |

| 0      | 1      | 1      | AUDIO                                           | Closes audio path to D+/D- only, no microphone switched - DP_CON connected to R_HOST - DM_CON connected to L_HOST                                                                                                                   |

| 1      | 0      | 0      | MONO AUDIO with MIC on D+ <sup>(2)</sup>        | Closes audio path to DM_CON and microphone on DP_CON pin. This is a mono-audio application.  - DP_CON connected to MIC  - DM_CON connected to L_HOST                                                                                |

| 1      | 0      | 1      | STEREO AUDIO with MIC<br>on VBUS <sup>(2)</sup> | Closes audio path to D+/D- and microphone on V <sub>BUS</sub> pin. This mode is typically used for stereo headset with microphone.  - DP_CON connected to R_HOST  - DM_CON connected to L_HOST  - V <sub>BUS</sub> connected to MIC |

| 1      | 1      | 0      | Undefined                                       | Reserved; do not use.                                                                                                                                                                                                               |

| 1      | 1      | 1      | Charger Detection Reset                         | Charger Detection Reset. Selecting this mode for greater than 30 $\mu$ s resets the FSA801 to check for a charger, the next time a SEL[2:0] state of '000' is applied for more than 30 $\mu$ s.                                     |

#### Notes:

- 1. The SELECT pins are CMOS inputs and should not be left in a floating condition. Some applications require the UART path be in the CLOSED position on power-up for initial programming of the device under test. If that condition is desired, the three SELECT pins should be pulled to the correct levels with external resistors that should exceed 100 KΩ to reduce the static power consumption. In other applications, adding weak pull-down resistors to GND defaults the device to all paths open (low-power mode).

- 2. When the audio switch is in the OPEN position, the R and L are terminated to GND with internal termination resistors to discharge any stray capacitance that could cause audio pop.

# **Pin Configuration**

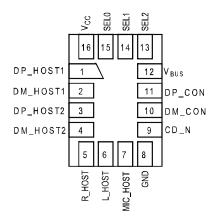

Figure 2. 16-Pin, UMLP Pin Assignments (Top-Through View)

# **Pin Descriptions**

| Name            | Pin#      | Description                                                                                                                             |  |  |  |  |  |

|-----------------|-----------|-----------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| USB, UART       | Interface |                                                                                                                                         |  |  |  |  |  |

| DP_HOST1        | 1         | signal, dedicated USB port to be connected to the resident USB or UART transceiver on ephone.                                           |  |  |  |  |  |

| DM_HOST1        | 2         | D- signal, dedicated USB port to be connected to the resident USB or UART transceiver on the phone.                                     |  |  |  |  |  |

| DP_HOST2        | 3         | D+ signal, dedicated USB port to be connected to the resident USB or UART transceiver on the phone.                                     |  |  |  |  |  |

| DM_HOST2        | 4         | O- signal, dedicated USB port to be connected to the resident USB or UART transceiver on the phone.                                     |  |  |  |  |  |

| Audio Interfa   | ace       |                                                                                                                                         |  |  |  |  |  |

| R_HOST          | 5         | Right audio channel from phone audio codec.                                                                                             |  |  |  |  |  |

| L_HOST          | 6         | Left audio channel from phone audio codec.                                                                                              |  |  |  |  |  |

| MIC_HOST        | 7         | Connected to the phone audio codec MIC input pin.                                                                                       |  |  |  |  |  |

| Power Interf    | ace       |                                                                                                                                         |  |  |  |  |  |

| V <sub>cc</sub> | 16        | Input voltage supply pin to be connected to the phone battery output.                                                                   |  |  |  |  |  |

| Connector In    | nterface  |                                                                                                                                         |  |  |  |  |  |

| $V_{BUS}$       | 12        | Input voltage supply pin to be connected to the V <sub>BUS</sub> pin of the USB connector.                                              |  |  |  |  |  |

| GND             | 8         | Ground.                                                                                                                                 |  |  |  |  |  |

| DP_CON          | 11        | Connected to the USB connector D+ pin; depending on the FSA801 signaling mode, this pin can share DP_HOST1, DP_HOST2 or R_HOST signals. |  |  |  |  |  |

| DM_CON          | 10        | Connected to the USB connector D- pin; depending on the FSA801 signaling mode, this pin can share DM_HOST1, DM_HOST2 or L_HOST signals. |  |  |  |  |  |

| Charger Det     | ection    |                                                                                                                                         |  |  |  |  |  |

| CD_N            | 9         | Active-LOW, open-drain output pin; requires pull-up resistor to baseband I/O voltage supply                                             |  |  |  |  |  |

| Switch Cont     | rol       |                                                                                                                                         |  |  |  |  |  |

| SEL[2:0]        | 13-15     | Switch selection pins; refer to Table 1 for truth table.                                                                                |  |  |  |  |  |

## **Absolute Maximum Ratings**

Stresses exceeding the absolute maximum ratings may damage the device. The device may not function or be operable above the recommended operating conditions and stressing the parts to these levels is not recommended. In addition, extended exposure to stresses above the recommended operating conditions may affect device reliability. The absolute maximum ratings are stress ratings only.

| Symbol              | Param                                                         |                             | Min.       | Max.                 | Unit                  |    |  |

|---------------------|---------------------------------------------------------------|-----------------------------|------------|----------------------|-----------------------|----|--|

| V <sub>CC</sub>     | Supply Voltage from Battery / Baseba                          | -0.5                        | 6.0        | V                    |                       |    |  |

| $V_{BUS}$           | Voltage from Mini/Micro-USB Connec                            | ctor                        |            | -0.5                 | 28.0                  | V  |  |

|                     |                                                               | USB/UART Path Activ         | е          | -0.5                 | V <sub>BUS</sub> +0.5 |    |  |

| $V_{SW}$            | Switch I/O Voltage                                            | Stereo/Mono Audio Pa        | ath Active | V <sub>CC</sub> -8.5 | V <sub>CC</sub> +0.5  | V  |  |

|                     |                                                               | All Other Channels          |            | -0.5                 | V <sub>CC</sub> +0.5  |    |  |

| I <sub>IK</sub>     | Input Clamp Diode Current                                     |                             |            | -50                  |                       | mA |  |

|                     |                                                               | USB                         |            |                      | 50                    |    |  |

| $I_{SW}$            | Switch I/O Current (Continuous)                               | Audio                       |            | 60                   | mA                    |    |  |

|                     |                                                               | All Other Channels          |            | 50                   |                       |    |  |

|                     |                                                               | USB                         |            | 150                  | mA                    |    |  |

| I <sub>SWPEAK</sub> | Peak Switch Current (Pulsed at 1ms Duration, <10% Duty Cycle) | Audio                       |            | 150                  | mA                    |    |  |

|                     | Buration, <10% Buty Cycle)                                    | All Other Channels          |            | 150                  | mA                    |    |  |

| T <sub>STG</sub>    | Storage Temperature Range                                     |                             |            | -65                  | +150                  | °C |  |

| $T_J$               | Maximum Junction Temperature                                  |                             |            |                      | +150                  | °C |  |

| $T_L$               | Lead Temperature (Soldering, 10 Sec                           |                             | +260       | °C                   |                       |    |  |

|                     |                                                               | USB Connector Pins          | Air Gap    |                      | 15                    |    |  |

| <b>505</b>          | IEC 61000-4-2 System                                          | (D+, D-, V <sub>BUS</sub> ) | Contact    |                      | 8                     |    |  |

| ESD                 | Human Body Model, JEDEC JESD22-A114 All Pins                  |                             |            |                      | 3                     | kV |  |

|                     | Charged Device Model, JEDEC JESE                              | )22-C101                    | All Pins   |                      | 2                     |    |  |

# **Recommended Operating Conditions**

The Recommended Operating Conditions table defines the conditions for actual device operation. Recommended operating conditions are specified to ensure optimal performance to the datasheet specifications. Fairchild does not recommend exceeding them or designing to Absolute Maximum Ratings.

| Symbol          | Parameter              | Min.                 | Max.                 | Units              |    |

|-----------------|------------------------|----------------------|----------------------|--------------------|----|

| V <sub>CC</sub> | Battery Supply Voltage |                      | 2.7                  | 4.4                | V  |

|                 |                        | USB/UART Path Active | 0                    | 4.4                | V  |

| $V_{SW}$        | Switch I/O Voltage     | Audio Path Active    | V <sub>CC</sub> -7.0 | 2.0                | V  |

|                 |                        | Mic Path Active      | 0                    | V <sub>CC</sub> -1 | V  |

| T <sub>A</sub>  | Operating Temperature  |                      | -40                  | +85                | °C |

### **Switch Path DC Electrical Characteristics**

All typical values are at 25°C unless otherwise specified.

| Cumbal               | Doromotor                                                | V (A)               | Conditions                                                                                       | $T_A = -40 \text{ to } +85^\circ$ |      | -85°C | Unit |

|----------------------|----------------------------------------------------------|---------------------|--------------------------------------------------------------------------------------------------|-----------------------------------|------|-------|------|

| Symbol               | Parameter                                                | V <sub>CC</sub> (V) | Conditions                                                                                       | Min.                              | Тур. | Max.  | Unit |

| Host Interfa         | ace Pins (SEL[2:0])                                      |                     |                                                                                                  |                                   |      |       |      |

| V <sub>IH</sub>      | Input High Voltage                                       | 3.2 to 4.4          |                                                                                                  | 1.3                               |      |       | V    |

| V <sub>IL</sub>      | Input Low Voltage                                        | 3.2 to 4.4          |                                                                                                  |                                   |      | 0.7   | V    |

| I <sub>IN</sub>      | Control Input Leakage                                    | 0 to 4.4            | V <sub>SW</sub> =0 to V <sub>CC</sub>                                                            | -1                                |      | 1     | μΑ   |

| l <sub>oz</sub>      | Off State Leakage                                        | 4.4                 | 0 ≤ DP_CON, DM_CON,<br>DP_HOSTn, DM_HOSTn,<br>R_HOST, L_HOST ≤ 3.6 V                             | -2                                |      | 2     | μA   |

| Charger De           | etect Pin (CD_N)                                         |                     |                                                                                                  |                                   |      |       |      |

| $V_{OL}$             | Output Low Voltage                                       | 3.2 to 4.4          | I <sub>OL</sub> =10 mA                                                                           |                                   |      | 0.4   | V    |

| V <sub>BUS</sub> Pin |                                                          |                     |                                                                                                  |                                   |      |       |      |

| V <sub>BUSTH</sub>   | Charger Detect Threshold                                 | 3.2 to 4.4          |                                                                                                  |                                   | 3.3  |       | V    |

| I <sub>BUSIN</sub>   | V <sub>BUS</sub> Input Leakage                           | 0 to 4.4            |                                                                                                  |                                   | 2    | 10    | μA   |

| Switch Off           | Characteristics                                          |                     |                                                                                                  |                                   |      |       | 1    |

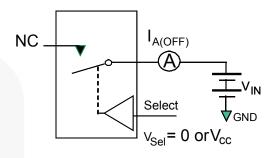

| l <sub>OFF</sub>     | Power Off Leakage Current                                | 0                   | All Ports Except MIC & Audio Path V <sub>SW</sub> =0 V to 4.4 V, Figure 7                        |                                   |      | 10    | μA   |

| USB Switcl           | h On Paths                                               |                     |                                                                                                  |                                   |      |       |      |

| R <sub>ONUSB</sub>   | HS USB Range Switch On Resistance                        | 3.2 to 4.4          | V <sub>DP_CON/DM_CON</sub> =0 V, 0.4 V,<br>I <sub>ON</sub> =8 mA, Figure 6                       |                                   | 6    | 9     | Ω    |

| R <sub>ONUART</sub>  | UART Range Switch On Resistance                          | 3.2 to 4.4          | V <sub>DP_CON/DM_CON</sub> =0 V, 3.2 V,<br>I <sub>ON</sub> =8 mA, Figure 6                       |                                   | 8    |       | Ω    |

| Audio R/L            | Switch On Paths                                          |                     |                                                                                                  |                                   | •    |       |      |

| R <sub>ONAUD</sub>   | Audio Switch On Resistance                               | 3.2 to 4.4          | V <sub>L/R</sub> =-0.8 V, 0.8 V, I <sub>ON</sub> =30 mA,                                         |                                   |      | 3     | Ω    |

| R <sub>FLAT</sub>    | Audio R <sub>ON</sub> Flatness <sup>(3)</sup>            | 3.8                 | Figure 6                                                                                         |                                   | 0.16 |       | Ω    |

| R <sub>TERM</sub>    | Internal Termination Resistors                           |                     |                                                                                                  |                                   | 1    |       | kΩ   |

| MIC Switch           | On Path                                                  |                     |                                                                                                  |                                   | •    |       |      |

| В                    | Switch On Resistance                                     | 3.2 to 4.4          | SEL[2:0]=100 (MIC to DP_CON),<br>V <sub>SW</sub> =0 V, 1.6 V, I <sub>ON</sub> =8 mA,<br>Figure 6 |                                   | 15   |       | Ω    |

| R <sub>ONMIC</sub>   | Switch Off Resistance                                    | 3.2 10 4.4          | SEL[2:0]=101 (MIC to VBUS), $V_{SW}$ =0 V, 1.6 V, $I_{ON}$ =8 mA, Figure 6                       |                                   | 28   |       | Ω    |

| Total Switc          | ch Current Consumption                                   |                     |                                                                                                  |                                   |      |       |      |

| I <sub>CCSL</sub>    | Battery Supply Sleep Mode<br>Average Current             | 3.2 to 4.4          | Static Current During Sleep Mode (SEL[2:0]=0)                                                    |                                   |      | 1     | μA   |

|                      |                                                          |                     | USB/UART Mode                                                                                    |                                   | 20   | 35    | μA   |

| I <sub>CCWK</sub>    | Battery Supply Active Mode<br>Average Current            | 3.2 to 4.4          | Audio Mode<br>(SEL[2:0]=011), V <sub>BUS</sub> =0 V                                              |                                   |      | 1     | μΑ   |

|                      |                                                          |                     | Audio Mode<br>(SEL[2:0]=100, 101)                                                                |                                   | 20   | 35    | μA   |

| l:-                  | Increase in I <sub>CCSL</sub> /I <sub>CCWK</sub> Current | 3.2 to 4.4          | $V_{SEL}$ = 2.8 V and $V_{CC}$ = 4.4 V                                                           |                                   |      | 8     | μA   |

| ICCSELT              | per Control Voltage and V <sub>CC</sub>                  | 3.2 10 4.4          | V <sub>SEL</sub> = 1.8 V and V <sub>CC</sub> = 4.4 V                                             |                                   |      | 10    | μΑ   |

### Note:

3. Flatness is defined as the difference between the maximum and minimum values of on resistance over the specified range of conditions.

# Switch Path AC Electrical Characteristics<sup>(4)</sup>

All typical value are for  $V_{\text{CC}}$  =3.8 V at 25°C unless otherwise specified.

| Symbol           | Parameter                                                                                              |                                                         | V <sub>cc</sub>                                                                     | Conditions                                                                          | $T_A = -40 \text{ to } +85^{\circ}\text{C}$ |      |      | Unit      | Figure    |

|------------------|--------------------------------------------------------------------------------------------------------|---------------------------------------------------------|-------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------|---------------------------------------------|------|------|-----------|-----------|

| Symbol           | Г                                                                                                      | arameter .                                              | (V)                                                                                 | Conditions                                                                          | Min.                                        | Тур. | Max. | Oilie     | rigure    |

|                  | Active Channel                                                                                         | Audio Mode                                              | 3.8                                                                                 | f=20 kHz, $R_T$ =32 $\Omega$ , $C_L$ =0 pF                                          |                                             | -95  |      |           |           |

|                  | Crosstalk DP_CON to DM_CON                                                                             |                                                         | 3.8                                                                                 | f=1 MHz, $R_T$ =50 $\Omega$ , $C_L$ =0 pF                                           |                                             | -78  |      |           |           |

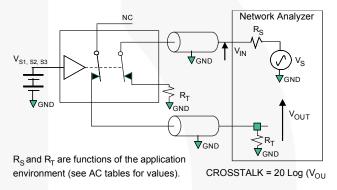

| Xtalk            |                                                                                                        | USB Mode                                                | 3.0                                                                                 | f=240 MHz, $R_T$ =50 $\Omega$ , $C_L$ =0 pF                                         |                                             | -36  |      | dB        | Figure 9  |

|                  | Active Channel                                                                                         | MIC on VBUS to<br>R_HOST, L_HOST                        | 3.8                                                                                 | f=20 kHz, $R_T$ =32 $\Omega$ , $C_L$ =0 pF                                          |                                             | -93  |      |           |           |

|                  | Crosstalk MIC                                                                                          | MIC on DP_CON to L_HOST                                 | 3.8                                                                                 | f=20 kHz, $R_T$ =32 $\Omega$ , $C_L$ =0 pF                                          |                                             | -105 |      |           |           |

|                  |                                                                                                        | Audio Rejection L_HOST to DM_CON, R_HOST to DP_CON      | 3.8                                                                                 | f=20 kHz, $R_T$ =32 $\Omega$ , $C_L$ =0 pF                                          |                                             | -100 |      | dB        |           |

|                  |                                                                                                        | MIC Rejection MIC_HOST to DP_CON                        | 3.8                                                                                 | f=20 kHz, $R_T$ =50 $\Omega$ , $C_L$ =0pF                                           |                                             | -110 |      |           |           |

| O <sub>IRR</sub> | Off Isolation                                                                                          | MIC Rejection<br>MIC_HOST to VBUS                       | 3.8                                                                                 | f=20 kHz, $R_T$ =50 $\Omega$ , $C_L$ =0 pF                                          |                                             | -110 |      |           | Figure 8  |

|                  | Rejection Ratio                                                                                        | USB Rejection DM_HOST to DM_CON, DP_HOST to DP_CON      | 20                                                                                  | f=1 MHz, $R_T$ =50 $\Omega$ , $C_L$ =0 pF                                           |                                             | -85  |      |           |           |

|                  |                                                                                                        |                                                         | f=240 MHz, $R_T$ =50 Ω, $C_L$ =0 pF                                                 |                                                                                     | -35                                         |      |      |           |           |

| PSRR             | Power Supply Rejection Ratio MIC on VBUS or MIC on DP_CON, to VCC or GND                               |                                                         | 3.8                                                                                 | Power Supply Noise<br>300Mv <sub>PP</sub> , f=217Hz                                 |                                             | -110 |      | dB        |           |

| THD+N            | Total Harmonic (                                                                                       | Distortion + Noise 3.8                                  | 20 Hz to 20 kHz,<br>R <sub>L</sub> =16 Ω, Input Signal<br>Range 1.6 V <sub>PP</sub> |                                                                                     | 0.10                                        |      | %    | Figure 13 |           |

| וויטלוו          | (Audio Path)                                                                                           |                                                         |                                                                                     | 20 Hz to 20 kHz,<br>R <sub>L</sub> =32 Ω, Input Signal<br>Range 1.6 V <sub>PP</sub> |                                             | 0.07 |      | %         | Figure 13 |

| t <sub>CDR</sub> | Charger Detection Reset Time: Minimum time in Selected State to Reset Charger Detection State Machine. |                                                         | 3.8                                                                                 | SEL[2:0]='111'                                                                      | 30                                          |      |      | μs        |           |

| t <sub>CDL</sub> |                                                                                                        | on Start Time: Minimum<br>State to Start Charger<br>nce | 3.8                                                                                 | SEL[2:0]='000'                                                                      | 30                                          |      |      | μs        |           |

#### Note:

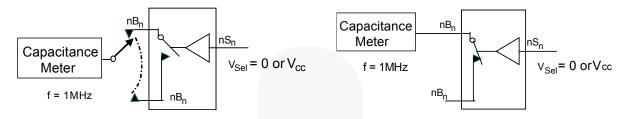

# Capacitance

| Symbol                   | Parameter                                          | V <sub>CC</sub> (V) | Conditions                        | T <sub>A</sub> = -40 to +85°C |      | Unit | Figure    |

|--------------------------|----------------------------------------------------|---------------------|-----------------------------------|-------------------------------|------|------|-----------|

| Syllibol                 | Farameter                                          | V <sub>CC</sub> (V) | Conditions                        | Тур.                          | Max. | Onn  | rigure    |

| C <sub>IN</sub>          | Select Pins Capacitance <sup>(5)</sup>             | 0                   | V <sub>BIAS</sub> =0.2 V          | 2.5                           |      | pF   | Figure 11 |

| C <sub>OFF(D+, D-)</sub> | D+, D- On Capacitance (HS USB Mode) <sup>(5)</sup> | 3.8                 | V <sub>BIAS</sub> =0.2 V, f=1 MHz | 4.7                           |      | pF   | Figure 11 |

| C <sub>ON(D+, D-)</sub>  | D+, D- On Capacitance (HS USB Mode) <sup>(5)</sup> | 3.8                 | V <sub>BIAS</sub> =0.2 V, f=1 MHz | 7.6                           |      | pF   | Figure 12 |

#### Note:

<sup>4.</sup> Guaranteed by characterization, not production tested.

<sup>5.</sup> Guaranteed by characterization, not production tested.

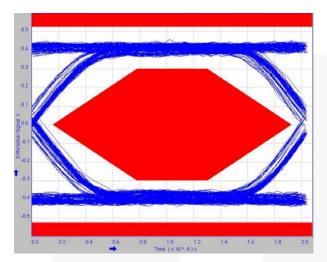

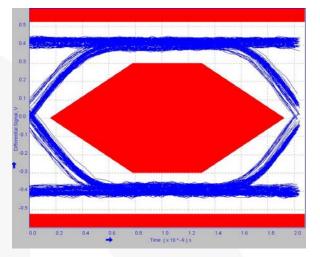

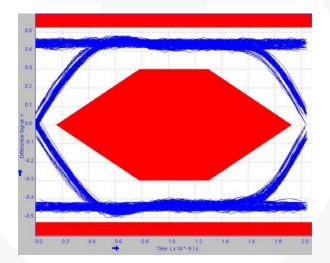

# **High-Speed USB Eye Compliance Results**

Figure 3. High-Speed Test Results (DP\_CON/DM\_CON - DP\_HOST1/DM\_HOST1)

Figure 4. High-Speed Test Results (DP\_CON/DM\_CON - DP\_HOST2/DM\_HOST2)

Figure 5. High-Speed Eye Compliance Input Signal

# **Test Diagrams**

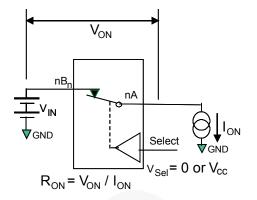

Figure 6. On Resistance

\*\*Each switch port is tested separately.

Figure 7. Off Leakage

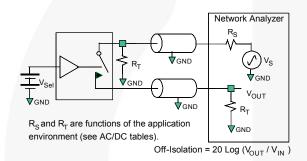

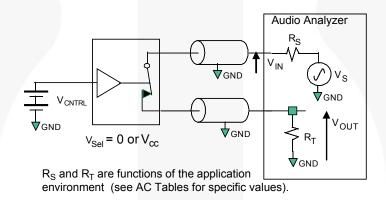

Figure 8. Channel Off Isolation

Figure 9. Active Channel Crosstalk

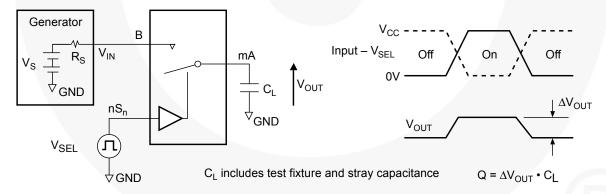

Figure 10. Charge Injection Test

# Test Diagrams (Continued)

Figure 11. Channel Off Capacitance

Figure 12. Channel On Capacitance

Figure 13. Total Harmonic Distortion + Noise

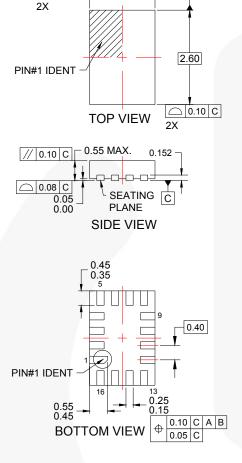

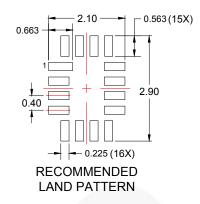

## **Physical Dimensions**

○ 0.10 C

1.80

-AB

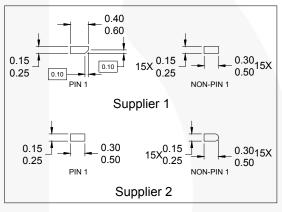

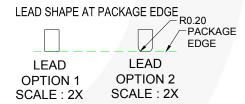

#### TERMINAL SHAPE VARIANTS

#### NOTES:

- A. PACKAGE DOES NOT FULLY CONFORM TO JEDEC STANDARD.

- B. DIMENSIONS ARE IN MILLIMETERS.

- C. DIMENSIONS AND TOLERANCES PER ASME Y14.5M, 1994.

- D. LAND PATTERN RECOMMENDATION IS BASED ON FSC DESIGN ONLY.

- E. DRAWING FILENAME: MKT-UMLP16Arev4.

- F. TERMINAL SHAPE MAY VARY ACCORDING TO PACKAGE SUPPLIER, SEE TERMINAL SHAPE VARIANTS.

#### Figure 14. 16-Lead, Ultrathin Molded Leadless Package (UMLP)

Package drawings are provided as a service to customers considering Fairchild components. Drawings may change in any manner without notice. Please note the revision and/or date on the drawing and contact a Fairchild Semiconductor representative to verify or obtain the most recent revision. Package specifications do not expand the terms of Fairchild's worldwide terms and conditions, specifically the warranty therein, which covers Fairchild products.

Always visit Fairchild Semiconductor's online packaging area for the most recent package drawings: <a href="http://www.fairchildsemi.com/packaging/">http://www.fairchildsemi.com/packaging/</a>.

#### **TRADEMARKS**

The following includes registered and unregistered trademarks and service marks, owned by Fairchild Semiconductor and/or its global subsidiaries, and is not intended to be an exhaustive list of all such trademarks.

2Cool™

F-PFS™

AccuPower™

FRET®

AX-CAP™\*

Global Power Resource®

BitSiC™

GreenBridge™

Build it Now™

Green FPS™

CorePLUS™

Green FPS™ e-Series™

CorePOWER™

Gmax™

CROSSVOLT™

GTO™

CTL™ IntelliMAX™

Current Transfer Logic™ ISOPLANAR™

DEUXPEED® Making Small Speakers Sound Louder

Dual Cool™ EcoSPARK® EfficientMax™ ESBC™

Fairchild<sup>®</sup>

Fairchild Semiconductor<sup>®</sup>

FACT Quiet Series™

FACT<sup>®</sup>

FAST<sup>®</sup>

FastvCore™

FETBench™ FlashWriter®\* FPS™ PowerTrench<sup>®</sup> PowerXS™

Programmable Active Droop™

QFET<sup>®</sup> QS™ Quiet Series™ RapidConfigure™

Saving our world, 1mW/W/kW at a time™

SignalWise™ SmartMax™ SMART START™

Solutions for Your Success™

SPM®

STEALTH™

SuperFET®

SuperSOT™-3

SuperSOT™-8

SupreMOS®

SyncFET™

Sync-Lock™

■ SYSTEM

■ GENERAL®\*

Frenchise

TinyBoost™

TinyBuck™

TinyCalc™

TinyCogic®

TINYOPTO™

TinyPower™

TinyPower™

TinyPWM™

TinyPWire™

Tran SIC™

TriFault Detect™

TRUECURRENT®\*

The Power Franchise®

SerDes\*

UHC®

Ultra FRFET™

UniFET™

VCX™

VisualMax™

VoltagePlus™

XS™

μSerDes™

\* Trademarks of System General Corporation, used under license by Fairchild Semiconductor.

and Better™

MICROCOUPLER™

MegaBuck™

MicroFET™

MicroPak™

MicroPak2™

MillerDrive™

Motion Max™

OPTOLOGIC®

OPTOPLANAR®

mWSaver™

OptoHiT™

#### DISCLAIMER

FAIRCHILD SEMICONDUCTOR RESERVES THE RIGHT TO MAKE CHANGES WITHOUT FURTHER NOTICE TO ANY PRODUCTS HEREIN TO IMPROVE RELIABILITY, FUNCTION, OR DESIGN. FAIRCHILD DOES NOT ASSUME ANY LIABILITY ARISING OUT OF THE APPLICATION OR USE OF ANY PRODUCT OR CIRCUIT DESCRIBED HEREIN; NEITHER DOES IT CONVEY ANY LICENSE UNDER ITS PATENT RIGHTS, NOR THE RIGHTS OF OTHERS, THESE SPECIFICATIONS DO NOT EXPAND THE TERMS OF FAIRCHILD'S WORLDWIDE TERMS AND CONDITIONS, SPECIFICALLY THE WARRANTY THEREIN, WHICH COVERS THESE PRODUCTS.

#### LIFE SUPPORT POLICY

FAIRCHILD'S PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS WITHOUT THE EXPRESS WRITTEN APPROVAL OF FAIRCHILD SEMICONDUCTOR CORPORATION.

#### As used herein:

- Life support devices or systems are devices or systems which, (a) are intended for surgical implant into the body or (b) support or sustain life, and (c) whose failure to perform when properly used in accordance with instructions for use provided in the labeling, can be reasonably expected to result in a significant injury of the user.

- A critical component in any component of a life support, device, or system whose failure to perform can be reasonably expected to cause the failure of the life support device or system, or to affect its safety or effectiveness.

#### ANTI-COUNTERFEITING POLICY

Fairchild Semiconductor Corporation's Anti-Counterfeiting Policy. Fairchild's Anti-Counterfeiting Policy is also stated on our external website, www.fairchildsemi.com, under Sales Support.

Counterfeiting of semiconductor parts is a growing problem in the industry. All manufacturers of semiconductor products are experiencing counterfeiting of their parts. Customers who inadvertently purchase counterfeit parts experience many problems such as loss of brand reputation, substandard performance, failed applications, and increased cost of production and manufacturing delays. Fairchild is taking strong measures to protect ourselves and our customers from the proliferation of counterfeit parts. Fairchild strongly encourages customers to purchase Fairchild parts either directly from Fairchild or from Authorized Fairchild Distributors who are listed by country on our web page cited above. Products customers buy either from Fairchild directly or from Authorized Fairchild Distributors are genuine parts, have full traceability, meet Fairchild's quality standards for handling and storage and provide access to Fairchild's full range of up-to-date technical and product information. Fairchild and our Authorized Distributors will stand behind all warranties and will appropriately address any warranty issues that may arise. Fairchild will not provide any warranty coverage or other assistance for parts bought from Unauthorized Sources. Fairchild is committed to combat this global problem and encourage our customers to do their part in stopping this practice by buying direct or from authorized distributors.

#### PRODUCT STATUS DEFINITIONS

#### Definition of Terms

| Deliminon of Terms       |                       |                                                                                                                                                                                                     |

|--------------------------|-----------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Datasheet Identification | Product Status        | Definition                                                                                                                                                                                          |

| Advance Information      | Formative / In Design | Datasheet contains the design specifications for product development. Specifications may change in any manner without notice.                                                                       |

| Preliminary              | First Production      | Datasheet contains preliminary data; supplementary data will be published at a later date. Fairchild Semiconductor reserves the right to make changes at any time without notice to improve design. |

| No Identification Needed | Full Production       | Datasheet contains final specifications. Fairchild Semiconductor reserves the right to make changes at any time without notice to improve the design.                                               |

| Obsolete                 | Not In Production     | Datasheet contains specifications on a product that is discontinued by Fairchild Semiconductor. The datasheet is for reference information only.                                                    |

Rev. 162

# **Mouser Electronics**

**Authorized Distributor**

Click to View Pricing, Inventory, Delivery & Lifecycle Information:

FSA801UMX