## INTEGRATED CIRCUITS

# DATA SHEET

For a complete data sheet, please also download:

- The IC06 74HC/HCT/HCU/HCMOS Logic Family Specifications

- The IC06 74HC/HCT/HCU/HCMOS Logic Package Information

- The IC06 74HC/HCT/HCU/HCMOS Logic Package Outlines

# **74HC/HCT7030**9-bit x 64-word FIFO register; 3-state

Product specification

File under Integrated Circuits, IC06

December 1990

## 74HC/HCT7030

#### **FEATURES**

- Synchronous or asynchronous operation

- · 3-state outputs

- · Master-reset input to clear control functions

- 33 MHz (typ.) shift-in, shift-out rates with or without flags

- · Very low power consumption

- · Cascadable to 25 MHz (typ.)

- · Readily expandable in word and bit dimensions

- Pinning arranged for easy board layout: input pins directly opposite output pins

- Output capability: standard

- I<sub>CC</sub> category: LSI

#### **GENERAL DESCRIPTION**

The 74HC/HCT7030 are high-speed Si-gate CMOS devices specified in compliance with JEDEC standard no. 7A.

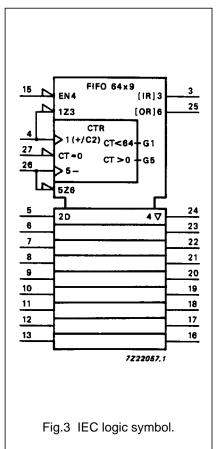

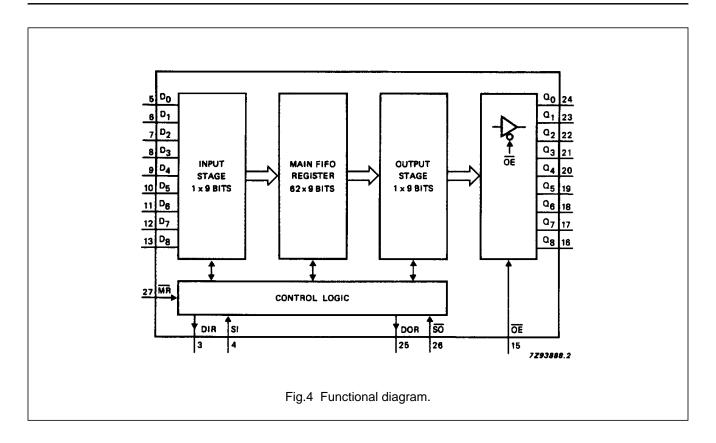

The 74HC/HCT7030 is an expandable, First-In First-Out (FIFO) memory organized as 64 words by 9 bits. A 33 MHz data-rate makes it ideal for high-speed applications. Even at high frequencies, the  $I_{CC}$  dynamic is very low ( $f_{max}$  = 18 MHz;  $V_{CC}$  = 5 V produces a dynamic  $I_{CC}$  of 80 mA). If the device is not continuously operating at  $f_{max}$ , then  $I_{CC}$  will decrease proportionally.

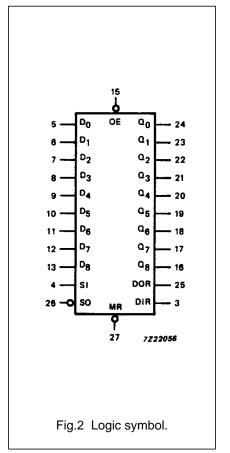

With separate controls for shift-in (SI) and shift-out  $(\overline{SO})$ , reading and writing operations are completely independent, allowing synchronous and asynchronous data transfers. Additional controls include a master-reset input  $(\overline{MR})$  and an output enable input  $(\overline{OE})$ . Flags for data-in-ready (DIR) and data-out-ready (DOR) indicate the status of the device.

Devices can be interconnected easily to expand word and bit dimensions. All output pins are directly opposite the corresponding input pins thus simplifying board layout in expanded applications.

#### **INPUTS AND OUTPUTS**

#### Data inputs (D<sub>0</sub> to D<sub>8</sub>)

As there is no weighting of the inputs, any input can be assigned as the MSB. The size of the FIFO memory can be reduced from the  $9\times64$  configuration, i.e.  $8\times64,$   $7\times64,$  down to  $1\times64,$  by tying unused data input pins to  $V_{CC}$  or GND.

#### Data outputs $(Q_0 \text{ to } Q_8)$

As there is no weighting of the outputs, any output can be assigned as the MSB. The size of the FIFO memory can be reduced from the  $9\times64$  configuration as described for data inputs. In a reduced format, the unused data output pins must be left open circuit.

#### Master-reset (MR)

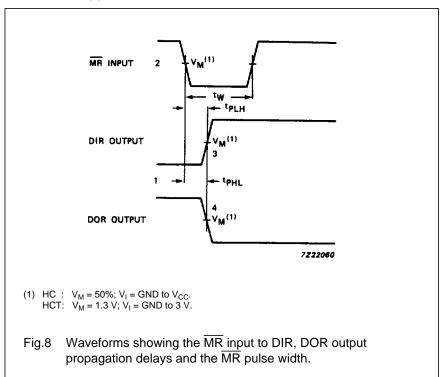

When MR is LOW, the control functions within the FIFO are cleared, and data content is declared invalid. The data-in-ready (DIR) flag is set HIGH and the data-out-ready (DOR) flag is set LOW. The output stage remains in the state of the last word that was shifted out, or in the random state existing at power-up.

## Status flag outputs (DIR, DOR)

Indication of the status of the FIFO is given by two status flags, data-in-ready (DIR) and data-out-ready (DOR):

- DIR = HIGH indicates the input stage is empty and ready to accept valid data

- DIR = LOW indicates that the FIFO is full or that a previous shift-in operation is not complete (busy)

- DOR = HIGH assures valid data is present at the outputs Q<sub>0</sub> to Q<sub>8</sub> (does not indicate that new data is awaiting transfer into the output stage)

- DOR = LOW indicates the output stage is busy or there is no valid data

#### Shift-in control (SI)

Data is loaded into the input stage on a LOW-to-HIGH transition of SI. A HIGH-to-LOW transition triggers an automatic data transfer process (ripple through). If SI is held HIGH during reset, data will be loaded at the rising edge of the  $\overline{\text{MR}}$  signal.

#### Shift-out control (SO)

A LOW-to-HIGH transition of  $\overline{SO}$  causes the DOR flags to go LOW. A HIGH-to-LOW transition of  $\overline{SO}$  causes upstream data to move into the output stage, and empty locations to move towards the input stage (bubble-up).

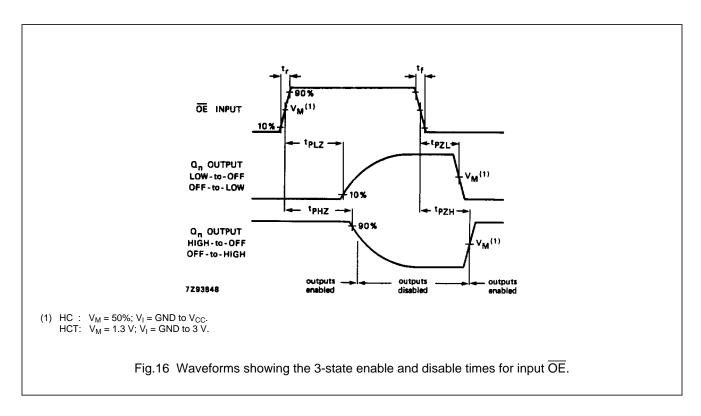

## Output enable (OE)

The outputs  $Q_0$  to  $Q_8$  are enabled when  $\overline{OE}$  = LOW. When  $\overline{OE}$  = HIGH the outputs are in the high impedance OFF-state.

# 9-bit x 64-word FIFO register; 3-state

74HC/HCT7030

## **QUICK REFERENCE DATA**

GND = 0 V;  $T_{amb}$  = 25 °C;  $t_r$  =  $t_f$  = 6 ns

| SYMBOL                              | PARAMETER                                 | CONDITIONS                                    | TYP | UNIT |      |

|-------------------------------------|-------------------------------------------|-----------------------------------------------|-----|------|------|

| STWIDOL                             | PARAMETER                                 | CONDITIONS                                    | нс  | нст  | UNII |

| t <sub>PHL</sub> / t <sub>PLH</sub> | propagation delay                         | C <sub>L</sub> = 15 pF; V <sub>CC</sub> = 5 V |     |      |      |

|                                     | MR to DIR and DOR                         |                                               | 21  | 26   | ns   |

|                                     | SO to Q <sub>n</sub>                      |                                               | 36  | 40   | ns   |

| f <sub>max</sub>                    | maximum clock frequency SI and SO         |                                               | 33  | 29   | MHz  |

| Cı                                  | input capacitance                         |                                               | 3.5 | 3.5  | pF   |

| C <sub>P</sub>                      | power dissipation capacitance per package | notes 1 and 2                                 | 660 | 660  | pF   |

#### **Notes**

1.  $C_{PD}$  is used to determine the dynamic power dissipation ( $P_D$  in  $\mu W$ ):

$$P_D = C_{PD} \times V_{CC}^2 \times f_i + \sum (C_L \times V_{CC}^2 \times f_o)$$

where:

$f_i$  = input frequency in MHz

$f_o$  = output frequency in MHz

$\sum (C_L \times V_{CC}^2 \times f_0) = \text{sum of outputs}$

C<sub>L</sub> = output load capacitance in pF

V<sub>CC</sub> = supply voltage in V

2. For HC the condition is  $V_I$  = GND to  $V_{CC}$ For HCT the condition is  $V_I$  = GND to  $V_{CC}$  – 1.5 V

#### **ORDERING INFORMATION**

See "74HC/HCT/HCU/HCMOS Logic Package Information".

## 74HC/HCT7030

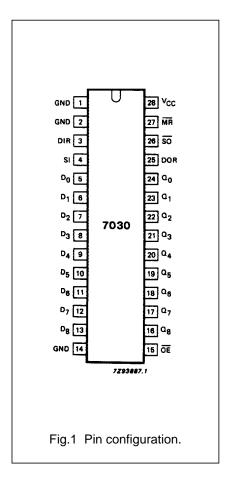

## **PIN DESCRIPTION**

| PIN NO.                            | SYMBOL                           | NAME AND FUNCTION                             |

|------------------------------------|----------------------------------|-----------------------------------------------|

| 1, 2, 14                           | GND                              | ground (0 V)                                  |

| 3                                  | DIR                              | data-in-ready output                          |

| 4                                  | SI                               | shift-in input (LOW-to-HIGH, edge-triggered)  |

| 5, 6, 7, 8, 9, 10, 11, 12, 13      | D <sub>0</sub> to D <sub>8</sub> | parallel data inputs                          |

| 15                                 | ŌĒ                               | output enable input (active LOW)              |

| 24, 23, 22, 21, 20, 19, 18, 17, 16 | Q <sub>0</sub> to Q <sub>8</sub> | 3-state parallel data outputs                 |

| 25                                 | DOR                              | data-out-ready output                         |

| 26                                 | SO                               | shift-out input (HIGH-to-LOW, edge-triggered) |

| 27                                 | MR                               | asynchronous master-reset input (active LOW)  |

| 28                                 | V <sub>CC</sub>                  | positive supply voltage                       |

#### Note

1. Pin 14 must be connected to GND. Pins 1 and 2 can be left floating or connected to GND, however it is not allowed to let current flow in either direction between pins 1, 2 and 14.

## 74HC/HCT7030

## **APPLICATIONS**

- High-speed disc or tape controller

- Video timebase correction

- A/D output buffers

- · Voice synthesis

- Input/output formatter for digital filters and FFTs

- Bit-rate smoothing

## 74HC/HCT7030

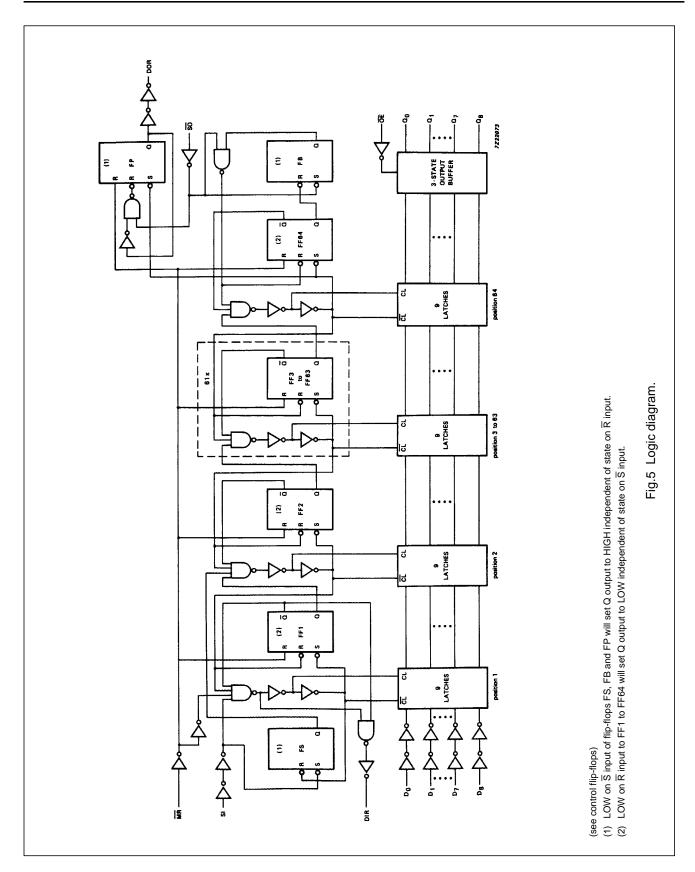

#### **FUNCTIONAL DESCRIPTION**

#### **Data input**

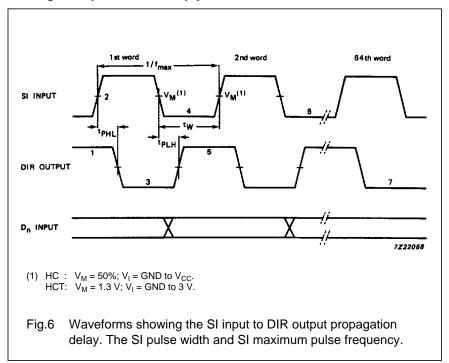

Following power-up, the master-reset  $(\overline{MR})$  input is pulsed LOW to clear the FIFO memory (see Fig.8). The data-in-ready flag (DIR = HIGH) indicates that the FIFO input stage is empty and ready to receive data. When DIR is valid (HIGH), data present at D<sub>0</sub> to D<sub>8</sub> can be shifted-in using the SI control input. With SI = HIGH, data is shifted into the input stage and a busy indication is given by DIR going LOW.

The data remains at the first location in the FIFO until SI is set to LOW. With SI = LOW data moves through the FIFO to the output stage, or to the last empty location. If the FIFO is not full after the SI pulse, DIR again becomes valid (HIGH) to indicate that space is available in the FIFO. The DIR flag remains LOW if the FIFO is full (see Fig.6). The SI pulse must be made LOW in order to complete the shift-in process.

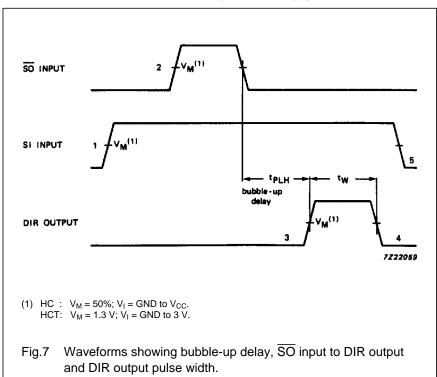

With the FIFO full, SI can be held HIGH until a shift-out  $(\overline{SO})$  pulse occurs. Then, following a shift-out of data, an empty location appears at the FIFO input and DIR goes HIGH to allow the next data to be shifted-in. This remains at the first FIFO location until SI again goes LOW (see Fig.7).

#### Data transfer

After data has been transferred from the input stage of the FIFO following SI = LOW, data moves through the FIFO asynchronously and is stacked at the output end of the register. Empty locations appear at the input end of the FIFO as data moves through the device.

#### **Data output**

The data-out-ready flag (DOR = HIGH) indicates that there is valid data at the output (Q<sub>0</sub> to Q<sub>8</sub>). The initial master-reset at power-on ( $\overline{MR} = LOW$ ) sets DOR to LOW (see Fig.8). After  $\overline{MR}$  = HIGH, data shifted into the FIFO moves through to the output stage causing DOR to go HIGH. As the DOR flag goes HIGH, data can be shifted-out using the  $\overline{SO}$  control input. With  $\overline{SO}$  = HIGH, data in the output stage is shifted out and a busy indication is given by DOR going LOW. When SO is made LOW, data moves through the FIFO to fill the output stage and an empty location appears at the input stage. When the output stage is filled DOR goes HIGH, but if the last of the valid data has been shifted out leaving the FIFO empty the DOR flag remains LOW (see Fig.9). With the FIFO empty, the last word that was shifted-out is latched at the output  $Q_0$  to  $Q_8$ .

With the FIFO empty, the  $\overline{SO}$  input can be held HIGH until the SI control input is used. Following an SI pulse, data moves through the FIFO to the output stage, resulting in the DOR flag pulsing HIGH and a shift-out of data occurring. The  $\overline{SO}$  control must be made LOW before additional data can be shifted out (see Fig.10).

#### High-speed burst mode

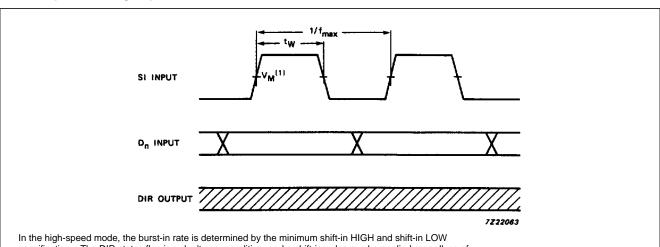

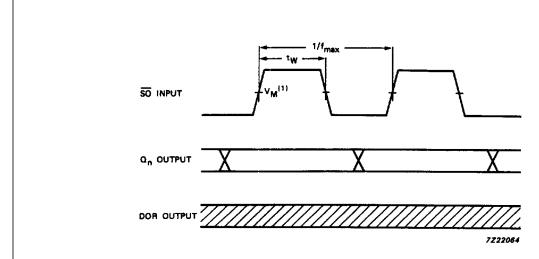

If it is assumed that the shift-in/shift-out pulses are not applied until the respective status flags are valid, it follows that the shift-in/shift-out rates are determined by the status flags. However, without the status flags a high-speed burst mode can be implemented. In this mode, the burst-in/burst-out rates are determined by the pulse widths of the shift-in/shift-out inputs and burst rates of 35 MHz can be obtained. Shift pulses can be applied without regard to the status flags but shift-in pulses that would overflow the storage capacity of the FIFO are not allowed (see Figs 11 and 12).

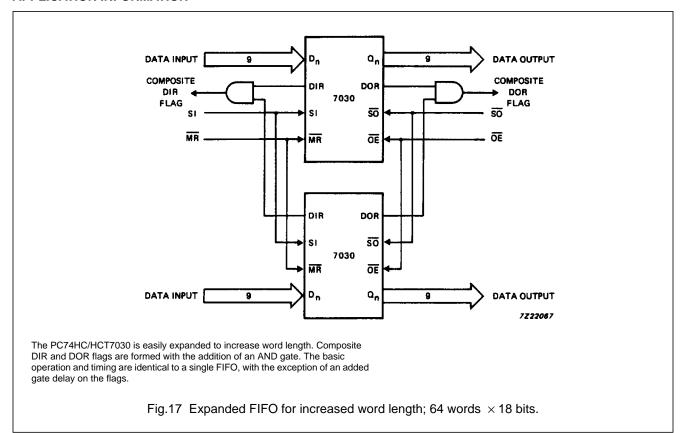

#### **Expanded format**

With the addition of a logic gate, the FIFO is easily expanded to increase word length (see Fig.17). The basic operation and timing are identical to a single FIFO, with the exception of an additional gate delay on the flag outputs. If during application, the following occurs:

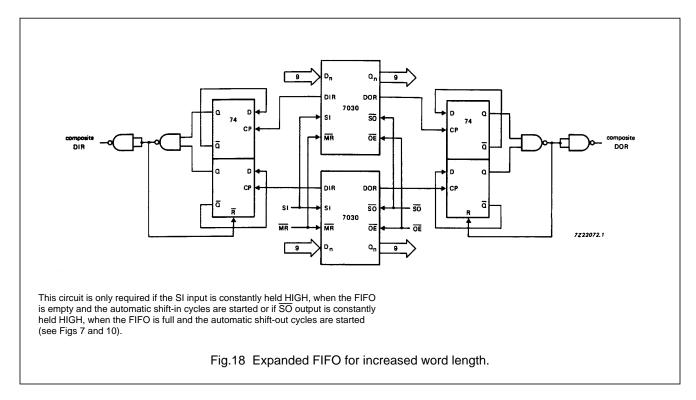

- SI is held HIGH when the FIFO is empty, some additional logic is required to produce a composite DIR pulse (see Figs 7 and 18).

- SO is held HIGH when the FIFO is full, some additional logic is required to produce a composite DOR pulse (see Figs 10 and 18).

Due to the part-to-part spread of the ripple through time, the flag signals of  $FIFO_A$  and  $FIFO_B$  will not always coincide and the AND-gate will not produce a composite flag signal. The solution is given in Fig.18.

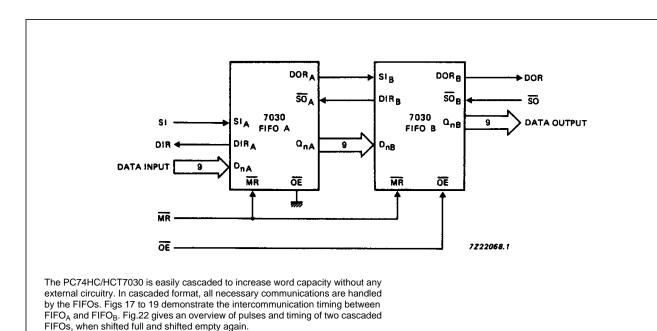

The "7030" is easily cascaded to increase the word capacity and no external components are needed. In the cascaded configuration, all necessary communications and timing are performed by the FIFOs. The intercommunication speed is determined by the minimum flag pulse widths and the flag delays. The data rate of cascaded devices is typically 25 MHz. Word-capacity can be expanded to and beyond 128-words  $\times$  9-bits (see Fig.19).

## 74HC/HCT7030

# 9-bit x 64-word FIFO register; 3-state

74HC/HCT7030

## DC CHARACTERISTICS FOR 74HC

For the DC characteristics see "74HC/HCT/HCU/HCMOS Logic Family Specifications".

Output capability: standard

I<sub>CC</sub> category: LSI

## **AC CHARACTERISTICS FOR 74HC**

$GND = 0 V; t_r = t_f = 6 ns; C_L = 50 pF$

|                                     |                                                         |               |                   | 7                  | Γ <sub>amb</sub> (° | C)               |                |                  |      | TEST CONDITIONS   |           |  |

|-------------------------------------|---------------------------------------------------------|---------------|-------------------|--------------------|---------------------|------------------|----------------|------------------|------|-------------------|-----------|--|

| CVMDOL                              | DADAMETER                                               |               |                   |                    | 74HC                | ;                |                |                  | UNIT |                   |           |  |

| SYMBOL                              | PARAMETER                                               |               | +25               |                    | -40 t               | o +85            | -40 to         | o +125           | UNII | V <sub>CC</sub>   | WAVEFORMS |  |

|                                     |                                                         | min.          | typ.              | max.               | min.                | max.             | min.           | max.             |      | (,,               |           |  |

| t <sub>PHL</sub> / t <sub>PLH</sub> | propagation delay MR to DIR, DOR                        |               | 69<br>25<br>20    | 210<br>42<br>36    |                     | 265<br>53<br>45  |                | 315<br>63<br>54  | ns   | 2.0<br>4.5<br>6.0 | Fig.8     |  |

| t <sub>PHL</sub> / t <sub>PLH</sub> | propagation delay<br>SI to DIR                          |               | 77<br>28<br>22    | 235<br>47<br>40    |                     | 295<br>59<br>50  |                | 355<br>71<br>60  | ns   | 2.0<br>4.5<br>6.0 | Fig.6     |  |

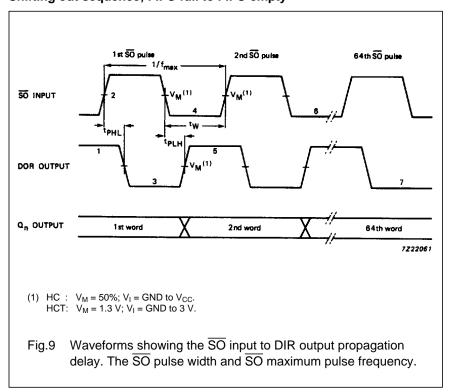

| t <sub>PHL</sub> / t <sub>PLH</sub> | propagation delay<br>SO to DOR                          |               | 102<br>37<br>30   | 315<br>63<br>54    |                     | 395<br>79<br>67  |                | 475<br>95<br>81  | ns   | 2.0<br>4.5<br>6.0 | Fig.9     |  |

| t <sub>PHL</sub> / t <sub>PLH</sub> | propagation delay DOR to Q <sub>n</sub>                 |               | 11<br>4<br>3      | 35<br>7<br>6       |                     | 45<br>9<br>8     |                | 55<br>11<br>9    | ns   | 2.0<br>4.5<br>6.0 | Fig.10    |  |

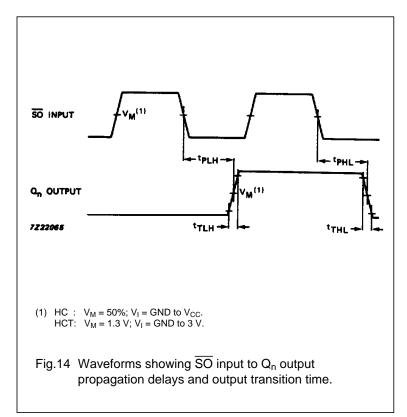

| t <sub>PHL</sub> / t <sub>PLH</sub> | propagation delay<br>SO to Q <sub>n</sub>               |               | 113<br>41<br>33   | 345<br>69<br>59    |                     | 430<br>86<br>73  |                | 520<br>104<br>88 | ns   | 2.0<br>4.5<br>6.0 | Fig.14    |  |

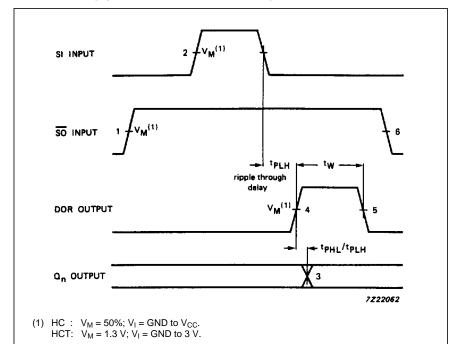

| t <sub>PLH</sub>                    | propagation delay/<br>ripple through delay<br>SI to DOR |               | 2.5<br>0.9<br>0.7 | 8.0<br>1.6<br>1.3  |                     | 10<br>2.0<br>1.6 |                | 12<br>2.4<br>1.9 | μs   | 2.0<br>4.5<br>6.0 | Fig.10    |  |

| t <sub>PLH</sub>                    | propagation delay/<br>bubble-up delay<br>SO to DIR      |               | 3.3<br>1.2<br>1.0 | 10.0<br>2.0<br>1.6 |                     | 12<br>2.5<br>2.0 |                | 15<br>3.0<br>2.4 | μs   | 2.0<br>4.5<br>6.0 | Fig.7     |  |

| t <sub>PZH</sub> / t <sub>PZL</sub> | 3-state output enable<br>OE to Q <sub>n</sub>           |               | 52<br>19<br>15    | 175<br>35<br>30    |                     | 220<br>44<br>37  |                | 265<br>53<br>45  | ns   | 2.0<br>4.5<br>6.0 | Fig.16    |  |

| t <sub>PHZ</sub> / t <sub>PLZ</sub> | 3-state output disable<br>OE to Q <sub>n</sub>          |               | 50<br>18<br>14    | 150<br>30<br>26    |                     | 190<br>38<br>33  |                | 225<br>45<br>38  | ns   | 2.0<br>4.5<br>6.0 | Fig.16    |  |

| t <sub>THL</sub> / t <sub>TLH</sub> | output transition time                                  |               | 19<br>7<br>6      | 75<br>15<br>13     |                     | 95<br>19<br>16   |                | 110<br>22<br>19  | ns   | 2.0<br>4.5<br>6.0 | Fig.14    |  |

| t <sub>W</sub>                      | SI pulse width<br>HIGH or LOW                           | 50<br>10<br>9 | 14<br>5<br>4      |                    | 65<br>13<br>11      |                  | 75<br>15<br>13 |                  | ns   | 2.0<br>4.5<br>6.0 | Fig.6     |  |

# 74HC/HCT7030

|                  |                                                        |                 |                   | -               | Γ <sub>amb</sub> (° |                 | TES              | TEST CONDITIONS |                                                                                                                                                                   |                   |                |

|------------------|--------------------------------------------------------|-----------------|-------------------|-----------------|---------------------|-----------------|------------------|-----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|----------------|

| 0)/11501         |                                                        |                 |                   |                 | 74HC                | ;               |                  |                 | NS 2.0 4.5 6.0  MHz 2.0 4.5 6.0  MHz 2.0 4.5 6.0  MHz 2.0 4.5 6.0 |                   |                |

| SYMBOL           | PARAMETER                                              |                 | +25               |                 | -40 t               | o +85           | -40 t            | o +125          |                                                                                                                                                                   | WAVEFORMS         |                |

|                  |                                                        | min.            | typ.              | max.            | min.                | max.            | min.             | max.            |                                                                                                                                                                   | ( ' /             |                |

| t <sub>W</sub>   | SO pulse width<br>HIGH or LOW                          | 100<br>20<br>17 | 33<br>12<br>10    |                 | 125<br>25<br>21     |                 | 150<br>30<br>26  |                 | ns                                                                                                                                                                | 4.5               | Fig.9          |

| t <sub>W</sub>   | DIR pulse width<br>HIGH                                | 10<br>5<br>4    | 47<br>17<br>14    | 145<br>29<br>25 | 8<br>4<br>3         | 180<br>36<br>31 | 8<br>4<br>3      | 220<br>44<br>38 | ns                                                                                                                                                                | 4.5               | Fig.7          |

| t <sub>W</sub>   | DOR pulse width<br>HIGH                                | 10<br>5<br>4    | 47<br>17<br>14    | 145<br>29<br>25 | 8<br>4<br>3         | 180<br>36<br>31 | 8<br>4<br>3      | 220<br>44<br>38 | ns                                                                                                                                                                | 4.5               | Fig.10         |

| t <sub>W</sub>   | MR pulse width LOW                                     | 70<br>14<br>12  | 22<br>8<br>6      |                 | 90<br>18<br>15      |                 | 105<br>21<br>18  |                 | ns                                                                                                                                                                | 4.5               | Fig.8          |

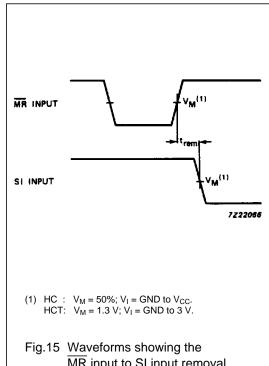

| t <sub>rem</sub> | removal time<br>MR to SI                               | 80<br>16<br>14  | 24<br>8<br>7      |                 | 100<br>20<br>17     |                 | 120<br>24<br>20  |                 | ns                                                                                                                                                                | 4.5               | Fig.15         |

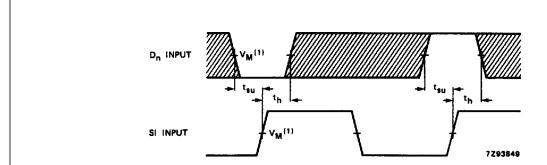

| t <sub>su</sub>  | set-up time<br>D <sub>n</sub> to SI                    | -35<br>-7<br>-6 | -36<br>-13<br>-10 |                 | -45<br>-9<br>-8     |                 | -55<br>-11<br>-9 |                 | ns                                                                                                                                                                | 4.5               | Fig.13         |

| t <sub>h</sub>   | hold time<br>D <sub>n</sub> to SI                      | 135<br>27<br>23 | 44<br>16<br>13    |                 | 170<br>34<br>29     |                 | 205<br>41<br>35  |                 | ns                                                                                                                                                                | 4.5               | Fig.13         |

| f <sub>max</sub> | maximum clock pulse<br>frequency<br>SI, SO burst mode  |                 | 9.9<br>30<br>36   |                 | 2.8<br>14<br>16     |                 | 2.4<br>12<br>14  |                 | MHz                                                                                                                                                               | 4.5               | Figs 11 and 12 |

| f <sub>max</sub> | maximum clock pulse<br>frequency<br>SI, SO using flags |                 | 9.9<br>30<br>36   |                 | 2.8<br>14<br>16     |                 | 2.4<br>12<br>14  |                 | MHz                                                                                                                                                               | 4.5               | Figs 6 and 9   |

| f <sub>max</sub> | maximum clock pulse<br>frequency<br>SI, SO cascaded    |                 | 7.6<br>23<br>27   |                 | 2.2<br>11<br>13     |                 | 1.8<br>9.2<br>11 |                 | MHz                                                                                                                                                               | 2.0<br>4.5<br>6.0 | Figs 6 and 9   |

# 9-bit x 64-word FIFO register; 3-state

74HC/HCT7030

## DC CHARACTERISTICS FOR 74HCT

For the DC characteristics see "74HC/HCT/HCU/HCMOS Logic Family Specifications".

Output capability: standard

I<sub>CC</sub> category: LSI

## Note to HCT types

The value of additional quiescent supply current ( $\Delta I_{CC}$ ) for a unit load of 1 is given in the family specifications. To determine  $\Delta I_{CC}$  per input, multiply this value by the unit load coefficient shown in the table below.

| INPUT          | UNIT LOAD COEFFICIENT |

|----------------|-----------------------|

| ŌĒ             | 1.00                  |

| SI             | 1.50                  |

| D <sub>n</sub> | 0.75                  |

| MR             | 1.50                  |

| SO             | 1.50                  |

## **AC CHARACTERISTICS FOR 74HCT**

$GND = 0 V; t_r = t_f = 6 ns; C_L = 50 pF$

|                                     |                                                        |      |      | •    | T <sub>amb</sub> (' | °C)    |        |      |      | TEST CONDITIONS |           |  |

|-------------------------------------|--------------------------------------------------------|------|------|------|---------------------|--------|--------|------|------|-----------------|-----------|--|

| SYMBOL                              | PARAMETER                                              |      |      |      | 74HC                | т      |        |      | UNIT |                 |           |  |

| STWIBOL                             | PARAMETER                                              |      | +25  |      | -40 t               | to +85 | –40 to | +125 | UNII | V <sub>CC</sub> | WAVEFORMS |  |

|                                     |                                                        | min. | typ. | max. | min.                | max.   | min.   | max. |      | (-,             |           |  |

| t <sub>PHL</sub> / t <sub>PLH</sub> | propagation delay MR to DIR, DOR                       |      | 30   | 51   |                     | 53     |        | 63   | ns   | 4.5             | Fig.8     |  |

| t <sub>PHL</sub> / t <sub>PLH</sub> | propagation delay<br>SI to DIR                         |      | 29   | 49   |                     | 61     |        | 74   | ns   | 4.5             | Fig.6     |  |

| t <sub>PHL</sub> / t <sub>PLH</sub> | propagation delay<br>SO to DOR                         |      | 39   | 67   |                     | 84     |        | 101  | ns   | 4.5             | Fig.9     |  |

| t <sub>PHL</sub> / t <sub>PLH</sub> | propagation delay<br>SO to Q <sub>n</sub>              |      | 46   | 78   |                     | 98     |        | 117  | ns   | 4.5             | Fig.14    |  |

| t <sub>PHL</sub> / t <sub>PLH</sub> | propagation delay DOR to Q <sub>n</sub>                |      | 7    | 12   |                     | 15     |        | 18   | ns   | 4.5             | Fig.10    |  |

| t <sub>PLH</sub>                    | propagation delay/ripple<br>through delay<br>SI to DOR |      | 0.9  | 1.6  |                     | 2.0    |        | 2.4  | μs   | 4.5             | Fig.10    |  |

| t <sub>PLH</sub>                    | propagation delay/<br>bubble-up delay<br>SO to DIR     |      | 1.2  | 2.0  |                     | 2.5    |        | 3.0  | μs   | 4.5             | Fig.7     |  |

| t <sub>PZH</sub> / t <sub>PZL</sub> | 3-state output enable<br>OE to Q <sub>n</sub>          |      | 20   | 35   |                     | 44     |        | 53   | ns   | 4.5             | Fig.16    |  |

| t <sub>PHZ</sub> / t <sub>PLZ</sub> | 3-state output disable<br>OE to Q <sub>n</sub>         |      | 19   | 35   |                     | 44     |        | 53   | ns   | 4.5             | Fig.16    |  |

| t <sub>THL</sub> / t <sub>TLH</sub> | output transition time                                 |      | 7    | 15   |                     | 19     |        | 22   | ns   | 4.5             | Fig.14    |  |

# 74HC/HCT7030

| SYMBOL           |                                                        |            |      |      | T <sub>amb</sub> ( | °C)    |        |      |      | TEST CONDITIONS                                |                |

|------------------|--------------------------------------------------------|------------|------|------|--------------------|--------|--------|------|------|------------------------------------------------|----------------|

|                  | DADAMETED                                              |            |      |      | 74HC               | T      |        |      |      | Vcc (V)  4.5  4.5  4.5  4.5  4.5  4.5  4.5  4. |                |

|                  | PARAMETER                                              |            | +25  |      | -40 t              | to +85 | -40 to | +125 | UNIT |                                                | WAVEFORMS      |

|                  |                                                        | min.       | typ. | max. | min.               | max.   | min.   | max. |      | (',                                            |                |

| t <sub>W</sub>   | SI pulse width<br>HIGH or LOW                          | 12         | 6    |      | 15                 |        | 18     |      | ns   | 4.5                                            | Fig.6          |

| t <sub>W</sub>   | SO pulse width<br>HIGH or LOW                          | 15         | 9    |      | 19                 |        | 22     |      | ns   | 4.5                                            | Fig.9          |

| t <sub>W</sub>   | DIR pulse width<br>HIGH                                | 7          | 22   | 37   | 6                  | 46     | 6      | 56   | ns   | 4.5                                            | Fig.7          |

| t <sub>W</sub>   | DOR pulse width<br>HIGH                                | 6          | 20   | 35   | 5                  | 44     | 5      | 53   | ns   | 4.5                                            | Fig.10         |

| t <sub>W</sub>   | MR pulse width LOW                                     | 18         | 10   |      | 23                 |        | 27     |      | ns   | 4.5                                            | Fig.8          |

| t <sub>rem</sub> | removal time MR to SI                                  | 18         | 10   |      | 23                 |        | 27     |      | ns   | 4.5                                            | Fig.15         |

| t <sub>su</sub>  | set-up time<br>D <sub>n</sub> to SI                    | <b>-</b> 5 | -16  |      | -4                 |        | -4     |      | ns   | 4.5                                            | Fig.13         |

| t <sub>h</sub>   | hold time<br>D <sub>n</sub> to SI                      | 30         | 18   |      | 38                 |        | 45     |      | ns   | 4.5                                            | Fig.13         |

| f <sub>max</sub> | maximum clock pulse<br>frequency<br>SI, SO burst mode  | 15         | 26   |      | 12                 |        | 10     |      | MHz  | 4.5                                            | Figs 11 and 12 |

| f <sub>max</sub> | maximum clock pulse<br>frequency<br>SI, SO using flags | 15         | 26   |      | 12                 |        | 10     |      | MHz  | 4.5                                            | Figs 6 and 9   |

| f <sub>max</sub> | maximum clock pulse<br>frequency<br>SI, SO cascaded    | 13         | 22   |      | 10                 |        | 8.6    |      | MHz  | 4.5                                            | Figs 6 and 9   |

## 9-bit x 64-word FIFO register; 3-state

## 74HC/HCT7030

#### **AC WAVEFORMS**

#### Shifting in sequence FIFO empty to FIFO full

## Notes to Fig.6

- 1. DIR initially HIGH; FIFO is prepared for valid data.

- 2. SI set HIGH; data loaded into input stage.

- 3. DIR drops LOW, input stage "busy".

- 4. SI set LOW; data from first location "ripple through".

- DIR goes HIGH, status flag indicates FIFO prepared for additional data.

- 6. Repeat process to load 2nd word through to 64th word into FIFO.

- DIR remains LOW; with attempt to shift into full FIFO, no data transfer occurs.

## With FIFO full; SI held HIGH in anticipation of empty location

#### Notes to Fig.7

- 1. FIFO is initially full, shift-in is held HIGH.

- SO pulse; data in the output stage is unloaded, "bubble-up process of empty locations begins".

- DIR HIGH; when empty location reached input stage, flag indicates FIFO is prepared for data input.

- DIR returns to LOW; FIFO is full again.

- SI brought LOW; necessary to complete shift-in process, DIR remains LOW, because FIFO is full.

## 9-bit x 64-word FIFO register; 3-state

## 74HC/HCT7030

## Master reset applied with FIFO full

#### Notes to Fig.8

- 1. DIR LOW, output ready HIGH; assume FIFO is full.

- 2. MR pulse LOW; clears FIFO.

- 3. DIR goes HIGH; flag indicates input prepared for valid data.

- DOR drops LOW; flag indicates FIFO empty.

## Shifting out sequence; FIFO full to FIFO empty

#### Notes to Fig.9

- 1. DOR HIGH; no data transfer in progress, valid data is present at output stage.

- SO set HIGH; results in DOR going LOW.

- 3. DOR drops LOW; output stage "busy".

- 4. SO is set LOW; data in the input stage is unloaded, and new data replaces it as empty location "bubbles-up" to input stage.

- DOR goes HIGH; transfer process completed, valid data present at output after the specified propagation delay.

- Repeat process to unload the 3rd through to the 64th word from FIFO.

- 7. DOR remains LOW; FIFO is empty.

## 9-bit x 64-word FIFO register; 3-state

## 74HC/HCT7030

## With FIFO empty; SO is held HIGH in anticipation

Fig.10 Waveforms showing ripple through delay SI input to DOR output, DOR output pulse width and propagation delay from the DOR pulse to the  $Q_n$  output.

#### Notes to Fig.10

- 1. FIFO is initially empty,  $\overline{SO}$  is held HIGH.

- SI pulse; loads data into FIFO and initiates ripple through process.

- 3. DOR flag signals the arrival of valid data at the output stage.

- Output transition; data arrives at output stage after the specified propagation delay between the rising edge of the DOR pulse to the Q<sub>n</sub> output.

- 5. DOR goes LOW; FIFO is empty again.

- SO set LOW; necessary to complete shift-out process. DOR remains LOW, because FIFO is empty.

#### Shift-in operation; high-speed burst mode

In the high-speed mode, the burst-in rate is determined by the minimum shift-in HIGH and shift-in LOW specifications. The DIR status flag is a don't care condition, and a shift-in pulse can be applied regardless of the flag. A SI pulse which would overflow the storage capacity of the FIFO is ignored.

(1) HC :  $V_M = 50\%$ ;  $V_I = GND$  to  $V_{CC}$ . HCT:  $V_M = 1.3$  V;  $V_I = GND$  to 3 V.

Fig.11 Waveforms showing SI minimum pulse width and SI maximum pulse frequency, in high-speed shift-in burst mode.

74HC/HCT7030

## Shift-out operation; high-speed burst mode

In the high-speed mode, the burst-out rate is determined by the minimum shift-out HIGH and shift-out LOW specifications. The DOR flag is a don't care condition and a SO pulse can be applied without regard to the flag.

(1) HC :  $V_M$  = 50%;  $V_I$  = GND to  $V_{CC}$ . HCT:  $V_M$  = 1.3 V;  $V_I$  = GND to 3 V.

Fig.12 Waveforms showing SO minimum pulse width and maximum pulse frequency, in high-speed shift-out burst mode.

The shaded areas indicate when the input is permitted to change for predictable output performance.

(1) HC :  $V_M$  = 50%;  $V_I$  = GND to  $V_{CC}$ . HCT:  $V_M$  = 1.3 V;  $V_I$  = GND to 3 V.

Fig.13 Waveforms showing hold and set-up times for D<sub>n</sub> input to SI input.

## 9-bit x 64-word FIFO register; 3-state

## 74HC/HCT7030

MR input to SI input removal time.

## 74HC/HCT7030

## **APPLICATION INFORMATION**

74HC/HCT7030

## **Expanded format**

Fig.19 shows two cascaded FIFOs providing a capacity of 128 words  $\times$  9 bits.

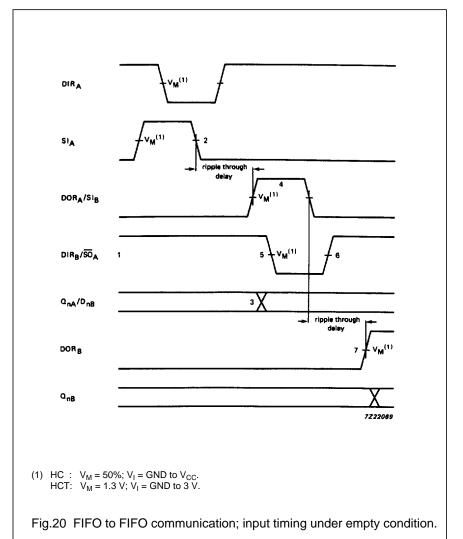

Fig.20 shows the signals on the nodes of both FIFOs after the application of a SI pulse, when both FIFOs are initially empty. After a rippled through delay, data arrives at the output of FIFO<sub>A</sub>. Due to  $\overline{SO}_A$  being HIGH, a DOR pulse is generated. The requirements of SI<sub>B</sub> and D<sub>nB</sub> are satisfied by the DOR<sub>A</sub> pulse width and the timing between the rising edge of DOR<sub>A</sub> and Q<sub>nA</sub>. After a second ripple through delay, data arrives at the output of FIFO<sub>B</sub>.

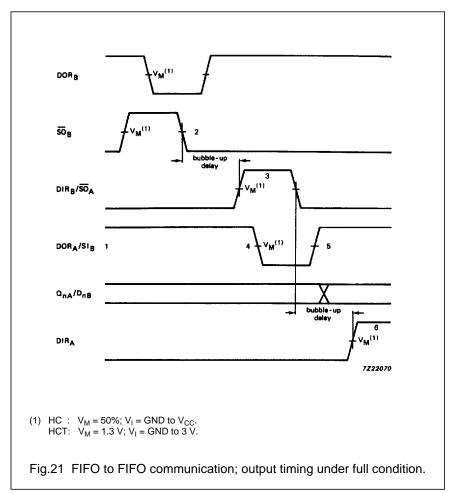

Fig.21 shows the signals on the nodes of both FIFOs after the application of a  $\overline{SO}_B$  pulse, when both FIFOs are initially full. After a bubble-up delay a DIR<sub>B</sub> pulse is generated, which acts as a  $\overline{SO}_A$  pulse for FIFO<sub>A</sub>. One word is transferred from the output of FIFO<sub>A</sub> to the input of FIFO<sub>B</sub>. The requirements of the  $\overline{SO}_A$  pulse for FIFO<sub>A</sub> is satisfied by the pulse width of DOR<sub>B</sub>. After a second bubble-up delay an empty space arrives at D<sub>nA</sub>, at which time DIR<sub>A</sub> goes HIGH. Fig.22 shows the waveforms at all external nodes of both FIFOs during a complete shift-in and shift-out sequence.

Fig.19 Cascading for increased word capacity; 128 words × 9 bits.

## 9-bit x 64-word FIFO register; 3-state

## 74HC/HCT7030

## Notes to Fig.20

- FIFO<sub>A</sub> and FIFO<sub>B</sub> initially empty, SO<sub>A</sub> held HIGH in anticipation of data.

- Load one word into FIFO<sub>A</sub>; SI pulse applied, results in DIR pulse.

- Data out A/data in B transition; valid data arrives at FIFOA output stage after a specified delay of the DOR flag, meeting data input set-up requirements of FIFOB.

- DOR<sub>A</sub> and SI<sub>B</sub> pulse HIGH; (ripple through delay after SI<sub>A</sub> LOW) data is unloaded from FIFO<sub>A</sub> as a result of the data output ready pulse, data is shifted into FIFO<sub>B</sub>.

- DIR<sub>B</sub> and SO<sub>A</sub> go LOW; flag indicates input stage of FIFO<sub>B</sub> is busy, shift-out of FIFO<sub>A</sub> is complete.

- DIR<sub>B</sub> and SO<sub>A</sub> go HIGH automatically; the input stage of FIFO<sub>B</sub> is again able to receive data, SO is held HIGH in anticipation of additional data.

- DOR<sub>B</sub> goes HIGH; (ripple through delay after SI<sub>B</sub> LOW) valid data is present one propagation delay later at the FIFO<sub>B</sub> output stage.

## 9-bit x 64-word FIFO register; 3-state

## 74HC/HCT7030

#### Notes to Fig.21

- FIFO<sub>A</sub> and FIFO<sub>B</sub> initially full, SI<sub>B</sub> held HIGH in anticipation of shifting in new data as empty location bubbles-up.

- Unload one word from FIFO<sub>B</sub>;

SO pulse applied, results in DOR pulse.

- DIR<sub>B</sub> and SO<sub>A</sub> pulse HIGH; (bubble-up delay after SO<sub>B</sub> LOW) data is loaded into FIFO<sub>B</sub> as a result of the DIR pulse, data is shifted out of FIFO<sub>A</sub>.

- DOR<sub>A</sub> and SI<sub>B</sub> go LOW; flag indicates the output stage of FIFO<sub>A</sub> is busy, shift-in to FIFO<sub>B</sub> is complete.

- DOR<sub>A</sub> and SI<sub>B</sub> go HIGH; flag indicates valid data is again available at FIFO<sub>A</sub> output stage, SI<sub>B</sub> is held HIGH, awaiting bubble-up of empty location.

- DIR<sub>A</sub> goes <u>HIGH</u>; (bubble-up delay after <u>SO<sub>A</sub></u> LOW) an empty location is present at input stage of FIFO<sub>A</sub>.

## 9-bit x 64-word FIFO register; 3-state

## 74HC/HCT7030

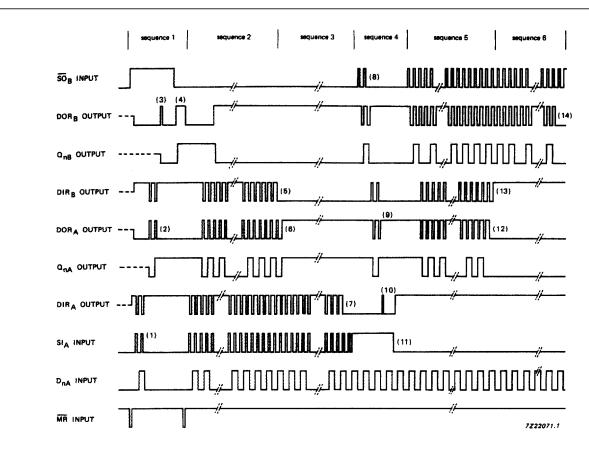

Sequence 1 (Both FIFOs empty, starting shift-in process):

After a  $\overline{\text{MR}}$  pulse has been applied FIFO<sub>A</sub> and FIFO<sub>B</sub> are empty. The DOR flags of FIFO<sub>A</sub> and FIFO<sub>B</sub> go LOW due to no valid data being present at the outputs. The DIR flags are set HIGH due to the FIFOs being ready to accept data.  $\overline{\text{SO}}_B$  is held HIGH and two SI<sub>A</sub> pulses are applied (1). These pulses allow two data words to ripple through to the output stage of FIFO<sub>A</sub> and to the input stage of FIFO<sub>B</sub> (2). When data arrives at the output of FIFO<sub>B</sub>, a DOR<sub>B</sub> pulse is generated (3). When  $\overline{\text{SO}}_B$  goes LOW, the first bit is shifted out and a second bit ripples through to the output after which DOR<sub>B</sub> goes HIGH (4).

Sequence 2 (FIFO<sub>B</sub> runs full):

After the  $\overline{\text{MR}}$  pulse, a series of 64 SI pulses are applied. When 64 words are shifted in, DIR<sub>B</sub> remains LOW due to FIFO<sub>B</sub> being full (5). DOR<sub>A</sub> goes LOW due to FIFO<sub>A</sub> being empty.

Sequence 3 (FIFO<sub>A</sub> runs full):

When 65 words are shifted in, DOR<sub>A</sub> remains HIGH due to valid data remaining at the output of FIFO<sub>A</sub>. Q<sub>nA</sub> remains HIGH, being the polarity of the 65th data word (6). After the 128th SI pulse, DIR remains LOW and both FIFOs are full (7). Additional pulses have no effect.

Sequence 4 (Both FIFOs full, starting shift-out process):

$SI_A$  is held HiGH and two  $\overline{SO}_B$  pulses are applied (8). These pulses shift out two words and thus allow two empty locations to bubble-up to the input stage of FIFO<sub>B</sub>, and proceed to FIFO<sub>A</sub> (9). When the first empty location arrives at the input of FIFO<sub>A</sub>, a DIR<sub>A</sub> pulse is generated (10) and a new word is shifted into FIFO<sub>A</sub>.  $SI_A$  is made LOW and now the second empty location reaches the input stage of FIFO<sub>A</sub>, after which DIR<sub>A</sub> remains HIGH (11).

Sequence 5 (FIFO<sub>A</sub> runs empty):

At the start of sequence 5 FIFO<sub>A</sub> contains 63 valid wor<u>ds</u> due to two words being shifted <u>out</u> and one word being shifted in in sequence 4. An additional series of  $\overline{SO}_B$  pulses are applied. After 63  $\overline{SO}_B$  pulses, all words from FIFO<sub>A</sub> are shifted into FIFO<sub>B</sub>. DOR<sub>A</sub> remains LOW (12).

Sequence 6 ( $\underline{\mathsf{FIFO}}_\mathsf{B}$  runs empty):

After the next  $\overline{SO}_B$  pulse, DIRB remains HIGH due to the input stage of FIFOB being empty (13). After another 63  $\overline{SO}_B$  pulses, DORB remains LOW due to both FIFOs being empty (14). Additional  $\overline{SO}_B$  pulses have no effect. The last word remains available at the output  $Q_n$ .

Fig.22 Waveforms showing the functionality and intercommunication between two FIFOs (refer to Fig.19).

# 9-bit x 64-word FIFO register; 3-state

74HC/HCT7030

## **PACKAGE OUTLINES**

See "74HC/HCT/HCU/HCMOS Logic Package Outlines".

# **Mouser Electronics**

**Authorized Distributor**

Click to View Pricing, Inventory, Delivery & Lifecycle Information:

## NXP:

<u>74HC7030D 74HC7030D-T 74HC7030N 74HCT7030D 74HCT7030D-T 74HCT7030N 74HC7030N,652 74HCT7030N,112</u>