# TC8569AF

## Floppy Disk Controller

### 1. GENERAL DESCRIPTION

TC8569AF is a single chip LSI for Floppy Disk Controller, which has VFO and other circuits with FDC chip for interfacing a processor to floppy disk drive and supports data rates up to 1Mbps.

### 2. FEATURES

- Si-gate CMOS single chip LSI

- Single +5V power supply

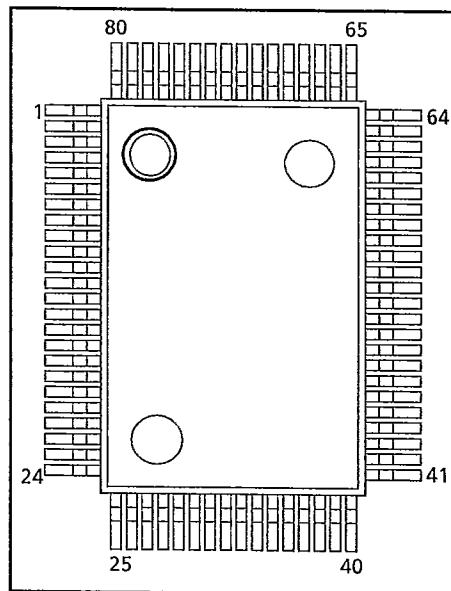

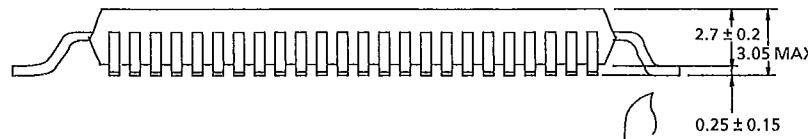

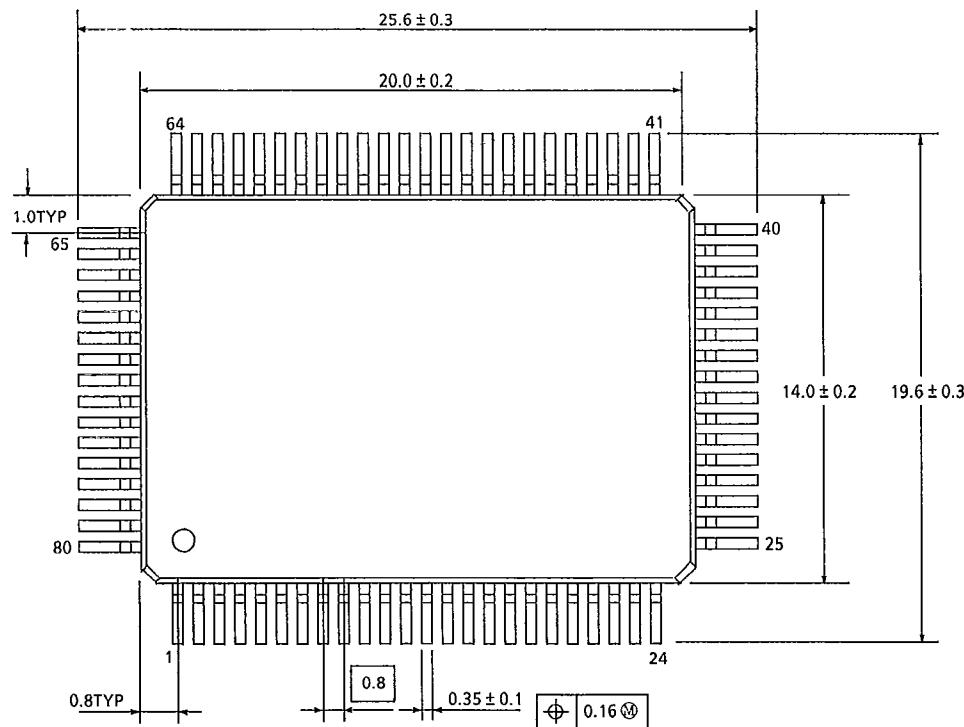

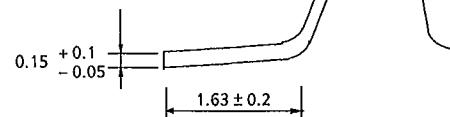

- 80pin plastic flat package

- Compatible with 8080 system data and control buses

- Built-in VFO circuit

- Standby function for battery operation.

- MFM recording formats ( 1M / 500K / 250Kbps )

- FM recording formats ( 250k / 125Kbps )

- Built-in write pre-compensation circuit

- Motor enable control for 2 drives

- Built-in address decoder

- Multi-sector data transfer

- Multi-track data transfer

- Direct interface to FDD with CMOS type interface system

- Programmable step rate time

- Compatible with IBM diskette 1 and 2

- Including CRC check function

( $X^{16} + X^{12} + X^5 + 1$ )

- DMA / Non-DMA ( interrupt ) data transfer

# FLOPPY DISK CONTROLLER

□ TC8569AF is an improvement on the TC8569F. The differences between them are as follows.

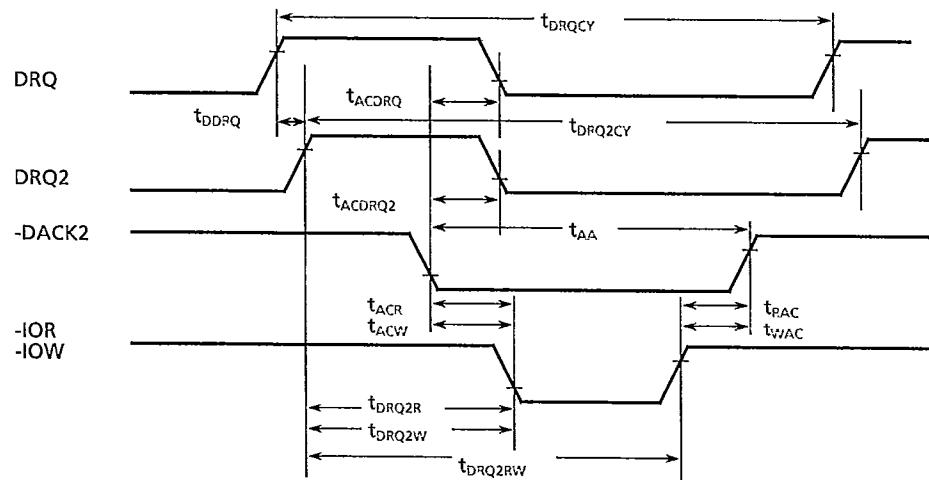

· DMA interface

TC8569F has the bug that DMA data transfer hangs up at using the DMA controller in verify mode [only -DACK2 is applied to FDC without -IOR and -IOW replying DRQ2], because DRQ2 is not reset.

DRQ2 is reset only by being applied -DACK2 and -IOR or -IOW at the same time. At using DAM controller in verify mode DMA controller applied only -DACK2 to FDC and therefore this trouble occurs.

TC8569AF resolves this problem. The verify mode of DMA controller is available.

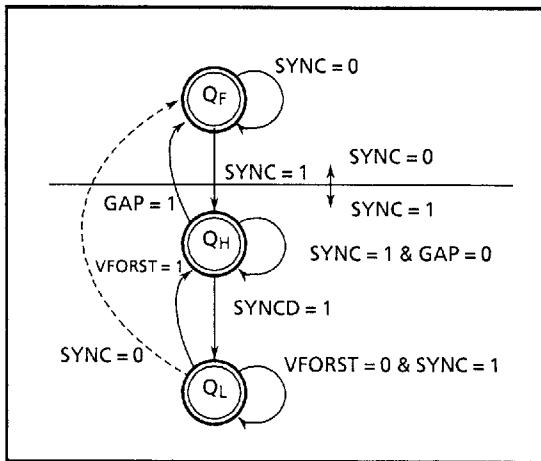

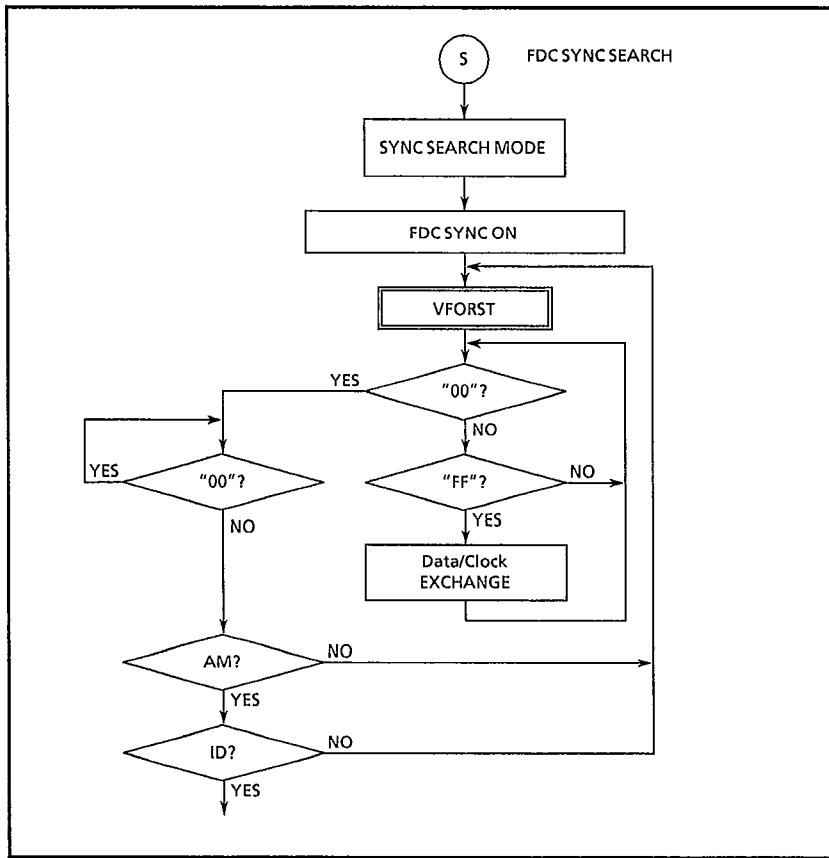

· VFO part

TC8569F's built-in VFO has the bug to decrease compatibility with IBM PC's FDC circuit. TC8569F can hardly read the first sector when the all of the following conditions are satisfied.

- ① Adopting a record format which doesn't include a certain data pattern to re-detect Sync within, from Index position to the first sector.

- ② Using FDC VFO in 2-filter mode

- ③ The first half of the sector data just before Index of the track is FF16 pattern.

TC8569AF improves this problem. Using TC8569AF in 2-filter mode, such a problem doesn't occur. TC8569AF has the same specification as TC8569F except the above two points.

## 3. FDC APPLICATION SYSTEM

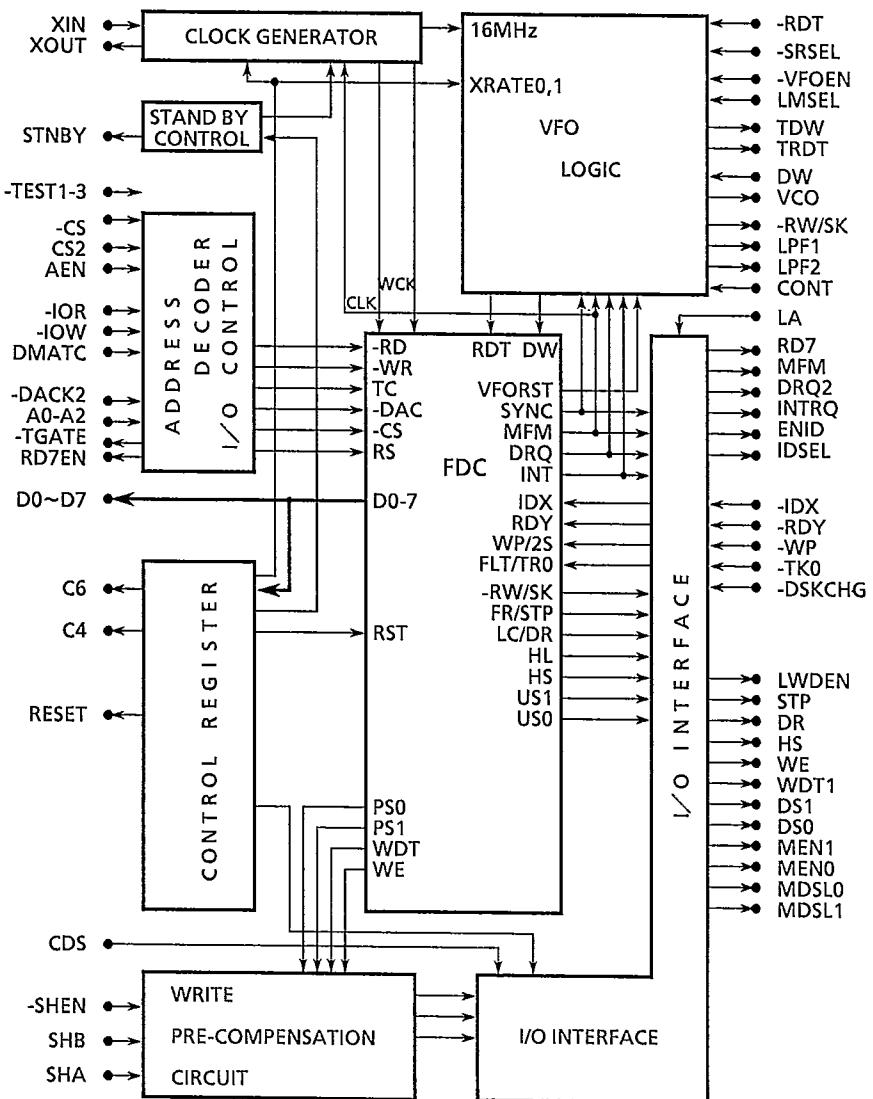

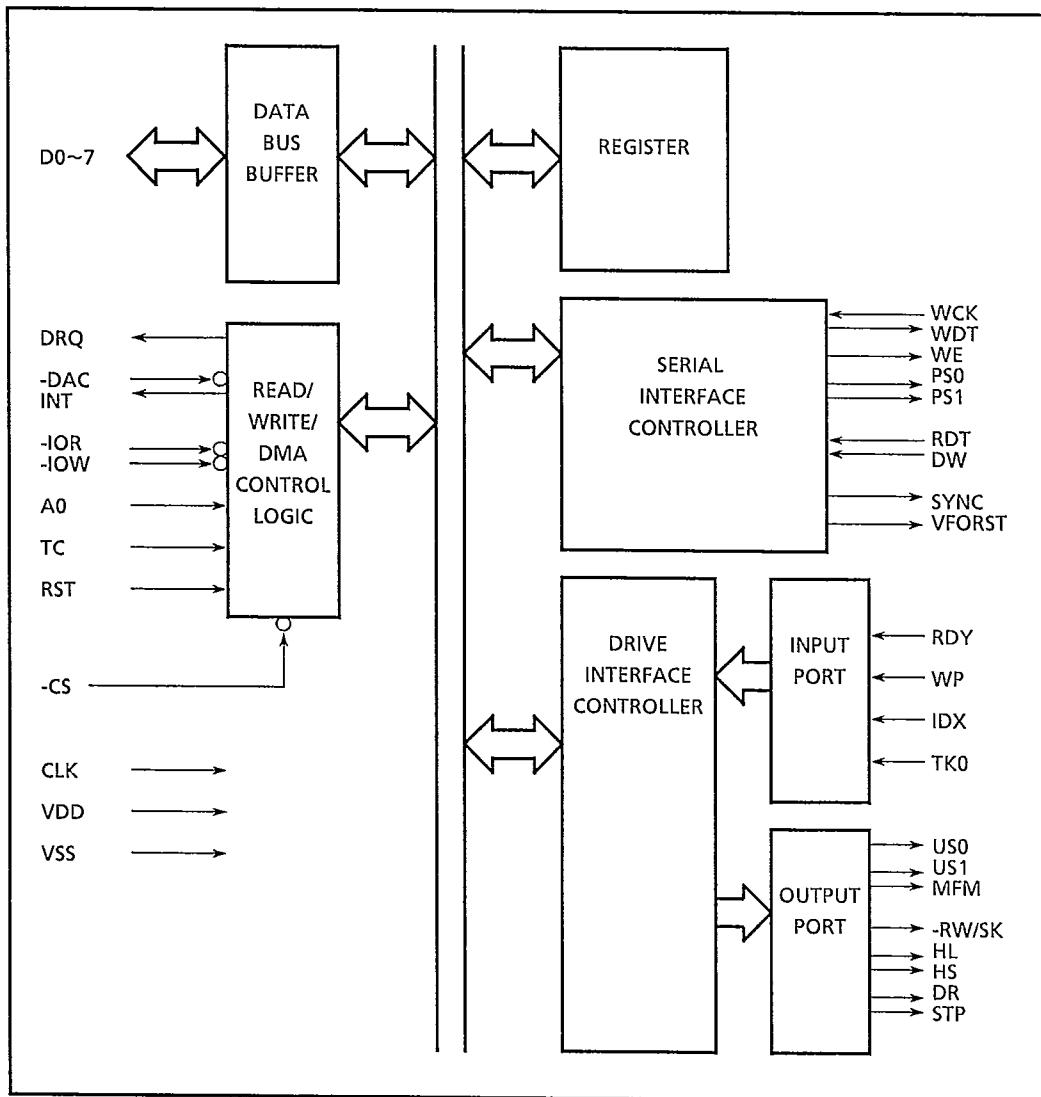

## 3.1 FDC BLOCK DIAGRAM

# FLOPPY DISK CONTROLLER

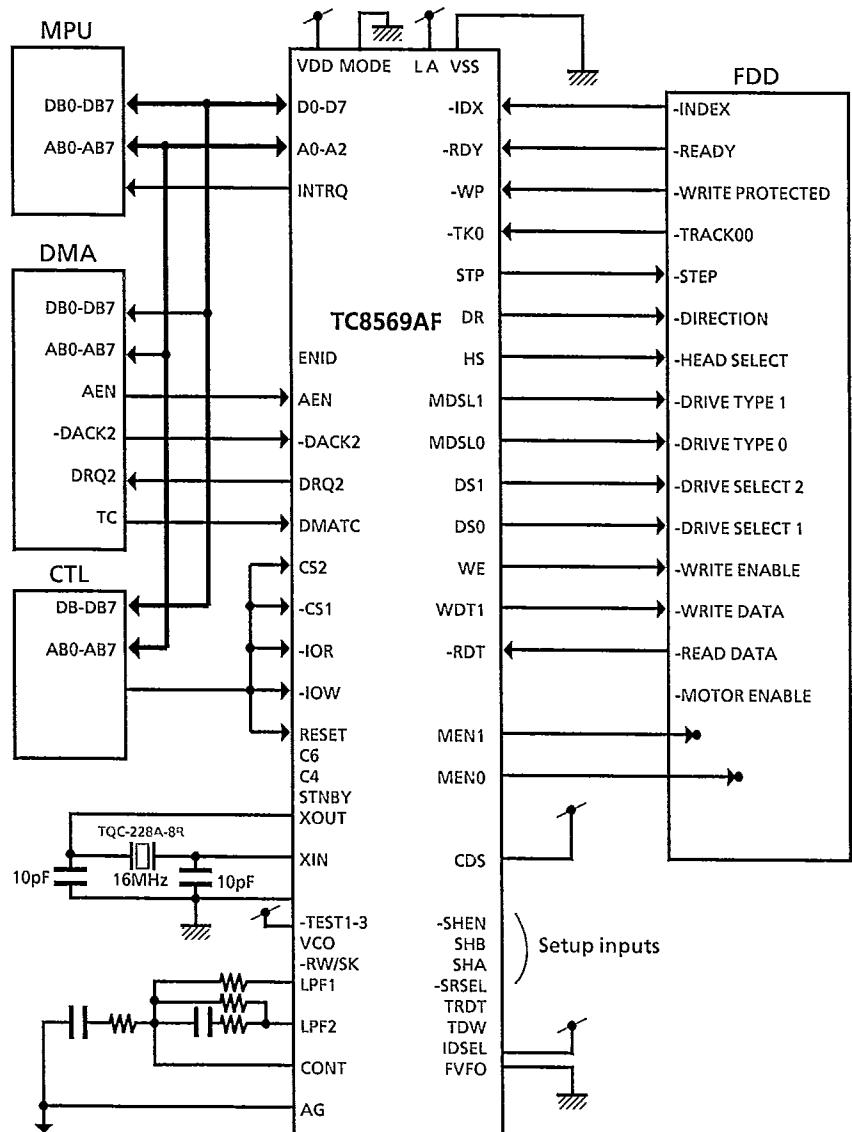

## 3.2 APPLICATION SYSTEM 1

TC8569AF corresponds with each floppy by changing value of D0 and D1 (XRATE0, XRATE1) on control register 2. TABLE 3.2 shows the correlation between XRATE0, XRATE1 and these floppys.

TABLE 3.2

| XRATE1 | XRATE0 | FLOPPY TYPE                     | CLOCK FREQ. OF INTERNAL FDC | TRANSFER RATE |

|--------|--------|---------------------------------|-----------------------------|---------------|

| 0      | 0      | Standard floppy                 | 8MHz                        | 500Kbps       |

| 0      | 1      | -                               | -                           | -             |

| 1      | 0      | Mini floppy                     | 4MHz                        | 250Kbps       |

| 1      | 1      | Perpendicular magnetized floppy | 16MHz                       | 1 Mbps        |

This technical data is only described feature of floppys (Standard floppy, Mini floppy and Perpendicular Magnetized floppy). It's no mention of these floppy size.

|                                    |                                                                                                          |

|------------------------------------|----------------------------------------------------------------------------------------------------------|

| 1. Standard floppy                 | 2HD type or 8 inch floppy<br>MFM recording formats (8MHz/500Kbps)<br>FM recording formats (8MHz/125Kbps) |

| 2. Mini floppy                     | 2D or 2DD type floppy<br>MFM recording formats (4MHz/250Kbps)<br>FM recording formats (4MHz/125Kbps)     |

| 3. Perpendicular Magnetized floppy | 2ED type floppy<br>MFM recording formats (1Mbps)<br>FM recording formats (not supported)                 |

## 3.3 APPLICATION SYSTEM 2

## 3.3.1 ALTERNATIVE FILTER MODE

## FLOPPY DISK CONTROLLER

## 3.3.2 FIXED FILTER MODE

TC8569AF-6

110989

828

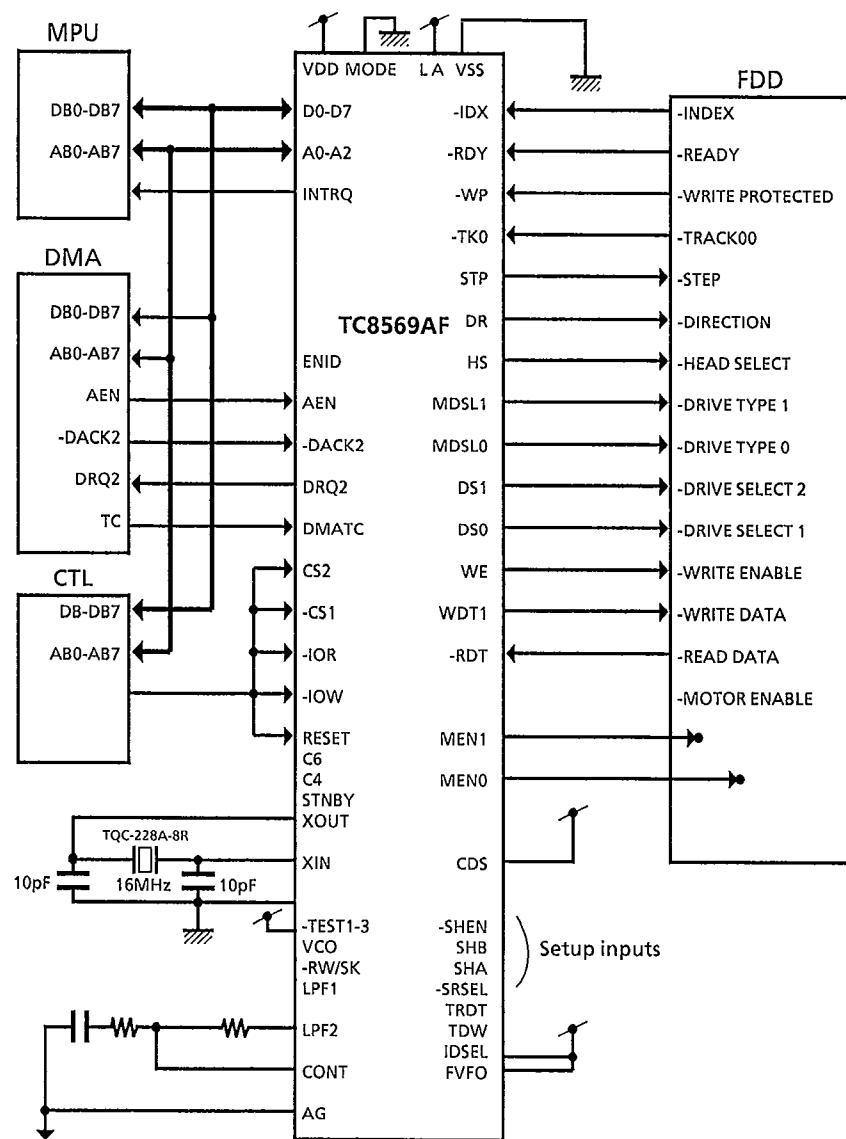

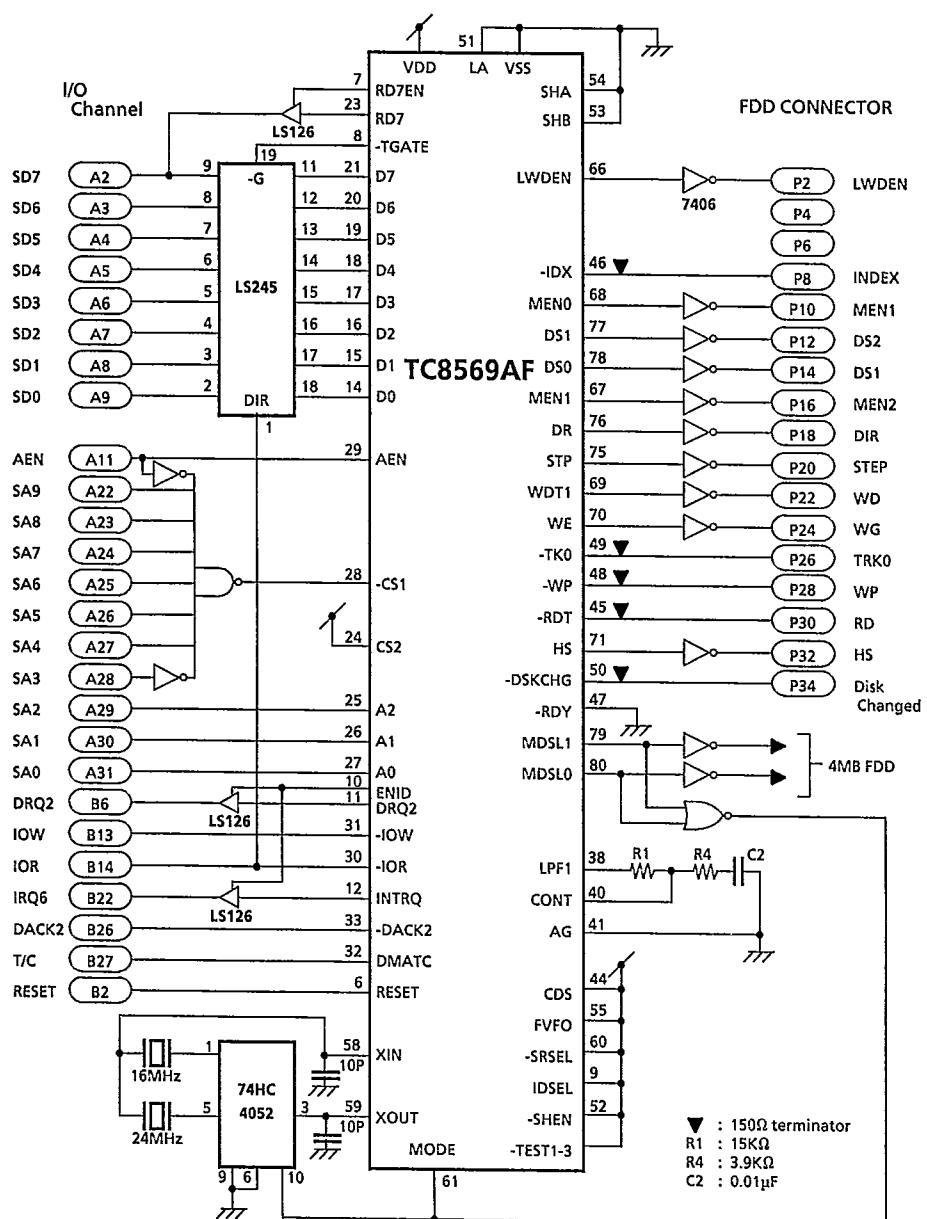

### 3.4 APPLICATION for INTERFACING to IBM PC/AT

TC8569AF has the compatible registers in the floppy controller board of the PC/AT that are CONTROL REGISTER 0 for the Digital Output Register (DOR) and CONTROL REGISTER 2 for the Data Rate Register (DRR) and Digital Input Register (DIR). Signals SA3 through SA9 and AEN in the slot of the PC/AT's system board are decoded and the decoded signal is applied to -CS1 input to be chosen 3F0H-3F7H address space to TC8569AF.

TC8569AF can support 300Kbps data transfer rate by 24MHz system clock and setting MODE input to "High". The content of CONTROL REGISTER 2 is as following table when the system clock is 24MHz and "High Level" is applied to MODE input.

TABLE 3.4 CONTENT of CONTROL REGISTER 2 (XIN = 24MHz , MODE = "High Level")

| XRATE1 | XRATE0 | FLOPPY          | SYSTEM CLOCK<br>of FDC PART | TRANSFER<br>RATE |

|--------|--------|-----------------|-----------------------------|------------------|

| 0      | 0      | Standard Floppy | 8MHz                        | 500Kbps          |

| 0      | 1      | Mini Floppy     | 4.8MHz                      | 300Kbps *        |

| 1      | 0      | Mini Floppy     | 4MHz                        | 250Kbps          |

| 1      | 1      | —               | —                           | —                |

\* : FM format is not supported at 300Kbps.

The typical application circuit of the floppy disk controller board for the PC/AT is shown in FIG.3.4b.

In this application circuit, 1Mbps, 500Kbps, 300Kbps and 250Kbps can be supported. The extra reset routine is necessary to expect a correct operation when XRATE1 and XRATE0 are changed. This is because that some glitches are generated when the system clock or MODE input level is changed. The extra reset is not necessary to use TC8569AF in a fixed mode (MODE input and the system clock are not changed during the operation).

-RDY input is connected to "Low level" in this application circuit when you should pay attention to the flowing item. The ready flag in the FDC block is set to not-ready after the FDC reset is released. Then four interrupt factors occur when FDC completes the drive scanning one cycle to detect the change of ready line against the four drives. Therefore, SENSE INTERRUPT STATUS COMMAND should be issued four times to reset the interrupt factors.

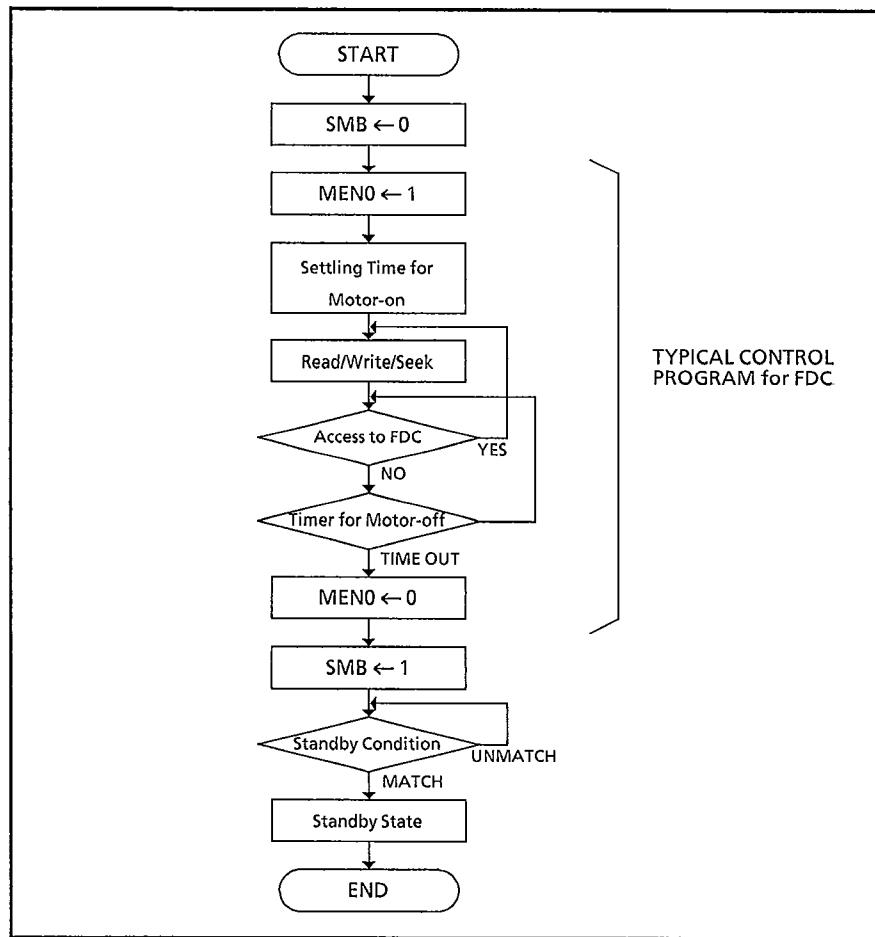

As commenting in the chapter 3.5, you should pay attention to the difference between the internal FDC of TC8569AF and the conventional type of FDC in programing the application software. If you use the standby mode, the control program for FDC should be modified as follow.

The state of the CONTROL REGISTER 0 has no relation to fulfill the standby condition. Therefore, you should insert the additional procedure to set SMB bit in the CONTROL REGISTER 1 after the motor-off routine and to reset SMB bit before the motor-on routine (Cf. FIG.3.4a)

## FLOPPY DISK CONTROLLER

FIG.3.4a FLOW CHART for STANDBY CONTROL

## FLOPPY DISK CONTROLLER

FIG.3.4b TYPICAL APPLICATION for IBM PC/AT

**FLOPPY DISK CONTROLLER****3.5 TC8569AF CAUTION IN PROGRAMMING****3.5.1 FDC COMMAND**

TC8569AF has a construction of commands which is almost compatible with that of TC8565P (compatible with  $\mu$ PD765A), but some commands are different from that of TC8565P. At programming, you should pay attention to the difference between TC8569AF and the conventional type of FDC as follows.

1 : Commands which is not supported with TC8569AF

TC8569AF does not have three commands that are SCAN EQUAL, SCAN LOW or EQUAL and SCAN HIGH or EQUAL.

2 : Command which has different function

SPECIFY COMMAND defines the time interval between step pulses, the head loading time and the head unloading time. But TC8569AF does not have the function of head load, then the head loading time and head unloading time have no meaning in the SPECIFY COMMAND of TC8569AF. It is necessary to find another method if the head loading time is used as the settling time for READ/WRITE operation.

3 : New Command

CONFIG COMMAND should be executed at initializing FDC.

**3.5.2 CAUTION AT INITIALIZING**

At initializing FDC and changing the type of floppy you should pay attention to the several points as follows.

1 : Reset operation for FDC block

TC8569AF can reset FDC block by writing 0 (zero) to bit D2 in CONTROL REGISTER 0. After TC8569AF is released from the reset state, this bit is set to 0 (zero). This bit need to be set to 1 when the FDC operation begins.

2 : Setting up the type of floppy

The standard floppy mode is set up after TC8569AF is released from the reset state. You should set up the correct floppy mode by writing to the CONTROL REGISTER 2 (XRATE1, XRATE0).

3 : Execution of CONFIG COMMAND

At initializing FDC, CONFIG COMMAND should be executed for the correct operation.

## 4. PIN DESCRIPTION

## 4.1 PIN CONNECTION

| NO. | I/O | PIN NAME | NO. | I/O | PIN NAME | NO. | I/O | PIN NAME |

|-----|-----|----------|-----|-----|----------|-----|-----|----------|

| 1   | O   | C6       | 31  | I   | -IOW     | 61  | I   | MODE     |

| 2   | O   | C4       | 32  | I   | DMATC    | 62  | O   | STNBY    |

| 3   | V   | VDD      | 33  | I   | -DACK2   | 63  | G   | VSS      |

| 4   | O   | TDW      | 34  | I   | -TEST1   | 64  | O   | -RW/SK   |

| 5   | O   | TRDT     | 35  | I   | -TEST2   | 65  | O   | LOCK     |

| 6   | I   | RESET    | 36  | I   | -TEST3   | 66  | O   | LWDEN    |

| 7   | O   | RD7EN    | 37  | G   | VSS      | 67  | O   | MEN1     |

| 8   | O   | -TGATE   | 38  | O   | LPF1     | 68  | O   | MEN0     |

| 9   | I   | IDSEL    | 39  | O   | LPF2     | 69  | O   | WDT1     |

| 10  | O   | ENID     | 40  | I   | CONT     | 70  | O   | WE       |

| 11  | O   | DRQ2     | 41  | AG  | AVSS     | 71  | O   | HS       |

| 12  | O   | INTRQ    | 42  | V   | VDD      | 72  | V   | VDD      |

| 13  | G   | VSS      | 43  | O   | VCO      | 73  | G   | VSS      |

| 14  | I/O | D0       | 44  | I   | CDS      | 74  | O   | HL       |

| 15  | I/O | D1       | 45  | I   | -RDT     | 75  | O   | STP      |

| 16  | I/O | D2       | 46  | I   | -IDX     | 76  | O   | DR       |

| 17  | I/O | D3       | 47  | I   | -RDY     | 77  | O   | DS1      |

| 18  | I/O | D4       | 48  | I   | -WP      | 78  | O   | DS0      |

| 19  | I/O | D5       | 49  | I   | -TK0     | 79  | O   | MDSL1    |

| 20  | I/O | D6       | 50  | I   | -DSKCHG  | 80  | O   | MDSL0    |

| 21  | I/O | D7       | 51  | I   | LA       |     |     |          |

| 22  | G   | VSS      | 52  | I   | -SHEN    |     |     |          |

| 23  | O   | RD7      | 53  | I   | SHB      |     |     |          |

| 24  | I   | CS2      | 54  | I   | SHA      |     |     |          |

| 25  | I   | A2       | 55  | I   | FVFO     |     |     |          |

| 26  | I   | A1       | 56  | O   | MFM      |     |     |          |

| 27  | I   | A0       | 57  | G   | VSS      |     |     |          |

| 28  | I   | -CS1     | 58  | I   | XIN      |     |     |          |

| 29  | I   | AEN      | 59  | O   | XOUT     |     |     |          |

| 30  | I   | -IOR     | 60  | I   | -SRSEL   |     |     |          |

**FLOPPY DISK CONTROLLER****4.2 DESCRIPTION OF PIN FUNCTION**

| NO. | PIN NAME | I/O | PIN FUNCTION                                                                                                                                                                                                                                                                                    |

|-----|----------|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1   | C6       | O   | Output port of C6 bit in a CONTROL REGISTER 1.                                                                                                                                                                                                                                                  |

| 2   | C4       | O   | Output port of C4 bit in a CONTROL REGISTER 1.                                                                                                                                                                                                                                                  |

| 3   | VDD      | V   | + 5V power supply                                                                                                                                                                                                                                                                               |

| 4   | TWD      | O   |                                                                                                                                                                                                                                                                                                 |

| 5   | TRDT     | O   | These terminals for test. Use in non-connect.                                                                                                                                                                                                                                                   |

| 6   | RESET    | I   | RESET CONTROL REGISTERS. The [-FRST] bit on the CONTROL REGISTER 0 is also reset, and consequently the internal FDC block is reset.                                                                                                                                                             |

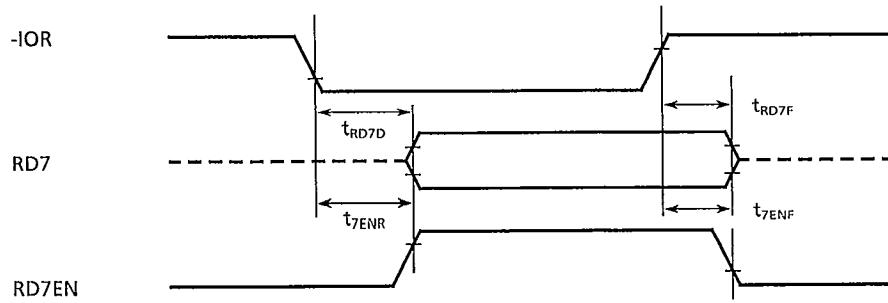

| 7   | RD7EN    | O   | Output control signal for DISK CHANGED. When DISK CHANGE which is output to [RD7] is connected to the system bus via LS126, use this output for the gate signal for LS126.                                                                                                                      |

| 8   | -TGATE   | O   | When the data bus is connected to the system bus via LS245, use this signal for the gate signal for LS245.                                                                                                                                                                                      |

| 9   | IDSEL    | I   | [DRQ2] and [INTRQ] become three state output when "Low Level" is applied to this input. When ENID in the CONTROL REGISTER 0 is set to 0 (zero), [DRQ2] and [INTRQ] output become high-impedance state. When "High Level" is applied to this input, [DRQ2] and [INTRQ] become totem-pole output. |

| 10  | ENID     | O   | Side output of ENID bit in a CONTROL REGISTER 0.                                                                                                                                                                                                                                                |

| 11  | DRQ2     | O   | Request signal for DMA transfer. This signal is the delayed [DRQ] from internal FDC chip. This signal is disabled to "Low level" with setting 0 (zero) on the ENID bit in the CONTROL REGISTER 0.                                                                                               |

| 12  | INTRQ    | O   | Interrupt request signal for system from internal FDC chip. This signal is disabled to "Low level" with setting 0 (zero) on the ENID bit in the CONTROL REGISTER 0.                                                                                                                             |

| 13  | VSS      | G   | Chips ground for digital circuits.                                                                                                                                                                                                                                                              |

| 14  | D0       | I/O | Bidirectional 8 bit data bus.                                                                                                                                                                                                                                                                   |

| 15  | D1       | I/O |                                                                                                                                                                                                                                                                                                 |

| 16  | D2       | I/O |                                                                                                                                                                                                                                                                                                 |

| 17  | D3       | I/O |                                                                                                                                                                                                                                                                                                 |

| 18  | D4       | I/O |                                                                                                                                                                                                                                                                                                 |

| 19  | D5       | I/O |                                                                                                                                                                                                                                                                                                 |

| 20  | D6       | I/O |                                                                                                                                                                                                                                                                                                 |

| 21  | D7       | I/O |                                                                                                                                                                                                                                                                                                 |

| 22  | VSS      | G   | Chips ground for digital circuits.                                                                                                                                                                                                                                                              |

## FLOPPY DISK CONTROLLER

| NO. | PIN NAME | I/O | PIN FUNCTION                                                                                                                                                                                                                                                                   |

|-----|----------|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 23  | RD7      | O   | DISK CHANGE output. When the address (A2 = 1, A1 = 1, A0 = 1) is accessed in the read operation (-IOR = Low), this output signal shows the inverting logic level which is applied to the [-DSKCHG] input. This output signal become high-impedance state in another condition. |

| 24  | CS2      | I   | Chip select input. High active control signal.                                                                                                                                                                                                                                 |

| 25  | A2       | I   | Address 2 input                                                                                                                                                                                                                                                                |

| 26  | A1       | I   | Address 1 input.                                                                                                                                                                                                                                                               |

| 27  | A0       | I   | Address 0 input.                                                                                                                                                                                                                                                               |

| 28  | -CS1     | I   | Chip select input. Low active control signal.                                                                                                                                                                                                                                  |

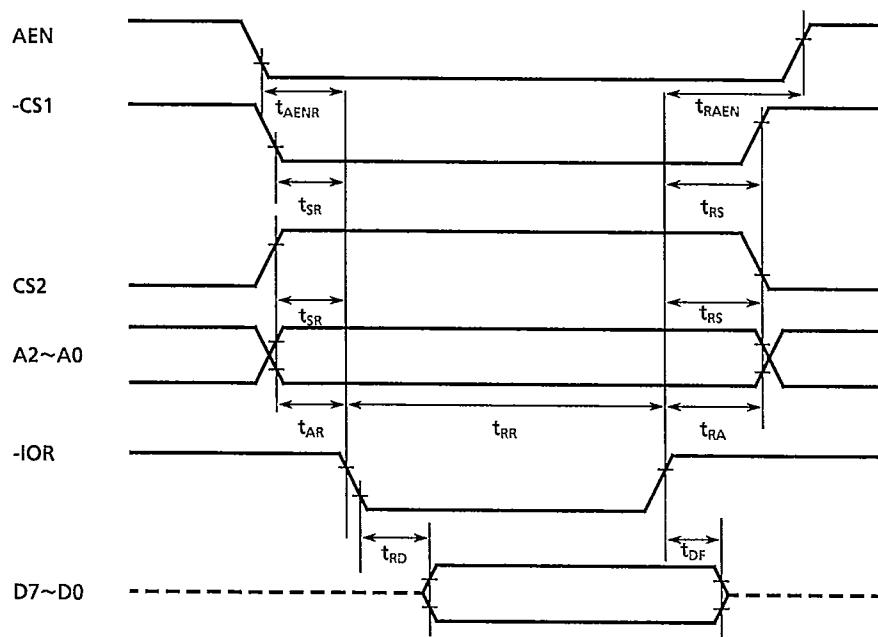

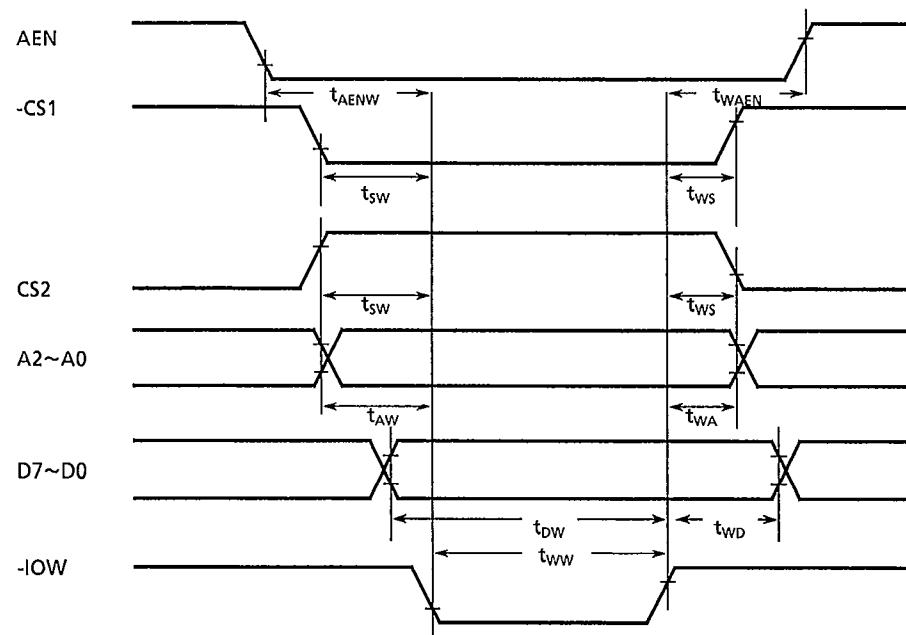

| 29  | AEN      | I   | Address enable input. "Low level" on [-CS1] and [AEN] and "High level" on [CS2] select the FDC-III, and allows [-IOR] and [-IOW] to be effective.                                                                                                                              |

| 30  | -IOR     | I   | Low active control signal to transfer data from the FDC to the Data-Bus.                                                                                                                                                                                                       |

| 31  | -IOW     | I   | Low active control signal to transfer data from the Data-bus to the FDC-III.                                                                                                                                                                                                   |

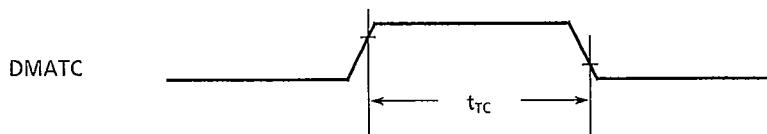

| 32  | DMATC    | I   | High active DMA transfer terminating signal. When the FDC works DMA MODE, this signal terminates the DMA transfer.                                                                                                                                                             |

| 33  | -DACK2   | I   | Low active DMA cycle executing signal. When the FDC works DMA MODE, this signal controls DMA I/O.                                                                                                                                                                              |

| 34  | -TEST1   | I   |                                                                                                                                                                                                                                                                                |

| 35  | -TEST2   | I   | These input terminals for LSI test. "High level" should be applied.                                                                                                                                                                                                            |

| 36  | -TEST3   | I   |                                                                                                                                                                                                                                                                                |

| 37  | VSS      | G   | Chips ground for digital circuits.                                                                                                                                                                                                                                             |

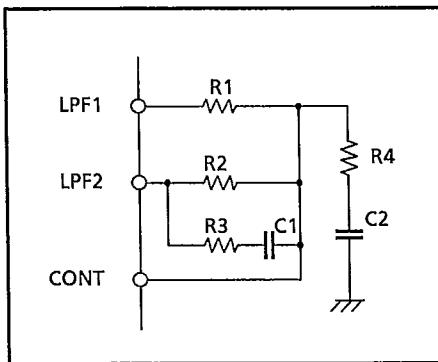

| 38  | LPF1     | O   | The charge pump output for external low pass filter. This output will activate when PLL circuit force to lock the read signal (Pull-in mode).                                                                                                                                  |

| 39  | LPF2     | O   | The charge pump output for external low pass filter. This output will be selected after PLL has pulled in the read signal and use low gain filter.                                                                                                                             |

| 40  | CONT     | I   | Analog voltage input for VCO.                                                                                                                                                                                                                                                  |

| 41  | AVSS     | AG  | Analog ground for VCO and PLL circuits.                                                                                                                                                                                                                                        |

| 42  | VDD      | V   | +5V power supply.                                                                                                                                                                                                                                                              |

| 43  | VCO      | O   | The output terminal for LSI test. Use in non-connect.                                                                                                                                                                                                                          |

| 44  | CDS      | I   | When "High Level" is applied to this input, the decode signal of bit 0 in CONTROL REGISTER 0 is selected for [DS1] and [DS0]. When "Low Level" is applied to this input, the non-decode signals of US1 and US0 of FDC block are selected for [DS1] and [DS0].                  |

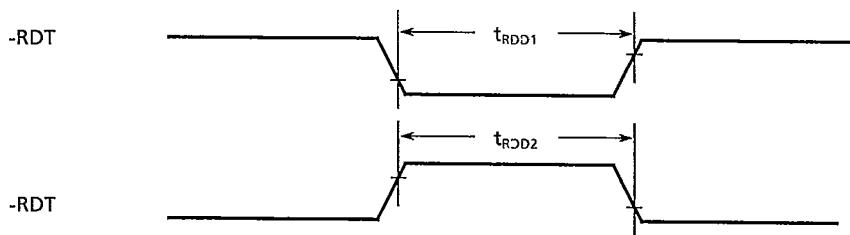

| 45  | -RDT     | I   | The input for the READ DATA from the floppy disk drive.                                                                                                                                                                                                                        |

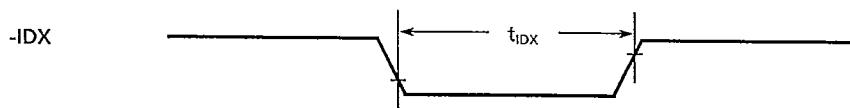

| 46  | -IDX     | I   | Index pulse input from FDD system interface.                                                                                                                                                                                                                                   |

## FLOPPY DISK CONTROLLER

| NO. | PIN NAME | I/O | PIN FUNCTION                                                                                                                                                                                                                                                                                        |

|-----|----------|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 47  | -RDY     | I   | Drive ready signal from FDD system interface.                                                                                                                                                                                                                                                       |

| 48  | -WP      | I   | Write protected indicate signal from FDD system interface.                                                                                                                                                                                                                                          |

| 49  | -TK0     | I   | Head position indicate signal from FDD system interface. Low level on this terminal means that the head of FDD is on the TRACK #0 position.                                                                                                                                                         |

| 50  | -DSKCHG  | I   | Disk change signal from FDD system interface.                                                                                                                                                                                                                                                       |

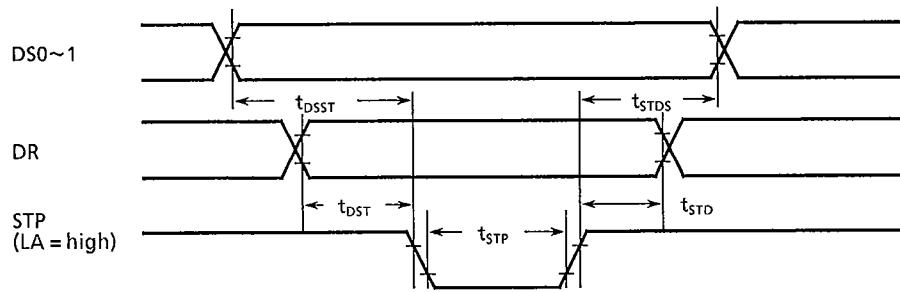

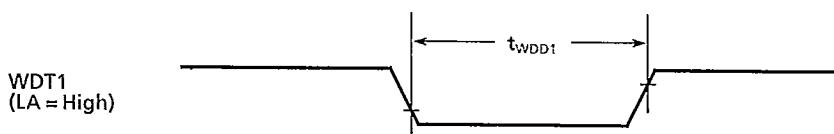

| 51  | LA       | I   | Physical active level select on the output of FDD system interface signal, that is WDT1, WE, HS, STP, DR, HL, LWDEN, MEN0~1, DS0~1 and MDSL0~1. High level on this terminal means that these signal will be low active and can connect to directly FDD which has CMOS type interface specification. |

| 52  | -SHEN    | I   | If "High level" on the terminal, no pre-compensation shifting will be done.                                                                                                                                                                                                                         |

| 53  | SHB      | I   | Refer to the section 5.1.8.                                                                                                                                                                                                                                                                         |

| 54  | SHA      | I   |                                                                                                                                                                                                                                                                                                     |

| 55  | FVFO     | I   | This signal decides the operation of the internal VFO circuit. The VFO operates in fixed filter non-switching mode when "High", and operates in alternative filters (high gain and low gain filters) switching mode when "Low".                                                                     |

| 56  | MFM      | O   | This output terminal will show the recording format of the operation of FDC. "High level" on this terminal shows that the FDC works at MFM recording format and otherwise shows FM recording format.                                                                                                |

| 57  | VSS      | G   | Chips ground for digital circuits.                                                                                                                                                                                                                                                                  |

| 58  | XIN      | I   | This input connects the crystal oscillator or external clock signal. In the standard usage, use 16MHz crystal oscillator.                                                                                                                                                                           |

| 59  | XOUT     | O   | This output is inverted signal of [XIN], or connected the crystal oscillator.                                                                                                                                                                                                                       |

| 60  | -SRSEL   | I   | "High Level" is applied to this input. If "Low Level" is applied, you will be able to program the step rate (Ref. SPECIFY COMMAND) at the step of 1ms in mini floppy mode.                                                                                                                          |

| 61  | MODE     | I   | "Low level" should be applied.                                                                                                                                                                                                                                                                      |

| 62  | STNBY    | O   | This signal shows that FDC-III is in a standby mode. In a standby mode, all internal clock is stopped for saving power dissipation and following signals are inactive states WDT1, WE, HS, STP, DR, HL, LWDEN, MEN0~1, DS0~1 and MDSL0~1.                                                           |

| 63  | VSS      | G   | Chips ground for digital circuits.                                                                                                                                                                                                                                                                  |

| 64  | -RW/SK   | O   | "Low" shows that read / write operation is selected, and "High" shows that seek operation is selected.                                                                                                                                                                                              |

| 65  | LOCK     | O   | The terminal for test. Use in non-connect.                                                                                                                                                                                                                                                          |

| 66  | LWDEN    | O   | Low density output for FDD. Low active when LA = High.                                                                                                                                                                                                                                              |

| NO. | PIN NAME | I/O | PIN FUNCTION                                                                                                                  |

|-----|----------|-----|-------------------------------------------------------------------------------------------------------------------------------|

| 67  | MEN1     | O   | Motor enable for drive #1 for FDD. Low active when LA = High.                                                                 |

| 68  | MEN0     | O   | Motor enable for drive #0 for FDD. Low active when LA = High.                                                                 |

| 69  | WDT1     | O   | Pre-compensated write data for FDD. Low active when LA = High.                                                                |

| 70  | WE       | O   | Write enable signal for FDD. Low active when LA = High.                                                                       |

| 71  | HS       | O   | Head select signal when LA = High<br>when LA = Low<br>High Head0 Head1<br>Low Head1 Head0                                     |

| 72  | VDD      | V   | + 5V power supply.                                                                                                            |

| 73  | VSS      | G   | Chips ground for digital circuits.                                                                                            |

| 74  | HL       | O   | The terminal for test. Use in non-connect.                                                                                    |

| 75  | STP      | O   | Decoded step pulse signal, connected disk drives for FDD. Low active when LA = High.                                          |

| 76  | DR       | O   | Decoded direction signal for head seek.<br>when LA = High LA = Low<br>Low inner seek outer seek<br>High outer seek inner seek |

| 77  | DS1      | O   | Drive select 1 signal for FDD. Low active when LA = High. Refer to TABLE 5.1.11a.                                             |

| 78  | DS0      | O   | Drive select 0 signal for FDD. Low active when LA = High. Refer to TABLE 5.1.11b.                                             |

| 79  | MDSL1    | O   | These outputs signals show the FDD type which this controller expects. Refer to TABLE 5.1.9.                                  |

| 80  | MDSL0    | O   |                                                                                                                               |

# FLOPPY DISK CONTROLLER

## 5. FUNCTIONAL DESCRIPTION

### 5.1 CONTROL REGISTER and PART of PERIPHERAL CIRCUIT

#### 5.1.1 RELATION of ADDRESS LINE and EACH REGISTER

| AEN | -CS | CS2 | A2 | A1 | A0 | -IOR | -IOW | SELECTION    |

|-----|-----|-----|----|----|----|------|------|--------------|

| H   | x   | x   | x  | x  | x  | x    | x    | NO-SELECTION |

| x   | H   | x   | x  | x  | x  | x    | x    |              |

| x   | x   | L   | x  | x  | x  | x    | x    |              |

| L   | L   | H   | L  | L  | x  | x    | x    |              |

| L   | L   | H   | L  | H  | L  | L    | H    |              |

| L   | L   | H   | L  | H  | H  | x    | x    |              |

| L   | L   | H   | H  | L  | L  | L    | H    |              |

| L   | L   | H   | H  | L  | H  | H    | L    |              |

| L   | L   | H   | H  | H  | L  | x    | x    |              |

| x   | x   | x   | x  | x  | x  | L    | L    | INHIBIT      |

| x   | x   | x   | x  | x  | x  | H    | H    | NO SELECTION |

H : High L : Low x : Don't Care

#### 5.1.2 CONDITION OF STANDBY STATE

LSI will enter into standby mode after several times elapsed, when the SBM bit in the CONTROL REGISTER 1 is set to "1" and following conditions are filled. The waiting time is decided by the state of internal FDC mode. Usually, 6ms to 8ms in MINI floppy mode and 3ms to 4ms in STANDRAD floppy mode. Additional condition is as follows.

- -FRST bit of CONTROL REGISTER 1 is set to "1".

- FDC is in the state that it is waiting command from the host.

The output terminal [STNBY] is activated when FDC is in the standby state, and X'tal oscillation stops. Standby state allows the drive output signals WDT1, WE, HS, STP, DR, HL, LWDEN, MEN0~1, DS0~1 and MDSL0~1 to be inactive.

LSI will take off from the standby state when one of following conditions is detected.

- SBM bit is set to "0".

- -FRST bit is set to "0".

- FDC receives a command.

## 5.1.3 CONTROL REGISTER 0

5 bit register for write only

| BIT | SYMBOL | NAME                     | MEANING                                                                                                    |

|-----|--------|--------------------------|------------------------------------------------------------------------------------------------------------|

| D7  |        | RESERVED                 |                                                                                                            |

| D6  |        | RESERVED                 |                                                                                                            |

| D5  | MEN1   | MOTOR ENABLE 1           | Radial motor on signal for #1 Drive                                                                        |

| D4  | MENO   | MOTOR ENABLE 0           | Radial motor on signal for #0 Drive                                                                        |

| D3  | ENID   | ENABLE INT & DMA REQUEST | INTRQ and DRQ2 are enabled when this bit is "High level".                                                  |

| D2  | -FRST  | NOT · FDC · RESET        | 0 on this bit will reset the internal FDC block. For normal operation, this bit should be set to 1.        |

| D1  |        | RESERVED                 | Drive Select bit : 0 on this bit indicates that drive A is selected, 1 indicates that drive B is selected. |

| D0  | DSA    | DRIVE SELECT A           |                                                                                                            |

If RESET signal get to "High ", all bits are cleared.

## 5.1.4 CONTROL REGISTER 1

4 bit register for write only

| BIT | SYMBOL   | NAME               | MEANING                                                                                                                                                                                                                     |

|-----|----------|--------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| D7  | ENABLE 6 |                    |                                                                                                                                                                                                                             |

| D6  | C6       | CONTROL 6          |                                                                                                                                                                                                                             |

| D5  | ENABLE 4 |                    |                                                                                                                                                                                                                             |

| D4  | C4       | CONTROL 4          | When 1 is applied to this bit during byte write operation of this register, the value of C6 becomes to D6. When 0 is applied to this bit during byte write operation of this register, the value of C6 is to be copy of D6. |

| D3  | ENABLE 2 |                    |                                                                                                                                                                                                                             |

| D2  | SBM      | STANDBY MODE       | When 1 is applied to this bit, FDC enables to transfer into standby mode.                                                                                                                                                   |

| D1  | ENABLE 1 |                    | FDC terminal count control bit. This bit will be used to terminate data transfer in Non-DMA                                                                                                                                 |

| D0  | FDCTC    | FDC TERMINAL COUNT |                                                                                                                                                                                                                             |

D7, D5, D3 and D1 are the write enable bit for the each lower bit. For example, when 03H is written to the register, only D0 can be set to 1.

# FLOPPY DISK CONTROLLER

## 5.1.5 CONTROL REGISTER 2

3 bit register for write and read

| BIT   | SYMBOL | I/O | NAME            | MEANING                                     |

|-------|--------|-----|-----------------|---------------------------------------------|

| D7    | DCHG   | O   | DISK CHANGE     | Use RD7 wired with D7. Refer to FIG. 5.1.5. |

| D6~D2 |        |     | RESERVED        |                                             |

| D1    | XRATE1 |     | TRANSFER RATE 1 |                                             |

| D0    | XRATE0 |     | TRANSFER RATE 0 | Refer to TABLE 3.2                          |

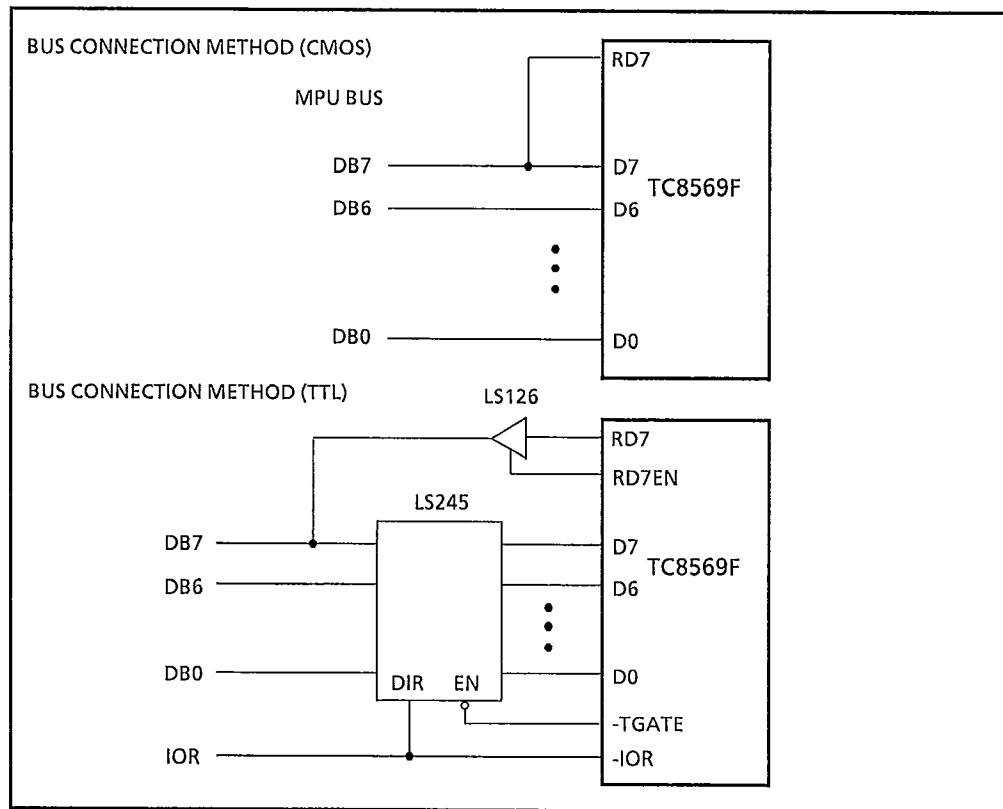

FIG.5.1.5 BUS CONNECTION METHOD

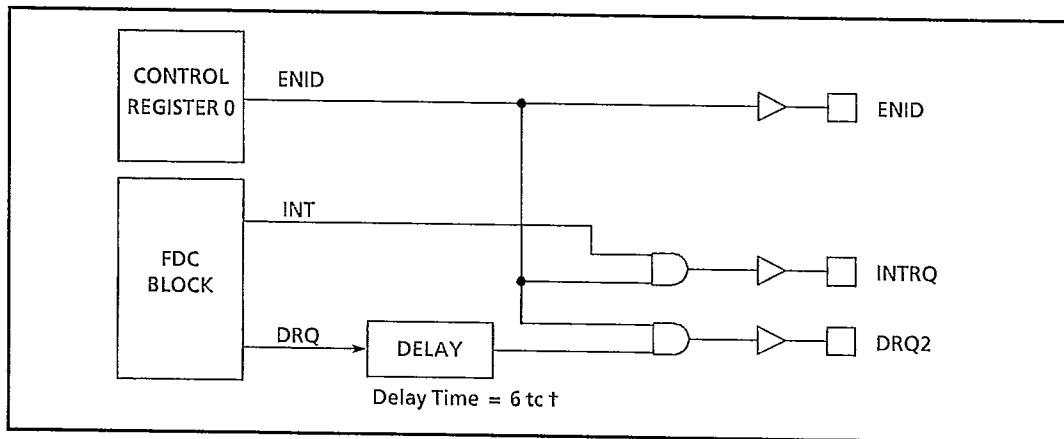

## 5.1.6 RELATION OF ENID, INT, INTRQ, DRQ, DRQ2

$t = tc : tc = 62.5\text{ns (1Mbps)}$

$125\text{ns (500Kbps)}$

$250\text{ns (250Kbps)}$

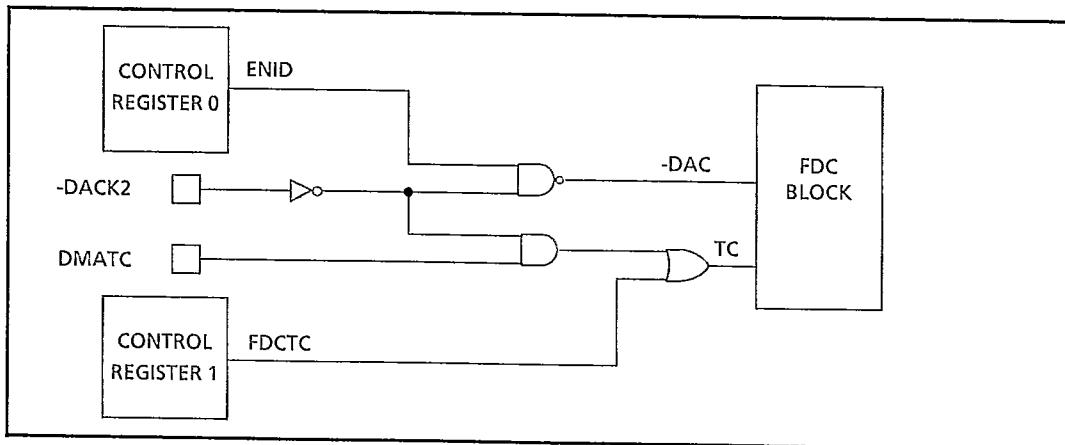

## 5.1.7 RELATION OF ENID, -DACK2, DMATC, FDCTD

**FLOPPY DISK CONTROLLER**

## 5.1.8 WRITE COMPENSATION CIRCUIT

| -SHEN | XRATE1 | XRATE0 | SHB | SHA | SHIFT    | TRANSFER RATE |

|-------|--------|--------|-----|-----|----------|---------------|

| H     | X      | X      | X   | X   | 0 ns     | 500 Kbps      |

| L     | L      | L      | L   | L   | 62.5 ns  |               |

| L     | L      | L      | L   | H   | 125.0 ns |               |

| L     | L      | L      | H   | L   | 187.5 ns |               |

| L     | L      | L      | H   | H   | 250.0 ns |               |

| L     | L      | H      | X   | X   | -        |               |

| L     | H      | L      | L   | L   | 125.0 ns | 250 Kbps      |

| L     | H      | L      | L   | H   | 250.0 ns |               |

| L     | H      | L      | H   | L   | 375.0 ns |               |

| L     | H      | L      | H   | H   | 500.0 ns |               |

| L     | H      | H      | L   | L   | 62.5 ns  | 1 Mbps        |

| L     | H      | H      | L   | H   | 125.0 ns |               |

| L     | H      | H      | H   | L   | 187.5 ns |               |

| L     | H      | H      | H   | H   | 250.0 ns |               |

## 5.1.9 FLOPPY DISK DRVE MODE CHANGE

TABLE 5.1.9 FLOPPY DISK DRIVE MODE CHANGE

| XRATE1 | XRATE0 | MDSL0 | MDSL1 | LWDEN |

|--------|--------|-------|-------|-------|

| 0      | 0      | H     | L     | H     |

| 0      | 1      | H     | H     | L     |

| 1      | 0      | L     | L     | L     |

| 1      | 1      | L     | H     | (L)   |

LA input = "High"

## 5.1.10 GATE OUTPUT FOR BUS TRANSCEIVER

| -DACK2 | AEN | -CS1 | CS2 | A2 | A1 | A0 | -IOR | -IOW | -TGATE  |

|--------|-----|------|-----|----|----|----|------|------|---------|

| H      | H   | X    | X   | X  | X  | X  | X    | X    | H       |

| H      | X   | H    | X   | X  | X  | X  | X    | X    | H       |

| H      | X   | X    | L   | X  | X  | X  | X    | X    | H       |

| X      | X   | X    | X   | X  | X  | X  | L    | L    | INHIBIT |

| H      | L   | L    | H   | L  | L  | L  | X    | X    | H       |

| H      | L   | L    | H   | L  | L  | H  | X    | X    | H       |

| H      | L   | L    | H   | L  | H  | L  | L    | H    | H       |

| H      | L   | L    | H   | L  | H  | L  | H    | L    | L       |

| H      | L   | L    | H   | L  | H  | L  | H    | H    | H       |

| H      | L   | L    | H   | L  | H  | H  | X    | X    | H       |

| H      | L   | L    | H   | H  | L  | L  | L    | H    | L       |

| H      | L   | L    | H   | H  | L  | L  | H    | L    | L       |

| H      | L   | L    | H   | H  | L  | H  | H    | H    | H       |

| H      | L   | L    | H   | H  | L  | H  | L    | H    | L       |

| H      | L   | L    | H   | H  | H  | H  | L    | H    | H       |

| H      | L   | L    | H   | H  | H  | H  | H    | L    | L       |

| H      | L   | L    | H   | H  | H  | H  | H    | H    | H       |

| L      | X   | X    | X   | X  | X  | X  | X    | X    | L       |

# FLOPPY DISK CONTROLLER

## 5.1.11 DRIVE SELECT OUTPUT

CDS = High, LA = High

TABLE 5.1.11a

| BIT 0 of the CONTROL<br>REGISTER 0 | US1 of FDC<br>BLOCK | US0 of FDC<br>BLOCK | DS1  | DS0  |

|------------------------------------|---------------------|---------------------|------|------|

| 1                                  | x                   | x                   | Low  | High |

| 0                                  | x                   | x                   | High | Low  |

x : Don't Care

CDS = Low, LA = High

TABLE 5.1.11b

| BIT 0 of the CONTROL<br>REGISTER 0 | US1 of FDC<br>BLOCK | US0 of FDC<br>BLOCK | DS1  | DS0  |

|------------------------------------|---------------------|---------------------|------|------|

| x                                  | 0                   | 0                   | High | High |

| x                                  | 0                   | 1                   | High | Low  |

| x                                  | 1                   | 0                   | Low  | High |

| x                                  | 1                   | 1                   | Low  | Low  |

x : Don't Care

## 5.2 PART OF FDC

### 5.2.1 DIAGRAM OF FDC

# FLOPPY DISK CONTROLLER

## 5.2.2 FDC'S REGISTER AND CPU INTERFACE

FDC has two 8-bit registers accessible by the main system processor. One is a Main Status Register, and the other is a Data Register. The Main Status Register indicates the status information of the FDC and is always accessible.

The Data Register is used for data transfer between the FDC and the main processor. Command bytes are written into the Data Register in order to program the FDC, and also Status bytes are read out of the Data Register in order to obtain the result after execution of the commands.

Main Status Register may be read and is used to facilitate the data transfer between the processor and the FDC. The relationship between Main Status Register and [-IOR], [-IOW] and [A0] signals is shown below.

CS2 = A2 = 1, A1 = 0, AEN = 0

| [-CS1] | [A0] | [-IOR] | [-IOW] | FUNCTION                      |

|--------|------|--------|--------|-------------------------------|

| H      | X    | X      | X      | Non Select                    |

| L      | L    | L      | L      | Illegal                       |

| L      | L    | L      | H      | Read Main Status Register     |

| L      | L    | H      | L      | Write into CONTROL REGISTER 1 |

| L      | H    | L      | L      | Illegal                       |

| L      | H    | L      | H      | Read from Data Register       |

| L      | H    | H      | L      | Write into Data Register      |

Each bit in the Main Status Register are defined as TABLE 5.2.2. The RQM and DIO bits in the Main Status Register indicate whether Data Register is ready or not and in which direction data will be transferred on Data Bus.

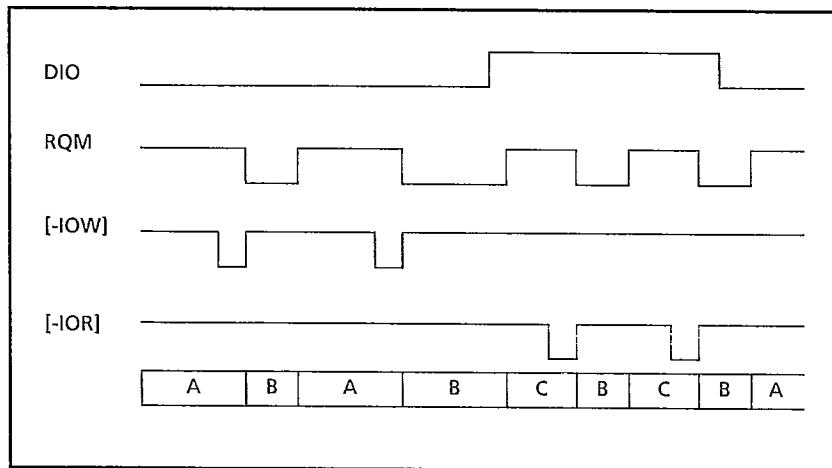

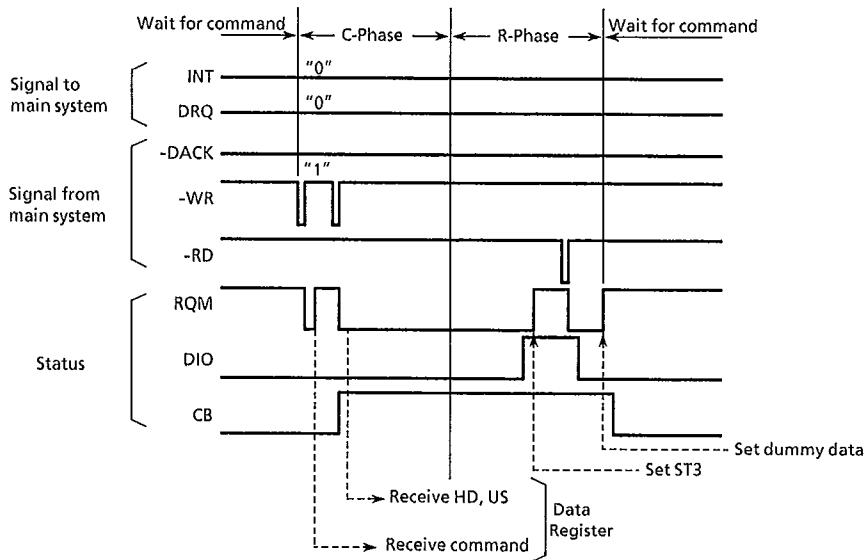

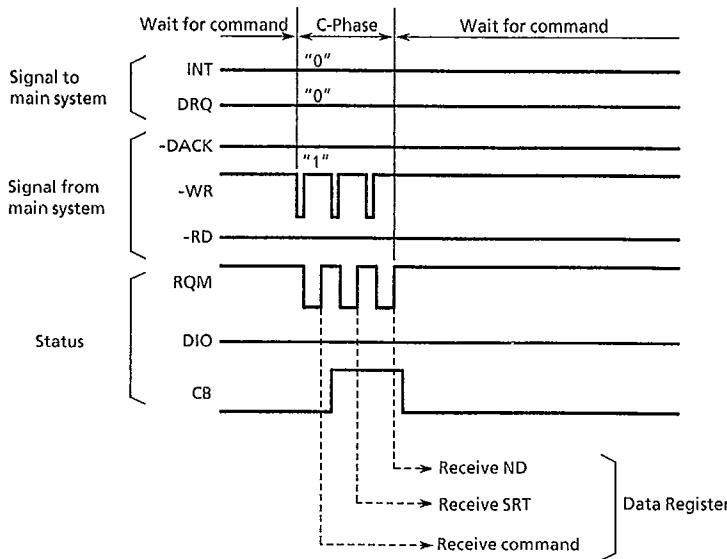

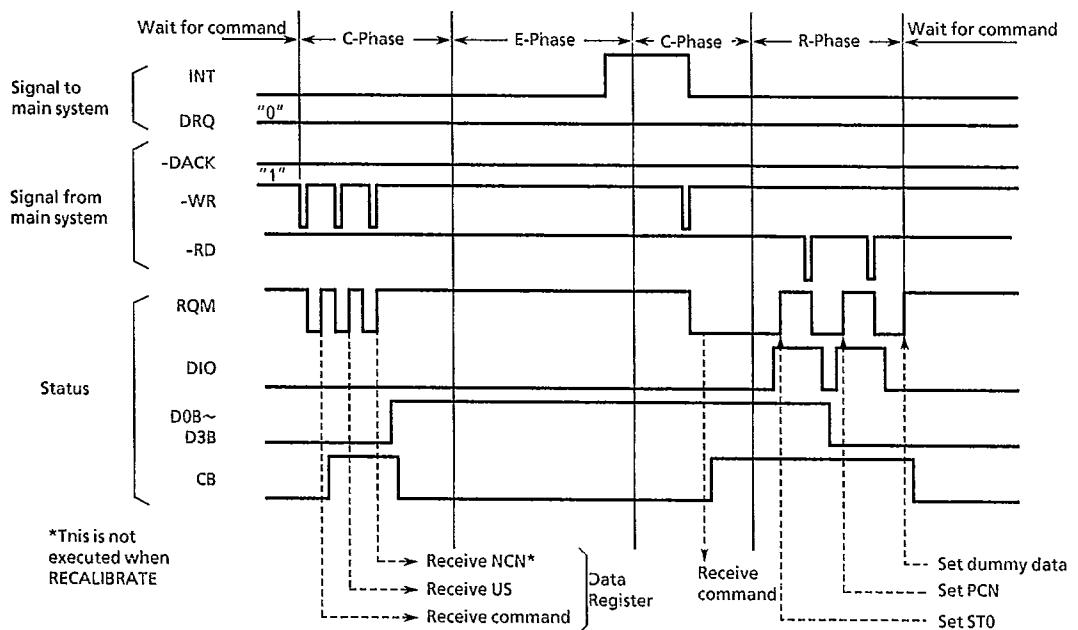

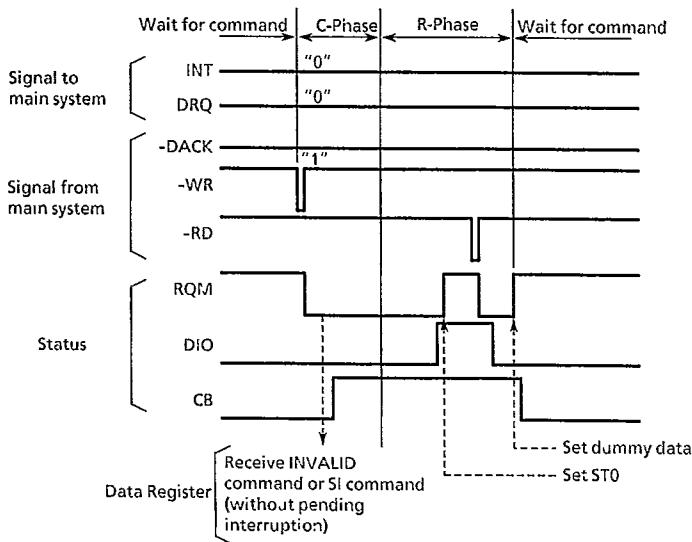

FIG.5.2.2 MAIN STATUS REGISTER TIMING

- A : (DIO = "Low" and RQM = "High") The processor may write the data in Data Register.

- B : (RQM = "Low") Data Register is not ready.

- C : (DIO = "High" and RQM = "High") In data register, data byte which will be read out by processor is already prepared.

**FLOPPY DISK CONTROLLER**

TABLE 5.2.2 MAIN STATUS REGISTER

| BIT | SYMBOL | NAME               | MEANING                                                                                                                                                                                                                        |

|-----|--------|--------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| D7  | RQM    | REQUEST for MASTER | Indicates that Data Register is ready to send the data to or to receive the data from the processor.                                                                                                                           |

| D6  | DIO    | DATA INPUT/OUTPUT  | Indicates the direction of data transfer between Data Register and the processor.<br>When DIO is a "High", transfer is from Data Register to the processor. When DIO is a "Low", transfer from the processor to Data Register. |

| D5  | NDM    | Non-DMA mode       | Indicates that the FDC is Non-DMA mode. It is set only during Execution-Phase in Non-DMA mode.                                                                                                                                 |

| D4  | CB     | FDC BUSY           | Indicates that FDC is in Execution-Phase of a read/write command, in Command-Phase, or in Result-Phase.                                                                                                                        |

| D3  | D3B    | FDD 3 BUSY         | FDD number 3 is in the Seek mode.                                                                                                                                                                                              |

| D2  | D2B    | FDD 2 BUSY         | FDD number 2 is in the Seek mode.                                                                                                                                                                                              |

| D1  | D1B    | FDD 1 BUSY         | FDD number 1 is in the Seek mode.                                                                                                                                                                                              |

| D0  | DOB    | FDD 0 BUSY         | FDD number 0 is in the Seek mode.                                                                                                                                                                                              |

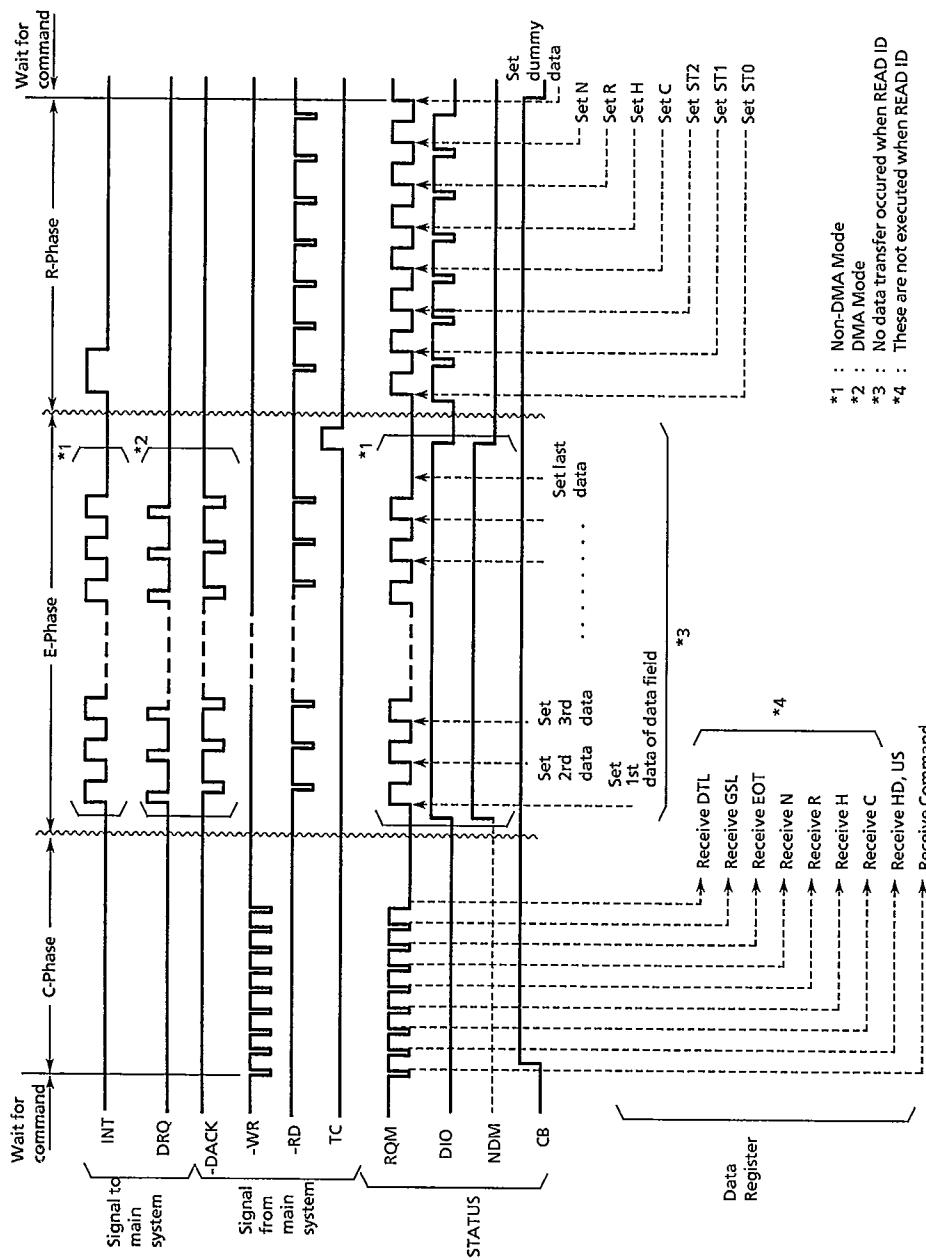

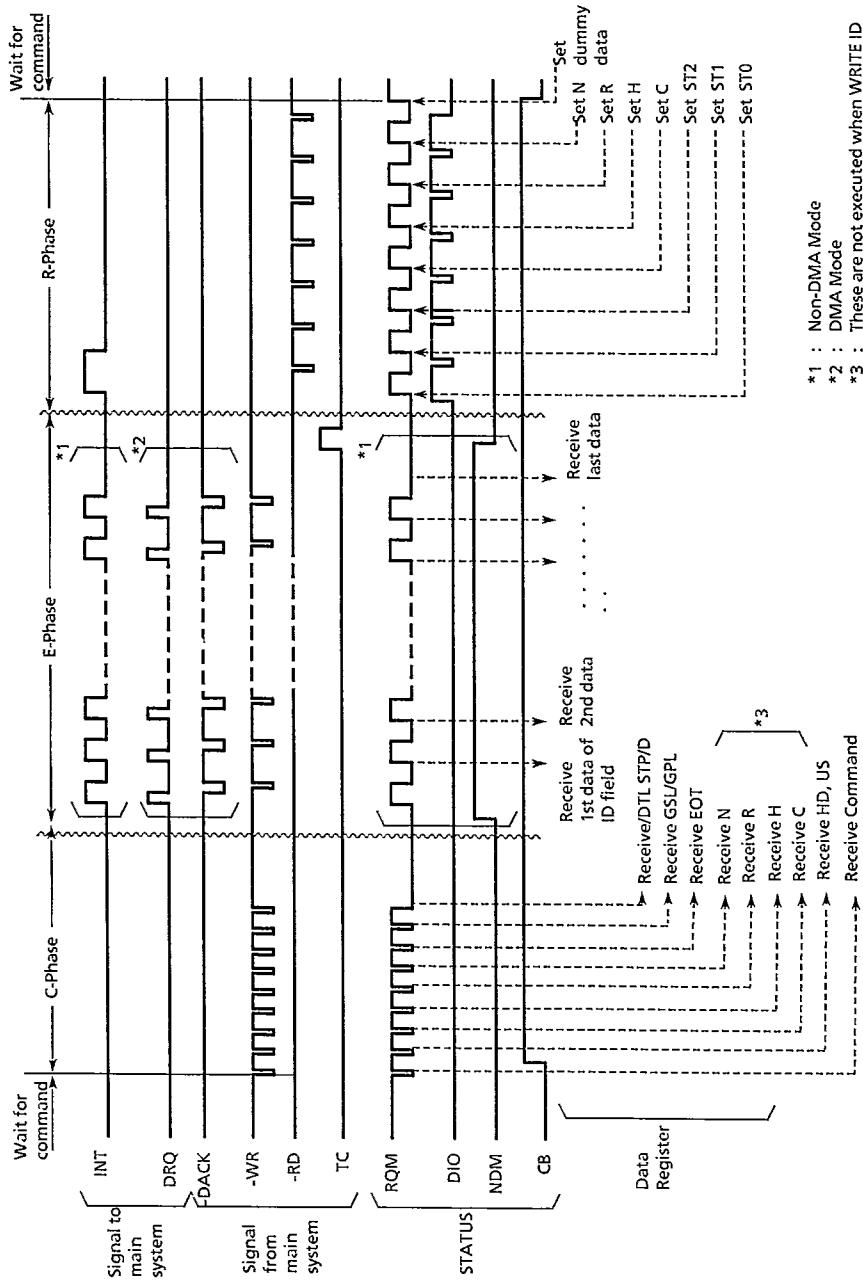

FDC supports thirteen different commands. Each of commands is initiated by a multi-byte transfer from the processor, and the result after executing of the command is a multi-byte transfer to the processor. Because the multi-byte information is interchanged between the FDC and the Processor, it is regarded that each command consists of following three phases.

Commands-Phase : The FDC receives the necessary information to perform a particular operation from the processor.

Execution-Phase : The FDC performs the specified operation.

Result-Phase : After the operation Result Status information or other information is sent to the processor.

In the Command-Phase or the Result-Phase, the processor must read out the Main Status Register before each byte of information is written into or read out from the Data Register.

When each byte of the command and the parameter is written into the FDC, bit D7 and D6 in the Main Status Register must be in high level and low level, respectively.

Because most of the Commands need multiple bytes, the Main Status Register must be read out before each byte is transferred to the FDC. In the Result-phase, the bit D7 and D6 in Main Status Register must be both in high levels before each byte is read out from the Data Register.

The reading out of the Main Status Register before each byte transfer to the FDC is necessary only in the Command-Phase and the Result-Phase, but it is not always necessary in the Execution-Phase.

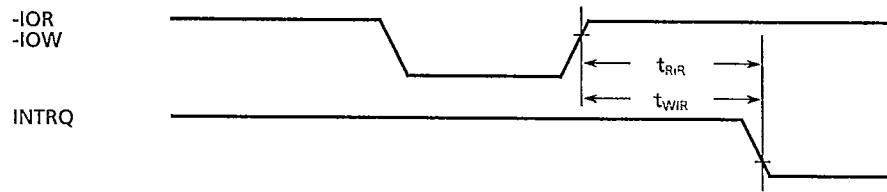

When the FDC is in Non-DMA mode, the receipt of each data byte (if the FDD is now reading out data from the FDD) is indicated by the Interrupt signal [INTRQ].

The generation of the Read signal ( $[-IOR]=0$ ) will not only output the data on the data bus but also reset the [INTRQ] signal. If the processor can not deal with interrupts fast enough (within 7.0 $\mu$ s for Perpendicular FDD mode), then it examines the Main Status Register, and then bit 7 (RQM) functions just like the Interrupt signal. Similarly in the Write command, Write signal resets the Interrupt signal.

If the FDC is in the DMA mode, then the Interrupt signal is not generated during the Execution-Phase. When the each data byte is available, the FDC generates [DRQ2] (DMA request) signal. Then the DMA controller generates both DMA Acknowledge signal and Read signal ( $[-DACK2]=0$  and  $[-IOR]=0$ ).

In a Read command, when the DMA acknowledge signal becomes low level, the FDC automatically resets the [DRQ2]. In a Write command, [-IOW] is substituted for [-IOR]. If the Execution-Phase is terminated (Terminal Count has been inputted), the Interrupt request is generated. This means the beginning of the Result-Phase. When the first data byte is read during the Result-Phase, Interrupt signal is automatically reset. During the Result-Phase, all data bytes shown in the COMMAND TABLE must be read.

For example, the READ DATA COMMAND has seven data bytes in the Result-Phase. All seven data bytes must be read out in order to complete the READ DATA COMMAND. This FDC will not accept the next command until all these seven data bytes are read out. In the same way, all the data bytes of the other commands must be read out during the Result-Phase. The FDC has five Status Registers. The Main Status Register mentioned above can always be read out by the processor. The other four Result Status Register (ST0, ST1, ST2, ST3) is available only in the Result-Phase, and read out only after the termination of the command.

The specified command determines how many the Result Status Registers will be read. The COMMAND TABLE shows the data bytes that are sent to the FDC in the Command-Phase and read out from the FDC in the Result-Phase. That is, the command code must be sent first, and the other bytes must be sent in order. So the Command-Phase and the Result-Phase can not be shorten. When the last data byte in the Command-Phase is sent to the FDC, the Execution-Phase automatically starts. Similarly, when the last byte in the Result-Phase is read out, the command is automatically terminated, and then the FDC is ready for a new command.

# FLOPPY DISK CONTROLLER

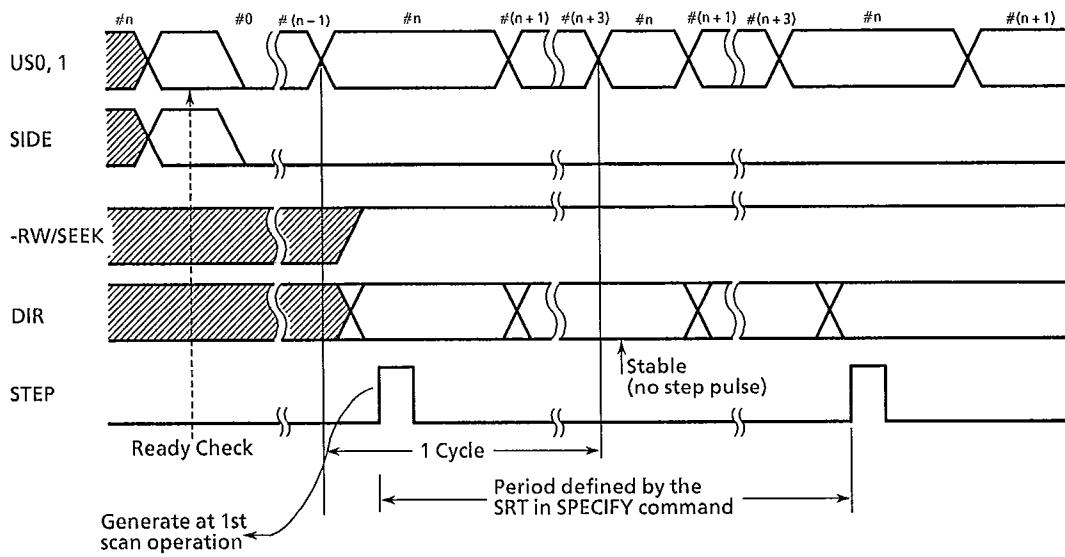

### 5.2.3 FUNCTION OF POLLING IN FDC

After the SPECIFY COMMAND has been sent to the FDC, the drive select signals, the DS1 and DS0, are automatically in the polling mode. Between the commands (and between the step pulses in the seek mode), the FDC checks the four FDDs looking for a change of the ready signals from drive units.

If the Ready Signal is changed, then the FDC generates the Interrupt Signal. After the processor has issued the SENSE INTERRUPT STATUS COMMAND, the Result Status Register 0 (ST0) is read out, and the Not Ready bit (NR) in ST0 shows the present status. Because of the polling of Ready Signal between the commands, the processor can notice which drives are on line or which drives are off line.

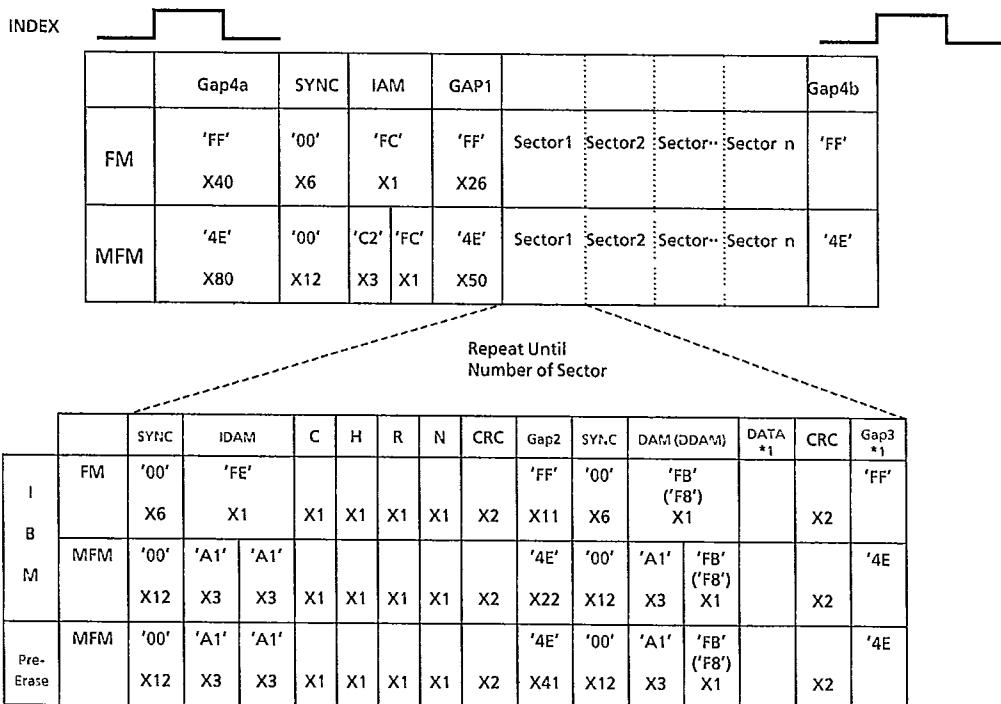

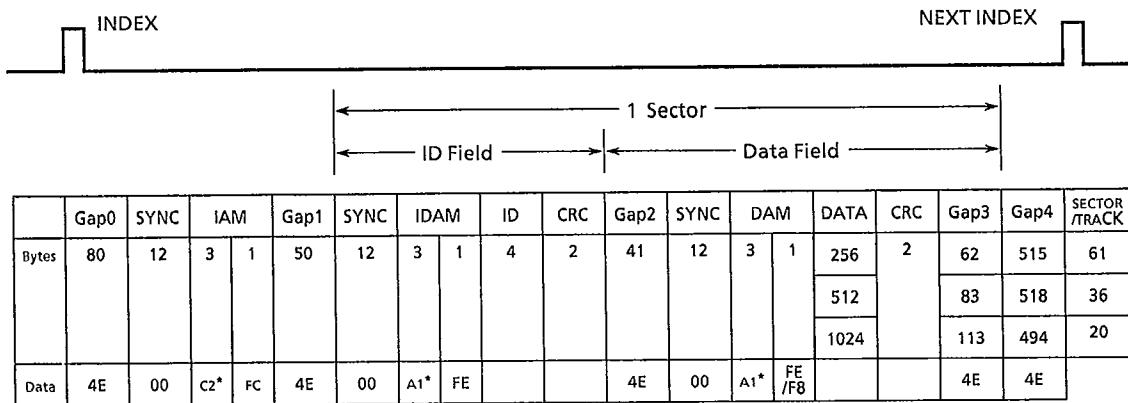

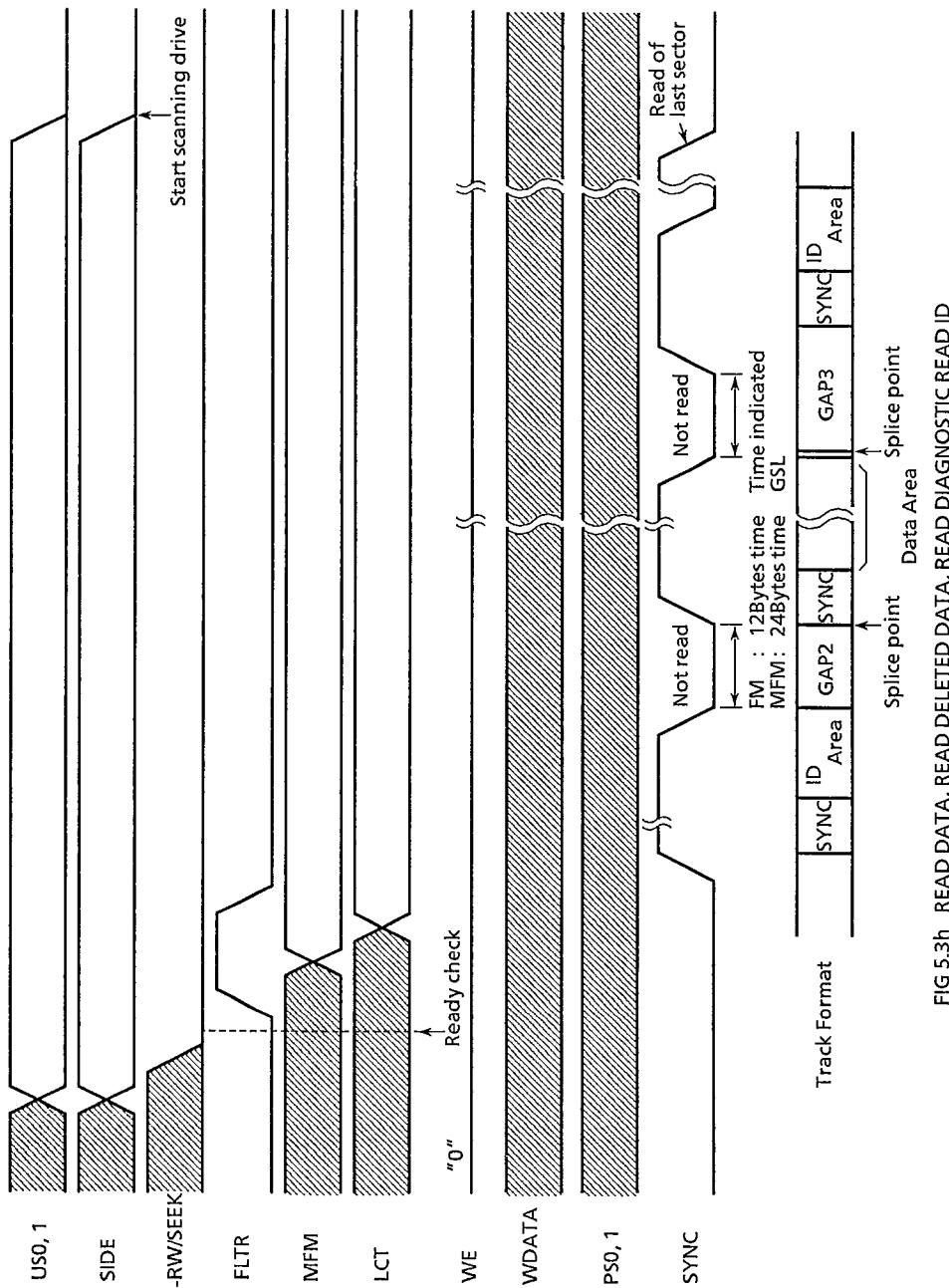

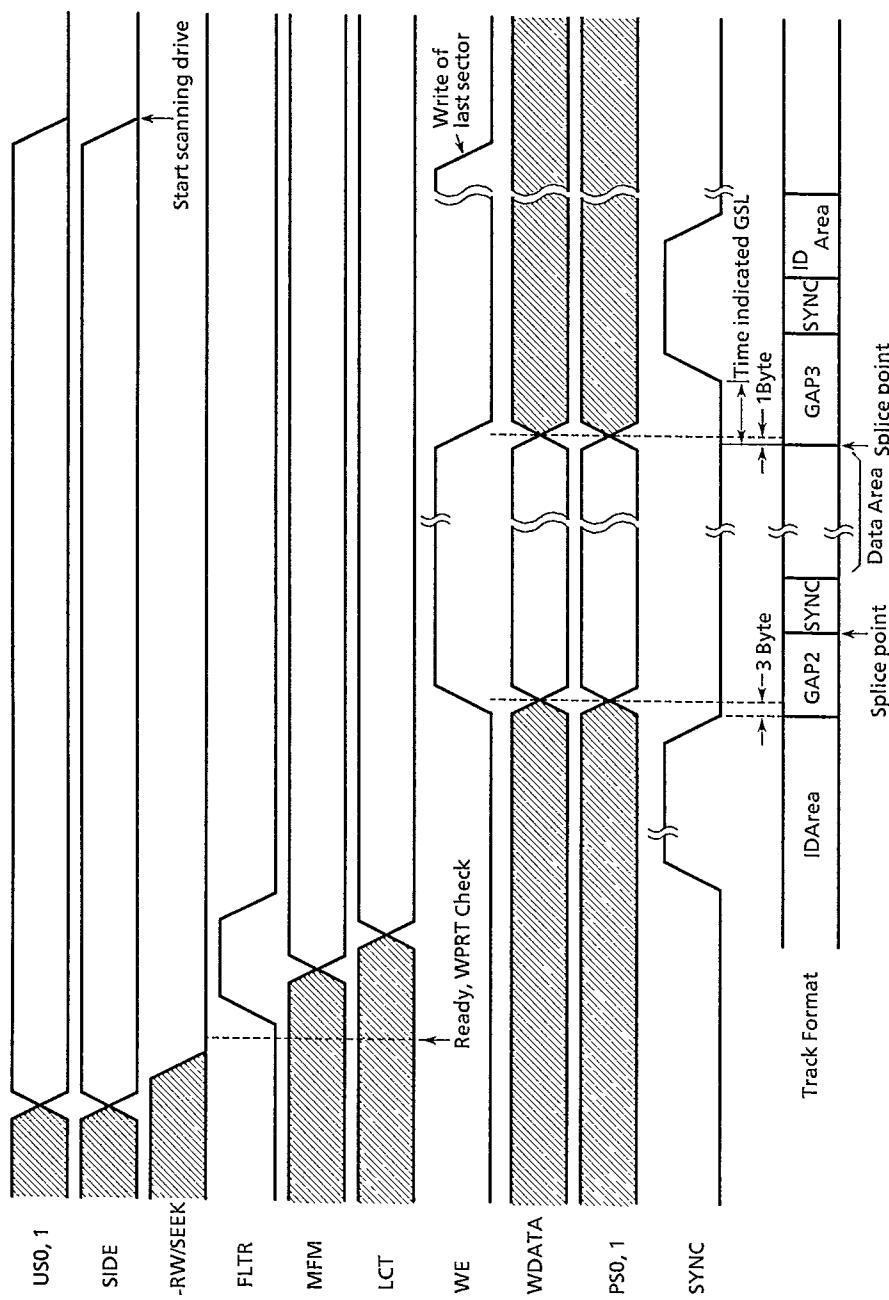

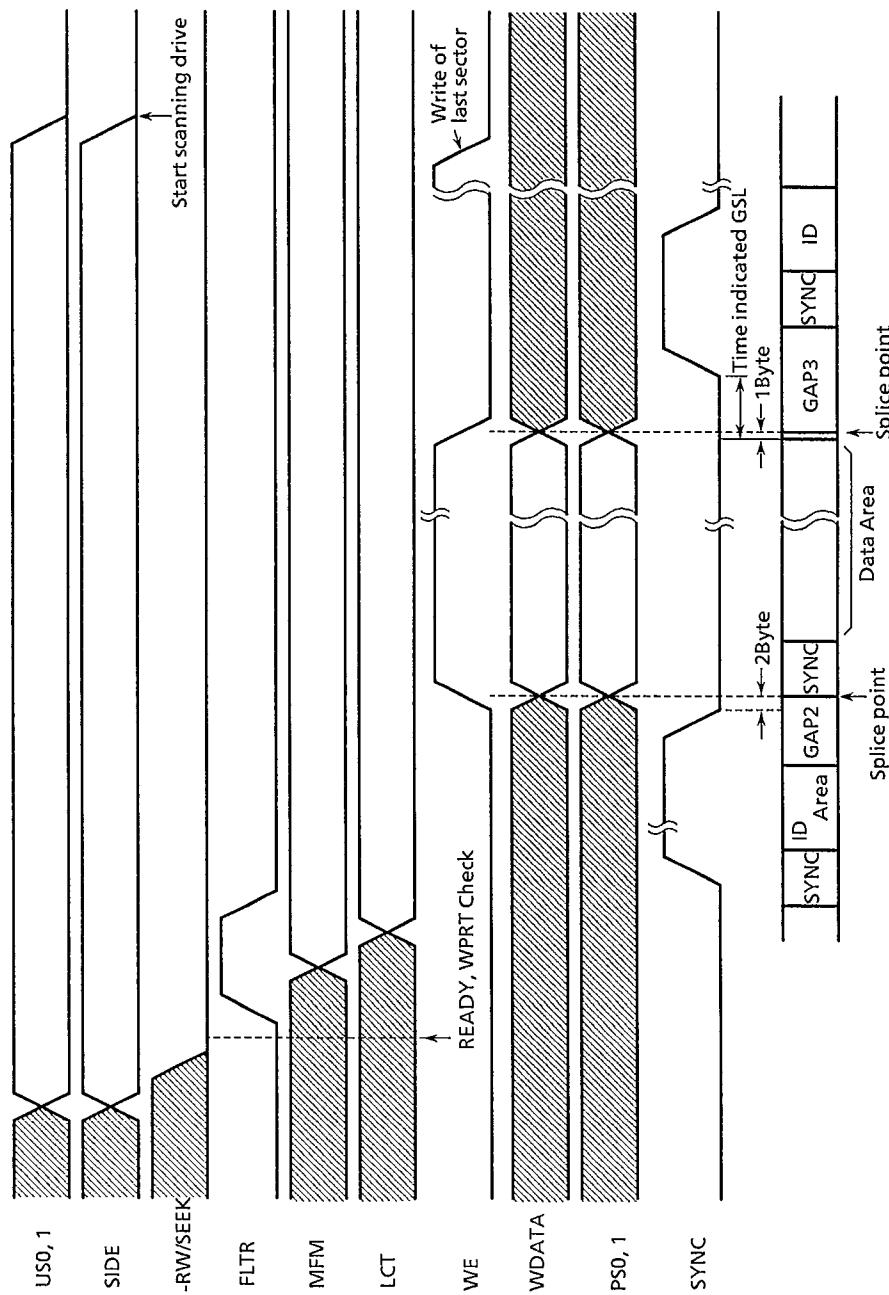

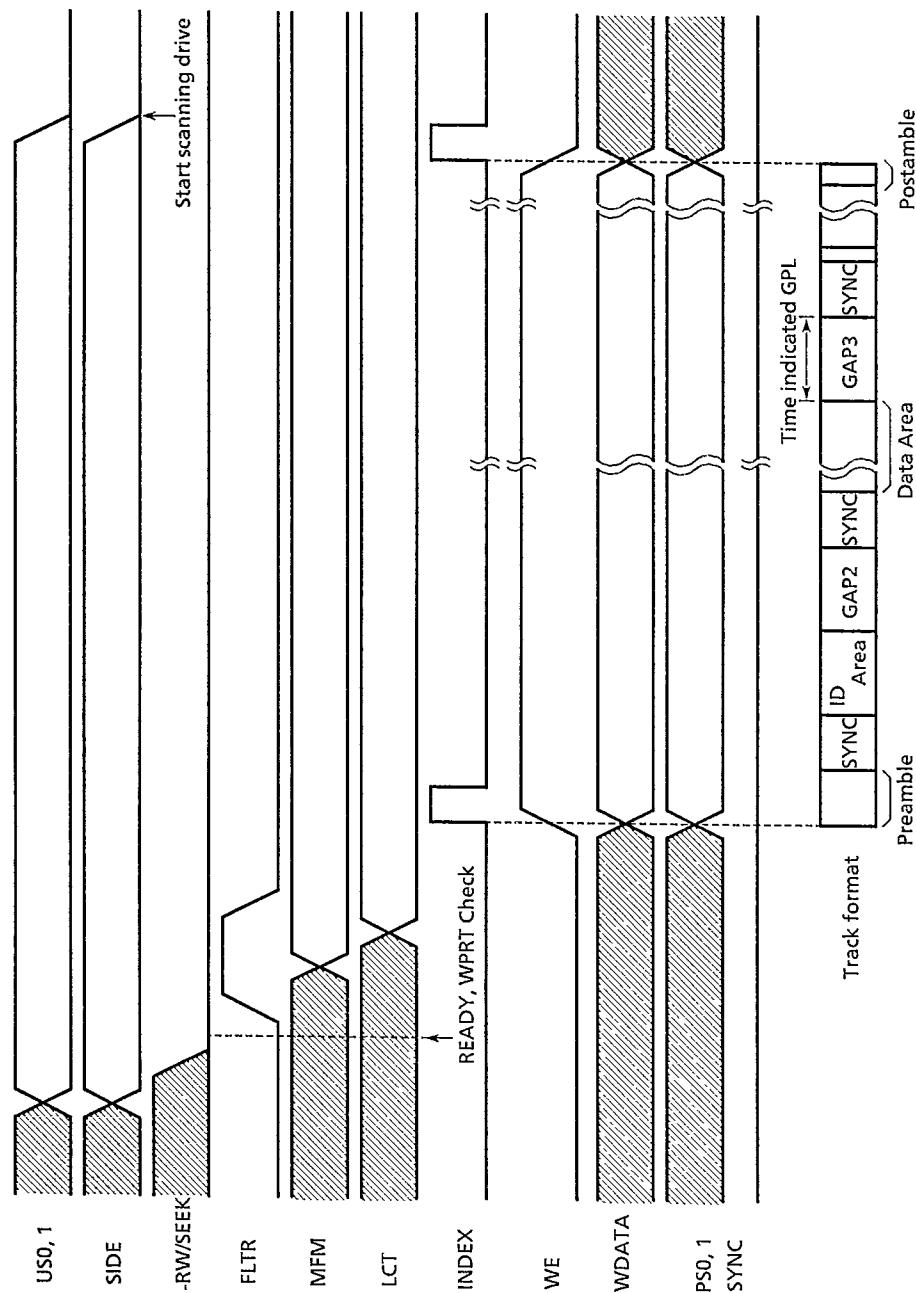

## 5.2.4 TRACK FORMAT

## (1) IBM FORMAT

(\*1) Programmable

Missing Clock of Address Mark

| AM   | FM   |       | MFM  |       |

|------|------|-------|------|-------|

|      | DATA | CLOCK | DATA | CLOCK |

| IAM  | FC   | D7    | C2   | 14    |

| IDAM | FE   | C7    | A1   | 0A    |

| DAM  | FB   | C7    | A1   | 0A    |

| DDAM | FB   | C7    | A1   | 0A    |

## FLOPPY DISK CONTROLLER

## (2) PFD Format

\* : Include Missing Clock Bits.

| Data | Clock |

|------|-------|

| C2   | 14    |

| A1   | 0A    |

FIG 5.2.4 WIDE ERASE FORMAT

TC8569AF-30

110989

852

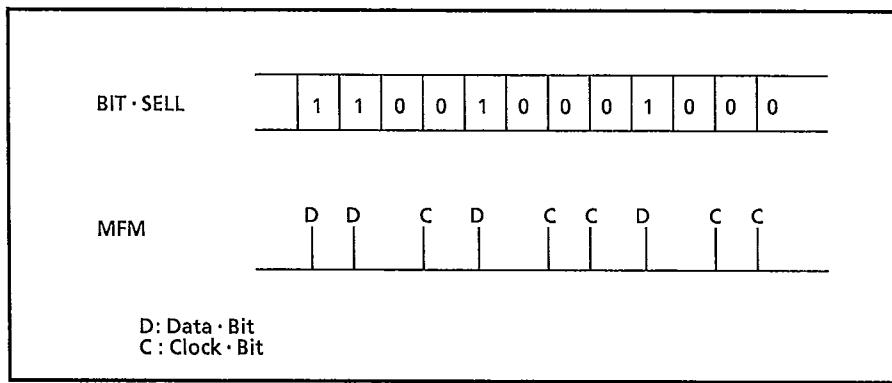

## 5.2.5 MFM RULES ( USE IN IBM DISKETTE 2D )

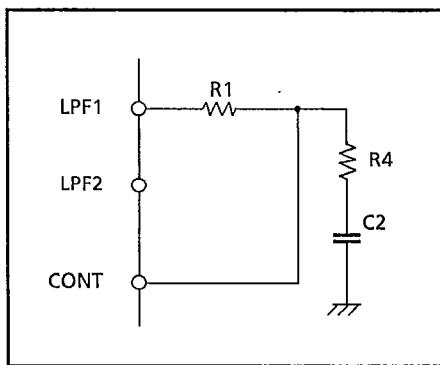

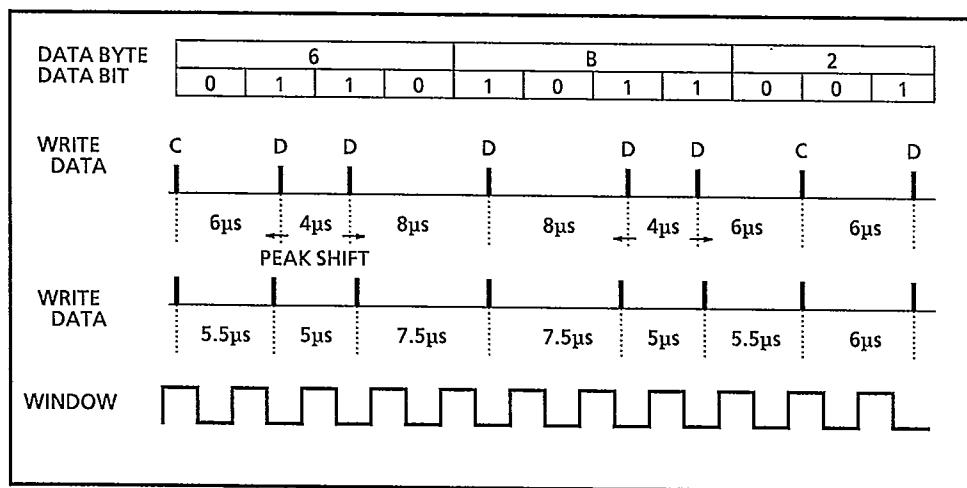

The data bit is written where the each bit will correspond to the center of the bit cell with "1". The clock bit is written at the head of the bit cell with "0" whose previous bit cell has "0".

FIG.5.2.5 MFM RULES

# FLOPPY DISK CONTROLLER

## 5.2.6 COMMAND TABLE

(X : Don't care)

## READ DATA COMMAND

| PHASE | R/W | D7 | D6  | D5 | D4 | D3 | D2  | D1  | D0  | REMARKS                                                  |

|-------|-----|----|-----|----|----|----|-----|-----|-----|----------------------------------------------------------|

| C     | W   | MT | MFM | SK | 0  | 0  | 1   | 1   | 0   | Command code                                             |

|       |     | X  | X   | X  | X  | X  | HS  | DS1 | DS0 | *                                                        |

|       |     |    |     |    |    |    | C   |     |     | *                                                        |

|       |     |    |     |    |    |    | H   |     |     | *                                                        |

|       |     |    |     |    |    |    | R   |     |     | *                                                        |

|       |     |    |     |    |    |    | N   |     |     | *                                                        |

|       |     |    |     |    |    |    | EOT |     |     | * ID information of starting sector of command execution |

|       |     |    |     |    |    |    | GPL |     |     |                                                          |

|       |     |    |     |    |    |    | DTL |     |     |                                                          |

|       |     |    |     |    |    |    |     |     |     |                                                          |

| E     |     |    |     |    |    |    |     |     |     | Data transfer                                            |

| R     | R   |    |     |    |    |    | ST0 |     |     |                                                          |

|       |     |    |     |    |    |    | ST1 |     |     |                                                          |

|       |     |    |     |    |    |    | ST2 |     |     |                                                          |

|       |     |    |     |    |    |    | C   |     |     | * ID information of end sector of command execution      |

|       |     |    |     |    |    |    | H   |     |     | *                                                        |

|       |     |    |     |    |    |    | R   |     |     | *                                                        |

|       |     |    |     |    |    |    | N   |     |     | *                                                        |

## WRITE DATA COMMAND

| PHASE | R/W | D7 | D6  | D5 | D4 | D3 | D2  | D1  | D0  | REMARKS                                                  |

|-------|-----|----|-----|----|----|----|-----|-----|-----|----------------------------------------------------------|

| C     | W   | MT | MFM | 0  | 0  | 0  | 1   | 0   | 1   | Command code                                             |

|       |     | X  | X   | X  | X  | X  | HS  | DS1 | DS0 | *                                                        |

|       |     |    |     |    |    |    | C   |     |     | *                                                        |

|       |     |    |     |    |    |    | H   |     |     | *                                                        |

|       |     |    |     |    |    |    | R   |     |     | *                                                        |

|       |     |    |     |    |    |    | N   |     |     | *                                                        |

|       |     |    |     |    |    |    | EOT |     |     | * ID information of starting sector of command execution |

|       |     |    |     |    |    |    | GPL |     |     |                                                          |

|       |     |    |     |    |    |    | DTL |     |     |                                                          |

|       |     |    |     |    |    |    |     |     |     |                                                          |

| E     |     |    |     |    |    |    |     |     |     | Data transfer                                            |

| R     | R   |    |     |    |    |    | ST0 |     |     |                                                          |

|       |     |    |     |    |    |    | ST1 |     |     |                                                          |

|       |     |    |     |    |    |    | ST2 |     |     |                                                          |

|       |     |    |     |    |    |    | C   |     |     | * ID information of end sector of command execution      |

|       |     |    |     |    |    |    | H   |     |     | *                                                        |

|       |     |    |     |    |    |    | R   |     |     | *                                                        |

|       |     |    |     |    |    |    | N   |     |     | *                                                        |

## WRITE DELETED DATA COMMAND

| PHASE | R/W | D7 | D6  | D5 | D4 | D3  | D2 | D1  | D0  | REMARKS                                                  |

|-------|-----|----|-----|----|----|-----|----|-----|-----|----------------------------------------------------------|

| C     | W   | MT | MFM | 0  | 0  | 1   | 0  | 0   | 1   | Command code                                             |

|       |     | X  | X   | X  | X  | X   | HS | DS1 | DS0 | *                                                        |

|       |     |    |     |    |    | C   |    |     |     | *                                                        |

|       |     |    |     |    |    | H   |    |     |     | *                                                        |

|       |     |    |     |    |    | R   |    |     |     | *                                                        |

|       |     |    |     |    |    | N   |    |     |     | *                                                        |

|       |     |    |     |    |    | EOT |    |     |     | * ID information of starting sector of command execution |

|       |     |    |     |    |    | GPL |    |     |     |                                                          |

|       | E   |    |     |    |    | DTL |    |     |     | Data transfer                                            |

| R     | R   |    |     |    |    | ST0 |    |     |     |                                                          |

|       |     |    |     |    |    | ST1 |    |     |     |                                                          |

|       |     |    |     |    |    | ST2 |    |     |     |                                                          |

|       |     |    |     |    |    | C   |    |     |     | *                                                        |

|       |     |    |     |    |    | H   |    |     |     | *                                                        |

|       |     |    |     |    |    | R   |    |     |     | *                                                        |

|       |     |    |     |    |    | N   |    |     |     | *                                                        |

|       |     |    |     |    |    |     |    |     |     | * ID information of end sector of command execution      |

## READ DELETED DATA COMMAND

| PHASE | R/W | D7 | D6  | D5 | D4 | D3  | D2 | D1  | D0  | REMARKS                                                  |

|-------|-----|----|-----|----|----|-----|----|-----|-----|----------------------------------------------------------|

| C     | W   | MT | MFM | SK | 0  | 1   | 1  | 0   | 0   | Command code                                             |

|       |     | X  | X   | X  | X  | X   | HS | DS1 | DS0 | *                                                        |

|       |     |    |     |    |    | C   |    |     |     | *                                                        |

|       |     |    |     |    |    | H   |    |     |     | *                                                        |

|       |     |    |     |    |    | R   |    |     |     | *                                                        |

|       |     |    |     |    |    | N   |    |     |     | *                                                        |

|       |     |    |     |    |    | EOT |    |     |     | * ID information of starting sector of command execution |

|       |     |    |     |    |    | GPL |    |     |     |                                                          |

|       | E   |    |     |    |    | DTL |    |     |     | Data transfer                                            |

| R     | R   |    |     |    |    | ST0 |    |     |     |                                                          |

|       |     |    |     |    |    | ST1 |    |     |     |                                                          |

|       |     |    |     |    |    | ST2 |    |     |     |                                                          |

|       |     |    |     |    |    | C   |    |     |     | *                                                        |

|       |     |    |     |    |    | H   |    |     |     | *                                                        |

|       |     |    |     |    |    | R   |    |     |     | *                                                        |

|       |     |    |     |    |    | N   |    |     |     | *                                                        |

|       |     |    |     |    |    |     |    |     |     | * ID information of end sector of command execution      |

6

## || FLOPPY DISK CONTROLLER

## READ DIAGNOSTIC COMMAND

| PHASE | R/W | D7 | D6  | D5 | D4 | D3 | D2  | D1  | D0  | REMARKS                                                  |

|-------|-----|----|-----|----|----|----|-----|-----|-----|----------------------------------------------------------|

| C     | W   | 0  | MFM | 0  | 0  | 0  | 0   | 1   | 0   | Command code                                             |

|       |     | X  | X   | X  | X  | X  | HS  | DS1 | DS0 | *                                                        |

|       |     |    |     |    |    |    | C   |     |     | *                                                        |

|       |     |    |     |    |    |    | H   |     |     | *                                                        |

|       |     |    |     |    |    |    | R   |     |     | R = No meaning                                           |

|       |     |    |     |    |    |    | N   |     |     | *                                                        |

|       |     |    |     |    |    |    | EOT |     |     | *                                                        |

|       |     |    |     |    |    |    | GPL |     |     | * ID information of starting sector of command execution |

|       |     |    |     |    |    |    | DTL |     |     |                                                          |

| E     |     |    |     |    |    |    |     |     |     | Data transfer                                            |

| R     | R   |    |     |    |    |    | ST0 |     |     |                                                          |

|       |     |    |     |    |    |    | ST1 |     |     |                                                          |

|       |     |    |     |    |    |    | ST2 |     |     |                                                          |

|       |     |    |     |    |    |    | C   |     |     | *                                                        |

|       |     |    |     |    |    |    | H   |     |     | *                                                        |

|       |     |    |     |    |    |    | R   |     |     | *                                                        |

|       |     |    |     |    |    |    | N   |     |     | *                                                        |

## READ ID COMMAND

| PHASE | R/W | D7 | D6  | D5 | D4 | D3 | D2  | D1  | D0  | REMARKS                                                |

|-------|-----|----|-----|----|----|----|-----|-----|-----|--------------------------------------------------------|

| C     | W   | 0  | MFM | 0  | 0  | 1  | 0   | 1   | 0   | Command code                                           |

|       |     | X  | X   | X  | X  | X  | HS  | DS1 | DS0 |                                                        |

| E     |     |    |     |    |    |    | ST0 |     |     |                                                        |

| R     | R   |    |     |    |    |    | ST1 |     |     |                                                        |

|       |     |    |     |    |    |    | ST2 |     |     |                                                        |

|       |     |    |     |    |    |    | C   |     |     | *                                                      |

|       |     |    |     |    |    |    | H   |     |     | *                                                      |

|       |     |    |     |    |    |    | R   |     |     | *                                                      |

|       |     |    |     |    |    |    | N   |     |     | *                                                      |

|       |     |    |     |    |    |    |     |     |     | * ID information which read out during execution-phase |

TC8569AF-34

110989

856

## FLOPPY DISK CONTROLLER

## FORMAT COMMAND

| PHASE | R/W | D7 | D6  | D5 | D4  | D3  | D2 | D1  | D0  | REMARKS                  |

|-------|-----|----|-----|----|-----|-----|----|-----|-----|--------------------------|

| C     | W   | 0  | MFM | 0  | 0   | 1   | 1  | 0   | 1   | Command code             |

|       |     | x  | x   | x  | x   | x   | HS | DS1 | DS0 |                          |

|       |     |    |     |    |     | N   |    |     |     |                          |

|       |     |    |     |    |     | SC  |    |     |     |                          |

|       |     |    |     |    |     | GPL |    |     |     |                          |

|       |     |    |     |    |     | D   |    |     |     |                          |

| E     |     |    |     |    |     |     |    |     |     | Data transfer            |

| R     | R   |    |     |    | ST0 |     |    |     |     | *<br>*<br>* = No meaning |

|       |     |    |     |    | ST1 |     |    |     |     |                          |

|       |     |    |     |    | ST2 |     |    |     |     |                          |

|       |     |    |     |    | C   |     |    |     |     |                          |

|       |     |    |     |    | H   |     |    |     |     |                          |

|       |     |    |     |    | R   |     |    |     |     |                          |

|       |     |    |     |    | N   |     |    |     |     |                          |

## SEEK COMMAND

| PHASE | R/W | D7 | D6 | D5 | D4 | D3  | D2 | D1  | D0  | REMARKS      |

|-------|-----|----|----|----|----|-----|----|-----|-----|--------------|

| C     | W   | 0  | 0  | 0  | 0  | 1   | 1  | 1   | 1   | Command code |

|       |     | x  | x  | x  | x  | x   | x  | DS1 | DS0 |              |

|       |     |    |    |    |    | NCN |    |     |     |              |

|       |     |    |    |    |    |     |    |     |     |              |

| E     |     |    |    |    |    |     |    |     |     | Seek         |

## RECALIBRATE COMMAND

| PHASE | R/W | D7 | D6 | D5 | D4 | D3 | D2 | D1  | D0  | REMARKS      |

|-------|-----|----|----|----|----|----|----|-----|-----|--------------|

| C     | W   | 0  | 0  | 0  | 0  | 0  | 1  | 1   | 1   | Command code |

|       |     | x  | x  | x  | x  | x  | x  | DS1 | DS0 |              |

| E     |     |    |    |    |    |    |    |     |     | RECALIBRATE  |

**FLOPPY DISK CONTROLLER**

## SENSE INTERRUPT COMMAND

| PHASE | R/W | D7 | D6 | D5 | D4  | D3 | D2 | D1 | D0 | REMARKS      |

|-------|-----|----|----|----|-----|----|----|----|----|--------------|

| C     | W   | 0  | 0  | 0  | 0   | 1  | 0  | 0  | 0  | Command code |

| R     | R   |    |    |    | ST0 |    |    |    |    |              |

|       |     |    |    |    | PCN |    |    |    |    |              |

## SPECIFY COMMAND

| PHASE | R/W | D7 | D6 | D5  | D4 | D3 | D2 | D1 | D0 | REMARKS      |

|-------|-----|----|----|-----|----|----|----|----|----|--------------|

|       |     | 0  | 0  | 0   | 0  | 0  | 0  | 1  | 1  |              |

| C     | W   |    |    | SRT |    | X  | X  | X  | X  | Command code |

|       |     | X  | X  | X   | X  | X  | X  | X  | ND |              |

## SENSE DEVICE STATUS COMMAND

| PHASE | R/W | D7 | D6 | D5  | D4 | D3 | D2 | D1  | D0  | REMARKS      |

|-------|-----|----|----|-----|----|----|----|-----|-----|--------------|

| C     | W   | 0  | 0  | 0   | 0  | 0  | 1  | 0   | 0   | Command code |

|       |     | X  | X  | X   | X  | X  | HS | DS1 | DS0 |              |

| R     | R   |    |    | ST3 |    |    |    |     |     |              |

## CONFIG COMMAND

| PHASE | R/W | D7 | D6 | D5 | D4 | D3 | D2 | D1 | D0  | REMARKS      |

|-------|-----|----|----|----|----|----|----|----|-----|--------------|

| C     | W   | 0  | 0  | 0  | 1  | 0  | 0  | 1  | 0   | Command code |

|       |     | X  | X  | X  | X  | X  | X  | WG | FMT |              |

## INVALID COMMAND

| PHASE | R/W | D7 | D6 | D5 | D4 | D3 | D2  | D1 | D0 | REMARKS                |

|-------|-----|----|----|----|----|----|-----|----|----|------------------------|

| C     | W   |    |    |    |    |    |     |    |    | The other command code |

| R     | R   |    |    |    |    |    | ST0 |    |    | ST0 = 80H              |

TABLE 5.2 SYMBOLS in the COMMAND TABLE (1/2)

| SYMBOL | NAME                    | DESCRIPTION                                                                          |

|--------|-------------------------|--------------------------------------------------------------------------------------|

| C      | Cylinder Number         | Indicates the cylinder number.                                                       |

| D      | Data                    | Indicates the data pattern which is going to be written into data field.             |

| D7-D0  | Data Bus                | 8 bit data bus , D7 is MSB and D0 is LSB.                                            |

| DS1, 0 | Drive Select            | Indicates the drive number (0, 1, 2, 3).                                             |

| DTL    | DATA Length             | IF N = 00, indicates the data length per sector which is going to be processed.      |

| EOT    | End of Track            | Indicates the last Sector of a cylinder.                                             |

| FMT    | Format                  | Indicates whether IBM format or pre-erase format is used.                            |