#### High-performance Video Signal Switchers

# Ultra Wide Band Triple Circuits Video Signal Switchers

**BA7657F,BH7659FS**No.11066EAT03

#### Description

The BA7657F, and BH7659FS are ICs that have been developed for use in PC monitors, HDTVs (high definition televisions), and other high-resolution display devices. In addition to their wide-range switching circuits for RGB signals, HD signals, and VD signals, the A7657F feature a separation (BUNRI) circuit for the synchronization signal that is superposed on the G signal, while the BH7659FS features an on-chip switch for I<sup>2</sup>C bus signals (SDA and SCL). These ICs can be used to simplify the input block configuration in advanced display devices.

#### Features

- 1) Operates on 5 V single power supply.

- 2) Built-in wide-range RGB signal switches. (BA7657F :fc = 230 MHz) (BH7659FS:fc = 250 MHz)

- 3) Built-in switching circuit for HD signal and VD signal.

- 4) Built-in separation (BUNRI) circuit for synchronization signal superposed on G signal. (BA7657F)

- 5) Built-in switch for I<sup>2</sup>C bus signals (SDA and SCL). (BH7659FS)

- 6) Built-in power saving function. (BH7659FS)

#### Applications

PC monitors, Plasma displays, LCD monitors, and Other devices that use wide-range RGB signal switching.

#### Line up matrix

| Parameter                                             | BA7657F                      | BH7659FS                         |

|-------------------------------------------------------|------------------------------|----------------------------------|

| Circuit current (mA)                                  | 35                           | 25                               |

| Circuit current during low-power mode (mA)            | _                            | 14                               |

| RGB signal SW block frequency characteristics (MHz)   | 230                          | 250                              |

| Synchronization signal SW block circuit configuration | 2 digital switching circuits | 4 CMOS analog switching circuits |

| Synchronization signal separation circuit             | <b>✓</b>                     | _                                |

| Package                                               | SOP24                        | SSOP-A32                         |

#### ●Absolute Maximum Ratings(Ta=25°C)

| Parameter             |          | Symbol | Ratings  | Unit  |

|-----------------------|----------|--------|----------|-------|

| Supply voltage        |          | Vcc    | 8.0      | V     |

| Dower dissination     | BA7657F  | Pd     | 550      | mW    |

| Power dissipation     | BH7659FS | Fu     | 800      | IIIVV |

| Operating temperature |          | Topr   | -25~+75  | °C    |

| Storage temperature   |          | Tstg   | -55~+125 | °C    |

<sup>\*\*</sup>Deratings is done at 5.5mW/°C (BA7657F), 8mW/°C (BA7659FS) above Ta=25°C.

#### ●Operating Range(Ta=25°C)

| Parameter      | Symbol |      | Unit |      |      |

|----------------|--------|------|------|------|------|

| Faianielei     | Symbol | Min. | Тур. | Max. | Unit |

| Supply voltage | Vcc    | 4.5  | 5.0  | 5.5  | V    |

<sup>\*</sup>This product is not designed for protection against radioactive rays.

#### Electrical characteristics

OBA7657F(Unless otherwise noted, Ta=25°C, Vcc=5.0V)

| OBA7657F(Unless otherwise noted,      |        |      | Limits |      | 1.1-20 | O Pro             |

|---------------------------------------|--------|------|--------|------|--------|-------------------|

| Parameter                             | Symbol | Min. | Тур.   | Max. | Unit   | Conditions        |

| Circuit current                       | ICC    | 20   | 35     | 50   | mA     | _                 |

| ⟨Analog SW block⟩                     |        |      |        |      |        |                   |

| Maximum output level                  | Vom    | 2.8  | _      | _    | VP-P   | f=1kHz            |

| Voltage gain                          | Gv     | -1.0 | -0.5   | 0    | dB     | f=1MHz,VIN=1VP-P  |

| Input pin voltage gain differential   | ΔGVI   | -0.2 | 0      | 0.2  | dB     | f=1MHz,VIN=1VP-P  |

| Inter block voltage gain differential | Gvв    | -0.2 | 0      | 0.2  | dB     | f=1MHz,VIN=1VP-P  |

| Input pin cross talk1                 | CTI1   | _    | -50    | -40  | dB     | f=10MHz,VIN=1VP-P |

| Interblock crosstalk1                 | CTB1   | _    | -50    | -40  | dB     | f=10MHz,VIN=1VP-P |

| ⟨Digital SW block⟩                    |        |      |        |      |        |                   |

| "H" level input voltage               | VIH    | 1.8  | _      | _    | V      | _                 |

| "L" level input voltage               | VIL    | _    | _      | 1.2  | V      | _                 |

| "H" level input current               | lін    | 80   | 100    | 130  | μΑ     | VIN=5.0V          |

| "L" level input current               | lı∟    | -3   | -1     | _    | μA     | VIN=0V            |

| Rise time                             | TR     | _    | 30     | 50   | ns     | _                 |

| Fall time                             | TF     | _    | 30     | 50   | ns     | _                 |

| Rise delay time                       | TRD    | _    | 50     | 80   | ns     | _                 |

| Fall delay time                       | TFD    | _    | 30     | 50   | ns     | _                 |

| "H" level output voltage              | Vон    | 3.0  | 3.7    | _    | V      | _                 |

| "L" level output voltage              | Vol    | _    | 0.2    | 0.4  | V      | _                 |

| "H" level output current              | Іон    | -400 | _      | _    | μΑ     | _                 |

| "L" level output current              | lol    | 5    | _      | _    | mA     | _                 |

| ⟨Synchronization signal separation    | block  |      |        |      |        |                   |

| Minimum SYNC separation level         | VSMin. | -50  | _      | 50   | mVP-P  | _                 |

| "H" level output voltage              | Vон    | 4.5  | 5.0    | _    | V      | _                 |

| "L" level output voltage              | Vol    | _    | 0.2    | 0.5  | V      | _                 |

| "L" level output current              | lol    | 2    | _      | _    | mA     | _                 |

| Rise time                             | TR     | _    | 80     | 130  | ns     | _                 |

| Fall time                             | TF     | _    | 30     | 80   | ns     | _                 |

| Rise delay time                       | Trd    | _    | 100    | 150  | ns     | _                 |

| Fall delay time                       | TFD    | _    | 100    | 150  | ns     | _                 |

| ⟨Control block⟩                       |        |      |        |      |        | -                 |

| "H" level input voltage               | VIH    | 1.8  | _      |      | V      | _                 |

| "L" level input voltage               | VIL    | _    | _      | 1.2  | V      | _                 |

| "H" level input current               | Іін    | 80   | 100    | 130  | μA     | _                 |

| "L" level input current               | lı∟    | -3   | -1     | _    | μΑ     | _                 |

|                                       |        |      |        |      |        |                   |

2/16

OBH7659FS(Unless otherwise noted, Ta=25°C, Vcc=5.0V)

|                                                                                                                                                                                                            | ns |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| \( \text{Min.} \) Typ. Max. \( \text{Kintire device} \) \( \text{Circuit current} \) ICc \( 15 \) 25 \( 35 \) mA \( - \text{Circuit current during power save} \) IPsv \( 7 \) 14 \( 22 \) mA \( PS="H" \) |    |

| Circuit current ICc 15 25 35 mA —  Circuit current during power save IPSV 7 14 22 mA PS="H"                                                                                                                |    |

| Circuit current during power save IPSV 7 14 22 mA PS="H"                                                                                                                                                   |    |

|                                                                                                                                                                                                            |    |

| ⟨R,G,B video SW⟩                                                                                                                                                                                           |    |

|                                                                                                                                                                                                            |    |

| Voltage gain         Gv         -1.0         -0.5         0         dB         f=10MHz                                                                                                                     |    |

| Interchannel relative gain $\triangle Gvc$ -0.5 0 0.5 dB f=10MHz                                                                                                                                           |    |

| Interblock relative gain $\triangle GVB$ -0.5 0 0.5 dB f=10MHz                                                                                                                                             |    |

| Output dynamic range Vom 2.6 - VP-P f=1kHz                                                                                                                                                                 |    |

| ⟨C-MOS analog SW⟩                                                                                                                                                                                          |    |

| On-resistance Ron - 200 400 $\Omega$ VIN=2.5V                                                                                                                                                              |    |

| Interchannel ON resistance differential $\triangle Ron$ — 20 40 $\Omega$ VIN=2.5V                                                                                                                          |    |

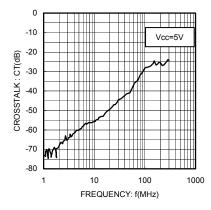

| Interchannel cross talk CT70 -55 dB f=150kHz                                                                                                                                                               |    |

| Transmission delay time tb - 20 - ns RL=100 Ω ,CL=50pF                                                                                                                                                     | :  |

| ⟨Control block⟩                                                                                                                                                                                            |    |

| "H" level voltage VH 3.5 - V -                                                                                                                                                                             |    |

| "L" level voltage VL — — 1.5 V —                                                                                                                                                                           |    |

#### Guaranteed design parameters

OBA7657F(Unless otherwise noted, Ta=25°C, Vcc=5.0V)

| Decemeter                                        | Cumbal            |      | Limits |      | Unit  | Conditions                     |  |  |

|--------------------------------------------------|-------------------|------|--------|------|-------|--------------------------------|--|--|

| Parameter                                        | Symbol            | Min. | Тур.   | Max. | Ullit | Conditions                     |  |  |

| ⟨Analog SW block⟩                                | ⟨Analog SW block⟩ |      |        |      |       |                                |  |  |

| Input pin cross talk 2                           | CTI2              | _    | -30    | -15  | dB    | f=230kHz, VIN=1VP-P            |  |  |

| Interblock cross talk 2                          | CTB2              | _    | -30    | -15  | dB    | f=230MHz,Vin=1V <sub>P-P</sub> |  |  |

| Frequency characteristic                         | Gf                | -6   | -3     | -1   | dB    | f=1MHz/230MHz, Vin=1VP-P       |  |  |

| Input pin frequency differential                 | ∆Gfl              | -1   | 0      | +1   | dB    | f=1MHz/100MHz, Vin=1VP-P       |  |  |

| Interblock frequency characteristic differential | ΔGfB              | -1   | 0      | +1   | dB    | f=1MHz/100MHz, VIN=1VP-P       |  |  |

| ⟨SYNC separation block⟩                          |                   |      |        |      |       |                                |  |  |

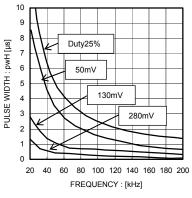

| SYNC separation frequency                        | fH-R              | 200  | _      | _    | kHz   | Input waveform **1             |  |  |

| SYNC separation pulse width 1                    | pwH1              | 3.0  | _      | _    | μs    | Input waveform **2 fH=20kHz    |  |  |

| SYNC separation pulse width 2                    | pwH2              | 0.5  | _      | _    | μs    | Input waveform **2 fH=100kHz   |  |  |

| SYNC separation pulse width 3                    | pwH3              | 0.3  | _      | _    | μs    | Input waveform **2 fH=200kHz   |  |  |

| SYNC separation level 1                          | VS1               | 300  | _      | _    | μs    | Input waveform **3 fH=20kHz    |  |  |

| SYNC separation level 2                          | VS2               | 100  | _      | _    | μs    | Input waveform **3 fH=100kHz   |  |  |

| SYNC separation level 3                          | VS3               | 60   | _      | _    | μs    | Input waveform **3 fH=200kHz   |  |  |

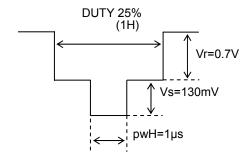

<sup>(</sup>Input waveform)

#### Period of horizontal synchronization signal

#### OBH7659FS(Unless otherwise noted, Ta=25°C, Vcc=5.0V)

| Parameter                                       | Cumbal           | Limits |      | Unit | Conditions |            |  |  |

|-------------------------------------------------|------------------|--------|------|------|------------|------------|--|--|

| Parameter                                       | Symbol           | Min.   | Тур. | Max. | Unit       | Conditions |  |  |

| ⟨R/G/B video SW⟩                                |                  |        |      |      |            |            |  |  |

| Frequency characteristics 1                     | f1               | -3.0   | 0    | +1.0 | dB         | f=50MHz    |  |  |

| Frequency characteristics 2                     | f2               | -6.0   | -3   | -1.0 | dB         | f=250MHz   |  |  |

| Interchannel relative frequency characteristics | Δfc              | -0.5   | 0    | 0.5  | dB         | f=50MHz    |  |  |

| Interblock relative frequency characteristics   | ΔfB              | -0.5   | 0    | 0.5  | dB         | f=50MHz    |  |  |

| Interchannel cross talk 1                       | CTC1             | _      | -50  | -35  | dB         | f=50kHz    |  |  |

| Interchannel cross talk 2                       | CTC2             | _      | -30  | -15  | dB         | f=250MHz   |  |  |

| Interblock cross talk 1                         | СТв1             | _      | -50  | -35  | dB         | f=50MHz    |  |  |

| Interblock cross talk 2                         | CT <sub>B2</sub> | _      | -30  | -15  | dB         | f=250MHz   |  |  |

X1 VS and pwH are variable. VS and pwH are inter-related. See the characteristics diagram.

<sup>※2</sup> VS = 130 mW and pwH are variable.

<sup>3</sup> pwH = 1  $\mu$ s and VS are variable.

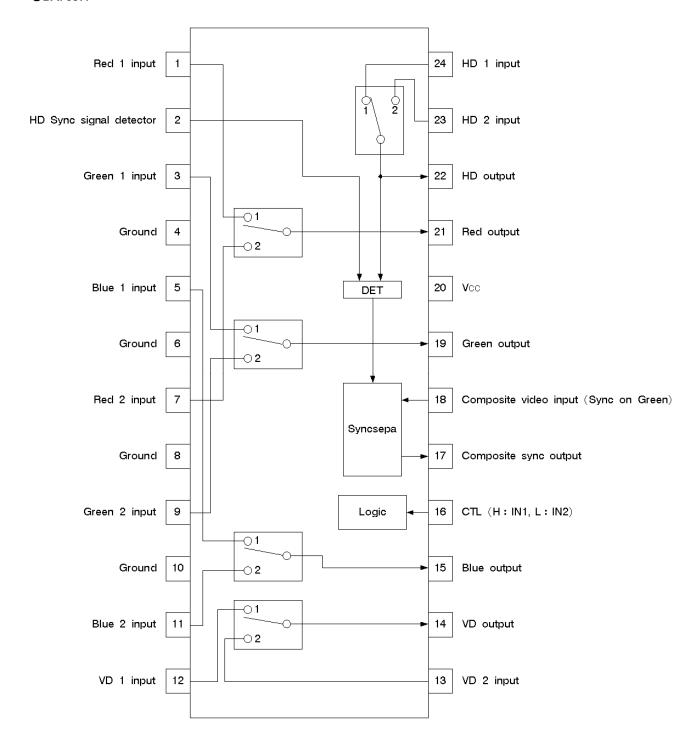

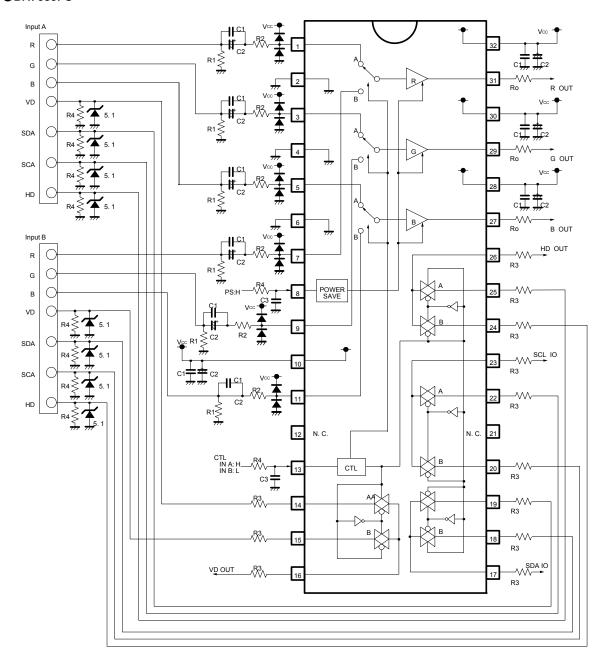

#### ●Block diagram ○BA7657F

Fig.1

Fig.2

### ●Pin descriptions (BA7657F)

|                             | DBA7657F                                                                               |                                                  |                     |                                                                                                                         |  |  |  |

|-----------------------------|----------------------------------------------------------------------------------------|--------------------------------------------------|---------------------|-------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Pin<br>No.                  | Pin name                                                                               | Reference potential                              | Equivalent circuit  | Function                                                                                                                |  |  |  |

| 1<br>3<br>5<br>7<br>9<br>11 | Red1 Input<br>Green1 Input<br>Blue1 Input<br>Red2 Input<br>Green2 Input<br>Blue2 Input | 3.7V<br>when selected<br>0V<br>when not selected | 100 6.8k            | 2-channel switching of R,<br>G, and B signals.<br>Select between:<br>CTL: H input1<br>CTL: L input2                     |  |  |  |

| 15<br>19<br>21              | Blue output<br>Green output<br>Red output                                              | 2.0V                                             | 50 ₹ Vcc            | Output pins for RGB signals. Insert resistance from 100 to 300 Ω near the pins to suppress f peaks at high frequencies. |  |  |  |

| 16                          | Control                                                                                | H≧1.8V<br>L≦1.2V                                 | Vcc \$35k           | CTL pins Select between: CTL: H input1 CTL: L input2                                                                    |  |  |  |

| 12<br>13<br>23<br>24        | VD1 input<br>VD2 input<br>HD2 input<br>HD1 input                                       | H≧1.8V<br>L≦1.2V                                 | 12, 13<br>23, 24pin | 2-channel switching of VD and<br>HD signals.<br>Select between:<br>CTL: H input1<br>CTL: L input2                       |  |  |  |

| 14<br>22                    | VD output<br>HD output                                                                 | Vон≧3.0V<br>Vo∟≦10.5V                            | 2.0k 100 14, 22pin  | Output pins for vertical synchronization signal (VD) And horizontal synchronization signal (HD).                        |  |  |  |

#### **OBA7657F**

| OBA765      | 07F                        |                     |                                          |                                                                                                                                                                      |

|-------------|----------------------------|---------------------|------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Pin<br>No.  | Pin name                   | Reference potential | Equivalent circuit                       | Function                                                                                                                                                             |

| 18          | Composite Video input      | 2.5V                | 25 k from DET out  18pin                 | Input pin for composite signal (Sync on Green).                                                                                                                      |

| 2           | HD Sync<br>Signal detector | _                   | from HD out to sync sepa  Vcc  25k  2pin | This pin is used to detect whether or not the HD signal is being input. When the HD signal is being input, the synchronization signal separation circuit is stopped. |

| 17          | Composite sync output      | _                   | 17pin                                    | Synchronization signal output pin  Synchronization separation is performed for the input signal from pin 18 if the Hb signal is not being input.                     |

| 20          | Vcc                        | 5V                  | _                                        | Insert a decoupling capacitor near the pin.                                                                                                                          |

| 4<br>6<br>8 | GND                        | 0V                  | _                                        | Use as large a GND pattern area as possible.                                                                                                                         |

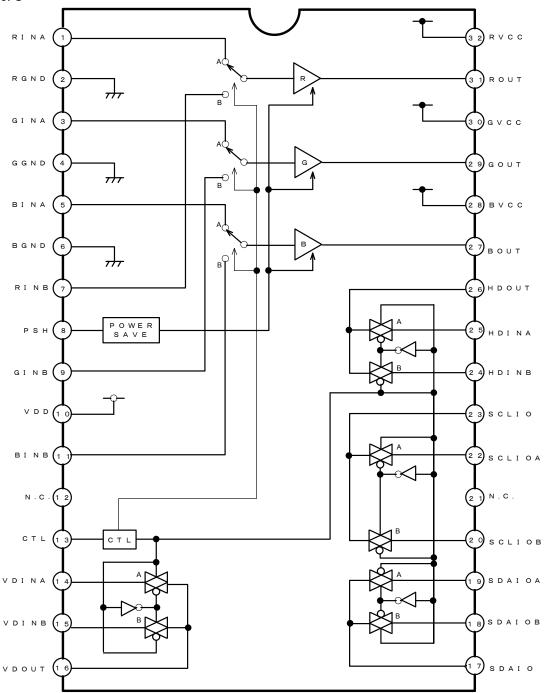

# ●Pin descriptions (BH7659FS) OBH7659FS

| Pin<br>NO             | Pin name                                                                                                                                                                                                                                             | Reference potential                              | Equivalent circuit | Function                                                                                                                                                     |

|-----------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------|--------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1<br>3<br>5<br>7<br>9 | R chroma signal input pin A (RINA) G chroma signal input pin A (GINA) B chroma signal input pin A (BINA) R chroma signal input pin B (RINB) G chroma signal input pin B (GINB) B chroma signal input pin B (GINB) B chroma signal input pin B (BINB) | 3.5V<br>when selected<br>0V<br>when not selected | 3.7V 10k 2k        | RGB signals are switched in two channels. When selected by SW, the DC potential is approximately 3.5V, and when not selected, the DC potential is about 0 V. |

| 27<br>29<br>31        | B chroma signal input pin (BOUT) G chroma signal input pin (GOUT) R chroma signal input pin (ROUT)                                                                                                                                                   | 1.85V                                            | 500\$ \$ 2k        | Power save function is used when PSH pin is set to high level.                                                                                               |

| 8 13                  | Power save input pin (PSH)  Control input pin (CTL)                                                                                                                                                                                                  | 0V                                               | 3.25V              | PSH Pin Power save off ≤1.5V Power save on ≥3.5V  CTL Pin Input A≥3.5V Input B≤1.5V                                                                          |

| OBH765         | 948                                                                                      |                     |                    | <del>_</del>                                                                      |

|----------------|------------------------------------------------------------------------------------------|---------------------|--------------------|-----------------------------------------------------------------------------------|

| Pin<br>No.     | Pin name                                                                                 | Reference potential | Equivalent circuit | Function                                                                          |

| 14<br>15<br>16 | VD signal input pin A (VDINA) VD signal input pin B (VDINB) VD signal output pin (VDOUT) | ·                   | Vpo <b>◆</b>       |                                                                                   |

| 17             | SDA signal output pin<br>(SDAIO)                                                         |                     |                    |                                                                                   |

| 18<br>19       | SDA signal input pin B<br>(SDAIOB)<br>SDA signal input pin A                             |                     |                    | Vp, Hp, SDA, and SCL are                                                          |

|                | (SDAIOA)                                                                                 | 0V                  |                    | switched in two channels.<br>Bidirectional access (I/O) is<br>enabled by the CMOS |

| 20             | SCL signal input pin B<br>(SCLIOB)<br>SCL signal input pin A                             |                     | <del></del>        | analog SW.                                                                        |

| 23             | (SCLIOA) SCL signal output pin (SCLIO)                                                   |                     |                    |                                                                                   |

| 24<br>25       | HD signal input pin B<br>(HDINB)<br>HD signal input pin A                                |                     |                    |                                                                                   |

| 26             | (HDINA)<br>HD signal output pin                                                          |                     |                    |                                                                                   |

| 2              | (HDOUT)  R GND pin (RGND)                                                                | 0V                  | _                  | This is the GND pin for the R video SW block.                                     |

| 4              | G GND pin<br>(GGND)                                                                      | 0V                  | _                  | This is the GND pin for the B video SW block.                                     |

| 6              | B GND pin<br>(BGND)                                                                      | 0V                  | _                  | This is the GND pin for the G video SW block , C-MOS SW block.                    |

| 10             | C-MOS supply voltage pin (VDD)                                                           | 5V                  | _                  | This is the VDD pin for the C-MOS SW block.                                       |

| 28             | B supply voltage pin (BVcc)                                                              | 5V                  | _                  | This is the Vcc pin for the B video SW block                                      |

| 30             | G supply voltage pin (GVcc)                                                              | 5V                  | _                  | This is the Vcc pin for the G video SW block                                      |

| 32             | R supply voltage pin (RVcc)                                                              | 5V                  | _                  | This is the Vcc pin for the R video SW block                                      |

#### Description of operations

#### **OBA7657F**

#### 1) Analog SW block

Two channels of RGB signals can be switched. IN1 can be selected when high-level voltage is applied to the CTL pin, and IN2 can be selected when low level voltage is applied.

#### 2) Digital SW block

This block switches between two channels of HD and VD ynchronization signals. HD and VD synchronization signals are output for IN1 when high-level voltage is applied to the CTL pin, and these signals are output for IN2 when a low-level voltage is applied to the CTL pin.

#### 3) Synchronization signal separation block

This block separates composite signals (Sync on Green) and synchronization signals and outputs positive-electrode composite synchronization signals. When an Hb signal is being input, the synchronization signal detector operates and stops the synchronization signal separation circuit. A low-level output voltage is used for output. The time at which the synchronization signal separation circuit will be stopped can be set using external time constants for the circuit detection pin.

#### I/O relations

| Input |    |               | Output |    |                |  |

|-------|----|---------------|--------|----|----------------|--|

| HD    | VD | Sync on Green | HD     | VD | Composite Sync |  |

| _     | _  | 0             | _      | _  | 0              |  |

| 0     | _  | 0             | 0      | _  | _              |  |

| _     | 0  | 0             | _      | 0  | 0              |  |

| 0     | 0  | 0             | 0      | 0  | _              |  |

| 0     | _  | _             | 0      | _  | _              |  |

| _     | 0  | _             | _      | 0  | _              |  |

| 0     | 0  | _             | 0      | 0  | _              |  |

#### **OBH7659FS**

#### 1) Analog SW block

R, G, and B chroma signals are switched in two channels. INA is selected by applying a high-level voltage to the CTL pin, and INB is selected by applying a low-level voltage. When the power save pin (pin 8) is set to high level, the current to the SW block's output transistors is reduced to lower the circuit current. Even during low power mode, signal switching can be performed normally as long as there is no drop in frequency characteristics.

#### 2) CMOS analog SW block

SDA and SDC signals are switched via an  $I^2C$  bus to handle two channels of HD and VD synchronization signals, and to exchange information bidirectional between a computer and a monitor. The switching circuits used by this IC handle are configured as CMOS analog switches in order to handle  $I^2C$  BUS signals and to transmit input and output signals bidirectional. (ON resistance: Ron 200  $\Omega$  typ.)

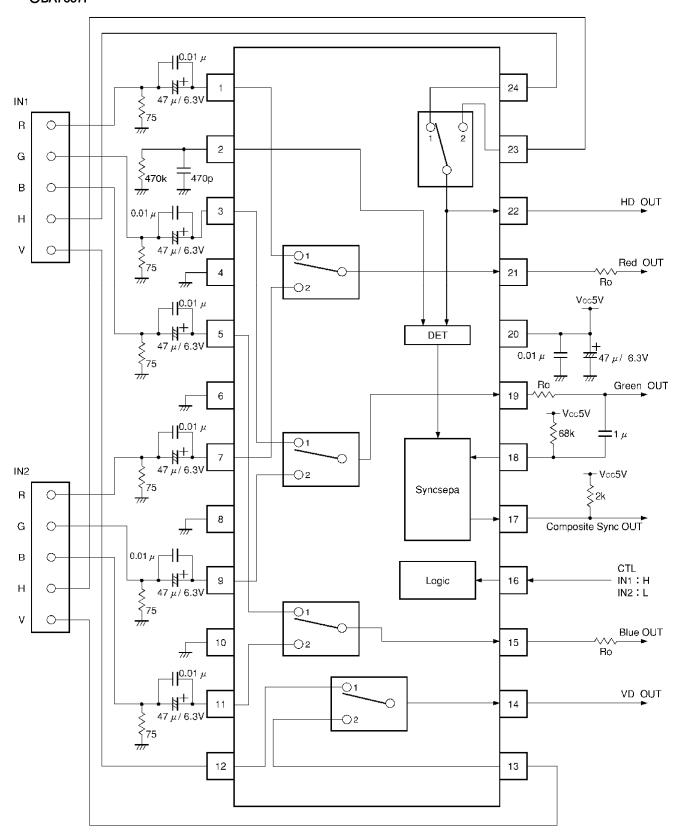

# ●Application circuit ○BA7657F

Fig.3

Fig.4

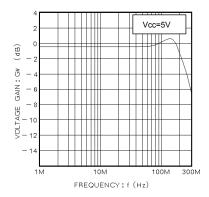

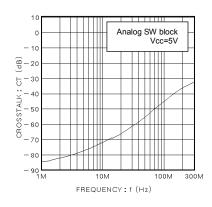

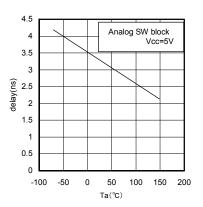

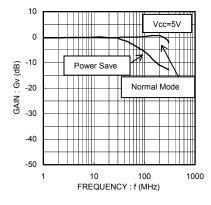

#### ●Reference data OBA7657F

Fig.5 Frequency characteristic

Fig.6 Interchannel crosstalk

Fig.7 Input/output delay timevs.

Temperatur

Fig.8 Minimum SYNC separation characteristic

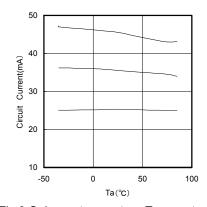

Fig.9 Quiescent current vs. Temperature

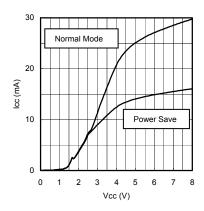

Fig.10 Circuit current vs. Supply voltage

Fig.11 interchannel crosstalk

Fig.12 Frequency characteristics

#### Notes for use

#### **OBA7657F. BH7659FS**

- 1) Numbers and data in entries are representative design values and are not guaranteed values of the items.

- 2) Although we are confident in recommending the sample application circuits, carefully check their characteristics further when using them. When modifying externally attached component constants before use, determine them so that they have sufficient margins by taking into account variations in externally attached components and the Rohm LSI, not only for static characteristics but also including transient characteristics.

- 3) Absolute maximum ratings

If applied voltage, operating temperature range, or other absolute maximum ratings are exceeded, the LSI may be damaged. Do not apply voltages or temperatures that exceed the absolute maximum ratings. If you think of a case in which absolute maximum ratings are exceeded, enforce fuses or other physical safety measures and investigate how not to apply the conditions under which absolute maximum ratings are exceeded to the LSI.

- 4) GND potential

- Make the GND pin voltage such that it is the lowest voltage even when operating below it. Actually confirm that the voltage of each pin does not become a lower voltage than the GND pin, including transient phenomena.

- Thermal design

- Perform thermal design in which there are adequate margins by taking into account the allowable power dissipation in actual states of use.

- 6) Shorts between pins and misinstallation

- When mounting the LSI on a board, pay adequate attention to orientation and placement discrepancies of the LSI. If it is misinstalled and the power is turned on, the LSI may be damaged. It also may be damaged if it is shorted by a foreign substance coming between pins of the LSI or between a pin and a power supply or a pin and a GND.

- Operation in strong magnetic fields

Adequately evaluate use in a strong magnetic field, since there is a possibility of malfunction.

#### **OBA7657F**

- 8) External resistance for analog SW block

- The frequency characteristics of analog switches vary according to the output load capacity. Set an external resistance value of R0 to keep frequency characteristics as flat as possible.

- 9) Polarity of input coupling capacitor

- When this IC is switched, variation is approximately 3.7 V when the input pin's DC voltage has been selected, but is 0 V when the input pin's DC voltage has not been selected. Therefore, the input coupling capacitor's polarity should be set so as to avoid applying a reverse voltage to capacitors, whether the input pin's DC voltage has been selected or not.

- 10) High-frequency characteristics of input coupling capacitor

- Since this IC handles signals at very high frequencies, when using an electrolytic capacitor as a coupling capacitor for input, be sure to insert high-frequency oriented ceramic capacitors (approximately 0.01 µF) in parallel.

- 11) Layout of target board

- Since this IC handles signals at very high frequencies, be sure to insert the power supply pin's decoupling capacitor close to the IC's power supply pin. Also, use as large a GND pattern as possible.

- 12) Switching speed

- Since this IC changes the DC voltage of input pins when switching, some time is required for switching. The amount of switching time can be determined by time constants that are in turn determined by the capacity of the coupling capacitor connected to the input pin, and the IC's internal input resistance. When using the recommended input coupling capacitor whose capacitance is  $47~\mu\text{F}$ , the switching time is approximately 0.5~seconds.

- 13) External resistance for analog SW block

- The frequency characteristics of analog switches vary according to the output load capacity. Set an external resistance value of R0 to keep frequency characteristics as flat as possible.

- 14) Polarity of input coupling capacitor

- When this IC is switched, variation is approximately 3.5 V when the input pin's DC voltage has been selected, but is 0 V when the input pin's DC voltage has not been selected. Therefore, the input coupling capacitor's polarity should be set so as to avoid applying a reverse voltage to capacitors, whether the input pin's DC voltage has been selected or not.

- 15) High frequency characteristics of input coupling capacitor

Since this IC handles signals at very high frequencies, when using an electrolytic capacitor as a coupling capacitor for input, be sure to insert high-frequency oriented ceramic capacitors (approximately 0.01 µF) in parallel.

- 16) Layout of target board

- Since this IC handles signals at very high frequencies, be sure to insert the power supply pin's decoupling capacitor close to the IC's power supply pin. Also, use as large a GND pattern as possible.

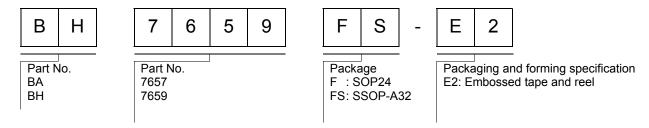

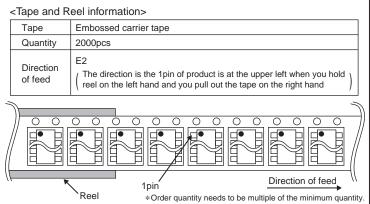

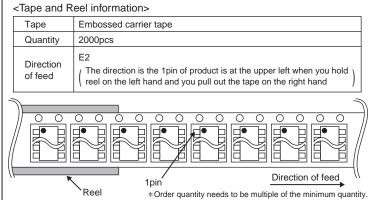

#### Ordering part number

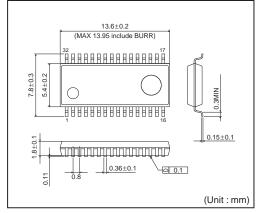

#### SOP24

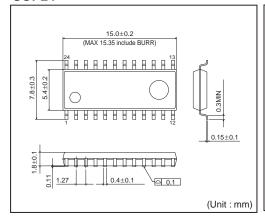

#### SSOP-A32

#### Notes

No copying or reproduction of this document, in part or in whole, is permitted without the consent of ROHM Co.,Ltd.

The content specified herein is subject to change for improvement without notice.

The content specified herein is for the purpose of introducing ROHM's products (hereinafter "Products"). If you wish to use any such Product, please be sure to refer to the specifications, which can be obtained from ROHM upon request.

Examples of application circuits, circuit constants and any other information contained herein illustrate the standard usage and operations of the Products. The peripheral conditions must be taken into account when designing circuits for mass production.

Great care was taken in ensuring the accuracy of the information specified in this document. However, should you incur any damage arising from any inaccuracy or misprint of such information, ROHM shall bear no responsibility for such damage.

The technical information specified herein is intended only to show the typical functions of and examples of application circuits for the Products. ROHM does not grant you, explicitly or implicitly, any license to use or exercise intellectual property or other rights held by ROHM and other parties. ROHM shall bear no responsibility whatsoever for any dispute arising from the use of such technical information.

The Products specified in this document are intended to be used with general-use electronic equipment or devices (such as audio visual equipment, office-automation equipment, communication devices, electronic appliances and amusement devices).

The Products specified in this document are not designed to be radiation tolerant.

While ROHM always makes efforts to enhance the quality and reliability of its Products, a Product may fail or malfunction for a variety of reasons.

Please be sure to implement in your equipment using the Products safety measures to guard against the possibility of physical injury, fire or any other damage caused in the event of the failure of any Product, such as derating, redundancy, fire control and fail-safe designs. ROHM shall bear no responsibility whatsoever for your use of any Product outside of the prescribed scope or not in accordance with the instruction manual.

The Products are not designed or manufactured to be used with any equipment, device or system which requires an extremely high level of reliability the failure or malfunction of which may result in a direct threat to human life or create a risk of human injury (such as a medical instrument, transportation equipment, aerospace machinery, nuclear-reactor controller, fuel-controller or other safety device). ROHM shall bear no responsibility in any way for use of any of the Products for the above special purposes. If a Product is intended to be used for any such special purpose, please contact a ROHM sales representative before purchasing.

If you intend to export or ship overseas any Product or technology specified herein that may be controlled under the Foreign Exchange and the Foreign Trade Law, you will be required to obtain a license or permit under the Law.

Thank you for your accessing to ROHM product informations. More detail product informations and catalogs are available, please contact us.

## ROHM Customer Support System

http://www.rohm.com/contact/