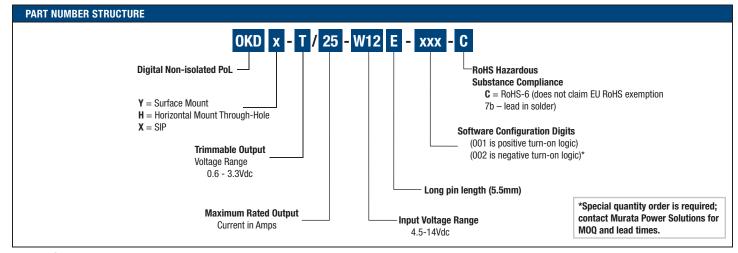

### Pkami OKDx-T/25-W12-xxx-C

25A Digital PoL DC-DC Converter Series

# Discontinued

#### **FEATURES**

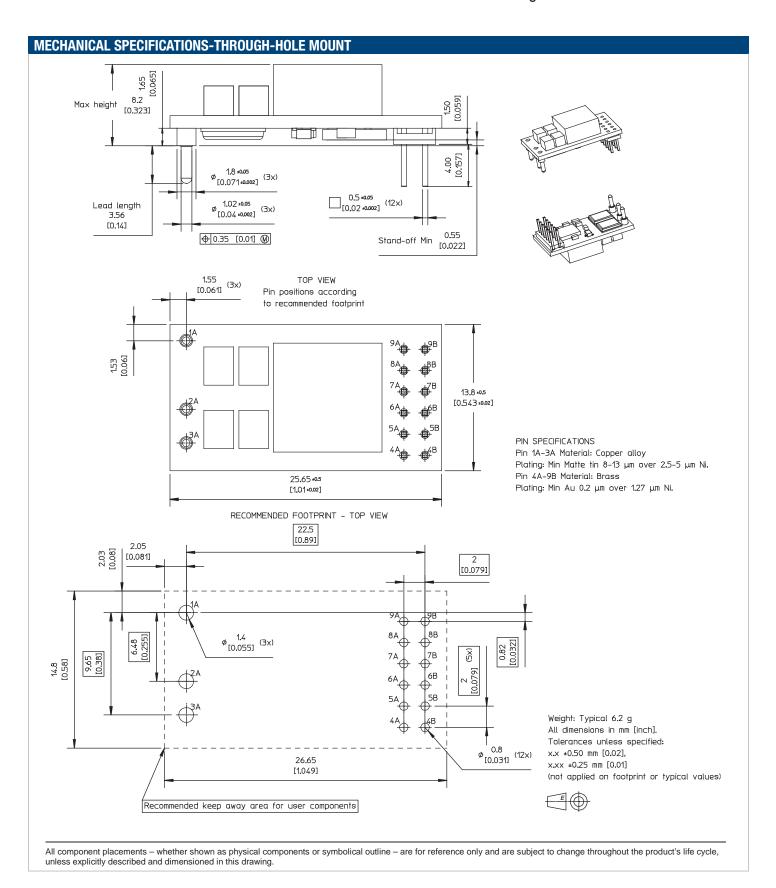

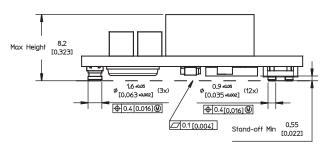

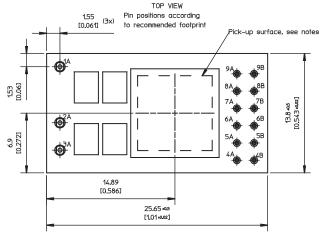

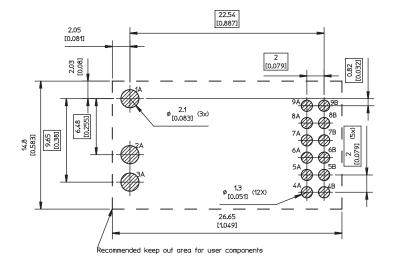

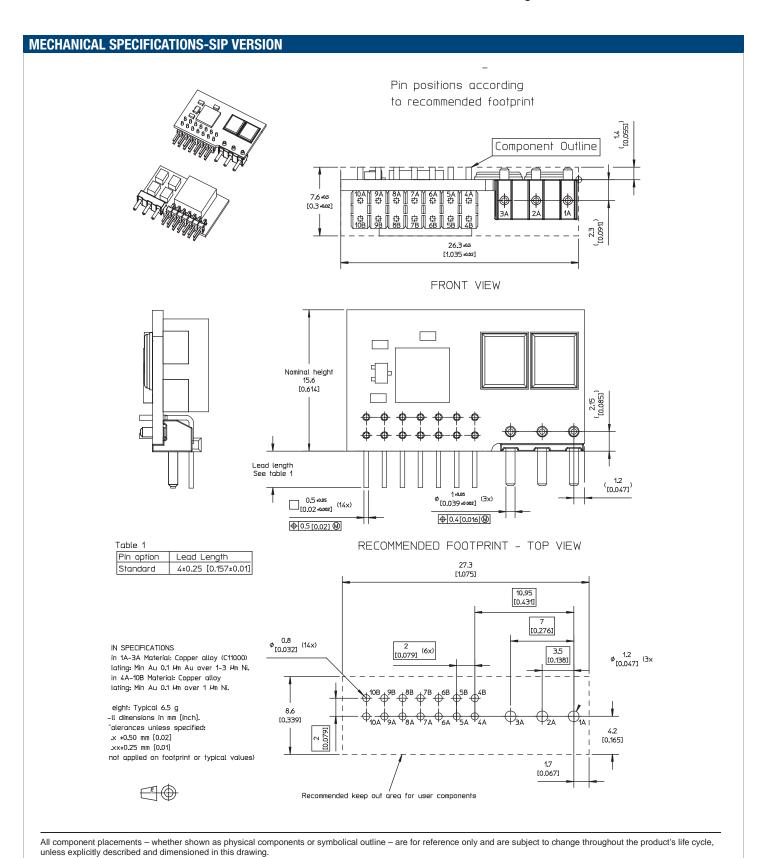

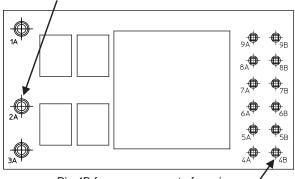

- Small package: 25.65 x 13.8 x 8.2 mm (1.01 x 0.543 x 0.323 in) SIP: 26.3 x 7.6 x 15.6 mm (1.035 x 0.30 x 0.614 in)

- 0.6 V 3.3 V output voltage range

- High efficiency, typ. 97.1% at 5Vin, 3.3Vout half load

- Configuration and Monitoring via PMBus™

- Adaptive compensation of PWM control loop & fast loop transient response

- Synchonization & phase spreading

- Current sharing, Voltage Tracking & Voltage margining

- MTBF 20.2 Mh

- Non-Linear Response for reduction of decoupling capacitor

- Remote control & power good

- Output short-circuit, output over voltage, & over temperature protection

- Certified to UL/IEC 60950-1

#### PRODUCT OVERVIEW

The OKDx-T/25-W12 series are high efficiency, digital point-of-Load (PoL) DC-DC power converters capable of delivering 25A/82.5W. Available in three different package formats, through-hole, single-inline, and surface mount, these converters have a typical efficiency of 97.1%. PMBus™ compatibility allows monitoring and configuration of critical system-level performance requirements. Apart from

standard PoL performance and safety features like OVP, OCP, OTP, and UVLO, these digital converters have advanced features: digital current sharing (full power, no derating), non-linear transient response, optimized dead time control, synchronization, and phase spreading. These converters are ideal for use in telecommunications, networking, and distributed power applications.

#### Power Management via PMBus™

- Configurable soft-start/stop

- Configurable output voltage (Vout) and voltage margins (Margin low and Margin high)

- Configurable protection limits for OVP, input over voltage, input under voltage, over current, on/off, and temperature

- Status monitor Vout, Iout, Vin, Temp, Power good, and On/Off

#### **Applications**

- Distributed power architectures

- Intermediate bus voltage applications

- Servers and storage applications

- Network equipment

| ORDERING GUIDE       |                          |

|----------------------|--------------------------|

| Model Number         | Output                   |

| OKDY-T/25-W12-001-C  |                          |

| OKDH-T/25-W12-001-C  | 0.6-3.3 V. 25 A/ 82.5 W  |

| OKDX-T/25-W12-001-C  | 0.0-3.3 V, 23 AV 02.3 VV |

| OKDX-T/25-W12E-001-C |                          |

#### **Absolute Maximum Ratings**

| Characte                                  | Characteristics                                                                          |               |      | Тур | Max | Unit |

|-------------------------------------------|------------------------------------------------------------------------------------------|---------------|------|-----|-----|------|

| T <sub>P1</sub> , T <sub>P2</sub>         | Operating temperature (see Thermal Consideration section)                                |               |      |     | 125 | °C   |

| Ts                                        | Ts Storage temperature                                                                   |               | -40  |     | 125 | °C   |

| Vı                                        | Input voltage (See Operating Information Section for input and output voltage relations) |               | -0.3 |     | 16  | V    |

| Logic I/O v                               | Logic I/O voltage CTRL, SAO, SA1, SALERT, SCL, SDA, VSET, SYNC, GCB, PG                  |               | -0.3 |     | 6.5 | V    |

| Ground voltage differential -S, PREF, GND |                                                                                          | -S, PREF, GND | -0.3 |     | 0.3 | V    |

| <u> </u>                                  |                                                                                          | VO, +S, VTRK  | -0.3 |     | 6.5 | V    |

| General and Safety | Conditions                         | Min | Тур  | Max | Unit |

|--------------------|------------------------------------|-----|------|-----|------|

| Safety             | Designed for UL/IEC/EN 60950 1     |     |      |     |      |

| Calculated MTBF    | Telcordia SR-332, Issue 2 Method 1 |     | 20.2 |     | Mhrs |

Stress in excess of Absolute Maximum Ratings may cause permanent damage. Absolute Maximum Ratings, sometimes referred to as no destruction limits, are normally tested with one parameter at a time exceeding the limits in the Electrical Specification. If exposed to stress above these limits, function and performance may degrade in an unspecified manner.

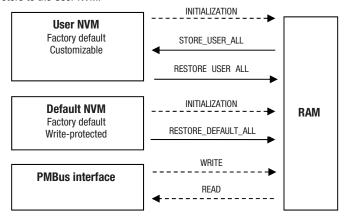

#### **Configuration File**

This product is designed with a digital control circuit. The control circuit uses a configuration file which determines the functionality and performance of the product. The Electrical Specification table shows parameter values of func-

tionality and performance with the default configuration file, unless otherwise specified. The default configuration file is designed to fit most application needs with focus on high efficiency. If different characteristics are required it is possible to change the configuration file to optimize certain performance characteristics. Note that current sharing operation requires changed configuration file.

In this Technical specification examples are included to show the possibilities with digital control. See Operating Information section for information about trade offs when optimizing certain key performance characteristics.

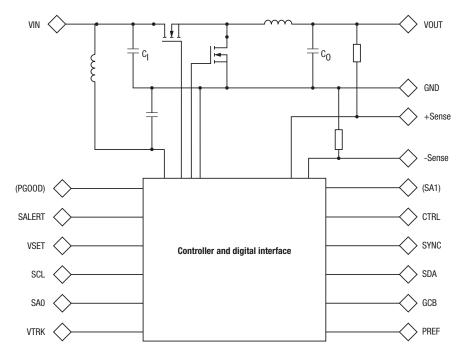

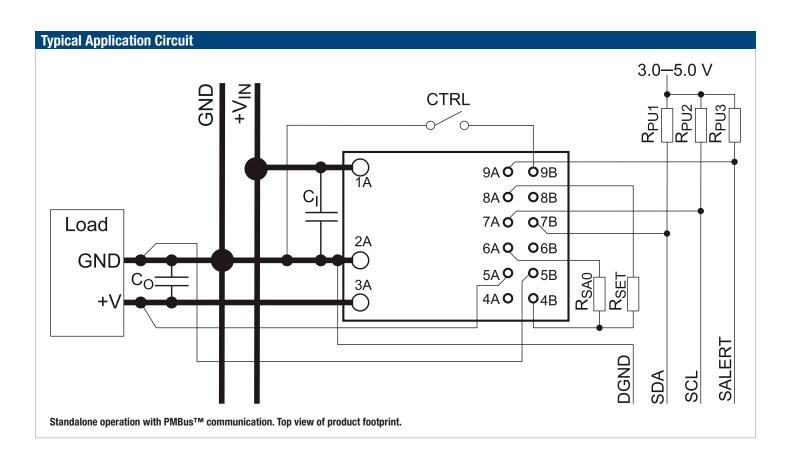

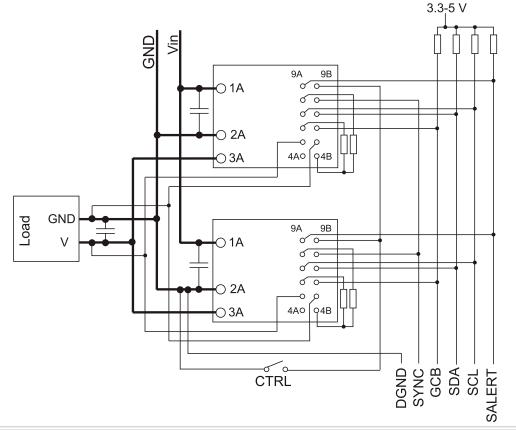

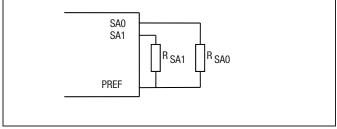

**Fundamental Circuit Diagram**

#### Electrical Specifications, OKDY-T/25-W12-xxx-C and OKDH-T/25-W12-xxx-C

$T_{P1} = -30 \text{ to } +95^{\circ}\text{C}, \text{ VIN} = 4.5 \text{ to } 14 \text{ V}, \text{ VIN} > \text{VOUT} + 1.0 \text{ V}$

Typical values given at: T<sub>P1</sub> = +25 °C, VIN = 12.0 V, max IOUT, unless otherwise specified under Conditions.

Default configuration file, 190 10-CDA 102 0206/001.

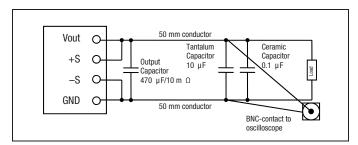

External CIN = 470  $\mu$ F/10 m $\Omega$ , COUT = 470  $\mu$ F/10 m $\Omega$ . See Operating Information section for selection of capacitor types.

Sense pins are connected to the output pins.

| Charac         | teristics                                  |                                    | Conditions                                     | Min   | Тур    | Max  | Unit     |  |

|----------------|--------------------------------------------|------------------------------------|------------------------------------------------|-------|--------|------|----------|--|

| V <sub>i</sub> | Input voltage rise time                    |                                    | monotonic                                      |       |        | 2.4  | V/ms     |  |

|                |                                            |                                    |                                                |       |        |      |          |  |

|                | Output voltage without                     | pin strap                          |                                                |       | 1.2    |      | V        |  |

|                | Output voltage adjustm                     |                                    |                                                | 0.60  | 1.2    | 3.3  | V        |  |

|                |                                            | ent including margining            | See Note 17                                    | 0.54  |        | 3.63 | V        |  |

|                | Output voltage set-poir                    |                                    | OCC NOTC 17                                    | 0.04  | ±0.025 | 3.00 | % Vo     |  |

|                | output voitage set-poil                    | it resolution                      | Including line, load, temp.                    |       | ±0.023 |      | /0 VO    |  |

|                |                                            |                                    |                                                | -1    |        | 1    | %        |  |

|                | Output voltage accurac                     | cy                                 | See Note 14                                    |       |        |      |          |  |

|                |                                            |                                    | Current sharing operation                      | -2    |        | 2    | %        |  |

|                |                                            | O L MOUT (OND                      | See Note 15                                    |       | 47     |      |          |  |

| )              | Internal resistance +S/                    | -S to VOUT/GND                     |                                                |       | 47     |      | Ω        |  |

|                |                                            |                                    | $V_0 = 0.6 \text{ V}$                          |       | 2      |      |          |  |

|                | Line regulation                            |                                    | $V_0 = 1.0 \text{ V}$                          |       | 2      |      | mV       |  |

|                | Line regulation                            |                                    | $V_0 = 1.8 \text{ V}$                          |       | 2      |      | 1114     |  |

|                |                                            |                                    | $V_0 = 3.3 \text{ V}$                          |       | 3      |      | <u> </u> |  |

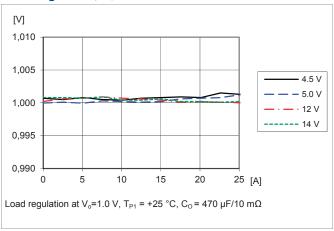

|                |                                            |                                    | $V_0 = 0.6 \text{ V}$                          |       | 2      |      |          |  |

|                | Lood von vlotion. L O                      | 1000/                              | $V_0 = 1.0 \text{ V}$                          |       | 2      |      | \/       |  |

|                | Load regulation; $I_0 = 0$                 | - 100%                             | $V_0 = 1.8 \text{ V}$                          |       | 2      |      | mV       |  |

|                |                                            |                                    | $V_0 = 1.8 \text{ V}$<br>$V_0 = 3.3 \text{ V}$ |       | 3      |      |          |  |

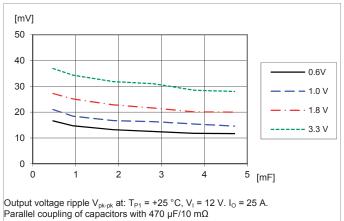

|                |                                            |                                    | $V_0 = 0.6 \text{ V}$                          |       | 20     |      |          |  |

|                | Output ripple & noise                      |                                    | $V_0 = 1.0 \text{ V}$                          |       | 30     |      |          |  |

| ac             |                                            | external capacitance). See Note 11 | $V_0 = 1.8 \text{ V}$                          |       | 40     |      | mVp-p    |  |

|                | 00 - 470 μι (ΠΙΙΠΙΠΙΙΙΙΙ                   | external capacitance). See Note 11 | $V_0 = 3.3 \text{ V}$                          |       | 60     |      |          |  |

|                |                                            |                                    | $ v_0  = 3.3 \text{ V}$                        |       | 00     |      |          |  |

|                | Ta                                         |                                    | T                                              |       | 1      |      |          |  |

|                | Output current                             |                                    | See Note 18                                    | 0.001 |        | 25   | A        |  |

|                |                                            |                                    | $V_0 = 0.6 \text{ V}$                          |       | 1.58   |      |          |  |

|                | Static input current at a                  | may I                              | $V_0 = 1.0 \text{ V}$                          |       | 2.43   |      | A        |  |

|                | Static input current at max I <sub>0</sub> |                                    | $V_0 = 1.8 \text{ V}$                          |       | 4.13   |      | Α        |  |

|                |                                            |                                    | $V_0 = 3.3 \text{ V}$                          |       | 7.32   |      |          |  |

| n              | Current limit threshold                    |                                    |                                                | 27    |        | 37.5 | Α        |  |

|                |                                            |                                    | $V_0 = 0.6 \text{ V}$                          |       | 8      |      |          |  |

|                |                                            |                                    | $V_0 = 1.0 \text{ V}$                          |       | 6      |      |          |  |

|                | Short circuit current                      | RMS, hiccup mode, See Note 3       | $V_0 = 1.8 \text{ V}$                          |       | 5      |      | Α        |  |

|                |                                            |                                    | $V_0 = 3.3 \text{ V}$                          |       | 4      |      |          |  |

|                |                                            |                                    | v <sub>0</sub> = 0.0 v                         |       | -      |      |          |  |

|                |                                            |                                    | W 0.0W                                         |       | 04.4   | 1    |          |  |

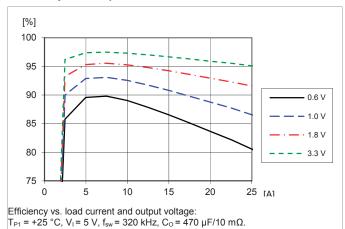

|                |                                            |                                    | $V_0 = 0.6 \text{ V}$                          |       | 84.4   |      |          |  |

|                |                                            | 50% of max I <sub>0</sub>          | $V_0 = 1.0 \text{ V}$                          |       | 89.4   |      | %        |  |

|                |                                            | oo /o or max io                    | $V_0 = 1.8 \text{ V}$                          |       | 93.1   |      | 70       |  |

|                | Efficiency                                 |                                    | $V_0 = 3.3 \text{ V}$                          |       | 95.2   |      |          |  |

|                | Lilloleticy                                |                                    | $V_0 = 0.6 \text{ V}$                          |       | 79.2   |      |          |  |

|                |                                            |                                    | $V_0 = 1.0 \text{ V}$                          |       | 85.7   |      | 0,4      |  |

|                |                                            | max I <sub>o</sub>                 | $V_0 = 1.8 \text{ V}$                          |       | 90.8   |      | %        |  |

|                |                                            |                                    | $V_0 = 3.3 \text{ V}$                          |       | 93.9   |      |          |  |

|                |                                            |                                    | $V_0 = 0.6 \text{ V}$                          |       | 3.93   |      |          |  |

|                |                                            |                                    | $V_0 = 0.0 \text{ V}$<br>$V_0 = 1.0 \text{ V}$ |       | 4.17   |      |          |  |

|                | Power dissipation at m                     | ax I <sub>0</sub>                  | V <sub>0</sub> = 1.0 V                         |       |        |      | W        |  |

|                |                                            |                                    | $V_0 = 1.8 \text{ V}$                          |       | 4.55   |      |          |  |

|                |                                            |                                    | $V_0 = 3.3 \text{ V}$                          |       | 5.34   |      |          |  |

|                |                                            |                                    | $V_0 = 0.6 \text{ V}$                          |       | 0.56   |      |          |  |

|                | Input idling power                         | Default configuration: Continues   | $V_0 = 1.0 \text{ V}$                          |       | 0.57   |      | W        |  |

|                | (no load)                                  | Conduction Mode, CCM               | $V_0 = 1.8 \text{ V}$                          |       | 0.67   |      | VV       |  |

|                |                                            |                                    | $V_0 = 3.3 \text{ V}$                          |       | 0.92   |      |          |  |

|                |                                            |                                    |                                                |       |        |      |          |  |

|                |                                            | Turned off with                    | Default configuration:                         |       |        |      | mW       |  |

| CTRL           | Input standby power                        | CTRL-pin                           | Monitoring enabled,                            |       | 170    |      | IIIVV    |  |

|                |                                            | OTTIL-PIII                         | Precise timing enabled                         |       |        |      |          |  |

|                |                                            |                                    | i recise timing chabica                        |       |        |      |          |  |

| i              | Internal input capacitar                   |                                    | Trooled arring origination                     |       | 70     |      | μF       |  |

| Charac           | teristics                                      |                                           | Conditions            | Min  | Тур                  | Max    | Unit             |

|------------------|------------------------------------------------|-------------------------------------------|-----------------------|------|----------------------|--------|------------------|

| $C_{\circ}$      | Internal output capacita                       | nce                                       |                       |      | 200                  |        | μF               |

|                  | Total external output ca                       | pacitance                                 | See Note 9            | 300  |                      | 15 000 | μF               |

| $C_{\text{out}}$ | ESR range of capacitors (per single capacitor) | 3                                         | See Note 9            | 5    |                      | 30     | $m\Omega$        |

|                  | (por emigro expanier)                          |                                           |                       | l    |                      |        |                  |

|                  | Load transient peak                            | Default configuration di/dt = 2 A/µs      | $V_0 = 0.6 \text{ V}$ |      | 95                   |        |                  |

| .,               | voltage deviation                              |                                           | $V_0 = 1.0 \text{ V}$ |      | 105                  |        | .,               |

| $V_{tr1}$        | (H to L)<br>Load step 25-75-25%                | $C_0 = 470  \mu F$ (minimum external      | $V_0 = 1.8 \text{ V}$ |      | 115                  |        | mV               |

|                  | of max I <sub>0</sub>                          | capacitance) see Note 12                  | $V_0 = 3.3 \text{ V}$ |      | 168                  |        |                  |

|                  | Load transient recovery                        | Default configuration                     | $V_0 = 0.6 \text{ V}$ |      | 74                   |        |                  |

|                  | time, Note 5                                   |                                           | $V_0 = 1.0 \text{ V}$ |      | 85                   |        |                  |

| t <sub>tr1</sub> | (H to L)<br>Load step 25-75-25%                | $C_0 = 470 \mu\text{F}$ (minimum external | $V_0 = 1.8 \text{ V}$ |      | 122                  |        | μs               |

|                  | of max I <sub>0</sub>                          | capacitance) see Note 12                  | $V_0 = 3.3 \text{ V}$ |      | 140                  |        |                  |

|                  |                                                |                                           | 10 0.01               |      |                      |        |                  |

|                  | Switching frequency                            |                                           |                       |      | 320                  |        | kHz              |

| f <sub>s</sub>   | Switching frequency rar                        | nge                                       | PMBus configurable    |      | 200-640              |        | kHz              |

|                  | Switching frequency set                        |                                           |                       | -5   |                      | 5      | %                |

|                  | Control Circuit PWM Du                         |                                           |                       | 5    |                      | 95     | %                |

|                  | Minimum Sync Pulse W                           |                                           |                       | 150  |                      |        | ns               |

|                  | Input Clock Frequency [                        | Orift Tolerance                           | External clock source | -13  |                      | 13     | %                |

|                  |                                                | UVLO threshold                            |                       |      | 3.85                 |        | V                |

|                  |                                                | UVLO threshold range                      | PMBus configurable    |      | 3.85-14              |        | V                |

|                  |                                                | Set point accuracy                        |                       | -150 |                      | 150    | mV               |

|                  | nder Voltage Lockout,                          | UVLO hysteresis                           |                       |      | 0.35                 |        | V                |

| UVLO             |                                                | UVLO hysteresis range                     | PMBus configurable    |      | 0-10.15              |        | V                |

|                  |                                                | Delay                                     |                       |      | 2.5                  |        | μS               |

|                  |                                                | Fault response                            | See Note 3            | A    | utomatic restart, 70 | ms     | -                |

|                  |                                                | IOVP threshold                            |                       |      | 16                   |        | V                |

|                  |                                                | IOVP threshold range                      | PMBus configurable    |      | 4.2-16               |        | V                |

| Innut Ou         | or Valtage Protection                          | Set point accuracy                        |                       | -150 |                      | 150    | mV               |

|                  | ver Voltage Protection,                        | IOVP hysteresis                           |                       |      | 1                    |        | V                |

| IOVP             |                                                | IOVP hysteresis range                     | PMBus configurable    |      | 0-11.8               |        | V                |

|                  |                                                | Delay                                     |                       |      | 2.5                  |        | μS               |

|                  |                                                | Fault response                            | See Note 3            | A    | utomatic restart, 70 | ms     |                  |

|                  |                                                | PG threshold                              |                       |      | 90                   |        | $% V_0$          |

| Power G          | Good, PG,                                      | PG hysteresis                             |                       |      | 5                    |        | % V <sub>0</sub> |

| See Note         | e 2                                            | PG delay                                  | See Note 19           |      | Direct after DLC     |        |                  |

|                  |                                                | PG delay range                            | PMBus configurable    |      | 0-500                |        | S                |

|                  |                                                | UVP threshold                             |                       |      | 85                   |        | % V <sub>0</sub> |

|                  |                                                | UVP threshold range                       | PMBus configurable    |      | 0-100                |        | % V <sub>0</sub> |

|                  |                                                | UVP hysteresis                            | j                     |      | 5                    |        | % V <sub>0</sub> |

| Output v         | voltage                                        | OVP threshold                             |                       |      | 115                  |        | % V <sub>0</sub> |

|                  | der Voltage Protection,                        | OVP threshold range                       | PMBus configurable    |      | 100-115              |        | % V <sub>0</sub> |

| OVP/UVF          |                                                | UVP/OVP response time                     | <u> </u>              |      | 25                   |        | μS               |

|                  |                                                | UVP/OVP                                   | PMRue configurable    |      | 5-60                 |        |                  |

|                  |                                                | response time range                       | PMBus configurable    |      |                      |        | μS               |

|                  |                                                | Fault response                            | See Note 3            | A    | utomatic restart, 70 | ms     |                  |

|                  |                                                | OCP threshold                             |                       |      | 32                   |        | Α                |

| Over C.          | rrant Drataation                               | OCP threshold range                       | PMBus configurable    |      | 0-32                 |        | Α                |

|                  | rrent Protection,                              | Protection delay,                         | See Note 4            |      | 32                   |        | $T_{sw}$         |

| OCP              |                                                | Protection delay range                    | PMBus configurable    |      | 1-32                 |        | T <sub>sw</sub>  |

|                  |                                                |                                           |                       |      |                      |        |                  |

# Pokami OKDx-T/25-W12-xxx-C

### 25A Digital PoL DC-DC Converter Series

|                                       | ristics                             |                                             | Conditions                                | Min        | Тур                  | Max             | Unit |

|---------------------------------------|-------------------------------------|---------------------------------------------|-------------------------------------------|------------|----------------------|-----------------|------|

|                                       |                                     | OTP threshold                               |                                           |            | 120                  |                 | °C   |

| Over Tempe                            | erature Protection,                 | OTP threshold range                         | PMBus configurable                        |            | -40+125              |                 | °C   |

| OTP at P2                             | ,                                   | OTP hysteresis                              | - J                                       |            | 25                   |                 | °C   |

| See Note 8                            | 3                                   | OTP hysteresis range                        | PMBus configurable                        |            | 0-165                |                 | °C   |

|                                       |                                     | Fault response                              | See Note 3                                | Au         | tomatic restart, 240 | ms              |      |

|                                       |                                     |                                             |                                           |            | ,                    | -               |      |

| <b>/</b> ,,                           | Logic input low three               | eshold                                      | SYNC, SAO, SA1, SCL, SDA, GCB, CTRL,      |            |                      | 0.8             | V    |

| <u>и.</u><br>И <sub>Н</sub>           | Logic input high thr                |                                             | VSET                                      | 2          |                      | 0.0             | V    |

| 'IH                                   | Logic input low sink                |                                             | CTRL                                      |            |                      | 0.6             | mA   |

| <u></u>                               | Logic output low sig                |                                             | OTTLE                                     |            |                      | 0.4             | V    |

| OL<br>OH                              | Logic output low sign               |                                             | _                                         | 2.25       |                      | 0.7             | V    |

|                                       | Logic output low sir                |                                             | SYNC, SCL, SDA, SALERT, GCB, PG           | 2.25       |                      | 4               | mA   |

| OL                                    | Logic output low si                 |                                             | _                                         |            |                      | 2               | mA   |

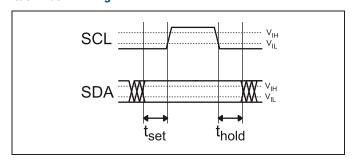

| OH                                    | Setup time, SMBus                   |                                             | See Note 1                                | 300        |                      |                 | ns   |

| set                                   | Hold time, SMBus                    |                                             | See Note 1                                | 250        |                      |                 | ns   |

| nold                                  | Bus free time, SMB                  | II.e                                        | See Note 1                                | 230        |                      |                 | ms   |

| free                                  | Internal capacitance                |                                             | OGG NOTE 1                                | ۷          | 10                   |                 | pF   |

| C <sub>p</sub>                        | internal capacitano                 | c on logic pins                             |                                           |            | IU                   |                 | μг   |

| *** ***                               |                                     |                                             | 0 11 10                                   |            | 10                   |                 |      |

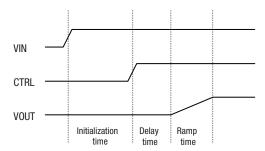

| nitializatior                         | on time                             | 15                                          | See Note 10                               |            | 40                   |                 | ms   |

|                                       |                                     | Delay duration                              | See Note 16                               |            | 10                   |                 | ms   |

| Output Volta                          | tage                                | Delay duration range                        | PMBus configurable                        |            | 5-500000             |                 |      |

| Delay Time                            |                                     | Delay accuracy                              |                                           |            | -0.25/+4             |                 | ms   |

| See Note 6                            |                                     | turn-on                                     |                                           |            | 0.207                |                 |      |

|                                       | Delay accuracy                      |                                             |                                           |            | -0.25/+4             |                 | ms   |

|                                       |                                     | turn-off                                    |                                           |            |                      |                 | 1110 |

| Output Volta                          | tane                                | Ramp duration                               |                                           |            | 10                   |                 | ms   |

| Ramp Time                             |                                     | Ramp duration range                         | PMBus configurable                        |            | 0-200                |                 | 1110 |

| See Note 1                            |                                     | Ramp time accuracy                          |                                           |            | 100                  |                 | μs   |

| JCC NOIC 1                            |                                     | Tramp time accuracy                         | Current sharing operation                 |            | 20                   |                 | %    |

|                                       |                                     |                                             |                                           |            |                      |                 |      |

| /TRK Input                            | t Bias Current                      |                                             | $V_{VTRK} = 5.5 \text{ V}$                |            | 110                  | 200             | μА   |

|                                       |                                     |                                             | 100% tracking, see Note 7                 | -100       |                      | 100             | m۷   |

| /TDI/ Track                           | vina Damp Assurace: A               | /                                           | Current sharing operation                 |            |                      |                 |      |

| vinn Itack                            | king Ramp Accuracy (\               | 70 - V <sub>VTRK</sub> )                    | 2 phases, 100% tracking                   |            | ±100                 |                 | mV   |

|                                       |                                     |                                             | $V_0 = 1.0 \text{ V}, 10 \text{ ms ramp}$ |            |                      |                 |      |

|                                       |                                     |                                             | 100% Tracking                             | -1         |                      | 1               | %    |

| VTRK Regulation Accuracy (Vo - VVTRK) |                                     | (VTRK)                                      | Current sharing operation                 |            |                      |                 |      |

| vikk kedu                             | VITAL TIOGRAM TO CATACOT (VO VITAK) |                                             | 100% Tracking                             | -2         |                      | 2               | %    |

| TRK Regu                              |                                     |                                             |                                           |            |                      |                 |      |

| /TKK Kegu                             |                                     |                                             |                                           |            |                      |                 |      |

|                                       |                                     |                                             | Steady state operation                    | May 2 y Di | EAD IOUT monitorin   | u accuracy      |      |

|                                       | ference between prod                | ucts in a current sharing group             | Steady state operation                    | Max 2 x R  | EAD_IOUT monitorin   | g accuracy      | Λ    |

| Current diff                          | <u> </u>                            |                                             | Steady state operation<br>Ramp-up         | Max 2 x R  | EAD_IOUT monitorin   |                 | А    |

| Current diff                          | ference between prod                |                                             | -                                         | Max 2 x R  |                      | g accuracy<br>7 | A    |

| Current diff                          | <u> </u>                            | sharing group                               | -                                         | Max 2 x R  | 2                    |                 |      |

| Current diff                          | <u> </u>                            | sharing group    READ_VIN vs V <sub>1</sub> | -                                         | Max 2 x R  | 3                    |                 | %    |

| Current diff                          | <u> </u>                            | sharing group                               | Ramp-up                                   | Max 2 x RI | 2                    |                 |      |

| Current diff                          | products in a current               | sharing group    READ_VIN vs V <sub>1</sub> | -                                         | Max 2 x Ri | 3                    |                 | %    |

Note 1: See section I2C/SMBus Setup and Hold Times - Definitions.

Note 2: Monitorable over PMBus Interface.

Note 3: Automatic restart ~70 or 240 ms after fault if the fault is no longer present. Continuous restart attempts if the fault reappear after restart. See Operating Information and AN302 for other fault response options.

Note 4: Tsw is the switching period.

Note 5: Within +/-3% of VO

Note 6: See section Soft-start Power Up.

Note 7: Tracking functionality is designed to follow a VTRK signal with slew rate < 2.4 V/ms. For faster VTRK signals accuracy will depend on the regulator bandwidth.

Note 8: See section Over Temperature Protection (OTP).

Note 9: See section External Capacitors.

Note 10: See section Initialization Procedure.

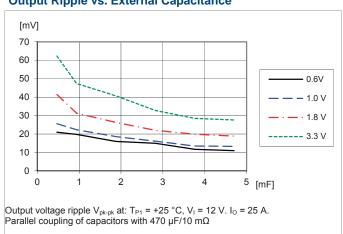

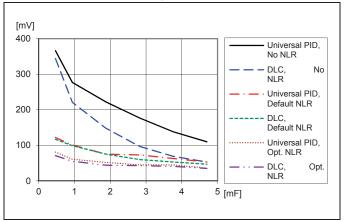

Note 11: See graph Output Ripple vs External Capacitance and Operating information section Output Ripple and Noise.

Note 12: See graph Load Transient vs. External Capacitance and Operating information section External Capacitors.

Note 13: Time for reaching 100% of nominal Vout.

Note 14: For Vout < 1.0 V accuracy is +/-10 mV. For further deviations see section Output Voltage Adjust using PMBus<sup>TM</sup>. Note 15: Accuracy here means deviation from ideal output voltage level given by configured droop and actual load.

Includes line, load and temperature variations. Note 16: For current sharing the Output Voltage Delay Time must be reconfigured to minimum 15 ms.

Note 17: For steady state operation above 1.05 x 3.3 V, please contact your local Murata sales representative.

Note 18: A minimum load current is not required if Low Power mode is used (monitoring disabled).

Note 19: See sections Dynamic Loop Compensation and Power Good.

## Typical Characteristics Efficiency and Power Dissipation

#### Efficiency vs. Output Current, $V_1 = 5 \text{ V}$

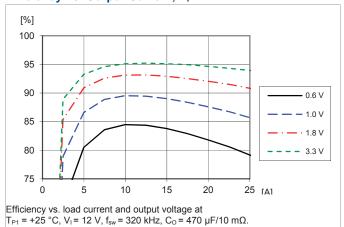

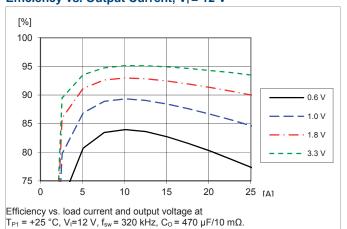

#### Efficiency vs. Output Current, V<sub>I</sub> = 12 V

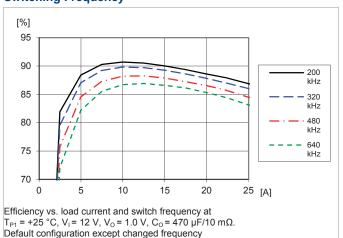

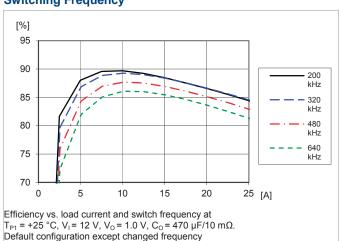

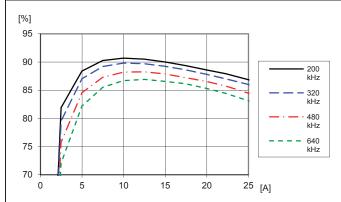

#### Efficiency vs. Output Current and Switching Frequency

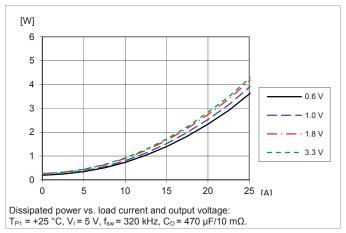

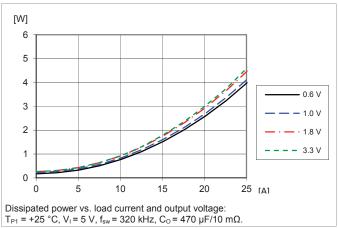

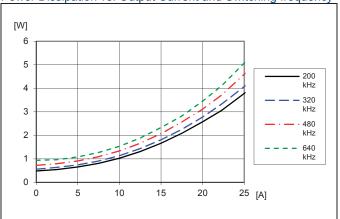

#### Power Dissipation vs. Output Current, $V_1 = 5 \text{ V}$

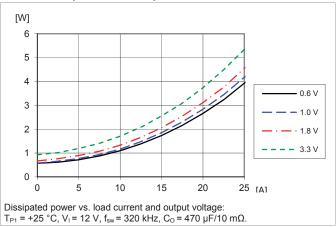

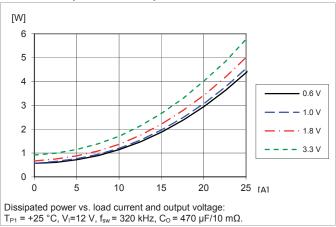

#### Power Dissipation vs. Output Current, $V_1 = 12 \text{ V}$

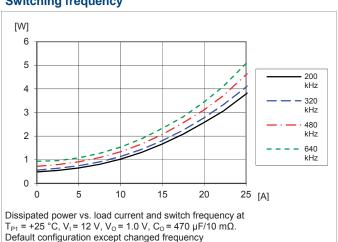

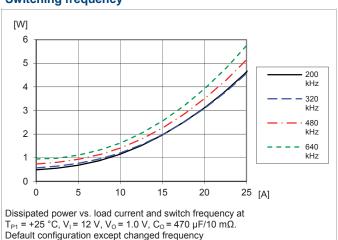

### Power Dissipation vs. Output Current and Switching frequency

#### **Typical Characteristics Load Transient**

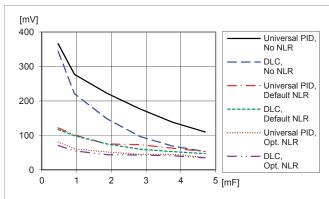

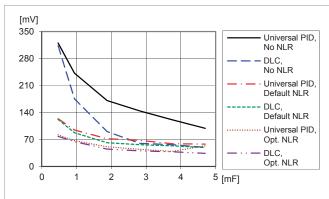

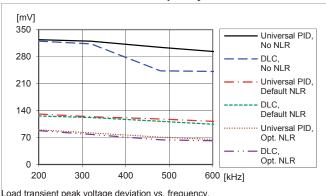

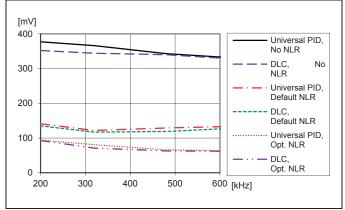

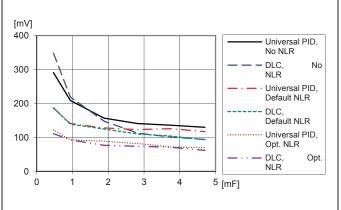

#### Load Transient vs. External Capacitance, Vo = 1.0 V

Load transient peak voltage deviation vs. external capacitance. Step (6.25-18.75-6.25 A). Parallel coupling of capacitors with 470  $\mu F/10$  m $\Omega$ ,  $T_{P1}$  = +25 °C,  $V_{I}$  = 12 V,  $V_{O}$  = 1.0 V,  $f_{sw}$  = 320 kHz, di/dt = 2 A/ $\mu$ s

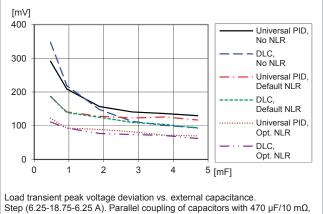

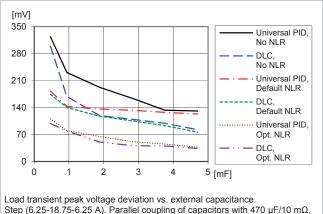

#### Load Transient vs. External Capacitance, Vo = 3.3 V

$T_{P1}$  = +25 °C,  $V_{I}$  = 12 V,  $V_{O}$  = 3.3 V,  $f_{sw}$  = 320 kHz, di/dt = 2 A/ $\mu$ s

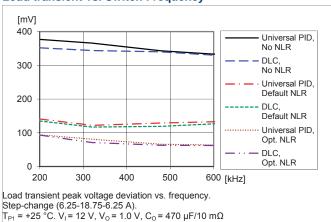

#### Load transient vs. Switch Frequency

Note: For Universal PID, see section Dynamic Loop Compensation (DLC).

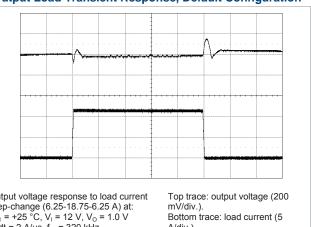

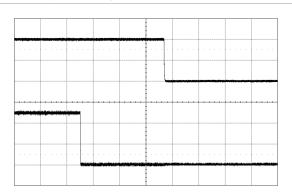

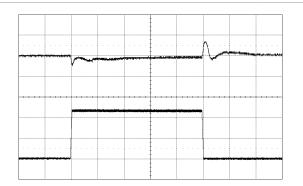

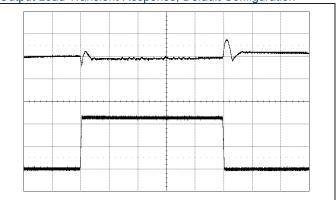

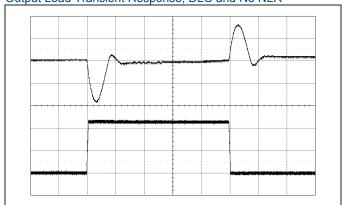

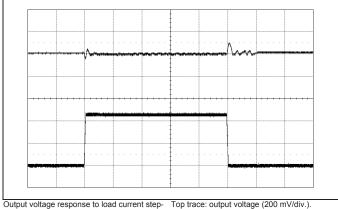

#### Output Load Transient Response, Default Configuration

Output voltage response to load current Step-change (6.25-18.75-6.25 A) at:  $T_{P1} = +25 \,^{\circ}\text{C}$ ,  $V_{I} = 12 \,\text{V}$ ,  $V_{O} = 1.0 \,\text{V}$  diddt = 2 Mµs,  $f_{sw} = 320 \,\text{kHz}$  $C_0 = 470 \ \mu F / 10 \ m\Omega$

A/div.). Time scale: (0.1 ms/div.).

#### **Typical Characteristics Output Current Characteristic**

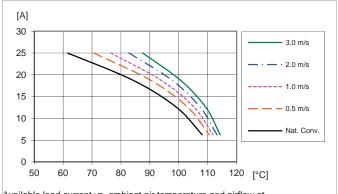

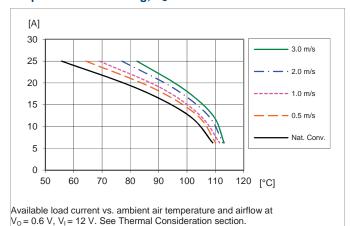

#### Output Current Derating, Vo = 0.6 V

Available load current vs. ambient air temperature and airflow at  $V_O = 0.6 \text{ V}$ ,  $V_I = 12 \text{ V}$ . See Thermal Consideration section.

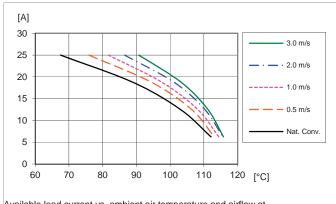

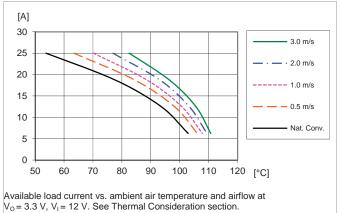

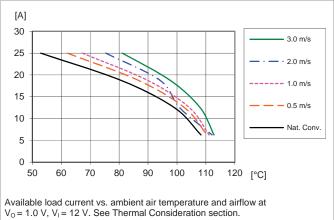

#### Output Current Derating, Vo = 1.0 V

$V_0 = 1.0 \text{ V}$ ,  $V_1 = 12 \text{ V}$ . See Thermal Consideration section.

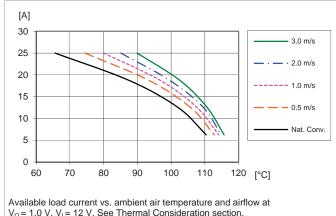

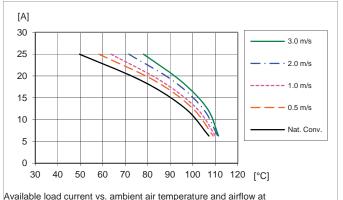

#### Output Current Derating, Vo = 1.8 V

Available load current vs. ambient air temperature and airflow at V<sub>O</sub> = 1.8 V, V<sub>I</sub> = 12 V. See Thermal Consideration section.

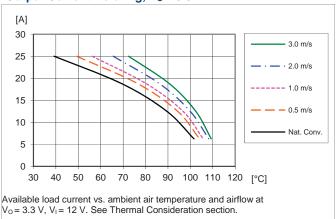

#### Output Current Derating, Vo = 3.3 V

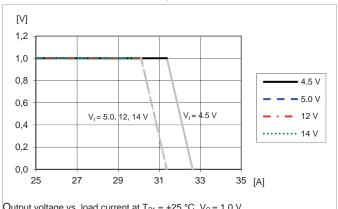

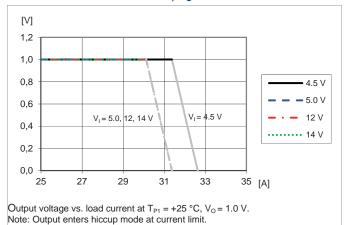

#### Current Limit Characteristics, Vo = 1.0 V

Output voltage vs. load current at  $T_{P1} = +25 \,^{\circ}\text{C}$ ,  $V_{O} = 1.0 \,^{\circ}\text{V}$ . Note: Output enters hiccup mode at current limit.

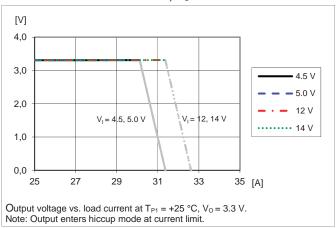

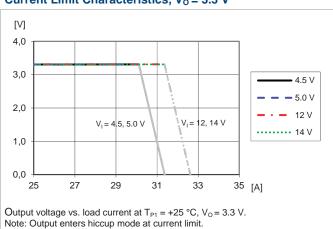

#### Current Limit Characteristics, Vo = 3.3 V

#### Typical Characteristics Output Voltage

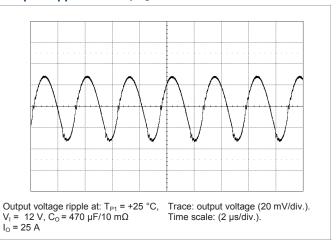

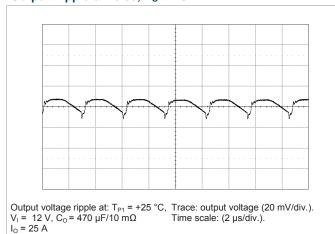

#### Output Ripple & Noise, Vo = 1.0 V

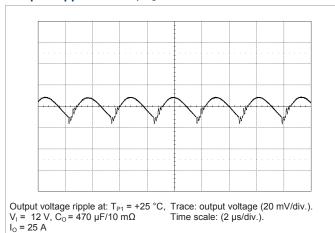

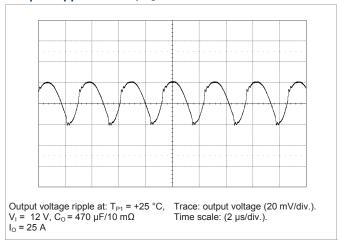

#### Output Ripple & Noise, Vo = 3.3 V

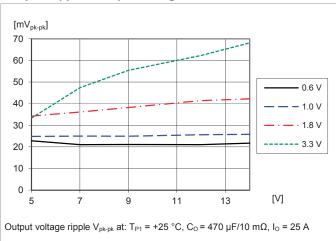

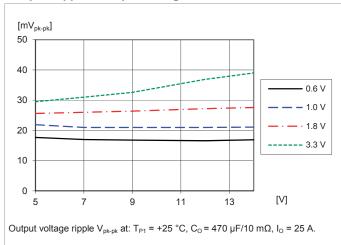

#### **Output Ripple vs. Input Voltage**

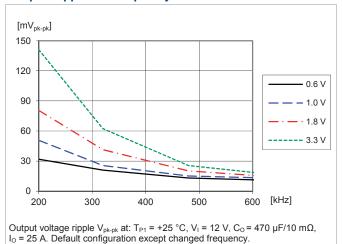

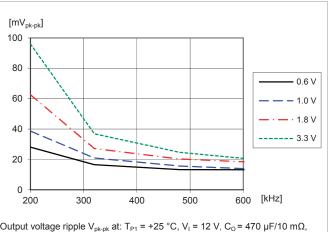

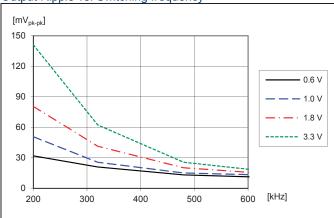

#### **Output Ripple vs. Frequency**

#### **Output Ripple vs. External Capacitance**

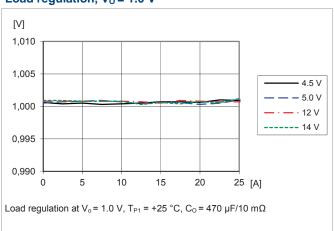

#### Load regulation, $V_0 = 1.0 \text{ V}$

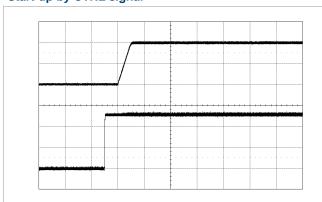

# Typical Characteristics Start-up and shut-down

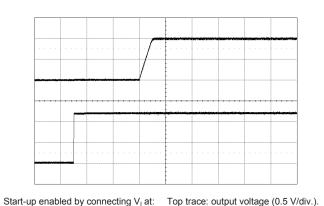

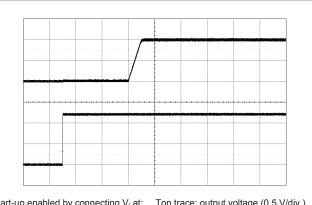

#### Start-up by input source

Start-up enabled by connecting  $V_1$  at:  $T_{P1} = +25 \,^{\circ}\text{C}$ ,  $V_1 = 12 \,\text{V}$ ,  $V_0 = 1.0 \,\text{V}$  $C_0 = 470 \,\mu\text{F}/10 \,\text{m}\Omega$ ,  $I_0 = 25 \,\text{A}$  Top trace: output voltage (0.5 V/div.). Bottom trace: input voltage (5 V/div.). Time scale: (20 ms/div.).

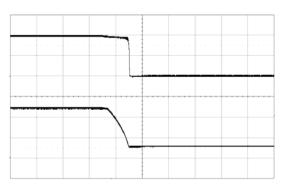

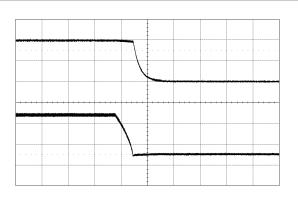

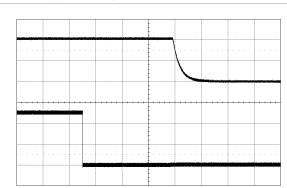

#### Shut-down by input source

Shut-down enabled by disconnecting  $V_{\scriptscriptstyle \parallel}$  at:

$T_{P1}$  = +25 °C,  $V_{I}$  = 12 V,  $V_{O}$  = 1.0 V  $C_{O}$  = 470  $\mu$ F/10 m $\Omega$ ,  $I_{O}$  = 25 A

Top trace: output voltage (0.5 V/div.). Bottom trace: input voltage (5 V/div.). Time scale: (2 ms/div.).

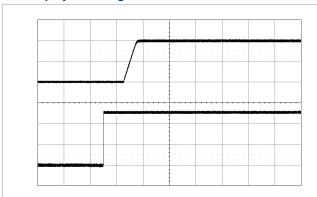

#### Start-up by CTRL signal

Start-up by enabling CTRL signal at:  $T_{P1}$  = +25 °C,  $V_{I}$  = 12 V,  $V_{O}$  = 1.0 V  $C_{O}$  = 470  $\mu F/10$  mΩ,  $I_{O}$  = 25 A

Top trace: output voltage (0.5 V/div.). Bottom trace: CTRL signal (2 V/div.). Time scale: (20 ms/div.).

#### Shut-down by CTRL signal

Shut-down enabled by disconnecting V<sub>I</sub> at:

$V_1$  at:  $T_{P1}$  = +25 °C,  $V_1$  = 12 V,  $V_0$  = 1.0 V  $C_0$  = 470  $\mu$ F/10 m $\Omega$ ,  $I_0$  = 25 A Top trace: output voltage (0.5 V/div). Bottom trace: CTRL signal (2 V/div.). Time scale: (2 ms/div.).

#### **Electrical Specifications, OKDX-T/25-W12-xxx-C**

$T_{P1} = -30 \text{ to } +95 \,^{\circ}\text{C}, V_{I} = 4.5 \text{ to } 14 \, \text{V}, V_{I} \! > \! V_{0} + 1.0 \, \text{V}$

Typical values given at:  $T_{P1} = +25$  °C,  $V_1 = 12.0$  V, max  $I_0$ , unless otherwise specified under Conditions.

Default configuration file, 190 10-CDA 102 0259/001.

External  $C_{\text{IN}} = 470~\mu\text{F}/10~\text{m}\Omega$ ,  $C_{\text{OUT}} = 470~\mu\text{F}/10~\text{m}\Omega$ . See Operating Information section for selection of capacitor types.

Sense pins are connected to the output pins.

| Characte   | eristics                                |                                            | Conditions                                     | Min   | Тур    | Max  | Unit   |  |

|------------|-----------------------------------------|--------------------------------------------|------------------------------------------------|-------|--------|------|--------|--|

| <b>/</b> , | Input voltage rise time                 |                                            | monotonic                                      |       |        | 2.4  | V/ms   |  |

|            |                                         |                                            |                                                |       |        |      |        |  |

|            | Output voltage without                  | pin strap                                  |                                                |       | 1.2    |      | V      |  |

|            | Output voltage adjustm                  |                                            |                                                | 0.60  |        | 3.3  | V      |  |

|            |                                         | ent including margining                    | See Note 17                                    | 0.54  |        | 3.63 | V      |  |

|            | Output voltage set-poir                 |                                            |                                                |       | ±0.025 |      | % Vo   |  |

|            | Jan |                                            | Including line, load, temp.                    | -     |        | 4    | %      |  |

|            | Output voltage coourse                  |                                            | See Note 14                                    | -1    |        | 1    | %      |  |

|            | Output voltage accurac                  | У                                          | Current sharing operation                      | 0     |        | 0    | 0/     |  |

|            |                                         |                                            | See Note 15                                    | -2    |        | 2    | %      |  |

| )          | Internal resistance +S/                 | -S to VOUT/GND                             |                                                |       | 47     |      | Ω      |  |

|            |                                         |                                            | $V_0 = 0.6 \text{ V}$                          |       | 2      |      |        |  |

|            | $V_0 = 1.0 \text{ V}$                   | 2                                          |                                                | m\/   |        |      |        |  |

|            | Line regulation                         |                                            | $V_0 = 1.8 \text{ V}$                          |       | 2      |      | mV     |  |

|            |                                         |                                            | $V_0 = 3.3 \text{ V}$                          |       | 3      |      |        |  |

|            |                                         |                                            | $V_0 = 0.6 \text{ V}$                          |       | 2      |      |        |  |

|            | Lood regulation I 0                     | 1000/                                      | $V_0 = 1.0 \text{ V}$                          |       | 2      |      |        |  |

|            | Load regulation; $I_0 = 0$              | - 10070                                    | $V_0 = 1.8 \text{ V}$                          |       | 2      |      | mV     |  |

|            |                                         |                                            | $V_0 = 3.3 \text{ V}$                          |       | 3      |      |        |  |

|            |                                         |                                            | $V_0 = 0.6 \text{ V}$                          |       | 20     |      |        |  |

|            | Output ripple & noise                   |                                            | $V_0 = 1.0 \text{ V}$                          |       | 30     |      | ml/n = |  |

| )ac        | $C_0 = 470 \mu F$ (minimum              | external capacitance). See Note 11         | $V_0 = 1.8 \text{ V}$                          |       | 40     |      | mVp-p  |  |

|            |                                         |                                            | $V_0 = 3.3 \text{ V}$                          |       | 60     |      |        |  |

|            |                                         |                                            |                                                |       |        |      |        |  |

|            | Output current                          |                                            | See Note 18                                    | 0.001 |        | 25   | А      |  |

|            |                                         |                                            | $V_0 = 0.6 \text{ V}$                          |       | 1.61   | -    |        |  |

|            |                                         |                                            | $V_0 = 1.0 \text{ V}$                          |       | 2.46   |      | _      |  |

|            | Static input current at r               | Furrent at max $I_0$ $V_0 = 1.8 \text{ V}$ | $V_0 = 1.8 \text{ V}$                          |       | 4.17   |      | Α      |  |

|            |                                         |                                            | $V_0 = 3.3 \text{ V}$                          |       | 7.35   |      |        |  |

| 1          | Current limit threshold                 |                                            |                                                | 27    |        | 37.5 | А      |  |

|            |                                         |                                            | $V_0 = 0.6 \text{ V}$                          |       | 8      |      |        |  |

|            |                                         | ent RMS, hiccup mode, See Note 3           | $V_0 = 1.0 \text{ V}$                          |       | 6      |      |        |  |

|            | Short circuit current                   |                                            | $V_0 = 1.8 \text{ V}$                          |       | 5      |      | Α      |  |

|            |                                         |                                            | $V_0 = 3.3 \text{ V}$                          |       | 4      |      |        |  |

|            | 1                                       |                                            | 1 0                                            | '     |        |      |        |  |

|            |                                         |                                            | $V_0 = 0.6 \text{ V}$                          |       | 83.6   |      |        |  |

|            |                                         |                                            | $V_0 = 1.0 \text{ V}$                          |       | 89.0   |      |        |  |

|            |                                         | 50% of max I <sub>0</sub>                  | $V_0 = 1.8 \text{ V}$                          |       | 92.8   |      | %      |  |

|            |                                         |                                            | $V_0 = 3.3 \text{ V}$                          |       | 95.1   |      |        |  |

|            | Efficiency                              |                                            | $V_0 = 0.6 \text{ V}$                          |       | 77.4   |      |        |  |

|            |                                         |                                            | $V_0 = 0.0 \text{ V}$                          |       | 84.6   |      |        |  |

|            |                                         | max I <sub>0</sub>                         | $V_0 = 1.8 \text{ V}$                          |       | 90.0   |      | %      |  |

|            |                                         |                                            | $V_0 = 3.3 \text{ V}$                          |       | 93.5   |      |        |  |

|            |                                         |                                            | $V_0 = 0.6 \text{ V}$                          |       | 4.37   |      |        |  |

|            |                                         |                                            | $V_0 = 0.0 \text{ V}$<br>$V_0 = 1.0 \text{ V}$ |       | 4.54   |      |        |  |

|            | Power dissipation at m                  | ax I <sub>o</sub>                          | $V_0 = 1.8 \text{ V}$                          |       | 5.01   |      | W      |  |

|            |                                         |                                            | $V_0 = 3.3 \text{ V}$                          |       | 5.77   |      |        |  |

|            | +                                       |                                            | $V_0 = 0.6 \text{ V}$                          |       | 0.56   |      |        |  |

|            | Input idling power                      | Default configuration: Continues           | $V_0 = 0.0 \text{ V}$<br>$V_0 = 1.0 \text{ V}$ |       | 0.57   |      | -      |  |

|            | (no load)                               | Conduction Mode, CCM                       | $V_0 = 1.0 \text{ V}$<br>$V_0 = 1.8 \text{ V}$ |       | 0.67   |      | W      |  |

|            | (IIU IUdu)                              | Conduction wode, COM                       | $V_0 = 1.8 \text{ V}$<br>$V_0 = 3.3 \text{ V}$ |       |        |      |        |  |

|            |                                         |                                            | ν <sub>0</sub> = 3.3 ν                         |       | 0.92   |      |        |  |

|            |                                         |                                            | Default configuration:                         |       |        |      |        |  |

| TRL        | Input standby power                     | Turned off with                            | Monitoring enabled,                            |       | 170    |      | mW     |  |

| 1116       | ,                                       | CTRL-pin                                   | Precise timing enabled                         |       |        |      |        |  |

|            |                                         |                                            |                                                |       |        |      |        |  |

|            | Internal input capacitar                |                                            |                                                |       | 70     |      |        |  |

| Charac           | teristics                       |                                                              | Conditions            | Min  | Тур                  | Max    | Unit             |  |

|------------------|---------------------------------|--------------------------------------------------------------|-----------------------|------|----------------------|--------|------------------|--|

| C <sub>o</sub>   | Internal output capacita        | nce                                                          |                       |      | 200                  |        | μF               |  |

| - 0              | Total external output ca        |                                                              | See Note 9            | 300  |                      | 15 000 | μF               |  |

| $C_{OUT}$        | ESR range of capacitors         | <b>,</b>                                                     | Can Note O            | 5    |                      |        |                  |  |

|                  | (per single capacitor)          |                                                              | See Note 9            | 5    |                      | 30     | mΩ               |  |

|                  |                                 |                                                              | $V_0 = 0.6 \text{ V}$ |      | 115                  |        |                  |  |

|                  | Load transient peak             | Default configuration                                        |                       |      | -                    |        |                  |  |

| $V_{tr1}$        | voltage deviation<br>(H to L)   | $di/dt = 2 A/\mu s$                                          | $V_0 = 1.0 \text{ V}$ |      | 122                  |        | mV               |  |

| uı               | Load step 25-75-25%             | $C_0 = 470 \mu F$ (minimum external capacitance) see Note 12 | $V_0 = 1.8 \text{ V}$ |      | 143                  |        |                  |  |

|                  | of max I <sub>o</sub>           | ,                                                            | $V_0 = 3.3 \text{ V}$ |      | 174                  |        |                  |  |

|                  | Load transient recovery         |                                                              | $V_0 = 0.6 \text{ V}$ |      | 60                   |        |                  |  |

|                  | time, Note 5                    | Default configuration<br>di/dt = 2 A/µs                      | $V_0 = 1.0 \text{ V}$ |      | 65                   |        |                  |  |

| t <sub>tr1</sub> | (H to L)<br>Load step 25-75-25% | $C_0 = 470 \mu\text{F}$ (minimum external                    | $V_0 = 1.8 \text{ V}$ |      | 115                  |        | μs               |  |

|                  | of max I <sub>0</sub>           | capacitance) see Note 12                                     | $V_0 = 3.3 \text{ V}$ |      | 130                  |        |                  |  |

|                  |                                 |                                                              | -0 0.0                |      | .00                  |        |                  |  |

|                  | Switching frequency             |                                                              |                       |      | 320                  |        | kHz              |  |

| f <sub>s</sub>   | Switching frequency rar         | nge                                                          | PMBus configurable    |      | 200-640              |        | kHz              |  |

| -8               | Switching frequency set         | <u> </u>                                                     | gardoro               | -5   | 200 010              | 5      | %                |  |

|                  | Control Circuit PWM Duty Cycle  |                                                              |                       | 5    |                      | 95     | %                |  |

|                  | Minimum Sync Pulse W            |                                                              |                       | 150  |                      | 30     | ns               |  |

|                  | Input Clock Frequency [         |                                                              | External clock source | -13  |                      | 13     | %                |  |

|                  | input block frequency t         | THE TOICIANCE                                                | External clock source | 10   |                      | 10     | /0               |  |

|                  |                                 | UVLO threshold                                               |                       |      | 3.85                 | ·      | V                |  |

|                  |                                 | UVLO threshold range                                         | PMBus configurable    |      | 3.85-14              |        | V                |  |

|                  |                                 | Set point accuracy                                           |                       | -150 |                      | 150    | mV               |  |

|                  | nder Voltage Lockout,           | UVLO hysteresis                                              |                       |      | 0.35                 |        | V                |  |

| UVLO             |                                 | UVLO hysteresis range                                        | PMBus configurable    |      | 0-10.15              |        | V                |  |

|                  |                                 | Delay                                                        | <b>J</b>              |      | 2.5                  |        | μS               |  |

|                  |                                 | Fault response                                               | See Note 3            | A    | utomatic restart, 70 | ms     |                  |  |

|                  |                                 | IOVP threshold                                               | 000 11010 0           | 7.5  | 16                   |        | V                |  |

|                  |                                 | IOVP threshold range                                         | PMBus configurable    |      | 4.2-16               |        | V                |  |

|                  |                                 | Set point accuracy                                           | 1 WE US COMINGUIA DIC | -150 | 7.2 10               | 150    | mV               |  |

| Input 0v         | ver Voltage Protection,         |                                                              |                       | -130 | 1                    | 130    | V                |  |

| IOVP             |                                 | IOVP hysteresis                                              | DMD. configurable     |      |                      |        | V                |  |

|                  |                                 | IOVP hysteresis range                                        | PMBus configurable    |      | 0-11.8               |        |                  |  |

|                  |                                 | Delay                                                        | 0. 11.1.0             |      | 2.5                  |        | μS               |  |

|                  |                                 | Fault response                                               | See Note 3            | Al   | utomatic restart, 70 | ms     | 0/1/             |  |

|                  |                                 | PG threshold                                                 |                       |      | 90                   |        | % V <sub>0</sub> |  |

|                  | Good, PG,                       | PG hysteresis                                                |                       |      | 5                    |        | % V <sub>0</sub> |  |

| See Not          | e 2                             | PG delay                                                     | See Note 19           |      | Direct after DLC     |        | ms               |  |

|                  |                                 | PG delay range                                               | PMBus configurable    |      | 0-500                |        | S                |  |

|                  |                                 | UVP threshold                                                |                       |      | 85                   |        | % V <sub>0</sub> |  |

|                  |                                 | UVP threshold range                                          | PMBus configurable    |      | 0-100                |        | % V <sub>0</sub> |  |

|                  |                                 | UVP hysteresis                                               |                       |      | 5                    |        | % V <sub>0</sub> |  |

| Output v         | /oltage                         | OVP threshold                                                |                       |      | 115                  |        | % V <sub>0</sub> |  |

|                  | der Voltage Protection,         | OVP threshold range                                          | PMBus configurable    |      | 100-115              |        | % V <sub>0</sub> |  |

| OVP/UV           |                                 | UVP/OVP response time                                        | bao comigarabio       |      | 25                   |        | μS               |  |

| O VI / U VI      | ı                               | UVP/OVP                                                      |                       |      |                      |        | μδ               |  |

|                  |                                 | response time range                                          | PMBus configurable    |      | 5-60                 |        | μS               |  |

|                  |                                 | Fault response                                               | See Note 3            | Λ.   | utomatic restart, 70 | me     |                  |  |

|                  |                                 |                                                              | SEC NUIC S            | A    |                      | 1119   | Λ                |  |

|                  |                                 | OCP threshold                                                | DMDue configurable    |      | 32                   |        | A                |  |

| Over Cu          | rrent Protection,               | OCP threshold range                                          | PMBus configurable    |      | 0-32                 |        | A                |  |

| OCP              | - /                             | Protection delay,                                            | See Note 4            |      | 32                   |        | T <sub>sw</sub>  |  |

|                  |                                 | Protection delay range                                       | PMBus configurable    |      | 1-32                 |        | T <sub>sw</sub>  |  |

|                  |                                 | Fault response                                               | See Note 3            | l Ai | utomatic restart, 70 | ms     |                  |  |

# Pokami OKDx-T/25-W12-xxx-C

### 25A Digital PoL DC-DC Converter Series

| Characteri                                       | stics                              |                                 | Conditions                                                    | Min       | Тур                  | Max          | Unit    |

|--------------------------------------------------|------------------------------------|---------------------------------|---------------------------------------------------------------|-----------|----------------------|--------------|---------|

|                                                  |                                    | OTP threshold                   |                                                               |           | 120                  |              | °C      |

| Over Temperature Protection, OTP threshold range |                                    | OTP threshold range             | PMBus configurable                                            |           | -40+125              |              | °C      |

| TP at P2                                         | •                                  | OTP hysteresis                  |                                                               |           | 25                   |              | °C      |

| ee Note 8                                        |                                    | OTP hysteresis range            | PMBus configurable                                            |           | 0-165                |              | °C      |

|                                                  |                                    | Fault response                  | See Note 3                                                    | Au        | tomatic restart, 240 | ms           |         |

|                                                  |                                    |                                 |                                                               |           |                      |              |         |

|                                                  | Logic input low three              | eshold                          | SYNC, SAO, SA1, SCL, SDA, GCB, CTRL,                          |           |                      | 0.8          | V       |

| H                                                | Logic input high thr               | eshold                          | VSET                                                          | 2         |                      |              | V       |

|                                                  | Logic input low sink               | c current                       | CTRL                                                          |           |                      | 0.6          | mA      |

| )L                                               | Logic output low sig               | gnal level                      |                                                               |           |                      | 0.4          | V       |

| )H                                               | Logic output high si               | ignal level                     | CANC CCL CDV CVIEDT CCD DC                                    | 2.25      |                      |              | V       |

| _                                                | Logic output low sir               | nk current                      | SYNC, SCL, SDA, SALERT, GCB, PG                               |           |                      | 4            | mA      |

| 1                                                | Logic output high so               |                                 |                                                               |           |                      | 2            | mA      |

| t                                                | Setup time, SMBus                  |                                 | See Note 1                                                    | 300       |                      |              | ns      |

| ıld                                              | Hold time, SMBus                   |                                 | See Note 1                                                    | 250       |                      |              | ns      |

| e                                                | Bus free time, SMB                 |                                 | See Note 1                                                    | 2         |                      |              | ms      |

| p                                                | Internal capacitance               | e on logic pins                 |                                                               |           | 10                   |              | pF      |

|                                                  |                                    |                                 |                                                               |           |                      |              |         |

| itialization                                     | time                               |                                 | See Note 10                                                   |           | 40                   |              | ms      |

|                                                  |                                    | Delay duration                  | See Note 16                                                   |           | 10                   |              | ma      |

| 2                                                |                                    | Delay duration range            | PMBus configurable                                            |           | 5-500000             |              | ms      |

| utput Voltage Delay accuracy elay Time turn-on   |                                    | Delay accuracy                  |                                                               |           | 0.05/.4              |              | mo      |

|                                                  |                                    | turn-on                         |                                                               |           | -0.25/+4             |              | ms      |

| ee note o                                        |                                    | Delay accuracy                  | curacy                                                        |           | -0.25/+4             |              | ms      |

|                                                  |                                    | turn-off                        |                                                               |           |                      |              | 1115    |

| utput Volta                                      | Ramp duration                      |                                 |                                                               |           | 10                   |              | ms      |

| amp Time                                         | go                                 | Ramp duration range             | PMBus configurable                                            |           | 0-200                |              | 1113    |

| ee Note 13                                       | <b>!</b>                           | Ramp time accuracy              |                                                               |           | 100                  |              | μs      |

| CC NOLC 10                                       | 1                                  | Trainp time accuracy            | Current sharing operation                                     |           | 20                   |              | %       |

|                                                  |                                    |                                 |                                                               |           |                      |              |         |

| TRK Input E                                      | Bias Current                       |                                 | $V_{VTRK} = 5.5 V$                                            |           | 110                  | 200          | μA      |

|                                                  |                                    |                                 | 100% tracking, see Note 7                                     | -100      |                      | 100          | mV      |