### **General Description**

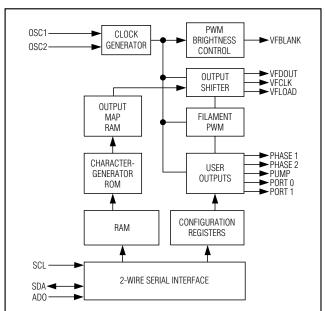

The MAX6851 compact vacuum-fluorescent display (VFD) controller provides microprocessors with the multiplex timing for 7-segment, 14-segment, or 16-segment alphanumeric VFD displays up to 96 characters and controls industry-standard, shift-register, high-voltage grid/anode VFD tube drivers. The device supports display tubes using either one or two digits per grid, as well as universal displays. Hardware is included to simplify the generation of cathode bias and filament supplies and to provide up to five logic outputs, including a buzzer driver. The MAX6851 provides an internal crosspoint switch to match any tube-driver, shift-register grid/anode order, and is compatible with both chip-inglass and external tube drivers.

The MAX6851 includes an ASCII 104-character font, multiplex scan circuitry, and static RAM that stores digit, cursor, and annunciator data, as well as font data for 24 user-definable characters. The display intensity can be adjusted by an internal 16-step digital brightness control. The device also includes separate annunciator and cursor control with automatic blinking, as well as a low-power shutdown mode.

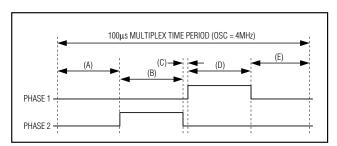

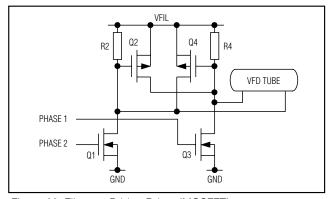

The MAX6851 provides timing to generate the PWM waveforms to drive the tube filament from a DC supply. The filament drive is synchronized to the display multiplexing to eliminate beat artifacts.

For a high-speed SPITM/QSPITM/MICROWIRETM interfaced version, refer to the MAX6850 data sheet.

## **Applications**

Display Modules

Retail POS Displays

Weight and Tare

Displays

Industrial Controllers White Goods Professional Audio Equipment

Bar Graph Displays

Pin Configuration and Functional Diagram appear at end of data sheet.

SPI and QSPI are trademarks of Motorola, Inc.

MICROWIRE is a trademark of National Semiconductor Corp.

#### **Features**

- ♦ 400kbps I<sup>2</sup>C-Compatible Serial Interface

- ♦ 2.7V to 3.6V Operation

- Controls Up to 48 Grids of 7-Segment, 14-Segment, or 16-Segment Alphanumeric Digits

- One Digit and Two Digits per Grid and Universal Displays Supported

- ♦ 16-Step Digital Brightness Control

- ♦ Built-In ASCII 104-Character Font

- ♦ 24 User-Definable Characters

- Up to Four Annunciators per Grid with Automatic Blinking Control

- ♦ Separate Cursor Control with Automatic Blinking

- ♦ Filament Drive Full-Bridge Waveform Synthesis

- ♦ Charge-Pump Drive Output to Generate Cathode Bias Supply

- Buzzer Tone Generator with Single-Ended or Push-Pull Driver

- ♦ Up to Five General-Purpose Logic Outputs

- ♦ 11µA Low-Power Shutdown (Data Retained)

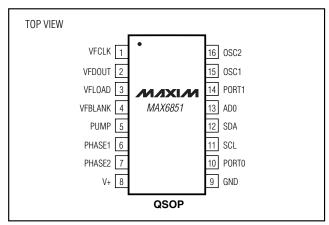

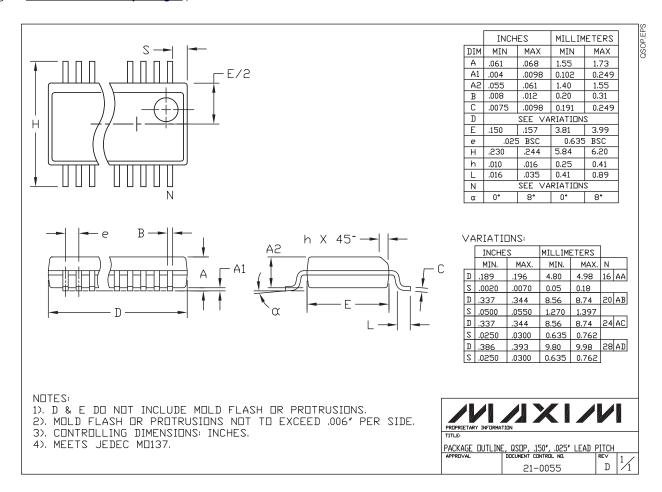

- ♦ 16-Pin QSOP Package

## Ordering Information

| PART       | TEMP RANGE      | PIN-PACKAGE |

|------------|-----------------|-------------|

| MAX6851AEE | -40°C to +125°C | 16 QSOP     |

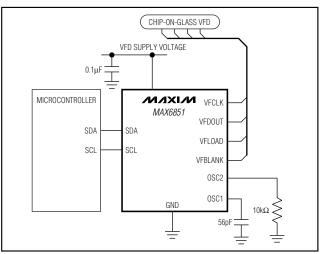

## \_Typical Application Circuit

MIXIM

Maxim Integrated Products

### **ABSOLUTE MAXIMUM RATINGS**

| Voltage (with respect to GND)   |                       |

|---------------------------------|-----------------------|

| V+                              | 0.3V to +4V           |

| ADO, SDA, SCL                   | 0.3V to +5.5V         |

| All Other Pins                  | 0.3V to $(V+ + 0.3V)$ |

| Current                         |                       |

| V+                              | 200mA                 |

| GND                             | 200mA                 |

| PHASE1, PHASE2, PORT0, PORT1, F | PUMP±150mA            |

| VFCLK, VFDOUT, VFLOAD, VFBLAN   | K±150mA               |

| SDA                             | 15mA                  |

| Continuous Power Dissipation ( $T_A = +70^{\circ}\text{C}$ )       | 7000) 007:\    |

|--------------------------------------------------------------------|----------------|

| 16-Pin QSOP (derate at 8.34mW/°C above -                           | F/U°C)66/MW    |

| Operating Temperature Range (T <sub>MIN</sub> , T <sub>MAX</sub> ) |                |

| MAX6851AEE                                                         | 40°C to +125°C |

| Junction Temperature                                               | +150°C         |

| Storage Temperature Range                                          | 65°C to +150°C |

| Lead Temperature (soldering, 10s)                                  | +300°C         |

|                                                                    |                |

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

#### DC ELECTRICAL CHARACTERISTICS

(Typical Operating Circuit, V+ = 2.7V to 3.6V,  $T_A = T_{MIN}$  to  $T_{MAX}$ , unless otherwise noted.) (Note 1)

| PARAMETER                                        | SYMBOL                            | CONDITIONS                                                                                   | 3                            | MIN  | TYP  | MAX  | UNITS |

|--------------------------------------------------|-----------------------------------|----------------------------------------------------------------------------------------------|------------------------------|------|------|------|-------|

| Operating Supply Voltage                         | V+                                |                                                                                              |                              | 2.7  |      | 3.6  | V     |

| Shutdown Supply Current                          | I <sub>SHDN</sub>                 | Shutdown mode, all digital inputs at V+ or GND                                               | $T_A = T_{MIN}$ to $T_{MAX}$ |      |      | 85   | μA    |

|                                                  |                                   | Inputs at V+ of GND                                                                          | T <sub>A</sub> = +25°C       |      | 11.5 | 30   |       |

| Operating Supply Current                         | l+                                | OSC = 4MHz<br>VFLOAD, VFDOUT, VFCLK,                                                         | $T_A = T_{MIN}$ to $T_{MAX}$ |      |      | 3.5  | mA    |

|                                                  |                                   | VFBLANK, loaded 100pF                                                                        | $T_A = +25$ °C               |      | 1.3  | 3.0  |       |

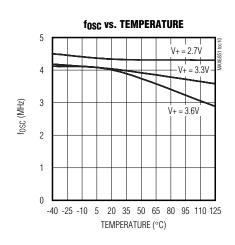

| Master Clock Frequency (OSC Internal Oscillator) | fosc                              | OSC1 fitted with $C_{OSC}$ = 56p with $R_{OSC}$ = 10k $\Omega$ ; see the 7 Operating Circuit |                              | 4    |      | MHz  |       |

| Master Clock Frequency (OSC External Oscillator) |                                   | OSC1 overdriven with extern                                                                  | 2                            |      | 8    | MHz  |       |

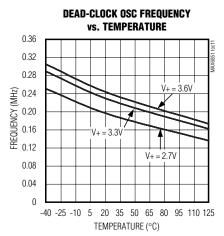

| Dead-Clock Protection Frequency                  |                                   |                                                                                              |                              |      | 200  |      | kHz   |

| OSC High Time                                    | tch                               |                                                                                              |                              | 50   |      |      | ns    |

| OSC Low Time                                     | t <sub>CL</sub>                   |                                                                                              |                              | 50   |      |      | ns    |

| Fast or Slow Segment Blink Duty<br>Cycle         |                                   | (Note 2)                                                                                     |                              | 49.5 |      | 50.5 | %     |

| LOGIC INPUTS AND OUTPUTS                         |                                   |                                                                                              |                              |      |      |      |       |

| Input Leakage Current ADO,<br>SDA, SCL           | I <sub>IH</sub> , I <sub>IL</sub> |                                                                                              |                              |      | 0.2  | 1    | μА    |

| Logic-High Input Voltage ADO,<br>SDA, SCL        | VIH                               |                                                                                              |                              | 2.4  |      |      | V     |

| Logic-Low Input Voltage ADO,<br>SDA, SCL         | VIL                               |                                                                                              |                              |      | _    | 0.6  | V     |

| SDA Output Low Voltage                           | Volsda                            | I <sub>SINK</sub> = 4mA                                                                      |                              |      |      | 0.5  | V     |

| Input Capacitance                                | Cı                                | (Note 2)                                                                                     |                              |      |      | 10   | рF    |

## **DC ELECTRICAL CHARACTERISTICS (continued)**

(Typical Operating Circuit, V+ = 2.7V to 3.6V,  $T_A = T_{MIN}$  to  $T_{MAX}$ , unless otherwise noted.) (Note 1)

| PARAMETER                                                                                                       | SYMBOL            | CONDITIONS                                                   | MIN      | TYP | MAX | UNITS |

|-----------------------------------------------------------------------------------------------------------------|-------------------|--------------------------------------------------------------|----------|-----|-----|-------|

| Output Rise and Fall Time<br>PHASE1, PHASE2, PORT0,<br>PORT1, PUMP, VFLOAD,<br>VFDOUT, VFCLK, VFBLANK           | trft              | C <sub>LOAD</sub> = 100pF                                    |          |     | 25  | ns    |

| Output High-Voltage<br>PHASE1, PHASE2, PORT0,<br>PORT1, PUMP, VFLOAD,<br>VFDOUT, VFCLK, VFBLANK                 | Voн               | ISOURCE = 10mA                                               | V+ - 0.6 |     |     | V     |

| Output Low-Voltage<br>PHASE1, PHASE2, PORT0,<br>PORT1, PUMP, VFLOAD,<br>VFDOUT, VFCLK, VFBLANK                  | V <sub>OL</sub>   | ISINK = 10mA                                                 |          |     | 0.4 | V     |

| Output Short-Circuit Source<br>Current PHASE1, PHASE2,<br>PORT0, PORT1, PUMP, VFLOAD,<br>VFDOUT, VFCLK, VFBLANK | I <sub>OHSC</sub> | Output programmed high, output short circuit to GND (Note 2) |          | 62  | 125 | mA    |

| Output Short-Circuit Sink Current<br>PHASE1, PHASE2, PORT0,<br>PORT1, PUMP, VFLOAD,<br>VFDOUT, VFCLK, VFBLANK   | lolsc             | Output programmed low, output short circuit to V+ (Note 2)   |          | 72  | 125 | mA    |

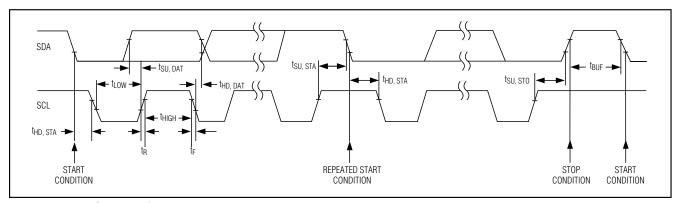

| 2-WIRE SERIAL INTERFACE TIM                                                                                     | NG CHARAC         | CTERISTICS (Figure 8)                                        |          |     |     |       |

| Serial Clock Frequency                                                                                          | fscl              |                                                              |          |     | 400 | kHz   |

| Bus Free Time Between a STOP and a START Condition                                                              | t <sub>BUF</sub>  |                                                              | 1.3      |     |     | μs    |

| Hold Time (Repeated) START Condition                                                                            | tHD,STA           |                                                              | 0.6      |     |     | μs    |

| Repeated START Condition Setup Time                                                                             | tsu,sta           |                                                              | 0.6      |     |     | μs    |

| STOP Condition Setup Time                                                                                       | tsu,sto           |                                                              | 0.6      |     |     | μs    |

| Data Hold Time                                                                                                  | thd,dat           |                                                              |          |     | 0.9 | μs    |

| Data Setup Time                                                                                                 | thd,dat           | (Note 3)                                                     | 100      |     |     | ns    |

| SCL Clock Low Period                                                                                            | tLOW              |                                                              | 1.3      |     |     | μs    |

| SCL Clock High Period                                                                                           | thigh             |                                                              | 0.6      |     |     | μs    |

### DC ELECTRICAL CHARACTERISTICS (continued)

(Typical Operating Circuit, V+ = 2.7V to 3.6V, TA = TMIN to TMAX, unless otherwise noted.) (Note 1)

| PARAMETER                                        | SYMBOL         | CONDITIONS   | MIN | TYP                       | MAX  | UNITS |

|--------------------------------------------------|----------------|--------------|-----|---------------------------|------|-------|

| Rise Time of Both SDA and SCL Signals, Receiving | t <sub>R</sub> | (Notes 2, 4) |     | 20 +<br>0.1C <sub>B</sub> | 300  | ns    |

| Fall Time of Both SDA and SCL Signals, Receiving | tF             | (Notes 2, 4) |     | 20 +<br>0.1C <sub>B</sub> | 300  | ns    |

| Fall Time of SDA Transmitting                    | tF             | (Notes 2, 5) |     | 20 +<br>0.1C <sub>B</sub> | 250  | ns    |

| Pulse Width of Spike Suppressed                  | tsp            | (Note 6)     | 50  |                           |      | ns    |

| Capacitive Load for Each Bus Line                | CB             | (Note 2)     |     | 400                       |      | рF    |

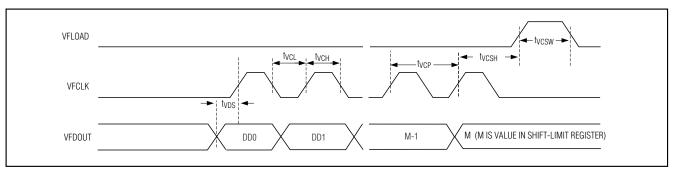

| VFD INTERFACE TIMING CHARA                       | CTERISTICS     | (Figure 16)  |     |                           |      |       |

| VFCLK Clock Period                               | tvcp           | (Note 2)     | 500 |                           | 2050 | ns    |

| VFCLK Pulse Width High                           | tvcH           | (Note 2)     | 250 |                           |      | ns    |

| VFCLK Pulse Width Low                            | tvcL           | (Note 2)     | 250 |                           |      | ns    |

| VFCLK Rise to VFD Load Rise<br>Hold Time         | tvcsh          | (Note 2)     | 19  |                           |      | μs    |

| VFDOUT Setup Time                                | tvds           | (Note 2)     | 50  |                           |      | ns    |

| VFLOAD Pulse High                                | tvcsw          | (Note 2)     | 245 |                           |      | ns    |

**Note 1:** All parameters tested at  $T_A = +25$ °C. Specifications over temperature are guaranteed by design.

Note 2: Guaranteed by design.

Note 3: A master device must provide a hold time of at least 300ns for the SDA signal (referred to V<sub>IL</sub> of the SCL signal) in order to bridge the undefined region of SCL's falling edge.

Note 4: CB = total capacitance of one bus line in pF; tR and tF measured between 0.3V+ and 0.7V+.

Note 5: I<sub>SINK</sub> ≤ 6mA; C<sub>B</sub> = total capacitance of one bus line in pF; t<sub>R</sub> and t<sub>F</sub> measured between 0.3V+ and 0.7V+.

Note 6: Input filters on the SDA and SCL inputs suppress noise spikes less than 50ns.

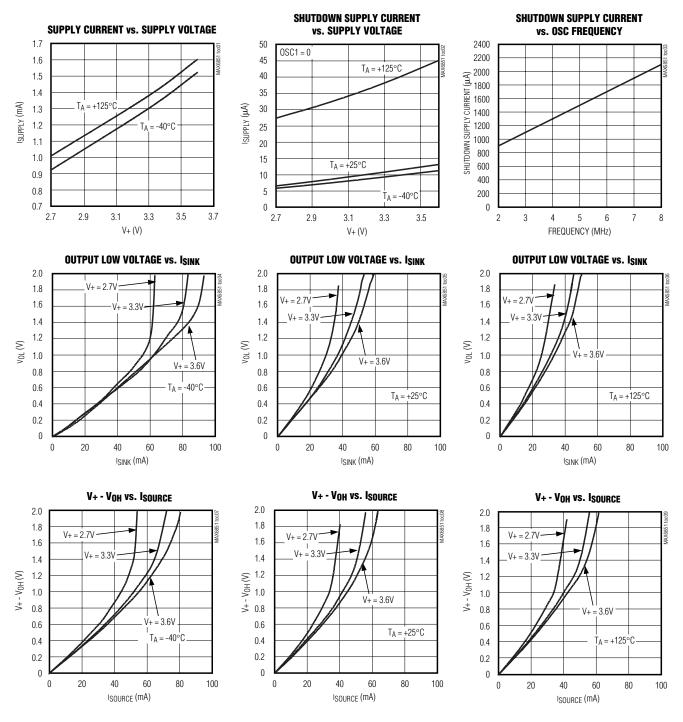

### **Typical Operating Characteristics**

(Typical Application Circuit, V+ = 3.3V, T<sub>A</sub> = +25°C, unless otherwise noted.)

## Typical Operating Characteristics (continued)

(Typical Application Circuit, V+ = 3.3V, T<sub>A</sub> = +25°C, unless otherwise noted.)

### Pin Description

| PIN | NAME    | FUNCTION                                                                                                                                                                        |

|-----|---------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1   | VFCLK   | Serial-Clock Output to External Driver. Push-pull clock output to external display driver. On VFCLK's falling edge, data is clocked out of VFDOUT.                              |

| 2   | VFDOUT  | Serial-Data Output to External Driver. Push-pull data output to external display driver.                                                                                        |

| 3   | VFLOAD  | Serial-Load Output to External Driver. Push-pull load output to external display driver. Rising edge is used by external display driver to load serial data into display latch. |

| 4   | VFBLANK | Display Blanking Output to External Driver. Push-pull blanking output to external display driver used for PWM intensity control.                                                |

| 5   | PUMP    | Pump General-Purpose Output. User-configurable push-pull logic output.                                                                                                          |

| 6   | PHASE1  | Filament Drive PHASE1 Output and General-Purpose Output. User-configurable push-pull logic output can also be used as a driver for external filament bridge drive.              |

| 7   | PHASE2  | Filament Drive PHASE2 Output and General-Purpose Output. User-configurable push-pull logic output can also be used as a driver for external filament bridge drive.              |

| 8   | V+      | Positive Supply Voltage. Bypass V+ to GND with a 0.1µF ceramic capacitor.                                                                                                       |

| 9   | GND     | Ground                                                                                                                                                                          |

| 10  | PORT0   | PORTO General-Purpose Output. User-configurable push-pull logic output.                                                                                                         |

| 11  | SCL     | Serial-Clock Input                                                                                                                                                              |

| 12  | SDA     | Serial-Data Input I/O                                                                                                                                                           |

| 13  | AD0     | Address Input 0. Sets device slave address. Connect to GND, V+, SCL, or SDA to give four logic combinations. See Table 25.                                                      |

| 14  | PORT1   | PORT1 General-Purpose Output. User-configurable push-pull logic output.                                                                                                         |

## Pin Description (continued)

| PIN | NAME | FUNCTION                                                                                                                                                                |

|-----|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 15  | OSC1 | Multiplex Clock Input 1. To use the internal oscillator, connect capacitor Cosc from OSC1 to GND. To use the external clock, drive OSC1 with a 2MHz to 8MHz CMOS clock. |

| 16  | OSC2 | Multiplex Clock Input 2. Connect resistor Rosc from OSC2 to GND.                                                                                                        |

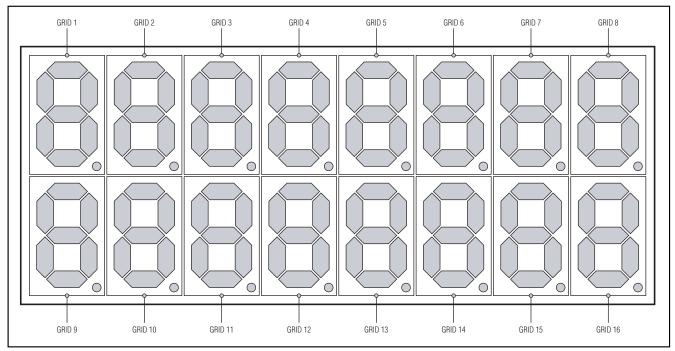

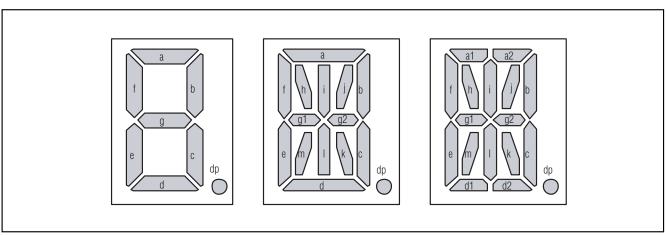

Figure 1. Example of a One-Digit-per-Grid Display

## Detailed Description Overview of the MAX6851

The MAX6851 VFD controller generates the multiplex timing for the following VFD display types:

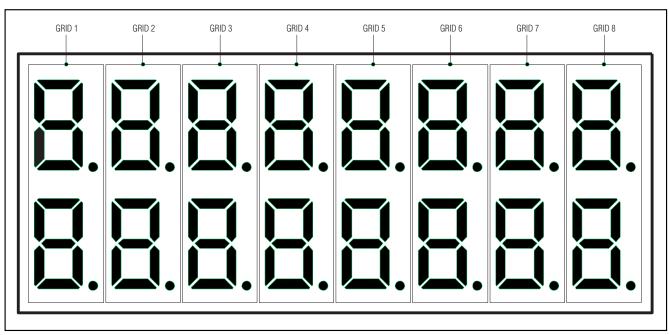

- Multiplexed displays with one digit per grid, and up to 48 grids (in 48/1 mode). Each grid can contain one 7-, 14-, or 16-segment character, a decimal place (DP) segment, a cursor segment, and four extra annunciator segments (Figure 1).

- Multiplexed displays with two digits per grid, and up to 48 grids (in 96/2 mode). Each grid can contain two 7-, 14-, or 16-segment characters, two DP segments, and two cursor segments. No annunciator segments are supported (Figure 2).

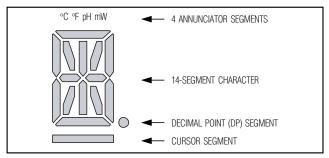

Each digit can have a 7-, 14-, or 16-segment character, a DP segment, a cursor segment, and (for one-digit-per-grid displays only) four annunciators (Figure 3).

The 7, 14, or 16 segments use on-chip fonts that map the segments. The fonts comprise an ASCII 104-character fixed-font set, and 24 user-definable characters. The predefined characters follow the Arial font, with the addition of the following common symbols: £, , ¥, °,  $\mu$ ,  $\pm$ , ↑, and  $\downarrow$ . The 24 user-definable characters are uploaded by the user into on-chip RAM through the serial interface and are lost when the device is powered down. As well as custom 7- and 14-segment characters, the user-definable fonts can control up to 14 custom segments, bar graph characters, or graphics.

Annunciator segments have individual, independent control, so any combination of annunciators can be lit. Annunciators can be off, lit, or blink either in phase or

Figure 2. Example of a Two-Digit-per-Grid Display

Figure 3. Digit Structure with 14-Segment Character, DP Segment, Cursor Segment, and Four Annunciators

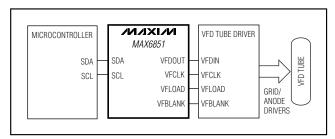

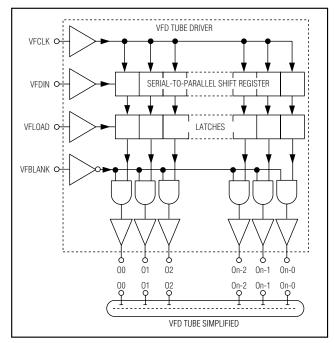

Figure 4. Connection of the MAX6851 to VFD Driver and VFD Tube

out of phase with the cursor. The blink-speed control is software selectable to be one or two blinks per second (OSC = 4MHz).

DP segments can be lit or off, but have no blink control. A DP segment is set by the same command that writes the digit's 7-, 14-, or 16-segment character.

The cursor segment is controlled differently. A single register selects one digit's cursor from the entire display, and that can be lit either continuously or blinking. All the other digits' cursors are off.

The designations of DP, cursor, and annunciator are interchangeable. For example, consider an application requiring only one DP lit at a time, but the DP needs to blink. The DP function does not have blink capability. Instead, the DP segments on the display are routed (using the output map) to the cursor function. In this case, the DP segments are controlled using the cursor register.

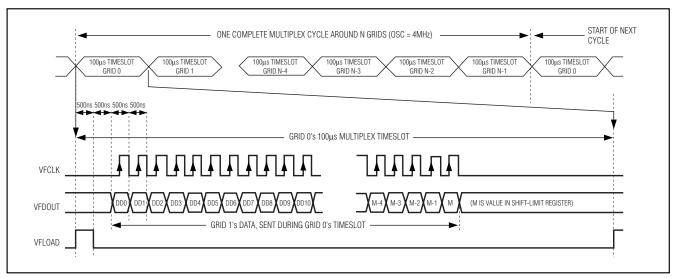

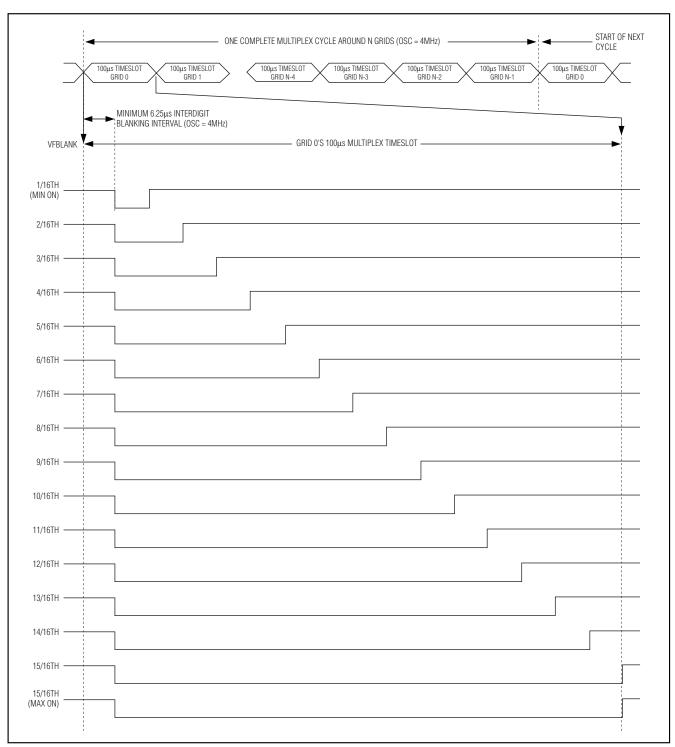

The output of the controller is a 4-wire serial stream that interfaces to industry-standard, shift-register, high-voltage grid/anode VFD tube drivers (Figure 4). This interface uses three outputs to transfer and latch grid and anode data into the tube drivers, and a fourth output that enables/disables the tube driver outputs (Figure 6). The enable/disable control is modulated by the MAX6851 for both PWM intensity control and interdigit

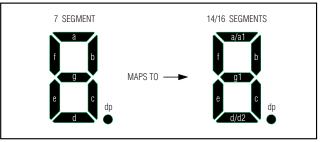

Figure 5. Segment Labeling for 7-, 14-, and 16-Segment Displays

blanking, and disables the tube driver in shutdown. The controller multiplexes the display by enabling each grid of the VFD in turn for 100µs (OSC = 4MHz) with the correct segment (anode) data. The data for the next grid is transferred to the tube drivers during the display time of the current grid.

The controller uses an internal output map to match any tube-driver's shift-register grid/anode order, and is therefore compatible with all VFD internal chip-in-glass or external tube drivers.

The MAX6851 provides five high-current output ports, which can be configured for a variety of functions:

The PUMP output can be configured as either an 80kHz (OSC = 4MHz) clock intended for DC-to-DC converter use, the 4-wire serial interface's DOUT data output, or a general-purpose logic output.

The PHASE1 and PHASE2 outputs can be individually configured as either 10kHz PWM outputs (OSC = 4MHz) intended for filament driving, blink status outputs, or general-purpose logic outputs.

The PORT0 and PORT1 outputs can be individually configured as either 625Hz, 1250Hz, or 2500Hz clocks (OSC = 4MHz) intended for buzzer driving, the 4-wire serial interface's DOUT data output, blink or shutdown status outputs, or general-purpose logic outputs. Figure 5 shows segment labeling for 7-, 14-, and 16-segment displays. Figure 6 is a block diagram of the VFD tube driver and VFD tube.

#### **Display Modes**

The MAX6851 has two display modes (Table 1), selected by the M bit in the configuration register (Table 23). The display modes trade the maximum allowable num-

Figure 6. Block Diagram of VFD Tube Driver and VFD Tube

ber of digits (96/2 mode) against the availability of annunciator segments (48/1 mode). Table 2 is the register address map.

#### **Initial Power-Up**

On initial power-up, all control registers are reset, the display segment and annunciator data are cleared, intensity is set to minimum, and shutdown is enabled (Table 3).

### **Table 1. Display Modes**

| DISPLAY<br>MODE | MAXIMUM NO. OF DIGITS                                  | MAXIMUM NO. OF ANNUNCIATORS | MAXIMUM NO. OF GRIDS | DIGITS COVERED<br>BY EACH GRID |

|-----------------|--------------------------------------------------------|-----------------------------|----------------------|--------------------------------|

| 48/1 mode       | 48 digits, each with a DP segment and a cursor segment | 4 per digit                 |                      | 1 digit per grid               |

| 96/2 mode       | 96 digits, each with a DP segment and a cursor segment | None                        | 48 grids             | 2 digits per grid              |

### **Table 2. Register Address Map**

| REGISTER                                    |   |     | COI | MMAND | ADDRE | SS  |    |    | HEX  |

|---------------------------------------------|---|-----|-----|-------|-------|-----|----|----|------|

| negioten                                    |   | D14 | D13 | D12   | D11   | D10 | D9 | D8 | CODE |

| No-Op                                       | 0 | 0   | 0   | 0     | 0     | 0   | 0  | 0  | 0x00 |

| VFBLANK polarity                            | 0 | 0   | 0   | 0     | 0     | 0   | 0  | 1  | 0x01 |

| Intensity                                   | 0 | 0   | 0   | 0     | 0     | 0   | 1  | 0  | 0x02 |

| Grids                                       | 0 | 0   | 0   | 0     | 0     | 0   | 1  | 1  | 0x03 |

| Configuration                               | 0 | 0   | 0   | 0     | 0     | 1   | 0  | 0  | 0x04 |

| User-defined fonts                          | 0 | 0   | 0   | 0     | 0     | 1   | 0  | 1  | 0x05 |

| Output map                                  | 0 | 0   | 0   | 0     | 0     | 1   | 1  | 0  | 0x06 |

| Display test and device ID                  | 0 | 0   | 0   | 0     | 0     | 1   | 1  | 1  | 0x07 |

| PUMP register                               | 0 | 0   | 0   | 0     | 1     | 0   | 0  | 0  | 0x08 |

| Filament duty cycle                         | 0 | 0   | 0   | 0     | 1     | 0   | 0  | 1  | 0x09 |

| PHASE1                                      | 0 | 0   | 0   | 0     | 1     | 0   | 1  | 0  | 0x0A |

| PHASE2                                      | 0 | 0   | 0   | 0     | 1     | 0   | 1  | 1  | 0x0B |

| PORT0                                       | 0 | 0   | 0   | 0     | 1     | 1   | 0  | 0  | 0x0C |

| PORT1                                       | 0 | 0   | 0   | 0     | 1     | 1   | 0  | 1  | 0x0D |

| Shift limit                                 | 0 | 0   | 0   | 0     | 1     | 1   | 1  | 0  | 0x0E |

| Cursor                                      | 0 | 0   | 0   | 0     | 1     | 1   | 1  | 1  | 0x0F |

| Factory reserved. Do not write to register. | Х | 0   | 0   | 1     | 0     | 0   | 0  | 0  | 0x10 |

#### **Character Registers**

The MAX6851 uses 48 character registers (48/1 mode) (Table 4) or 96 character registers (96/2 mode) (Table 5) to store the 7-, 14-, and 16-segment characters (Table 6). Each digit is represented by 1 byte of memory. The data in the character registers does not control the character segments directly. Instead, the register data is used to address a character generator, which stores the data of the 128-character font (Table 7). The lower 7 bits of the character data (D6 to D0) select a character from the font table. The most significant bit (MSB) of the register data (D7) controls the DP segment of the digit; it is set to light the DP, cleared to leave it unlit.

The character registers address maps are shown in Table 4 (48/1 mode) and Table 5 (96/2 mode).

In 48/1 mode, the character registers use a single address range 0x20 to  $\{0x20 + g\}$ , where g is the value in the grids register (Table 28). The 48/1 mode upper address limit, when g is 0x2F, is therefore 0x4F. The address range 0x50 to 0x7F is used for annunciator data in 48/1 mode.

In 96/2 mode, the character registers use two address ranges. The first row's address range is 0x20 to  $\{0x20+g\}$ . The second row's address range is 0x50 to  $\{0x50+g\}$ . Therefore, in 96/2 mode, the character registers are only one contiguous memory range when a 48-grid display is used.

**Table 3. Initial Power-Up Register Status**

| DECICTED                          | DOWED UP CONDITION                                             | COMMAND |    |    | R       | EGISTI   | ER DAT | Ά               |      |    |  |

|-----------------------------------|----------------------------------------------------------------|---------|----|----|---------|----------|--------|-----------------|------|----|--|

| REGISTER                          | POWER-UP CONDITION                                             | ADDRESS | D7 | D6 | D5      | D4       | D3     | D2              | D1   | D0 |  |

| VFBLANK polarity                  | VFBLANK is high to disable the display                         | 0x01    | Х  | Х  | Х       | Х        | Х      | Х               | 0    | 0  |  |

| Intensity                         | 1/16 (min on)                                                  | 0x02    | Χ  | Χ  | Χ       | Χ        | 0      | 0               | 0    | 0  |  |

| Grids                             | Display has 1 grid                                             | 0x03    | Χ  | Χ  | 0       | 0        | 0      | 0               | 0    | 0  |  |

| Configuration                     | Shutdown enabled, configuration unlocked                       | 0x04    | 1  | 0  | 0       | 0        | 0      | 0               | 0    | 0  |  |

| User-defined font address pointer | Address 0x80; pointing to the first user-defined font location | 0x05    | 1  | 0  | 0       | 0        | 0      | 0               | 0    | 0  |  |

| User-defined fonts                | Predefined for hex fonts                                       | _       |    | Se | e Table | 11 for p | ower-u | p patter        | rns. |    |  |

| Output map pointer                | Address 0x80; pointing to first entry address                  | 0x06    | 1  | 0  | 0       | 0        | 0      | 0               | 0    | 0  |  |

| Output map data                   | Predefined for 40-digit display                                | _       |    | Se | e Table | 32 for p | ower-u | er-up patterns. |      |    |  |

| Display test                      | Normal operation                                               | 0x07    | Χ  | Χ  | Χ       | Χ        | Χ      | Χ               | Χ    | 0  |  |

| PUMP                              | General-purpose output, logic                                  | 0x08    | 0  | 0  | 0       | 0        | 0      | 0               | 0    | 0  |  |

| Filament duty cycle               | Minimum duty cycle                                             | 0x09    | 0  | 0  | 0       | 0        | 0      | 0               | 0    | 1  |  |

| PHASE1                            | General-purpose output, logic                                  | 0x0A    | 0  | 0  | 0       | 0        | 0      | 0               | 0    | 0  |  |

| PHASE2                            | General-purpose output, logic                                  | 0x0B    | 0  | 0  | 0       | 0        | 0      | 0               | 0    | 0  |  |

| PORT0                             | General-purpose output, logic                                  | 0x0C    | 0  | 0  | 0       | 0        | 0      | 0               | 0    | 0  |  |

| PORT1                             | General-purpose output, logic                                  | 0x0D    | 0  | 0  | 0       | 0        | 0      | 0               | 0    | 1  |  |

| Shift limit                       | 1 output bit                                                   | 0x0E    | Χ  | 0  | 0       | 0        | 0      | 0               | 0    | 1  |  |

| Cursor                            | Off                                                            | 0x0F    | 0  | 1  | 1       | 0        | 0      | 0               | 0    | 0  |  |

| Character and annunciator data    | Clear                                                          | 0×20    | 0  | 0  | 0       | 0        | 0      | 0               | 0    | 0  |  |

| UP TO                             | _                                                              | UP TO   | _  | _  | _       | _        | _      | _               | _    | _  |  |

| Character and annunciator data    | Clear                                                          | 0x7F    | 0  | 0  | 0       | 0        | 0      | 0               | 0    | 0  |  |

### **Character Generator Font Mapping**

The font comprises 104 characters in ROM, and 24 user-definable characters. The selection from the total of 128 characters is represented by the lower 7 bits of the 8-bit digit registers. The MSB, shown as X in the ROM maps (Tables 7 and 8), controls the DP segment of the digit; it is set to light the DP.

There are two font maps stored in the MAX6851. One font map covers 14-segment displays (Table 8), and the other suits 16-segment displays (Table 7). The F bit in the configuration register (Table 20) selects between the two font maps. The F bit may be set either high or low for 7-segment displays; 7-segment displays use a subset of the 14- or 16-segment display described in two font maps (Figure 7).

Figure 7. 14- and 16-Segment Fonts Map a Subset of Their 14 or 16 Segments to a 7-Segment Digit

Table 4. Character and Annunciator Register Address Map in 48/1 Mode

| DECICTED              |     | COMMAND ADDRESS |     |     |     |     |    |    |      |  |

|-----------------------|-----|-----------------|-----|-----|-----|-----|----|----|------|--|

| REGISTER              | D15 | D14             | D13 | D12 | D11 | D10 | D9 | D8 | CODE |  |

| Digit 0 character     | 0   | 0               | 1   | 0   | 0   | 0   | 0  | 0  | 0x20 |  |

| Digit 1 character     | 0   | 0               | 1   | 0   | 0   | 0   | 0  | 1  | 0x21 |  |

| Digit 2 character     | 0   | 0               | 1   | 0   | 0   | 0   | 1  | 0  | 0x22 |  |

| UP TO                 | _   | _               | _   | _   | _   | _   | _  | _  | _    |  |

| Digit 45 character    | 0   | 1               | 0   | 0   | 1   | 1   | 0  | 1  | 0x4D |  |

| Digit 46 character    | 0   | 1               | 0   | 0   | 1   | 1   | 1  | 0  | 0x4E |  |

| Digit 47 character    | 0   | 1               | 0   | 0   | 1   | 1   | 1  | 1  | 0x4F |  |

| Digit 0 annunciators  | 0   | 1               | 0   | 1   | 0   | 0   | 0  | 0  | 0x50 |  |

| Digit 1 annunciators  | 0   | 1               | 0   | 1   | 0   | 0   | 0  | 1  | 0x51 |  |

| Digit 2 annunciators  | 0   | 1               | 0   | 1   | 0   | 0   | 1  | 0  | 0x52 |  |

| UP TO                 | _   | _               | _   | _   | _   | _   | _  | _  | _    |  |

| Digit 45 annunciators | 0   | 1               | 1   | 1   | 1   | 1   | 0  | 1  | 0x7D |  |

| Digit 46 annunciators | 0   | 1               | 1   | 1   | 1   | 1   | 1  | 0  | 0x7E |  |

| Digit 47 annunciators | 0   | 1               | 1   | 1   | 1   | 1   | 1  | 1  | 0x7F |  |

Table 5. Character Register Address Map in 96/2 Mode

| DECICTED                    |     |     | C   | OMMAND | ADDRES | SS  |    |    | HEX  |

|-----------------------------|-----|-----|-----|--------|--------|-----|----|----|------|

| REGISTER                    | D15 | D14 | D13 | D12    | D11    | D10 | D9 | D8 | CODE |

| Digit 0 character, 1st row  | 0   | 0   | 1   | 0      | 0      | 0   | 0  | 0  | 0x20 |

| Digit 1 character, 1st row  | 0   | 0   | 1   | 0      | 0      | 0   | 0  | 1  | 0x21 |

| Digit 2 character, 1st row  | 0   | 0   | 1   | 0      | 0      | 0   | 1  | 0  | 0x22 |

| UP TO                       | 0   | _   | _   | _      | _      | _   | _  | _  | _    |

| Digit 45 character, 1st row | 0   | 1   | 0   | 0      | 1      | 1   | 0  | 1  | 0x4D |

| Digit 46 character, 1st row | 0   | 1   | 0   | 0      | 1      | 1   | 1  | 0  | 0x4E |

| Digit 47 character, 1st row | 0   | 1   | 0   | 0      | 1      | 1   | 1  | 1  | 0x4F |

| Digit 0 character, 2nd row  | 0   | 1   | 0   | 1      | 0      | 0   | 0  | 0  | 0x50 |

| Digit 1 character, 2nd row  | 0   | 1   | 0   | 1      | 0      | 0   | 0  | 1  | 0x51 |

| Digit 2 character, 2nd row  | 0   | 1   | 0   | 1      | 0      | 0   | 1  | 0  | 0x52 |

| UP TO                       | 0   | _   | _   | _      | _      | _   | _  | _  | _    |

| Digit 45 character, 2nd row | 0   | 1   | 1   | 1      | 1      | 1   | 0  | 1  | 0x7D |

| Digit 46 character, 2nd row | 0   | 1   | 1   | 1      | 1      | 1   | 1  | 0  | 0x7E |

| Digit 47 character, 2nd row | 0   | 1   | 1   | 1      | 1      | 1   | 1  | 1  | 0x7F |

The character map follows the Arial font for 96 characters in the x0100000 through x1111111 range. The first 32 characters map the 24 user-definable positions (RAM00 to RAM23), plus eight extra common characters in ROM.

#### **User-Defined Fonts**

The 24 user-definable characters are represented by 48 entries of 7-bit data, two entries per character, and are stored in the MAX6851's internal RAM.

**Table 6. Character Registers Format**

| MODE                                                                     | COMMAND ADDRESS                                      |    | REGISTER DATA                               |    |    |    |     |    |    |  |

|--------------------------------------------------------------------------|------------------------------------------------------|----|---------------------------------------------|----|----|----|-----|----|----|--|

| MODE                                                                     | COMMAND ADDRESS                                      | D7 | D6                                          | D5 | D4 | D3 | D2  | D1 | D0 |  |

| Writing character data to use font map data with DP segment <b>unlit</b> | 0x20 to 0x4F (48/1 mode)<br>0x20 to 0x7F (96/2 mode) | 0  | Dia Doub Double of first all and the 107    |    |    |    | 107 |    |    |  |

| Writing character data to use font map data with DP segment <b>lit</b>   | 0x20 to 0x4F (48/1 mode)<br>0x20 to 0x7F (96/2 mode) | 1  | Bits D6 to D0 select font characters 0 to 1 |    |    |    | 127 |    |    |  |

The user-definable characters are preloaded on powerup with 24 fonts. These fonts are intended to be useful for 7-segment displays, and include the hexadecimal set for the first 16 characters, plus eight other useful segment combinations. Table 12 shows how the 14-segment and 16-segment fonts map to 7-segment displays.

The 48 user-definable font data entries are written and read through a single register, address 0x05. An autoincrementing font address pointer in the MAX6851 indirectly accesses the font data. The font address pointer can be written, setting one of 48 addresses between 0x00 and 0x2F, but cannot be read back. The font data is written to and read from the MAX6851 indirectly, using this font address pointer. Unused font locations can be used as general-purpose scratch RAM, bearing in mind that the font registers are only 7 bits wide, not 8.

Table 9 shows how to use the single user-defined font register 0x05 to set the font address pointer, write font data, and read font data. A read action always returns font data from the font address pointer position. A write action sets the 7-bit font address pointer if the MSB is set, or writes 7-bit font data to the font address pointer position if the MSB is clear.

The font address pointer autoincrements after a valid access to the user-definable font data. Autoincrementing allows the 48-font data entries to be written and read back very quickly because the font pointer address needs to be set only once. After the last data location 0x2F has been written, further font data entries are ignored until the font address pointer is reset. If the font address pointer is set to an out-of-range address by writing data in the 0xB0 to 0xFF range, then address 0x00 is set instead (Table 10).

Table 11 shows the user-definable font pointer addresses.

Table 12 shows bit/segment mapping for user-defined fonts when applied to 7-, 14-, or 16-segment digits.

Table 13 illustrates how to set the font address pointer to a value within the acceptable range. D7 is set (1) to denote that the user is writing the font address pointer. If the user attempts to set the font address to one of the out-of-range addresses by writing data in range 0xB0 to 0xFF, then address 0x00 is set instead.

The font address pointer autoincrements from address (the last user font location) to point to address 0x00 (the first user font location). Thus, the font address pointer autoincrements indefinitely through font RAM.

#### **Cursor Register**

The cursor register controls the behavior of the cursor segments (Table 14). The MAX6851 controls 48 cursors in 48/1 mode, and 96 cursors in 96/2 mode. The cursor register selects one digit's cursor to be lit either continuously or blinking. All the other digits' cursors are off.

The 7 least significant bits (LSBs) of the cursor register identify the cursor position. The MSB is clear for the cursor to be on continuously, and set for the cursor to be lit only during the first half of each blink period.

The valid cursor position address range is contiguous: 0 to 47 (0x00 to 0x2F) for the first row, and 48 to 95 (0x30 to 0x5F) for the 2nd row. If the cursor register is programmed with an out-of-range value of 96 to 127 (0x60 to 0x7F), then all cursors are off.

### **Annunciator Registers**

The annunciator registers are organized in bytes, with each segment of each grid being represented by 2 bits. Thus, the four annunciators segments allowed for each grid are represented by exactly 1 byte (Table 15). Annunciators are only available in 48/1 mode. The annunciator address map is shown in Table 4.

#### **Configuration Register**

The configuration register is used to enter and exit shutdown, lock the key VFD configuration settings, select the blink rate, globally clear the digit and annunciator data, reset the blink timing, and select between 48/1 and 96/2 display modes (Table 16).

Table 7. 16-Segment Display Font Map

| MSB<br>LSB | x000  | x001  | x010 | x011 | x100 | x101 | x110 | x111 |

|------------|-------|-------|------|------|------|------|------|------|

| 0000       | RAM00 | RAM10 |      |      |      |      |      |      |

| 0001       | RAM01 | RAM11 |      |      |      |      |      |      |

| 0010       | RAM02 | RAM12 |      |      |      |      |      |      |

| 0011       | RAM03 | RAM13 | 器    |      |      |      |      |      |

| 0100       | RAM04 | RAM14 |      |      |      |      |      |      |

| 0101       | RAM05 | RAM15 |      |      |      |      |      |      |

| 0110       | RAM06 | RAM16 |      |      |      |      |      |      |

| 0111       | RAM07 | RAM17 |      |      |      |      |      |      |

| 1000       | RAM08 |       |      |      |      |      |      |      |

| 1001       | RAM09 |       |      |      |      |      |      |      |

| 1010       | RAM0A |       | XX   |      |      |      |      |      |

| 1011       | RAM0B |       |      |      |      |      |      |      |

| 1100       | RAM0C |       |      |      |      |      |      |      |

| 1101       | RAMOD |       |      |      |      |      |      |      |

| 1110       | RAM0E |       |      |      |      |      |      |      |

| 1111       | RAM0F |       |      |      |      |      |      |      |

**Table 8. 14-Segment Display Font Map**

| LSB MSB | x000  | x001  | x010 | x011     | x100 | x101 | x110 | x111 |

|---------|-------|-------|------|----------|------|------|------|------|

| 0000    | RAM00 | RAM10 |      | <b>X</b> |      |      |      |      |

| 0001    | RAM01 | RAM11 |      |          |      |      |      |      |

| 0010    | RAM02 | RAM12 |      |          |      |      |      |      |

| 0011    | RAM03 | RAM13 | 罴    |          |      |      |      |      |

| 0100    | RAM04 | RAM14 |      |          |      |      |      |      |

| 0101    | RAM05 | RAM15 | 洲    |          |      |      |      |      |

| 0110    | RAM06 | RAM16 | 洲    |          |      | X    |      |      |

| 0111    | RAM07 | RAM17 |      |          |      | 洲    |      | 黑    |

| 1000    | RAM08 |       |      |          |      | X    |      | X    |

| 1001    | RAM09 | X     |      |          |      |      |      |      |

| 1010    | RAM0A |       | 米    |          |      |      |      |      |

| 1011    | RAM0B |       |      |          |      |      |      |      |

| 1100    | RAMOC |       |      |          |      |      |      |      |

| 1101    | RAMOD |       |      |          |      |      |      |      |

| 1110    | RAM0E | X     |      |          |      |      |      |      |

| 1111    | RAM0F | X     |      |          |      |      |      |      |

14 \_\_\_\_\_\_ **////XI///**

Table 9. Memory Mapping of User-Defined Font Register 0x05

| COMMAND<br>ADDRESS | REGISTER<br>DATA | READ OR<br>WRITE | FUNCTION                                                                                                                                                    |

|--------------------|------------------|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0x05               | 0x00-0x7F        | Read             | Read 7-bit user-definable font data entry from current font address. MSB of the register data is clear. Font address pointer is incremented after the read. |

| 0x05               | 0x00-0x7F        | Write            | Write 7-bit user-definable font data entry to current font address. Font address pointer is incremented after the write.                                    |

| 0x05               | 0x80-0xFF        | Write            | Write font address pointer with the register data.                                                                                                          |

### **Table 10. Font Pointer Address Behavior**

| FONT POINTER<br>ADDRESS | ACTION                                                                                                                                            |

|-------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------|

| 0x80 to 0xAE            | Valid range to set the font address pointer. Pointer autoincrements after a font data read or write, while pointer address remains in this range. |

| 0xAF                    | Last valid address. Further font data is ignored after a font data read or write to this pointer address.                                         |

| 0xB0 to 0xFF            | Invalid range to set the font address pointer. Pointer is set to 0x80.                                                                            |

### **Table 11. User-Definable Font Pointer Addresses**

| FONT         | POWER-UP      | POWER-UP    | COMMAND | REGISTER |    |    | RE | GIST | ER DA | TA |    |    |

|--------------|---------------|-------------|---------|----------|----|----|----|------|-------|----|----|----|

| CHARACTER    | DEFAULT (BIN) | CHARACTER   | ADDRESS | DATA     | D7 | D6 | D5 | D4   | D3    | D2 | D1 | D0 |

| RAM00 byte 0 | 111 1110      | 7-segment 0 | 0x05    | 0x80     | 1  | 0  | 0  | 0    | 0     | 0  | 0  | 0  |

| RAM00 byte 1 | 000 0000      | _           | 0x05    | 0x81     | 1  | 0  | 0  | 0    | 0     | 0  | 0  | 1  |

| RAM01 byte 0 | 011 0000      | 7-segment 1 | 0x05    | 0x82     | 1  | 0  | 0  | 0    | 0     | 0  | 1  | 0  |

| RAM01 byte 1 | 000 0000      | _           | 0x05    | 0x83     | 1  | 0  | 0  | 0    | 0     | 0  | 1  | 1  |

| RAM02 byte 0 | 110 1101      | 7-segment 2 | 0x05    | 0x84     | 1  | 0  | 0  | 0    | 0     | 1  | 0  | 0  |

| RAM02 byte 1 | 000 0000      | _           | 0x05    | 0x85     | 1  | 0  | 0  | 0    | 0     | 1  | 0  | 1  |

| RAM03 byte 0 | 111 1001      | 7-segment 3 | 0x05    | 0x86     | 1  | 0  | 0  | 0    | 0     | 1  | 1  | 0  |

| RAM03 byte 1 | 000 0000      | _           | 0x05    | 0x87     | 1  | 0  | 0  | 0    | 0     | 1  | 1  | 1  |

| RAM04 byte 0 | 011 0011      | 7-segment 4 | 0x05    | 0x88     | 1  | 0  | 0  | 0    | 1     | 0  | 0  | 0  |

| RAM04 byte 1 | 000 0000      | _           | 0x05    | 0x89     | 1  | 0  | 0  | 0    | 1     | 0  | 0  | 1  |

| RAM05 byte 0 | 101 1011      | 7-segment 5 | 0x05    | A8x0     | 1  | 0  | 0  | 0    | 1     | 0  | 1  | 0  |

| RAM05 byte 1 | 000 0000      | _           | 0x05    | 0x8B     | 1  | 0  | 0  | 0    | 1     | 0  | 1  | 1  |

| RAM06 byte 0 | 101 1111      | 7-segment 6 | 0x05    | 0x8C     | 1  | 0  | 0  | 0    | 1     | 1  | 0  | 0  |

| RAM06 byte 1 | 000 0000      | _           | 0x05    | 0x8D     | 1  | 0  | 0  | 0    | 1     | 1  | 0  | 1  |

| RAM07 byte 0 | 111 0000      | 7-segment 7 | 0x05    | 0x8E     | 1  | 0  | 0  | 0    | 1     | 1  | 1  | 0  |

| RAM07 byte 1 | 000 0000      | _           | 0x05    | 0x8F     | 1  | 0  | 0  | 0    | 1     | 1  | 1  | 1  |

| RAM08 byte 0 | 111 1111      | 7-segment 8 | 0x05    | 0x90     | 1  | 0  | 0  | 1    | 0     | 0  | 0  | 0  |

| RAM08 byte 1 | 000 0000      | _           | 0x05    | 0x91     | 1  | 0  | 0  | 1    | 0     | 0  | 0  | 1  |

| RAM09 byte 0 | 111 1011      | 7-segment 9 | 0x05    | 0x92     | 1  | 0  | 0  | 1    | 0     | 0  | 1  | 0  |

| RAM09 byte 1 | 000 0000      | _           | 0x05    | 0x93     | 1  | 0  | 0  | 1    | 0     | 0  | 1  | 1  |

| RAM10 byte 0 | 111 0111      | 7-segment A | 0x05    | 0x94     | 1  | 0  | 0  | 1    | 0     | 1  | 0  | 0  |

**Table 11. User-Definable Font Pointer Addresses (continued)**

| FONT         | POWER-UP      | POWER-UP    | COMMAND | REGISTER |    |    | RE | GISTI | ER DA | TA |    |    |

|--------------|---------------|-------------|---------|----------|----|----|----|-------|-------|----|----|----|

| CHARACTER    | DEFAULT (BIN) | CHARACTER   | ADDRESS | DATA     | D7 | D6 | D5 | D4    | D3    | D2 | D1 | D0 |

| RAM10 byte 1 | 000 0000      | _           | 0x05    | 0x95     | 1  | 0  | 0  | 1     | 0     | 1  | 0  | 1  |

| RAM11 byte 0 | 001 1111      | 7-segment B | 0x05    | 0x96     | 1  | 0  | 0  | 1     | 0     | 1  | 1  | 0  |

| RAM11 byte 1 | 000 0000      | _           | 0x05    | 0x97     | 1  | 0  | 0  | 1     | 0     | 1  | 1  | 1  |

| RAM12 byte 0 | 100 1110      | 7-segment C | 0x05    | 0x98     | 1  | 0  | 0  | 1     | 1     | 0  | 0  | 0  |

| RAM12 byte 1 | 000 0000      | _           | 0x05    | 0x99     | 1  | 0  | 0  | 1     | 1     | 0  | 0  | 1  |

| RAM13 byte 0 | 011 1101      | 7-segment D | 0x05    | 0x9A     | 1  | 0  | 0  | 1     | 1     | 0  | 1  | 0  |

| RAM13 byte 1 | 000 0000      | _           | 0x05    | 0x9B     | 1  | 0  | 0  | 1     | 1     | 0  | 1  | 1  |

| RAM14 byte 0 | 100 1111      | 7-segment E | 0x05    | 0x9C     | 1  | 0  | 0  | 1     | 1     | 1  | 0  | 0  |

| RAM14 byte 1 | 000 0000      | _           | 0x05    | 0x9D     | 1  | 0  | 0  | 1     | 1     | 1  | 0  | 1  |

| RAM15 byte 0 | 100 0111      | 7-segment F | 0x05    | 0x9E     | 1  | 0  | 0  | 1     | 1     | 1  | 1  | 0  |

| RAM15 byte 1 | 000 0000      | _           | 0x05    | 0x9F     | 1  | 0  | 0  | 1     | 1     | 1  | 1  | 1  |

| RAM16 byte 0 | 000 1101      | 7-segment c | 0x05    | 0xA0     | 1  | 0  | 1  | 0     | 0     | 0  | 0  | 0  |

| RAM16 byte 1 | 000 0000      | _           | 0x05    | 0xA1     | 1  | 0  | 1  | 0     | 0     | 0  | 0  | 1  |

| RAM17 byte 0 | 001 0101      | 7-segment n | 0x05    | 0xA2     | 1  | 0  | 1  | 0     | 0     | 0  | 1  | 0  |

| RAM17 byte 1 | 000 0000      | _           | 0x05    | 0xA3     | 1  | 0  | 1  | 0     | 0     | 0  | 1  | 1  |

| RAM18 byte 0 | 111 0110      | 7-segment N | 0x05    | 0xA4     | 1  | 0  | 1  | 0     | 0     | 1  | 0  | 0  |

| RAM18 byte 1 | 000 0000      | _           | 0x05    | 0xA5     | 1  | 0  | 1  | 0     | 0     | 1  | 0  | 1  |

| RAM19 byte 0 | 001 1101      | 7-segment o | 0x05    | 0xA6     | 1  | 0  | 1  | 0     | 0     | 1  | 1  | 0  |

| RAM19 byte 1 | 000 0000      | _           | 0x05    | 0xA7     | 1  | 0  | 1  | 0     | 0     | 1  | 1  | 1  |

| RAM20 byte 0 | 000 0101      | 7-segment r | 0x05    | 0xA8     | 1  | 0  | 1  | 0     | 1     | 0  | 0  | 0  |

| RAM20 byte 1 | 000 0000      | _           | 0x05    | 0xA9     | 1  | 0  | 1  | 0     | 1     | 0  | 0  | 1  |

| RAM21 byte 0 | 100 1111      | 7-segment t | 0x05    | 0xAA     | 1  | 0  | 1  | 0     | 1     | 0  | 1  | 0  |

| RAM21 byte 1 | 000 0000      | _           | 0x05    | 0xAB     | 1  | 0  | 1  | 0     | 1     | 0  | 1  | 1  |

| RAM22 byte 0 | 001 1100      | 7-segment u | 0x05    | 0xAC     | 1  | 0  | 1  | 0     | 1     | 1  | 0  | 0  |

| RAM22 byte 1 | 000 0000      | _           | 0x05    | 0xAD     | 1  | 0  | 1  | 0     | 1     | 1  | 0  | 1  |

| RAM23 byte 0 | 011 1011      | 7-segment y | 0x05    | 0xAE     | 1  | 0  | 1  | 0     | 1     | 1  | 1  | 0  |

| RAM23 byte 1 | 000 0000      | _           | 0x05    | 0xAF     | 1  | 0  | 1  | 0     | 1     | 1  | 1  | 1  |

#### Shutdown Mode (S Data Bit D0) Format

The S bit in the configuration register selects shutdown or normal operation (Table 17). The display driver can be programmed while in shutdown mode, and shutdown mode is overridden when in display test mode. For normal operation, set S bit to 1.

When the MAX6851 is in shutdown mode, the multiplex oscillator is halted at the end of the current 100µs multiplex period (OSC = 4MHz), and the VFBLANK output is used to disable the VFD tube driver. Data in the digit and other control registers remain unaltered.

If the PUMP output is configured as a square-wave clock, then the PUMP output is forced low for the dura-

tion of shutdown, and the square-wave clock restored when the MAX6851 comes out of shutdown.

If the PHASE1 output or PHASE2 output is configured as a filament driver, then that output is forced low for the duration of shutdown and the filament drive waveforms restored when the MAX6851 comes out of shutdown.

When the MAX6851 comes out of shutdown, the external VFD tube driver is presumed to contain invalid data. The VFBLANK output is used to disable the VFD tube driver for the first multiplex cycle after exiting shutdown, clearing any invalid data. The next multiplex cycle uses newly sent valid data.

**Table 12. User-Definable Character Mapping**

| BIT/SEGMENT  | MAPPING FOR | USER-DEFINAB | LE FONTS WHE | N APPLIED TO | 7-SEGMENT DIG | GITS      |           |

|--------------|-------------|--------------|--------------|--------------|---------------|-----------|-----------|

| FONT BYTE    | BIT 6       | BIT 5        | BIT 4        | BIT 3        | BIT 2         | BIT 1     | BIT 0     |

| RAMxx byte 0 | 7-seg a     | 7-seg b      | 7-seg c      | 7-seg d      | 7-seg e       | 7-seg f   | 7-seg g   |

| RAMxx byte 1 | No action   | No action    | No action    | No action    | No action     | No action | No action |

| BIT/SEGMENT  | MAPPING FOR | USER-DEFINAB | LE FONTS WHE | N APPLIED TO | 14-SEGMENT DI | GITS      |           |

| FONT BYTE    | BIT 6       | BIT 5        | BIT 4        | BIT 3        | BIT 2         | BIT 1     | BIT 0     |

| RAMxx byte 0 | 7-seg a     | 7-seg b      | 7-seg c      | 7-seg d      | 7-seg e       | 7-seg f   | 7-seg g1  |

| RAMxx byte 1 | 14-seg g2   | 14-seg h     | 14-seg i     | 14-seg j     | 14-seg k      | 14-seg I  | 14-seg m  |

| BIT/SEGMENT  | MAPPING FOR | USER-DEFINAB | LE FONTS WHE | N APPLIED TO | 16-SEGMENT DI | GITS      |           |

| FONT BYTE    | BIT 6       | BIT 5        | BIT 4        | BIT 3        | BIT 2         | BIT 1     | BIT 0     |

| RAMxx byte 0 | 7-seg a1    | 7-seg b      | 7-seg c      | 7-seg d2     | 7-seg e       | 7-seg f   | 7-seg g1  |

| RAMxx byte 1 | 14-seg g2   | 14-seg h     | 14-seg i     | 14-seg j     | 14-seg k      | 14-seg l  | 14-seg m  |

## **Table 13. Setting a Font Character to RAM**

| MODE                                                                                                                 | COMMAND |    |    | REGISTER DATA |                                    |    |    |              |    |  |

|----------------------------------------------------------------------------------------------------------------------|---------|----|----|---------------|------------------------------------|----|----|--------------|----|--|

| MODE                                                                                                                 | ADDRESS | D7 | D6 | D5            | D4                                 | D3 | D2 | D1 0 1 0 1 1 | D0 |  |

| Set font address to minimum (zero) with data 128 or 0x80. (Note that this address is set as power-up default.)       | 0x05    | 1  | 0  | 0             | 0                                  | 0  | 0  | 0            | 0  |  |

| Set font address to maximum (47 or 0x2F) with data 175 or 0xAF.                                                      | 0x05    | 1  | 0  | 1             | 0                                  | 1  | 1  | 1            | 1  |  |

| Set font address out of range (48 or 0x30) with data 176 or 0xB0 results in font address pointer being set to zero.  | 0x05    | 1  | 1  | 1             | 1                                  | 1  | 0  | 0            | 0  |  |

| UP TO                                                                                                                | 0x05    |    |    |               | UP                                 | то |    |              |    |  |

| Set font address out of range (127 or 0x7F) with data 255 or 0xFF results in font address pointer being set to zero. | 0x05    | 1  | 1  | 1             | 1                                  | 1  | 1  | 1            | 1  |  |

| Read font address.                                                                                                   | 0x05    | 0  | F  | ont ad        | nt address; has value 0x00 to 0xAF |    |    |              | =  |  |

## **Table 14. Cursor Register Format**

| MODE                                                                           | COMMAND |       | REGISTER DATA |    |      |        |        |    |    |

|--------------------------------------------------------------------------------|---------|-------|---------------|----|------|--------|--------|----|----|

| MODE                                                                           | ADDRESS | D7    | D6            | D5 | D4   | D3     | D2     | D1 | D0 |

| Cursor register.                                                               | 0x0F    | BLINK |               |    | CURS | OR POS | SITION |    |    |

| 1st row digit 0's cursor is lit continuously.                                  | 0x0F    | 0     | 0             | 0  | 0    | 0      | 0      | 0  | 0  |

| 1st row digit 0's cursor is lit only for the first half of each blink period.  | 0x0F    | 1     | 0             | 0  | 0    | 0      | 0      | 0  | 0  |

| UP TO                                                                          | 0x0F    |       |               |    | UP   | то     |        |    |    |

| 2nd row digit 47's cursor is lit continuously.                                 | 0x0F    | 0     | 1             | 0  | 1    | 1      | 1      | 1  | 1  |

| 2nd row digit 47's cursor is lit only for the first half of each blink period. | 0x0F    | 1     | 1             | 0  | 1    | 1      | 1      | 1  | 1  |

| No cursor is lit.                                                              | 0x0F    | Х     | 1             | 1  | Х    | Χ      | Χ      | Χ  | Χ  |

Table 15. Annunciator Registers Format

| ANNUNCIATOR BYTE                                                     |    |         |    | REGISTI       | R DATA | 1            |       |    |

|----------------------------------------------------------------------|----|---------|----|---------------|--------|--------------|-------|----|

| ANNUNCIATOR BYTE                                                     | D7 | D6      | D5 | D4            | D3     | D2           | D1    | D0 |

| BIT ALLOCATIONS                                                      |    | ICIATOR | 1  | ICIATOR<br>A3 |        | CIATOR<br>12 | ANNUN |    |

| Annunciator A1 is off.                                               | Х  | Х       | Χ  | Х             | Χ      | Х            | 0     | 0  |

| Annunciator A1 is lit only for the first half of each blink period.  | Х  | Х       | Х  | X             | Х      | Х            | 0     | 1  |

| Annunciator A1 is lit only for the second half of each blink period. | Х  | Х       | Х  | Х             | Х      | Х            | 1     | 0  |

| Annunciator A1 is lit continuously.                                  | Х  | Х       | Х  | Х             | Х      | Х            | 1     | 1  |

| Annunciator A2 is off.                                               | Х  | Х       | Х  | Х             | 0      | 0            | Х     | Х  |

| Annunciator A2 is lit only for the first half of each blink period.  | Х  | Х       | Х  | Х             | 0      | 1            | Х     | Х  |

| Annunciator A2 is lit only for the second half of each blink period. | Х  | Х       | Х  | Х             | 1      | 0            | Х     | Х  |

| Annunciator A2 is lit continuously.                                  | Х  | Х       | Х  | Х             | 1      | 1            | Х     | Х  |

| Annunciator A3 is off.                                               | Х  | Х       | 0  | 0             | Χ      | Χ            | Χ     | Х  |

| Annunciator A3 is lit only for the first half of each blink period.  | X  | Х       | 0  | 1             | Х      | Х            | X     | Х  |

| Annunciator A3 is lit only for the second half of each blink period. | Х  | Х       | 1  | 0             | Х      | Х            | Х     | Х  |

| Annunciator A3 is lit continuously.                                  | Х  | Х       | 1  | 1             | Х      | Х            | Х     | Х  |

| Annunciator A4 is off.                                               | 0  | 0       | Х  | Х             | Х      | Х            | Х     | Х  |

| Annunciator A4 is lit only for the first half of each blink period.  | 0  | 1       | Х  | Х             | Х      | Х            | Х     | Х  |

| Annunciator A4 is lit only for the second half of each blink period. | 1  | 0       | Х  | Х             | Х      | Х            | Х     | Х  |

| Annunciator A4 is lit continuously.                                  | 1  | 1       | Х  | Х             | Χ      | Х            | Х     | Х  |

### **Table 16. Configuration Register Format**

| MODE                   |    |    | RE | GISTE | R DA | TA |    |    |

|------------------------|----|----|----|-------|------|----|----|----|

| WIODE                  | D7 | D6 | D5 | D4    | D3   | D2 | D1 | D0 |

| Configuration register | Р  | М  | R  | Т     | F    | В  | L  | S  |

## Table 17. Shutdown Control (S Data Bit D0) Format

| MODE             |    | REGISTER DATA |    |    |    |    |    |    |  |  |  |  |

|------------------|----|---------------|----|----|----|----|----|----|--|--|--|--|

| MODE             | D7 | D6            | D5 | D4 | D3 | D2 | D1 | D0 |  |  |  |  |

| Shutdown         | Р  | М             | R  | Т  | F  | В  | L  | 0  |  |  |  |  |

| Normal operation | Р  | М             | R  | Т  | F  | В  | L  | 1  |  |  |  |  |

#### Configuration Lock (L Data Bit D1) Format

The configuration lock register is a safety feature to reduce the risk of the VFD configuration settings being inadvertently changed due to spurious writes if software fails. When set, the shift-limit register (0x0E), grids register (0x03), and output map data (0x06) can be read but cannot be written. The output map data pointer itself may be written in order to allow the output map data to be read back (Table 18).

#### Blink Rate Selection (B Data Bit D2) Format

The B bit in the configuration register selects the blink rate of the cursor and annunciator segments. This is the speed that the segments blink on and off when blinking is selected for these segments. The frequency of the multiplex clock OSC and the setting of the B bit (Table 19) determine the blink rate.

## Table 18. Configuration Lock (L Data Bit D1) Format

| MODE     |    |    | RE | GISTE         | R DA | ATA |   |   |  |  |

|----------|----|----|----|---------------|------|-----|---|---|--|--|

| WIODE    | D7 | D6 | D5 | 5 D4 D3 D2 D1 |      |     |   |   |  |  |

| Unlocked | Р  | М  | R  | Т             | F    | В   | 0 | S |  |  |

| Locked   | Р  | М  | R  | Т             | F    | В   | 1 | S |  |  |

#### Font Selection (F Data Bit D3) Format

The F bit (Table 20) selects the internal font map between 14-segment and 16-segment displays. If a 7segment display is used, the F bit can be either set or cleared.

#### Global Blink Timing Synchronization (T Data Bit D4) Format

Setting the T bit in multiple MAX6851s at the same time (or in quick succession) synchronizes the blink timing across all the devices (Table 21). The display multiplexing sequence is also reset, which can give rise to a one-time display flicker when the register is written.

**Global Clear Digit Data (R Data Bit D5) Format**When the R bit (Table 22) is set, the segment and annunciator data are cleared.

#### Display Mode (M Data Bit D6) Format

The M bit (Table 23) selects the display modes (Table 1). The display modes trade maximum allowable number of digits (mode 96/2) against the availability of annunciator segments (mode 48/1).

#### Blink Phase Readback (P Data Bit D7) Format

When the configuration register is read, the P bit reflects the blink phase at that time (Table 24).

### **Serial Interface** Serial Addressing

The MAX6851 operates as a slave that sends and receives data through an I<sup>2</sup>C-compatible 2-wire interface. The interface uses a serial data line (SDA) and a serial clock line (SCL) to achieve bidirectional communication between master(s) and slave(s). A master (typically a microcontroller) initiates all data transfers to and from the MAX6851, and generates the SCL clock that synchronizes the data transfer (Figure 8).

The MAX6851 SDA line operates as both an input and an open-drain output. A pullup resistor, typically 4.7k $\Omega$ , is required on the SDA. The MAX6851 SCL line operates only as an input. A pullup resistor, typically 4.7k $\Omega$ , is required on SCL if there are multiple masters on the 2-wire interface, or if the master in a single-master system has an open-drain SCL output.

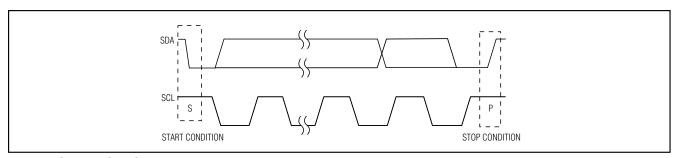

Each transmission consists of a START condition (Figure 9) sent by a master, followed by the MAX6851 7-bit slave address plus R/W bit (Figure 10), a register address byte, 1 or more data bytes, and finally a STOP condition (Figure 9).

#### Start and Stop Conditions

Both SCL and SDA remain high when the interface is not busy. A master signals the beginning of a transmission with a START (S) condition by transitioning SDA from high to low while SCL is high. When the master has finished communicating with the slave, it issues a STOP (P) condition by transitioning the SDA from low to high while SCL is high. The bus is then free for another transmission (Figure 9).

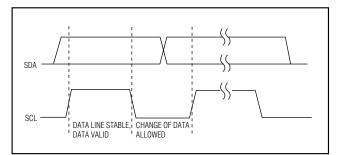

#### Bit Transfer

One data bit is transferred during each clock pulse. The data on the SDA line must remain stable while SCL is high (Figure 11).

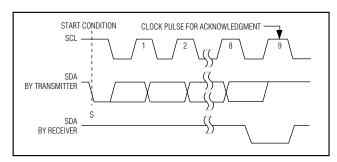

#### Acknowledge

The acknowledge bit is a clocked 9th bit that the recipient uses to handshake receipt of each byte of data (Figure 12). Thus, each byte transferred effectively requires 9 bits. The master generates the 9th clock pulse, and the recipient pulls down SDA during the acknowledge clock pulse, such that the SDA line is stable low during the high period of the clock pulse. When the master is transmitting to the MAX6851, the MAX6851 generates the acknowledge bit because the MAX6851 is the recipient. When the MAX6851 is transmitting to the master, the master generates the acknowledge bit because the master is the recipient. In this case, the master acknowledges all bytes received from the MAX6853 except for the last byte required, after which the master issues a STOP condition to signify end of transmission.

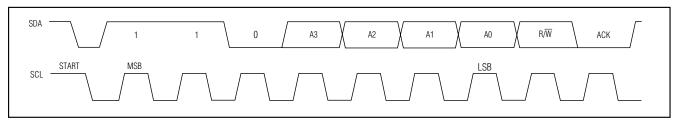

#### Slave Address

The MAX6851 has a 7-bit-long slave address (Figure 10). The eighth bit following the 7-bit slave address is the  $R/\overline{W}$  bit. Set it low for a write command, high for a read command.

The first 5 bits (MSBs) of the MAX6851 slave address are always 11101. Slave address bits A1 and A0 correspond to the state of the address input pin AD0. This input may be connected to GND, V+, SDA, or SCL. The MAX6851 has four possible slave addresses and therefore a maximum of four MAX6851 devices may share the same interface.

### Table 19. Blink Rate Selection (B Data Bit D2) Format

| MODE                                                                                    | REGISTER DATA |    |    |    |    |    |    |    |  |  |  |

|-----------------------------------------------------------------------------------------|---------------|----|----|----|----|----|----|----|--|--|--|

| MODE                                                                                    | D7            | D6 | D5 | D4 | D3 | D2 | D1 | D0 |  |  |  |

| Slow blinking (cursor and annunciators blink on for 1s, off for 1s, for OSC = 4MHz)     | Р             | М  | R  | Т  | F  | 0  | L  | S  |  |  |  |

| Fast blinking (cursor and annunciators blink on for 0.5s, off for 0.5s, for OSC = 4MHz) | Р             | М  | R  | Т  | F  | 1  | L  | S  |  |  |  |

## Table 20. Font Selection (F Data Bit D3) Format

| MODE                    |    | REGISTER DATA |    |    |    |    |    |    |  |  |  |  |

|-------------------------|----|---------------|----|----|----|----|----|----|--|--|--|--|

| MODE                    | D7 | D6            | D5 | D4 | D3 | D2 | D1 | D0 |  |  |  |  |

| 14- and 7-segment fonts | Р  | М             | R  | Т  | 0  | В  | L  | S  |  |  |  |  |

| 16- and 7-segment fonts | Р  | М             | R  | Т  | 1  | В  | L  | S  |  |  |  |  |

### Table 21. Global Blink Timing Synchronization (T Data Bit D4) Format

| MODE                                                                         | REGISTER DATA |    |    |    |    |    |    |    |  |  |  |

|------------------------------------------------------------------------------|---------------|----|----|----|----|----|----|----|--|--|--|

| WODE                                                                         | D7            | D6 | D5 | D4 | D3 | D2 | D1 | D0 |  |  |  |

| Blink timing counters are unaffected.                                        | Р             | М  | R  | 0  | F  | В  | L  | S  |  |  |  |

| Blink timing counters are cleared at the end of the present multiplex cycle. | Р             | М  | R  | 1  | F  | В  | L  | S  |  |  |  |

### Table 22. Global Clear Digit Data (R Data Bit D5) Format

| MODE                                                                                                           | REGISTER DATA |    |    |    |    |    |    |    |  |  |  |

|----------------------------------------------------------------------------------------------------------------|---------------|----|----|----|----|----|----|----|--|--|--|

| MODE                                                                                                           | D7            | D6 | D5 | D4 | D3 | D2 | D1 | D0 |  |  |  |

| Segment and annunciator data are unaffected.                                                                   | Р             | М  | 0  | Т  | F  | В  | L  | S  |  |  |  |

| Segment and annunciator data (address range 0x20 to 0x7F) are cleared during the I <sup>2</sup> C acknowledge. | Р             | М  | 1  | Т  | F  | В  | L  | S  |  |  |  |

### Table 23. Display Mode (M Data Bit D6) Format

| MODE | DISPLAY TYPE                       | REGISTER DATA |    |    |    |    |    |    |    |  |  |  |

|------|------------------------------------|---------------|----|----|----|----|----|----|----|--|--|--|

| MODE | DISPLAT TIPE                       | D7            | D6 | D5 | D4 | D3 | D2 | D1 | D0 |  |  |  |

| 48/1 | Up to 48 digits, 1 digit per grid  | Р             | 0  | R  | Т  | F  | В  | L  | S  |  |  |  |

| 96/2 | Up to 96 digits, 2 digits per grid | Р             | 1  | R  | Т  | F  | В  | L  | S  |  |  |  |

## Table 24. Blink Phase Readback (P Data Bit D7) Format

| MODE           |   |   | REGISTER DATA |    |    |    |    |    |  |  |  |  |  |  |

|----------------|---|---|---------------|----|----|----|----|----|--|--|--|--|--|--|

|                |   |   | D5            | D4 | D3 | D2 | D1 | D0 |  |  |  |  |  |  |

| P1 blink phase | 0 | М | R             | Т  | F  | В  | L  | S  |  |  |  |  |  |  |

| P0 blink phase | 1 | М | R             | Т  | F  | В  | L  | S  |  |  |  |  |  |  |

Figure 8. 2-Wire Serial Interface Timing Details

Figure 9. Start and Stop Conditions

Figure 10. Slave Address

Figure 11. Bit Transfer

Figure 12. Acknowledge

#### **Message Format for Writing**

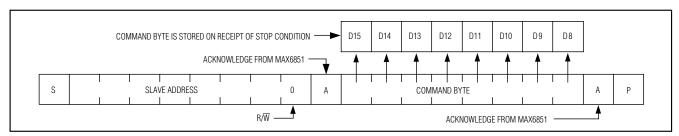

A write to the MAX6851 comprises the transmission of the MAX6851's slave address with the  $R/\overline{W}$  bit set to zero, followed by at least 1 byte of information. The first byte of information is the command byte, which determines which register of the MAX6851 is to be written by the next byte, if received. If a STOP condition is detected after the command byte is received, then the MAX6851 takes no further action (Figure 13) beyond storing the command byte.

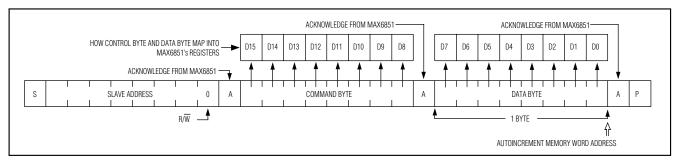

Any bytes received after the command byte are data bytes. The first data byte goes into the internal register of the MAX6851 selected by the command byte (Figure 14).

If multiple data bytes are transmitted before a STOP condition is detected, these bytes are generally stored in subsequent MAX6851 internal registers because the command byte address generally autoincrements (Table 26) (Figure 15).

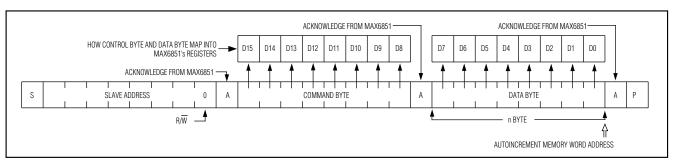

#### Message Format for Reading

The MAX6851 is read using the MAX6851's internally stored command byte as address pointer, the same way the stored command byte is used as address pointer for a write. The pointer generally autoincrements after each data byte is read using the same rules as for a write (Table 26). Thus, a read is initiated by first configuring the MAX6851's command byte by perform-

ing a write (Figure 13). The master can now read n consecutive bytes from the MAX6851, with the first data byte being read from the register addressed by the initialized command byte (Figure 15). When performing read-after-write verification, reset the command byte's address because the stored byte address generally is autoincremented after the write (Table 26).

### **Operation with Multiple Masters**