# 7846 16-Bit Digital to Analog Converter

#### **FEATURES:**

- Rad-Pak® technology-hardened against natural space radiation

- · Total dose hardness:

- > 100 krad (Si)

- Dependent upon orbit

- Excellent Single Event Effects

- SEL<sub>TH</sub> > 114 MeV/mg/cm<sup>2</sup>

- SEU < 8 MeV/mg/cm<sup>2</sup>

- · Package:

- -28 pin RAD-PAK Flat Pack

- Microprocessor compatible with readback capability

- · 16-Bit monotonicity over temperature

- ±2 LSBs integral linearity error

- Unipolar or bipolar output

- Multiplying capability

- Low power (100 mW typical)

### **DESCRIPTION:**

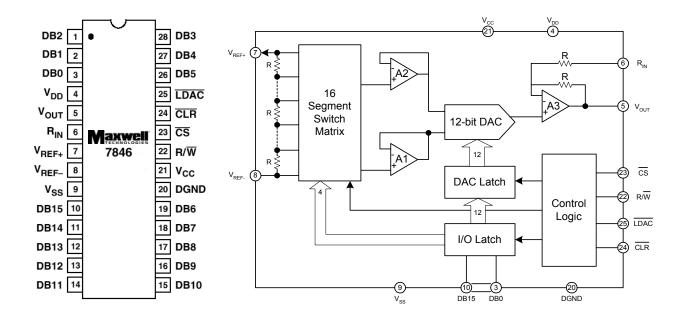

Maxwell Technologies' 7846 16-Bit DAC converter microcircuit features a greater than 100 krad (Si) total dose tolerance, dependent upon orbit. The 7846 has  $V_{RFF+}$  and  $V_{RFF-}$  reference inputs and an on-chip output amplifier which gives the option of unipolar or bipolar output. The 7846 uses a segmented architecture. The 4 MSBs in the DAC latch select one of the segments in a 16-resistor string. Both taps of the segment are buffered by amplifiers and fed to a 12-bit DAC, which provides a further 12 bits of resolution. This architecture ensures 16-bit monotonicity. Excellent integral linearity results from tight matching between the input offset voltages of the two buffer amplifiers. In addition to the excellent accuracy specifications, the 7846 also offers a comprehensive microprocessor interface. There are 16 data I/O pins, plus control lines (CS, R/W, LDAC and CLR). R/W and CS have readback function which allows writing to and reading from the I/O latch. Maxwell Technologies' patented RAD-PAK® packaging technology incorporates radiation shielding in the microcircuit package. It eliminates the need for box shielding while providing the required radiation shielding for a lifetime in orbit or space mission. In a GEO orbit, RAD-PAK provides greater than 100 krad (Si) radiation dose tolerance. This product is available with screening up to Class S.

TABLE 1. PINOUT DESCRIPTION

| Pin   | Symbol            | Description                                                                                                                                                                |

|-------|-------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1-3   | DB2-DB0           | Data I/O pins. DB0 is LSB.                                                                                                                                                 |

| 4     | $V_{DD}$          | Positive supply for analog circuitry. This is +15V nominal.                                                                                                                |

| 5     | V <sub>OUT</sub>  | DAC output voltage pin.                                                                                                                                                    |

| 6     | R <sub>IN</sub>   | Input to summing resistor of DAC output amplifier. This is used to select output voltage ranges.                                                                           |

| 7     | V <sub>REF+</sub> | $V_{REF+}$ Input. The DAC is speccified for $V_{REF+} = +5 \text{ V}$ .                                                                                                    |

| 8     | V <sub>REF-</sub> | $V_{\text{REF-}}$ Input. For unipolar operation connect $V_{\text{REF-}}$ to 0 V and for bipolar operation connect it to -5 V. The device is specified for both conditions |

| 9     | V <sub>SS</sub>   | Negative supply for the analog circuitry. This is -15 V nominal.                                                                                                           |

| 10-19 | SB15-DB6          | Data I/O pins. DB0 is MSB.                                                                                                                                                 |

| 20    | DGND              | Ground pin for digital circuitry.                                                                                                                                          |

| 21    | V <sub>CC</sub>   | Positive supply for digital circuitry. This is +5V nominal.                                                                                                                |

| 22    | R/W               | R/W input. This can be used to load data to the DAC or to read back the DAC latch contents.                                                                                |

| 23    | CS                | Chip select input. This selects the device.                                                                                                                                |

| 24    | CLR               | Clear Input. The DAC can be cleared to 000000 or 100000.                                                                                                                   |

| 25    | LDAC              | Asynchronous load input to DAC.                                                                                                                                            |

| 26-28 | DB5-DB3           | Data I/O pins.                                                                                                                                                             |

Table 2. 7846 PINOUT DESCRIPTION

| Pin   | Symbol            | Description                                                                                                                                                               |

|-------|-------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1-3   | DB2-DB0           | Data I/O pins. DB0 is LSB.                                                                                                                                                |

| 4     | V <sub>DD</sub>   | Positive supply for analog circuitry. This is +15V nominal.                                                                                                               |

| 5     | V <sub>OUT</sub>  | DAC output voltage pin.                                                                                                                                                   |

| 6     | R <sub>IN</sub>   | Input ot summing resistor of DAC output amplifier. This is used to select output voltage ranges.                                                                          |

| 7     | V <sub>REF+</sub> | $V_{REF+}$ Input. The DAC is specified for $V_{REF+}$ = +5V.                                                                                                              |

| 8     | V <sub>REF-</sub> | V <sub>REF-</sub> Input. For unipolar operation connect V <sub>REF-</sub> to 0V and for bipolar operation connect it to -5V. The device is specified for both conditions. |

| 9     | V <sub>SS</sub>   | Negative supply for the analog circuitry. This is -15V nominal.                                                                                                           |

| 10-19 | DB15-DB6          | Data I/O pins. DB15 is MSB.                                                                                                                                               |

| 20    | DGND              | Ground pin for digital circuitry.                                                                                                                                         |

TABLE 2. 7846 PINOUT DESCRIPTION

| Pin   | Symbol          | Description                                                                                 |

|-------|-----------------|---------------------------------------------------------------------------------------------|

| 21    | V <sub>CC</sub> | Positive supply for digital circuitry. This is +5V nominal.                                 |

| 22    | R/W             | R/W Input. This can be used to load data to the DAC or to read back the DAC latch contents. |

| 23    | CS              | Chip select input. This selects the device.                                                 |

| 24    | CLR             | Clear Input. The DAC can be cleared to 000000 or 100000.                                    |

| 25    | LDAC            | Asynchronous load input to DAC.                                                             |

| 26-28 | DB5-DB3         | Data I/O pins.                                                                              |

Table 3, 7846 Absolute Maximum Ratings 1

| PARAMETER                                                      | Min  | Max                                                  | Unit        |

|----------------------------------------------------------------|------|------------------------------------------------------|-------------|

| V <sub>DD</sub> to DGND                                        | -0.3 | +17                                                  | V           |

| V <sub>CC</sub> to DGND <sup>2</sup>                           | -0.3 | V <sub>DD</sub> +0.3 or 7<br>(Whichever Is<br>Lower) | V           |

| V <sub>SS</sub> to DGND                                        | -17  | +0.3                                                 | V           |

| V <sub>REF+</sub> to DGND                                      | -25  | +25                                                  | V           |

| V <sub>REF-</sub> to DGND                                      | -25  | +25                                                  | V           |

| V <sub>OUT</sub> to DGND <sup>3</sup>                          | -25  | +25                                                  | V           |

| R <sub>IN</sub> to DGND                                        | -25  | +25                                                  | V           |

| Digital Input Voltage to DGND                                  | -0.3 | V <sub>CC</sub> +0.3                                 | V           |

| Digital Output Voltage to DGND                                 | -0.3 | V <sub>CC</sub> +0.3                                 | V           |

| Power Dissipation (Any Package) To +75 °C Derates above +75 °C |      | 1000<br>10                                           | mW<br>mW/°C |

| Operating Temperature Range                                    | -55  | +125                                                 | °C          |

| Storage Temperature Range                                      | -65  | +150                                                 | °C          |

Stresses above those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress

rating only and functional operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods of time may

affect device reliability. Only one absolute maximum rating may be applied at any one time.

V<sub>CC</sub> must not exceed V<sub>DD</sub> by more than 0.3 V. If it is possible for this to happen during power supply sequencing, the following diode protection scheme will ensure protection.

<sup>3.</sup> V<sub>OUT</sub> may be shorted to DGND, V<sub>DD</sub>, V<sub>SS</sub> and V<sub>CC</sub> provided that the power dissipation of the package is not exceeded.

Table 4. 7846 Electrical Specifications  $^{1, 6}$  ( $V_{CC}$  = +5 V ±5%,  $T_A$  = -55 To +125°C)

|                                                                | (V <sub>CC</sub> - +5 V ±5%, I <sub>A</sub> 55 10 +125 C | /                                    |                      |

|----------------------------------------------------------------|----------------------------------------------------------|--------------------------------------|----------------------|

| Parameter                                                      | TEST CONDITIONS/COMMENTS                                 | T <sub>A</sub> =-55 °C то +125<br>°C | Unit                 |

| Resolution                                                     |                                                          | 16                                   | Bits                 |

| UNIPOLAR OUTPUT                                                | V <sub>REF-</sub> =0V, V <sub>OUT</sub> =0V to +10V      |                                      |                      |

| Relative Accuracy @ 25 °C                                      | 1LSB=153µV                                               | ±16                                  | LSB typ              |

| - T <sub>MIN</sub> to T <sub>MAX</sub>                         | 123Β=133μν                                               | ±16                                  | LSB typ              |

| Differential Nonlinearity Error                                | Guaranteed Monotonic                                     | ±10                                  | LSB max              |

| Gain Error @ 25 °C                                             | $V_{OUT}$ Load= $10M\Omega$                              | ±12                                  | LSB typ              |

| - T <sub>MIN</sub> to T <sub>MAX</sub>                         | VOUT LOUIS TOWING                                        | ±24                                  | LSB max              |

| Offset Error @ 25 °C                                           |                                                          | ±12                                  | LSB typ              |

| - T <sub>MIN</sub> to T <sub>MAX</sub>                         |                                                          | ±24                                  | LSB max              |

| Gain TC <sup>2</sup>                                           |                                                          | ±2                                   | ppm FSR/°C typ       |

| Offset TC <sup>2</sup>                                         |                                                          | ±2                                   | ppm FSR/°C typ       |

|                                                                | \\ - 5\\\\ - 40\\\                                       |                                      | pp 1 01 4 0 13p      |

| BIPOLAR OUTPUT                                                 | V <sub>REF</sub> =-5V, V <sub>OUT</sub> =-10V to +10V    | . C                                  | I CD 4               |

| Relative Accuracy @ 25 °C                                      | 1LSB=305μV                                               | ±6                                   | LSB typ              |

| - T <sub>MIN</sub> to T <sub>MAX</sub>                         | Cuaranteed Manatania                                     | ±8                                   | LSB max              |

| Differential Nonlinearity Error                                | Guaranteed Monotonic                                     | ±1                                   | LSB max              |

| Gain Error @ 25 °C                                             | ${ m V}_{ m OUT}$ Load=10M $\Omega$                      | ±6<br>±16                            | LSB typ<br>LSB max   |

| - T <sub>MIN</sub> to T <sub>MAX</sub>                         | V Lood=10MO                                              | ±16<br>±6                            |                      |

| Offset Error @ 25 °C                                           | ${ m V}_{ m OUT}$ Load=10M $\Omega$                      | ±0<br>±16                            | LSB typ<br>LSB max   |

| - T <sub>MIN</sub> to T <sub>MAX</sub>                         |                                                          | ±10<br>±6                            | LSB fliax<br>LSB typ |

| Bipolar Zero Error @ 25 °C                                     |                                                          | ±0<br>±16                            | LSB typ<br>LSB max   |

| - T <sub>MIN</sub> to T <sub>MAX</sub><br>Gain TC <sup>2</sup> |                                                          | ±10                                  | ppm FSR/°C typ       |

| Offset TC <sup>2</sup>                                         |                                                          | ±2<br>±2                             | ppm FSR/°C typ       |

| Bipolar Zero TC <sup>2</sup>                                   |                                                          | ±2                                   | ppm FSR/°C typ       |

| ·                                                              |                                                          | 12                                   | ррин он онур         |

| REFERENCE INPUT                                                | Desistance from V to V                                   | 00                                   | VOi                  |

| Input Resistance                                               | Resistance from V <sub>REF-</sub> to V <sub>REF+</sub>   | 20                                   | K $\Omega$ min       |

| V Danse                                                        | Typically 30k $\Omega$                                   | 40                                   | K $\Omega$ max       |

| V <sub>REF+</sub> Range                                        |                                                          | $V_{SS} + 6 \text{ to } V_{DD} - 6$  | V<br>V               |

| V <sub>REF-</sub> Range                                        |                                                          | $V_{SS}$ + 6 to $V_{DD}$ - 6         | V                    |

| OUTPUT CHARACTERISTICS                                         |                                                          |                                      |                      |

| Output Voltage Swing                                           |                                                          | $V_{SS}$ + 4 to $V_{DD}$ - 3         | V max                |

| Resistive Load <sup>1</sup>                                    | To 0V                                                    | 3                                    | k $\Omega$ min       |

| Capacitive Load <sup>3</sup>                                   | To 0V                                                    | 1000                                 | pF max               |

| Output Resistance                                              |                                                          | 0.3                                  | $\Omega$ typ         |

| Short Circuit Current                                          | To 0V or Any Power Supply                                | ±25                                  | mA typ               |

| DIGITAL INPUTS                                                 |                                                          |                                      |                      |

| V <sub>IH</sub> (Input High Voltage)                           |                                                          | 2.4                                  | V min                |

| V <sub>IL</sub> (Input Low Voltage)                            |                                                          | 0.8                                  | V max                |

| I <sub>IN</sub> (Input Current)                                |                                                          | ±10                                  | μA max               |

| C <sub>IN</sub> (Input Capacitance) <sup>2</sup>               |                                                          | 10                                   | pF max               |

| DIGITAL OUTPUTS                                                |                                                          |                                      |                      |

| V <sub>OL</sub> (Output Low Voltage)                           | I <sub>SINK</sub> = 1.6mA                                | 0.4                                  | V max                |

| V <sub>OH</sub> (Output High Voltage)                          | $I_{\text{SOURCE}} = 400 \mu A$                          | 4.0                                  | V min                |

| Floating State Leakage Current                                 | DB0-DB15 = 0 to V <sub>CC</sub>                          | ±10                                  | μA max               |

| Floating State Output Capacitance <sup>2</sup>                 |                                                          | 10                                   | pF max               |

| •                                                              |                                                          |                                      | ·                    |

09.26.01RevA

Table 4. 7846 Electrical Specifications 1, 6

$(V_{CC} = +5 \text{ V } \pm 5\%, T_A = -55 \text{ to } +125^{\circ}\text{C})$

| Parameter                                                                                                                                                                     | Test Conditions/Comments                                                      | T <sub>A</sub> =-55 °C то +125<br>°C                                   | Unit                                                                                           |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------|------------------------------------------------------------------------|------------------------------------------------------------------------------------------------|

| Resolution                                                                                                                                                                    |                                                                               | 16                                                                     | Bits                                                                                           |

| POWER REQUIREMENTS 4  V <sub>DD</sub> V <sub>SS</sub> V <sub>CC</sub> I <sub>DD</sub> I <sub>SS</sub> I <sub>CC</sub> Power Supply Sensitivity <sup>5</sup> Power Dissipation | $V_{\text{OUT}}$ Unloaded $V_{\text{OUT}}$ Unloaded $V_{\text{OUT}}$ Unloaded | +11.4/+15.75<br>-11.4/-15.75<br>+4.75/+5.25<br>5<br>5<br>1<br>2<br>100 | V min/V max<br>V min/V max<br>V min/V max<br>mA max<br>mA max<br>mA max<br>LSB/V max<br>mW typ |

- 1. Minimum load is  $3k\Omega$ .

- 2. Sample tested to ensure compliance.

- 3. Maximum load is 1000pF.

- 4. 7846RP is functional with power supplies of ±12V. See typical performance curves.

- 5. Sensitivity to Gain Error, Offset Error and Bipolar Zero Error to  $\rm V_{DD}, \rm V_{SS}$  variations.

- 6. Guaranteed by design

TABLE 5. DELTA LIMITS

| Parameter       | Variation |  |

|-----------------|-----------|--|

| I <sub>DD</sub> | ±10%      |  |

| I <sub>EE</sub> | ±10%      |  |

| I <sub>CC</sub> | ±10%      |  |

# Table 6. 7846 AC Performance Characteristics<sup>1</sup>

$(V_{CC} = +5 \text{ V } \pm 5\%, T_A = -55 \text{ to } +125^{\circ}\text{C})$

| Parameter                                     | TEST CONDITIONS                                                                               | T <sub>A</sub> =25°C | T <sub>A</sub> =T <sub>MIN</sub> TO T <sub>MAX</sub> | Unit         |

|-----------------------------------------------|-----------------------------------------------------------------------------------------------|----------------------|------------------------------------------------------|--------------|

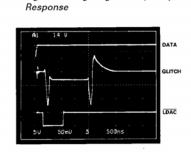

| Output Settling Time                          | To 0.006% FSR. V <sub>OUT</sub> loaded. V <sub>REF-</sub> =0V.                                | 7                    | 7                                                    | µs max       |

|                                               | To 0.003% FSR. $V_{OUT}$ loaded. $V_{REF}$ =-5V.                                              | 9                    | 9                                                    | µs max       |

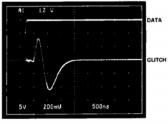

| Digital-to-Analog Glitch Impulse              | DAC alternately loaded with 100000 and 011111. V <sub>OUT</sub> unloaded.                     | 400                  | 400                                                  | nV-secs typ  |

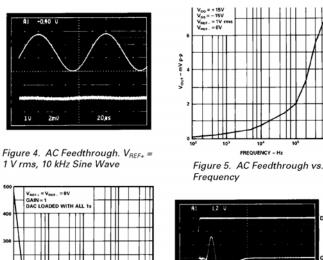

| AC Feed through                               | V <sub>REF-</sub> =0V, V <sub>REF+</sub> =1V rms, 10kHz sine wave.<br>DAC loaded with all 0s. | 0.5                  | 0.5                                                  | mV pk-pk typ |

| Digital Feed through                          | DAC alternately loaded with all 1s and all 0s. CS High.                                       | 10                   | 10                                                   | nV-secs typ  |

| Output Noise Voltage Density<br>(1kHz-100kHz) | Measured at $V_{OUT}$ . DAC loaded with 011101111. $V_{REF+} = V_{REF-} = 0V$ .               | 50                   | 50                                                   | nV/(Hz)½ typ |

1. Guaranteed by design.

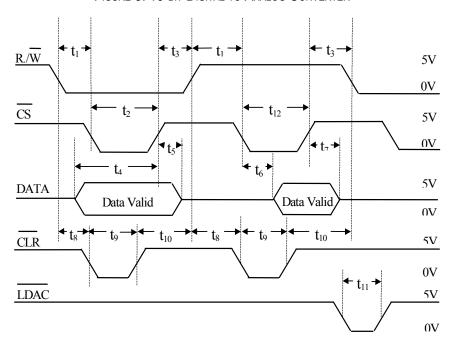

Table 7. 7846 Timing Characteristics  $^{1,2,3,4}$  (V<sub>DD</sub> = +14.25V to 15.75V; V<sub>SS</sub> = -14.25V to -15.75V; V<sub>CC</sub> = 4.75 to 5.25V; unless otherwise specified)

| PARAMETER       | Test Conditions/Comments     | L <sub>I</sub> MIT Aт<br>Т <sub>A</sub> =-55 °С то +125 °С | Unit   |

|-----------------|------------------------------|------------------------------------------------------------|--------|

| t <sub>1</sub>  | R/W to CS Setup Time         | 50                                                         | ns min |

| t <sub>2</sub>  | CS Pulse Width (Write Cycle) | 190                                                        | ns min |

| t <sub>3</sub>  | R/W to CS Hold Time          | 50                                                         | ns min |

| t <sub>4</sub>  | Data Setup Time              | 120                                                        | ns min |

| t <sub>5</sub>  | Data Hold Time               | 0                                                          | ns min |

| t <sub>6</sub>  | Data Access Time             | 320                                                        | ns max |

| t <sub>7</sub>  | Bus Relinquish Time          | 10                                                         | ns min |

|                 |                              | 90                                                         | ns max |

| t <sub>8</sub>  | CLR Setup Time               | 20                                                         | ns min |

| t <sub>9</sub>  | CLR Pulse Width              | 150                                                        | ns min |

| t <sub>10</sub> | CLR Hold Time                | 0                                                          | ns min |

| t <sub>11</sub> | LDAC Pulse Width             | 100                                                        | ns min |

| t <sub>12</sub> | CS Pulse Width (Read Cycle)  | 330                                                        | ns min |

<sup>1.</sup> Guaranteed by design. All input control signals are specified with  $t_R = t_F = 5$ ns (10% to 90% of +5V) and timed from a voltage level of 1.6V.

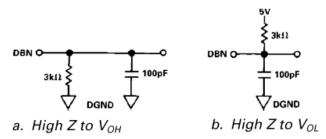

<sup>2.</sup> t<sub>6</sub> is measured with the load circuits of Figure 1 and defined as the time required for an output to cross 0.8V or 2.4V.

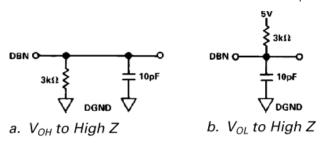

<sup>3.</sup> t<sub>7</sub> is defined as the time required for an output to change 0.5V when loaded with the circuits of Figure 2. Specifications subject to change without notice.

<sup>4.</sup> See Figure 3 on page 7.

FIGURE 1. LOAD CIRCUITS FOR ACCESS TIME  $(t_6)$

FIGURE 2. LOAD CIRCUITS FOR BUS RELINQUISH TIME  $(t_7)$

FIGURE 3. 16-BIT DIGITAL TO ANALOG CONVERTER

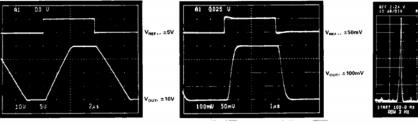

Figure 6. Large Signal Frequency

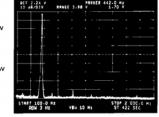

Figure 7. Noise Spectral Density

Figure 7. Noise Spectral Density

Figure 8. Digital-to-Analog Glitch

Impulse without Internal Deglitcher

(10 . . . 000 to 011 . . . 111 Transition)

Figure 9. Digital-to-Analog Glitch Impulse with Internal Deglitcher (10...000 to 011...111 Transition)

Figure 10. Pulse Response (Large Signal)

Figure 11. Pulse Response (Small Signal)

Figure 12. Spectral Response of Digitally Constructed Sine Wave

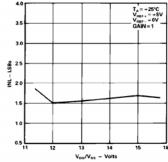

Figure 13. Typical Linearity vs.  $V_{DD}/V_{SS}$

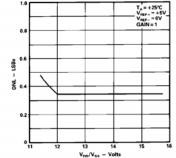

Figure 14. Typical Monotonicity vs. V<sub>DD</sub>/V<sub>SS</sub>

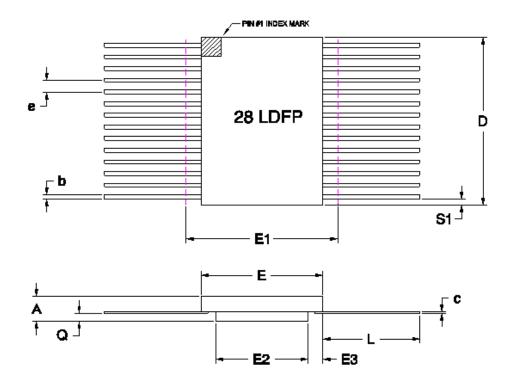

28 PIN RAD-PAK® FLAT PACKAGE

| Symbol | DIMENSION |           |       |

|--------|-----------|-----------|-------|

|        | Мім       | Nом       | Max   |

| A      | 0.190     | 0.207     | 0.224 |

| b      | 0.015     | 0.017     | 0.022 |

| С      | 0.004     | 0.005     | 0.009 |

| D      |           | 0.720     | 0.740 |

| E      | 0.380     | 0.410     | 0.420 |

| E1     |           |           | 0.440 |

| E2     | 0.180     | 0.250     |       |

| E3     | 0.030     | 0.080     |       |

| е      |           | 0.050 BSC |       |

| L      | 0.360     | 0.370     | 0.380 |

| Q      | 0.062     | 0.073     | 0.081 |

| S1     | 0.000     | 0.027     |       |

| N      |           | 28        |       |

F28-02 Note: All dimensions in inches

#### Important Notice:

These data sheets are created using the chip manufacturers published specifications. Maxwell Technologies verifies functionality by testing key parameters either by 100% testing, sample testing or characterization.

The specifications presented within these data sheets represent the latest and most accurate information available to date. However, these specifications are subject to change without notice and Maxwell Technologies assumes no responsibility for the use of this information.

Maxwell Technologies' products are not authorized for use as critical components in life support devices or systems without express written approval from Maxwell Technologies.

Any claim against Maxwell Technologies must be made within 90 days from the date of shipment from Maxwell Technologies. Maxwell Technologies' liability shall be limited to replacement of defective parts.

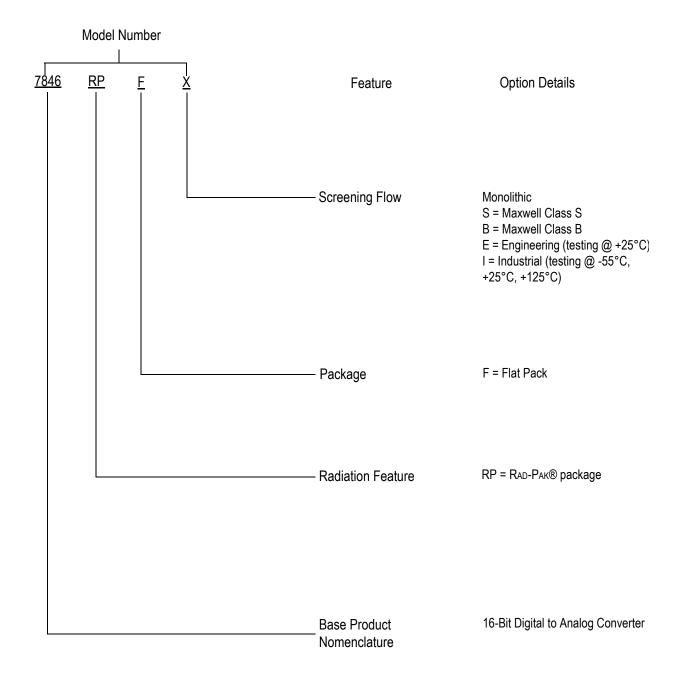

## **Product Ordering Options**