- Two 16-Bit Analog-to-Digital Converters (ADC)

- Two 16-Bit Digital-to-Analog Converters (DAC)

- Programmable Input/Output Gain

- Analog Crosspoint to Connect the Two Coder/Decoders (Codecs) to Any of the I/O Ports. Controlled Through the Serial Port or the I<sup>2</sup>C Bus

- 8-Bit A-Law/μ-Law Companded Data or 16-Bit Linear Data Complying With G.711 Standard

- Programmable ADC and DAC Conversion Rate

- Typical 77-dB Signal-to-Noise + Distortion for ADC

- Typical 78-dB Signal-to-Noise + Distortion for the DAC

- Typical 80-dB Dynamic Range

- All Typical Sampling Rates, Such as 7.2, 8, 8.229, 9.6, 10.285, 12, 14.4, and 16 kHz Supported

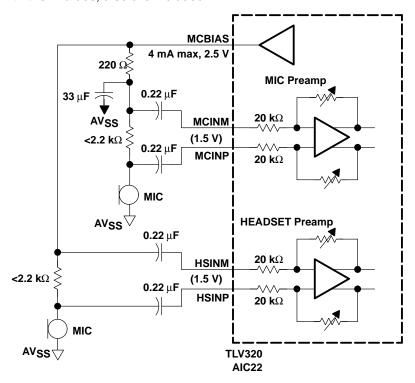

- Preamplifiers for Microphone, Handset, Headset, and Speaker Phone Gain Selectable Via the Serial Port or I<sup>2</sup>C Bus

- 2.5-V Microphone Bias Voltage

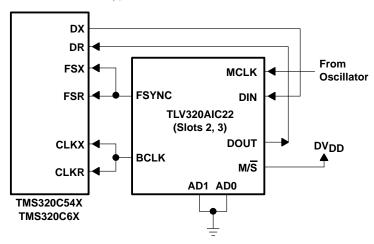

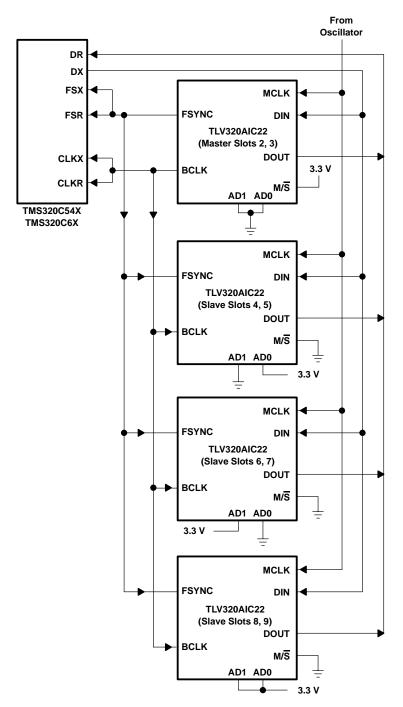

- Seamless Interface to a Single Multichannel Buffered Serial Port (McBSP) of a C54x or a C6x DSP

- Four TLV320AIC22 ICs Can Be Cascaded Together to Allow up to Eight Channels

- 2s-Complement Data Format

- Differential Outputs

- Typical Low Crosstalk < –85 dB (Interchannel)

- Hardware/Software Power Down

- Independent Power Down for Drivers

- Single 3.3-V Supply Operation

- 120-mW Typical Power Consumption

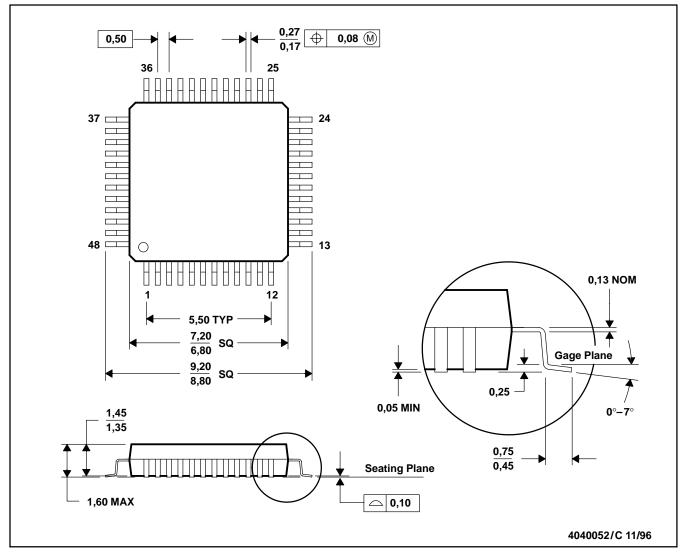

- Packaged in 48-Pin Low-Profile Quad Flatpack (LQFP) Package

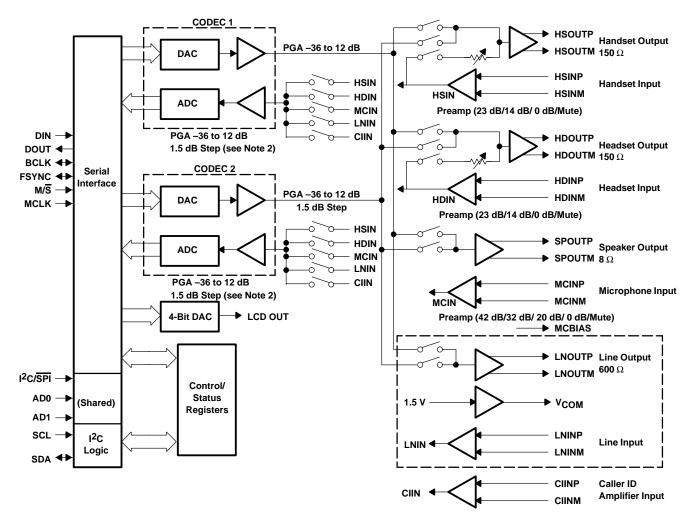

## description

The TLV320AIC22 is a dual coder/decoder (codec) for voice applications, including voice-over-internet protocol (VOIP). It features two ADC conversion channels and two DAC conversion channels that can be connected to a handset, headset, speaker, microphone, or a subscriber line via an analog crosspoint.

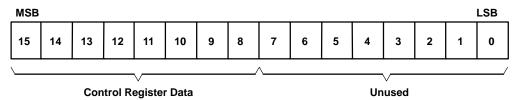

The TLV320AIC22 has a flexible serial interface that allows the two channels of the TLV320AIC22 to be interfaced to a single multichannel buffered serial port (McBSP) of the DSP. The two channels share the digital interface at different time slots. Up to four TLV320AIC22 units can be cascaded together to allow eight channels. For control purposes, either the serial interface or the I<sup>2</sup>C interface can be used. Programmable gain amplifiers, preamplifier gain, microphone bias voltages, and analog crosspoint are programmed through the serial interface or the I<sup>2</sup>C interface. The TLV320AIC22 can be powered down, via a dedicated pin or by using software control, to reduce power dissipation.

The TLV320AIC22 is available in a 48-pin LQFP package and is characterized for operation from -40°C to 85°C.

#### ORDERING INFORMATION

|               | PACKAGE                       |

|---------------|-------------------------------|

| TA            | PLASTIC QUAD FLATPACK<br>(PT) |

| -40°C to 85°C | TLV320AIC22PT                 |

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

NC - No internal connection

## functional block diagram

NOTES: 1. Input and output analog signals are differential. All switches are register controlled.

2. The attenuation on the ADC PGA (12 dB to –36 dB) is done after the ADC. This attenuation cannot prevent clipping. To prevent clipping, both the gain of the preamp and the PGA should be lowered to the required value.

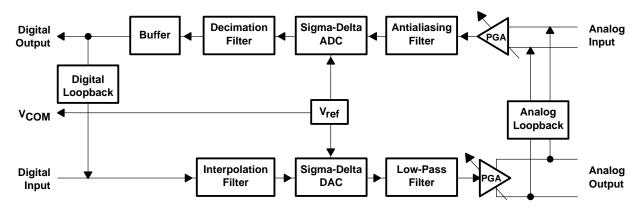

## functional block diagram (one of two codecs shown)

## **Terminal Functions**

| TERMI             | NAL    |     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|-------------------|--------|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NAME              | NO.    | 1/0 | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

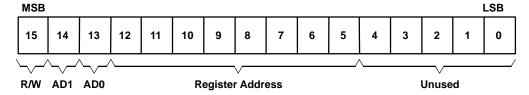

| AD1               | 12     | I   | In I <sup>2</sup> C mode, AD1 is used with AD0 to form the lower two bits of the 7-bit I <sup>2</sup> C chip address. The upper five bits are fixed at 11100. AD1 also is used in conjunction with AD0 to assign the two time slots for the codec in serial-port mode. AD1 is the MSB.                                                                                                                                                                              |

| AD0               | 13     | I   | In $I^2C$ mode, AD0 is used with AD1 to form the lower two bits of the 7-bit $I^2C$ chip address. The upper five bits are fixed at 11100. AD0 also is used in conjunction with AD1 to assign the two time slots for the codec in serial-port mode. AD0 is the LSB.                                                                                                                                                                                                  |

| AV <sub>DD1</sub> | 33     | I   | Analog power supply. Connect to AV <sub>DD2</sub> . See Note 3                                                                                                                                                                                                                                                                                                                                                                                                      |

| AV <sub>DD2</sub> | 5      | 1   | Analog power supply. Connect to AV <sub>DD1</sub> . See Note 3                                                                                                                                                                                                                                                                                                                                                                                                      |

| AV <sub>DD3</sub> | 27     | I   | Analog power supply for $8-\Omega$ speaker driver. This pin can be connected to $AV_{DD1}$ and $AV_{DD2}$ . Because this signal requires large amounts of current, it is recommended that a separate PCB trace be run to this pin and connected to the main supply at the power-supply connection to the PC board. See Note 3                                                                                                                                       |

| AVSS1             | 32     | I   | Analog ground. Connect to AV <sub>SS2</sub> . See Note 3                                                                                                                                                                                                                                                                                                                                                                                                            |

| AV <sub>SS2</sub> | 6      | I   | Analog ground. Connect to AV <sub>SS1</sub> . See Note 3                                                                                                                                                                                                                                                                                                                                                                                                            |

| AV <sub>SS3</sub> | 25, 29 | I   | Analog ground for $8-\Omega$ speaker driver. These pins can be connected to AVSS1 and AVSS2. Because this signal requires large amounts of current, it is recommended that a separate PCB trace be run to this pin and connected to the main supply at the power-supply connection to the PC board. See Note 3                                                                                                                                                      |

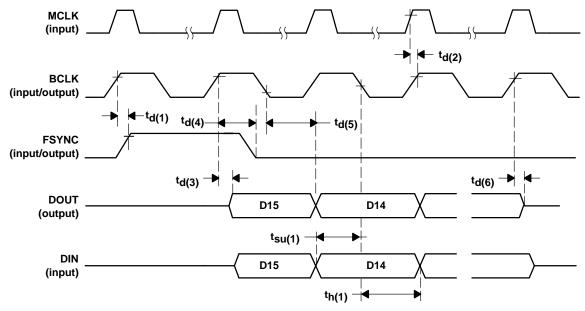

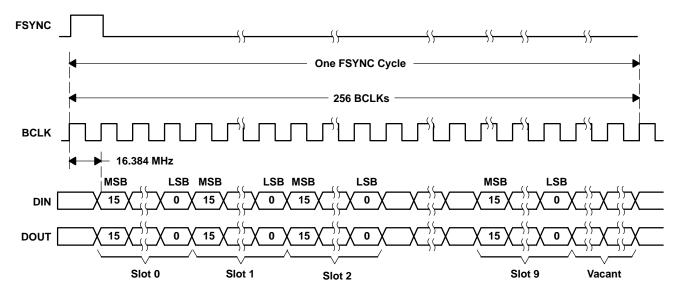

| BCLK              | 20     | I/O | Bit clock. BCLK clocks serial data into DIN and out of DOUT. When configured as an output (master mode), BCLK is generated internally by multiplying the frame-sync signal frequency by 256. When configured as an input (slave mode), BCLK is an input and must be synchronous with the master clock and frame sync.                                                                                                                                               |

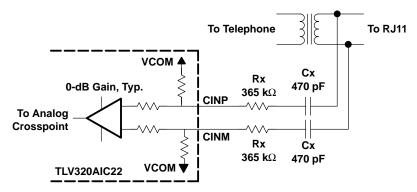

| CIINM             | 30     | I   | CallerID amplifier analog inverting input                                                                                                                                                                                                                                                                                                                                                                                                                           |

| CIINP             | 31     | I   | CallerID amplifier analog noninverting input                                                                                                                                                                                                                                                                                                                                                                                                                        |

| DIN               | 18     | I   | Data input. DIN receives the DAC input data and register data from the external digital signal processor (DSP) or controller and is synchronized to BCLK. Data is latched on the falling edge of BCLK in the two time slots that are specified by the AD1 and AD0 bits. Codec 1 receives data in the first assigned time slot, followed by codec 2 receiving data in the second assigned time slot.                                                                 |

| DOUT              | 17     | 0   | Data output. DOUT transmits the ADC output bits and the register data. It is synchronized to BCLK. Data is transmitted on the rising edge of BCLK in the two time slots that are specified by the AD1 and AD0 bits. DOUT is at high impedance during time slots not assigned to the codec. Codec 1 transmits data in the first assigned time slot, followed by codec 2 in the second assigned time slot.                                                            |

| $DV_{DD}$         | 15     | ı   | Digital power supply. See Note 3                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| DVSS              | 16     | ı   | Digital ground. See Note 3                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| FILT1             | 43     | 0   | Reference filter node. FILT1 and FILT2 provide decoupling of the reference voltage. This reference is 2.25 V. The optimal capacitor value is $0.1~\mu F$ (ceramic) and is connected between FILT1 and FILT2. FILT1 should not be used as a voltage source.                                                                                                                                                                                                          |

| FILT2             | 42     | 0   | Reference filter node. FILT1 and FILT2 provide decoupling of the reference voltage. This reference is 0 V. The optimal capacitor value is $0.1\mu\text{F}$ (ceramic) and is connected between FILT1 and FILT2.                                                                                                                                                                                                                                                      |

| FSYNC             | 19     | I/O | Frame sync. FSYNC indicates the beginning of a frame and the start of time slot 0. When FSYNC is sampled high on the rising edge of BCLK, the codec receives or transmits data in its specified time slot (specified by AD0 and AD1) in the frame. FSYNC is generated by the master device (output) and is an input to the slave devices. Codec 1 communicates in the first assigned time slot, followed by codec 2 communicating in the second assigned time slot. |

| HDINM             | 1      | I   | Headset amplifier analog inverting input. A connection between HDIN and HDOUT occurs, with selected echo gain, unless the echo gain is muted. See register 14                                                                                                                                                                                                                                                                                                       |

| HDINP             | 2      | I   | Headset amplifier analog noninverting input                                                                                                                                                                                                                                                                                                                                                                                                                         |

| HDOUTM            | 3      | 0   | Inverting headset output. The HDOUTM pin, together with the HDOUTP pin, forms the differential output. With HDOUTP, a 150- $\Omega$ load can be driven, differentially. HDOUTM also can be used alone for single-ended operation.                                                                                                                                                                                                                                   |

| HDOUTP            | 4      | 0   | Noninverting headset output. HDOUTP can be used alone for single-ended operation. With HDOUTM, a 150- $\Omega$ load can be driven, differentially.                                                                                                                                                                                                                                                                                                                  |

NOTE 3: This device has separate analog and digital power and ground pins. For best operation and results, the PC board design should utilize separate analog and digital power supplies as well as separate analog and digital ground planes. Mixed-signal design practices should be used.

## **Terminal Functions (Continued)**

| TERMINAL             |      |     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|----------------------|------|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NAME                 | NO.  | 1/0 | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| HSINM                | 40   | ı   | Handset amplifier analog inverting input. A connection between HSIN and HSOUT occurs, with selected echo gain, unless the echo gain is muted. See register 13.                                                                                                                                                                                                                                                                                                                  |

| HSINP                | 41   | I   | Handset amplifier analog noninverting input. A connection between the HSIN and HSOUT occurs, with programmed echo gain, unless the echo gain is muted. See register 13.                                                                                                                                                                                                                                                                                                         |

| HSOUTM               | 38   | 0   | Inverting handset output. The HSOUTM pin, together with the HSOUTP pin forms the differential output. With HSOUTP, a 150- $\Omega$ load can be driven differentially. HSOUTM also can be used alone for single-ended operation.                                                                                                                                                                                                                                                 |

| HSOUTP               | 39   | 0   | Noninverting handset output. With HSOUTM, a 150- $\Omega$ load can be driven, differentially. HSOUTP also can be used alone for single-ended operation.                                                                                                                                                                                                                                                                                                                         |

| I <sup>2</sup> C/SPI | 14   | I   | I <sup>2</sup> C/serial port interface select. Setting this pin high allows the user to program the registers using the I <sup>2</sup> C interface. A low state configures the serial interface to be used for control register programming during normal data transmission using time slots 0 and 1. When set high (I <sup>2</sup> C interface selected) time slots 0 and 1 in the normal data transmission are ignored.                                                       |

| LCDOUT               | 37   | 0   | 4-bit DAC output voltage, programmed through the control interface. This can be used to provide the bias voltage for an LCD display.                                                                                                                                                                                                                                                                                                                                            |

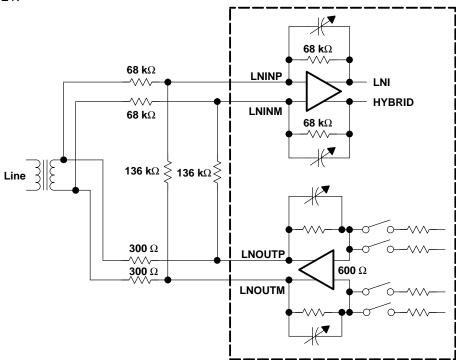

| LNINP                | 44   | I   | Line-port amplifier analog noninverting input. See Note 4.                                                                                                                                                                                                                                                                                                                                                                                                                      |

| LNINM                | 45   | I   | Line-port amplifier analog inverting input. See Note 4.                                                                                                                                                                                                                                                                                                                                                                                                                         |

| LNOUTM               | 46   | 0   | Inverting line-port output. The LNOUTM pin, together with the LNOUTP pin, forms the differential output. With LNOUTP, a $600-\Omega$ load can be driven differentially. LNOUTM also can be used alone for single-ended operation. See Note 4.                                                                                                                                                                                                                                   |

| LNOUTP               | 47   | 0   | Noninverting line-port output. With LNOUTM, a $600-\Omega$ load can be driven, differentially. LNOUTP also can be used alone for single-ended operation. See Note 4.                                                                                                                                                                                                                                                                                                            |

| MCLK                 | 22   | I   | Master clock input. All internal clocks are derived from this clock. This clock typically is 32.768 MHz or 24.576 MHz.                                                                                                                                                                                                                                                                                                                                                          |

| MCBIAS               | 36   | 0   | MCBIAS provides a bias voltage and current to operate Electret microphones. The bias voltage is specified across the microphone at 2.5 V.                                                                                                                                                                                                                                                                                                                                       |

| MCINM                | 34   | I   | Microphone amplifier analog inverting input                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| MCINP                | 35   | I   | Microphone amplifier analog noninverting input                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| M/S                  | 21   | ı   | Master/slave select input. When M/S is high, the device is the master, and when it is low, it is a slave.                                                                                                                                                                                                                                                                                                                                                                       |

| PWRDWN               | 9    | ı   | Power down. PWRDWN is active high. When PWRDWN is pulled high, the device goes into a power-down mode, and the output drivers and most of the high-speed clocks are disabled. The serial interface and I <sup>2</sup> C interface are enabled. However, all register values are sustained and the device resumes full-power operation without reinitialization when PWRDWN is pulled low again. PWRDWN resets the counters only and preserves the programmed register contents. |

| RESET                | 23   | I   | Codec device reset. RESET initializes all device internal registers to default values. This signal is active low.                                                                                                                                                                                                                                                                                                                                                               |

| SCL                  | 11   | ı   | SCL is the serial control interface clock for the I <sup>2</sup> C interface, and is used to clock control bits into and out of the device through the SDA pin. Tie this pin to DV <sub>DD</sub> when not used.                                                                                                                                                                                                                                                                 |

| SDA                  | 10   | I/O | Bidirectional control data I/O line for the $I^2C$ interface. Data is clocked into and out of the device by SCL. Tie this pin to $DV_{DD}$ when not used.                                                                                                                                                                                                                                                                                                                       |

| SPOUTP               | 26   | 0   | Inverting analog output from 8- $\Omega$ speaker amplifier                                                                                                                                                                                                                                                                                                                                                                                                                      |

| SPOUTM               | 28   | 0   | Noninverting analog output from 8-Ω speaker amplifier                                                                                                                                                                                                                                                                                                                                                                                                                           |

| NC                   | 7, 8 |     | Reserved. Leave unconnected.                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| VCOM                 | 48   | 0   | V <sub>COM</sub> provides a reference voltage of 1.5 V. The maximum source or sink current at this terminal is 2.5 mA.                                                                                                                                                                                                                                                                                                                                                          |

| VSS                  | 24   | I   | Internal substrate connection. VSS should be tied to AVSS1 and AVSS2. See Note 3.                                                                                                                                                                                                                                                                                                                                                                                               |

NOTES: 3. This device has separate analog and digital power and ground pins. For best operation and results, the PC board design should utilize separate analog and digital power supplies as well as separate analog and digital ground planes. Mixed-signal design practices should be used.

4. The LNINP and LNINM are sensitive to crosstalk from LNOUTP and LNOUTM. Keep the LNOUT and LNIN signals separated on the printed circuit board. Do not route the LNOUT signals parallel to the LNIN signals.

SLAS281B - JULY 2000 - REVISED JUNE 2002

## absolute maximum ratings over operating free-air temperature (unless otherwise noted)†

#### recommended operating conditions

|                                                                                                                            |                  | MIN | TYP | MAX                                   | UNIT     |

|----------------------------------------------------------------------------------------------------------------------------|------------------|-----|-----|---------------------------------------|----------|

| Supply voltage, AV <sub>DD1</sub> , AV <sub>DD2</sub> , AV <sub>DD3</sub> , DV <sub>DD</sub> (3.3-V supply)                |                  | 3   | 3.3 | 3.6                                   | V        |

| Analog signal peak-to-peak input voltage, $V_{\mbox{\scriptsize I(analog)}}$ differential (LNINP, LNINM, CIINP, CIINM)     | - Preamplifier   |     |     | 4                                     | ٧        |

| Analog signal peak-to-peak input voltage, V <sub>I(analog)</sub> , differential (HSINP, HSINM, HDINP, HDINM, MCINP, MCINM) | gain set to 0 dB |     |     | 4 (scaled by<br>the selected<br>gain) | <b>V</b> |

| High-level input voltage, any digital input, VIH                                                                           |                  | 2   |     |                                       | V        |

| Low-level input voltage, any digital input. V <sub>IL</sub>                                                                |                  |     |     | 0.8                                   | V        |

| Differential output load resistance, R <sub>L</sub> (LNOUTP, LNOUTM)                                                       |                  |     | 600 |                                       |          |

| Differential output load resistance, R <sub>L</sub> (SPOUTP, SPOUTM)                                                       |                  | 8   |     |                                       | Ω        |

| Differential output load resistance, R <sub>L</sub> (HDOUTP, HDOUTM)                                                       |                  | 150 |     |                                       | 22       |

| Differential output load resistance, R <sub>L</sub> (HSOUTP, HSOUTM)                                                       |                  | 150 |     |                                       |          |

| Input resistance connected externally to hybrid amps (LNINP, LNINM)                                                        |                  |     | 68  |                                       | kΩ       |

| Master clock input                                                                                                         |                  |     |     | 32.768                                | MHz      |

| Load capacitance, C <sub>L</sub> (unless otherwise specified)                                                              |                  |     |     | 20                                    | pF       |

| ADC or DAC conversion rate                                                                                                 | <u> </u>         | 7.2 |     | 16                                    | kHz      |

| Operating free-air temperature, TA                                                                                         |                  | -40 |     | 85                                    | °C       |

## electrical characteristics over recommended operating free-air temperature range, $DV_{DD} = 3.3 \text{ V}$ , $AV_{DD1} = AV_{DD2} = AV_{DD3} = 3.3 \text{ V}$ (unless otherwise noted)

#### digital inputs and outputs

|                   | PARAMETER                                                 | TEST CONDITIONS           | MIN | TYP | MAX | UNIT |

|-------------------|-----------------------------------------------------------|---------------------------|-----|-----|-----|------|

| Vон               | High-level output voltage, any digital output             | I <sub>OH</sub> = -360 μA | 2.4 |     |     | V    |

| VOL               | Low-level output voltage, any digital output              | $I_{OL} = 2 \text{ mA}$   |     |     | 0.4 | V    |

| ΊΗ                | High-level input current, any digital input               | V <sub>IH</sub> = 3.3 V   |     |     | 10  | μA   |

| I <sub>IL</sub>   | Low-level input current, any digital input                | V <sub>IL</sub> = 0.6 V   |     |     | 10  | μΑ   |

| Cl                | Input capacitance, any digital input                      |                           |     | 5   |     | pF   |

| Co                | Output capacitance, any digital output                    |                           |     | 10  |     | þΓ   |

| I <sub>lkg1</sub> | Input leakage current, any digital input (except for DIN) |                           |     |     | 10  | μΑ   |

| 1                 | Innut lookage current DIN                                 | V <sub>IH</sub> = 3.3 V   |     |     | 10  |      |

| llkg2             | Input leakage current, DIN                                | V <sub>IL</sub> = 0.6 V   |     |     | -60 | μΑ   |

| loz               | Output leakage current, any digital output                |                           |     |     | 10  | μΑ   |

<sup>†</sup> Stresses beyond those listed under "absolute maximum ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated under "recommended operating conditions" is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

## ADC channel transfer response characteristics over recommended ranges of supply voltage and operating free-air temperature, when selecting handset or headset as input

| PARAMETER                         | TEST CONDITIONS                                                                   |                      | MIN  | TYP | MAX   | UNIT |

|-----------------------------------|-----------------------------------------------------------------------------------|----------------------|------|-----|-------|------|

|                                   |                                                                                   | 0 Hz to 60 Hz        |      |     | -26   |      |

|                                   |                                                                                   | 200 Hz               | -1.8 |     | 0.35  |      |

|                                   |                                                                                   | 300 Hz to 3 kHz      | -0.3 |     | 0.3   |      |

|                                   | -17 dBr input signal, preamp gain = 14 dB, HSIN                                   | 3.3 kHz              | -0.4 |     | 0.2   | dB   |

|                                   | or HDIN selected, PGA gain = 0 dB (seen Note 5 and Note 6), Sampling rate = 8 kHz | 3.4 kHz              | -1   |     | -0.1  | uБ   |

|                                   | , , ,                                                                             | 4 kHz                |      |     | -12.5 |      |

|                                   |                                                                                   | 4.6 kHz to 8 kHz     |      |     | -60   |      |

|                                   |                                                                                   | Above 8 kHz          |      |     | -70   |      |

| Gain relative to gain at 1.02 kHz |                                                                                   | 0 Hz to 120 Hz       |      |     | -26   |      |

|                                   |                                                                                   | 400 Hz               | -1.8 |     | 0.35  |      |

|                                   |                                                                                   | 600 Hz to 6 kHz      | -0.3 |     | 0.3   |      |

|                                   | –24 dBr input signal, preamp gain = 14 dB, HSIN                                   | 6.6 kHz              | -0.4 |     | 0.2   |      |

|                                   | or HDIN selected, PGA gain = 0 dB (seen Note 5                                    | 6.8 kHz              | -1   |     | -0.1  | dB   |

|                                   | and Note 7), Sampling rate = 16 kHz                                               | 8 kHz                | -    |     | -12.5 |      |

|                                   |                                                                                   | 9.2 kHz to<br>16 kHz |      |     | -60   |      |

|                                   |                                                                                   | Above 16 kHz         |      |     | -56   |      |

- NOTES: 5. The filter gain outside of the passband is measured with respect to the gain at 1020 Hz. The analog input test signal is a sine wave with 0 dBr = 4 V<sub>I</sub>(PP) differential as the reference level for ADC analog input signal.

- 6. When the high-pass filter is bypassed, the passband is 0 Hz to 3 kHz. When the high-pass filter is inserted, the passband is 300 Hz to 3 kHz.

- 7. When the high-pass filter is bypassed, the passband is 0 Hz to 6 kHz. When the high-pass filter is inserted, the passband is 600 Hz to 6 kHz.

#### ADC channel passband frequency characteristics with microphone selected as input

| PARAMETER                                      | TEST CONDITIONS                                                                          |                 | MIN  | TYP MAX | UNIT |

|------------------------------------------------|------------------------------------------------------------------------------------------|-----------------|------|---------|------|

|                                                | –35 dBr input signal, preamp gain = 32 dB, MICIN selected. PGA gain = 0 dB (see Note 5), | 300 Hz to 3 kHz | -0.3 | 0.3     |      |

| Gain relative to gain at 1.02 kHz (see Note 6) |                                                                                          | 3.3 kHz         | -0.4 | 0.2     | dB   |

| (666 11616 6)                                  |                                                                                          | 3.4 kHz         | -1   | -0.1    |      |

|                                                | MICIN selected. PGA gain = 0 dB (see Note 5),                                            | 600 Hz to 6 kHz | -0.3 | 0.3     |      |

| Gain relative to gain at 1.02 kHz (see Note 7) |                                                                                          | 6.6 kHz         | -0.5 | 0.2     | dB   |

| (666 1.6.6 1)                                  |                                                                                          | 6.8 kHz         | -1.1 | -0.1    |      |

- NOTES: 5. The filter gain outside of the passband is measured with respect to the gain at 1020 Hz. The analog input test signal is a sine wave with 0 dBr = 4 V<sub>I(PP)</sub> differential as the reference level for ADC analog input signal.

- 6. When the high-pass filter is bypassed, the passband is 0 Hz to 3 kHz. When the high-pass filter is inserted, the passband is 300 Hz to 3 kHz

- 7. When the high-pass filter is bypassed, the passband is 0 Hz to 6 kHz. When the high-pass filter is inserted, the passband is 600 Hz to 6 kHz.

## ADC channel passband frequency characteristics with line input selected

| PARAMETER                                                                                      | TEST CONDITIONS                                                                                                           |                 | MIN      | TYP MAX | UNIT |

|------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------|-----------------|----------|---------|------|

|                                                                                                | -10 dBr input signal, LNIN selected,                                                                                      | 300 Hz to 3 kHz | -0.3     | 0.3     |      |

| ·                                                                                              | PGA gain = 0 dB (see Note 5)<br>Sampling rate = 8 kHz                                                                     | 3.3 kHz         | -0.4     | 0.2     | dB   |

| (occ reactor)                                                                                  | Pole select = 64, 32, 21.3, or 16 kHz                                                                                     | 3.4 kHz         | -0.3 0.3 |         |      |

|                                                                                                | -9 dBr input signal, LNIN selected, PGA gain = 0 dB (see Note 5) Sampling rate = 16 kHz Pole select = 64, 32, or 21.3 kHz | 600 Hz to 6 kHz | -0.7     | 0.3     |      |

|                                                                                                |                                                                                                                           | 6.6 kHz         | -0.9     | 0.2     | dB   |

| Gain relative to gain at 1.02 kHz (see Note 6)  Gain relative to gain at 1.02 kHz (see Note 7) |                                                                                                                           | 6.8 kHz         | -1.5     | -0.1    |      |

| (see Note 7)                                                                                   | -21 dBr input signal, LNIN selected,                                                                                      | 600 Hz to 6 kHz | -0.9     | 0.3     |      |

|                                                                                                | PGA gain = 0 dB (see Note 5) Sampling rate = 16 kHz                                                                       | 6.6 kHz         | -1.5     | 0.15    | dB   |

|                                                                                                | Pole select = 16 kHz                                                                                                      | 6.8 kHz         | -2.5     | C       | 1    |

- NOTES: 5. The filter gain outside of the passband is measured with respect to the gain at 1020 Hz. The analog input test signal is a sine wave with 0 dBr = 4 V<sub>I</sub>(PP) differential as the reference level for ADC analog input signal.

- 6. When the high-pass filter is bypassed, the passband is 0 Hz to 3 kHz. When the high-pass filter is inserted, the passband is 300 Hz to 3 kHz.

- 7. When the high-pass filter is bypassed, the passband is 0 kHz to 6 kHz. When the high-pass filter is inserted, the passband is 600 Hz to 6 kHz.

## ADC dynamic performance characteristics (see Note 5 and Note 8)

| PARAMETER                                              | TEST CONDITIONS                                                                                                 |       | MIN | TYP | MAX | UNIT |  |

|--------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------|-------|-----|-----|-----|------|--|

|                                                        |                                                                                                                 | THD   |     |     | -72 |      |  |

|                                                        | V <sub>I</sub> = −3 dBr, PGA gain = 0 dB, Sampling rate = 8 kHz                                                 | SNR   |     |     | -70 | dB   |  |

|                                                        |                                                                                                                 | THD+N |     |     | -68 |      |  |

|                                                        |                                                                                                                 | THD   |     |     | -72 |      |  |

| ADC dynamic performance with line input selected       | V <sub>I</sub> = −9 dBr, PGA gain = 0 dB, Sampling rate = 8 kHz                                                 | SNR   |     |     | -70 | dB   |  |

|                                                        |                                                                                                                 | THD+N |     |     | -68 |      |  |

|                                                        |                                                                                                                 | THD   |     |     | -45 |      |  |

|                                                        | $V_I = -40$ dBr, PGA Gain = 0 dB, Sampling rate = 8 kHz                                                         | SNR   |     |     | -40 | dB   |  |

|                                                        |                                                                                                                 | THD+N |     |     | -38 |      |  |

|                                                        | V <sub>I</sub> = -35 dBr, Preamp gain = 32 dB, PGA gain = 0 dB, Sampling rate = 16 kHz (-3 dBr at ADC input)    | THD   |     |     | -72 |      |  |

|                                                        |                                                                                                                 | SNR   |     |     | -70 | dB   |  |

|                                                        |                                                                                                                 | THD+N |     |     | -68 |      |  |

| l                                                      |                                                                                                                 | THD   |     |     | -70 |      |  |

| ADC dynamic performance with microphone input selected | V <sub>I</sub> = -41 dBr, Preamp gain = 32 dB, PGA gain = 0 dB,<br>Sampling rate = 16 kHz (-9 dBr at ADC input) | SNR   |     |     | -68 | dB   |  |

| morephone input selected                               | ouripling rate = 10 km2 ( o dbi at 7650 input)                                                                  | THD+N |     |     | -65 |      |  |

|                                                        |                                                                                                                 | THD   |     |     | -70 |      |  |

|                                                        | V <sub>I</sub> = -45 dBr, Preamp gain = 42 dB, PGA gain = 0 dB,<br>Sampling rate = 16 kHz (-3 dBr at ADC input) | SNR   |     |     | -62 | dB   |  |

|                                                        | Campung and - To the E ( Cabi at 7150 mpat)                                                                     | THD+N |     |     | -60 |      |  |

NOTES: 5. The filter gain outside of the passband is measured with respect to the gain at 1020 Hz. The analog input test signal is a sine wave with 0 dBr = 4 V<sub>I</sub>(pp) differential as the reference level for ADC analog input signal.

8. The test condition is a 1020-Hz input signal with an 8-kHz conversion rate. Input and output common mode is 1.5 V.

## ADC dynamic performance characteristics (see Note 5 and Note 8) (continued)

| PARAMETER                                                | TEST CONDITIONS                                                                         |       | MIN | TYP | MAX | UNIT |

|----------------------------------------------------------|-----------------------------------------------------------------------------------------|-------|-----|-----|-----|------|

|                                                          |                                                                                         | THD   |     |     | -68 |      |

|                                                          | V <sub>I</sub> = −9 dBr, PGA gain = 0 dB, Sampling rate = 8 kHz                         | SNR   |     |     | -66 | dB   |

| ADC dynamic performance with                             |                                                                                         | THD+N |     |     | -65 |      |

| caller ID input selected                                 |                                                                                         | THD   |     |     | -45 |      |

|                                                          | $V_I = -40$ dBr, PGA gain = 0 dB, Sampling rate = 8 kHz                                 | SNR   |     |     | -40 | dB   |

|                                                          |                                                                                         | THD+N |     |     | -38 |      |

|                                                          | V <sub>I</sub> = −3 dBr, PGA gain = 0 dB, Preamp gain = 0 dB<br>Sampling rate = 16 kHz  | THD   |     |     | -72 |      |

|                                                          |                                                                                         | SNR   |     |     | -70 | dB   |

|                                                          |                                                                                         | THD+N |     |     | -68 |      |

|                                                          |                                                                                         | THD   |     |     | -72 |      |

| ADC dynamic performance with handset or headset selected | V <sub>I</sub> = −9 dBr, PGA gain = 0 dB, Preamp gain = 0 dB<br>Sampling rate = 16 kHz  | SNR   |     |     | -70 | dB   |

| Transact of Treadset selected                            | Camping rate = 10 km2                                                                   | THD+N |     |     | -68 |      |

|                                                          |                                                                                         | THD   |     |     | -50 |      |

|                                                          | V <sub>I</sub> = -40 dBr, PGA gain = 0 dB, Preamp gain = 0 dB<br>Sampling rate = 16 kHz | SNR   |     |     | -42 | dB   |

|                                                          | Outripling 10.0 = 10 KHZ                                                                | THD+N |     |     | -40 |      |

NOTES: 5. The filter gain outside of the passband is measured with respect to the gain at 1020 Hz. The analog input test signal is a sine wave with 0 dBr = 4 V<sub>I</sub>(PP) differential as the reference level for ADC analog input signal.

8. The test condition is a 1020-Hz input signal with an 8-kHz conversion rate. Input and output common mode is 1.5 V.

#### **ADC** characteristics

|                     | PARAMETER                                       | TEST CONDITIONS                                                                                                                | MIN | TYP               | MAX | UNIT   |

|---------------------|-------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------|-----|-------------------|-----|--------|

| V <sub>I(PP)</sub>  | Peak-input voltage, differential                | Preamp gain = 0 dB                                                                                                             |     |                   | 4   | V      |

|                     | Dynamic range                                   |                                                                                                                                |     | 82                |     | dB     |

|                     | Intrachannel isolation (measured at ADC output) | HSIN is selected for ADC input.<br>Ground the input to the ADC;<br>full-scale input applied to DAC.                            | 85  |                   |     | dB     |

| E-                  | Gain error (valid for HSIN, HDIN, and MCIN)     | V <sub>I</sub> = −1 dB at 1020 kHz                                                                                             | -1  |                   | 1   | dB     |

| EG                  | Gain error (valid for LNIN)                     | V  = -1 UB at 1020 kHz                                                                                                         |     | ±2.5              |     | dB     |

| E <sub>O(ADC)</sub> | ADC channel offset error                        | HSIN selected for ADC input,<br>preamp gain = 14 dB, 0-V<br>differential input signal, inputs<br>are ac coupled                |     |                   | 50  | mV     |

| CMRR                | Common-mode rejection ratio                     | HSIN selected for ADC input,<br>preamp gain = 14 dB, 0-V<br>differential input signal, common<br>mode signal of -10 dB applied | 50  | 65                |     | dB     |

|                     | Idle channel noise                              | HSIN selected for ADC input,<br>preamp gain = 14 dB, 0-V<br>differential input signal, inputs<br>are ac coupled                |     | 30                | 75  | μV rms |

|                     | Channel delay (high-pass filter bypassed)       |                                                                                                                                | •   | 14/f <sub>S</sub> |     | S      |

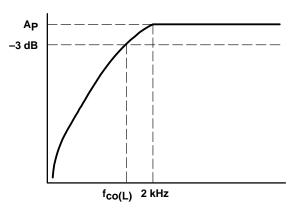

## callerID frequency response characteristics (see Figure 1)

|                    | PARAMETER                                 | TEST CONDITIONS                 | MIN | TYP | MAX | UNIT |

|--------------------|-------------------------------------------|---------------------------------|-----|-----|-----|------|

| f <sub>co(L)</sub> | Low-cutoff frequency                      | Connected as shown in Figure 23 |     | 570 |     | Hz   |

| Ap                 | Passband gain at 2 kHz                    |                                 |     | 1.5 |     | dB   |

|                    | Attenuation from input to IC pin at 60 Hz |                                 |     | -44 |     | dB   |

NOTE 9: All values are applicable when used with external components as shown in Figure 23.

Figure 1. CallerID Frequency Response

## **DAC** dynamic performance characteristics

| PARAMETER                                                                | TEST CONDITIONS                                                                   |       | MIN | TYP | MAX | UNIT |

|--------------------------------------------------------------------------|-----------------------------------------------------------------------------------|-------|-----|-----|-----|------|

|                                                                          |                                                                                   | THD   |     |     | -72 |      |

|                                                                          | V <sub>I</sub> = -3 dBr, PGA gain = 0 dB,<br>Sampling rate = 8 kHz, See Note 10   | SNR   |     |     | -70 | dB   |

|                                                                          | Camping rate = 5 km2, Gee Note 16                                                 | THD+N |     |     | -65 |      |

|                                                                          |                                                                                   | THD   |     |     | -63 |      |

| DAC dynamic performance with handset or headset drivers (HSOUT or HDOUT) | V <sub>I</sub> = -9 dBr, PGA gain = 0 dB,<br>Sampling rate = 8 kHz, See Note 10   | SNR   |     |     | -70 | dB   |

| neduser drivers (Fieder of Fieder)                                       | Camping rate = 5 km2, dec rete 15                                                 | THD+N |     |     | -60 |      |

|                                                                          |                                                                                   | THD   |     |     | -45 | dB   |

|                                                                          | V <sub>I</sub> = -40 dBr, PGA gain = 0 dB,<br>Sampling rate = 8 kHz, See Note 10  | SNR   |     |     | -40 |      |

|                                                                          |                                                                                   | THD+N |     |     | -38 |      |

|                                                                          |                                                                                   | THD   |     |     | -62 |      |

|                                                                          | V <sub>I</sub> = -3 dBr, PGA gain = 0 dB,<br>Sampling rate = 16 kHz, See Note 12  | SNR   |     |     | -75 | dB   |

|                                                                          | Camping rate = 10 kmz, eec Note 12                                                | THD+N |     |     | -60 |      |

| DAO da santa a seferma a santita O O deixas                              |                                                                                   | THD   |     |     | -60 |      |

| DAC dynamic performance with 8-Ω driver (SPOUT)                          | V <sub>I</sub> = -9 dBr, PGA gain = 0 dB,<br>Sampling rate = 16 kHz, See Note 12  | SNR   |     |     | -70 | dB   |

| (6. 55.)                                                                 | Campling rate = 10 kmz, occ Note 12                                               | THD+N |     |     | -55 |      |

|                                                                          | V 40 dBr B0A min 0 dB                                                             | THD   |     |     | -38 |      |

|                                                                          | V <sub>I</sub> = -40 dBr, PGA gain = 0 dB,<br>Sampling rate = 16 kHz, See Note 12 | SNR   |     |     | -35 | dB   |

|                                                                          |                                                                                   | THD+N |     |     | -32 |      |

NOTES: 10. The input signal is the digital equivalent of a sine wave (digital full scale = 0 dBr). A 0 dBr or full-scale digital input results in a 4-V(p-p) differential output.

<sup>12.</sup> The input signal is the digital equivalent of a sine wave (digital full scale = 0 dBr). A 0 dBr or full-scale digital input results in a 5-V<sub>(P-P)</sub> differential output.

## DAC dynamic performance characteristics (continued)

| PARAMETER                                       | TEST CONDITIONS                                                                   |       | MIN | TYP | MAX             | UNIT |

|-------------------------------------------------|-----------------------------------------------------------------------------------|-------|-----|-----|-----------------|------|

|                                                 |                                                                                   | THD   |     |     | -72             |      |

|                                                 | V <sub>I</sub> = -3 dBr, PGA gain = 0 dB,<br>Sampling rate = 16 kHz, See Note 10  | SNR   |     |     | -73             | dB   |

|                                                 | Campling rate = 10 km2, 000 Note 10                                               | THD+N |     |     | -70             |      |

| DAC dynamic performance with line-output driver | \\\ = _10 dBr PGA gain = 0 dB                                                     | THD   |     |     | -72             |      |

| (LNOUT), 16-kHz pole selected, 1000-Hz input    |                                                                                   | SNR   |     |     | -73             | dB   |

| signal                                          | Camping rate = 10 km2, eec rete 10                                                | THD+N |     |     | -70             |      |

|                                                 |                                                                                   | THD   |     |     | -50             | dB   |

|                                                 | Sampling rate = 16 kHz, See Note 10                                               | SNR   |     |     | -40             |      |

|                                                 |                                                                                   | THD+N |     |     | -38             |      |

|                                                 |                                                                                   | THD   |     |     | -72             |      |

|                                                 | V <sub>I</sub> = −3 dBr, PGA gain = 0 dB,<br>Sampling rate = 16 kHz, See Note 10  | SNR   |     |     | -73             | dB   |

|                                                 | Camping rate = 10 km2, eec rete 10                                                | THD+N |     |     | -70             |      |

| DAC dynamic performance with line-output driver |                                                                                   | THD   |     |     | -72             |      |

| (LNOUT), 64-kHz pole selected, 1000-Hz input    | V <sub>I</sub> = -10 dBr, PGA gain = 0 dB,<br>Sampling rate = 16 kHz, See Note 10 | SNR   |     |     | -73             | dB   |

| signal                                          | Camping rate = 10 km2, occ rector                                                 | THD+N |     |     | -70             |      |

|                                                 | V 40 dB                                                                           | THD   |     |     | <del>-</del> 50 | _    |

|                                                 | Sampling rate = 16 kHz, See Note 10                                               | SNR   |     |     | -40             | dB   |

|                                                 |                                                                                   | THD+N |     |     | -38             |      |

NOTES: 10. The input signal is the digital equivalent of a sine wave (digital full scale = 0 dBr). A 0 dBr or full-scale digital input results in a 4-V<sub>(P-P)</sub> differential output.

# DAC channel transfer response characteristics over recommended ranges of supply voltage and operating free-air temperature (see Note 10 and Note 11), with DAC connected to handset (HSOUT) or headset (HDOUT) drivers

| PARAMETER                         | TEST CONDITI                  | ONS                | MIN  | TYP MA       | UNIT |

|-----------------------------------|-------------------------------|--------------------|------|--------------|------|

|                                   |                               | 0 Hz to 3 kHz      | -0.3 | 0.           | 3    |

|                                   | Input signal at DIN is 0 dBr, | 3.3 kHz            | -0.5 | 0.           |      |

|                                   | PGA gain = 0 dB,              | 3.4 kHz            | -1   | -0.          | dB   |

|                                   | Sampling rate = 8 kHz         | 4 kHz              |      | <b>-12</b> . | 5    |

| Cain relative to gain at 1 02 kl  |                               | 4.6 kHz, and above |      | -4           | )    |

| Gain relative to gain at 1.02 kHz |                               | 0 Hz to 6 kHz      | -0.3 | 0.           | 3    |

|                                   | Input signal at DIN is 0 dBr, | 6.6 kHz            | -0.5 | 0.           |      |

|                                   | PGA gain = 0 dB,              | 6.8 kHz            | -1   | -0.          | dB   |

|                                   | Sampling rate = 16 kHz        | 8 kHz              |      | <b>–12</b> . | 5    |

|                                   |                               | 9.2 kHz, and above |      | -4           |      |

NOTES: 10. The input signal is the digital equivalent of a sine wave (digital full scale = 0 dBr). A 0 dBr or full-scale digital input results in a 4-V<sub>(P-P)</sub> differential output.

<sup>11.</sup> The filter gain is measured with respect to the gain at 1020 Hz.

SLAS281B - JULY 2000 - REVISED JUNE 2002

## DAC channel passband frequency characteristics with DAC connected to 8- $\Omega$ speaker driver (SPOUT) (see Note 11 and Note 12)

| PARAMETER                         | TEST CONDITIONS                                                          |               | MIN  | TYP MA | UNIT |

|-----------------------------------|--------------------------------------------------------------------------|---------------|------|--------|------|

|                                   |                                                                          | 0 Hz to 3 kHz | -0.2 | 0.     | 1    |

|                                   | Input signal at DIN is 0 dBr, PGA gain = 0 dB,<br>Sampling rate = 8 kHz  | 3.3 kHz       | -0.4 | 0.     | 2 dB |

| Coin relative to gain at 1 02 kHz |                                                                          | 3.4 kHz       | -1.5 | -0.    |      |

| Gain relative to gain at 1.02 kHz |                                                                          | 0 Hz to 6 kHz | -0.2 | 0.     | 1    |

|                                   | Input signal at DIN is 0 dBr, PGA gain = 0 dB,<br>Sampling rate = 16 kHz | 6.6 kHz       | -0.5 | 0.     | 2 dB |

|                                   | Camping rate = 10 tt 12                                                  | 6.8 kHz       | -1.5 | -0.    |      |

NOTES: 11. The filter gain is measured with respect to the gain at 1020 Hz.

## DAC channel passband frequency characteristics with DAC connected to line output driver (LNOUT) (see Note 10 and Note 11)

| PARAMETER                           | TEST CONDITIONS                                |               | MIN  | TYP MAX | UNIT |

|-------------------------------------|------------------------------------------------|---------------|------|---------|------|

|                                     |                                                | 0 Hz to 3 kHz | -0.2 | 0.4     |      |

|                                     | Input signal at DIN is 0 dBr, PGA gain = 0 dB, | 3.3 kHz       | -0.4 | 0.2     |      |

|                                     | Sampling rate = 8 kHz,                         | 3.4 kHz       | -1   | -0.1    | dB   |

|                                     | Pole select = 64, 32, 21.3, or 16 kHz          | 4 kHz         |      | -12.5   |      |

| Coin relative to goin at 1 02 kl la |                                                | Above 4.6 kHz |      | -40     |      |

| Gain relative to gain at 1.02 kHz   |                                                | 0 Hz to 6 kHz | -0.2 | 0.4     |      |

|                                     | Input signal at DIN is 0 dBr, PGA gain = 0 dB, | 6.6 kHz       | -0.4 | 0.2     |      |

|                                     | Sampling rate = 16 kHz,                        | 6.8 kHz       | -1   | -0.3    | dB   |

|                                     | Pole select = 64, 32, 21.3, or 16 kHz          | 8 kHz         |      | -12.5   |      |

|                                     |                                                | Above 9.2 kHz |      | -40     |      |

NOTES: 10. The input signal is the digital equivalent of a sine wave (digital full scale = 0 dBr). A 0 dBr or full-scale digital input results in a 4-V<sub>(P-P)</sub> differential output.

#### line output out-of-band performance characteristics

| PARAMETER               | TEST CONDITIONS                                                                     |                        | MIN | TYP | MAX | UNIT               |

|-------------------------|-------------------------------------------------------------------------------------|------------------------|-----|-----|-----|--------------------|

| Line output out-of-band |                                                                                     | Pole select = 64 kHz   |     | 32  |     |                    |

|                         | Noise measured in 1-kHz bandwidth from 4.6 kHz to 300 kHz; -10-dB input signal; PGA | Pole select = 32 kHz   |     | 20  |     | uV/√ <del>Hz</del> |

|                         | gain is 0 dB; output load = $600 \Omega$ .                                          | Pole select = 21.3 kHz |     | 14  |     | μν/νπΖ             |

|                         | -                                                                                   | Pole select = 16 kHz   |     | 11  |     |                    |

<sup>12.</sup> The input signal is the digital equivalent of a sine wave (digital full scale = 0 dBr). A 0 dBr or full-scale digital input results in a 5-V<sub>(P-P)</sub> differential output.

<sup>11.</sup> The filter gain is measured with respect to the gain at 1020 Hz.

#### **DAC** characteristics

|    | PARAMETER                                                   | TEST CONDITIONS                                                        | MIN | TYP               | MAX | UNIT    |

|----|-------------------------------------------------------------|------------------------------------------------------------------------|-----|-------------------|-----|---------|

|    | Dynamic range                                               |                                                                        |     | 82                |     | dB      |

|    | Intrachannel isolation (measured at SPOUT)                  | All zeros applied to DAC. Full-scale signal applied to ADC at HSIN.    | 85  |                   |     | dB      |

| EG | Gain error, 0 dB                                            | $V_{ } = -1 \text{ dB at } 1020 \text{ kHz}$                           | -1  |                   | 1   | dB      |

|    | Idle channel noise                                          | 0 kHz to 4 kHz, See Note 12                                            |     | 30                | 75  | μV rms  |

|    | Channel delay                                               |                                                                        |     | 13/f <sub>S</sub> |     | S       |

| Vo | Analog output voltage, (SPOUTP-SPOUTM)                      | Differential for full-scale digital input;<br>See Note 13 and Note 14. |     | ±2.5              |     | V(D, D) |

|    | Analog output voltage (handset/headset and line interfaces) | Differential for full-scale digital input;<br>See Note 13 and Note 14. |     | ±2                |     | V(P-P)  |

NOTES: 12. The conversion rate is 8 kHz.

- 13. This amplifier should be used only in differential mode.

- 14. Common mode: 1.5 V

## power-supply rejection characteristics (see Note 15)

|                    | PARAMETER                                                                              | TEST CONDITIONS              | MIN | TYP | MAX         | UNIT |

|--------------------|----------------------------------------------------------------------------------------|------------------------------|-----|-----|-------------|------|

| V <sub>DD(1)</sub> | Supply-voltage rejection ratio, ADC channel, AV <sub>DD1</sub> , and AV <sub>DD2</sub> | $f_I = 0 \text{ to } f_S/2$  |     |     | <b>-</b> 50 | dB   |

| V <sub>DD(2)</sub> | Supply-voltage rejection ratio, DAC channel, and DV <sub>DD</sub>                      | f <sub>I</sub> = 0 to 30 kHz |     |     | -50         | uБ   |

NOTE 15: Power-supply rejection measurements are made with both the ADC and the DAC channels idle and a 200-mV peak-to-peak signal applied to the appropriate supply.

## power-supply characteristics

|                             | PARAMETER                                                                  | TEST CONDITIONS          | MIN | TYP  | MAX  | UNIT |

|-----------------------------|----------------------------------------------------------------------------|--------------------------|-----|------|------|------|

| I <sub>DD(analog)</sub>     | Codec power-supply current, analog (including drivers); AVDD1, AVDD2       | Operating                |     | 30.8 | 61.5 |      |

| I <sub>DD</sub> (digital)   | Codec power-supply current, digital; DV <sub>DD</sub> .                    | Operating                |     | 5.5  |      | mA   |

| I <sub>DD</sub> (speaker)   | Power-supply current, $8-\Omega$ speaker driver; AV <sub>DD3</sub> .       | Operating                |     | 200  | 400  |      |

| I <sub>DD</sub> (quiescent) | 8- $\Omega$ driver dc current without swing at output; AV <sub>DD3</sub> . |                          |     | 1    |      |      |

| I <sub>DD(analog)</sub>     | Codec power-supply current, analog (hardware power down mode)              | PWRDWN pin = logic 1     |     | 100  |      | μΑ   |

| I <sub>DD</sub> (digital)   | Codec power-supply current, digital (hardware power down mode)             | PWRDWN pin = logic 1     |     | 2.2  | 4    | mA   |

| I <sub>DD</sub> (analog)    | Codec power-supply current, analog                                         | Analog master power down |     |      | 500  | μΑ   |

## speaker driver characteristics

|                    | PARAMETER                                               | TEST CONDITIONS                                                                                                    | MIN | TYP | MAX | UNIT               |

|--------------------|---------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------|-----|-----|-----|--------------------|

| V <sub>N(PP)</sub> | Output peak-to-peak voltage (between SPOUTP and SPOUTM) | AV <sub>DD3</sub> = 3.3 V, fully differential, $8-\Omega$ load, 0 dBr = full-scale digital input; PGA gain = 0 dB. |     | 5   |     | V <sub>(P-P)</sub> |

| Voo                | Output offset voltage                                   | Fully differential                                                                                                 |     | ±5  |     | mV                 |

| THD                | Total harmonic distortion                               | $AV_{DD3} = 3.3 \text{ V}, 80\text{-mW output}, 8-\Omega \text{ load}$                                             |     | -60 |     | dB                 |

|                    | Max output power (peak)                                 | $R_{I} = 8 \Omega$ , $AV_{DD3} = 3.3 V$                                                                            |     | 390 |     | mW                 |

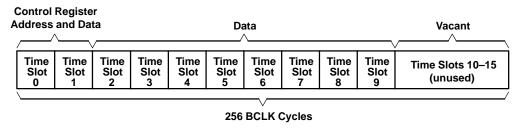

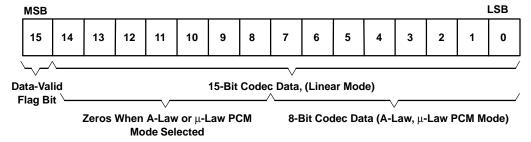

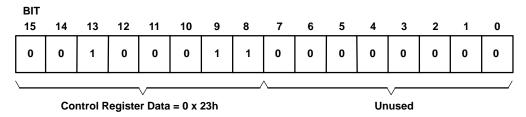

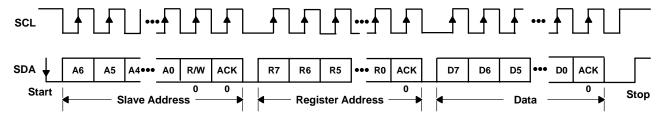

|                    | Mute                                                    |                                                                                                                    |     | -80 |     | dB                 |