# **TLE9255W**

# **HS CAN Transceiver with Partial Networking**

#### 1 Overview

#### **Features**

- Fully compliant to ISO 11898-2 (2016)

- HS CAN standard data rates up to 1MBit/s

- CAN FD data rates up to 5 MBit/s

- Wide common mode range for electromagnetic immunity (EMI)

- Very low electromagnetic emission (EME)

- Excellent ESD robustness, ± 10 kV according to IEC 61000-4-2

- Independent supply concept on  $V_{CC}$  and  $V_{BAT}$  pins

- Fail safe features

- TxD-timeout

- overtemperature shutdown

- overtemperature warning

- Extended supply range on  $V_{CC}$  and  $V_{IO}$  supply

- CAN short circuit proof to ground, battery and  $V_{CC}$

- Overtemperature protection

- Advanced bus biasing according to ISO 11898-2 (2016)

- Wake filter time  $0.5\mu s < t_{Filter} < 1.8\mu s$  meeting worldwide OEM requirements

1

- Wake-up pattern (WUP) detection in all low-power modes

- Wake-up frame (WUF) detection according to ISO 11898-2 (2016)

- Wake-up frame detection with CAN FD tolerant feature

- Local wake-up input

- SPI clock frequency up to 4 MHz

- Green Product (RoHS compliant)

- **AEC Qualified**

### **Applications**

- HS CAN networks in automotive applications

- HS CAN networks in industrial applications

#### **TLE9255W**

#### **HS CAN Transceiver with Partial Networking**

#### Overview

#### Description

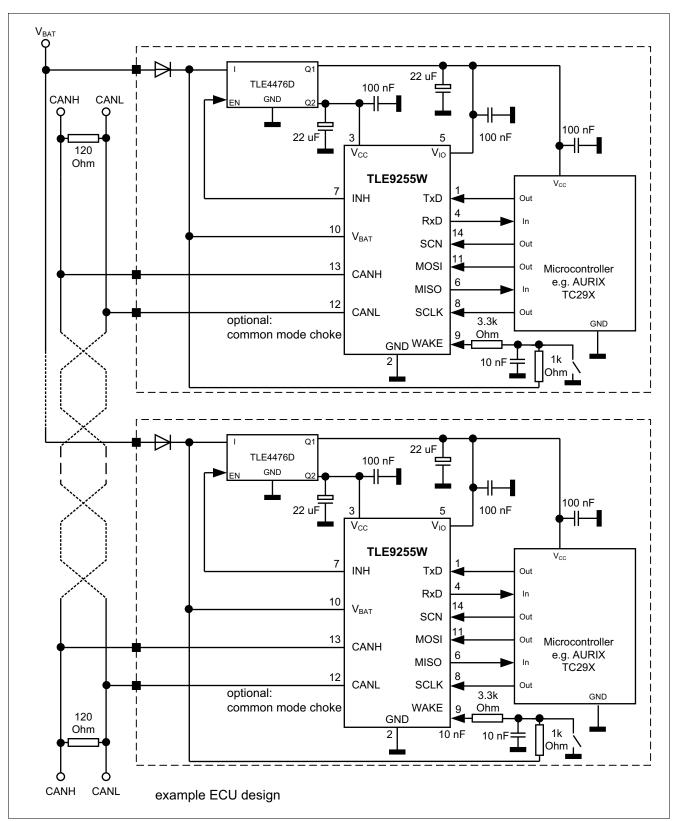

As an interface between the physical bus layer and the CAN protocol controller, the TLE9255W drives the signals to the bus and protects the microcontroller from interference generated within the network. Based on the high symmetry of the CANH and CANL signals, the TLE9255W provides a very low level of electromagnetic emission within a wide frequency range, allowing the operation of the TLE9255W without a common mode choke in automotive and industrial applications.

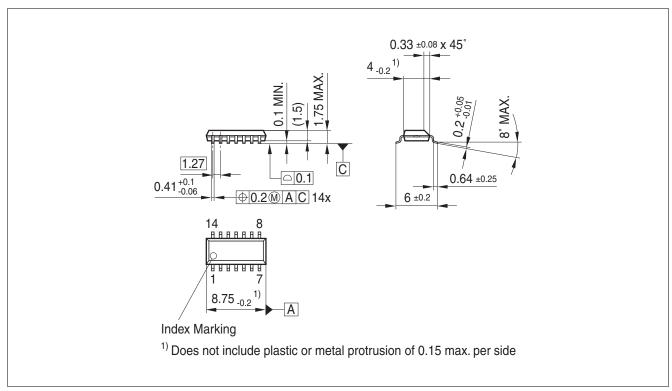

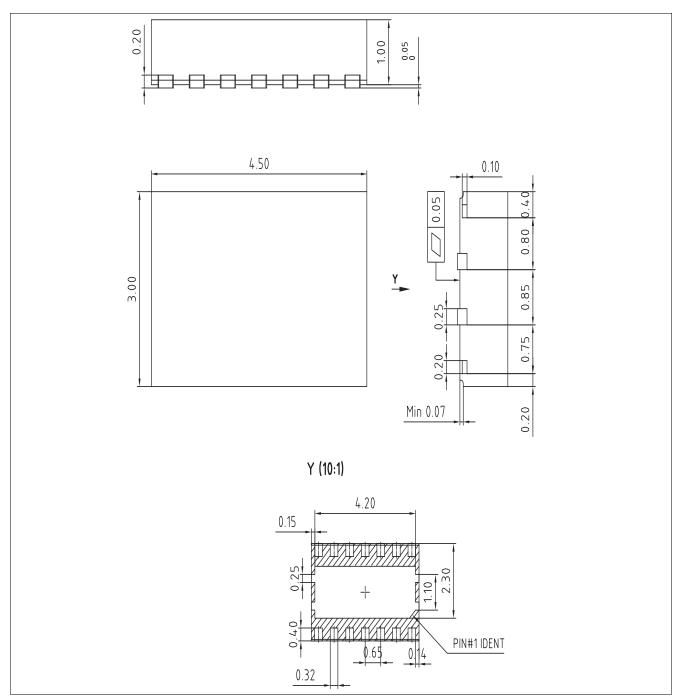

The TLE9255W is enclosed in an RoHS compliant PG-DSO-14 or PG-TSON-14 package and fulfills the requirements of the ISO11898-2 (2016).

The TLE9255W is part of the Infineon standard HS CAN transceiver family and provides beside CAN partial networking functions also a CAN FD capability up to 5 MBit/s in HS CAN networks. Configured as a partial networking HS CAN transceiver the TLE9255W can drive and receive CAN FD messages. it can also be used to block the payload of CAN FD messages. This CAN FD tolerant feature allows the usage of microcontrollers in CAN FD networks, which are not CAN FD capable.

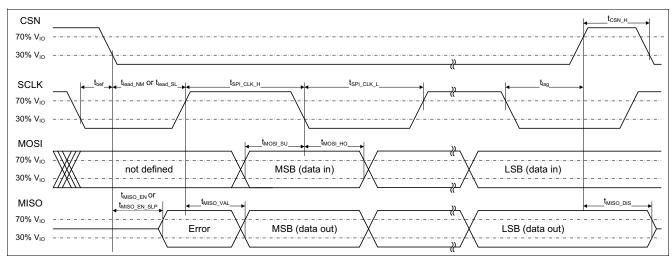

The SPI of TLE9255W controls the setup of the wake-up messages and the status message generated by the internal state machine. Most of the functions, including wake-up functions, INH output control, mode control, undervoltage control are configurable by the SPI. This allows a very flexible usage of the TLE9255W in different applications.

The two non-low power modes (Normal-operating Mode and Receive-only Mode) and the two low power modes (Sleep Mode and Stand-by Mode) provide minimum current consumption based on the required functionality.

In Sleep Mode the TLE9255W can detect a wake-up pattern (WUP) on the HS CAN and then change the mode of operation accordingly; even at a quiescent current below 26 μA over the full temperature range.

In Selective-wake Sub-mode the TLE9255W monitors the CAN messages on the HS CAN bus. If the TLE9255W detects a matching wake-up frame, then it triggers a mode change. The TLE9255W monitors wake-up identifiers up to 29 bit as well as up to 64 bit wide data. The internal protocol handler counts all bus errors. The SPI indicates failures, error counter overflow and synchronization failures to the microcontroller.

The unique power-supply management allows the application to use the TLE9255W without the battery supply  $V_{\rm BAT}$  connected. In this case the TLE9255W is supplied over the  $V_{\rm CC}$  pin. The  $V_{\rm IO}$  voltage reference supports 3.3 V and 5 V supplied microcontrollers.

Based on Infineon Smart Power Technology (SPT), the TLE9255W provides excellent immunity together with a very high electromagnetic immunity (EMI). The TLE9255W and the Infineon SPT are AEC qualified and tailored to withstand the harsh conditions of the automotive environment.

| Туре       | Package    | Marking |

|------------|------------|---------|

| TLE9255WSK | PG-DSO-14  | 9255W   |

| TLE9255WLC | PG-TSON-14 | 9255W   |

# **Table of Contents**

| 1                      | Overview                                             | . 1 |

|------------------------|------------------------------------------------------|-----|

| 2                      | Block Diagram                                        | . 6 |

| <b>3</b><br>3.1<br>3.2 | Pin Configuration                                    | . 7 |

| 4                      | High Speed CAN Functional Description                | . 9 |

| 4.1                    | High Speed CAN Physical Layer                        | . 9 |

| 5                      | Modes of Operation                                   | 11  |

| 5.1                    | Normal-operating Mode                                | 13  |

| 5.2                    | Receive-only Mode                                    | 14  |

| 5.3                    | Stand-by Mode                                        |     |

| 5.4                    | Sleep Mode                                           |     |

| 5.4.1                  | Sleep WUP Sub-Mode                                   |     |

| 5.4.2                  | Selective Wake Sub-Mode                              |     |

| 5.4.3                  | Selective Sleep Sub-Mode                             |     |

| 5.5                    | Power On Reset                                       |     |

| 5.6                    | Automatic Bus Voltage Biasing                        |     |

| 5.7                    | Wake-up event                                        |     |

| 5.7.1                  | Wake-up pattern (WUP)                                |     |

| 5.7.2                  | Wake-up frame (WUF)                                  |     |

| 5.7.3<br>5.8           | Local Wake-up (LWU)                                  |     |

| 5.8.1                  | RxD pin wake-up behavior                             |     |

| 5.8.2                  | RxD Toggle                                           |     |

|                        |                                                      |     |

| 6                      | Fail Safe Functions                                  |     |

| 6.1                    | Short Circuit Protection                             |     |

| 6.2                    | Undervoltage detection                               |     |

| 6.2.1                  | Undervoltage detection on V <sub>BAT</sub>           |     |

| 6.2.2                  | Short-term Undervoltage detection on V <sub>CC</sub> |     |

| 6.2.3                  | Long-term undervoltage detection on $V_{\rm CC}$     |     |

| 6.2.4<br>6.2.5         | Short-term Undervoltage detection on V <sub>10</sub> |     |

| 6.3                    | Long-term Undervoltage detection on $V_{10}$         |     |

| 6.4                    | TxD Time-out Function                                |     |

| 6.5                    | Overtemperature Protection                           |     |

| 6.6                    | Delay Time for Mode Change                           |     |

|                        |                                                      |     |

| <b>7</b><br>7.1        | CAN Partial Networking                               |     |

| 7.1.1                  | Wake-up frame evaluation                             |     |

| 7.1.1<br>7.1.2         | DLC and data field evaluation                        |     |

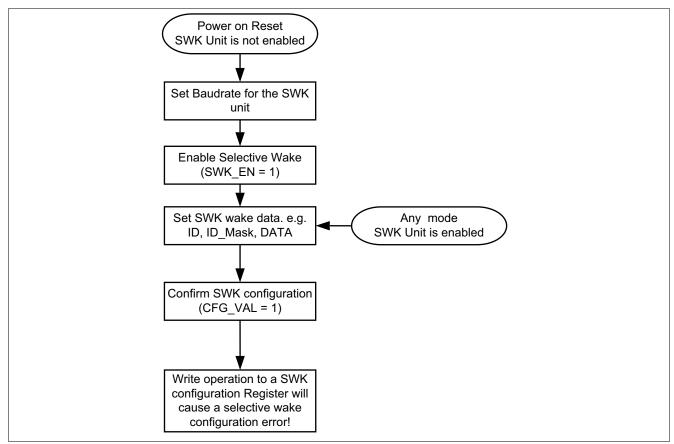

| 7.1.2<br>7.2           | Activation of Selective Wake                         |     |

| 7.3                    | Frame Error Counter                                  |     |

| 7.3<br>7.4             | Selective Wake Configuration Error                   |     |

# **TLE9255W**

| 7.5                                                                                                                                                                | CAN Flexible Data Rate (CAN FD) Tolerant Feature                                                                                                                                                                                                                                                                                                                     | 44                                                                                                 |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------|

| 7.6                                                                                                                                                                | Selective wake SPI flags                                                                                                                                                                                                                                                                                                                                             | 45                                                                                                 |

| 7.6.1                                                                                                                                                              | SysErr Flag                                                                                                                                                                                                                                                                                                                                                          | 45                                                                                                 |

| 7.6.2                                                                                                                                                              | SYNC Flag                                                                                                                                                                                                                                                                                                                                                            | 45                                                                                                 |

| 7.6.3                                                                                                                                                              | CANTO Flag                                                                                                                                                                                                                                                                                                                                                           | 46                                                                                                 |

| 7.6.4                                                                                                                                                              | CANSIL Flag                                                                                                                                                                                                                                                                                                                                                          | 46                                                                                                 |

| 7.6.5                                                                                                                                                              | SWK_ACTIVE Flag                                                                                                                                                                                                                                                                                                                                                      | 46                                                                                                 |

| 7.6.6                                                                                                                                                              | CFG_VAL Flag                                                                                                                                                                                                                                                                                                                                                         | 46                                                                                                 |

| 8                                                                                                                                                                  | Serial Peripheral Interface                                                                                                                                                                                                                                                                                                                                          | . 47                                                                                               |

| 8.1                                                                                                                                                                | SPI command format                                                                                                                                                                                                                                                                                                                                                   |                                                                                                    |

| 8.2                                                                                                                                                                | Control and Status Register                                                                                                                                                                                                                                                                                                                                          |                                                                                                    |

| 8.3                                                                                                                                                                | Status Information Field                                                                                                                                                                                                                                                                                                                                             |                                                                                                    |

| 8.4                                                                                                                                                                | SPI Failure                                                                                                                                                                                                                                                                                                                                                          |                                                                                                    |

| 8.5                                                                                                                                                                | Invalid SPI Command                                                                                                                                                                                                                                                                                                                                                  |                                                                                                    |

| 8.6                                                                                                                                                                | CSN Timeout                                                                                                                                                                                                                                                                                                                                                          |                                                                                                    |

| 8.7                                                                                                                                                                | SPI Register                                                                                                                                                                                                                                                                                                                                                         |                                                                                                    |

| 8.7.1                                                                                                                                                              | Mode Control Register                                                                                                                                                                                                                                                                                                                                                |                                                                                                    |

| 8.7.2                                                                                                                                                              | Selective Wake Control Register                                                                                                                                                                                                                                                                                                                                      |                                                                                                    |

| 8.7.3                                                                                                                                                              | Status Register                                                                                                                                                                                                                                                                                                                                                      |                                                                                                    |

|                                                                                                                                                                    | <u> </u>                                                                                                                                                                                                                                                                                                                                                             |                                                                                                    |

| 9                                                                                                                                                                  | General Product Characteristics                                                                                                                                                                                                                                                                                                                                      |                                                                                                    |

| 9.1                                                                                                                                                                | Absolute Maximum Ratings                                                                                                                                                                                                                                                                                                                                             |                                                                                                    |

| 9.2                                                                                                                                                                | Functional Range                                                                                                                                                                                                                                                                                                                                                     |                                                                                                    |

| 9.3                                                                                                                                                                | Thermal Resistance                                                                                                                                                                                                                                                                                                                                                   | /1                                                                                                 |

|                                                                                                                                                                    |                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                    |

| 10                                                                                                                                                                 | Electrical Characteristics                                                                                                                                                                                                                                                                                                                                           |                                                                                                    |

| 10.1                                                                                                                                                               | General Timing Parameter                                                                                                                                                                                                                                                                                                                                             | 72                                                                                                 |

| 10.1<br>10.2                                                                                                                                                       | General Timing Parameter  Power Supply Interface                                                                                                                                                                                                                                                                                                                     | 72<br>72                                                                                           |

| 10.1<br>10.2<br>10.2.1                                                                                                                                             | General Timing Parameter                                                                                                                                                                                                                                                                                                                                             | 72<br>72<br>72                                                                                     |

| 10.1<br>10.2<br>10.2.1<br>10.2.2                                                                                                                                   | General Timing Parameter  Power Supply Interface  Current Consumption  Undervoltage Detection                                                                                                                                                                                                                                                                        | 72<br>72<br>72<br>76                                                                               |

| 10.1<br>10.2<br>10.2.1<br>10.2.2<br>10.2.3                                                                                                                         | General Timing Parameter Power Supply Interface Current Consumption Undervoltage Detection INH Output                                                                                                                                                                                                                                                                | 72<br>72<br>72<br>76<br>77                                                                         |

| 10.1<br>10.2<br>10.2.1<br>10.2.2<br>10.2.3<br>10.3                                                                                                                 | General Timing Parameter  Power Supply Interface  Current Consumption  Undervoltage Detection  INH Output  CAN Controller Interface                                                                                                                                                                                                                                  | 72<br>72<br>72<br>76<br>77                                                                         |

| 10.1<br>10.2<br>10.2.1<br>10.2.2<br>10.2.3<br>10.3<br>10.4                                                                                                         | General Timing Parameter Power Supply Interface Current Consumption Undervoltage Detection INH Output CAN Controller Interface Transmitter and Receiver                                                                                                                                                                                                              | 72<br>72<br>72<br>76<br>77<br>77                                                                   |

| 10.1<br>10.2<br>10.2.1<br>10.2.2<br>10.2.3<br>10.3<br>10.4<br>10.4.1                                                                                               | General Timing Parameter Power Supply Interface Current Consumption Undervoltage Detection INH Output CAN Controller Interface Transmitter and Receiver Transmitter                                                                                                                                                                                                  | 72<br>72<br>72<br>76<br>77<br>77<br>79                                                             |

| 10.1<br>10.2<br>10.2.1<br>10.2.2<br>10.2.3<br>10.3<br>10.4<br>10.4.1<br>10.4.2                                                                                     | General Timing Parameter Power Supply Interface Current Consumption Undervoltage Detection INH Output CAN Controller Interface Transmitter and Receiver Transmitter Receiver                                                                                                                                                                                         | 72<br>72<br>76<br>77<br>77<br>79<br>79                                                             |

| 10.1<br>10.2<br>10.2.1<br>10.2.2<br>10.2.3<br>10.3<br>10.4<br>10.4.1<br>10.4.2<br>10.4.3                                                                           | General Timing Parameter Power Supply Interface Current Consumption Undervoltage Detection INH Output CAN Controller Interface Transmitter and Receiver Transmitter Receiver Dynamic Transceiver Parameter                                                                                                                                                           | 72<br>72<br>76<br>77<br>77<br>79<br>81<br>82                                                       |

| 10.1<br>10.2<br>10.2.1<br>10.2.2<br>10.2.3<br>10.3<br>10.4<br>10.4.1<br>10.4.2<br>10.4.3<br>10.5                                                                   | General Timing Parameter Power Supply Interface Current Consumption Undervoltage Detection INH Output CAN Controller Interface Transmitter and Receiver Transmitter Receiver Dynamic Transceiver Parameter Selective Wake Parameter                                                                                                                                  | 72<br>72<br>76<br>77<br>77<br>79<br>81<br>82<br>86                                                 |

| 10.1<br>10.2<br>10.2.1<br>10.2.2<br>10.2.3<br>10.3<br>10.4<br>10.4.1<br>10.4.2<br>10.4.3<br>10.5<br>10.5.1                                                         | General Timing Parameter Power Supply Interface Current Consumption Undervoltage Detection INH Output CAN Controller Interface Transmitter and Receiver Transmitter Receiver Dynamic Transceiver Parameter Selective Wake Parameter General Timings                                                                                                                  | 72<br>72<br>72<br>76<br>77<br>77<br>79<br>81<br>82<br>86<br>86                                     |

| 10.1<br>10.2<br>10.2.1<br>10.2.2<br>10.2.3<br>10.3<br>10.4<br>10.4.1<br>10.4.2<br>10.4.3<br>10.5<br>10.5.1                                                         | General Timing Parameter Power Supply Interface Current Consumption Undervoltage Detection INH Output CAN Controller Interface Transmitter and Receiver Transmitter Receiver Dynamic Transceiver Parameter Selective Wake Parameter General Timings CAN FD Tolerance                                                                                                 | 72<br>72<br>72<br>76<br>77<br>77<br>79<br>81<br>82<br>86<br>86<br>87                               |

| 10.1<br>10.2<br>10.2.1<br>10.2.2<br>10.2.3<br>10.3<br>10.4<br>10.4.1<br>10.4.2<br>10.4.3<br>10.5<br>10.5.1<br>10.5.2                                               | General Timing Parameter Power Supply Interface Current Consumption Undervoltage Detection INH Output CAN Controller Interface Transmitter and Receiver Transmitter Receiver Dynamic Transceiver Parameter Selective Wake Parameter General Timings CAN FD Tolerance Wake-Up                                                                                         | 72<br>72<br>76<br>77<br>77<br>79<br>81<br>82<br>86<br>86<br>87<br>88                               |

| 10.1<br>10.2<br>10.2.1<br>10.2.2<br>10.2.3<br>10.3<br>10.4<br>10.4.1<br>10.4.2<br>10.4.3<br>10.5<br>10.5.1<br>10.5.2<br>10.6<br>10.6.1                             | General Timing Parameter Power Supply Interface Current Consumption Undervoltage Detection INH Output CAN Controller Interface Transmitter and Receiver Transmitter Receiver Dynamic Transceiver Parameter Selective Wake Parameter General Timings CAN FD Tolerance Wake-Up General Timings                                                                         | 72<br>72<br>76<br>77<br>77<br>79<br>81<br>82<br>86<br>87<br>88<br>88                               |

| 10.1<br>10.2<br>10.2.1<br>10.2.2<br>10.2.3<br>10.3<br>10.4<br>10.4.1<br>10.4.2<br>10.4.3<br>10.5<br>10.5.1<br>10.5.2<br>10.6<br>10.6.1                             | General Timing Parameter Power Supply Interface Current Consumption Undervoltage Detection INH Output CAN Controller Interface Transmitter and Receiver Transmitter Receiver Dynamic Transceiver Parameter Selective Wake Parameter General Timings CAN FD Tolerance Wake-Up                                                                                         | 72<br>72<br>76<br>77<br>77<br>79<br>81<br>82<br>86<br>87<br>88<br>88                               |

| 10.1<br>10.2<br>10.2.1<br>10.2.2<br>10.2.3<br>10.3<br>10.4<br>10.4.1<br>10.4.2<br>10.4.3<br>10.5<br>10.5.1<br>10.5.2<br>10.6<br>10.6.1                             | General Timing Parameter Power Supply Interface Current Consumption Undervoltage Detection INH Output CAN Controller Interface Transmitter and Receiver Transmitter Receiver Dynamic Transceiver Parameter Selective Wake Parameter General Timings CAN FD Tolerance Wake-Up General Timings WUP detection Characteristics Local Wake-Up                             | 72<br>72<br>72<br>76<br>77<br>77<br>79<br>81<br>82<br>86<br>87<br>88<br>88<br>88<br>89             |

| 10.1<br>10.2<br>10.2.1<br>10.2.2<br>10.2.3<br>10.3<br>10.4<br>10.4.1<br>10.4.2<br>10.4.3<br>10.5<br>10.5.1<br>10.5.2<br>10.6<br>10.6.1                             | General Timing Parameter Power Supply Interface Current Consumption Undervoltage Detection INH Output CAN Controller Interface Transmitter and Receiver Transmitter Receiver Dynamic Transceiver Parameter Selective Wake Parameter General Timings CAN FD Tolerance Wake-Up General Timings WUP detection Characteristics                                           | 72<br>72<br>72<br>76<br>77<br>77<br>79<br>81<br>82<br>86<br>87<br>88<br>88<br>88<br>89             |

| 10.1<br>10.2<br>10.2.1<br>10.2.2<br>10.2.3<br>10.3<br>10.4<br>10.4.1<br>10.4.2<br>10.4.3<br>10.5<br>10.5.1<br>10.5.2<br>10.6<br>10.6.1<br>10.6.2                   | General Timing Parameter Power Supply Interface Current Consumption Undervoltage Detection INH Output CAN Controller Interface Transmitter and Receiver Transmitter Receiver Dynamic Transceiver Parameter Selective Wake Parameter General Timings CAN FD Tolerance Wake-Up General Timings WUP detection Characteristics Local Wake-Up SPI Application Information | 72<br>72<br>72<br>76<br>77<br>77<br>79<br>81<br>82<br>86<br>87<br>88<br>88<br>89<br>90<br>90       |

| 10.1<br>10.2<br>10.2.1<br>10.2.2<br>10.2.3<br>10.3<br>10.4<br>10.4.1<br>10.4.2<br>10.4.3<br>10.5<br>10.5.1<br>10.5.2<br>10.6<br>10.6.1<br>10.6.2<br>10.6.3<br>10.7 | General Timing Parameter Power Supply Interface Current Consumption Undervoltage Detection INH Output CAN Controller Interface Transmitter and Receiver Transmitter Receiver Dynamic Transceiver Parameter Selective Wake Parameter General Timings CAN FD Tolerance Wake-Up General Timings WUP detection Characteristics Local Wake-Up SPI                         | 72<br>72<br>72<br>76<br>77<br>77<br>79<br>81<br>82<br>86<br>87<br>88<br>88<br>89<br>90<br>90       |

| 10.1<br>10.2<br>10.2.1<br>10.2.2<br>10.2.3<br>10.3<br>10.4<br>10.4.1<br>10.4.2<br>10.4.3<br>10.5<br>10.5.1<br>10.5.2<br>10.6<br>10.6.1<br>10.6.2<br>10.6.3<br>10.7 | General Timing Parameter Power Supply Interface Current Consumption Undervoltage Detection INH Output CAN Controller Interface Transmitter and Receiver Transmitter Receiver Dynamic Transceiver Parameter Selective Wake Parameter General Timings CAN FD Tolerance Wake-Up General Timings WUP detection Characteristics Local Wake-Up SPI Application Information | 72<br>72<br>72<br>76<br>77<br>77<br>79<br>81<br>82<br>86<br>87<br>88<br>88<br>90<br>90<br>90<br>91 |

# **TLE9255W**

| 11.4 | Further Application Information | 95 |

|------|---------------------------------|----|

| 12   | Package Outlines                | 96 |

| 13   | Revision History                | 99 |

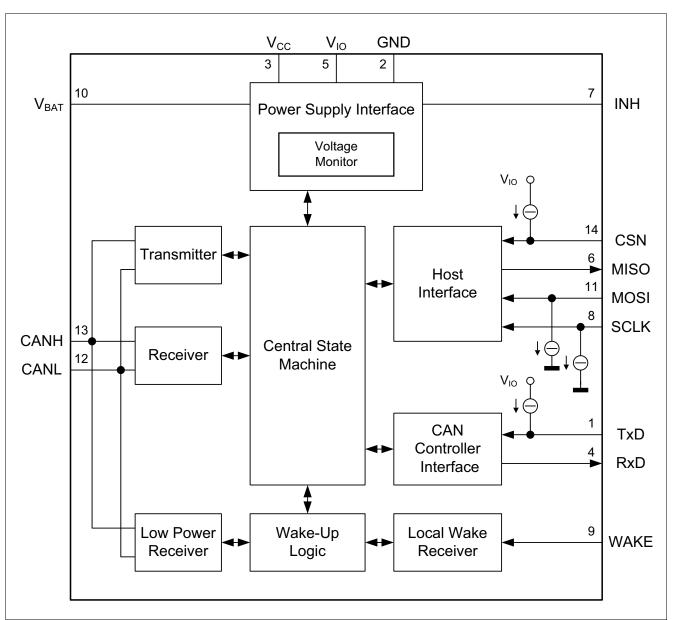

Block Diagram

# 2 Block Diagram

Figure 1 Block Diagram

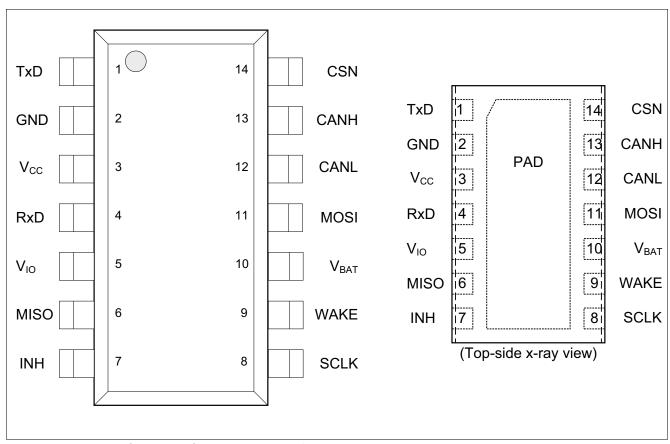

**Pin Configuration**

# 3 Pin Configuration

# 3.1 Pin Assignment

Figure 2 Pin configuration for PG-DSO-14 and PG-TSON-14

# 3.2 Pin Definitions

Table 1 Pin definitions and functions

| Pin | Symbol          | Function                                                                                                               |

|-----|-----------------|------------------------------------------------------------------------------------------------------------------------|

| 1   | TxD             | Transmit Data Input; integrated pull-up current source to $V_{10}$ , "low" to drive a dominant signal on CANH and CANL |

| 2   | GND             | Ground.                                                                                                                |

| 3   | V <sub>cc</sub> | Transmitter Supply Voltage; 100 nF decoupling capacitor to GND is recommended                                          |

# Pin Configuration

Table 1

Pin definitions and functions (cont'd)

| Pin | Symbol          | Function                                                                    |

|-----|-----------------|-----------------------------------------------------------------------------|

| 4   | RxD             | Receive Data Output;                                                        |

|     |                 | "low" while a dominant signal is on the HS CAN bus,                         |

|     |                 | output voltage adapted to the voltage on the $V_{\rm IO}$ level shift input |

| 5   | V <sub>IO</sub> | Level Shift Input;                                                          |

|     |                 | reference voltage for the digital input and output pins,                    |

|     |                 | 100 nF decoupling capacitor to GND is recommended                           |

| 6   | MISO            | SPI Serial Data Output;                                                     |

|     |                 | tri-state while CSN is "high"                                               |

| 7   | INH             | Inhibit Output;                                                             |

|     |                 | open drain output to control external circuitry                             |

| 8   | SCLK            | SPI Clock Input;                                                            |

|     |                 | integrated pull-down current source to GND                                  |

| 9   | WAKE            | Wake-up Input;                                                              |

|     |                 | local wake-up input, terminated against GND and $V_{BAT}$ ,                 |

|     |                 | wake-up input sensitive to signal changes in both directions                |

| 10  | $V_{BAT}$       | Battery Supply Voltage;                                                     |

|     |                 | 100 nF decoupling capacitor to GND is recommended                           |

| 11  | MOSI            | SPI Serial Data Input;                                                      |

|     |                 | integrated pull-down current source to GND                                  |

| 12  | CANL            | Low-level HS CAN Bus Line                                                   |

| 13  | CANH            | High-level HS CAN Bus Line                                                  |

| 14  | CSN             | SPI Chip Select Not Input;                                                  |

|     |                 | integrated pull-up current source to $V_{10}$                               |

| PAD | -               | Connect to PCB heat sink area.                                              |

|     |                 | Do not connect to other potential than GND.                                 |

**High Speed CAN Functional Description**

# 4 High Speed CAN Functional Description

High speed CAN (HS CAN) is a serial bus system that connects microcontrollers, sensors and actuators for real-time control applications. ISO 11898-2 (2016) describes the use of the Controller Area Network (CAN) within road vehicles. According to the 7-layer OSI reference model the physical layer of a HS CAN bus system specifies the data transmission from one CAN node to all other available CAN nodes within the network. The CAN transceiver is part of the physical layer. The physical layer specification of a CAN bus system includes all electrical specifications of a CAN network.

### The TLE9255W supports:

- · standard bus wake-up functionality

- CAN Partial Networking with selective wake-up functionality according to ISO 11898-2 (2016)

- CAN Flexible data rate (CAN FD) transmission up to 5 MBit/s

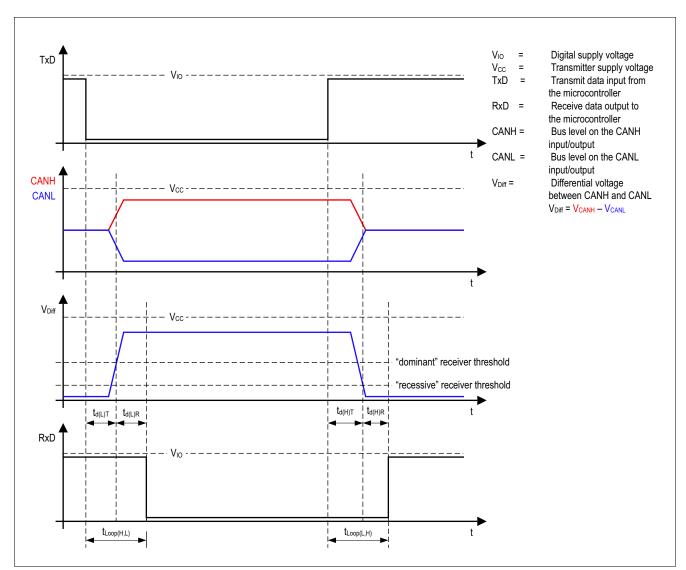

## 4.1 High Speed CAN Physical Layer

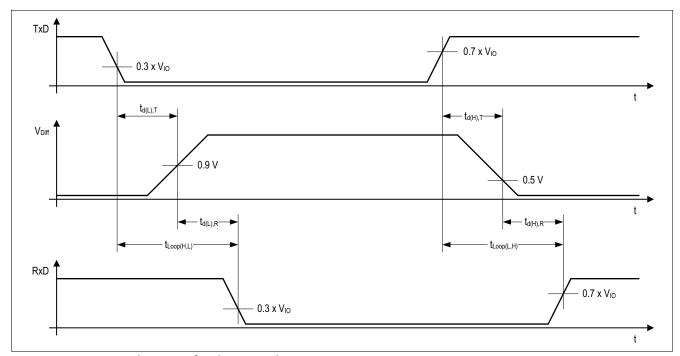

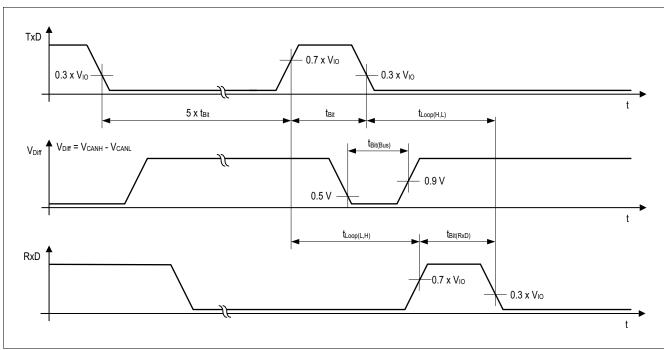

Figure 3 High speed CAN bus signals and logic signals

#### **High Speed CAN Functional Description**

The TLE9255W is a HS CAN transceiver operating as an interface between the CAN controller and the physical bus medium. A HS CAN network is a two wire, differential network which allows data transmission rates up to 5 MBit/s. HS CAN networks have two signal states on the CAN bus (see Figure 3):

- dominant

- recessive

The CANH and CANL pins are the interface to the CAN bus and operate both as an input and as an output. The RxD and TxD pins are the interface to the microcontroller. The TxD pin is the serial data input from the CAN controller. The RxD pin is the serial data output to the CAN controller. The HS CAN transceiver TLE9255W includes a receiver and a transmitter unit, allowing the transceiver to send data to the bus medium and monitoring the data from the bus medium at the same time (see Figure 1). The TLE9255W converts the serial data stream, which is available on the transmit data input TxD, to a differential output signal on the CAN bus, provided by the CANH and CANL pins. The receiver stage of the TLE9255W monitors the data on the CAN bus and converts it to a serial, single-ended signal on the RxD output pin. A "low" signal on the TxD pin creates a dominant signal on the CAN bus, followed by a "low" signal on the RxD pin (see Figure 3). The feature of broadcasting data to the CAN bus and listening to the data traffic on the CAN bus simultaneously is essential to support the bit-to-bit arbitration within CAN networks.

ISO 11898-2 (2016) defines the voltage levels for HS CAN transceivers. Whether a data bit is dominant or recessive depends on the voltage difference between the CANH and CANL pins:

$$V_{\text{Diff}} = V_{\text{CANH}} - V_{\text{CANL}}$$

To transmit a dominant signal to the CAN bus the amplitude of the differential signal  $V_{\text{Diff}}$  is  $\geq 1.5$  V. To receive a recessive signal from the CAN bus the amplitude of the differential  $V_{\text{Diff}}$  is  $\leq 0.5$  V.

Partially supplied High-Speed CAN networks have CAN bus nodes with different power supply conditions. Some nodes are connected to the common power supply, while other nodes are disconnected from the power supply and in power-down state. Regardless of whether the CAN bus subscriber is supplied or not, each subscriber connected to the common bus media must not interfere with the communication. The TLE9255W is designed to support Partially supplied networks. In power-down state, the receiver input resistors are switched off and the transceiver input has a high resistance.

For permanently supplied ECUs, the TLE9255W provides low power modes. In these low power modes, the current consumption of the TLE9255W is optimized to a minimum, while the TLE9255W can still recognize wake-up patterns or wake-up frames on the CAN bus and signal the wake-up event to the external microcontroller.

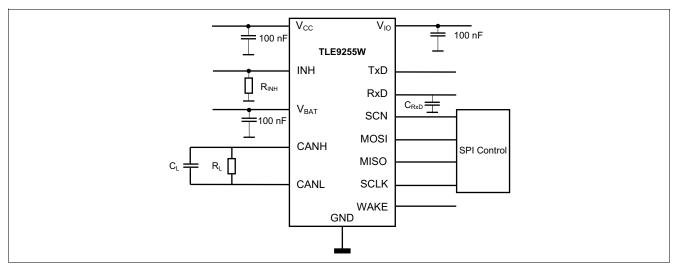

The voltage level on the digital input TxD and the digital output RxD is determined by the reference supply level at the  $V_{\rm IO}$  pin. Depending on the voltage level at the  $V_{\rm IO}$  pin, the signal levels on the logic pins (CSN, SCLK, MOSI, MISO, TxD and RxD) are compatible to microcontrollers having a 5 V or 3.3 V I/O supply. It is highly recommended that the digital power supply of  $V_{\rm IO}$  of the transceiver is connected to the I/O power supply of the microcontroller; this is the way it is intended to be used (see Figure 53).

# 5 Modes of Operation

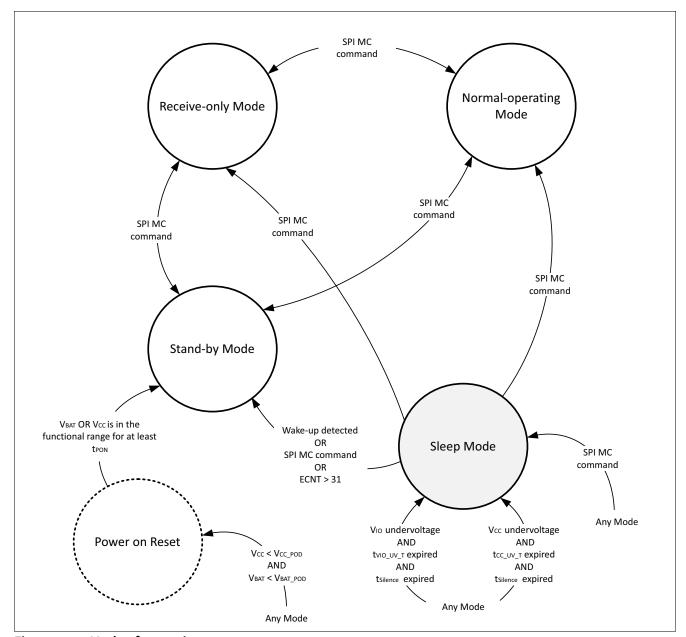

The TLE9255W supports four different Modes of operation (see Figure 4):

- Normal-operating Mode (Chapter 5.1)

- Receive-only Mode (Chapter 5.2)

- Stand-by Mode (Chapter 5.3)

- Sleep Mode (Chapter 5.4)

Figure 4 Mode of operation

Table 2 Types of Modes and Sub-Modes

| Type of mode      | Mode                  | Sub-Mode                 |

|-------------------|-----------------------|--------------------------|

| Normal power mode | Normal-operating mode | -                        |

|                   | Receive-only Mode     | -                        |

| Low power mode    | Stand-by Mode         | -                        |

|                   | Sleep Mode            | Sleep WUP Sub-Mode       |

|                   |                       | Selective Wake Sub-Mode  |

|                   |                       | Selective Sleep Sub-Mode |

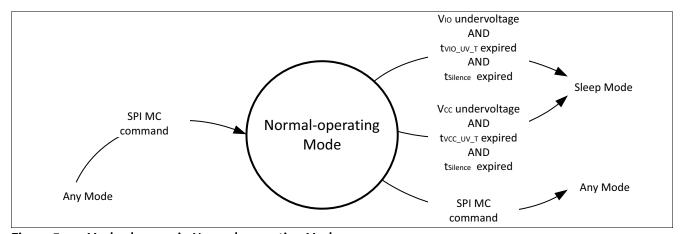

### 5.1 Normal-operating Mode

In Normal-operating mode all functions of the TLE9255W are available. The TLE9255W can receive data from the HS CAN bus as well as transmit data to the HS CAN bus.

- The transmitter is active and drives the serial data stream on the TxD input pin to the bus pins CANH, CANL.

- The normal mode receiver is active and converts the signals from the bus to a serial data stream on the RxD output pin.

- · The bus biasing is on.

- The TxD timeout function is enabled (Chapter 6.4).

- The overtemperature protection is enabled (Chapter 6.5).

- The undervoltage detection on V<sub>BAT</sub> is enabled(Chapter 6.2.1)

- The undervoltage detection on V<sub>CC</sub> is enabled (Chapter 6.2.2).

- The undervoltage detection on  $V_{10}$  is enabled (Chapter 6.2.4).

- The INH output pin is "high".

- A valid wake-up pattern is not signalled in the SPI bit WUP (Chapter 5.7.1).

- Only if the selective wake function is enabled (SWK\_EN = 1), then the HS CAN bus will be continuously monitored for a valid WUF (Chapter 5.7.2).

- Local wake-up function is disabled (Chapter 5.7.3).

Conditions for entering the Normal-operating Mode:

• Normal-operating Mode can be entered via an SPI MC command from any mode of operation.

Conditions for leaving the Normal-operating Mode:

- If V<sub>IO</sub> < V<sub>IO\_UV</sub> AND t<sub>VIO\_UV\_T</sub> has expired ANDt<sub>silence</sub> has expired, then this triggers a mode change to Sleep Mode

- If V<sub>CC</sub> < V<sub>CC\_UV</sub> AND t<sub>VCC\_UV\_T</sub> has expired AND t<sub>silence</sub> has expired, then this triggers a mode change to Sleep Mode.

- An SPI MC command triggers a mode change.

Figure 5 shows possible mode changes.

Figure 5 Mode changes in Normal-operating Mode

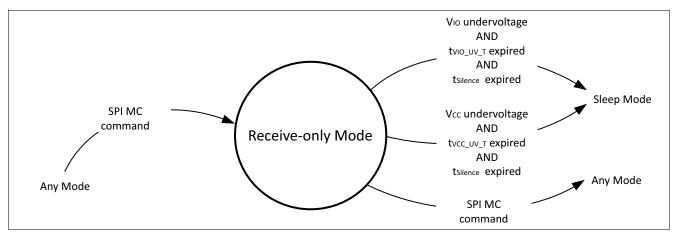

### 5.2 Receive-only Mode

In Receive-only Mode the transmitter is disabled and the receiver is enabled. The TLE9255W can receive data from the HS CAN bus, but cannot transmit data to the HS CAN bus.

- The transmitter is disabled and the data available on the TxD input is blocked.

- The RxD output pin indicates the data received by the normal-mode receiver.

- The bus biasing is on.

- The TxD timeout function is disabled (Chapter 6.4).

- The overtemperature protection is disabled (Chapter 6.5).

- The undervoltage detection on V<sub>BAT</sub> is enabled(Chapter 6.2.1)

- The undervoltage detection on V<sub>CC</sub> is enabled (Chapter 6.2.2).

- The undervoltage detection on  $V_{10}$  is enabled (Chapter 6.2.4).

- The INH output pin is "high".

- A valid wake-up pattern is not signalled in the SPI bit WUP (Chapter 5.7.1).

- Only if the selective wake function is enabled (SWK\_EN = 1), then the HS CAN bus is continuously monitored for a valid WUF (Chapter 5.7.2).

- Local wake-up function is disabled (Chapter 5.7.3).

Conditions for entering the Receive-only Mode:

Receive-only Mode can be entered via an SPI MC command from any mode of operation.

Conditions for leaving the Received-only Mode:

- If  $V_{10} < V_{10\_UV}$  AND  $t_{V10\_UV\_T}$  has expired AND  $t_{silence}$  has expired, then this triggers a mode change to Sleep Mode.

- If V<sub>CC</sub> < V<sub>CC\_UV</sub> AND t<sub>VCC\_UV\_T</sub> has expired AND t<sub>silence</sub> has expired, then this triggers a mode change to Sleep Mode.

- An SPI MC command triggers a mode change.

Figure 6 shows possible mode changes.

Figure 6 Mode changes in Receive-only Mode

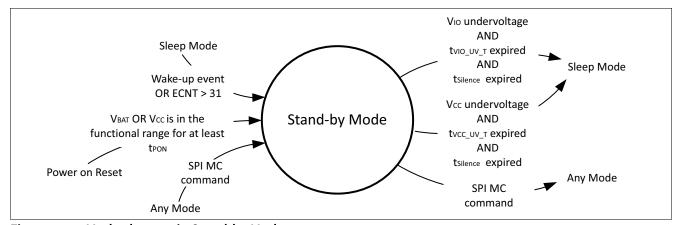

## 5.3 Stand-by Mode

Stand-by Mode is a low power mode of the TLE9255W with both the transmitter and the receiver disabled. In Stand-by Mode the transceiver can neither send data to the HS CAN bus nor can it receive data from the HS CAN bus:

- The transmitter is disabled and the data available on the TxD input is blocked.

- The RxD output pin indicates a wake-up event (Chapter 5.8). If no wake-up event is pending, then the default value of the RxD output pin is "high".

- After Power on Reset the bus biasing is off. Chapter 5.6 describes the conditions for the bus biasing.

- The TxD timeout function is disabled (Chapter 6.4).

- The overtemperature protection is disabled (Chapter 6.5).

- The undervoltage detection on V<sub>BAT</sub> is enabled(Chapter 6.2.1)

- The undervoltage detection on  $V_{CC}$  is enabled (Chapter 6.2.2).

- The undervoltage detection on  $V_{10}$  is enabled (Chapter 6.2.4).

- The INH output pin is "high".

- If the selective wake function is disabled (SWK\_EN = 0), then the HS CAN bus is continuously monitored for a valid wake-up pattern (Chapter 5.7.1). If the selective wake function is enabled, then a valid wake-up pattern is not signalled in the SPI bit WUP.

- Only if the selective wake function is enabled (SWK\_EN = 1), then the HS CAN bus is continuously monitored for a valid WUF (Chapter 5.7.2).

- Local wake-up function is enabled (Chapter 5.7.3).

- If  $V_{10} > V_{10-11V}$ , then a mode change is possible.

Conditions for entering the Stand-by Mode:

- After Power on Reset: If V<sub>CC</sub> OR V<sub>BAT</sub> is within the functional range for at least t<sub>PON</sub>, then the TLE9255W enters Stand-by Mode.

- If a wake-up (WUP, WUF, LWU) is detected in Sleep Mode, then the TLE9255W enters Stand-by Mode.

- If the selective wake unit is active (Selective wake Sub-Mode) AND if the value of the error counter is 32 (see Chapter 7.3),

- then the TLE9255W enters Stand-by Mode.

- Stand-by Mode can be entered via an SPI MC command from any mode of operation.

Conditions for leaving the Stand-by Mode:

- If V<sub>IO</sub> < V<sub>IO\_UV</sub> AND t<sub>VIO\_UV\_T</sub> has expired AND t<sub>silence</sub> has expired, then this triggers a mode change to Sleep Mode.

- If V<sub>CC</sub> < V<sub>CC\_UV</sub> AND t<sub>VCC\_UV\_T</sub> has expired AND t<sub>silence</sub> has expired, then this triggers a mode change to Sleep Mode.

- An SPI MC command triggers a mode change.

Figure 7 shows possible mode changes.

Figure 7 Mode changes in Stand-by Mode

### 5.4 Sleep Mode

Sleep mode is a low power mode with minimized quiescent current. If the TLE9255W detects a wake-up event in Sleep Mode, then it changes to Stand-by Mode. Sleep Mode has three Sub-Modes.

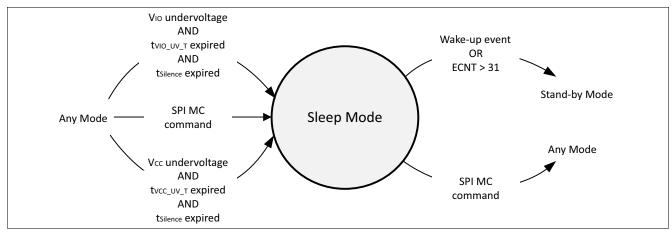

Figure 8 Mode change in Sleep Mode

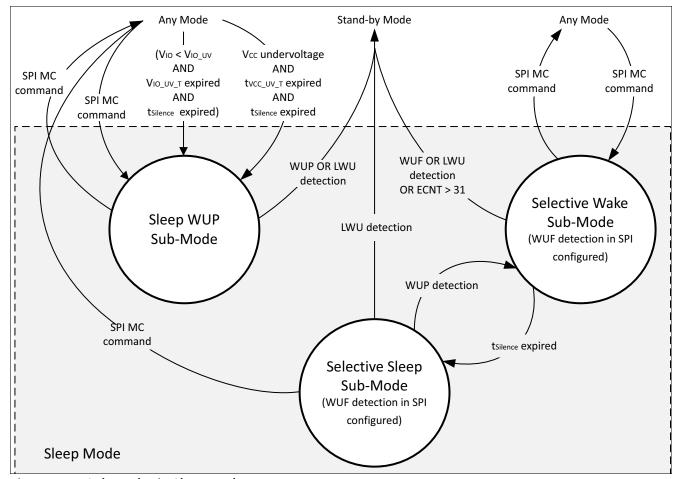

Figure 9 Sub-Modes in Sleep Mode

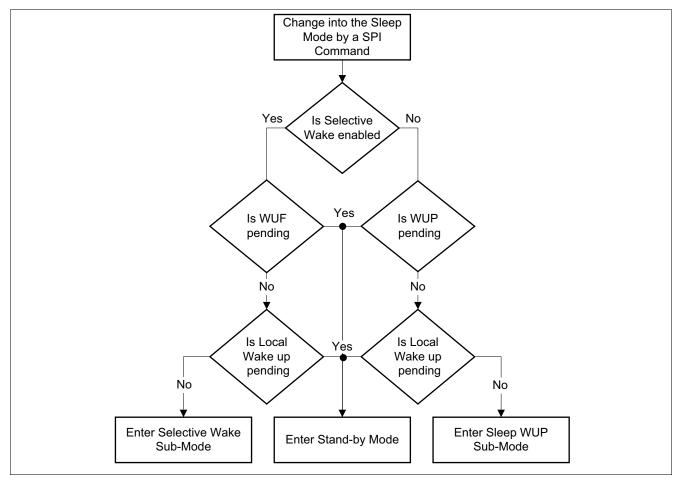

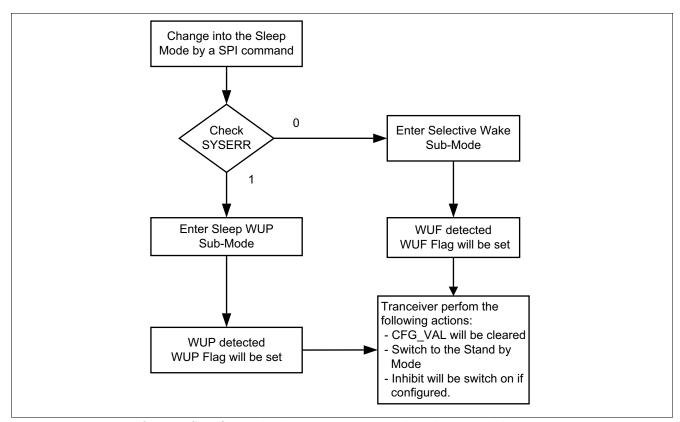

**Figure 10** shows the internal behavior of the TLE9255W in case the microcontroller sends a change to Sleep Mode SPI command.

Figure 10 Internal behavior of the TLE9255W after receiving a change to Sleep Mode SPI command

### 5.4.1 Sleep WUP Sub-Mode

Sleep WUP Sub-Mode is a low power mode of the TLE9255W. Sleep WUP Sub-Mode reduces current consumption. The following conditions are valid for the Sleep WUP Sub-Mode:

- The transmitter is disabled and the data available on the TxD input is blocked.

- The value of the RxD output pin depends on the power supply circuit of  $V_{10}$ .

- Permanent power supply of  $V_{10}$  (INH pin is not used) The RxD output pin is "high"

- The INH pin controls the power supply of  $V_{\rm IO}$ The RxD output pin is "low"

- If the t<sub>Silence</sub> timer has expired, then the bus biasing is off.

- The TxD timeout function is disabled (Chapter 6.4).

- The overtemperature protection is disabled (Chapter 6.5).

- The undervoltage detection on V<sub>BAT</sub> (Chapter 6.2.1) is not signalled in the SPI bit VBAT\_UV.

- The undervoltage detection on V<sub>CC</sub> is disabled(Chapter 6.2.2).

- The undervoltage detection on  $V_{10}$  (Chapter 6.2.4) is not signalled in the SPI bits VIO\_LTUV and VIO\_STUV.

- The INH output pin is "low". The SPI bit VBAT\_CON in the register SWK\_CTRL\_1 controls the behavior of the INH pin.

- The HS CAN bus is continuously monitored for a valid wake-up pattern (Chapter 5.7.1).

- The HS CAN bus is not monitored for a valid WUF (Chapter 5.7.2).

- Local wake-up function is enabled.

Conditions for entering the Sleep WUP Sub-Mode:

- If  $V_{\rm IO}$  <  $V_{\rm IO\_UV}$  ( $V_{\rm IO}$  undervoltage) AND  $t_{\rm VIO\_UV\_T}$  has expired AND  $t_{\rm silence}$  has expired, then the TLE9255W enters Sleep WUP Sub-Mode.

- If  $V_{CC} < V_{CC\_UV}$  ( $V_{CC}$  undervoltage) AND  $t_{VCC\_UV\_T}$  has expired AND  $t_{silence}$  has expired, then the TLE9255W enters Sleep WUP Sub-Mode. The SPI bit STTS\_EN controls this state transition.

- The Sleep WUP Sub-Mode can be entered via an SPI MC command from any mode of operation.

Conditions for leaving the Sleep WUP Sub-Mode:

- If a wake-up (WUP, LWU) is detected in Sleep WUP Sub-Mode, then the TLE9255W enters Stand-by Mode.

- An SPI MC command triggers a mode change to any mode of operation.

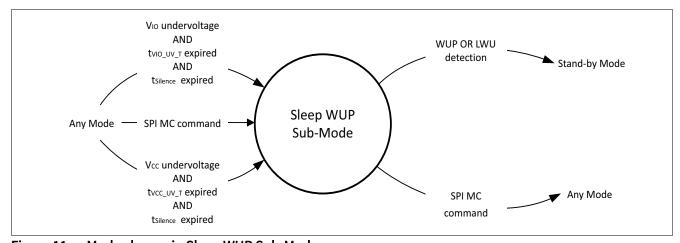

Figure 11 Mode change in Sleep WUP Sub-Mode

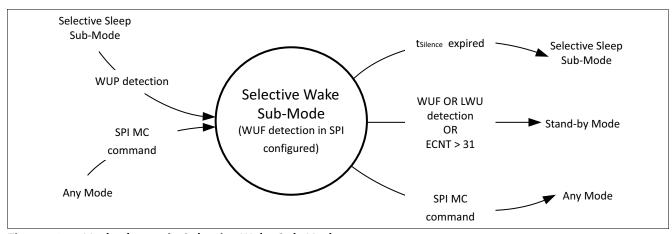

#### 5.4.2 Selective Wake Sub-Mode

Selective Wake Sub-Mode is a low power mode of the TLE9255W. Only if the selective wake function is enabled (SWK\_EN= 1), then the TLE9255W can enter Selective Wake Sub-Mode. Chapter 7 describes the partial networking functionality and the configuration. The following conditions are valid for the Selective Wake Sub-Mode:

- The transmitter is disabled and the data available on the TxD input is blocked.

- The default value of the RxD output pin depends on the power supply circuit of  $V_{10}$ .

- Permanent power supply of  $V_{10}$  (INH pin is not used) The RxD output pin is "high"

- The INH pin controls the power supply of  $V_{\rm IO}$ The RxD output pin is "low"

- · The bus biasing is on.

- The TxD timeout function is disabled (Chapter 6.4).

- The overtemperature protection is disabled (Chapter 6.5).

- The undervoltage detection on V<sub>BAT</sub> is enabled (Chapter 6.2.1).

- The undervoltage detection on V<sub>CC</sub> is disabled(Chapter 6.2.2).

- The undervoltage detection on  $V_{10}$  is enabled (Chapter 6.2.4).

- The INH output pin is "low". The SPI bit **VBAT\_CON** in the register **SWK\_CTRL\_1** controls the behavior of the INH pin.

- A valid wake-up pattern is not signalled in the SPI bit WUP (Chapter 5.7.1).

- The HS CAN bus is continuously monitored for a valid WUF (Chapter 5.7.2).

- Local wake-up function is enabled.

Conditions for entering the Selective Wake Sub-Mode:

- The Selective Wake Sub-Mode can be entered via an SPI MC command from any mode of operation.

- If the TLE9255W detects a WUP in Selective Sleep Sub-Mode, then it enters Selective Wake Sub-Mode. Conditions for leaving the Selective Wake Sub-Mode:

- If a wake-up (WUF, LWU) is detected in Selective Wake Sub-Mode, then Stand-by Mode is entered.

- If the error counter > 31 (Chapter 7.3) in Selective Wake Sub-Mode, then Stand-by Mode is entered.

- If  $t_{Silence}$  has expired, then Selective Sleep Sub-Mode is entered.

- An SPI MC command will trigger a mode change to any mode of operation.

Figure 12 Mode change in Selective Wake Sub-Mode

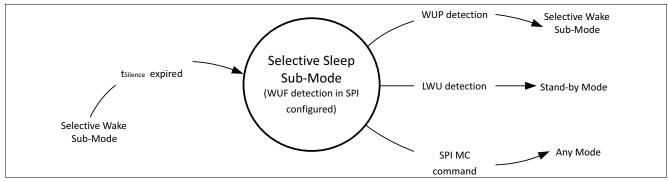

### 5.4.3 Selective Sleep Sub-Mode

Selective Sleep Sub-mode is a low power mode with optimized quiescent current. The following conditions are valid for the Selective Wake Sub-Mode:

- The transmitter is disabled and the data available on the TxD input is blocked.

- The default value of the RxD output pin depends on the power supply circuit of  $V_{10}$ .

- Permanent power supply of  $V_{10}$  (INH pin is not used) The RxD output pin is "high"

- The INH pin controls the power supply of  $V_{\rm IO}$ The RxD output pin is "low"

- The bus biasing is off.

- The TxD timeout function is disabled (Chapter 6.4).

- The overtemperature protection is disabled (Chapter 6.5).

- The undervoltage detection on V<sub>BAT</sub> (Chapter 6.2.1) is not signalled in the SPI bit VBAT\_UV.

- The undervoltage detection on V<sub>CC</sub> is disabled(Chapter 6.2.2).

- The undervoltage detection on  $V_{10}$  (Chapter 6.2.4) is not signalled in the SPI bits VIO\_LTUV and VIO\_STUV.

- The INH output pin is "low". The SPI bit VBAT\_CON in the register SWK\_CTRL\_1 controls the behavior of the INH pin.

- The HS CAN bus is continuously monitored for a valid wake-up pattern (Chapter 5.7.1), but a valid wake-up pattern is not signalled in the SPI bit WUP (Chapter 5.7.1).

- The HS CAN bus is not monitored for a valid WUF (Chapter 5.7.2).

- Local wake-up function is enabled.

Conditions for entering the Selective Sleep Sub-Mode:

If there is no communication on the HS CAN bus for longer than t<sub>Silence</sub> in the Selective Wake Sub-Mode, then the TLE9255W enters the Selective Sleep Sub-Mode.

Conditions for leaving the Selective Sleep Sub-Mode:

- If a WUP is detected, then Selective Wake Sub-Mode is entered.

- If an LWU has been detected, then Stand-by Mode will be entered.

- An SPI MC command triggers a mode change to any mode of operation.

Figure 13 Mode change in Selective Sleep Sub-Mode

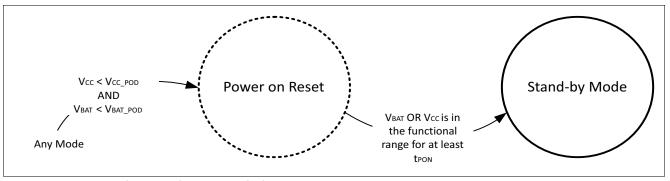

#### 5.5 Power On Reset

Power on Reset is a transition state of the TLE9255W after power is applied and the transceiver is not yet fully functional.

- The transmitter and receiver are disabled.

- The bus biasing is off.

- The TxD timeout function is disabled.

- The overtemperature protection is disabled.

- The undervoltage detection on  $V_{BAT}$  is enabled (Chapter 6.2.1), but it is not signalled in the SPI bit VBAT\_UV.

- The undervoltage detection on  $V_{CC}$  is disabled.

- The undervoltage detection on V<sub>IO</sub> is enabled (Chapter 6.2.4), but it is not signalled in the SPI bits VIO\_LTUV and VIO\_STUV.

- The SPI communication is blocked (MOSI, SCLK, CSN),

- RxD and MISO pins are high impedance.

- · TxD pin is blocked

- If  $V_{\text{BAT}} > V_{\text{BAT POD}}$  OR  $V_{\text{CC}} > V_{\text{CC POD}}$ , then the INH output pin is switched on

- All SPI registers are reset to default values.

- The HS CAN bus is not continuously monitored for a valid wake-up pattern (Chapter 5.7.1)

- The HS CAN bus is not monitored for a valid WUF (Chapter 5.7.2).

- Local wake-up function is disabled.

Conditions for entering the Power on Reset:

V<sub>BAT</sub> < V<sub>BAT POD</sub> AND V<sub>CC</sub> < V<sub>CC POD</sub> threshold.

Conditions for leaving the Power on Reset:

If V<sub>BAT</sub> is within the functional range for at least t<sub>PON</sub> OR if V<sub>CC</sub> is within the functional range for at least t<sub>PON</sub>, then the TLE9255W enters Stand-by Mode

Figure 14 shows power up behavior and power down behavior:

Figure 14 Power down and power up behavior

#### **SPI bit POR**

The **POR** flag indicates that all registers are reset and the state machine is in the default mode (Stand-by Mode) If all of the following conditions are fulfilled, then the **POR** flag is set:

•  $V_{BAT}$  is within the functional range for at least  $t_{PON}$  OR  $V_{CC}$  is within the functional range for at least  $t_{PON}$ , then the TLE9255W enters Stand-by Mode

### **TLE9255W**

# **Modes of Operation**

-  $V_{IO}$  is within the functional range (SPI communication is possible)

Any of the following events resets the POR flag:

- an SPI clear command

- a transition to the Normal-operating Mode

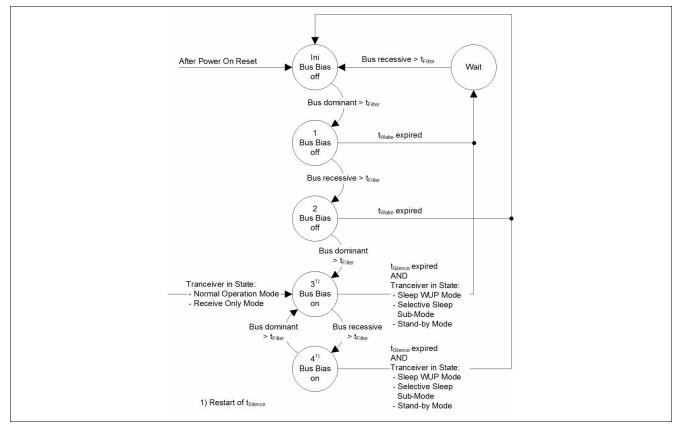

### 5.6 Automatic Bus Voltage Biasing

The automatic bus voltage biasing improves EMC performance of the entire network and increases the reliability of communication performance in networks using CAN partial networking.

The automatic bus voltage biasing is enabled in all low power modes. The biasing unit operates independently from all other transceiver functions and only depending on the network activity ( $t_{\rm Silence}$ ). If  $t_{\rm Silence}$  has expired, then there is no activity on the CAN bus. The  $t_{\rm Silence}$  timer is restarted under the following conditions:

- If  $t_{\text{Silence}}$  has expired in Sleep WUP Sub-Mode AND a WUP is detected

- If  $t_{\text{Silence}}$  has not expired in Sleep WUP Sub-Mode AND a rising or falling edge is detected AND the pulse width (dominant or recessive) is greater than  $t_{\text{Filter}}$

- If a WUP is detected in Selective Sleep Sub-Mode

- If t<sub>Silence</sub> has expired in Stand-by Mode AND a WUP is detected

- If the  $t_{\rm Silence}$  has not expired in Stand-by Mode AND a rising edge or a falling edge is detected AND the pulse width (dominant or recessive) is greater than  $t_{\rm Filter}$

- If a rising or falling edge is detected in any other mode AND the pulse width (dominant or recessive) is greater than  $t_{\rm Filter}$

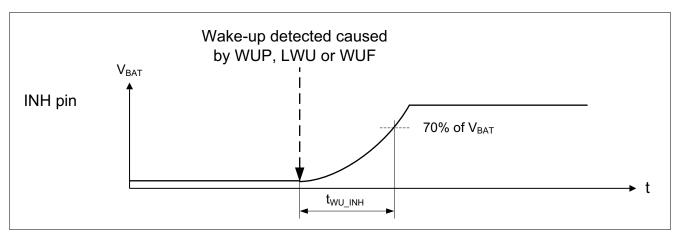

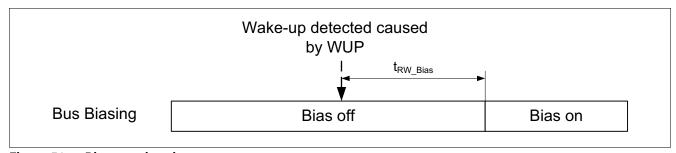

If there is no activity on the bus for longer than  $t_{\rm SILENCE}$ , then the internal resistors bias the bus pins towards GND. On detection of a valid wake-up pattern (WUP), the internal biasing is enabled and terminates the biasing resistors towards 2.5 V within  $t > t_{\rm RW~Bias}$ .

Figure 15 Bus Biasing and  $t_{Silence}$

### 5.7 Wake-up event

Valid wake-up events are:

- a Wake-up pattern (WUP) in Sleep WUP Sub-Mode

- a Wake-up frame (WUF) in Selective Wake Sub-Mode

- a Local Wake-up (LWU) in Sleep WUP Sub-Mode, Selective Sleep Sub-Mode or Selective Wake Sub-Mode If a valid wake-up event is detected, then this triggers a mode change to Stand-by Mode.

### 5.7.1 Wake-up pattern (WUP)

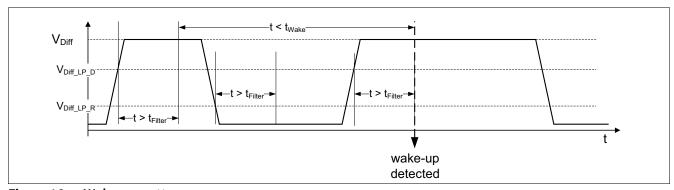

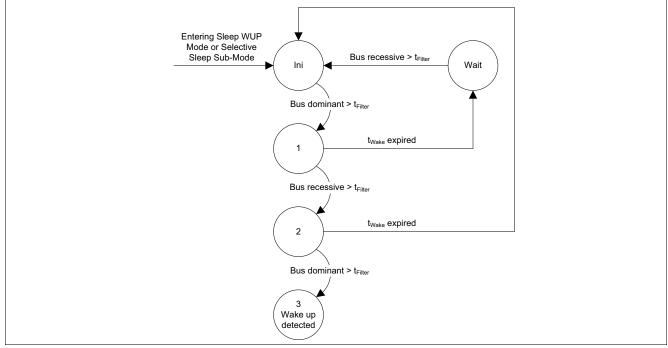

Within the maximum wake-up time  $t_{\text{WAKE}}$ , the wake-up pattern consists of the following sequence (see Figure 16):

- a dominant signal with pulse width t > t<sub>Filter</sub>

- a recessive signal with pulse width  $t > t_{Filter}$

- a dominant signal with pulse width t > t<sub>Filter</sub>

Figure 16 Wake-up pattern

Figure 17 WUP detection

The WUP bit in the register WAKE\_STAT indicates detection of a wake-up pattern on the HS CAN bus. If the transceiver is not in the Selective Sleep Sub-Mode AND if the transceiver detects a valid wake-up pattern, then the WUP bit is set. An SPI clear command resets the bit. A wake-up is not executed under the following conditions:

- A mode change to Normal-operating Mode is performed during the wake-up pattern.

- The maximum wake-up time  $t_{\text{WAKE}}$  expires before a valid WUP is detected.

- The transceiver is powered down ( $V_{CC} < V_{CC POD}$  AND  $V_{BAT} < V_{BAT POD}$ ).

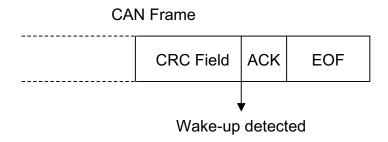

### 5.7.2 Wake-up frame (WUF)

If the selective wake unit is enabled (SWK\_EN =1), then the selective wake unit continuously monitors the HS CAN Bus for a valid wake-up frame. If a valid WUF is detected, then the WUF bit in the register WAKE\_STAT is set to "1". An SPI clear command resets the WUF bit. Chapter 7 describes the selective wake feature.

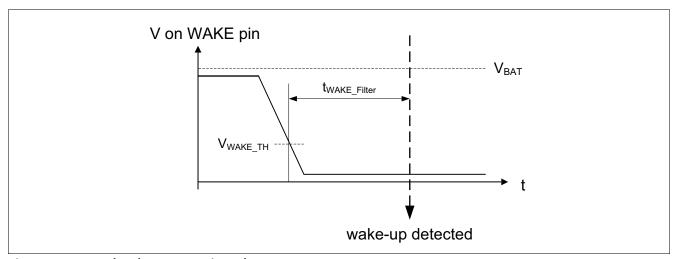

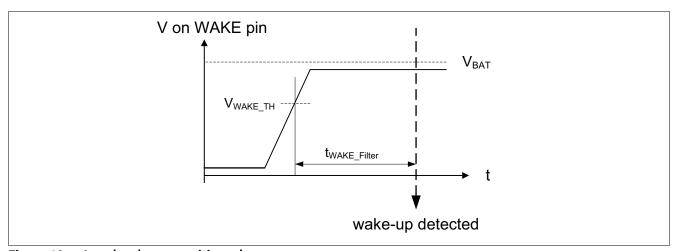

### 5.7.3 Local Wake-up (LWU)

The WAKE input pin can detect a rising edge as well as a falling edge as a wake-up event (configurable in LWU\_NEG, LWU\_POS). The LWU bit in the register WAKE\_STAT indicates that a local wake-up is detected on the local wake-up pin. The transceiver sets the LWU bit. An SPI command resets the LWU bit. The LWU\_DIR bit in the register WAKE\_STAT indicates on which edge a local wake-up has been detected. The transceiver sets the LWU\_DIR flag and it is only valid, if a local wake-up has been detected. Chapter 10.6.3 describes the local wake-up timing.

Figure 18 Local wake-up negative edge

Figure 19 Local wake-up positive edge

### 5.8 RxD pin wake-up behavior

The RxD output pin indicates a wake-up event to the microcontroller. On detection of a valid wake-up event the RxD output pin reacts with one of the following behaviors, depending on the WAKE\_TOG bit in the SPI register HW\_CTRL:

- RxD output pin is set to "low"

- RxD output pin starts to toggle

If Stand-by Mode is re-entered by a mode change (microcontroller) the previous indication of a valid wake-up event is not signalled on the RxD pin. Only if a new wake-up event has been detected, the RxD pin indicates the wake-up event. The clearing of a WUP, WUF or LWU has no influence on the behavior of the RxD pin.

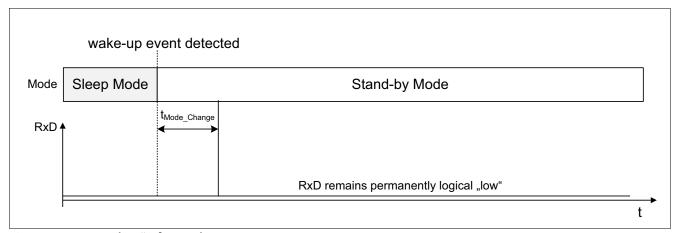

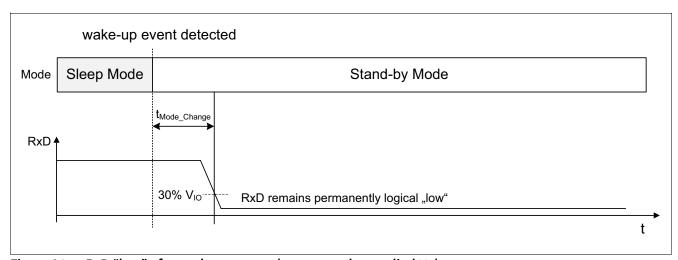

### 5.8.1 RxD permanent "low"

If a valid wake-up event is detected AND if SPI bit **WAKE\_TOG** = 0, then the RxD output pin is set to "low". If a mode change occurs, then the RxD output pin behavior is defined by the new state.

Figure 20 RxD "low" after wake-up event

Figure 21 RxD "low" after wake-up event (permanently supplied  $V_{10}$ )

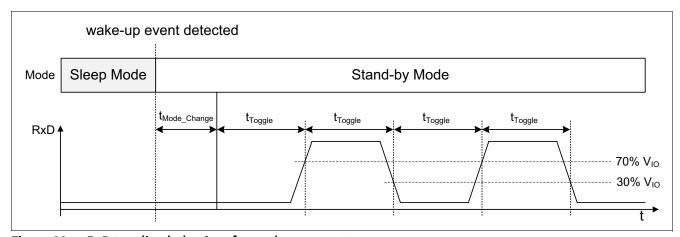

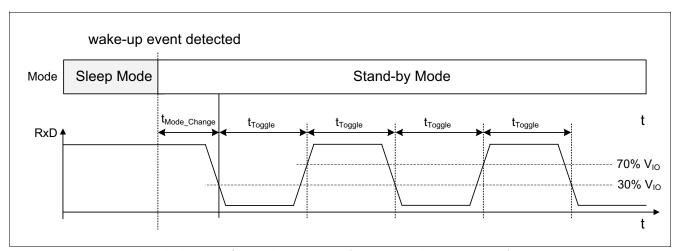

### 5.8.2 RxD Toggle

If WAKE\_TOG is set to 1 AND if a valid wake-up event is detected AND if  $V_{\rm IO}$  is within the functional range, then the RxD output pin starts to toggle from "low" to "high" and "high" to "low" with time period of  $t_{\rm Toggle}$ . Figure 22 and Figure 23 show this behavior. If a mode change occurs, then the RxD output pin behavior is defined by the new state.

Figure 22 RxD toggling behavior after wake-up event

Figure 23 RxD toggling behavior after wake-up event (permanently supplied  $V_{10}$ )

### 6 Fail Safe Functions

### 6.1 Short Circuit Protection

The CANH and CANL bus pins are proven to cope with a short circuit fault to GND and to the supply voltages. A current limiting circuit protects the transceiver from damage.

### 6.2 Undervoltage detection

The TLE9255W has independent undervoltage detection on  $V_{BAT}$ ,  $V_{CC}$  and  $V_{IO}$ . Undervoltage events at these pins may have impact on the functionality of the device and also may change the mode of operation.

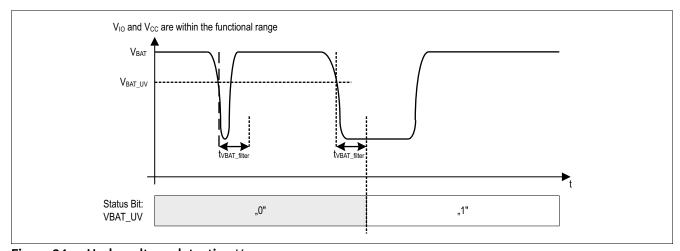

## 6.2.1 Undervoltage detection on $V_{BAT}$

If the power supply  $V_{\text{BAT}} < V_{\text{BAT\_UV}}$  for more than the glitch filter time  $t_{\text{VBAT\_filter}}$ , then an undervoltage is detected. On detection of undervoltage the TLE9255W performs the following actions:

- disable Local wake-up

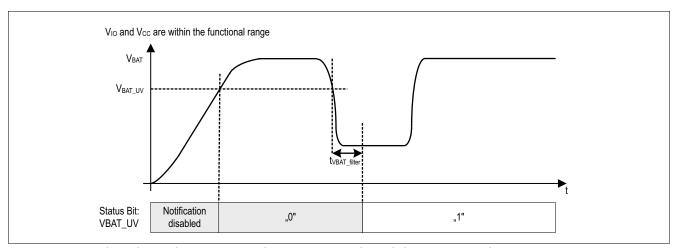

- Set the bit VBAT\_UV in the SPI register TRANS\_UV\_STAT to "1". After the completion of a Power on Reset or after a transition from Sleep Mode to Stand-by Mode the V<sub>BAT</sub> supply stabilization period must be completed before an undervoltage notification can be recorded in the VBAT\_UV bit. The undervoltage notification is only possible once the V<sub>BAT</sub> supply has exceeded the threshold V<sub>BAT\_UV</sub>, that is V<sub>BAT\_UV</sub>. Figure 25 shows this scenario.

Only an SPI command can reset the undervoltage bit VBAT\_UV (see Chapter 8.2). The glitch filter is implemented in order to prevent an undervoltage detection due to short voltage transients on  $V_{\text{BAT}}$ . Figure 24 shows the effect of glitch filter time in different undervoltage scenarios.

Figure 24 Undervoltage detection  $V_{BAT}$

Figure 25 Undervoltage detection  $V_{\rm BAT}$  during  $V_{\rm BAT}$  supply stabilization period

After power up the application can set the **VBAT\_CON** to "0" in the SPI Register **SUPPLY\_CTRL** in order to disable undervoltage detection.

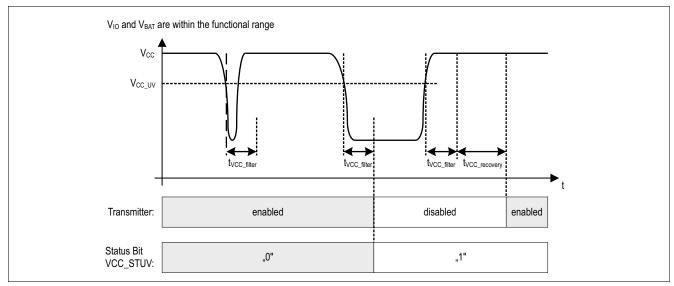

# 6.2.2 Short-term Undervoltage detection on $V_{CC}$

If the power supply  $V_{\rm CC} < V_{\rm CC\_UV}$  for more than the glitch filter time  $t_{\rm VCC\_filter}$ , then a short-term undervoltage on  $V_{\rm CC}$  is detected. The glitch filter prevents an undervoltage detection due to short voltage transients on  $V_{\rm CC}$ . On detection of short-term undervoltage the TLE9255W performs the following actions:

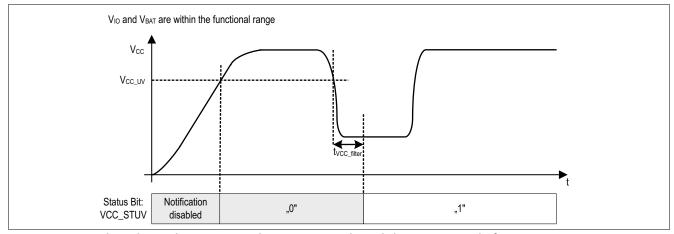

- Set short-term undervoltage bit VCC\_STUV to "1" in the SPI register TRANS\_UV\_STAT. Only after the completion of a Power on Reset, the V<sub>CC</sub> supply stabilization period must be completed before an undervoltage notification can be recorded in the VCC\_STUV bit. After Power on Reset the undervoltage notification is only possible once the V<sub>CC</sub> supply has exceeded the threshold V<sub>CC\_UV</sub>, that is V<sub>CC</sub> > V<sub>CC\_UV</sub>. Figure 27 shows this scenario.

- · disable the transmitter

An SPI command can reset the undervoltage bit VCC\_STUV. If  $V_{\rm CC} > V_{\rm CC\_UV}$  for more than the glitch filter time  $t_{\rm VCC\ filter}$  AND if the transmitter recovery time  $t_{\rm VCC\ recovery}$  has expired, then the transmitter is re-enabled.

Figure 26  $V_{CC}$  undervoltage detection

Figure 27 Undervoltage detection  $V_{CC}$  during  $V_{CC}$  supply stabilization period after Power on Reset

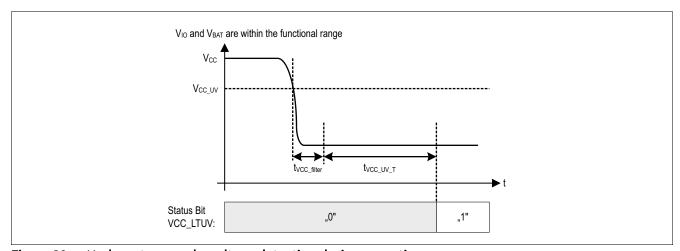

## 6.2.3 Long-term undervoltage detection on $V_{cc}$

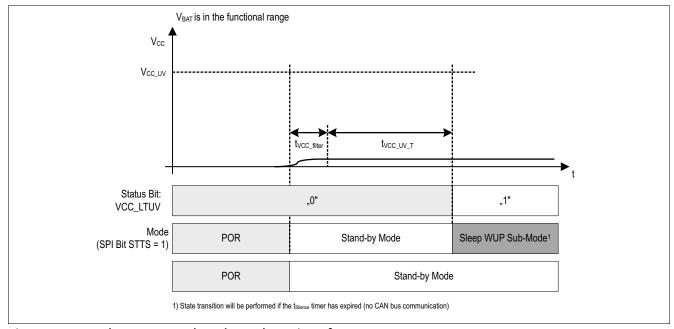

If  $V_{\text{CC}} < V_{\text{CC\_UV}}$  for more than the glitch filter time  $t_{\text{VCC\_filter}}$ , then the undervoltage detection timer is started. If  $t_{\text{VCC\_UV\_T}}$  has expired, then a long-term undervoltage is detected and the bit **VCC\_LTUV** is set to "1". Besides, if the SPI bit **STTS\_EN** = 1 (default value) AND if  $t_{\text{Silence}}$  has expired, then a state transition to Sleep WUP Sub-Mode is triggered. If  $V_{\text{CC}} > V_{\text{CC\_UV}}$  for more than the glitch filter time  $t_{\text{VCC\_filter}}$ , then the timer  $t_{\text{VCC\_UV\_T}}$  is stopped and reset. Only an SPI command can reset the undervoltage bit **VCC\_LTUV**. The  $t_{\text{VCC\_UV\_T}}$  can be configured in the SPI register **SUPPLY\_CTRL**.

Figure 28  $V_{cc}$  long-term undervoltage detection after power up

Figure 29  $V_{cc}$  long-term undervoltage detection during operation

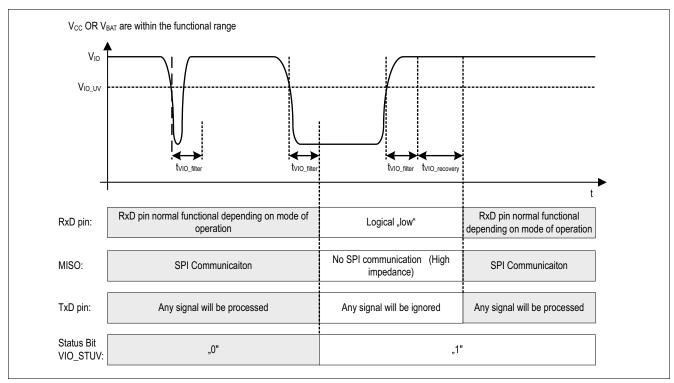

### 6.2.4 Short-term Undervoltage detection on $V_{10}$

If the power supply  $V_{\rm IO}$  <  $V_{\rm IO\_UV}$  for more than the glitch filter time  $t_{\rm VIO\_filter}$ , then short-term undervoltage on  $V_{\rm IO}$  is detected. The glitch filter prevents an undervoltage detection due to short voltage transients on  $V_{\rm IO}$ . On detection of short-term undervoltage the TLE9255W performs the following actions:

- Set the short-term undervoltage bit VIO\_STUV to "1" in the SPI register TRANS\_UV\_STAT. After the completion of a Power on Reset, the V<sub>IO</sub> supply stabilization period must be completed before an undervoltage notification can be recorded in the VIO\_STUV bit. After Power on Reset the undervoltage notification is only be possible once the V<sub>IO</sub> supply has exceeded the threshold V<sub>IO\_UV</sub>, that is V<sub>IO</sub> > V<sub>IO\_UV</sub>. Figure 31 shows this scenario.

- · set the RxD pin to "low"

- disable SPI communication by switching the MISO pin to high impedance

- TLE9255W ignores all signals on the input TxD pin

Only an SPI command can reset the undervoltage bit VIO\_STUV. If  $V_{IO}$  has recovered ( $V_{IO} > V_{IO\_UV}$ ) for more than the glitch filter time  $t_{VIO\_filter}$  AND if the  $t_{VIO\_recovery}$  time has expired, then the RxD pin returns to normal functionality depending on the mode of operation and the SPI communication is restored.

Figure 30  $V_{10}$  short-term undervoltage detection

Figure 31 Undervoltage detection  $V_{10}$  during  $V_{10}$  supply stabilization period after Power on Reset

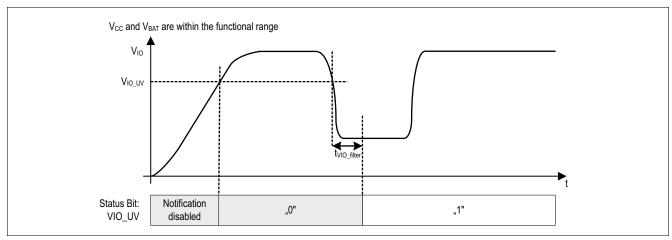

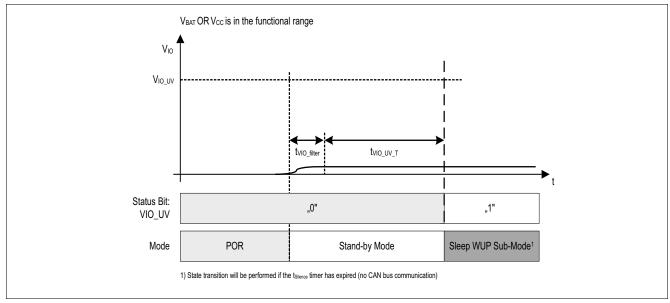

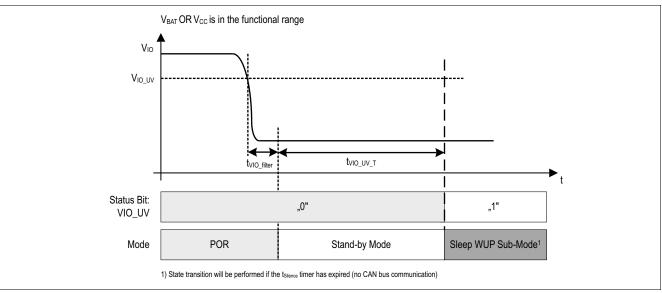

# 6.2.5 Long-term Undervoltage detection on $V_{10}$

If  $V_{\text{IO}} < V_{\text{IO}_{\text{UV}}}$  for more than the glitch filter time  $t_{\text{VIO}_{\text{filter}}}$ , then the undervoltage detection timer is started. If  $t_{\text{VIO}_{\text{UV}_{\text{T}}}}$  expires, then a long-term undervoltage is detected. On detection of long-term undervoltage the TLE9255W performs the following actions:

- set the bit VIO\_LTUV to "1"

- perform a mode change to Sleep WUP Sub-Mode only after  $t_{\text{Silence}}$  has expired (no bus communication)

If  $V_{\text{IO}} > V_{\text{IO}_{\text{UV}}}$  for more than the glitch filter time  $t_{\text{VIO}_{\text{filter}}}$ , then the timer  $t_{\text{VIO}_{\text{UV}_{\text{T}}}}$  is stopped and reset. Only an SPI command can reset the undervoltage bit  $\text{VIO}_{\text{LTUV}}$ . The  $t_{\text{VIO}_{\text{UV}_{\text{T}}}}$  is configurable in the SPI Register SUPPLY\_CTRL.

Figure 32  $V_{10}$  long-term undervoltage detection after power up

#### **Fail Safe Functions**

Figure 33  $V_{10}$  long-term undervoltage detection during operation

# 6.3 Unconnected Logic Pins

If the input pins are not connected and floating, the integrated pull-up and pull-down resistors at the digital input pins force the TLE9255W into fail safe behavior (see **Table 3**).

Table 3 Logical Inputs when unconnected

| Input Signal | Default State | Comment                                   |

|--------------|---------------|-------------------------------------------|

| TxD          | "high"        | pull-up current source to V <sub>IO</sub> |

| MOSI         | "low"         | pull-down current source to GND           |

| SCLK         | "low"         | pull-down current source to GND           |

| CSN          | "high"        | pull-up current source to V <sub>IO</sub> |

#### **Fail Safe Functions**

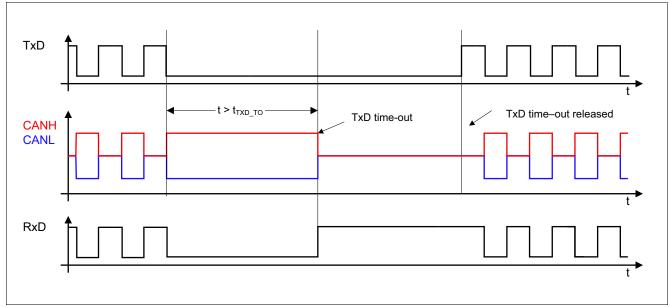

#### 6.4 TxD Time-out Function

If the logical signal on the TxD pin is permanently "low", then the TxD time-out feature protects the CAN bus from blocked communication due to this errant logic signal on TxD. A permanent "low" signal on the TxD pin can occur due to a locked-up microcontroller or in a short circuit on the printed circuit board, for example. In Normal-operating Mode, a "low" signal on the TxD pin for the time  $t > t_{TXD\_TO}$  enables the TxD time-out feature and the TLE9255W disables the transmitter (see Figure 34) and sets the TXD\_TO bit in the register TRANS\_STAT. The timer  $t_{TXD\_TO}$  is configurable in SPI register TXD\_TO\_CTRL. The receiver is still active and the RxD output pin continues monitoring data on the bus.

Figure 34 TxD time-out function

**Figure 34** shows how the transmitter is deactivated and re-activated. To release the transmitter after a TxD time-out event, the TLE9255W requires a signal change on the TxD input pin from "low" to "high".

#### **Fail Safe Functions**

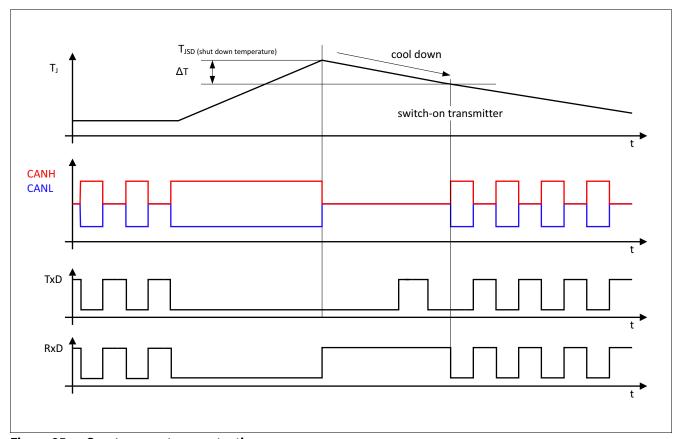

# 6.5 Overtemperature Protection

Integrated overtemperature detection protects the TLE9255W from thermal overstress of the transmitter. The overtemperature protection is active in Normal-operating Mode only. The temperature sensor provides the temperature threshold  $T_{\rm JSD}$ . If the junction temperature exceeds the upper threshold  $T_{\rm JSD}$ , then the TLE9255W disables the transmitter and sets the bit TSD, indicating that a critical temperature situation is reached. After the device cools down the transmitter is re-enabled. Only an SPI command can reset the TSD bit. A hysteresis is implemented within the temperature sensor.

Figure 35 Overtemperature protection

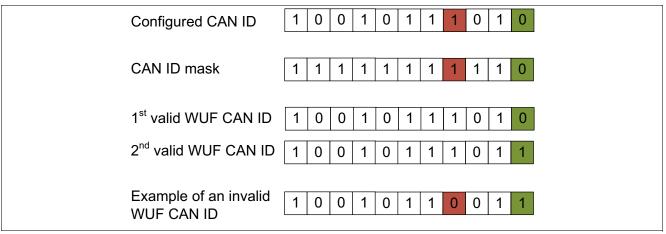

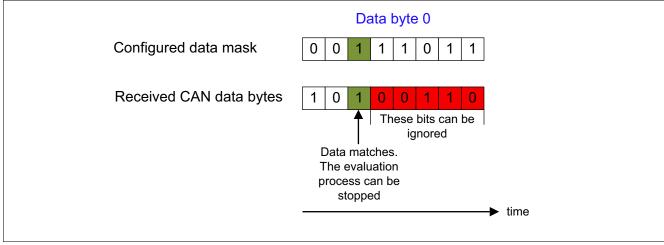

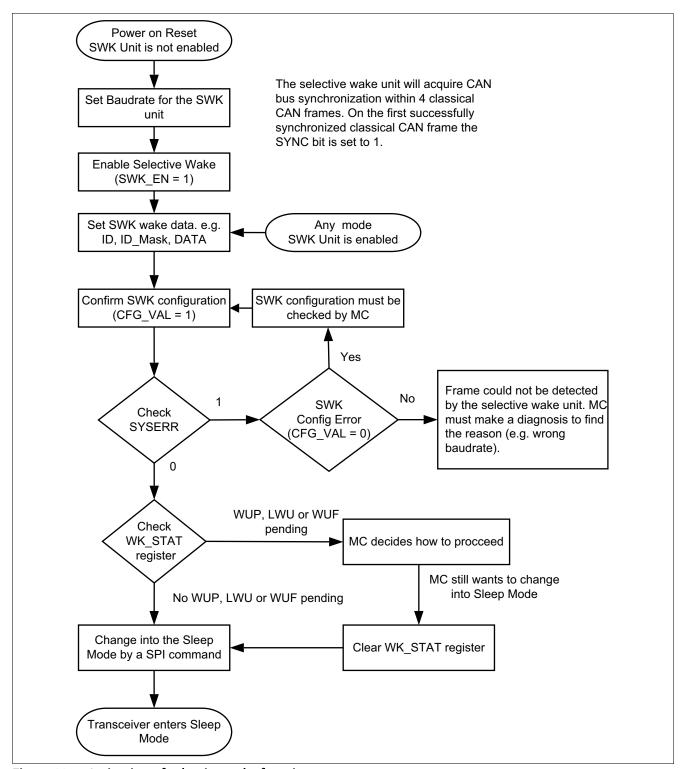

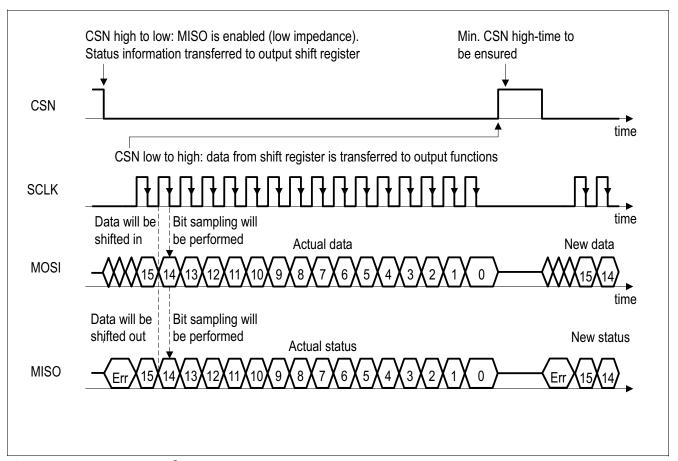

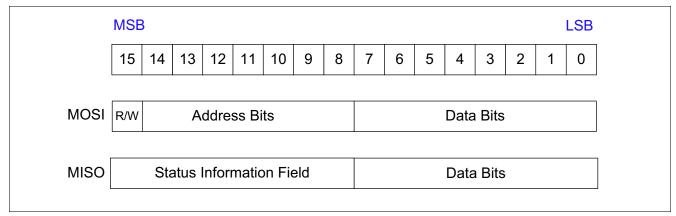

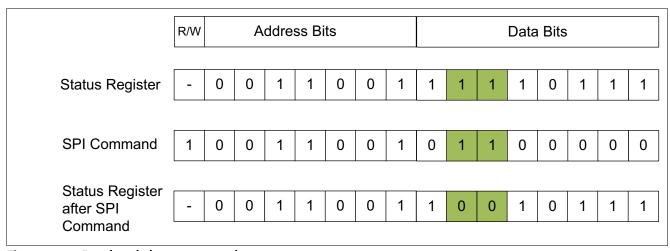

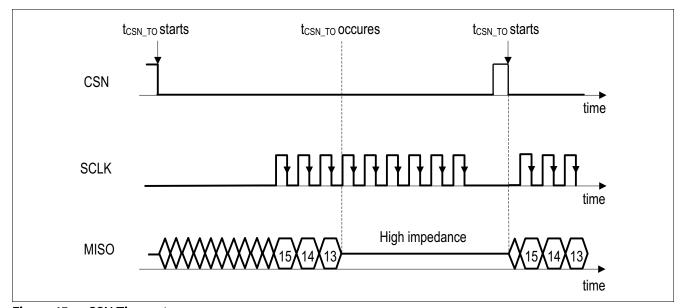

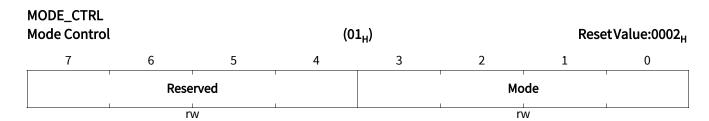

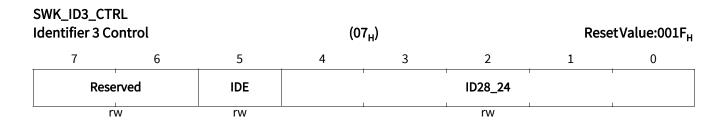

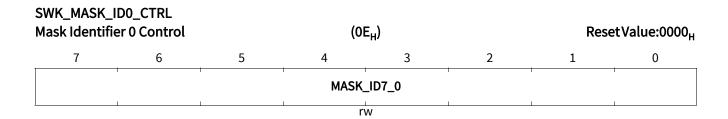

# 6.6 Delay Time for Mode Change