# AN-2250 LM3533 Evaluation Kit

#### 1 Introduction

The LM3533 Evaluation Module (LM3533EVM) is designed to fully evaluate the LM3533 Dual String backlight driver + 5 indicator LED driver. The LM3533EVM consists of the USB Interface Board and the LM3533 Evaluation Board. The USB Interface Board Rev 1.1 provides the hardware link between a PC and LM3533 Evaluation Board. On the PC side, the LM3533.exe software communicates to the LM3533EVM to provide an easy control over all the features of the LM3533. Both the USB Interface Board and the LM3533 Evaluation Board plug together at the USBL and USBR connectors and are keyed so the boards can only fit together one way.

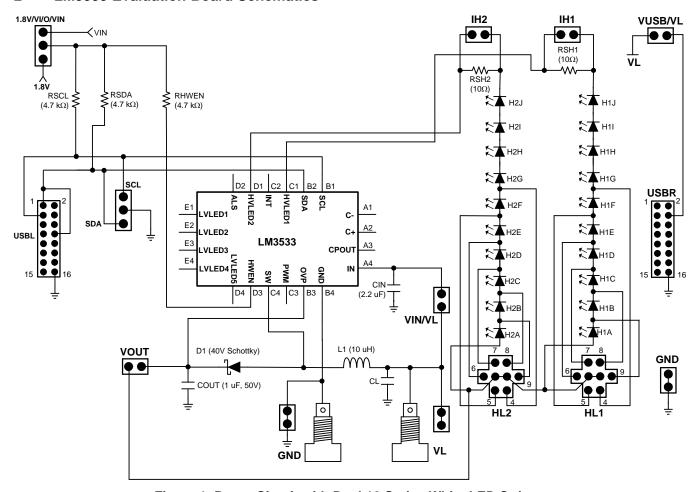

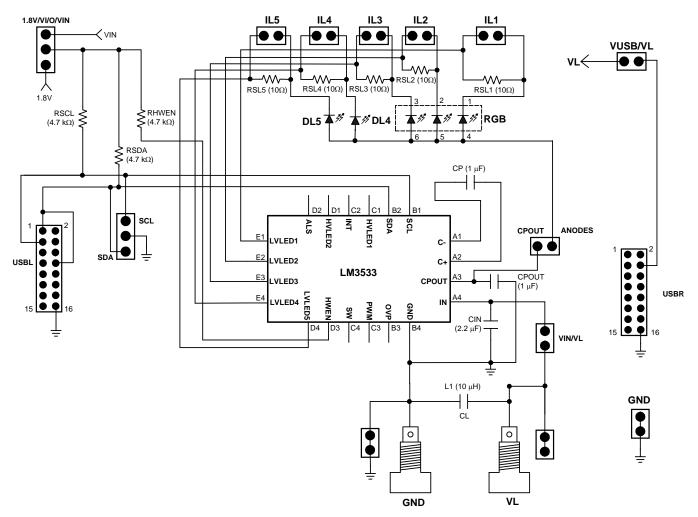

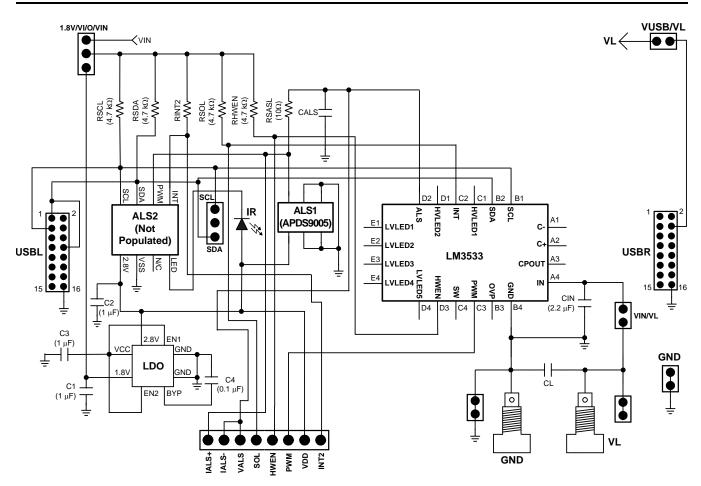

#### 2 LM3533 Evaluation Board Schematics

Figure 1. Boost Circuit with Dual 10 Series White LED Strings

All trademarks are the property of their respective owners.

Figure 2. Charge Pump and Low Voltage Indicator LEDs

Figure 3. Ambient Light Sensor and Logic Pull-ups

Bill of Materials www.ti.com

## 3 Bill of Materials

| Component<br>Symbol | Value                                                             | Manufacturer         | Part #              | Size/Package<br>(L x W x H)    |

|---------------------|-------------------------------------------------------------------|----------------------|---------------------|--------------------------------|

| LM3533              | LED Driver                                                        | Texas<br>Instruments | LM3533              | (2.015mm × 1.755mm x<br>0.6mm) |

| LDO                 | 1.8V/2.8V dual linear regulator                                   | Texas<br>Instruments | LP3986              | (1.55mm x 1.55mm x 0.6mm)      |

| RGB                 | RGB Indicator LEDs                                                | Kingbright           | APF3236SURKZGQBDC   | (3.6mm x 3.2mm x 1.1mm)        |

| DL4, DL5            | Red Indicator LED                                                 | Rohm                 | SML-310VTT86        | 0603                           |

| L1                  | 10 $\mu$ H, I <sub>SAT</sub> = 1A, R <sub>L</sub> = 0.22 $\Omega$ | TDK                  | VLF4014ST-100M1R0   | (3.8mm x 3.6mmx 1.4mm)         |

| CIN                 | 2.2µF, 10V, X5R                                                   | TDK                  | C1005X5R1A225M      | 0402                           |

| COUT                | 1μF, 50V, X7R                                                     | TDK                  | C3216X7R1H105M      | 0805                           |

| CPOUT               | 1μF, 10V, X5R                                                     | TDK                  | C1005X5R1A105K      | 0402                           |

| СР                  | 1μF, 10V, X5R                                                     | TDK                  | C1005X5R1A105K      | 0402                           |

| CL                  | 10μF, 10V                                                         | TDK                  | C1608X5R1A106K      | 0603                           |

| C1 - C4             | 1μF, 10V, X5R                                                     | TDK                  | C1005X5R1A105K      | 0402                           |

| D1                  | Schottky, 40V, 250mA                                              | On-Semi              | NSR0240V2T1GOSCT-ND | SOD-523                        |

| H1A - H1J           | White LED                                                         | Rohm                 | SML312WBCW1         | 0603                           |

| H2A - H2J           | White LED                                                         | Rohm                 | SML312WBCW1         | 0603                           |

| ALS1                | Ambient Light Sensor                                              | Avago                | APDS-9005-020       | (1.6mm x 1.5mm x 0.55mm)       |

| ALS2                | Ambient Light Sensor                                              | N/A                  | N/A                 | N/A                            |

| RHWEN               | 4.7kΩ                                                             | Vishay               | CRCW06034K70JNEA    | 0603                           |

| RSDA                | 4.7kΩ                                                             | Vishay               | CRCW06034K70JNEA    | 0603                           |

| RSCL                | 44.7kΩ                                                            | Vishay               | CRCW06034K70JNEA    | 0603                           |

| RSOL                | 4.7kΩ                                                             | Vishay               | CRCW06034K70JNEA    | 0603                           |

| RSASL               | 10Ω, 1%                                                           | Panasonic            | ERJ-3EKF10R0V       | 0603                           |

| RSH1, RSH2          | 10Ω, 0.01%                                                        | Bourns               | CRT0805-BY-10R0ELF  | 0805                           |

| RSL1 - RSL5         | 10Ω, 0.01%                                                        | Bourns               | CRT0805-BY-10R0ELF  | 0805                           |

www.ti.com Board Layout

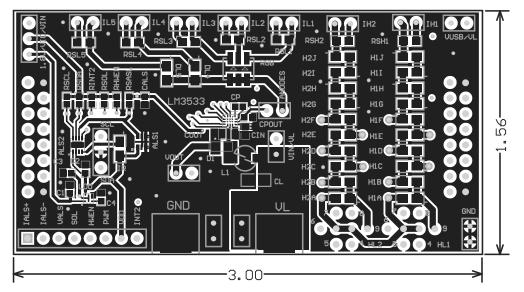

# 4 Board Layout

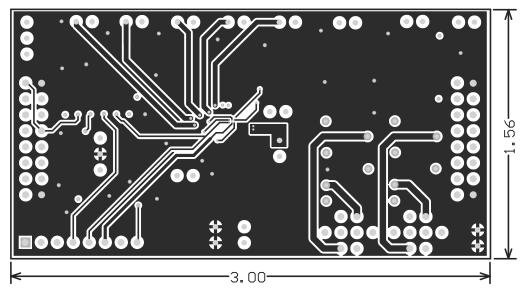

Figure 4. Top Layer

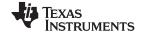

Figure 5. Mid Layer 1

Board Layout www.ti.com

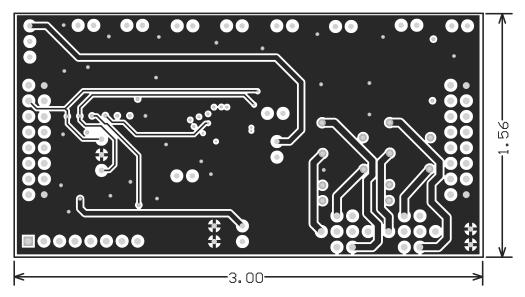

Figure 6. Mid Layer 2

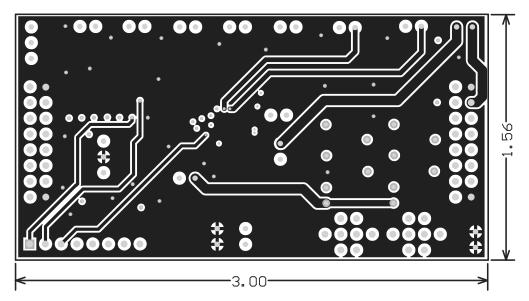

Figure 7. Bottom Layer

www.ti.com Board Set-Up

#### 5 Board Set-Up

The LM3533EVM requires jumpers installed at the following headers for proper operation:

- 1.8V/VIO/VIN: The center pin (VIO) of this three position header connects to the top side of the pull-up resistors (RSCL, RSDA, RSOL, and RHWEN). Jumper this pin to either the 1.8V output from the on board LDO or to VIN.

- 2. **VOUT:** The VOUT header connects the LM3533's boost output to the top side of the high voltage LED strings (HL1 and HL2)

- 3. VIN/VL: This header jumpers the voltage at VL to the LM3533's IN bump (VIN)

- 4. **ANODES:** This header jumpers the LM3533's charge pump output to the top side of the low voltage indicator LEDs (RGB, DL4, and DL5)

Once the jumpers are installed, connect a 2.5V to 5.5V power supply to the banana plug inputs (VL) and (GND).

#### 6 USB Interface Board

The LM3533 Evaluation Board can be controlled via an I<sup>2</sup>C master by connecting directly to the I<sup>2</sup>C header (SCL SDA) or it can be controlled with the USB Interface Board. The USB Interface Board requires the use of the LM3533.exe software that operates from a PC.

To operate the LM3533 Evaluation Board with the USB Interface Board, ensure the LM3533 Evaluation Board is connected to the USB Interface Board. The boards are keyed so they will only fit together one way. Next, follow the jumper settings in Section 5. After this, apply power to the board and open the LM3533.exe program. The LM3533.exe software is grouped into tabs, see the following sections for each tab description.

#### 7 LM3533 Graphical User Interface

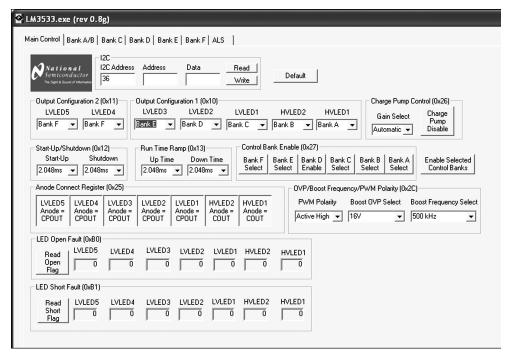

Figure 8. Main Control Tab

#### 7.1 Main Control Tab

The Main Control tab (Figure 8) contains the pulldown menu's and buttons for configuring the LM3533's global registers. The main tab is separated into different sections, where each section represents a specific register within the LM3533. When any of the pulldown menus or buttons are selected the specific data will get written to the LM3533. The exception is for the Control Bank Enable Buttons. These must first be selected and then the Enable Selected Control Banks button must be pressed to write the data. A button that is pushed indicates a 1 is written to the register. A button un-pushed indicates a 0. Table 1 through Table 10 show the break down of each register in the Main Control Tab.

Table 1. Output Configuration 1 (0x10)

| Bit [7:6]<br>LVLED3                                         | Bits [5:4]<br>LVLED2                                  | Bits [3:2]<br>LVLED1                                  | Bit [1]<br>HVLED2                                          | Bit 0<br>HVLED1                                            |

|-------------------------------------------------------------|-------------------------------------------------------|-------------------------------------------------------|------------------------------------------------------------|------------------------------------------------------------|

| 00 = LVLED3 is<br>controlled by Control<br>Bank C           | 00 = LVLED2 is<br>controlled by Control<br>Bank C     | 00 = LVLED1 is controlled by Control Bank C (Default) | 0 = HVLED2 is<br>controlled by Control<br>Bank A           | 0 = HVLED1 is<br>controlled by Control<br>Bank A (Default) |

| 01 = LVLED3 is<br>controlled by Control<br>Bank D           | 01 = LVLED2 is controlled by Control Bank D (Default) | 01 = LVLED1 is controlled by Control Bank D           | 1 = HVLED2 is<br>controlled by Control<br>Bank B (Default) | 1 = HVLED1 is<br>controlled by Control<br>Bank B           |

| 10 = LVLED3 is<br>controlled by Control<br>Bank E (Default) | 10 = LVLED2 is<br>controlled by Control<br>Bank E     | 10 = LVLED1 is controlled<br>by Control Bank E        |                                                            |                                                            |

| 11 = LVLED3 is<br>controlled by Control<br>Bank F           | 11 = LVLED2 is<br>controlled by Control<br>Bank F     | 11 = LVLED1 is controlled<br>by Control Bank F        |                                                            |                                                            |

### Table 2. Output Configuration 2 (0x11)

| Bits [3:2]<br>LVLED5                                  | Bits [1:0]<br>LVLED4                                  |

|-------------------------------------------------------|-------------------------------------------------------|

| 00 = LVLED5 is controlled by Control Bank C           | 00 = LVLED4 is controlled by Control Bank C           |

| 01 = LVLED5 is controlled by Control Bank D           | 01 = LVLED4 is controlled by Control Bank D           |

| 10 = LVLED5 is controlled by Control Bank E           | 10 = LVLED4 is controlled by Control Bank E           |

| 11 = LVLED5 is controlled by Control Bank F (Default) | 11 = LVLED4 is controlled by Control Bank F (Default) |

Table 3. Charge Pump Control (0x26)

| Bits [2:1]                                                                            | Bit 0                                                                                                 |

|---------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------|

| Gain Select                                                                           | Charge Pump Disable                                                                                   |

| 0X = Automatic gain select ( <b>Default</b> ) 10 = Gain set at 1x 11 = Gain set at 2x | 0 = Charge pump enabled ( <b>Default</b> ) 1 = Charge pump disabled (high impedance from IN to CPOUT) |

Table 4. Start-Up/Shutdown (0x12)

| Bits [5:3]<br>Start-up Transition Time                                       | Bits [2:0]<br>Shutdown Transition Time                     |

|------------------------------------------------------------------------------|------------------------------------------------------------|

| 000 = 2.048ms (Default)                                                      | 000 = 2.048ms ( <b>Default</b> )                           |

| 001 = 262ms                                                                  | 001 = 262ms                                                |

| 010 = 524ms                                                                  | 010 = 524ms                                                |

| 011 = 1.049s                                                                 | 011 = 1.049s                                               |

| 100 = 2.097s                                                                 | 100 = 2.097s                                               |

| 101 = 4.194s                                                                 | 101 = 4.194s                                               |

| 110 = 8.389s                                                                 | 110 = 8.389s                                               |

| 111 = 16.78s                                                                 | 111 = 16.78s                                               |

| Startup time is from when the device is enabled via I <sup>2</sup> C to when | Shutdown ramp time is from when the device is shutdown via |

| the initial target current is reached.                                       | I <sup>2</sup> C until the current sink ramps to 0.        |

## Table 5. Run Time Ramp (0x13)

| Bits [5:3]<br>Transition Time Ramp Up | Bits [2:0]<br>Transition Time Ramp Down |

|---------------------------------------|-----------------------------------------|

| 000 = 2048μs ( <b>Default</b> )       | 000 = 2048μs <b>(Default)</b>           |

| 001 = 262ms                           | 001 = 262ms                             |

| 010 = 524ms                           | 010 = 524ms                             |

| 011 = 1.049s                          | 011 = 1.049s                            |

| 100 =2.097s                           | 100 =2.097s                             |

| 101 = 4.194s                          | 101 = 4.194s                            |

| 110 = 8.389s                          | 110 = 8.389s                            |

| 111 = 16.78s                          | 111 = 16.78s                            |

#### Table 6. Control Bank Enable (0x27)

| Bit 5<br>Control F Select                | Bit 4<br>Control E Select                | Bit 3<br>Control D Select                | Bit 2<br>Control C Select                | Bit 1<br>Control B Select                         | Bit 0<br>Control A Select                |

|------------------------------------------|------------------------------------------|------------------------------------------|------------------------------------------|---------------------------------------------------|------------------------------------------|

| 0 = Control Bank F is disabled (Default) | 0 = Control Bank E is disabled (Default) | 0 = Control Bank D is disabled (Default) | 0 = Control Bank C is disabled (Default) | 0 = Control Bank B is disabled ( <b>Default</b> ) | 0 = Control Bank A is disabled (Default) |

| 1 = Control Bank F is enabled            | 1 = Control Bank E is enabled            | 1 = Control Bank D is enabled            | 1 = Control Bank C is enabled            | 1 = Control Bank B is enabled                     | 1 = Control Bank A is enabled            |

## Table 7. Anode Connect (0x25)

| Bit 6<br>LVLED5 Anode<br>Connect                              | Bit 5<br>LVLED4 Anode<br>Connect                              | Bit 4<br>LVLED3 Anode<br>Connect                              | Bit 3<br>LVLED2 Anode<br>Connect                                 | Bit 2<br>LVLED1 Anode<br>Connect                              | Bit 1<br>HVLED2<br>Anode<br>Connect                                       | Bit 0<br>HVLED1<br>Anode<br>Connect                                       |

|---------------------------------------------------------------|---------------------------------------------------------------|---------------------------------------------------------------|------------------------------------------------------------------|---------------------------------------------------------------|---------------------------------------------------------------------------|---------------------------------------------------------------------------|

| 0 = LVLED5 LED<br>anode is not<br>connected to<br>CPOUT       | 0 = LVLED4 LED<br>anode is not<br>connected to<br>CPOUT       | 0 = LVLED3 LED<br>anode is not<br>connected to<br>CPOUT       | 0 = LVLED2<br>LED anode is<br>not connected to<br>CPOUT          | 0 = LVLED1 LED<br>anode is not<br>connected to<br>CPOUT       | 0 = HVLED2<br>LED string<br>anode is not<br>connected to<br>COUT          | 0 = HVLED1<br>LED string<br>anode is not<br>connected to<br>COUT          |

| 1 = LVLED5 LED<br>anode is<br>connected to<br>CPOUT (Default) | 1 = LVLED4 LED<br>anode is<br>connected to<br>CPOUT (Default) | 1 = LVLED3 LED<br>anode is<br>connected to<br>CPOUT (Default) | 1 = LVLED2<br>LED anode is<br>connected to<br>CPOUT<br>(Default) | 1 = LVLED1 LED<br>anode is<br>connected to<br>CPOUT (Default) | 1 = HVLED2<br>LED string<br>anode is<br>connected to<br>COUT<br>(Default) | 1 = HVLED1<br>LED string<br>anode is<br>connected to<br>COUT<br>(Default) |

## Table 8. OVP/Boost Frequency/PWM Polarity (0x2C)

| Bit 3                                                         | Bit [2:1]                                                     | Bit 1                                    |

|---------------------------------------------------------------|---------------------------------------------------------------|------------------------------------------|

| PWM Polarity                                                  | Boost OVP Select                                              | Boost Frequency Select                   |

| 0 = Active Low Polarity<br>1 = Active High Polarity (Default) | 00 = 16V <b>(Default)</b><br>01 = 24V<br>10 = 32V<br>11 = 40V | 0 = 500 kHz <b>(Default)</b><br>1 = 1MHz |

## Table 9. LED Open Fault (0xB0)

| Bit 6      | Bit 5      | Bit 4      | Bit 3      | Bit 2      | Bit 1      | Bit 0      |

|------------|------------|------------|------------|------------|------------|------------|

| (LVLED5)   | (LVLED4)   | (LVLED3)   | (LVLED2)   | (LVLED1 )  | (HVLED2)   | (HVLED1 )  |

| 0 = Normal |

| Operation  |

| 1 = Open   |

# Table 10. LED Short Fault (0xB1)

| Bit 6<br>(LVLED5) | Bit 5<br>(LVLED4) | Bit 4<br>(LVLED3) | Bit 3<br>(LVLED2) | Bit 2<br>(LVLED1 ) | Bit 1<br>(HVLED2) | Bit 0<br>(HVLED1 ) |

|-------------------|-------------------|-------------------|-------------------|--------------------|-------------------|--------------------|

| 0 = Normal         | 0 = Normal        | 0 = Normal         |

| Operation         | Operation         | Operation         | Operation         | Operation          | Operation         | Operation          |

| 1 = Short          | 1 = Short         | 1 = Short          |

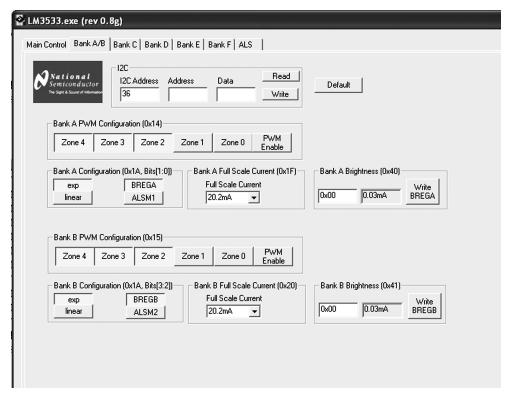

#### 7.2 Bank A/B Control Tab

The Bank A/B Control Tab (Figure 9) contains all the register options that are unique to the High Voltage Control Banks (A and B). Table 11 through Table 15 describe these registers.

Figure 9. Bank A/B Control Tab

Table 11. Bank A or Bank B PWM Configuration (0x14, 0x15)

| Bit 5<br>Zone 4 PWM<br>Enabled                     | Bit 4<br>Zone 3 PWM<br>Enabled                     | Bit 3<br>Zone 2 PWM<br>Enabled                     | Bit 2<br>Zone 1 PWM<br>Enabled                      | Bit 1<br>Zone 0 PWM Enabled                   | Bit 0<br>PWM Enabled                         |

|----------------------------------------------------|----------------------------------------------------|----------------------------------------------------|-----------------------------------------------------|-----------------------------------------------|----------------------------------------------|

| 0 = PWM input is disabled in Zone 4                | 0 = PWM input is disabled in Zone 3                | 0 = PWM input is disabled in Zone 2                | 0 = PWM input is<br>disabled in Zone 1<br>(Default) | 0 = PWM input is disabled in Zone 0 (Default) | 0 = PWM Input is disabled ( <b>Default</b> ) |

| 1 = PWM input is<br>enabled in Zone 4<br>(Default) | 1 = PWM input is<br>enabled in Zone 3<br>(Default) | 1 = PWM input is<br>enabled in Zone 2<br>(Default) | 1 = PWM input is<br>enabled in Zone 1               | 1 = PWM input is<br>enabled in Zone 0         | 1 = PWM Input is enabled                     |

Table 12. Bank A Configuration (0x1A, Bits[1:0])

| Bit 1<br>Control Bank A Mapping Mode | Bit 0<br>BREGA/ALSM1 Control                                                                 |  |

|--------------------------------------|----------------------------------------------------------------------------------------------|--|

| 0 = Exponential Mapping (Default)    | 0 = Control Bank A is configured for Brightness Register Current Control (Default)           |  |

| 1 = Linear Mapping                   | 1 = Control Bank A is configured for ALS current control via the ALSM1 Zone Target Registers |  |

# Table 13. Bank A or Bank B Full Scale Current (0x1F, 0x20)

| Bits [4:0]<br>Full-Scale Current (800μA per setting) |  |  |  |

|------------------------------------------------------|--|--|--|

| 00000 = 5mA                                          |  |  |  |

| :                                                    |  |  |  |

| :                                                    |  |  |  |

| 10011 = 20.2mA ( <b>Default</b> )                    |  |  |  |

| :                                                    |  |  |  |

| :                                                    |  |  |  |

| 11111 = 29.8mA                                       |  |  |  |

#### Table 14. Bank B Configuration (0x1A, Bits[3:2])

| Bit 3<br>Control Bank B Mapping Mode       | Bit 2<br>BREGB/ALSM2 Control                                                                 |  |

|--------------------------------------------|----------------------------------------------------------------------------------------------|--|

| 0 = Exponential Mapping ( <b>Default</b> ) | 0 = Control Bank B is configured for Brightness Register Current Control (Default)           |  |

| 1 = Linear Mapping                         | 1 = Control Bank B is configured for ALS current control via the ALSM2 Zone Target Registers |  |

#### Table 15. Bank A and Bank B Brightness (0x40, 0x41)

#### Brightness Code Bits[7:0}

When the Mapping Mode is set for exponential mapping (Control Bank X Brightness Configuration Register, Bit [2] = 0), the current approximates the equation:

$$I_{LED} = I_{LED\_FULLSCALE} \times \frac{1}{255} \times Code$$

(1)

When the Mapping Mode is set for linear mapping (Control Bank X Brightness Configuration Register, Bit [2] = 1), the current approximates the equation:

$$I_{LED} = I_{LED\_FULLSCALE} \times 0.85^{\left[40 \cdot \left(\frac{\text{Code} + 1}{6.4}\right)\right]}$$

(2)

#### 7.3 Bank C, D, E, and F Tab

Each low voltage Control Bank (C, D, E, and F) has its own tab. Each tab has all the register options that are unique to each of the low voltage control banks and the pattern generators. Table 16 through Table 24 describe these registers.

Figure 10. Low Voltage Control Bank Tab

Table 16. Bank (C/D/E/F) Configuration (0x1B, 0x1C, 0x1D, 0x1E), Bits[2:0]

| Bit 2<br>Mapping Mode                      | Bits [1:0]<br>Current Control                                                                                                      |

|--------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------|

| 0 = Exponential Mapping ( <b>Default</b> ) | 0X = Control Bank_ is configured for Brightness Register Current Control via the respective Brightness Register ( <b>Default</b> ) |

| 1 = Linear Mapping                         | 10 = Control Bank_ is configured for ALS current control via the ALSM2 Zone Target Registers                                       |

|                                            | 11 = Control Bank_ is configured for ALS current control via the ALSM3 Zone Target Registers                                       |

#### Table 17. Bank C/D/E/F High Brightness (0x42, 0x43, 0x44, 0x45)

#### Brightness Code Bits[7:0]

When the Mapping Mode is set for exponential mapping (Control Bank\_Brightness Configuration Register Bit [2] = 0), the current approximates the equation:

$$I_{LED} = I_{LED\_FULLSCALE} \times \frac{1}{255} \times Code$$

(3)

When the Mapping Mode is set for linear mapping (Control Bank\_Brightness Configuration Register Bit [2] = 1), the current approximates the equation:

$$I_{LED} = I_{LED\_FULLSCALE} \times 0.85^{\left[40 \cdot \left(\frac{\text{Code + 1}}{6.4}\right)\right]}$$

(4)

Table 18. Bank (C/D/E/F) Full Scale Current (0x21, 0x22, 0x23, 0x24)

| Bits [4:0]<br>Full-Scale Current (800μA per setting) |  |  |

|------------------------------------------------------|--|--|

| 00000 = 5mA                                          |  |  |

| :                                                    |  |  |

| :                                                    |  |  |

| 10011 = 20.2mA ( <b>Default</b> )                    |  |  |

| :                                                    |  |  |

| :                                                    |  |  |

| 11111 = 29.8mA                                       |  |  |

Table 19. Bank (C/D/E/F) PWM Configuration (0x16, 0x17, 0x18, 0x19)

| Bit 5<br>Zone 4                                    | Bit 4<br>Zone 3                                    | Bit 3<br>Zone 2                                    | Bit 2<br>Zone 1                               | Bit 1<br>Zone 0                               | Bit 0<br>PWM Enabled                         |

|----------------------------------------------------|----------------------------------------------------|----------------------------------------------------|-----------------------------------------------|-----------------------------------------------|----------------------------------------------|

| 0 = PWM input is disabled in Zone 4                | 0 = PWM input is disabled in Zone 3                | 0 = PWM input is disabled in Zone 2                | 0 = PWM input is disabled in Zone 1 (Default) | 0 = PWM input is disabled in Zone 0 (Default) | 0 = PWM Input is disabled ( <b>Default</b> ) |

| 1 = PWM input is<br>enabled in Zone 4<br>(Default) | 1 = PWM input is<br>enabled in Zone 3<br>(Default) | 1 = PWM input is<br>enabled in Zone 2<br>(Default) | 1 = PWM input is<br>enabled in Zone 1         | 1 = PWM input is<br>enabled in Zone 0         | 1 = PWM Input is enabled                     |

The PGEN Enable field in the low voltage control bank tabs is mirrored for each tab. Once a check box is selected, the Enable Selected Patterns button must be pushed to write the specific bit to register 0x28. A checked box means a 1 is being written and an empty box means a 0 is bing written.

Table 20. PGEN Enable (0X28, Bits[0, 2, 4, 6])

| Bit 6<br>Pattern 4<br>Enable     | Bit 4<br>Pattern 3<br>Enable     | Bit 2<br>Pattern 2<br>Enable     | Bit 0<br>Pattern 1<br>Enable     |

|----------------------------------|----------------------------------|----------------------------------|----------------------------------|

| 0 = Pattern 4 Disabled (Default) | 0 = Pattern 3 Disabled (Default) | 0 = Pattern 2 Disabled (Default) | 0 = Pattern 1 Disabled (Default) |

| 1 = Pattern 4 Enabled            | 1 = Pattern 3 Enabled            | 1 = Pattern 2 Enabled            | 1 = Pattern 1 Enabled            |

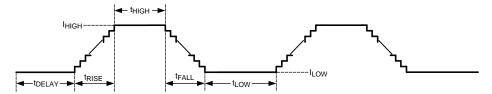

Each low voltage control bank has its own pattern generator control. Bank C has Pattern Generator 1, Bank D has Pattern Generator 2, Bank E has Pattern Generator 3, and Bank F has Pattern Generator 4. Each pattern generator has registers that control the pulse high time, pulse low time, pulse rise time, pulse fall time, pulse delay from when the pattern is enabled, and the pulse low brightness. The pulse high brightness is the same as the high brightness register for the particular Control Bank.

Figure 11. Pattern Generator Timing

Table 21. Low Time(s) (0x71, 0x81, 0x91, 0xA1)

| Bit [7:0] t <sub>Low</sub> times                   |

|----------------------------------------------------|

| 0x00 = 16.384ms (16.384ms/step) ( <b>Default</b> ) |

| 0x01 = 32.768ms                                    |

| :                                                  |

| 0x3B = 983.05ms                                    |

| 0x3C = 999.424ms                                   |

| 0x3D = 1130.496ms (131.072ms/step)                 |

| 0x3E = 1261.568ms                                  |

| :                                                  |

| 0x7F = 9781.248ms                                  |

| 0x80 = 10.305536s (524.288ms/step)                 |

| :                                                  |

| 0xFF = 76.890112s                                  |

Table 22. High Time(s) (0x72, 0x82, 0x92, 0xA2)

| Bit [6:0]<br>t <sub>HIGH</sub> times               |

|----------------------------------------------------|

| 0x00 = 16.384ms (16.384ms/step) ( <b>Default</b> ) |

| 0x01 = 32.768ms                                    |

| :                                                  |

| 0x3B = 983.05ms                                    |

| 0x3C = 999.424ms                                   |

| 0x3D = 1130.496ms (131.072ms/step)                 |

| 0x3E = 1261.568ms                                  |

| :                                                  |

| 0x7F = 9781.248ms                                  |

For Exponential Mapping Mode the low-level current becomes:

$$I_{LED} = I_{LED\_FULLSCALE} \times \frac{1}{255} \times Code$$

(5)

For Linear Mapping Mode the low-level current becomes:

$$I_{LED} = I_{LED\_FULLSCALE} \times 0.85^{\left[40 - \left(\frac{\text{Code } + 1}{6.4}\right)\right]}$$

(6)

## 7.4 LOW BRIGHTNESS (0x73, 0x83, 0x93, 0xA3)

Table 23. Rise Time (0x74, 0x84, 0x94, 0xA4)

| Bits [2:0]<br>t <sub>RISE</sub> (from I <sub>LOW</sub> to I <sub>HIGH</sub> ) |  |  |  |

|-------------------------------------------------------------------------------|--|--|--|

| 000 = 2048μs <b>(Default)</b>                                                 |  |  |  |

| 001 = 262ms                                                                   |  |  |  |

| 010 = 524ms                                                                   |  |  |  |

| 011 = 1.049s                                                                  |  |  |  |

| 100 = 2.097s                                                                  |  |  |  |

| 101 = 4.194s                                                                  |  |  |  |

| 110 = 8.389s                                                                  |  |  |  |

| 111 = 16.78s                                                                  |  |  |  |

Table 24. Fall Time (0x75, 0x85, 0x95, 0xA5)

| Bits [2:0]<br>t <sub>FALL</sub> (from I <sub>HIGH</sub> to I <sub>LOW</sub> ) |  |  |  |

|-------------------------------------------------------------------------------|--|--|--|

| 000 = 2048μs <b>(Default)</b>                                                 |  |  |  |

| 001 = 262ms                                                                   |  |  |  |

| 010 = 524ms                                                                   |  |  |  |

| 011 = 1.049s                                                                  |  |  |  |

| 100 = 2.097s                                                                  |  |  |  |

| 101 = 4.194s                                                                  |  |  |  |

| 110 = 8.389s                                                                  |  |  |  |

| 111 = 16.78s                                                                  |  |  |  |

#### 7.5 ALS TAB

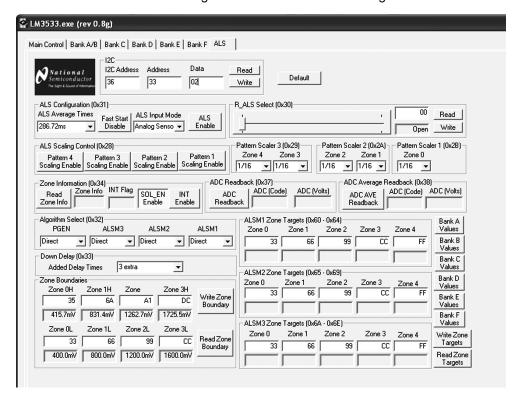

The Ambient Light Sensor (ALS) tab (Figure 12) contains all the registers that are applicable to the LM3533's ALS interface. Table 25 through Table 34 describe these registers.

Figure 12. ALS Tab

Table 25. ALS Configuration (0x31)

| Bits [5:3]                                                                                                                                             | Bit 2                                                                               | Bit 1                                                                                                            | Bit 0                                                  |

|--------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------|

| ALS Average Times                                                                                                                                      | Fast startup Enable/Disable                                                         | ALS Input Mode                                                                                                   | ALS Enable/Disable                                     |

| 000 = 17.92 ms<br>001 = 35.84ms<br>010 = 71.68ms<br>011 = 143.36ms<br>100 = 286.72ms (Default)<br>101 = 573.44ms<br>110 = 1146.88ms<br>111 = 2293.76ms | 0 = ALS fast startup is enabled ( <b>Default</b> ) 1 = ALS fast startup is disabled | 0 = ALS is set for Analog<br>Sensor Input Mode ( <b>Default</b> )<br>1 = ALS is set for PWM Sensor<br>Input Mode | 0 = ALS is disabled<br>(Default)<br>1 = ALS is enabled |

Table 26. Algorithm Select (0X32)

| Bits [7:6]<br>PGEN            | Bits [5:4]<br>ALSM3           | Bits [3:2]<br>ALSM2           | Bits [1:0]<br>ALSM1           |  |

|-------------------------------|-------------------------------|-------------------------------|-------------------------------|--|

| 00 = Direct Control (Default) |  |

| 01 = Up Only Control          | 01 = Up Only Control          | 01 = Up Only                  | 01 = Up Only                  |  |

| 1X = Down Delay Control       | 1X = Down Delay Control       | 1X = Down Delay               | 1X = Down Delay               |  |

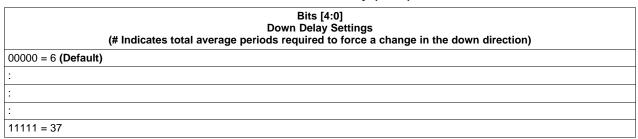

#### Table 27. Down Delay (0x33)

#### Table 28. Zone Information (0x34)

| Bits [4:2]                                                                             | Bit 1                                                                                                                                        | Bit 0                                                            |

|----------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------|

| Average Zone Information Bits                                                          | Zone Change Bit                                                                                                                              | Interrupt Enable Bit                                             |

| 000 = Zone 0 (Default)<br>001 = Zone 1<br>010 = Zone 2<br>011 = Zone 3<br>1XX = Zone 4 | 0 = no change in the ALS zone since the last read back of this register ( <b>Default</b> ) 1 = the ALS zone has changed. A read back of this | 0 = INT Mode Disabled ( <b>Default</b> )<br>1 = INT Mode Enabled |

#### Table 29. ADC Readback (0x37)

| Bit 7<br>MSB | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0<br>LSB |

|--------------|-------|-------|-------|-------|-------|-------|--------------|

| Data         | Data  | Data  | Data  | Data  | Data  | Data  | Data         |

#### Table 30. Read-Average ADC Register (ADDRESS 0x38)

| Bit 7<br>MSB | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0<br>LSB |

|--------------|-------|-------|-------|-------|-------|-------|--------------|

| Data         | Data  | Data  | Data  | Data  | Data  | Data  | Data         |

#### Table 31. Zone Boundaries

| Name    | Address | Function                 |

|---------|---------|--------------------------|

| Zone 0H | 0x50    | ALS Zone Boundary 0 High |

| Zone 0L | 0x51    | ALS Zone Boundary 0 Low  |

| Zone 1H | 0x52    | ALS Zone Boundary 1 High |

| Zone 1L | 0x53    | ALS Zone Boundary 1 Low  |

| Zone 2H | 0x54    | ALS Zone Boundary 2 High |

| Zone 2L | 0x55    | ALS Zone Boundary 2 Low  |

| Zone 3H | 0x56    | ALS Zone Boundary 3 High |

| Zone 3L | 0x57    | ALS Zone Boundary 3 Low  |

Note: Each Zone Boundary register is 8 bits with a maximum voltage of 2V. This gives a step size for each Zone Boundary Register bit of:

ZoneBoundaryLSB =

$$\frac{2V}{255}$$

= 7.8 mV

(7)

## Table 32. ALSM1 Zone Target Registers (ADDRESS 0x60 - 0x64)

| Address | Function            |

|---------|---------------------|

| 0x60    | ALSM1 Zone Target 0 |

| 0x61    | ALSM1 Zone Target 1 |

| 0x62    | ALSM1 Zone Target 2 |

| 0x63    | ALSM1 Zone Target 3 |

| 0x64    | ALSM1 Zone Target 4 |

## Table 33. ALSM2 Zone Target Registers (ADDRESS 0x65 - 0x69)

| Address | Function            |

|---------|---------------------|

| 0x65    | ALSM2 Zone Target 0 |

| 0x66    | ALSM2 Zone Target 1 |

| 0x67    | ALSM2 Zone Target 2 |

| 0x68    | ALSM2 Zone Target 3 |

| 0x69    | ALSM2 Zone Target 4 |

## Table 34. ALSM3 Zone Target Registers (ADDRESS 0x6A - 0x6E)

| Address | Function            |

|---------|---------------------|

| 0x6A    | ALSM3 Zone Target 0 |

| 0x6B    | ALSM3 Zone Target 1 |

| 0x6C    | ALSM3 Zone Target 2 |

| 0x6D    | ALSM3 Zone Target 3 |

| 0x6E    | ALSM3 Zone Target 4 |

#### IMPORTANT NOTICE

Texas Instruments Incorporated and its subsidiaries (TI) reserve the right to make corrections, enhancements, improvements and other changes to its semiconductor products and services per JESD46, latest issue, and to discontinue any product or service per JESD48, latest issue. Buyers should obtain the latest relevant information before placing orders and should verify that such information is current and complete. All semiconductor products (also referred to herein as "components") are sold subject to TI's terms and conditions of sale supplied at the time of order acknowledgment.

TI warrants performance of its components to the specifications applicable at the time of sale, in accordance with the warranty in TI's terms and conditions of sale of semiconductor products. Testing and other quality control techniques are used to the extent TI deems necessary to support this warranty. Except where mandated by applicable law, testing of all parameters of each component is not necessarily performed.

TI assumes no liability for applications assistance or the design of Buyers' products. Buyers are responsible for their products and applications using TI components. To minimize the risks associated with Buyers' products and applications, Buyers should provide adequate design and operating safeguards.

TI does not warrant or represent that any license, either express or implied, is granted under any patent right, copyright, mask work right, or other intellectual property right relating to any combination, machine, or process in which TI components or services are used. Information published by TI regarding third-party products or services does not constitute a license to use such products or services or a warranty or endorsement thereof. Use of such information may require a license from a third party under the patents or other intellectual property of the third party, or a license from TI under the patents or other intellectual property of TI.

Reproduction of significant portions of TI information in TI data books or data sheets is permissible only if reproduction is without alteration and is accompanied by all associated warranties, conditions, limitations, and notices. TI is not responsible or liable for such altered documentation. Information of third parties may be subject to additional restrictions.

Resale of TI components or services with statements different from or beyond the parameters stated by TI for that component or service voids all express and any implied warranties for the associated TI component or service and is an unfair and deceptive business practice. TI is not responsible or liable for any such statements.

Buyer acknowledges and agrees that it is solely responsible for compliance with all legal, regulatory and safety-related requirements concerning its products, and any use of TI components in its applications, notwithstanding any applications-related information or support that may be provided by TI. Buyer represents and agrees that it has all the necessary expertise to create and implement safeguards which anticipate dangerous consequences of failures, monitor failures and their consequences, lessen the likelihood of failures that might cause harm and take appropriate remedial actions. Buyer will fully indemnify TI and its representatives against any damages arising out of the use of any TI components in safety-critical applications.

In some cases, TI components may be promoted specifically to facilitate safety-related applications. With such components, TI's goal is to help enable customers to design and create their own end-product solutions that meet applicable functional safety standards and requirements. Nonetheless, such components are subject to these terms.

No TI components are authorized for use in FDA Class III (or similar life-critical medical equipment) unless authorized officers of the parties have executed a special agreement specifically governing such use.

Only those TI components which TI has specifically designated as military grade or "enhanced plastic" are designed and intended for use in military/aerospace applications or environments. Buyer acknowledges and agrees that any military or aerospace use of TI components which have *not* been so designated is solely at the Buyer's risk, and that Buyer is solely responsible for compliance with all legal and regulatory requirements in connection with such use.

TI has specifically designated certain components as meeting ISO/TS16949 requirements, mainly for automotive use. In any case of use of non-designated products, TI will not be responsible for any failure to meet ISO/TS16949.

Products Applications

Audio www.ti.com/audio Automotive and Transportation www.ti.com/automotive Communications and Telecom **Amplifiers** amplifier.ti.com www.ti.com/communications **Data Converters** dataconverter.ti.com Computers and Peripherals www.ti.com/computers **DLP® Products** www.dlp.com Consumer Electronics www.ti.com/consumer-apps

DSP **Energy and Lighting** dsp.ti.com www.ti.com/energy Clocks and Timers www.ti.com/clocks Industrial www.ti.com/industrial Interface interface.ti.com Medical www.ti.com/medical logic.ti.com Logic Security www.ti.com/security

Power Mgmt power.ti.com Space, Avionics and Defense www.ti.com/space-avionics-defense

Microcontrollers <u>microcontroller.ti.com</u> Video and Imaging <u>www.ti.com/video</u>

RFID www.ti-rfid.com

OMAP Applications Processors <a href="www.ti.com/omap">www.ti.com/omap</a> TI E2E Community <a href="e2e.ti.com">e2e.ti.com</a>

Wireless Connectivity <u>www.ti.com/wirelessconnectivity</u>