# Design Note - DN05024/D

# **Evaluation Boards for NCP1593 Synchronous Buck Regulator**

| РСВ                          | Device               | Input<br>Voltage           | Output<br>Voltage   | Output<br>Current | Topology            | I/O<br>Isolation |

|------------------------------|----------------------|----------------------------|---------------------|-------------------|---------------------|------------------|

| NCP1593AGEVB<br>NCP1593AGEVB | NCP1593A<br>NCP1593B | 4.0 to 5.5 V <sub>DC</sub> | 1.2 V <sub>DC</sub> | 3 A               | Synchronous<br>Buck | NONE             |

| Characteristic                         | Min  | Тур | Max | Unit |

|----------------------------------------|------|-----|-----|------|

| Output Voltage                         | 1.05 |     | 3.3 | ٧    |

| Output Current                         | 0    | 2   | 3   | Α    |

| Oscillator Frequency                   |      | 1.0 |     | MHz  |

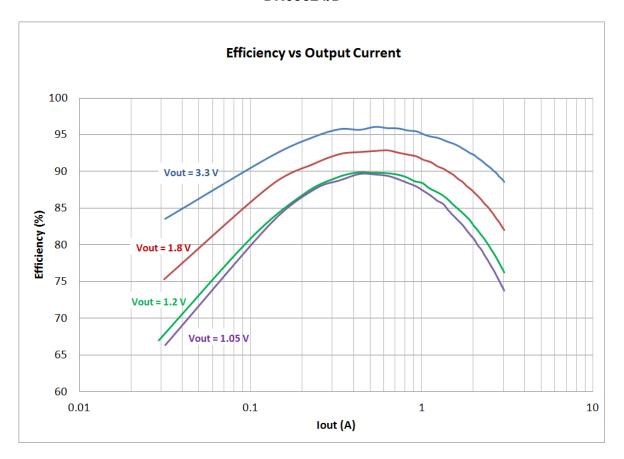

| Peak Efficiency                        |      | 96  |     | %    |

| PCB Layers                             |      | 4   |     |      |

| DC-DC Converter Dimensions 1.8" X 2.6" |      | "   |     |      |

#### **Circuit Description**

The NCP1593 is a fixed 1 MHz, high–output–current, synchronous PWM converter that integrates a low–resistance, high–side P–channel MOSFET and a low–side N–channel MOSFET. The NCP1593 utilizes internally compensated current mode control to provide good transient response, ease of implementation and excellent loop stability. It regulates input voltages from 4.0 V to 5.5 V down to an output voltage as low as 0.6 V and is able to supply up to 3 A of load current. The NCP1593 includes an internally fixed switching frequency, and an internal soft–start to limit inrush current. Other features include cycle–by–cycle current limiting, 100% duty cycle operation, short– circuit protection, power saving mode and thermal shutdown.

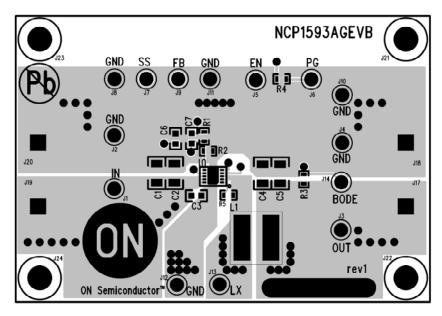

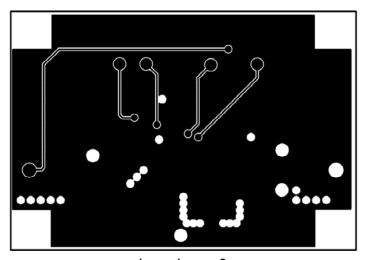

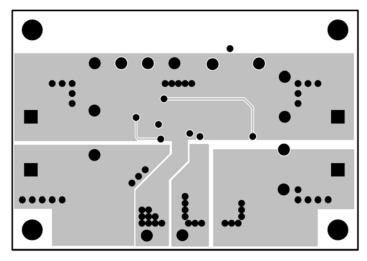

Top

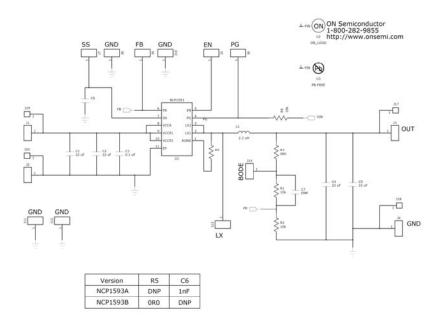

Figure 1: Schematic and TOP Layer with Silkscreen

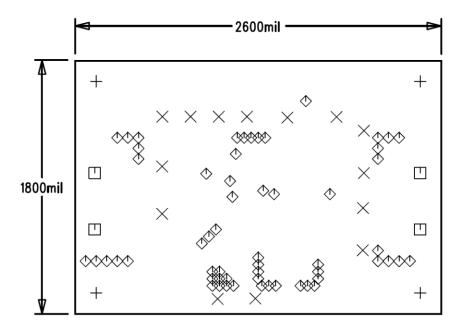

| SIZE | QTY | SYM            | PLATED | TOL    |

|------|-----|----------------|--------|--------|

| 125  | 4   | +              | YES    | +/-0.0 |

| 63   | 14  | ×              | YES    | +/-0.0 |

| 81   | 4   |                | YES    | +/-0.0 |

| 20   | 58  | $\diamondsuit$ | YES    | +/-0.0 |

Figure 2: Drill Drawing with Dimensions

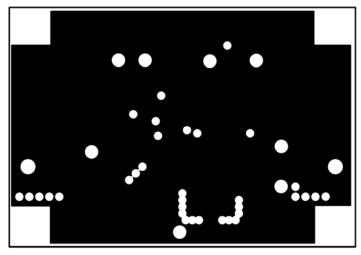

Inner Layer 2

Inner Layer 3

Bottom

Figure 3: Remaining Copper Layers

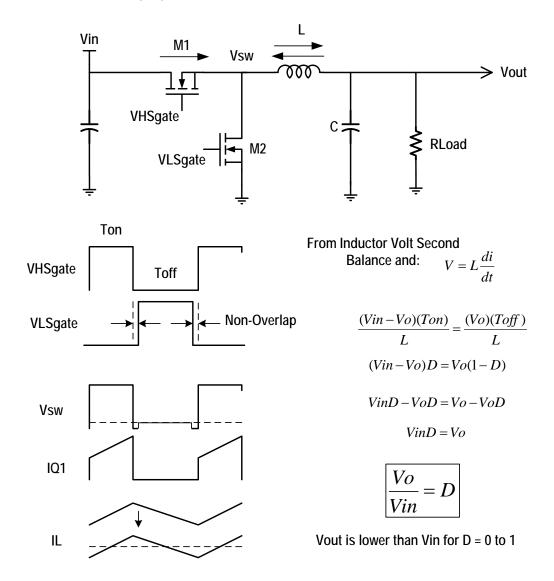

#### **Basic Buck Power Topology**

The principle of the Buck converter is fairly simple (see Figure 2):

The input voltage source is directly connected to the load through the Buck Inductor when M1 is turned ON. This is referred to as the ON state (D).

After M1 turns OFF and M2 Turns ON, the inductor maintains its current flow through M2 from ground. This is known as the OFF state (1-D).

Non- Overlap time is essential for preventing short circuit of the input supply. During this time the body drain diode of M2 conducts preventing high voltage transients across M2.

Synchronous Buck Converters never allow the inductor current to settle since current can be bidirectional during the off time. At lighter loads current in the inductor will actually flow in the reverse direction from Vout through the inductor to ground through the Low side FET M2.

The formulas in Figure 2 derive the input to output transfer function for a Continuous Conduction Buck Converter in terms of Duty Cycle.

Figure 4 – Buck Operation

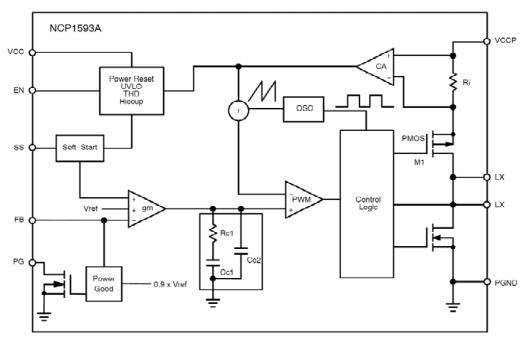

# DN05024/D BLOCK DIAGRAM

Figure 1. Block Diagram

#### PIN DESCRIPTIONS

| Pin No | Symbol           | Description                                                                                                                                                                                               |

|--------|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1      | NC / LX          | No connect pin for NCP1593A. The user may ground this pin or leave it floating. / LX pin for NCP1593B                                                                                                     |

| 2, 3   | LX               | The drains of the internal MOSFETs. The output inductor should be connected to these pins.                                                                                                                |

| 4      | PG               | Open drain output from the Power Good logic. When the FB voltage is within regulation, this is a high impedance pin. Otherwise it is pulled low.                                                          |

| 5      | EN               | Logic input to enable the part. Logic high to turn on the part and a logic low to shut off the part. An internal pullup forces the part into an enable state when no external bias is present on the pin. |

| 6      | FB               | Feedback input pin of the Error Amplifier. Connect a resistor divider from the converter's output voltage to this pin to set the converter's regulated voltage.                                           |

| 7      | SS / NC          | An external capacitor on this pin sets the soft-start ramp time. Leaving this pin open sets the soft-start time at 500 µs. For NCP1593B this pin is a no connect and should be left floating.             |

| 8      | V <sub>CC</sub>  | Input supply pin for internal bias circuitry. Connect a 0.1 μF ceramic bypass capacitor to this pin.                                                                                                      |

| 9, 10  | V <sub>CCP</sub> | Input for the power stage                                                                                                                                                                                 |

| EP     | GND              | Exposed pad of the package provides both electrical contact to the ground and good thermal contact to the PCB. This pad must be soldered to the PCB for proper operation.                                 |

Figure 5 – Block Diagram and Pinout

Figure 6: Efficiency vs Output Voltage and Current

<sup>1</sup> © 2011 ON Semiconductor.

**Disclaimer**: ON Semiconductor is providing this design note "AS IS" and does not assume any liability arising from its use; nor does ON Semiconductor convey any license to its or any third party's intellectual property rights. This document is provided only to assist customers in evaluation of the referenced circuit implementation and the recipient assumes all liability and risk associated with its use, including, but not limited to, compliance with all regulatory standards. ON Semiconductor may change any of its products at any time, without notice.

# **Mouser Electronics**

**Authorized Distributor**

Click to View Pricing, Inventory, Delivery & Lifecycle Information:

**ON Semiconductor:**

NCP1593AGEVB NCP1593BGEVB