# TP3404 Quad Digital Adapter for Subscriber Loops (QDASL)

Check for Samples: TP3404

## **FEATURES**

- 4 COMPLETE ISDN PBX 2-WIRE DATA TRANSCEIVERS INCLUDING:

- Quad 2 B Plus D Channel Interface for PBX "U" Interface

- 144 kb/s Full-Duplex on 1 Twisted Pair Using Burst Mode Transmission Technique

- Loop Range up to 6 kft (#24AWG)

- Alternate Mark Inversion Coding with Transmit Pulse Shaping DAC, Smoothing Filter, and Scrambler for Low Emi Radiation

- Adaptive Line Equalizer

- On-Chip Timing Recovery, No External Components

- Programmable Time-Slot Assignment TDM Interface for B Channels

- Separate Interface for D Channel with Programmable Sub-Slot Assignment

- 4.096 MHz Master Clock

- 4 Loop-Back Test Modes

- MICROWIRE™ Compatible Serial Control Interface

- 5V Operation

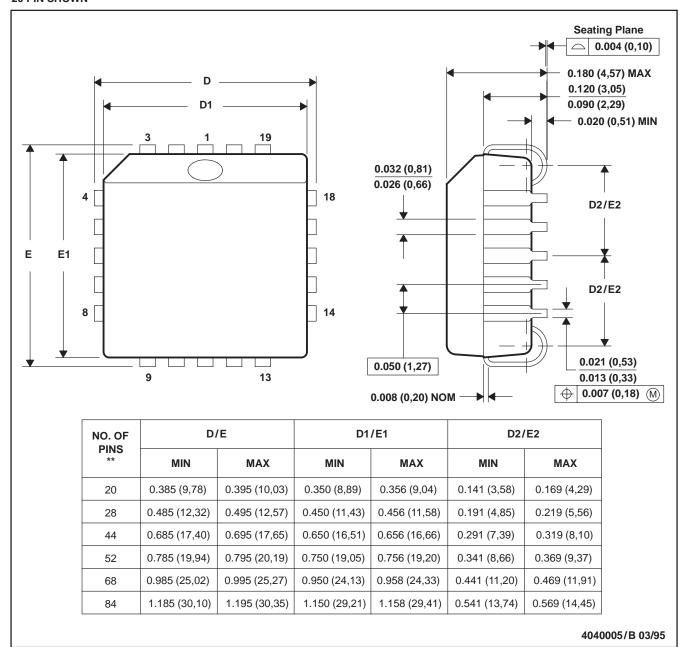

- 28-Pin PLCC Package

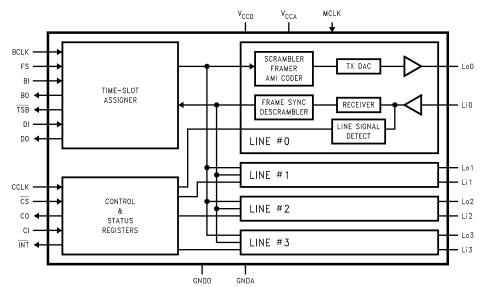

# **BLOCK DIAGRAM**

### DESCRIPTION

The TP3404 is a combination 4-line transceiver for voice and data transmission on twisted pair subscriber loops, typically in PBX line card applications. It is a companion device to the TP3401/2/3 DASL single-channel transceivers. In addition to 4 independent transceivers, a time-slot assignment circuit is included to support interfacing to the system backplane.

Each QDASL line operates as an ISDN "U" Interface for short loop applications, typically in a PBX environment, providing transmission for 2 B channels and 1 D channel.

Full-duplex transmission at 144 kb/s is achieved on single twisted wire pairs using a burst-mode technique (Time Compression Multiplexed). All timing sequences necessary for loop activation and deactivation are generated on-chip.

Alternate Mark Inversion (AMI) line coding is used to ensure low error rates in the presence of noise with lower emi radiation than other codes such as Biphase (Manchester). On #24 AWG cable the range is at least 1.8 km (6k ft.).

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

MICROWIRE is a trademark of Texas Instruments.

All other trademarks are the property of their respective owners.

These devices have limited built-in ESD protection. The leads should be shorted together or the device placed in conductive foam during storage or handling to prevent electrostatic damage to the MOS gates.

# **ABSOLUTE MAXIMUM RATINGS (1)(2)**

| V <sub>DDA</sub> /V <sub>DDD</sub> to GNDA/GNDD | 7V                               |

|-------------------------------------------------|----------------------------------|

| Voltage at Any Li, Lo Pin                       | V <sub>CC</sub> + 1V to GND - 1V |

| Current at Any Lo                               | ±100 mA                          |

| Voltage at Any Digital Input                    | V <sub>CC</sub> + 1V to GND - 1V |

| Current at Any Digital Output                   | ±50 mA                           |

| Storage Temperature Range                       | -65°C to +150°C                  |

| Lead Temperature (Soldering, 10 sec.)           | 300°C                            |

- (1) Absolute Maximum Ratings indicate limits beyond which damage to the device may occur. Operating ratings indicate conditions for which the device is functional, but do not ensure specific performance limits.

- (2) If Military/Aerospace specified devices are required, please contact the Texas Instruments Sales Office/ Distributors for availability and specifications.

### **ELECTRICAL CHARACTERISTICS**

Unless otherwise specified, limits printed in **BOLD** characters are specified for  $V_{CCA} = V_{CCD} = 5V \pm 5\%$ ,  $T_A = 0^{\circ}C$  to +70°C. Typical characteristics are specified at  $V_{DDA} = V_{DDD} = 5.0V$ ,  $T_A = 25^{\circ}C$ . All signals are referenced to GND, which is the common of GNDA and GNDD

| Symbol            | Parameter                                    | Conditions                                                             | Min      | Тур   | Max  | Units |

|-------------------|----------------------------------------------|------------------------------------------------------------------------|----------|-------|------|-------|

| DIGITAL I         | NTERFACES                                    |                                                                        | <u> </u> |       |      |       |

| V <sub>IH</sub>   | Input High Voltage                           | All Digital Inputs (DC)                                                | 2        |       |      | V     |

| V <sub>IL</sub>   | Input Low Voltage                            | All Digital Inputs (DC)                                                |          |       | 0.8  | V     |

| V <sub>OH</sub>   | Output High Voltage                          | I <sub>L</sub> = +1 mA                                                 | 2.4      |       |      | V     |

| V <sub>OL</sub>   | Output Low Voltage                           | I <sub>L</sub> = −1 mA                                                 |          |       | 0.4  | V     |

| I <sub>IL</sub>   | Input Low Current                            | All Digital Input, GND < V <sub>IN</sub> < V <sub>IL</sub>             | -10      |       | 10   | μΑ    |

| I <sub>IH</sub>   | Input High Current                           | All Digital Input, V <sub>IH</sub> < V <sub>IN</sub> < V <sub>CC</sub> | -10      |       | 10   | μΑ    |

| l <sub>OZ</sub>   | Output Current in High Impedance (TRI-STATE) | BO, CO, and DO                                                         | -10      |       | 10   | μΑ    |

| LINE INTE         | ERFACES                                      |                                                                        | <u> </u> |       |      |       |

| R <sub>Li</sub>   | Input Resistance                             | 0V < V <sub>Li</sub> < V <sub>CC</sub>                                 | 20       |       |      | kΩ    |

| C <sub>LLo</sub>  | Load Capacitance                             | From Lo to GND                                                         |          |       | 200  | pF    |

| ROLS              | Output Resistance                            | Load = 60Ω in Series with 2 μF to GND                                  |          |       | 3    | Ω     |

| $V_{DC}$          | Mean DC Voltage at Lo<br>Voltage at LS+, LS- | Load = $200\Omega$ in Series with 2 $\mu$ F to GND                     | 1.75     |       | 2.25 | V     |

| POWER D           | DISSIPATION                                  |                                                                        | <u> </u> |       |      |       |

| I <sub>CC</sub> 0 | Power Down Current                           | BCLK = 0 Hz; MCLK = 0 Hz, CCLK = 0 Hz                                  |          |       | 10   | mA    |

| I <sub>CC</sub> 1 | Power Up Current                             | All 4 Channels Activated                                               |          |       | 75   | mA    |

| TRANSMI           | SSION PERFORMANCE                            | •                                                                      | *        | •     |      | •     |

|                   | Transmit Pulse Amplitude at Lo               | $R_L = 200\Omega$ in Series with 2 $\mu F$ to GND                      | 1.1      | 1.3   | 1.5  | Vpk   |

|                   | Input Pulse Amplitude at Li                  |                                                                        | ±60      |       |      | mVpk  |

| TIMING S          | PECIFICATIONS                                |                                                                        |          |       | •    |       |

| Symbol            | Parameter                                    | Conditions                                                             | Min      | Тур   | Max  | Units |

| MASTER            | CLOCK INPUT SPECIFICATIONS                   |                                                                        |          | •     | •    |       |

| f <sub>MCLK</sub> | Frequency of MCLK                            |                                                                        |          | 4.096 |      | MHz   |

|                   | Master Clock Tolerance                       | Relative 2X MCLK in Slave                                              | -100     |       | +100 | ppm   |

| t <sub>WMH</sub>  | Period of MCLK High                          | Measured from V <sub>IH</sub> to V <sub>IH</sub>                       | 70       |       |      | ns    |

| t <sub>WML</sub>  | Period of MCLK Low                           | Measured from V <sub>IL</sub> to V <sub>IL</sub>                       | 70       |       |      | ns    |

| t <sub>RM</sub>   | Rise Time of MCLK                            | Measured from V <sub>IL</sub> to V <sub>IH</sub>                       |          |       | 15   | ns    |

| t <sub>FM</sub>   | Fall Time of MCLK                            | Measured from V <sub>IH</sub> to V <sub>IL</sub>                       |          |       | 15   | ns    |

# **ELECTRICAL CHARACTERISTICS (continued)**

Unless otherwise specified, limits printed in **BOLD** characters are specified for  $V_{CCA} = V_{CCD} = 5V \pm 5\%$ ,  $T_A = 0^{\circ}C$  to +70°C. Typical characteristics are specified at  $V_{DDA} = V_{DDD} = 5.0V$ ,  $T_A = 25^{\circ}C$ . All signals are referenced to GND, which is the common of GNDA and GNDD

| Symbol             | Parameter                                 | Conditions                                       | Min | Тур   | Max | Units |

|--------------------|-------------------------------------------|--------------------------------------------------|-----|-------|-----|-------|

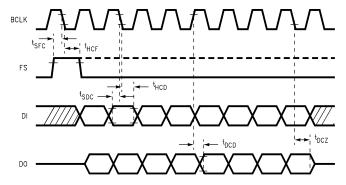

| DIGITAL            | INTERFACE TIMING                          |                                                  |     |       |     |       |

| f <sub>BCLK</sub>  | BCLK Frequency                            |                                                  |     | 4.096 | 4.1 | MHz   |

| t <sub>WBH</sub> , | Clock Pulse Width High                    | Measured from V <sub>IH</sub> to V <sub>IH</sub> | 70  |       |     | ns    |

| t <sub>WBL</sub>   | and Low for BCLK                          | Measured from V <sub>IL</sub> to V <sub>IL</sub> | 70  |       |     |       |

| t <sub>RB</sub> ,  | Rise Time and Fall Time                   | Measured from V <sub>IL</sub> to V <sub>IH</sub> |     |       | 15  | ns    |

| t <sub>FB</sub>    | of BCLK                                   | Measured from $V_{\rm IH}$ to $V_{\rm IL}$       |     |       | 15  |       |

| t <sub>HBM</sub>   | BCLK Transition to MCLK High or Low       |                                                  | -30 |       | 30  | ns    |

| t <sub>SFC</sub>   | Set up Time, FS Valid to BCLK Invalid     |                                                  | 20  | 4     |     | ns    |

| t <sub>HCF</sub>   | Hold Time, BCLK Low to FS Invalid         |                                                  | 40  | 30    |     | ns    |

| t <sub>SBC</sub>   | Setup Time, BI Valid to BCLK Invalid      |                                                  | 30  | 11    |     | ns    |

| t <sub>HCB</sub>   | Hold Time, BCLK Valid to BI Invalid       |                                                  | 40  | 7     |     | ns    |

| t <sub>SDC</sub>   | Setup Time, DI Valid to BCLK Low          |                                                  | 30  |       |     | ns    |

| t <sub>HCD</sub>   | Hold Time, BCLK Low to DI Invalid         |                                                  | 40  |       |     | ns    |

| t <sub>DCB</sub>   | Delay Time, BCLK High to BO Valid         | Load = 2 LSTTL + 100 pF                          |     |       | 80  | ns    |

| t <sub>DCBZ</sub>  | Delay Time, BCLK Low to BO High-Z         |                                                  | 80  |       | 120 | ns    |

| t <sub>DCD</sub>   | Delay Time, BCLK High to DO valid         | Load = 2 LSTTL + 100 pF                          |     |       | 80  | ns    |

| t <sub>DCZ</sub>   | Delay Time, BCLK Low to DO High Impedance |                                                  | 40  |       | 120 | ns    |

| t <sub>DCT</sub>   | Delay Time, BCLK High to TSB Low          |                                                  |     |       | 120 | ns    |

| t <sub>ZBT</sub>   | Disable Time, BCLK Low to TSB High-Z      |                                                  |     |       | 120 | ns    |

| MICROW             | IRE CONTROL INTERFACE TIMING              |                                                  |     |       |     |       |

| f <sub>CCLK</sub>  | Frequency of CCLK                         |                                                  |     |       | 2.1 | MHz   |

| t <sub>CH</sub>    | Period of CCLK High                       | Measured from V <sub>IH</sub> to V <sub>IH</sub> | 150 |       |     | ns    |

| t <sub>CL</sub>    | Period of CCLK Low                        | Measured from V <sub>IL</sub> to V <sub>IL</sub> | 150 |       |     | ns    |

| t <sub>SSC</sub>   | Setup Time, CS Low to CCLK High           |                                                  | 50  |       |     | ns    |

| t <sub>HCS</sub>   | Hold Time, CCLK High to CS Transition     |                                                  | 40  |       |     | ns    |

| t <sub>SIC</sub>   | Setup Time, CI Valid to CCLK High         |                                                  | 50  |       |     | ns    |

| t <sub>HCI</sub>   | Hold Time, CCLK High to CI Invalid        |                                                  | 20  |       |     | ns    |

| t <sub>DCO</sub>   | Delay Time, CCLK Low to CO Valid          |                                                  |     |       | 80  | ns    |

| t <sub>DSOZ</sub>  | Delay Time, CS High to CO High-Z          |                                                  |     |       | 80  | ns    |

| t <sub>DCIZ</sub>  | Delay Time, CCLK to INT High-Z            |                                                  |     |       | 100 | ns    |

# **PIN DESCRIPTIONS**

| Pin                | Pin                      | PIN DESCRIPTIONS                                                                                                                                                                                                                                                                                       |

|--------------------|--------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| No.                | Name                     | Description                                                                                                                                                                                                                                                                                            |

| 1                  | GNDA                     | Analog Ground or 0V. All analog signals are referenced to this pin.                                                                                                                                                                                                                                    |

| 15                 | GNDD                     | Digital Ground 0V. It must connect to GNDA with a shortest possible trace. This can be done directly underneath the part.                                                                                                                                                                              |

| 28                 | VDDA                     | Positive power supply input to QDASL analog section. It must be 5V ±5%.                                                                                                                                                                                                                                |

| 16                 | VDDD                     | Positive power supply input to QDASL digital section. It must be 5V ±5%, and connect to VDDA with the shortest possible trace. This can be done directly underneath the part.                                                                                                                          |

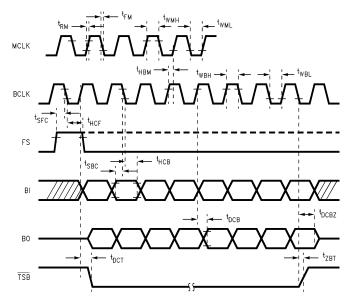

| 11                 | FS                       | Frame Sync input: this signal is the 8 kHz clock which defines the start of the transmit and receive frames at the digital interfaces.                                                                                                                                                                 |

| 9                  | MCLK                     | This pin is the 4.096 MHz Master Clock input, which requires a CMOS logic level clock from a stable source. MCLK must be synchronous with BCLK.                                                                                                                                                        |

| 10                 | BCLK                     | Bit Clock logic input, which determines the data shift rate for B and D channel data at the BI, BO, DI and DO pins. BCLK may be any multiple of 8 kHz from 256 kHz to 4.096 MHz, but must be synchronous with MCLK.                                                                                    |

| 12                 | ВІ                       | Time-division multiplexed input for B1 and B2 channel data to be transmitted to the 4 lines. Data on this pin is shifted in on the failing edge of BCLK into the B1 and B2 channels during the selected transmit time-slots.                                                                           |

| 13                 | ВО                       | Time-division multiplexed receive data output bus. B1 and B2 channel data from all 4 lines is shifted out on the rising edge of BCLK on this pin during the assigned receive time-slots. At all other times this output is TRI-STATE (high impedance).                                                 |

| 14                 | TSB                      | This pin is an open-drain output which is normally high impedance but pulls low during any active B channel receive time slots at the BO pin.                                                                                                                                                          |

| 7                  | DI                       | Time-division multiplexed input for D channel data to be transmitted to the 4 lines. Data on this pin is shifted in on the failing edge of BCLK into the D channel during the selected transmit sub-time-slots.                                                                                        |

| 8                  | DO                       | Time-division multiplexed output for D channel data received from the 4 lines. Data on this pin is shifted out on the rising edge of BCLK during the selected receive sub-time-slot.                                                                                                                   |

| 19                 | CCLK                     | Microwire Control Clock input. This clock shifts serial control information into CI and out from CO when the $\overline{\text{CS}}$ input is low, depending on the current instruction. CCLK may be asynchronous with the other system clocks.                                                         |

| 21                 | CI                       | Control data Input. Serial control information is shifted into the QDASL on this pin on the rising edges of CCLK when $\overline{\text{CS}}$ is low.                                                                                                                                                   |

| 17                 | ĪNT                      | Interrupt request output, a latched output signal which is normally high impedance and goes low to indicate a change of status of any of the 4 loop transmission systems. This latch is cleared when the Status Register is read by the microprocessor. Bipolar Violation does not effect this output. |

| 20                 | СО                       | Control data Output. Serial control/status information is shifted out from the QDASL on this pin on the falling edges of CCLK when CS is low.                                                                                                                                                          |

| 18                 | CS                       | Chip Select input. When this pin is pulled low, the Microwire interface is enabled to allow control information to be written in to and out from the device via the Cl and CO ins. When high, this pin inhibits the Microwire interface.                                                               |

| 4<br>3<br>26<br>25 | Lo0<br>Lo1<br>Lo2<br>Lo3 | Line driver transmit outputs for the 4 transmission channels. Each output is an amplifier intended to drive a transformer.                                                                                                                                                                             |

| 5<br>2<br>27<br>24 | Li0<br>Li1<br>Li2<br>Li3 | Line receive amplifier inputs for the 4 transmission channels. Each Li pin is a self-biased high impedance input which should be connected to the transformer via the recommended line interface circuit.                                                                                              |

Submit Documentation Feedback

Copyright © 2004, Texas Instruments Incorporated

# **CONNECTION DIAGRAM**

<sup>\*</sup> Do not connect to this pin.

Figure 1. Top View See Package Number FN0028A

Copyright © 2004, Texas Instruments Incorporated

**NSTRUMENTS**

SNOS703 – DECEMBER 2004 www.ti.com

#### FUNCTIONAL DESCRIPTION

The QDASL contains 4 transceivers, each of which can interoperate with any of the TP340X family of single-channel DASL transceivers. Each QDASL transceiver has its own independent line transmit and receive section, timing recovery circuit, scrambler/descrambler and loop activation controller. Functions which are shared by the 4 transceivers include the Microwire control port and the digital interface with time-slot assignment.

#### **BURST MODE OPERATION**

For full-duplex operation over a single twisted-pair, burst mode timing is used, with the QDASL end of each line acting as the loop timing master, and the DASL at the terminal being the timing slave (the QDASL transceivers cannot operate in loop timing slave mode).

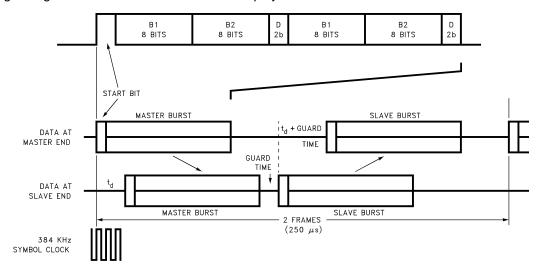

Each burst within a DASL line is initiated by the QDASL Master transmitting a start bit, for burst framing, followed by the B1, B2 and D channel data from 2 consecutive 8 kHz frames, combined in the format shown in Figure 2. During transmit bursts the receiver input for that channel is inhibited to avoid disturbing the adaptive circuits. The slave's receiver is enabled at this time and it synchronizes to the start bit of the burst, which is always an unscrambled "1" (of the opposite polarity to the last "1" sent in the previous burst). When the slave detects that 36 bits following the start bit have been received, it disables the received input, waits 6 line symbol periods to match the other end settling guard time, and then begins to transmit its burst back towards the master, which by this time has enabled its receiver input. The burst repetition rate is thus 4 kHz.

## LINE TRANSMIT SECTIONS

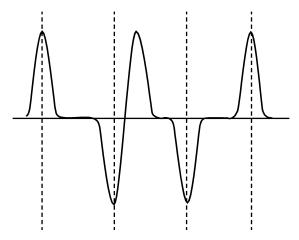

Alternate Mark Inversion (AMI) line coding, in which binary "1"s are alternately transmitted as a positive pulse then a negative pulse, is used on each DASL line because of its spectral efficiency and null DC energy content. All transmitted bits, excluding the start bit, are scrambled by a 9-bit scrambler to provide good spectral spreading with a strong timing content. The scrambler feedback polynomial is:  $X^9 + X^5 + 1$ .

Figure 2. Burst Mode Timing on the Line

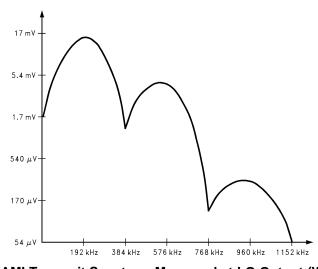

Pulse shaping is obtained by means of a Digital to Analog Converter followed by a Continuous Smoothing Filter, in order to limit RF energy and crosstalk while minimizing Inter-Symbol Interference (ISI). Figure 3 shows the pulse shape at the Lo output, while a template for the typical power spectrum transmitted to the line with random data is shown in Figure 4.

Each line-driver output, Lo0–Lo3, is designed to drive a transformer through a capacitor and termination resistor. A 1:1 transformer, terminated in  $100\Omega$ , results in signal amplitude of typically 1.3 Vpk on the line. Over-voltage protection must be included in each interface circuit.

### LINE RECEIVE SECTIONS

The input of each receive section, Li0–Li3, consists of a continuous anti-alias filter followed by a switched-capacitor low-pass filter designed to limit the noise bandwidth with minimum intersymbol interference. To correct pulse attenuation and distortion caused by the transmission line an AGC circuit and first-order equalizer adapt to the received pulse shape, thus restoring a "flat" channel response with maximum received eye opening over a wide spread of cable attenuation characteristics.

From the equalized output a DPLL (Digital Phase-Locked Loop) recovers a low-jitter clock for optimum sampling of the received symbols. The MCLK input provides the reference clock for the DPLL at 4.096 MHz.

Following detection of the recovered symbols, the received data is de-scrambled by the same  $X^9 + X^5 + 1$  polynomial and presented to the digital system interface circuit.

When a transmission line is de-activated, a Line-Signal Detect Circuit is enabled to detect the presence of incoming bursts if the far-end starts to activate the loop.

Figure 3. Typical AMI Waveform at Lo

Figure 4. Typical AMI Transmit Spectrum Measured at LO Output (With RGB = 100 Hz)

## **ACTIVATION AND LOOP SYNCHRONIZATION**

Activation (i.e. power-up and loop synchronization) may be initiated from either end of the loop. If the master (QDASL) end is activating the loop, it sends normal bursts of scrambled "1"s which are detected by the slave's line-signal-detect circuitry. The slave then replies with bursts of scrambled "1"s synchronized to the received bursts, and the Framing Detection circuit at each end searches for 4 consecutive correctly formatted receive bursts to acquire full loop synchronization. The QDASL receiver indicates when it is correctly in sync with received bursts by setting an indication in the Status Register and pulling the INT pin low.

For the slave end to initiate activation, it begins transmission of alternate bursts i.e., the burst repetition rate is 2 kHz, not 4 kHz. At this point the slave is running from its local oscillator and is not receiving any sync information from the master. When the master's Line-Signal Detect Circuit recognizes this "wake-up" signal, the appropriate QDASL line must be activated by writing to the Control Register. The master begins to transmit bursts synchronized, as normal, to the FS input with a 4 kHz repetition rate. This enables the slave's receiver to correctly identify burst timing from the master and to re-synchronize its own burst transmissions to those it receives. The Framing Detection Circuits then acquire full loop sync as described earlier.

Loop synchronization is considered to be lost if the Framing Detection Circuit does not find four framing marks of the four consecutive 4 kHz line frames. At this point an indication is set in the Status Register, the INT output is pulled low, and the receiver searches to re-acquire loop sync.

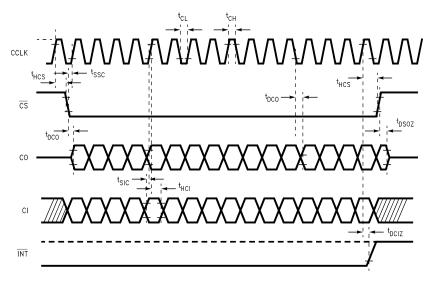

#### MICROWIRE CONTROL INTERFACE

A serial interface, which can be clocked independently from the B and D channel system interfaces, is provided for microcontroller access to the time-slot assignment, Control and Status Registers in the QDASL. The microcontroller is normally the timing master of this interface, and it supplies the CCLK and CS signals.

All data transfers consist of simultaneous read and write cycles, in which 2 continuous bytes are sampled on the CI pin, at the same time as 2 bytes are shifted out from the CO pin, see Figure 7. The first byte is a register address and the second is the data. To initiate a Microwire read/write cycle, CS must be pulled low for 16 cycles of CCLK. Data on CI is sampled on rising edges of CCLK, and shifted out from CO on failing edges. When CS is high, the CO pin is in the high-impedance TRI-STATE, enabling the CO pins of many devices to be multiplexed together.

Whenever a change (except Bipolar Violation) in any of the QDASL status conditions occurs, the Interrupt output INT is pulled low to alert the microprocessor to initiate a read cycle of the Status Register. This latched output is cleared when the read cycle is initiated.

Table 1 lists the address map of control functions and status indicators. Table 2 lists the addresses for the Control Registers for each QDASL line. Even-numbered addresses are read-write cycles, in which the data returned by the CO pin is previous contents of the addressed register. Odd-numbered addresses are readback commands only.

Address Registers (Hex) 00-0F LINE 0 Control (TSX,TSR,CTRL) 10-1F LINE 1 Control (TSX,TSR,CTRL) 20-2F LINE 2 Control (TSX,TSR,CTRL) 30-3F LINE 3 Control (TSX,TSR,CTRL) 40-CF Not used FF Common Status Register for all lines (0-3). See Table 6

Table 1. Global Register Address Map

Table 2. Per Line Control Register Address Map

| Function                            |   | MSB N | ibble <sup>(2)</sup> |   | LSB Nibble |   |   |   | Byte 2 <sup>(1)</sup> |

|-------------------------------------|---|-------|----------------------|---|------------|---|---|---|-----------------------|

|                                     | 7 | 6     | 5                    | 4 | 3          | 2 | 1 | 0 |                       |

| Write TSXD Register                 | N |       |                      |   | 0          | 0 | 0 | 0 | See Table 5           |

| Read TSXD Register                  | N |       |                      |   | 0          | 0 | 0 | 1 | See Table 5           |

| Write TSXB1 Register                | N |       |                      |   | 0          | 0 | 1 | 0 | See Table 4           |

| Read TSXB1 Register                 | N |       |                      |   | 0          | 0 | 1 | 1 | See Table 4           |

| Write TSXB2 Register                | N |       |                      |   | 0          | 1 | 0 | 0 | See Table 4           |

| Read TSXB2 Register                 | N |       |                      |   | 0          | 1 | 0 | 1 | See Table 4           |

| Write TSRD Register                 | N |       |                      |   | 0          | 1 | 1 | 0 | See Table 5           |

| Read TSRD Register                  | N |       |                      |   | 0          | 1 | 1 | 1 | See Table 5           |

| Write TSRB1 Register                | N |       |                      |   | 1          | 0 | 0 | 0 | See Table 4           |

| Read TSRB1 Register                 | N |       |                      |   | 1          | 0 | 0 | 1 | See Table 4           |

| Write TSRB2 Register                | N |       |                      |   | 1          | 0 | 1 | 0 | See Table 4           |

| Read TSRB2 Register                 | N |       |                      |   | 1          | 0 | 1 | 1 | See Table 4           |

| Write Line Control Register (CTR L) | N |       |                      |   | 1          | 1 | 1 | 0 | See Table 3           |

| Read Line Control Register (CTRL)   | N |       |                      |   | 1          | 1 | 1 | 1 | See Table 3           |

<sup>(1)</sup> Bit 7 of bytes 1 and 2 is always the first bit clocked into or out from the CI and CO pins.

#### LINE CONTROL REGISTERS CTRLN

Each of the 4 transceivers has a Line Control Register, CTRL0-CTRL3, which provides for control of loop activation, loopbacks, Interrupt enabling and D channel interface enabling. Table 3 lists the functions.

## **POWER ON INITIALIZATION**

Following the initial application of power, the QDASL enters the power-down (de-activated) state, in which all the internal circuits are inactive and in a low power state except for a Line-Signal Detect Circuit for each of the 4 lines, and the necessary bias circuits. The 4 line outputs, Lo0–Lo3, are in a high impedance state and all digital outputs are inactive. All bits in the Line Control Registers power-up initially set to "0". While powered-down, each Line-Signal Detect Circuit continually monitors its line, to detect if the far-end initiates loop transmission.

## POWER-UP/DOWN CONTROL

To power-up the device and initiate activation, bit C7 in any of the 4 Line Control Registers must be set high, see Table 3. Setting C7 low de-activates the loop, or puts the channel in power-down state. During power-down state, internal register data is retained, and still can be accessed.

## **LOOPBACKS**

Four different loopbacks can be set for each line. They are enabled and disabled by setting the corresponding bits in the Control Register, see Table 3. In addition, a line must be activated to see the effect of loopback commands.

- 1. 2B+D Line Loopback

- When bit 5 is set to 1, this loop will transfer all three channels, B1, B2 and D, that are received at the Li pin back to the Lo pin. Data out on BO/DO is still the same as received at the Li input.

- 2. B1 Line Loopback

- When bit 4 is set high, the loop path is the same as (1) but only data on the B1 channel is looped back to the line. Transmit data in the B2 and D channels is from the Bi/DI pins.

- 3. B2 Line Loopback

- As (2) but for the B2 channel.

- 4. 2B+D Digital Loopback

Copyright © 2004, Texas Instruments Incorporated

<sup>(2)</sup> N = 0, 1, 2, or 3 in straight Binary notation for Line 0, 1, 2, or 3 respectively.

This loop will transfer all data (2B+D) received at BI/DI back to BO/DO. The data is also transmitted to the line.

### TIME-SLOT ASSIGNMENT

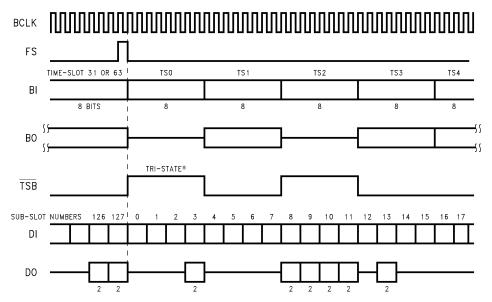

The digital interface of the QDASL uses time-division multiplexing, with data framed in up to 64 possible 8-bit time-slots per 125 µs frame. Channels B1 and B2 for all 4 lines are clocked in (towards the line) at the BI pin and clocked out (from the line) at the BO pin. A separate port is provided for the D channel data for all 4 lines, which is clocked in on DI and out on DO. In addition to time-slot assignment, D channel data may be assigned into 2-bit sub-slots within each time slot, with up to 256 sub-slots per frame (with BCLK = 4.096 MHz). Each frame starts with the first positive edge of BCLK after the FS signal goes high, and counting of timeslots starts from zero at the beginning of the frame. Figure 5 shows the timing, with some example time-slot assignments.

For each of the 4 QDASL lines there are 6 Time-Slot Assignment control registers, one each for transmit and receive B1, B2 and D channels. Selection of time-slots for transmit data into the BI or DI pin is made by writing the timeslot number (in Hex notation) into the appropriate TSX register. TSXB1 is the time-slot assignment for the transmit B1, TSXB2 is the time-slot assignment register for the transmit B2 channel and TSXD is the sub-slot assignment register for the transmit D channel.

| Bit Number |   |   |   |   |   |   | Function |                                    |  |

|------------|---|---|---|---|---|---|----------|------------------------------------|--|

| 7          | 6 | 5 | 4 | 3 | 2 | 1 | 0        |                                    |  |

| 0          |   |   |   |   |   |   |          | Deactivate Line                    |  |

| 1          |   |   |   |   |   |   |          | Activate Line                      |  |

|            | 0 |   |   |   |   |   |          | Disable Digital Loopback           |  |

|            | 1 |   |   |   |   |   |          | Enable 2B+D Digital Loopback       |  |

|            |   | 0 |   |   |   |   |          | Disable Line Loopback              |  |

|            |   | 1 |   |   |   |   |          | Enable 2B+D Line Loopback          |  |

|            |   |   | 0 |   |   |   |          | Disable B1 Line Loopback           |  |

|            |   |   | 1 |   |   |   |          | Enable B1 Line Loopback            |  |

|            |   |   |   | 0 |   |   |          | Disable B2 Line Loopback           |  |

|            |   |   |   | 1 |   |   |          | Enable B2 Line Loopback            |  |

|            |   |   |   |   | 0 |   |          | Disable Interrupt from this Line   |  |

|            |   |   |   |   | 1 |   |          | Enable Interrupt from this Line    |  |

|            |   |   |   |   |   | 0 |          | D Channel enabled from DO to Line  |  |

|            |   |   |   |   |   | 1 |          | D Channel disabled from DO to Line |  |

|            |   |   |   |   |   |   | 0        | D Channel enabled from Line to DI  |  |

|            |   |   |   |   |   |   | 1        | D Channel disabled from Line to DI |  |

Table 3. Byte 2 of Control Register (CTRLN)

In the same manner the time-slot number should be written into the appropriate TSR registers for receive data at the BO and DO pins. TSRB1 is the time-slot assignment for the receive B1 channel, TSRB2 is the time-slot assignment register for the receive B2 channel and TSRD is the sub-slot assignment register for the receive D channel.

Whenever any receive time-slot is active at BO, the TSB output is also pulled low.

### REGISTERS TSXB1, TSXB2, TSRB1, TSRB2

The data format for all B channel time-slot assignment registers is shown in Table 4.

#### **BIT 7 TRANSPARENCY CONTROL: EB**

This bit enables or disables data transparency between the digital interface and the line interface for the selected channel.

EB = 0 disables the channel.

EB = 1 enables the channel.

10

When the transmit direction (towards the line) is disabled there will be all "ONE's" (scrambled) as data for this channel at the Lo pin. If the receive direction (from the line) is disabled, BO will stay high impedance for the programmed time slot while, if it is enabled, data out on BO in the assigned time slot is the data from Li.

#### BITS 5-0: TS5-TS0

These bits define the binary number of the time-slot selected. Time-slots are numbered from 0–63. The frame sync signal is used as marker pulses for the beginning of time slot 0.

Table 4. Byte 2 of Register TSXB1, TSXB2, TSRB1 or TSRB2 for B Channel Time-Slot Assignment

|    |   |            | Function    |              |                      |     |     |  |

|----|---|------------|-------------|--------------|----------------------|-----|-----|--|

| 7  | 6 | 5          | 4           | 3 2 1 0      |                      |     |     |  |

| EB | Х | TS5        | TS4         | TS3          | TS2                  | TS1 | TS0 |  |

| 0  | Х | X          | X X X X X X |              | Disable B1 and/or B2 |     |     |  |

| 1  | Х | Assign One | Binary Code | ed Time-Slot | Enable B1 and/or B2  |     |     |  |

# **REGISTERS TXD, TRD**

The data format for all D channel time-slot assignment registers is as follows:

Data transparency between the digital interface and the line interface for the D channels can be controlled via the Channel Control Register, see Table 3.

## BITS 7-0: TS7-TS0

These bits define the binary number of the sub-slot selected. Sub-slots are numbered from 0–255. The frame sync signal is used as marker pulses for the beginning of Sub-slot 0.

Table 5. Byte 2 of Register TSXD or TSRD for D Channel Time-Slot Assignment

| Bit Number and Name |    |    |    |    |    |    |    |  |  |

|---------------------|----|----|----|----|----|----|----|--|--|

| 7                   | 6  | 5  | 4  | 3  | 2  | 1  | 0  |  |  |

| SS                  | SS | SS | SS | SS | SS | SS | SS |  |  |

| 7                   | 6  | 5  | 4  | 3  | 2  | 1  | 0  |  |  |

Figure 5. QDASL Digital Interface Timing

Product Folder Links: TP3404

Copyright © 2004, Texas Instruments Incorporated

## **Table 6. Status Register Functions**

|   |   |   | Ву | te 2 |   |   |   | Indication                                  |  |  |

|---|---|---|----|------|---|---|---|---------------------------------------------|--|--|

| 7 | 6 | 5 | 4  | 3    | 2 | 1 | 0 |                                             |  |  |

| 0 | 0 |   |    |      |   |   |   | Line 3: deactivated                         |  |  |

| 0 | 1 |   |    |      |   |   |   | Line 3: line signal present but not in sync |  |  |

| 1 | 0 |   |    |      |   |   |   | Line 3: activated, bipolar violation (1)    |  |  |

| 1 | 1 |   |    |      |   |   |   | Line 3: activated, no bipolar violation     |  |  |

|   |   | 0 | 0  |      |   |   |   | Line 2: deactivated                         |  |  |

|   |   | 0 | 1  |      |   |   |   | Line 2: line signal present but not in sync |  |  |

|   |   | 1 | 0  |      |   |   |   | Line 2: activated, bipolar violation (1)    |  |  |

|   |   | 1 | 1  |      |   |   |   | Line 2: activated, no bipolar violation     |  |  |

|   |   |   |    | 0    | 0 |   |   | Line 1: deactivated                         |  |  |

|   |   |   |    | 0    | 1 |   |   | Line 1: line signal present but not in sync |  |  |

|   |   |   |    | 1    | 0 |   |   | Line 1: activated, bipolar violation (1)    |  |  |

|   |   |   |    | 1    | 1 |   |   | Line 1: activated, no bipolar violation     |  |  |

|   |   |   |    |      |   | 0 | 0 | Line 0: deactivated                         |  |  |

|   |   |   |    |      |   | 0 | 1 | Line 0: line signal present but not in sync |  |  |

|   |   |   |    |      |   | 1 | 0 | Line 0: activated, bipolar violation (1)    |  |  |

|   |   |   |    |      |   | 1 | 1 | Line 0: activated, no bipolar violation     |  |  |

<sup>(1)</sup> Bipolar Violation does not cause an Interrupt.

## **STATUS REGISTER**

Status information for all 4 channels may be read from the common Status Register by addressing location X'FF. 2 bits per line are coded as shown in Table 6. A change in the status of 1 or more lines is indicated by the INT pin being pulled low, provided bit 2 of the corresponding control register is set to "ONE" to enable the interrupt for that line.

#### **BIPOLAR VIOLATION DETECTOR**

On an activated line, whenever a line error is received there will be a violation of the AMI coding rule. This is reported by setting the code 10 for that line. The violation indication is cleared to 11 after a read of the Status Register.

As an example of the interpretation of the Status Register contents, if the byte 2 read back from the Status Register =00111001 (=X'39), this indicates the following status of the 4 lines: line 3 is deactivated; line 2 is in sync with no error since the last read cycle; line 1 is in sync but there has been 1 or more errors since the last read cycle of the Status Register; line 0 is receiving a line signal but the line transmission is not synchronized.

#### **APPLICATIONS INFORMATION**

#### **POWER SUPPLIES**

While the pins of the TP3404 QDASL device are well protected against electrical misuse, it is recommended that the standard CMOS practice of applying GND to the device before any other connections are made should always be followed. In applications where the printed circuit card may be plugged into a hot socket with power and clocks already present, an extra long ground pin on the connector should be used.

To minimize noise sources, the VDDA and VDDD pins should be connected together via the shortest possible trace; likewise the GNDA and GNDD pins must be connected together. These two connections can be done directly underneath the part. All other ground connections to each device should meet at a common point as close as possible to the GNDD pin in order to prevent the interaction of ground return currents flowing through a common bus impedance. A power supply decoupling capacitor of 0.1 µF should be connected from this common point to VDDD as close as possible to the device pins.

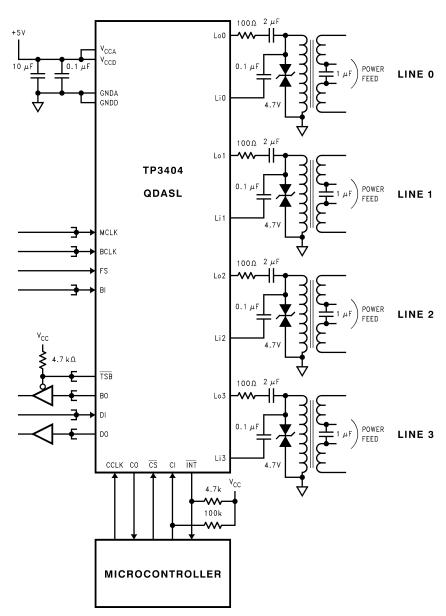

Figure 6 shows a typical 4 line application of the QDASL. The current list of suitable commercial transformers is:

Schott Corporation (Nashville);

Phone 615-889-8800.

Part numbers: 67110850 (dry);

67110860 (50 mA DC).

Pulse Engineering (San Diego);

Phone 619-674-8100.

Part number:TBD.

Note that the Zener diode protection shown in Figure 9 is only intended as secondary protection for inside wiring applications; primary protection is also necessary. Further information can be found in the datasheet for the TP3401/2/3 DASL devices (SNOSC12) and in Application Note AN-509 "Using the TP3401/2/3 ISDN PBX Transceivers".

Texas Instruments

SNOS703 – DECEMBER 2004 www.ti.com

Figure 6. Typical Application

Figure 7. Microwire Control Interface Timing Details

Figure 8. B Channel Digital Interface Details

Figure 9. D-Channel Digital Interface Timing Details

Copyright © 2004, Texas Instruments Incorporated

# PACKAGE OPTION ADDENDUM

30-Oct-2013

#### PACKAGING INFORMATION

| Orderable Device | Status | Package Type | _       | Pins | _   | Eco Plan                   | Lead/Ball Finish | MSL Peak Temp           | Op Temp (°C) | Device Marking | Samples |

|------------------|--------|--------------|---------|------|-----|----------------------------|------------------|-------------------------|--------------|----------------|---------|

|                  | (1)    |              | Drawing |      | Qty | (2)                        | (6)              | (3)                     |              | (4/5)          |         |

| TP3404V/63SN     | NRND   | PLCC         | FN      | 28   | 750 | Green (RoHS<br>& no Sb/Br) | SN               | Level-2A-245C-4<br>WEEK |              | TP3404V        |         |

| TP3404V/NOPB     | NRND   | PLCC         | FN      | 28   | 35  | Green (RoHS<br>& no Sb/Br) | SN               | Level-3-245C-168 HR     |              | TP3404V        |         |

(1) The marketing status values are defined as follows:

**ACTIVE:** Product device recommended for new designs.

LIFEBUY: TI has announced that the device will be discontinued, and a lifetime-buy period is in effect.

NRND: Not recommended for new designs. Device is in production to support existing customers, but TI does not recommend using this part in a new design.

PREVIEW: Device has been announced but is not in production. Samples may or may not be available.

**OBSOLETE:** TI has discontinued the production of the device.

(2) Eco Plan - The planned eco-friendly classification: Pb-Free (RoHS), Pb-Free (RoHS Exempt), or Green (RoHS & no Sb/Br) - please check http://www.ti.com/productcontent for the latest availability information and additional product content details.

**TBD:** The Pb-Free/Green conversion plan has not been defined.

**Pb-Free (RoHS):** TI's terms "Lead-Free" or "Pb-Free" mean semiconductor products that are compatible with the current RoHS requirements for all 6 substances, including the requirement that lead not exceed 0.1% by weight in homogeneous materials. Where designed to be soldered at high temperatures, TI Pb-Free products are suitable for use in specified lead-free processes.

**Pb-Free (RoHS Exempt):** This component has a RoHS exemption for either 1) lead-based flip-chip solder bumps used between the die and package, or 2) lead-based die adhesive used between the die and leadframe. The component is otherwise considered Pb-Free (RoHS compatible) as defined above.

Green (RoHS & no Sb/Br): TI defines "Green" to mean Pb-Free (RoHS compatible), and free of Bromine (Br) and Antimony (Sb) based flame retardants (Br or Sb do not exceed 0.1% by weight in homogeneous material)

- (3) MSL, Peak Temp. The Moisture Sensitivity Level rating according to the JEDEC industry standard classifications, and peak solder temperature.

- (4) There may be additional marking, which relates to the logo, the lot trace code information, or the environmental category on the device.

- (5) Multiple Device Markings will be inside parentheses. Only one Device Marking contained in parentheses and separated by a "~" will appear on a device. If a line is indented then it is a continuation of the previous line and the two combined represent the entire Device Marking for that device.

- (6) Lead/Ball Finish Orderable Devices may have multiple material finish options. Finish options are separated by a vertical ruled line. Lead/Ball Finish values may wrap to two lines if the finish value exceeds the maximum column width.

**Important Information and Disclaimer:** The information provided on this page represents TI's knowledge and belief as of the date that it is provided. TI bases its knowledge and belief on information provided by third parties, and makes no representation or warranty as to the accuracy of such information. Efforts are underway to better integrate information from third parties. TI has taken and continues to take reasonable steps to provide representative and accurate information but may not have conducted destructive testing or chemical analysis on incoming materials and chemicals. TI and TI suppliers consider certain information to be proprietary, and thus CAS numbers and other limited information may not be available for release.

# **PACKAGE OPTION ADDENDUM**

30-Oct-2013

| In no event shall TI's liability arising out of such information exceed the | otal purchase price of the TI part(s) at issue in this document sold by | TI to Customer on an annual basis. |

|-----------------------------------------------------------------------------|-------------------------------------------------------------------------|------------------------------------|

|-----------------------------------------------------------------------------|-------------------------------------------------------------------------|------------------------------------|

## FN (S-PQCC-J\*\*)

#### 20 PIN SHOWN

## PLASTIC J-LEADED CHIP CARRIER

NOTES: A. All linear dimensions are in inches (millimeters).

B. This drawing is subject to change without notice.

C. Falls within JEDEC MS-018

#### IMPORTANT NOTICE

Texas Instruments Incorporated and its subsidiaries (TI) reserve the right to make corrections, enhancements, improvements and other changes to its semiconductor products and services per JESD46, latest issue, and to discontinue any product or service per JESD48, latest issue. Buyers should obtain the latest relevant information before placing orders and should verify that such information is current and complete. All semiconductor products (also referred to herein as "components") are sold subject to TI's terms and conditions of sale supplied at the time of order acknowledgment.

TI warrants performance of its components to the specifications applicable at the time of sale, in accordance with the warranty in TI's terms and conditions of sale of semiconductor products. Testing and other quality control techniques are used to the extent TI deems necessary to support this warranty. Except where mandated by applicable law, testing of all parameters of each component is not necessarily performed.

TI assumes no liability for applications assistance or the design of Buyers' products. Buyers are responsible for their products and applications using TI components. To minimize the risks associated with Buyers' products and applications, Buyers should provide adequate design and operating safeguards.

TI does not warrant or represent that any license, either express or implied, is granted under any patent right, copyright, mask work right, or other intellectual property right relating to any combination, machine, or process in which TI components or services are used. Information published by TI regarding third-party products or services does not constitute a license to use such products or services or a warranty or endorsement thereof. Use of such information may require a license from a third party under the patents or other intellectual property of the third party, or a license from TI under the patents or other intellectual property of TI.

Reproduction of significant portions of TI information in TI data books or data sheets is permissible only if reproduction is without alteration and is accompanied by all associated warranties, conditions, limitations, and notices. TI is not responsible or liable for such altered documentation. Information of third parties may be subject to additional restrictions.

Resale of TI components or services with statements different from or beyond the parameters stated by TI for that component or service voids all express and any implied warranties for the associated TI component or service and is an unfair and deceptive business practice. TI is not responsible or liable for any such statements.

Buyer acknowledges and agrees that it is solely responsible for compliance with all legal, regulatory and safety-related requirements concerning its products, and any use of TI components in its applications, notwithstanding any applications-related information or support that may be provided by TI. Buyer represents and agrees that it has all the necessary expertise to create and implement safeguards which anticipate dangerous consequences of failures, monitor failures and their consequences, lessen the likelihood of failures that might cause harm and take appropriate remedial actions. Buyer will fully indemnify TI and its representatives against any damages arising out of the use of any TI components in safety-critical applications.

In some cases, TI components may be promoted specifically to facilitate safety-related applications. With such components, TI's goal is to help enable customers to design and create their own end-product solutions that meet applicable functional safety standards and requirements. Nonetheless, such components are subject to these terms.

No TI components are authorized for use in FDA Class III (or similar life-critical medical equipment) unless authorized officers of the parties have executed a special agreement specifically governing such use.

Only those TI components which TI has specifically designated as military grade or "enhanced plastic" are designed and intended for use in military/aerospace applications or environments. Buyer acknowledges and agrees that any military or aerospace use of TI components which have *not* been so designated is solely at the Buyer's risk, and that Buyer is solely responsible for compliance with all legal and regulatory requirements in connection with such use.

TI has specifically designated certain components as meeting ISO/TS16949 requirements, mainly for automotive use. In any case of use of non-designated products, TI will not be responsible for any failure to meet ISO/TS16949.

Products Applications

Audio www.ti.com/audio Automotive and Transportation www.ti.com/automotive Communications and Telecom **Amplifiers** amplifier.ti.com www.ti.com/communications **Data Converters** dataconverter.ti.com Computers and Peripherals www.ti.com/computers **DLP® Products** www.dlp.com Consumer Electronics www.ti.com/consumer-apps

DSP **Energy and Lighting** dsp.ti.com www.ti.com/energy Clocks and Timers www.ti.com/clocks Industrial www.ti.com/industrial Interface interface.ti.com Medical www.ti.com/medical logic.ti.com Logic Security www.ti.com/security

Power Mgmt power.ti.com Space, Avionics and Defense www.ti.com/space-avionics-defense

Microcontrollers <u>microcontroller.ti.com</u> Video and Imaging <u>www.ti.com/video</u>

RFID www.ti-rfid.com

OMAP Applications Processors <a href="www.ti.com/omap">www.ti.com/omap</a> TI E2E Community <a href="e2e.ti.com">e2e.ti.com</a>

Wireless Connectivity <u>www.ti.com/wirelessconnectivity</u>