# Driver for segmented LCD module with key input function BU9768AK / BU9768AKV

The BU9768AK / BU9768AKV are man-machine interface ICs with key input, designed for portable multimedia terminals and other devices. They can be used as drivers for operation mode display LCD panels on portable terminals, household products, car stereos, and other appliances. Up to 126 cells can be displayed, and up to 30 keys can be input.

Also, a maximum of four outputs are possible using expansion pins. (The number of outputs for each pin can be changed using control codes.)

# Applications

Portable multi-media terminals, POS terminals, wireless radios, telephones, cameras, VCRs, movie projectors, car stereos, others

### Features

- 1) Drive of up to 42 segment outputs, three common outputs, and up to 126 cells is possible.

- 2) Up to 30 keys can be input.

- A maximum of four pins can be used as output pins for expansion.

- 4) 1 / 3 duty drive.

- A bias of 1 / 2 or 1 / 3 can be selected for the LCD display power supply.

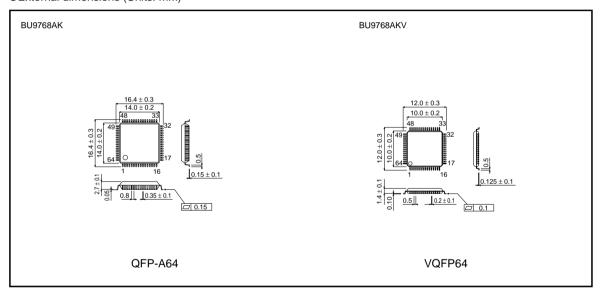

# Block diagram

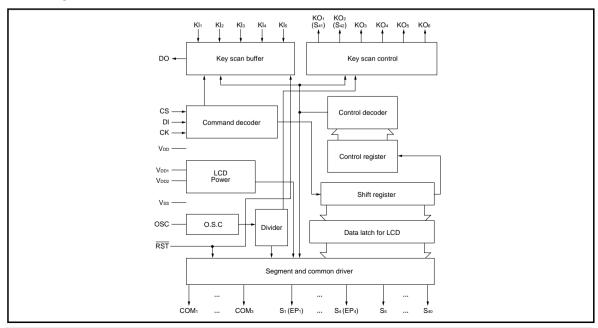

# Pin assignments

Fig.1

# Pin descriptions

| Pin No. | Pin name             | 1/0 | Function                                                                                                                                                                                                                                                                                                 | Processing if not used |

|---------|----------------------|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------|

| 1 ~ 4   | S1 (EP1) ~ S4 (EP4)  | 0   | Output pins for switching between segment output and expansion pin output. Switched using control codes $P_0$ and $P_1$ . When expansion pins are used, these output set data (1 or 0).                                                                                                                  | OPEN                   |

| 5 ~ 40  | S5 ~ S40             | 0   | Segment output pins. These output waveforms correspond to serial data input from DI.                                                                                                                                                                                                                     | OPEN                   |

| 41 ~ 43 | COM1 ~ COM3          | 0   | Common output pins                                                                                                                                                                                                                                                                                       | OPEN                   |

| 44, 45  | KO1 (S41), KO2 (S42) | 0   | Output pins for switching between key scan output and segment output. Switching is enabled using control codes $K_0$ and $K_1$ .                                                                                                                                                                         | OPEN                   |

| 46 ~ 49 | KO3 ~ KO6            | 0   | Key scan output pins                                                                                                                                                                                                                                                                                     | OPEN                   |

| 50 ~ 54 | KI1 ~ KI5            | I   | Key scan input pins                                                                                                                                                                                                                                                                                      | OPEN                   |

| 55      | RST                  | I   | Reset input pin for Low Active state. Segment and common outputs are fixed at LOW level while RST is LOW, and all displays disappear. Data for LCD displays is not reset. All data in the key scan buffer is cleared.                                                                                    | Vod                    |

| 57      | VDD1                 | _   | Internal reference voltage for LCD. When using in the $1/2$ bias mode, this should be connected to $V_{\text{DD2}}$ .                                                                                                                                                                                    | _                      |

| 58      | VDD2                 | _   | Internal reference voltage for LCD. When using in the 1 / 2 bias mode, this should be connected to V <sub>DD1</sub> .                                                                                                                                                                                    | _                      |

| 60      | OSC                  | _   | Oscillator pin for segment / common alternating waveforms                                                                                                                                                                                                                                                | _                      |

| 61      | DO                   | 0   | Key buffer data output pin. After a key scan has been completed, if key input existed, this changes to LOW. Also, if the key data communications command is input, the contents of the key buffer are output as serial data. Since this is open drain output, it should be used with a pull-up resistor. | OPEN                   |

| 62      | CS                   | I   | Chip select input pin                                                                                                                                                                                                                                                                                    | Vss                    |

| 63      | СК                   | I   | Synchronous clock input pin for data transmission                                                                                                                                                                                                                                                        | Vss                    |

| 64      | DI                   | I   | Data input pin for LCD display                                                                                                                                                                                                                                                                           | Vss                    |

# ● Absolute maximum ratings (Ta = 25°C)

| Parameter           |             | Symbol          | Pin                                 | Limits                        | Unit  |  |

|---------------------|-------------|-----------------|-------------------------------------|-------------------------------|-------|--|

| Power sup           | ply voltage | V <sub>DD</sub> | V <sub>DD</sub>                     | <b>−</b> 0.3 ~ <b>+</b> 7.0   | V     |  |

| Input volta         | ge          | VIN             | RST, OSC, CS, CK, DI, KI1 ~ KI5     | - 0.3 ~ V <sub>DD</sub> + 0.3 | V     |  |

| Output vol          | tage        | Vouт            | OSC, DO, KO1 ~ KO6, EP1 ~ EP4       | - 0.3 ~ V <sub>DD</sub> + 0.3 | V     |  |

|                     |             | Іоит (1)        | COM <sub>1</sub> ~ COM <sub>3</sub> | mA                            |       |  |

| 0                   |             | Іоит (2)        | EP <sub>1</sub> ~ EP <sub>4</sub> 5 |                               | mA    |  |

| Output cur          | rent        | Іоит (3)        | S1 ~ S40                            | 300                           | μΑ    |  |

|                     |             | Іоит (4)        | KO <sub>1</sub> ~ KO <sub>6</sub>   | 1                             | mA    |  |

| Power               | BU9768AK    | Б               |                                     | 800                           | mW*   |  |

| dissipation         | BU9768AKV   | Pd              | _                                   | 750                           | IIIVV |  |

| Storage temperature |             | Tstg            | _                                   | - 55 ~ + 125                  | °C    |  |

<sup>\*</sup> This is the maximum voltage which may be applied to the Vss pin.

Reduced by 8.0mW (AK) or 7.5mW (AKV) for each increase in Ta of 1°C over 25°C.

# ●Recommended operating conditions (Ta = 25°C)

| Parameter             | Symbol          | Pin             | Min.  | Тур. | Max.  | Unit |

|-----------------------|-----------------|-----------------|-------|------|-------|------|

| Power supply voltage  | V <sub>DD</sub> | V <sub>DD</sub> | + 4.5 | _    | + 6.0 | V    |

| Operating temperature | Topr            | _               | - 40  | _    | + 85  | °C   |

# ●Electrical characteristics (unless otherwise noted, V<sub>DD</sub> = 4.5V to 6.0V, Ta = 25°C)

| Parameter                         | Symbol   | Pin             | Min.           | Тур.       | Max.           | Unit | Conditions    |

|-----------------------------------|----------|-----------------|----------------|------------|----------------|------|---------------|

| Input high level                  | VIH (1)  | RST, CS, CK, DI | 0.8Vpd         | _          | Vdd            | V    |               |

| voltage                           | VIH (2)  | KI1 ~ KI5       | 0.6Vpd         | _          | Vdd            | V    |               |

| Input low level                   | Vı∟ (1)  | RST, CS ,CK, DI | 0              | _          | 0.2Vdd         | V    |               |

| voltage                           | VIL (2)  | KI1 ~ KI5       | 0              | _          | 0.2Vpd         | V    |               |

| Input high level current          | lін      | RST, CS, CK, DI | _              | _          | 6.0            | μΑ   | V1 = VDD      |

| Input low level current           | lı∟      | RST, CS, CK, DI | _              | _          | 6.0            | μΑ   | V1 = Vss      |

| Input floating voltage            | Vif      | KI1 ~ KI5       | _              | _          | 0.05Vpp        | V    |               |

| Pull-down resistance              | Rpd      | KI1 ~ KI5       | 50             | 100        | 200            | kΩ   | VDD = 5.0V    |

| Output off leakage current        | Іоггн    | DO              | _              | _          | 6.0            | μА   | Vo = VDD      |

|                                   | Vон (1)  | KO1 ~ KO6       | VDD - 2.0      | VDD - 1.0  | VDD - 0.5      | V    | Io = - 1mA    |

| Output high level                 | Vон (2)  | EP1 ~ EP4       | VDD - 1.5      | _          | _              | V    | Ιο = – 300μΑ  |

| voltage                           | Vон (3)  | S1 ~ S42        | _              | VDD - 1.0  | _              | V    | Io = - 20μA   |

|                                   | Vон (4)  | COM1 ~ COM3     | _              | VDD - 1.0  | _              | V    | Io = - 100μA  |

|                                   | Vol (1)  | KO1 ~ KO6       | 0.5            | 1.0        | 2.0            | V    | Ιο = 50μΑ     |

| Output low level                  | Vol (2)  | EP1 ~ EP4       | _              | _          | 1.0            | V    | Ιο = 300μΑ    |

| voltage                           | Vol (3)  | S1 ~ S42        | _              | 1.0        | _              | V    | Ιο = 20μΑ     |

| voltage                           | Vol (4)  | COM1 ~ COM3     | _              | 1.0        | _              | V    | Io = 100μA    |

|                                   | Vol (5)  | DO              | _              | 0.2 (200Ω) | 0.5 (500Ω)     | V    | Io = 1mA      |

|                                   | Vмід (1) | COM1 ~ COM3     | 1 / 2VDD — 1.0 | _          | 1 / 2VDD + 1.0 | V    | 1 / 2bias     |

| 0 1 1 1 1 1 1 1 1 1 1 1 1         | Vмід (2) | S1 ~ S42        | 2/3Vpp - 1.0   | _          | 2/3Vpp + 1.0   | V    | 1 / 3bias     |

| Output intermediate level voltage | Vмід (3) | COM1 ~ COM3     | 2/3Vpp - 1.0   | _          | 2/3Vpp + 1.0   | V    | 1 / 3bias     |

|                                   | Vмід (4) | S1 ~ S42        | 1/3Vpp - 1.0   | _          | 1/3Vpp + 1.0   | V    | 1 / 3bias     |

|                                   | Vмід (5) | COM1 ~ COM3     | 1/3Vpp - 1.0   | _          | 1/3Vpp + 1.0   | V    | 1 / 3bias     |

| Dower supply sures of             | IDD1     | _               | _              | 30         | 70             | μΑ   | In sleep mode |

| Power supply current              | IDD2     | _               | _              | 200        | 500            | μΑ   | fosc = 38kHz  |

$<sup>\ \</sup>bigcirc$  Not designed for radiation resistance.

# ●AC timing characteristics (V<sub>DD</sub> = 4.5V to 6.0V, Ta = 25°C)

| Parameter                    | Symbol             | Pin        | Min. | Тур. | Max.     | Unit |

|------------------------------|--------------------|------------|------|------|----------|------|

| Rise time                    | tu                 | CS, CK, DI | _    | _    | 300      | ns   |

| Fall time                    | <b>t</b> d         | CS, CK, DI | _    | _    | 300      | ns   |

| Data setup time              | ts (1)             | CK, DI     | 100  | _    | _        | ns   |

| Data hold time               | t <sub>h</sub> (1) | CK, DI     | 100  | _    | _        | ns   |

| CS wait time                 | tcw                | CS, CK     | 100  | _    | _        | ns   |

| CS setup time                | ts (2)             | CS, CK     | 100  | _    | _        | ns   |

| CS hold time                 | t <sub>h</sub> (2) | CS, CK     | 100  | _    | _        | ns   |

| CK HIGH level time           | tн                 | СК         | 100  | _    | _        | ns   |

| CK LOW level time            | t∟                 | СК         | 100  | _    | _        | ns   |

| DO output dolov timo         | <b>4</b>           | DO         |      |      | 200      | 200  |

| D0 output delay time         | <b>t</b> dl        | DO         |      | _    | (Note 1) | ns   |

| Oscillation guaranteed range | fosc               | osc        | 19   | 38   | 76       | kHz  |

(Note 1) Since DO is open drain output, the output delay time varies depending on the pull-up resistance. (Note 2) Values measured for attachments of R =  $47k\Omega$ , C = 1000pF.

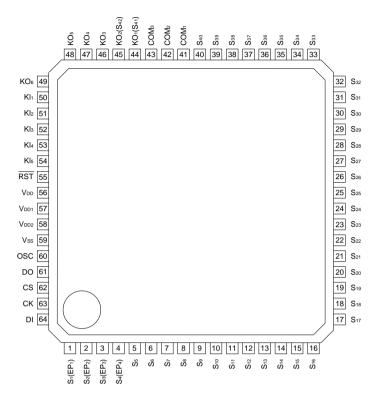

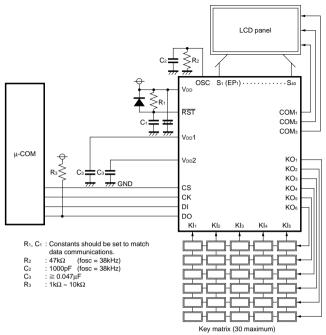

# ●Application example (1 / 2 bias mode)

Fig. 2

<sup>\*</sup> The pull-up resistor value should be set to a value so that the waveform is not destroyed by the wiring capacitance or other factors.

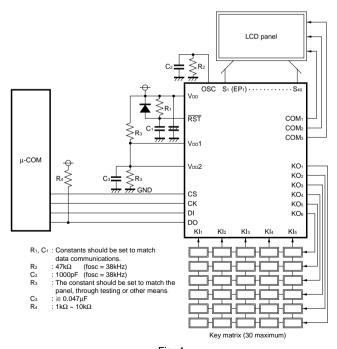

(1 / 3 bias mode)

Fig. 3

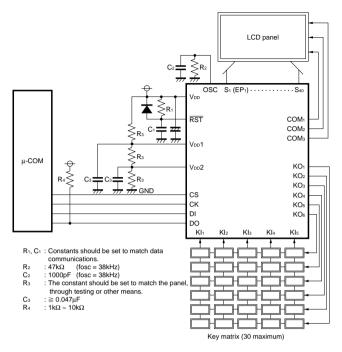

(1 / 2 bias mode)

Fig. 4

<sup>\*</sup> The pull-up resistor value should be set to a value so that the waveform is not destroyed by the wiring capacitance or other factors.

(1/3 bias mode)

Fig. 5

\* The pull-up resistor value should be set to a value so that the waveform is not destroyed by the wiring capacitance or other factors.

## Circuit operation

# (1) Data communications

The BU9768AK / BU9768AKV are able to receive LCD display data output from the controller, as well as the results of key scans.

# 1) LCD display data output (from controller)

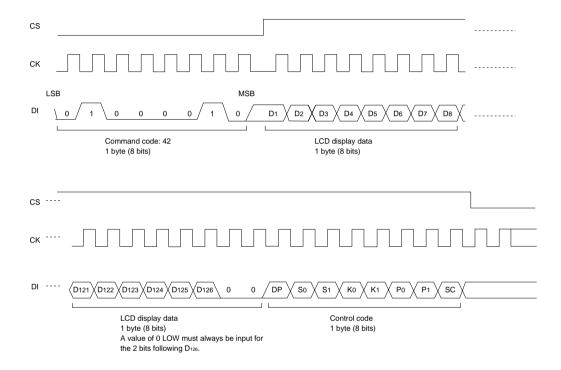

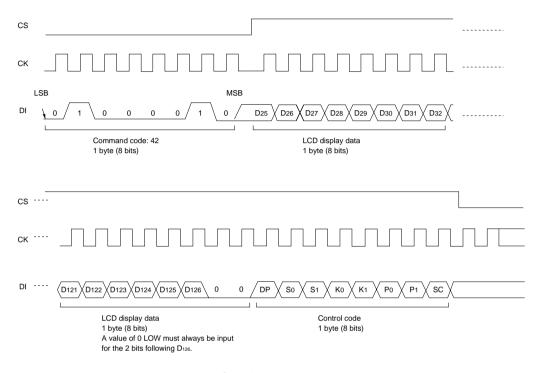

When LCD data is output, the command code "42" must be output at the beginning of the data. Fig. 6 shows an example of LCD display data output.

Fig. 6 Example of LCD display data transmission

- ① During the time that CS is LOW, the command code "42" is input synchronized to the CK clock, and CS is then set to HIGH before the rise of the next CK clock.

- 2 The LCD data is sent, and 0 (LOW level) is input for the two bits following D<sub>126</sub>.

- 3 An 8-bit control code is input, and CS is set to LOW.

# Segment data correspondence table

|                                   | СОМз                               | COM <sub>2</sub> | COM <sub>1</sub> |

|-----------------------------------|------------------------------------|------------------|------------------|

|                                   |                                    |                  |                  |

| S <sub>1</sub> (EP <sub>1</sub> ) | D <sub>1</sub> (EP <sub>1</sub> )  | D <sub>2</sub>   | D <sub>3</sub>   |

| S <sub>2</sub> (EP <sub>2</sub> ) | D4 (EP2)                           | D₅               | D <sub>6</sub>   |

| S <sub>3</sub> (EP <sub>3</sub> ) | D7 (EP3)                           | D <sub>8</sub>   | D <sub>9</sub>   |

| S4 (EP4)                          | D <sub>10</sub> (EP <sub>4</sub> ) | D <sub>11</sub>  | D <sub>12</sub>  |

| <b>S</b> 5                        | D <sub>13</sub>                    | D <sub>14</sub>  | D <sub>15</sub>  |

| S <sub>6</sub>                    | D <sub>16</sub>                    | D <sub>17</sub>  | D <sub>18</sub>  |

| S <sub>7</sub>                    | D <sub>19</sub>                    | D <sub>20</sub>  | D <sub>21</sub>  |

| S <sub>8</sub>                    | D <sub>22</sub>                    | D <sub>23</sub>  | D <sub>24</sub>  |

| S <sub>9</sub>                    | D <sub>25</sub>                    | D <sub>26</sub>  | D <sub>27</sub>  |

| <b>S</b> 10                       | D <sub>28</sub>                    | D <sub>29</sub>  | D <sub>30</sub>  |

| S <sub>11</sub>                   | D31                                | D <sub>32</sub>  | D33              |

| S <sub>12</sub>                   | D34                                | D <sub>35</sub>  | D36              |

| <b>S</b> 13                       | <b>D</b> 37                        | D <sub>38</sub>  | D39              |

| S <sub>14</sub>                   | D40                                | D41              | D <sub>42</sub>  |

| <b>S</b> 15                       | D43                                | D44              | D <sub>45</sub>  |

| <b>S</b> 16                       | D46                                | D47              | D48              |

| S <sub>17</sub>                   | D49                                | D <sub>50</sub>  | D <sub>51</sub>  |

| S <sub>18</sub>                   | D <sub>52</sub>                    | D <sub>53</sub>  | D <sub>54</sub>  |

| <b>S</b> 19                       | <b>D</b> 55                        | D <sub>56</sub>  | D <sub>57</sub>  |

| S <sub>20</sub>                   | D <sub>58</sub>                    | D59              | D <sub>60</sub>  |

| S <sub>21</sub>                   | D <sub>61</sub>                    | D <sub>62</sub>  | D <sub>63</sub>  |

|                                    | СОМз             | COM <sub>2</sub> | COM <sub>1</sub> |

|------------------------------------|------------------|------------------|------------------|

| S <sub>22</sub>                    | D <sub>64</sub>  | D <sub>65</sub>  | D66              |

| S <sub>23</sub>                    | D <sub>67</sub>  | D <sub>68</sub>  | D69              |

| S <sub>24</sub>                    | D <sub>70</sub>  | D <sub>71</sub>  | D <sub>72</sub>  |

| S <sub>25</sub>                    | D <sub>73</sub>  | D74              | D <sub>75</sub>  |

| S <sub>26</sub>                    | D <sub>76</sub>  | D <sub>77</sub>  | D <sub>78</sub>  |

| S <sub>27</sub>                    | D <sub>79</sub>  | D <sub>80</sub>  | D <sub>81</sub>  |

| S <sub>28</sub>                    | D <sub>82</sub>  | D83              | D <sub>84</sub>  |

| S <sub>29</sub>                    | D <sub>85</sub>  | D <sub>86</sub>  | D87              |

| <b>S</b> 30                        | D <sub>88</sub>  | D89              | D90              |

| <b>S</b> 31                        | D <sub>91</sub>  | D <sub>92</sub>  | D93              |

| S <sub>32</sub>                    | D <sub>94</sub>  | D <sub>95</sub>  | D <sub>96</sub>  |

| <b>S</b> 33                        | D <sub>97</sub>  | D <sub>98</sub>  | D99              |

| <b>S</b> 34                        | D <sub>100</sub> | D <sub>101</sub> | D <sub>102</sub> |

| <b>S</b> 35                        | D <sub>103</sub> | D <sub>104</sub> | D <sub>105</sub> |

| S36                                | D <sub>106</sub> | D <sub>107</sub> | D <sub>108</sub> |

| <b>S</b> 37                        | D <sub>109</sub> | D <sub>110</sub> | D <sub>111</sub> |

| S <sub>38</sub>                    | D <sub>112</sub> | D113             | D <sub>114</sub> |

| <b>S</b> 39                        | D <sub>115</sub> | D <sub>116</sub> | D <sub>117</sub> |

| S <sub>40</sub>                    | D <sub>118</sub> | D119             | D <sub>120</sub> |

| KO <sub>1</sub> (S <sub>41</sub> ) | D <sub>121</sub> | D <sub>122</sub> | D <sub>123</sub> |

| KO <sub>2</sub> (S <sub>42</sub> ) | D <sub>124</sub> | D <sub>125</sub> | D <sub>126</sub> |

## 1. If there is an unused segment output

If there is segment output that is not used, depending on the panel, the transmission of the LCD display data can be simplified by deciding the pin or pins to be used starting from  $S_{40}$  ( $S_{42}$  if pins 44 and 45 are used as segment output, and  $S_{41}$  if only pin 44 is used as segment output).

Fig. 7 Simplified data communication

This figure shows an example in which the 30 segment outputs from  $S_{11}$  to  $S_{40}$  are used, and assumes that communication is done in units of eight bits (one byte). For this reason, the data of  $S_{9}$  and  $S_{10}$  (from  $D_{25}$  to  $D_{30}$ ), which are not used, is input as dummy data. If the unit is not eight bits, this dummy data can be omitted, in which case the data should be input after the command code, starting from the data of  $D_{31}$ . However, even if Pins 44 and 45 are used as key scan output and not as segment output, the data for  $D_{121}$  to  $D_{126}$  cannot be omitted.

### 2. Control codes

The BU9768AK is designed to support various applications, depending on the combination of control codes used.

DP: Display mode control

Depending on the type of display, either 1 / 2 bias drive or 1 / 3 bias drive may be selected.

1: 1 / 2 bias drive

0: 1/3 bias drive

• So and S1: Sleep mode control

In the sleep modes, all displays are turned off, and the oscillation of the OSC pin is stopped, enabling a lower power consumption. In sleep modes, although all of the displays are turned off, key scans are enabled. For information on key scans in the sleep modes, please refer to pages 15 to 22.

Various sleep modes can be selected, depending on the application.

| Contro         | Control code   |        | Segment / common | osc         | Key scan output |                 |     |                 |     |                 |

|----------------|----------------|--------|------------------|-------------|-----------------|-----------------|-----|-----------------|-----|-----------------|

| S <sub>0</sub> | S <sub>1</sub> | Mode   | output           | pin         | KΟ1             | KO <sub>2</sub> | КОз | KO <sub>4</sub> | KO₅ | KO <sub>6</sub> |

| 0              | 0              | Normal | Output           | Oscillating | Н               | Н               | Н   | Н               | Н   | Н               |

| 0              | 1              | Sleep  | Fixed at LOW     | Stopped     | L               | L               | L   | L               | L   | Н               |

| 1              | 0              | Sleep  | Fixed at LOW     | Stopped     | L               | L               | L   | L               | Н   | Н               |

| 1              | 1              | Sleep  | Fixed at LOW     | Stopped     | Н               | Н               | Н   | Н               | Н   | Н               |

In the Sleep modes, oscillation of the OSC pin stops, but if a button is pressed while the key scan output is on the HIGH line, oscillation begins and a key scan is carried out. When the key scan has been completed, oscillation stops again.

- K<sub>0</sub>, K<sub>1</sub>: Control that switches between key scan and segment output

- P<sub>0</sub>, P<sub>1</sub>: Control that switches between segment and expansion pin output

The output can be switched to match a variety of applications, depending on the combination of the four bits.

|    | Contro         | l code         | )              |                 | scan /<br>ment  |                 | Segm<br>expans  |                 |                | Max. no.<br>of display | Max.<br>key |

|----|----------------|----------------|----------------|-----------------|-----------------|-----------------|-----------------|-----------------|----------------|------------------------|-------------|

| Κo | K <sub>1</sub> | P <sub>0</sub> | P <sub>1</sub> | 44pin           | 45pin           | 1pin            | 2pin            | 3pin            | 4pin           | segments               | input       |

| 0  | 0              | 0              | 0              | KO <sub>1</sub> | KO <sub>2</sub> | S <sub>1</sub>  | S <sub>2</sub>  | S <sub>3</sub>  | S <sub>4</sub> | 120                    | 30          |

| 0  | 0              | 0              | 1              | KO <sub>1</sub> | KO <sub>2</sub> | EP <sub>1</sub> | EP <sub>2</sub> | S <sub>3</sub>  | S <sub>4</sub> | 114                    | 30          |

| 0  | 0              | 1              | 0              | KO <sub>1</sub> | KO <sub>2</sub> | EP <sub>1</sub> | EP <sub>2</sub> | EP₃             | S <sub>4</sub> | 111                    | 30          |

| 0  | 0              | 1              | 1              | KO <sub>1</sub> | KO <sub>2</sub> | EP <sub>1</sub> | EP <sub>2</sub> | EP₃             | EP4            | 108                    | 30          |

| 0  | 1              | 0              | 0              | S <sub>41</sub> | KO <sub>2</sub> | S <sub>1</sub>  | S <sub>2</sub>  | S <sub>3</sub>  | S <sub>4</sub> | 123                    | 25          |

| 0  | 1              | 0              | 1              | S <sub>41</sub> | KO <sub>2</sub> | EP <sub>1</sub> | EP <sub>2</sub> | S <sub>3</sub>  | S <sub>4</sub> | 117                    | 25          |

| 0  | 1              | 1              | 0              | S <sub>41</sub> | KO <sub>2</sub> | EP <sub>1</sub> | EP <sub>2</sub> | EP₃             | S <sub>4</sub> | 114                    | 25          |

| 0  | 1              | 1              | 1              | S <sub>41</sub> | KO <sub>2</sub> | EP <sub>1</sub> | EP <sub>2</sub> | EP₃             | EP4            | 111                    | 25          |

| 1  | *              | 0              | 0              | S <sub>41</sub> | S42             | S <sub>1</sub>  | S <sub>2</sub>  | S <sub>3</sub>  | S <sub>4</sub> | 126                    | 20          |

| 1  | *              | 0              | 1              | S <sub>41</sub> | S42             | EP <sub>1</sub> | EP <sub>2</sub> | S <sub>3</sub>  | S <sub>4</sub> | 120                    | 20          |

| 1  | *              | 1              | 0              | S <sub>41</sub> | S42             | EP <sub>1</sub> | EP <sub>2</sub> | EP3             | S <sub>4</sub> | 117                    | 20          |

| 1  | *              | 1              | 1              | S <sub>41</sub> | S42             | EP <sub>1</sub> | EP <sub>2</sub> | EP <sub>3</sub> | EP4            | 114                    | 20          |

<sup>\*</sup> Don't Care

• SC: Control switching the LCD display on and off

Switching the LCD display on and off can be done regardless of the input data.

- 1: Display off

- 0: Display on (when displayed, displays can be obtained in accordance with the input data.)

Note: When the power supply is turned on, the following settings are in effect for control codes. These initial settings for control codes should be changed to match the mode being used.

When the power supply is turned on:

$(DP, S_0, S_1, K_0, K_1, P_0, P_1, SC) = (0, 0, 0, 1, 1, 0, 0, 0)$

# 2) Transmission of key data

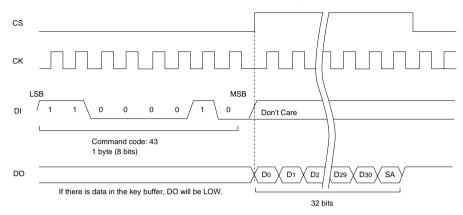

A command code of "43" should be input in order to output the results of a key scan to the BU9768AK / BU9768AKV.

Fig. 8 Transmission of key data

If CS is changed to HIGH level after the command code is input, the data in the key buffer is output synchronized to the rise of CK.

# Key data correspondence table

|                                    | KI₁             | KI <sub>2</sub> | KIз             | KI <sub>4</sub> | KI <sub>5</sub> |

|------------------------------------|-----------------|-----------------|-----------------|-----------------|-----------------|

| KO <sub>1</sub> (S <sub>41</sub> ) | D <sub>1</sub>  | D <sub>2</sub>  | Dз              | D4              | D <sub>5</sub>  |

| KO <sub>2</sub> (S <sub>42</sub> ) | D <sub>6</sub>  | D <sub>7</sub>  | D <sub>8</sub>  | D <sub>9</sub>  | D <sub>10</sub> |

| КО₃                                | D <sub>11</sub> | D <sub>12</sub> | D <sub>13</sub> | D <sub>14</sub> | D <sub>15</sub> |

| KO <sub>4</sub>                    | D <sub>16</sub> | D <sub>17</sub> | D <sub>18</sub> | D <sub>19</sub> | D <sub>20</sub> |

| KO <sub>5</sub>                    | D <sub>21</sub> | D <sub>22</sub> | D <sub>23</sub> | D <sub>24</sub> | D <sub>25</sub> |

| KO <sub>6</sub>                    | D <sub>26</sub> | D <sub>27</sub> | D <sub>28</sub> | D <sub>29</sub> | D30             |

- The data D<sub>0</sub>, which is output synchronized to the rise of CS, is unstable and should not be used.

- The output SA of the 32nd bit is a state acknowledge signal and outputs the current BU9768AK / BU9768AKV mode.

SA: State acknowledge signal In normal modes: SA = LOW In sleep modes : SA = HIGH

# (2) Key scan operation

With the BU9768AK / BU9768AKV, up to 30 key inputs can be received.

Fig. 9 Key scan operation

One key scan requires 15ms (if fosc = 38kHz, 582 / fosc (sec)). Key scans which are shorter than this time cannot be received. Also, in order to prevent chattering, the key scan waveform (KO output) reaches the HIGH level twice during one key scan. After scanning has been carried out twice, the data from the two scans is compared, and if the data for all of the keys does not match, an error occurs.

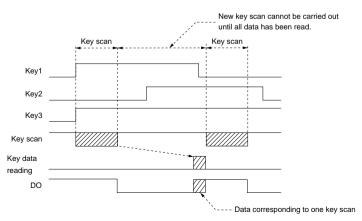

# 1) Key scans and key data communications

With the BU9768AK / BU9768AKV, if normal key input is received, DO changes from HIGH to LOW, so if DO is connected to the interrupt input pin of the controller, interrupt processing can be carried out based on the key input. Also, after DO changes to LOW following completion of a key scan, a new key scan cannot be carried out until all of the key data has been read.

If multiple keys are pressed at once, multiple key data is set for the various key inputs to be distinguished.

Fig. 10 Relationship between key scan and data communications

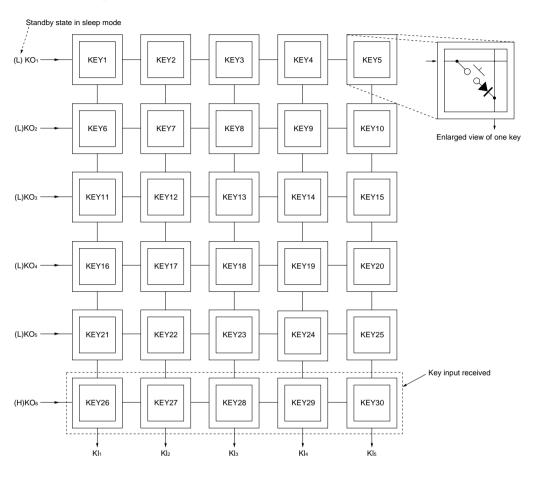

# 2) Key scans in sleep modes

In sleep modes, depending on the mode, the key scan standby state of the KO pin is restricted.

Fig. 11 Example of key matrix configuration

(The diodes installed on each key are to prevent erroneous recognition if multiple keys are pressed.)

The figure above assumes that the control codes  $S_0$  and  $S_1$  have been set to 0 and 1, respectively. In this case, if any key between key 26 and key 30 is pressed, an HIGH level is input on the KIn line, oscillation begins, and a key scan is carried out. If any key between key 1 and key 25 is pressed, all of the KIn lines remain at LOW level, and no key scan is carried out. Oscillation resumes when the key scan has been completed.

If key input in a sleep mode is to be used and interrupt processing carried out, a key on a KOn = HIGH line should be used.

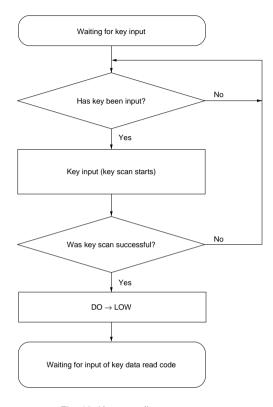

# 3) Operation flow in a key scan

The flow of operations taking place during a key scan is shown below.

Fig. 12 Key scan flow

The "successful" judgment of the key scan shown in the illustration is based on the data from the two key scans matching for all of the keys, as described on page 13.

If an error occurs, the key scan is carried out once again after the first key scan has been completed if a key has remained pressed, and continues to be carried out as long as the key is pressed, until it is successfully completed. After a key scan has been successfully completed, no new key scans can be carried out until reading of the key data has been completed.

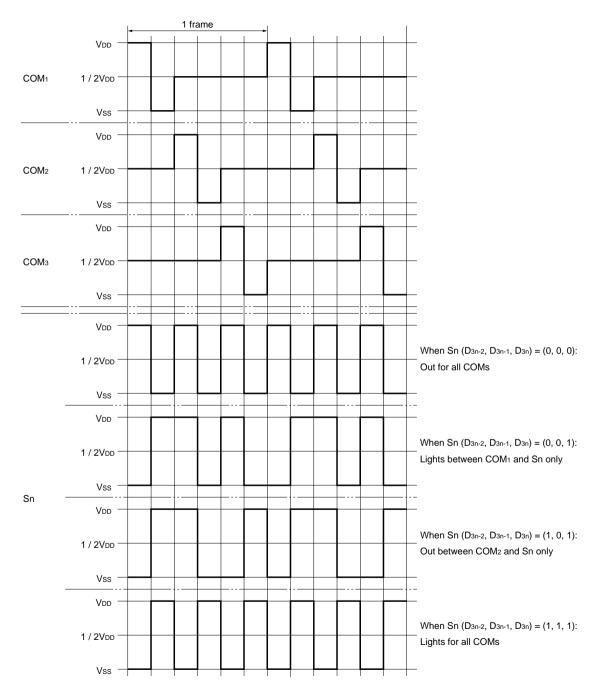

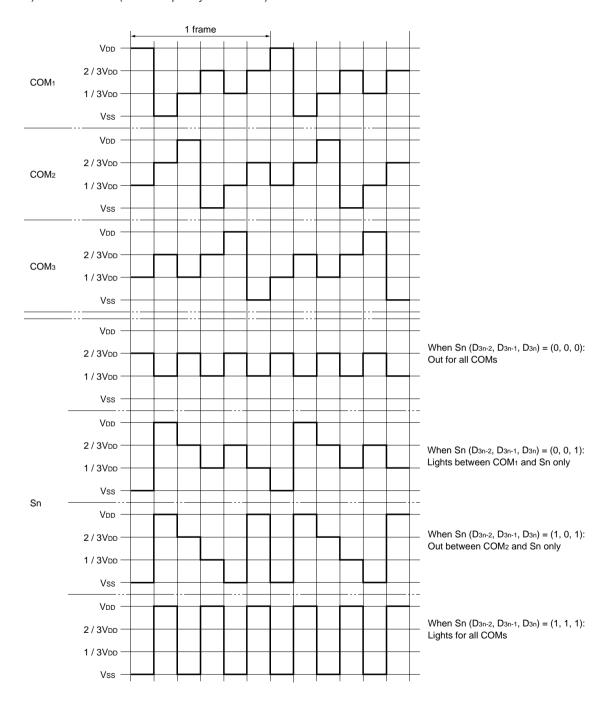

- (3) Output waveforms

- 1) 1 / 2 bias mode (frame frequency = fosc / 384)

2) 1 / 3 bias mode (frame frequency = fosc / 384)

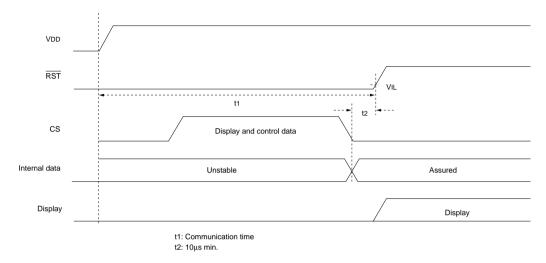

# (4) RST and display control

After the power supply has been turned on, because the internal data of the BU9768AK / BU9768AKV (D<sub>1</sub> to D<sub>126</sub>) is unstable,  $\overline{RST}$  goes LOW at the same time that the power supply is turned on. While  $\overline{RST}$  is LOW, data is transmitted using the microcomputer, and when data transmission has been completed,  $\overline{RST}$  can be set to HIGH to prevent meaningless displays. (For the states of control codes when the power supply is turned on, see page 11.)

Fig. 13 Communication, display and RST timing

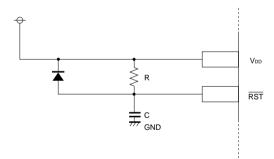

Fig. 14 Example of RST pin processing

In the circuit example shown above, the value of t1 is determined by the value of the capacitor and resistor. The value should be set in such a way that the constant determined by the capacitor and resistor is the initialized communication time + t2.

## Operation notes

(1) Using the product with the synchronous clock stopped

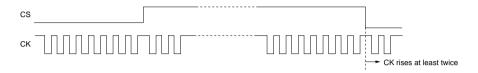

If the synchronous clock is to be stopped during the period that data is not being transmitted, program the product so that the rise of CK is input at least twice after the fall of CS.

Fig. 15 When CK is stopped at HIGH

Fig. 16 When CK is stopped at LOW

(2) Precautions concerning key scans when the power supply is turned on

To carry out a key scan immediately after the power supply is turned on, without transmitting data, the parameters must be set so that the following conditions are met.

- 1) The rise of the synchronous clock pulse is input to the CK pin at least twice.

- 2) Since input can only be received from keys on the KO₃ to KO₆ line, other keys should not be used for functions such as interrupts. (For information on the status when the power supply is turned on, please see page 11.)

- \* If data is being transferred before a key scan is carried out, after the power supply is turned on, these precautions do not apply.

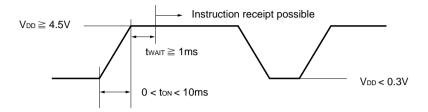

Make sure of the following when resetting when the power is on.

- When using the external reset terminal, make RST = "L" at 1ms or more with V<sub>DD</sub> at 4.5V or more.

- When not using the external reset terminal, VDD has to satisfy the following conditions.

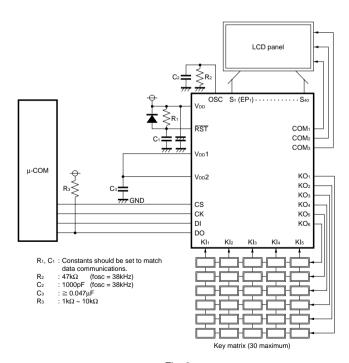

# External dimensions (Units: mm)