# ***LUPA-4000***

**4M Pixel

CMOS Image Sensor**

## **Datasheet**

**Document history record**

| <b>Issue</b> | <b>Date</b>       | <b>Description of changes</b>                                                                                                   |

|--------------|-------------------|---------------------------------------------------------------------------------------------------------------------------------|

| 1.0          | August, 2004      | Origination                                                                                                                     |

| 1.0          | November, 2004    | Correct bias voltages precharge_bias and Pre_load                                                                               |

| 1.1          | November, 2004    | Updated timing diagrams and timing explanation                                                                                  |

| 1.2          | December 23, 2004 | Added Cypress equivalent part numbers, ordering information<br>Added Cypress Document # 38-05712 Rev ** in the document footer. |

## TABLE OF CONTENTS

|                                                          |           |

|----------------------------------------------------------|-----------|

| <b>1 PREAMBLE .....</b>                                  | <b>5</b>  |

| 1.1 OVERVIEW.....                                        | 5         |

| 1.2 MAIN FEATURES .....                                  | 5         |

| 1.3 PART NUMBER.....                                     | 5         |

| <b>2 SPECIFICATIONS.....</b>                             | <b>6</b>  |

| 2.1 GENERAL SPECIFICATIONS.....                          | 6         |

| 2.2 ELECTRO-OPTICAL SPECIFICATIONS.....                  | 6         |

| 2.2.1 <i>Overview</i> .....                              | 6         |

| 2.2.2 <i>Spectral response curve</i> .....               | 7         |

| 2.2.3 <i>Photo-voltaic response curve</i> .....          | 8         |

| 2.3 FEATURES AND GENERAL SPECIFICATIONS.....             | 9         |

| 2.4 ELECTRICAL SPECIFICATIONS .....                      | 10        |

| 2.4.1 <i>Recommended operating conditions</i> .....      | 10        |

| <b>3 SENSOR ARCHITECTURE .....</b>                       | <b>11</b> |

| 3.1 THE 6-T PIXEL .....                                  | 12        |

| 3.2 FRAME RATE AND WINDOWING.....                        | 13        |

| 3.2.1 <i>Frame rate</i> .....                            | 13        |

| 3.2.2 <i>ROI read out (windowing)</i> .....              | 13        |

| 3.3 OUTPUT AMPLIFIER.....                                | 14        |

| 3.4 PIXEL ARRAY DRIVERS.....                             | 14        |

| 3.5 COLUMN AMPLIFIERS.....                               | 15        |

| 3.6 ANALOG TO DIGITAL CONVERTER.....                     | 15        |

| 3.6.1 <i>ADC timing</i> .....                            | 16        |

| 3.6.2 <i>Setting of the ADC reference voltages</i> ..... | 16        |

| 3.7 SYNCHRONOUS SHUTTER.....                             | 17        |

| 3.8 NON-DESTRUCTIVE READOUT (NDR).....                   | 17        |

| 3.9 OPERATION AND SIGNALLING .....                       | 18        |

| 3.9.1 <i>Power supplies and ground</i> .....             | 18        |

| 3.9.2 <i>Start-up sequence</i> .....                     | 20        |

| 3.9.3 <i>Biassing and analog signals</i> .....           | 20        |

| 3.10 PIXEL ARRAY SIGNALS .....                           | 22        |

| 3.10.1 <i>Digital signals</i> .....                      | 24        |

| 3.10.2 <i>Test signals</i> .....                         | 24        |

| <b>4 TIMING AND READ OUT OF THE IMAGE SENSOR.....</b>    | <b>26</b> |

| 4.1 TIMING OF THE PIXEL ARRAY .....                      | 27        |

| 4.2 READ OUT OF THE IMAGE SENSOR.....                    | 29        |

| 4.2.1 <i>X- and Y-addressing</i> .....                   | 29        |

| 4.2.2 <i>Reduced Row Overhead Time timing</i> .....      | 32        |

| 4.2.2.a Standard timing (200ns) .....                    | 33        |

| 4.2.2.b Back-up timing (ROT =100-200 ns).....            | 33        |

---

|                                                       |           |

|-------------------------------------------------------|-----------|

| 4.2.3 <i>Precharging of the buses</i> .....           | 34        |

| 4.3 SERIAL-PARALLEL-INTERFACE (SPI) .....             | 35        |

| <b>5 PIN LIST</b> .....                               | <b>36</b> |

| <b>6 GEOMETRY AND MECHANICAL SPECIFICATIONS</b> ..... | <b>40</b> |

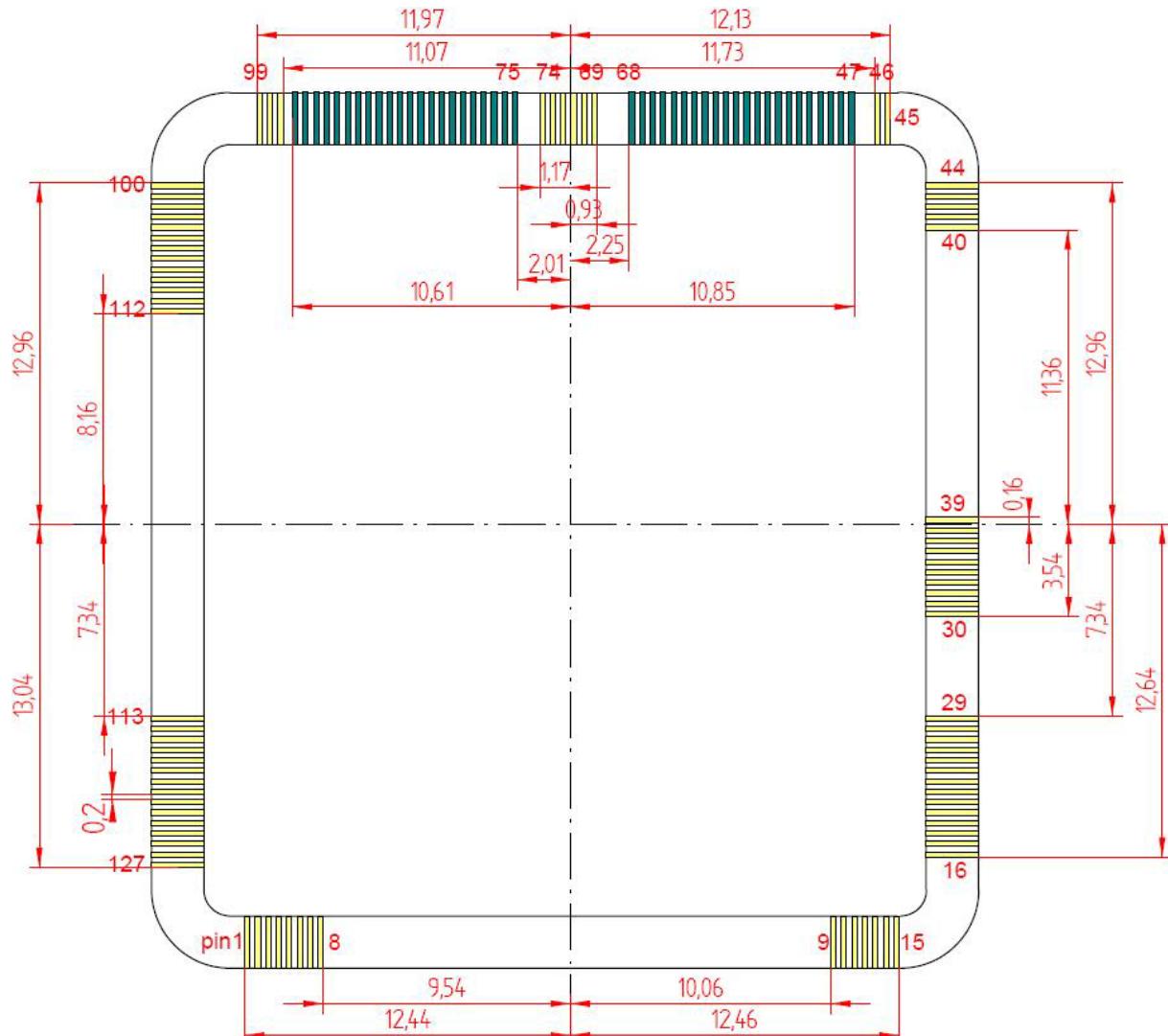

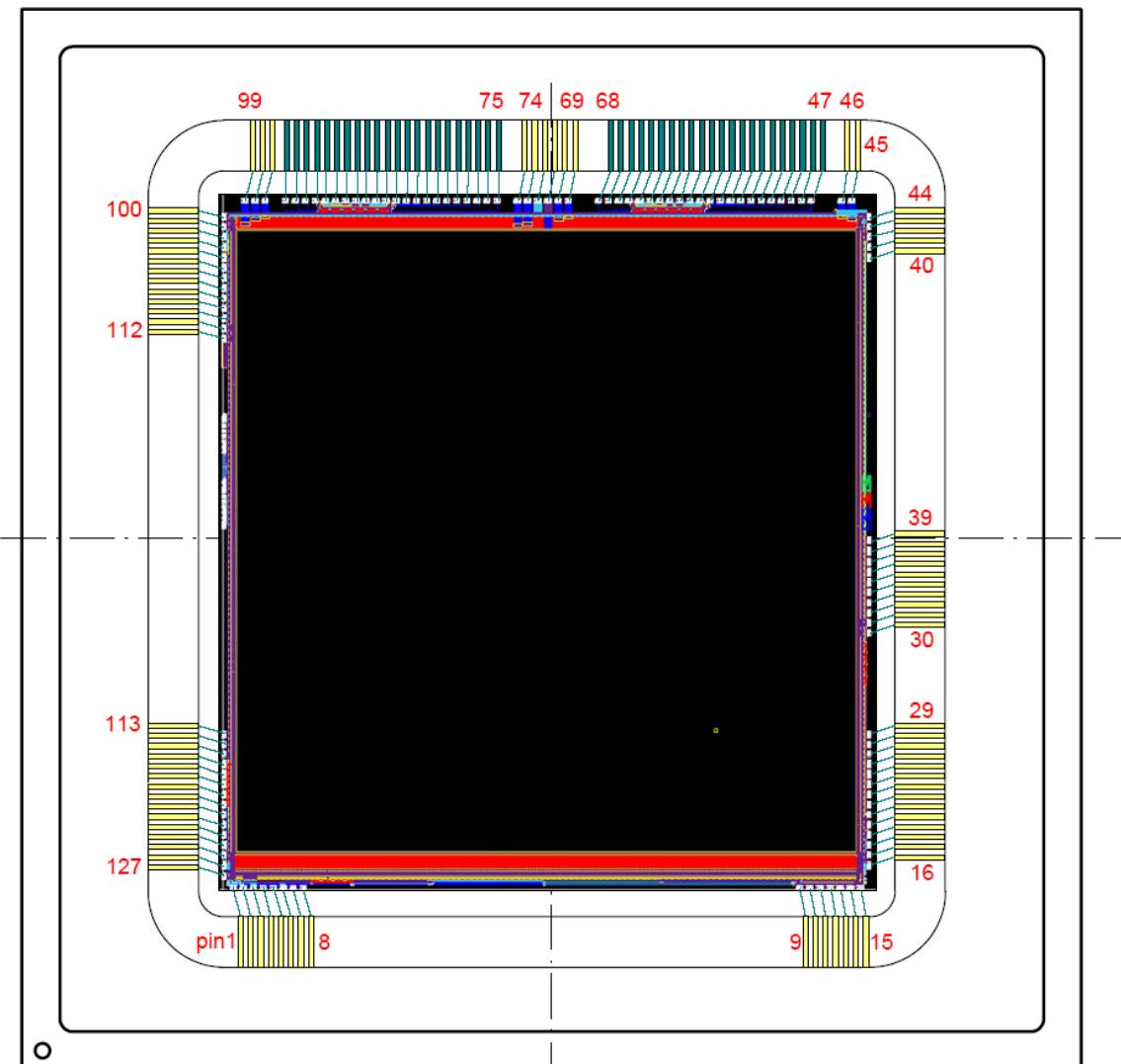

| 6.1 BARE DIE .....                                    | 40        |

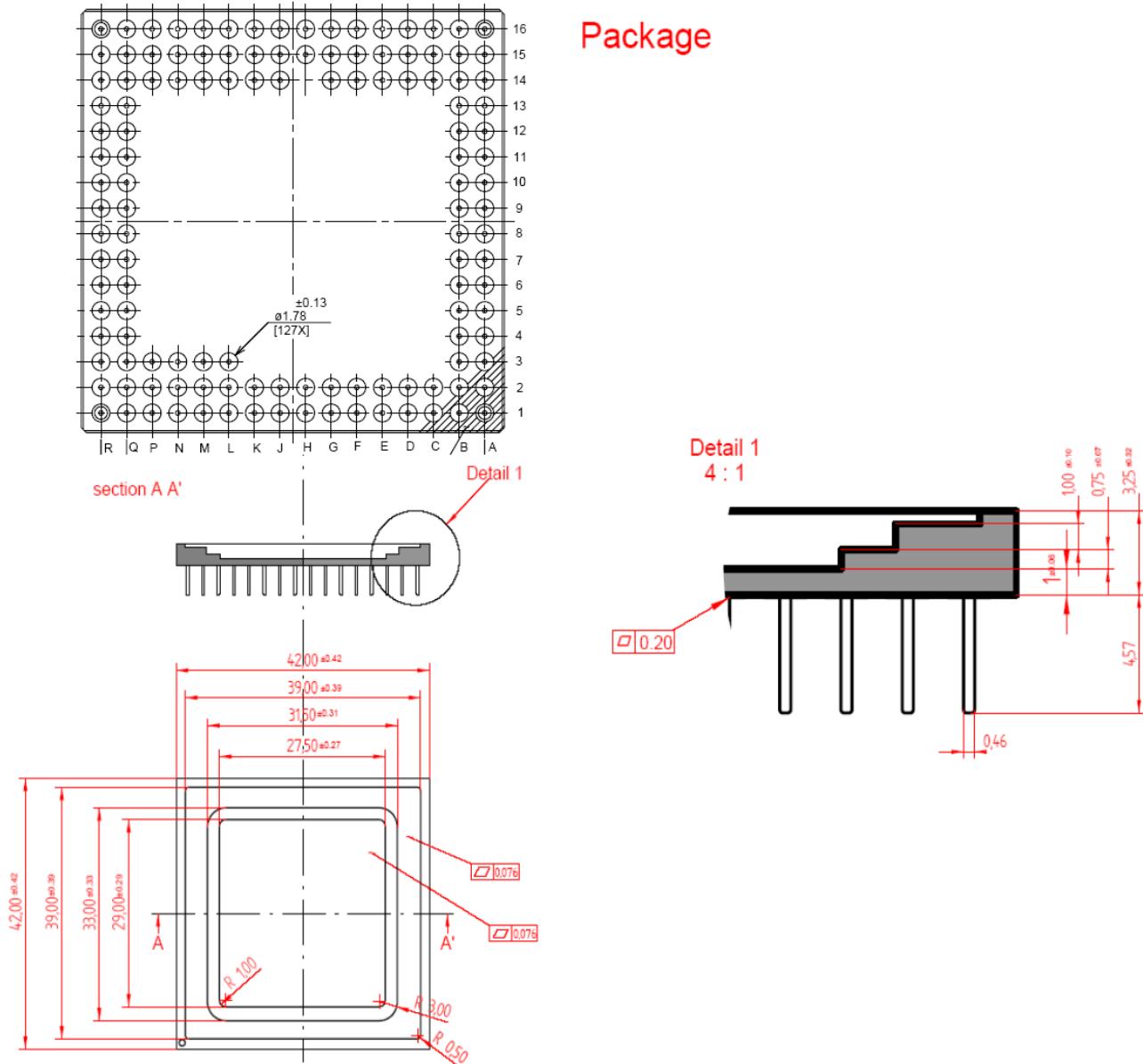

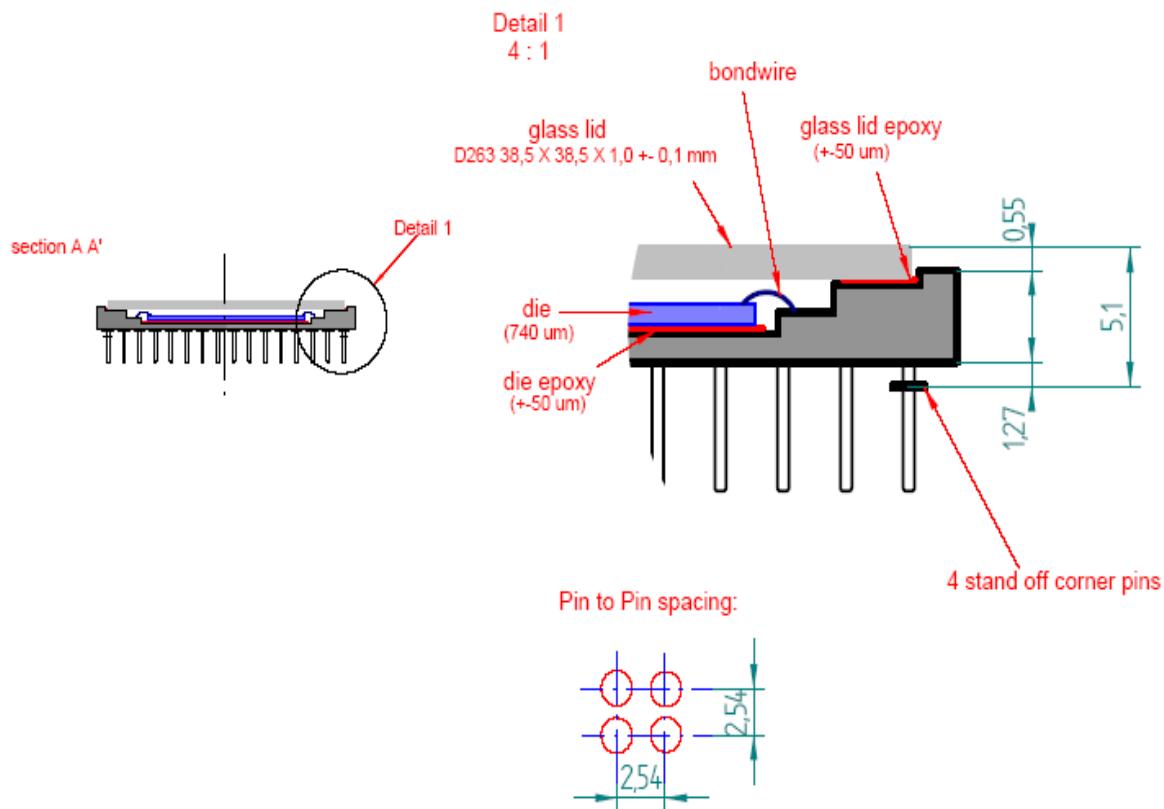

| 6.2 PACKAGE DRAWING.....                              | 41        |

| 6.3 BONDING PADS .....                                | 43        |

| 6.4 BONDING DIAGRAM .....                             | 44        |

| <b>7 HANDLING AND SOLDERING PRECAUTIONS</b> .....     | <b>45</b> |

| <b>8 ORDERING INFORMATION</b> .....                   | <b>46</b> |

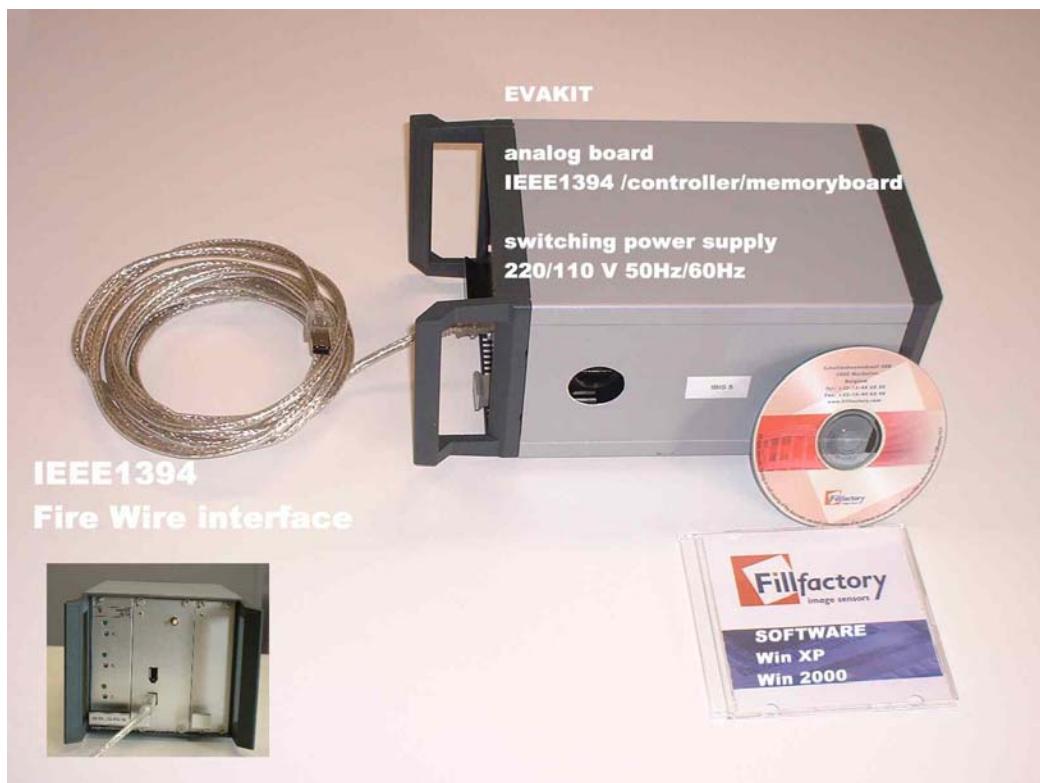

| <b>APPENDIX A: LUPA-4000 EVALUATION SYSTEM</b> .....  | <b>47</b> |

| <b>APPENDIX B: FREQUENTLY ASKED QUESTIONS</b> .....   | <b>48</b> |

## 1 Preamble

### 1.1 Overview

This document describes the interfacing and the driving of the LUPA-4000 image sensor. This 4 mega-pixel CMOS active pixel sensor features synchronous shutter and a maximal frame-rate of 15fps in full resolution. The readout speed can be boosted by means of sub sampling and windowed Region Of Interest (ROI) readout. High dynamic range scenes can be captured using the double and multiple slope functionality.

The sensor can be used with one or two outputs. Two on chip 10-bit ADC's can be used to convert the analog data to a 10-bit digital word stream. The sensor uses a 3-wire Serial-Parallel (SPI) interface. It is housed in a 127-pin ceramic PGA package. This datasheet allows the user to develop a camera-system based on the described timing and interfacing.

### 1.2 Main features

The main features of the image sensor are identified as:

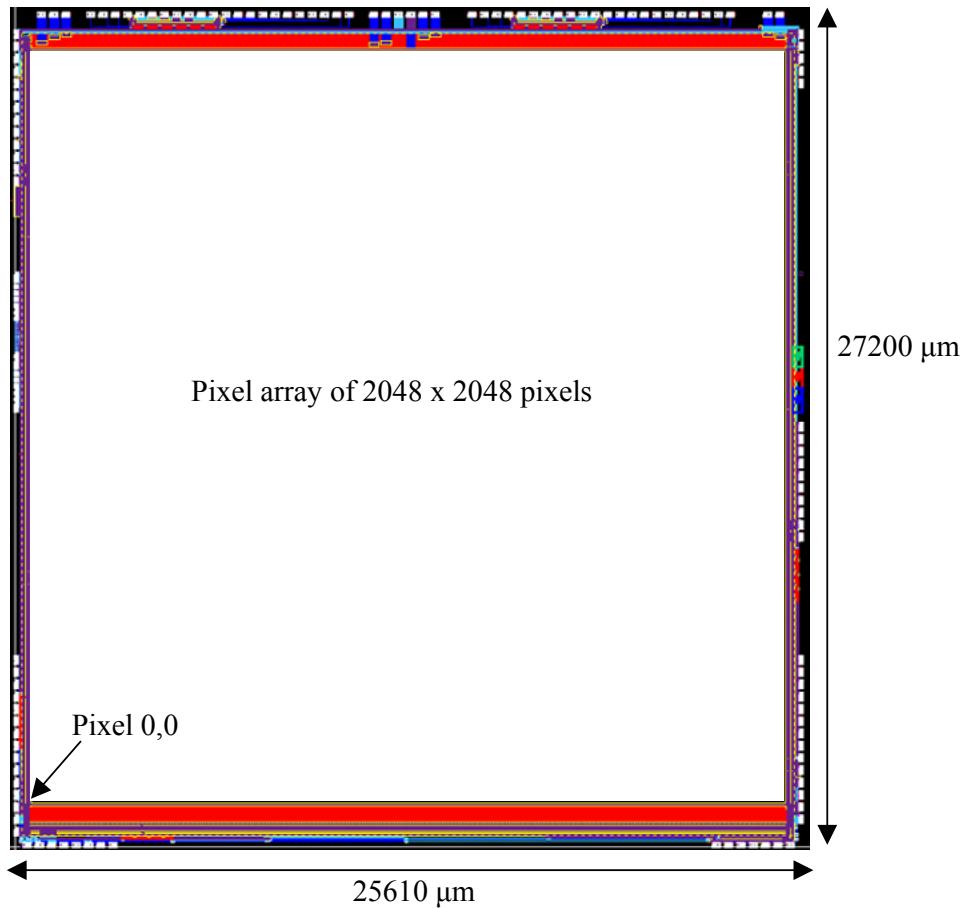

- 2048 x 2048 active pixels (4M pixel resolution).

- 12  $\mu\text{m}^2$  square pixels (based on the high-fill factor active pixel sensor technology of FillFactory (US patent No. 6,225,670 and others)).

- Peak QE x FF of 37.50%.

- Optical format: 24,6 mm x 24,6 mm

- Pixel rate of 66 MHz using a 33 MHz system clock.

- Optical dynamic range: 66 dB (2000:1) in single slope operation and up to 90 dB in multiple slope operation.

- 2 On-chip 10 bit, 33 MSamples/s ADC.

- Full snapshot shutter.

- Random programmable windowing and sub-sampling modes.

- 127-pin PGA package

- Binning (Voltage averaging in X-direction)

- Programmable read out direction (X and Y)

### 1.3 Part Number

| <b>Name</b>                     | <b>Package</b> | <b>Monochrome / color</b> |

|---------------------------------|----------------|---------------------------|

| LUPA-4000-M                     | 127 pin        | Monochrome                |

| CYIL1SM4000AA-GBC (preliminary) | ceramic PGA    |                           |

## 2 Specifications

### 2.1 General specifications

Table 1: General specifications

| Parameter                 | Specification                          | Remarks                                                                                 |

|---------------------------|----------------------------------------|-----------------------------------------------------------------------------------------|

| <b>Pixel architecture</b> | <i>6T-pixel</i>                        | <i>Based on the high fill-factor active pixel sensor technology of FillFactory</i>      |

| <b>Pixel size</b>         | $12 \mu\text{m} \times 12 \mu\text{m}$ | <i>The resolution and pixel size results in a 24,6 mm x 24,6mm optical active area.</i> |

| <b>Resolution</b>         | 2048 x2048                             |                                                                                         |

| <b>Pixel rate</b>         | 66 MHz                                 | <i>Using a 33 MHz system clock and 1 or 2 parallel outputs.</i>                         |

| <b>Shutter type</b>       | <i>Pipelined snapshot shutter</i>      | <i>Full snapshot shutter (integration during read out is possible).</i>                 |

| <b>Full frame rate</b>    | 15 frames/second                       | <i>Frame rate increase possible with ROI read out and/or sub sampling.</i>              |

### 2.2 Electro-optical specifications

#### 2.2.1 Overview

Table 2: Electro-optical specifications

| Parameter                         | Specification                        | Remarks                                                                                                 |

|-----------------------------------|--------------------------------------|---------------------------------------------------------------------------------------------------------|

| <b>FPN</b>                        | $<1.25\% \text{ RMS}$                | of max. output swing                                                                                    |

| <b>PRNU</b>                       | $<2.5\% \text{ RMS}$                 | at 25% and 75% (% of the signal)                                                                        |

| <b>Conversion gain</b>            | 13.5 uV/electron                     | (@ output (measured).                                                                                   |

| <b>Output signal amplitude</b>    | 1V                                   | Converted by 2 on-chip 10-bit ADC's in 2x10 parallel digital outputs. Or to be used with external ADC's |

| <b>Saturation charge</b>          | 80.000 e-                            |                                                                                                         |

| <b>Sensitivity</b>                | 2090 V.m2/W.s                        | <i>Average white light.</i>                                                                             |

|                                   | 11.61 V/lux.s                        | <i>Visible band only (180 lx = 1 W/m2).</i>                                                             |

| <b>Peak QE * FF</b>               | 37.5 %                               | <i>Average QE*FF = 35%.</i>                                                                             |

| <b>Peak SR * FF</b>               | 0.19 A/W                             | <i>Average SR*FF = 0.15 A/W.</i><br><i>See spectral response curve.</i>                                 |

| <b>Dark current (@ 21 °C)</b>     | $<140 \text{ mV/s}$<br>or 10000 e-/s |                                                                                                         |

| <b>Noise electrons</b>            | $< 40 \text{ e-}$                    |                                                                                                         |

| <b>S/N ratio</b>                  | 2000:1                               | 66 dB.                                                                                                  |

| <b>Spectral sensitivity range</b> | 400 – 1000 nm                        |                                                                                                         |

| <b>Parasitic sensitivity</b>      | $< 1/5000$                           | <i>I.e. sensitivity of the storage node during read out (after integration).</i>                        |

| <b>MTF</b>                        | 64%                                  |                                                                                                         |

| <b>Power dissipation</b>          | $<200 \text{ mWatt}$                 | <i>Typical (without ADC's).</i>                                                                         |

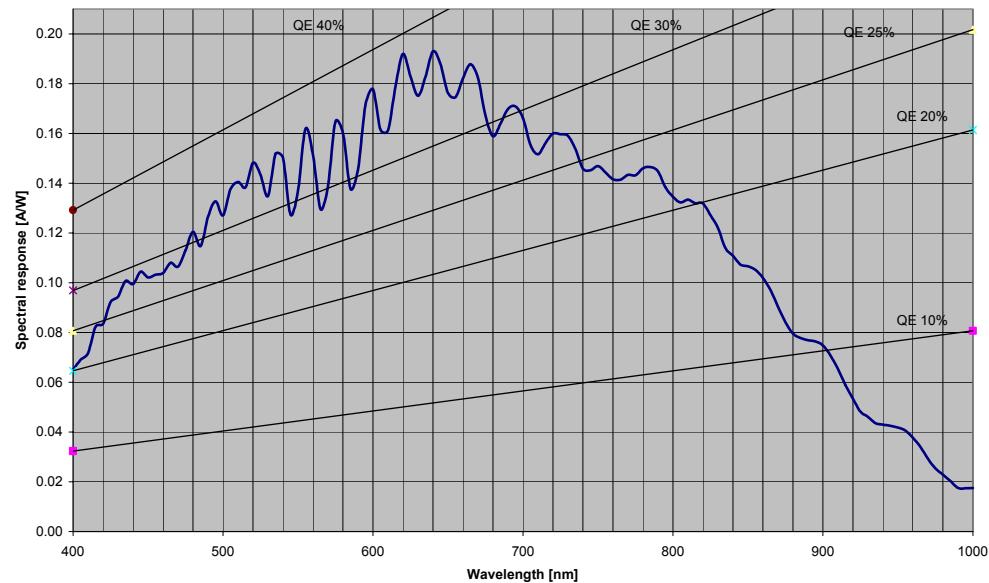

## 2.2.2 Spectral response curve

Figure 1: Spectral response curve

Figure 1 shows the spectral response characteristic. The curve is measured directly on the pixels. It includes effects of non-sensitive areas in the pixel, e.g. interconnection lines. The sensor is light sensitive between 400 and 1000 nm. The peak QE \* FF is 37.5% approximately between 500 and 700 nm. In view of a fill factor of 60%, the QE is thus larger than 60% between 500 and 700 nm.

### 2.2.3 Photo-voltaic response curve

*Figure 2: Photo-voltaic response curve*

Figure 2 shows the pixel response curve in linear response mode. This curve is the relation between the electrons detected in the pixel and the output signal. The resulting voltage-electron curve is independent of any parameters. The voltage to electrons conversion gain is  $13.5 \mu\text{V/electron}$ .

Note that the upper part of the curve (near saturation) is actually a logarithmic response.

## 2.3 Features and general specifications

Table 3: Features and general specifications

| Feature                               | Specification/Description                                                                 |

|---------------------------------------|-------------------------------------------------------------------------------------------|

| <b>Electronic shutter type</b>        | <i>Full snapshot shutter (integration during read out is possible).</i>                   |

| <b>Windowing (ROI)</b>                | <i>Randomly programmable ROI read out.</i>                                                |

| <b>Sub-sampling and binning modes</b> | <i>2:1 subsampling and voltage averaging is possible (only in the X-direction).</i>       |

| <b>Read out direction</b>             | <i>Read out direction can be reversed in X and Y.</i>                                     |

| <b>Extended dynamic range</b>         | <i>Multiple slope (up to 90 dB optical dynamic range).</i>                                |

| <b>Analog output</b>                  | <i>The output rate of 66 Mpixels/s can be achieved with either 1 or 2 analog outputs.</i> |

| <b>Digital output</b>                 | <i>2 on-chip 10-bit ADC's @ 33 Msamples/s.</i>                                            |

| <b>Supply voltage VDD</b>             | <i>Nominal 2.5V (some supplies require 3.3V).</i>                                         |

| <b>Logic levels</b>                   | <i>3.3V.</i>                                                                              |

| <b>Operational temperature range</b>  | <i>0°C to 60°C; with degradation of dark current.</i>                                     |

| <b>Interface</b>                      | <i>Serial-to Parallel Interface (SPI).</i>                                                |

| <b>Package</b>                        | <i>127 pin PGA package</i>                                                                |

| <b>Power dissipation</b>              | <i>&lt;200mW</i>                                                                          |

| <b>Mass</b>                           | <i>&lt;100g</i>                                                                           |

| <b>Output amplifiers</b>              | <i>Differential</i>                                                                       |

| <b>External output load</b>           | <i>R &gt; 10 kΩ<br/>C &lt; 20 pF (&lt;10 pF is advised)</i>                               |

| <b>Number of outputs</b>              | <i>1 at 66 Mpixels/sec<br/>2 at 33Mpixels/sec</i>                                         |

## 2.4 Electrical specifications

### 2.4.1 Recommended operating conditions

*Table 4: Recommended operation conditions*

| Symbol               | Parameter                                       | Min  | Typ | Max | Unit     |

|----------------------|-------------------------------------------------|------|-----|-----|----------|

| <b>Vaa</b>           | <i>Power supply column read out module.</i>     |      | 2.5 |     | <i>V</i> |

| <b>Va3</b>           | <i>Power supply column read out module</i>      |      | 3.3 | 3.3 | <i>V</i> |

| <b>Vdd</b>           | <i>Power supply digital modules</i>             |      | 2.5 |     | <i>V</i> |

| <b>Voo</b>           | <i>Power supply output stages</i>               |      | 2.5 |     | <i>V</i> |

| <b>Vres</b>          | <i>Power supply reset drivers</i>               | 2.5  | 3.3 | 3.5 | <i>V</i> |

| <b>Vres_ds</b>       | <i>Power supply multiple slope reset driver</i> | 2.0  | 2.5 | 3.3 | <i>V</i> |

| <b>Vmem_h</b>        | <i>Power supply memory element (high level)</i> | 2.5  | 3.3 | 3.5 | <i>V</i> |

| <b>Vmem_l</b>        | <i>Power supply memory element (low level)</i>  | 2.0  | 2.6 | 3.0 | <i>V</i> |

| <b>Vpix</b>          | <i>Power supply pixel array</i>                 | 2.0  | 2.6 | 3.3 | <i>V</i> |

| <b>Vpre_l</b>        | <i>Power supply for Precharge off-state</i>     | -0.4 | 0   | 0   | <i>V</i> |

| <b>T<sub>A</sub></b> | <i>Commercial operating temperature.</i>        | 0    | 30  | 60  | °C       |

Note:

1. All parameters are characterized for DC conditions after thermal equilibrium has been established.

2. Unused inputs must always be tied to an appropriate logic level, e.g. either VDD or GND.

3. This device contains circuitry to protect the inputs against damage due to high static voltages or electric fields; however it is recommended that normal precautions be taken to avoid application of any voltages higher than the maximum rated voltages to this high impedance circuit.

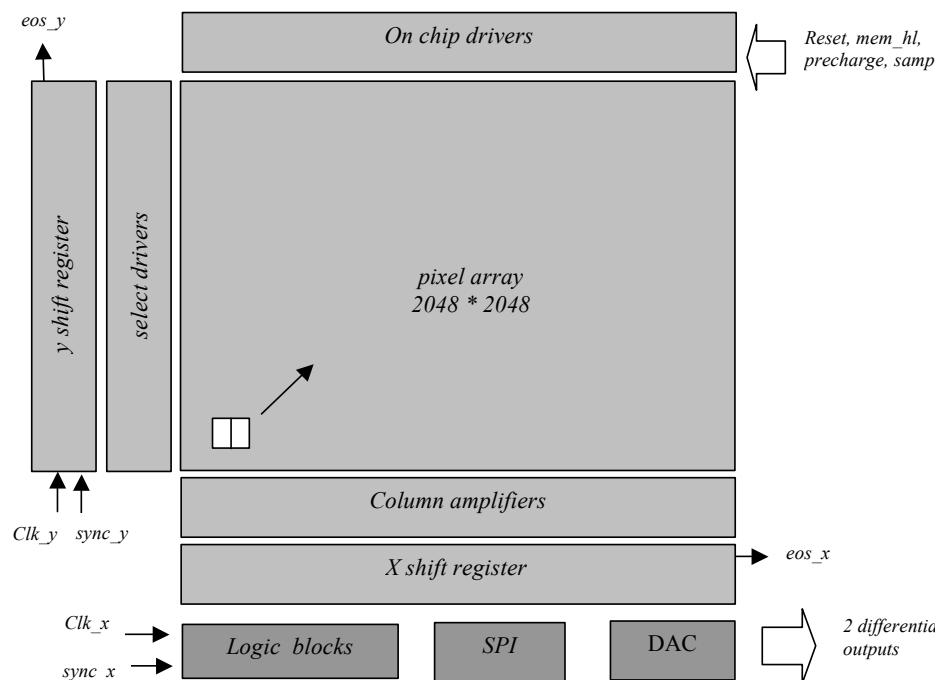

### 3 Sensor architecture

A schematic drawing of the architecture is given in the block diagram below. The image core consists of a pixel array, one X- and two Y-addressing registers (only one drawn), pixel array drivers and column amplifiers. The image sensor of 2048 \* 2048 pixels is read out in progressive scan. One or two output amplifiers read out the image sensor. The output amplifiers are working at 66MHz pixel rate nominal speed or each at 33MHz pixel rate in case the 2 output amplifiers are used to read out the imager. The complete image sensor has been designed for operation up to 66MHz. The structure allows having a programmable addressing in the x-direction in steps of 2 and in the y-direction in steps of 2 (only even start addresses in X- and Y-direction are possible). The starting point of the address is uploadable by means of the Serial-Parallel Interface (SPI).

Figure 3: Block diagram of the image sensor

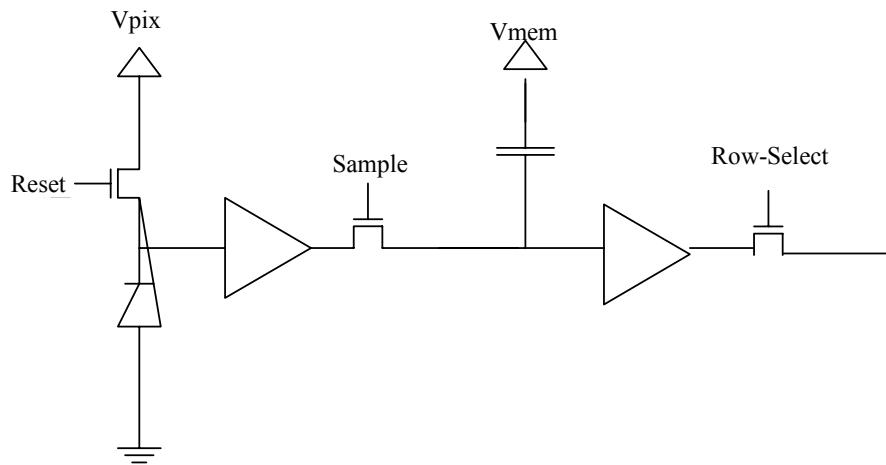

### 3.1 The 6-T pixel

To obtain the global shutter feature combined with a high sensitivity and good Parasitic Light Sensitivity (PLS), the pixel architecture given in the figure below is implemented.

*Figure 4: 6T-pixel architecture*

This pixel architecture is designed in a  $12 * 12 \mu\text{m}^2$  pixel pitch. The pixel is designed to meet the specifications as described in Tables 1, 2 and 3.

## 3.2 Frame rate and windowing

### 3.2.1 Frame rate

To obtain a frame rate a 15 frames /sec, one needs 1 output amplifier, working at 66MHz pixel rate or 2 output amplifiers working at 33MHz each (assuming a Row Overhead Time (ROT) of 200nsec).

The frame period of the LUPA-4000 sensor can be calculated as follows:

$$\text{Frame period} = \text{FOT} + (\text{Nr. Lines} * (\text{ROT} + \text{pixel period} * \text{Nr. Pixels}))$$

with: FOT: Frame Overhead Time = 5 us.

Nr. Lines: Number of Lines read out each frame (Y).

Nr. Pixels: Number of pixels read out each line (X).

ROT: Row Overhead Time = 200 ns (nominal; can be further reduced).

Pixel period: 1/66 MHz = 15.15 ns.

Example read out of the full resolution at nominal speed (66 MHz pixel rate):

$$\text{Frame period} = 5 \text{ us} + (2048 * (200 \text{ ns} + 15.15 \text{ ns} * 2048)) = 64 \text{ ms} \Rightarrow 15 \text{ fps.}$$

### 3.2.2 ROI read out (windowing)

Windowing can easily be achieved by a serial-parallel uploadable interface in which the starting point of the x- and y-address is uploaded. This downloaded starting point initiates the shift register in the x- and y-direction triggered by the Sync\_x and Sync\_y pulse. The minimum step size for the x-address and the y-address is 2 (only even start addresses can be chosen). The size of both address registers is 10 bits. When for instance the addresses 0000000001 and 0000000001 are uploaded, the readout will start at line 2 and column 2.

Table 5: Frame rate as function of ROI read out and/or sub sampling

| Image Resolution (X*Y) | Frame rate [frames/s] | Frame readout time [ms] | Comment                   |

|------------------------|-----------------------|-------------------------|---------------------------|

| 2048 x 2048            | 15                    | 67                      | Full resolution.          |

| 1024 x 2048            | 31                    | 32                      | Subsample in X-direction. |

| 1024 x 1024            | 62                    | 16                      | ROI read out.             |

| 640 x 480              | 210                   | 4.7                     | ROI read out.             |

### 3.3 Output amplifier

1 output amplifier working at 66Mpixels/sec is required to bring the whole pixel array of 2048 by 2048 pixels at the required frame rate to the outside world. A second output stage is also foreseen to convert the analog data on-chip by 2 10-bit ADC's each working at 33 MHz. By having a second output stage working in parallel, the pixel rate can be more relaxed to 33MHz for both output amplifiers. Using only one output-stage, the output signal will be the result of multiplexing between the 2 internal buses. When using 2 output-stages, both outputs will be in phase.

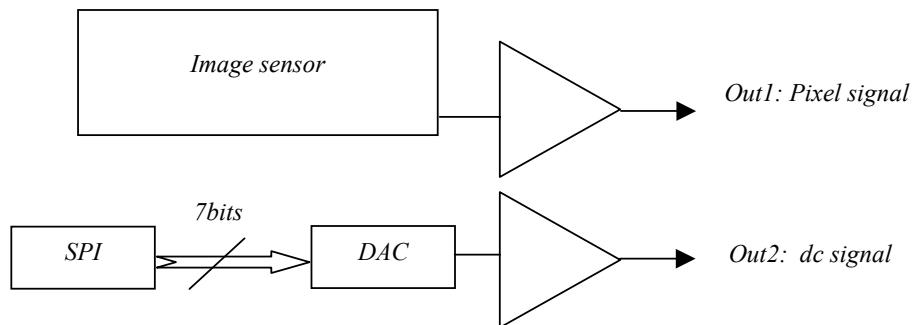

Each output-stage has 2 outputs. One output is the pixel signal; the second output is a DC signal which offset can be programmed using a 7-bit word. The DC signal can be used for common mode rejection between the 2 signals. The disadvantage is an increase in power dissipation however this can be reduced by setting the highest DAC voltage by means of the SPI.

Figure 5: Output stage architecture

The output voltage of Out1 will be between 1.3V (dark level) and 0.3V (white level) and depends on process variations and voltage supply settings. The output voltage of Out2 is determined by the DAC.

### 3.4 Pixel array drivers

We have foreseen on this image sensor on chip drivers for the pixel array signals. Not only the driving on system level is easy and flexible, also the maximum currents applied to the sensor are controlled on chip. This means that the charging on sensor level is fixed and that the sensor cannot be overdriven from externally. In the paragraph on the timing, the operation of the on-chip drivers is explained more in detail.

### 3.5 Column amplifiers

The column amplifiers are designed for minimum power dissipation and minimum loss of signal for this reason multiple biasing signals are needed.

The column amplifiers also have the “voltage-averaging” feature integrated. In case of voltage averaging mode, the voltage average between 2 columns is taken and read out. In this mode only 2:1 pixels have to be read out.

To achieve the voltage-averaging mode, an additional external digital signal called “voltage-averaging” is required in combination with a bit from the SPI.

### 3.6 Analog to Digital Converter

The LUPA4000 has a two 10 bit flash analog digital converters running nominally at 33 Msamples/s. The ADC's are electrically separated from the image sensor. The inputs of the ADC should be tied externally to the outputs of the output amplifiers.

One ADC will sample the even columns and the other one will sample the odd columns. Although the input range of the ADC is between 1V and 2V and the output range of the analog signal is only between 0.3V and 1.3V, the analog output and digital input may be tied to each other directly. This is possible because there is an on chip level-shifter located in front of the ADC to lift up the analog signal to the ADC range.

*Table 6: ADC specifications*

| Parameter                           | Specification                   |

|-------------------------------------|---------------------------------|

| <b>Input range</b>                  | <i>1 – 2V (*)</i>               |

| <b>Quantization</b>                 | <i>10 Bits</i>                  |

| <b>Nominal data rate</b>            | <i>33 Msamples/s</i>            |

| <b>DNL (linear conversion mode)</b> | <i>Typ. &lt; 0.4LSB RMS</i>     |

| <b>INL (linear conversion mode)</b> | <i>Typ. &lt; 3.5 LSB</i>        |

| <b>Input capacitance</b>            | <i>&lt; 2 pF</i>                |

| <b>Power dissipation @ 33 MHz</b>   | <i>50 mW</i>                    |

| <b>Conversion law</b>               | <i>Linear / Gamma-corrected</i> |

(\*): The internal ADC range will be typ. 50mV lower then the external applied ADC\_VHIGH and ADC\_VLOW voltages due to voltage drops over parasitic internal resistors in the ADC.

### 3.6.1 ADC timing

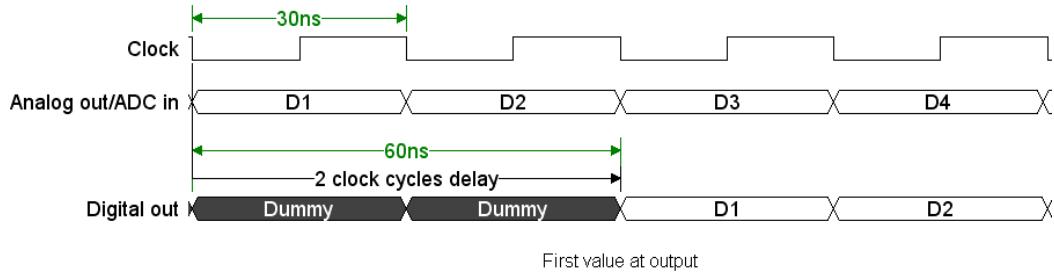

The ADC converts the pixel data on the falling edge of the ADC\_CLOCK but it takes 2 clock cycles before this pixel data is at the output of the ADC. This pipeline delay is shown in Figure 6.

Figure 6: ADC timing

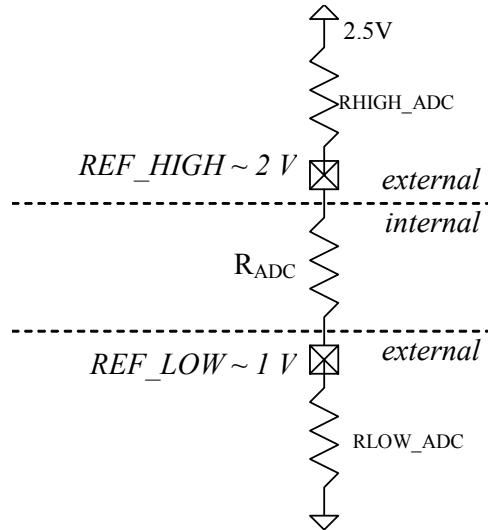

### 3.6.2 Setting of the ADC reference voltages

Figure 7: In- and external ADC connections

The internal resistor  $R_{ADC}$  has a value of approximately  $300 \Omega$ . This results in the values for the external resistors:

| Resistor         | Value ( $\Omega$ ) |

|------------------|--------------------|

| $R_{ADC\_VHIGH}$ | 75                 |

| $R_{ADC}$        | 300                |

| $R_{ADC\_VLOW}$  | 220                |

The values of the resistors depend on the value of  $R_{ADC}$ . The voltage difference between  $ADC\_VLOW$  and  $ADC\_VHIGH$  should be at least 1.0V to assure proper working of the ADC.

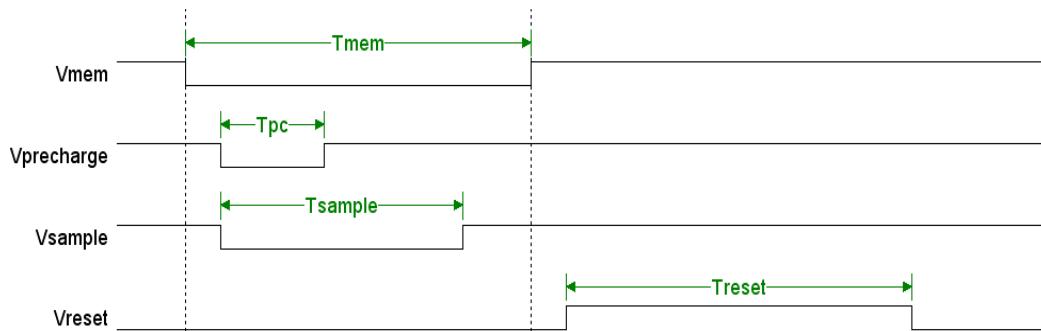

### 3.7 Synchronous shutter

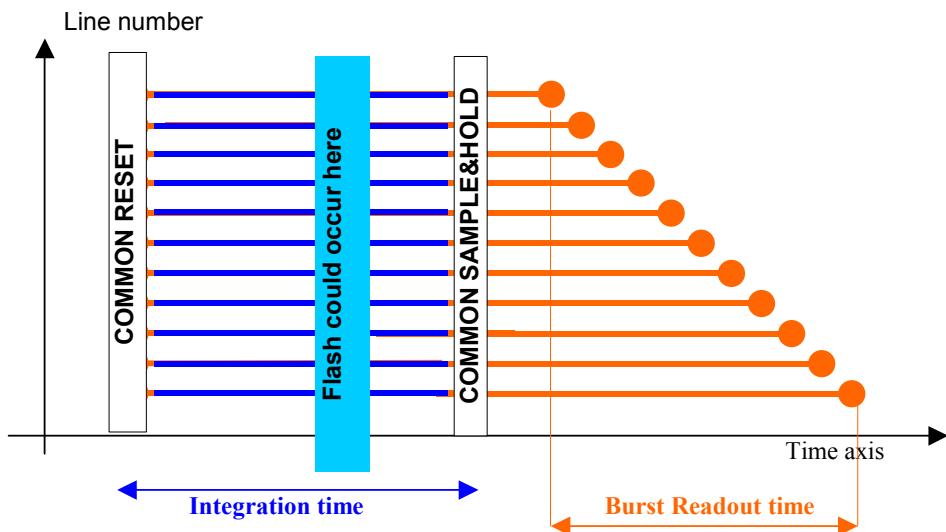

In a synchronous (snapshot) shutter light integration takes place on all pixels in parallel, although subsequent readout is sequential.

Figure 8: Synchronous shutter operation

Figure 8 shows the integration and read out sequence for the synchronous shutter. All pixels are light sensitive at the same period of time. The whole pixel core is reset simultaneously and after the integration time all pixel values are sampled together on the storage node inside each pixel. The pixel core is read out line by line after integration. Note that the integration and read out cycle can occur in parallel or in sequential mode. (ref. 4. Timing and read out of the image sensor)

### 3.8 Non-destructive readout (NDR)

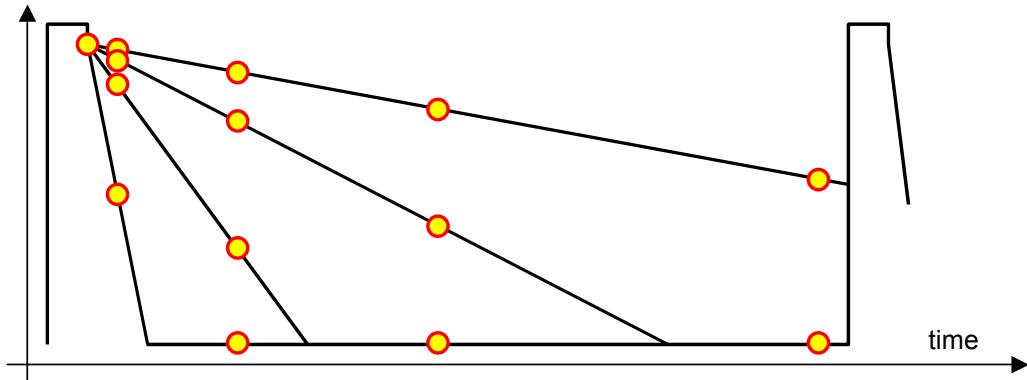

The sensor can also be read out in a non-destructive way. After a pixel is initially reset, it can be read multiple times, without resetting. The initial reset level and all intermediate signals can be recorded. High light levels will saturate the pixels quickly, but a useful signal is obtained from the early samples. For low light levels, one has to use the later or latest samples.

Figure 9. Principle of non-destructive readout.

Essentially an active pixel array is read multiple times, and reset only once. The external system intelligence takes care of the interpretation of the data. Table 7 summarizes the advantages and disadvantages of non-destructive readout.

Table 7: Advantages and disadvantages of non-destructive readout.

| Advantages                                                                                | Disadvantages                                                                  |

|-------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------|

| Low noise – as it is true CDS.                                                            | System memory required to record the reset level and the intermediate samples. |

| High sensitivity – as the conversion capacitance is kept rather low.                      | Requires multiple readings of each pixel, thus higher data throughput.         |

| High dynamic range – as the results includes signal for short and long integration times. | Requires system level digital calculations.                                    |

### 3.9 Operation and signalling

One can distinguish the different signals into different groups:

- Power supplies and grounds

- Biasing and Analog signals

- Pixel array signals

- Digital signals

- Test signals

#### 3.9.1 Power supplies and ground

Every module on chip, as there are: column amplifiers, output stages, digital modules, drivers... has its own power supply and ground. Off chip the grounds can be combined, but not all power supplies may be combined. This results in several different power supplies, but this is required to reduce electrical cross-talk and to improve shielding, dynamic range and output swing.

On chip we have the ground lines of every module which are kept separately to improve shielding and electrical cross talk between them.

An overview of the supplies is given in table 8 and 9. Table 9 summarizes the supplies related to the pixel array signals, where table 8 summarizes the supplies related with all other modules.

*Table 8: Power supplies*

| Name        | DC Current  | Max.current  | Typ.        | Max.        | Description                                                                |

|-------------|-------------|--------------|-------------|-------------|----------------------------------------------------------------------------|

| <b>Vaa</b>  | <i>7mA</i>  | <i>50mA</i>  | <i>2.5V</i> |             | <i>Power supply column readout module.</i>                                 |

| <b>Va3</b>  | <i>10mA</i> | <i>50mA</i>  | <i>3.3V</i> | <i>3.3V</i> | <i>Power supply column readout module. Should be tuneable to 3.3V max.</i> |

| <b>Vdd</b>  | <i>1mA</i>  | <i>200mA</i> | <i>2.5V</i> |             | <i>Power supply digital modules</i>                                        |

| <b>Voo</b>  | <i>20mA</i> | <i>20mA</i>  | <i>2.5V</i> |             | <i>Power supply output stages</i>                                          |

| <b>Vdda</b> | <i>1mA</i>  | <i>200mA</i> | <i>2.5V</i> |             | <i>Analog supply of ADC circuitry</i>                                      |

| <b>Vddd</b> | <i>1mA</i>  | <i>200mA</i> | <i>2.5V</i> |             | <i>Digital supply of ADC circuitry</i>                                     |

*Table 9: Overview of the power supplies related to the pixel signals*

| Name           | DC current  | Max. current | Min.          | Typ.         | Max.        | Description                                                                            |

|----------------|-------------|--------------|---------------|--------------|-------------|----------------------------------------------------------------------------------------|

| <b>Vres</b>    | <i>1mA</i>  | <i>200mA</i> | <i>2.5V</i>   | <i>3.3V</i>  | <i>3.5V</i> | <i>Power supply reset drivers.</i>                                                     |

| <b>Vres_ds</b> | <i>1mA</i>  | <i>200mA</i> | <i>2.0V</i>   | <i>2.5V</i>  | <i>3.3V</i> | <i>Power supply dual slope reset drivers.</i>                                          |

| <b>Vmem_h</b>  | <i>1mA</i>  | <i>200mA</i> | <i>2.5V</i>   | <i>3.3V</i>  | <i>3.5V</i> | <i>Power supply memory elements in pixel for high voltage level</i>                    |

| <b>Vmem_l</b>  | <i>1mA</i>  | <i>200mA</i> | <i>2.0V</i>   | <i>2.5 V</i> | <i>3.0V</i> | <i>Power supply memory elements in pixel for low voltage level. Should be tuneable</i> |

| <b>Vdd</b>     | <i>1mA</i>  | <i>200mA</i> | <i>2.0V</i>   | <i>2.5V</i>  | <i>3.0V</i> | <i>Power supply for Sample</i>                                                         |

| <b>Vpix</b>    | <i>12mA</i> | <i>500mA</i> | <i>2.0V</i>   | <i>2.5V</i>  | <i>3.3V</i> | <i>Power supply pixel array. Should be tuneable to 3.3V</i>                            |

| <b>Vpre_l</b>  | <i>1mA</i>  | <i>200mA</i> | <i>-400mV</i> | <i>0V</i>    | <i>0V</i>   | <i>Power supply for Precharge in off-stat. May be connected to ground.</i>             |

The maximum currents mentioned in table 8 and 9 are peak currents which occur once per frame (except for Vres\_ds in multiple slope mode). All power supplies should be able to deliver these currents except for Vmem\_l and Vpre\_l, which must be able to sink this current.

The maximum peak current for Vpix should not be higher than 500mA. It is important to notice that no power supply filtering on chip is implemented and that noise on these power supplies can contribute immediately to the noise on the signal. Especially the voltage supplies Vpix and Vaa are important to be well noise free.

### 3.9.2 Start-up sequence

The LUPA-4000 will go in latch up (draw high current) as soon as all power supplies are turned on at the same time. The sensor will come out of latch-up and start working normally as soon as it is being clocked. A power supply with a 400 mA limit is recommended to avoid damage to the sensor. It is recommended to avoid the time that the device is in the latch-up state, so clocking of the sensor should start as soon as possible (i.e. as soon as the system is turned on).

In order to completely avoid latch-up of the image sensor, the next sequence should be taken into account:

- Apply Vdd

- Apply clocks and digital pulses to the sensor

- Count 2048 clock\_x and 2048 clock\_y pulses to empty the shift registers

- Apply other supplies

### 3.9.3 Biasing and analog signals

The analog output levels that may be expected are between 0.3V for a white, saturated, pixel and 1.3V for a black pixel.

2 Output stages are foreseen, each consisting of 2 output amplifiers, resulting in 4 outputs. 1 Output amplifier is used for the analog signal resulting from the pixels. The second amplifier is used for a dc reference signal. The dc-level from the buffer is defined by a DAC, which is controlled by a 7-bit word downloaded in the SPI. Additionally, an extra bit in the SPI defines if 1 output or the 2 output stages are used.

Table 10 summarizes the biasing signals required to drive this image sensor. For optimisation reasons of the biasing of the column amplifiers with respect to power dissipation, we need several biasing resistors. This optimisation results in an increase of signal swing and dynamic range.

*Table 10: Overview of bias signals*

| Signal             | Comment                                                         | Related module           | DC-level     |

|--------------------|-----------------------------------------------------------------|--------------------------|--------------|

| <b>Out_load</b>    | <i>Connect with 60 KΩ to Voo and capacitor of 100 nF to Gnd</i> | <i>Output stage</i>      | <i>0.7 V</i> |

| <b>dec_x_load</b>  | <i>Connect with 2 MΩ to Vdd and capacitor of 100 nF to Gnd</i>  | <i>X-addressing</i>      | <i>0.4 V</i> |

| <b>muxbus_load</b> | <i>Connect with 25 KΩ to Vaa and capacitor of 100 nF to Gnd</i> | <i>Multiplex bus</i>     | <i>0.8 V</i> |

| <b>nsf_load</b>    | <i>Connect with 5 KΩ to Vaa and capacitor of 100 nF to Gnd</i>  | <i>Column amplifiers</i> | <i>1.2 V</i> |

| Signal                | Comment                                                                | Related module           | DC-level     |

|-----------------------|------------------------------------------------------------------------|--------------------------|--------------|

| <b>uni_load_fast</b>  | <i>Connect with 10KΩ to Vaa and capacitor of 100 nF to Gnd</i>         | <i>Column amplifiers</i> | <i>1.2 V</i> |

| <b>uni_load</b>       | <i>Connect with 1MΩ to Vaa and capacitor of 100 nF to Gnd</i>          | <i>Column amplifiers</i> | <i>0.5 V</i> |

| <b>pre_load</b>       | <i>Connect with 3 KΩ to Vaa and capacitor of 100 nF to Gnd</i>         | <i>Column amplifiers</i> | <i>0.6 V</i> |

| <b>col_load</b>       | <i>Connect with 1 MΩ to Vaa and capacitor of 100 nF to Gnd</i>         | <i>Column amplifiers</i> | <i>0.5 V</i> |

| <b>dec_y_load</b>     | <i>Connect with 2 MΩ to Vdd and capacitor of 100 nF to Gnd</i>         | <i>Y-addressing</i>      | <i>0.4 V</i> |

| <b>psf_load</b>       | <i>Connect with 1 MΩ to Vaa and capacitor of 100 nF to Gnd</i>         | <i>Column amplifiers</i> | <i>0.5 V</i> |

| <b>precharge_bias</b> | <i>Connect with 1kΩ to Vdd and capacitor of at least 200nF to Gnd.</i> | <i>Pixel drivers</i>     | <i>1.4V</i>  |

Each biasing signal determines the operation of a corresponding module in the sense that it controls speed and dissipation. Some modules have 2 biasing resistors: one to achieve the high speed and another to minimize power dissipation.

### 3.10 Pixel array signals

The Pixel array of the image sensor requires digital control signals and several different power supplies. This paragraph explains the relation between the control signals and the applied supplies and the internal generated pixel array signals.

From figure 9 one can see that the internal generated pixel array signals are Reset, Sample, Precharge, Vmem and Row\_select. These are internal generated signals derived by on chip drivers from external applied signals. Row\_select is generated by the y addressing and will not be discussed in this paragraph.

The function of each of the signals is:

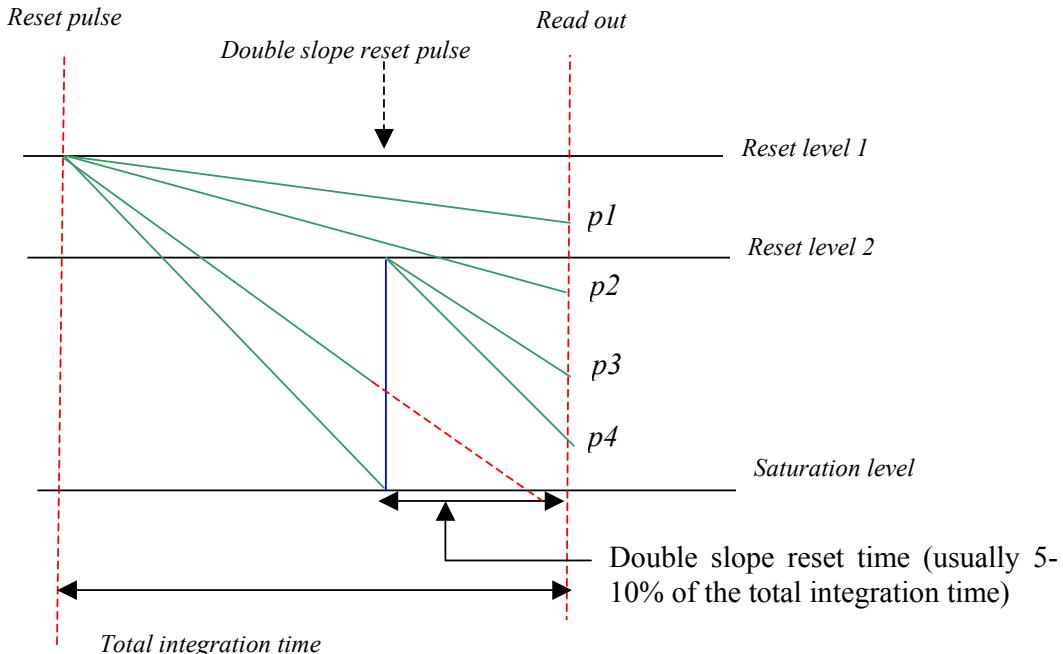

**Reset:** Resets the pixel and initiates the integration time. If reset is high than the photodiode is forced to a certain voltage, depending on Vpix, which is the pixel supply; and depending on the high level of reset signal. The higher these signals or supplies are, the higher the voltage-swing. The limitation on the high level of Reset and Vpix is 3.3V. Nevertheless, it has no sense increasing Vpix without increasing the reset level. The opposite does make sense. Additionally, it is this reset pulse that also controls the dual or multiple slope feature inside the pixel. By giving a reset pulse during integration, but not at full reset level, the photodiode is reset to a new value, only if his value is sufficient decreased due to light illumination.

The low level of reset is 0V, but the high level is 2.5V or higher (3.3V) for the normal reset and a lower (<2.5V) level for the multiple slope reset.

**Precharge:** Precharge serves as a load for the first source follower in the pixel and is activated to overwrite the current information on the storage node by the new information on the photodiode. Precharge is controlled by an external digital signal between 0 and 2.5V.

**Sample:** Samples the photodiode information onto the memory element. This signal is also a standard digital level between 0 and 2.5V

**Vmem:** this signal increases the information on the memory element with a certain offset. This way one can increase the output voltage variation. Vmem changes between Vmem\_l (2.5V) and Vmem\_h (3.3V).

*Figure 10: Internal timing of the pixel. Levels are defined by the pixel array voltage supplies (For the correct polarities of the signals refer to table 11).*

The signals in figure 10 are generated from the on chip drivers. These on chip drivers need 2 types of signals to generate the exact type of signal. It needs digital control signals between 0 and 3.3V (internally converted to 2.5V) with normal driving capability and power supplies. The control signals are required to indicate the moment they need to occur and the power supplies indicate the level.

$V_{mem}$  is made of a control signal  $Mem\_hl$  and 2 supplies  $V_{mem\_h}$  and  $V_{mem\_l}$ . If the signal  $Mem\_hl$  is the logic “0” than the internal signal  $V_{mem}$  is low, if  $Mem\_hl$  is logic “1” the internal signal  $V_{mem}$  is high.

Reset is made by means of 2 control signals: Reset and  $Reset\_ds$  and 2 supplies:  $V_{res}$  and  $V_{res\_ds}$ . Depending on the signal that becomes active, the corresponding supply level is applied to the pixel.

Table 11 summarizes the relation between the internal and external pixel array signals.

*Table 11: Overview of the in- and external pixel array signals*

| Internal Signal | Vlow         | Vhigh        | External control signal       | Low DC-level | High DC-level               |

|-----------------|--------------|--------------|-------------------------------|--------------|-----------------------------|

| Precharge       | 0            | $0.45V$      | Precharge (AL)                | $V_{pre\_l}$ | Controlled by bias-resistor |

| Sample          | 0            | $2.5V$       | Sample (AL)                   | Gnd          | $V_{dd}$                    |

| Reset           | 0            | $2.5 - 3.3V$ | Reset (AH) & $Reset\_ds$ (AH) | Gnd          | $V_{res}$ & $V_{res\_ds}$   |

| $V_{mem}$       | $2.0 - 2.5V$ | $2.5 - 3.3V$ | $Mem\_hl$ (AL)                | $V_{mem\_l}$ | $V_{mem\_h}$                |

AH: Active High

AL: Active Low

In case the dual slope operation is desired, one needs to give a second reset pulse to a lower reset level during integration. This can be done by the control signal  $Reset\_ds$  and by the power supply  $V_{res\_ds}$  that defines the level to which the pixel has to be reset.

Note that Reset is dominant over  $Reset\_ds$ , which means that the high voltage level will be applied for reset, if both pulses occur at the same time.

Note that multiple slopes are possible having multiple  $Reset\_ds$  pulses with a lower  $V_{res\_ds}$  level for each pulse given within the same integration time.

The rise and fall times of the internal generated signals are not very fast (200nsec). In fact they are made rather slow to limit the maximum current through the power supply lines (Vm<sub>mem\_h</sub>, Vm<sub>mem\_l</sub>, V<sub>res</sub>, V<sub>res\_ds</sub>, V<sub>dd</sub>). Current limitation of those power supplies is not required. Nevertheless, it is advisable to limit the currents not higher than 400mA.

The power supply Vm<sub>mem\_l</sub> must be able to sink this current because it must be able to discharge the internal capacitance from the level Vm<sub>mem\_h</sub> to the level Vm<sub>mem\_l</sub>. The external control signals should be capable of driving input capacitance of about 10pF.

### 3.10.1 Digital signals

The digital signals control the readout of the image sensor. These signals are:

- Sync\_y (AH): Starts the readout of the frame. This pulse synchronises the y-address register: active high. This signal is at the same time the end of the frame or window and determines the window width.

- Clock\_y (AH): Clock of the y-register. On the rising edge of this clock, the next line is selected.

- Sync\_x (AH): Starts the readout of the selected line at the address defined by the x-address register. This pulse synchronises the x-address register: active high. This signal is at the same time the end of the line and determines the window length.

- Clock\_x (AH): Determines the pixel rate. A clock of 33MHz is required to achieve a pixel rate of 66MHz.

- Spi\_data (AH): the data for the SPI

- Spi\_clock (AH): clock of the serial parallel interface. This clock downloads the data into the SPI register.

- Spi\_load (AH): when the SPI register is uploaded, then the data will be internally available on the rising edge of SPI\_load

- Sh\_kol (AL): control signal of the column readout. Is used in sample & hold mode and in binning mode

- Norowsel (AH): Control signal of the column readout. (See timing)

- Pre\_col (AL): Control signal of the column readout to reduce row blanking time

- Voltage averaging (AH): Signal required obtaining voltage averaging of 2 pixels.

### 3.10.2 Test signals

The test structures implemented in this image sensor are:

- Array of pixels (6\*12) which outputs are tied together: used for spectral response measurement.

- Temperature diode (2): Apply a forward current of 10-100 $\mu$ A and measure the voltage V<sub>T</sub> of the diode. V<sub>T</sub> varies linear with the temperature (V<sub>T</sub> decreases with approximately 1,6 mV/ $^{\circ}$ C).

- End of scan pulses (do not use to trigger other signals):

---

- Eos\_x: end of scan signal: is an output signal, indicating when the end of the line is reached. Is not generated when doing windowing

- Eos\_y: end of scan signal: is an output signal, indicating when the end of the frame is reached. Is not generated when doing windowing.

- Eos\_spi: output signal of the SPI to check if the data is transferred correctly through the SPI.

## 4 Timing and read out of the image sensor

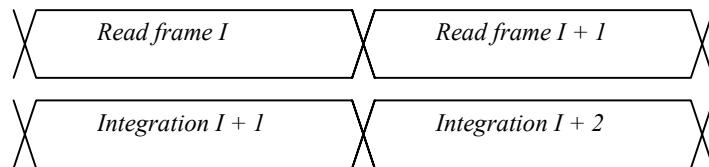

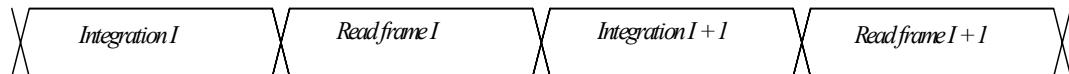

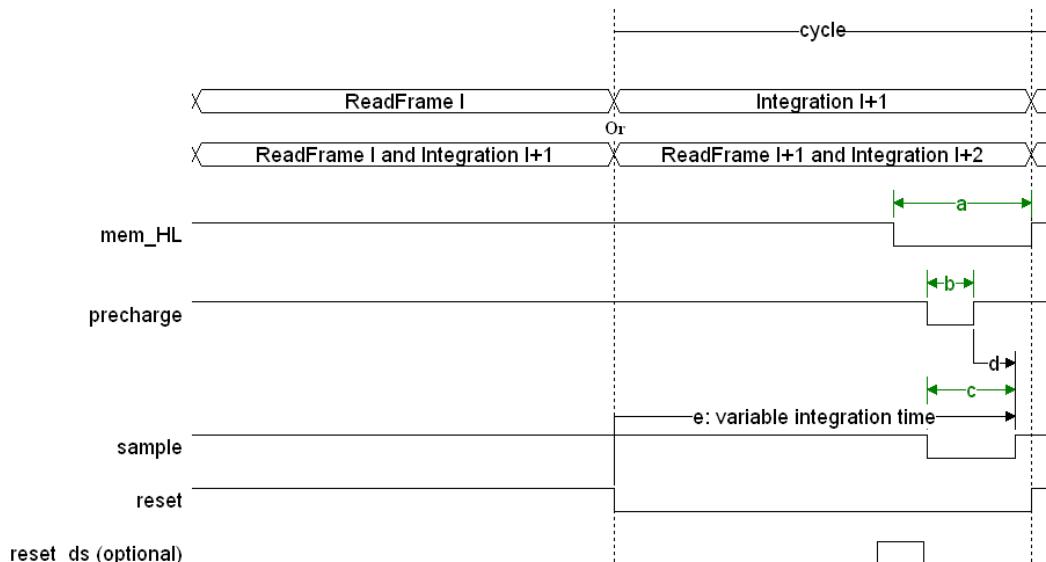

The timing of the LUPA-4000 sensor consists of 2 parts. The first part is related with the control of the pixels, the integration time and the signal level. The second part is related with the readout of the image sensor. As this image sensor is able for full synchronous shutter, integration time and readout can be in parallel or sequential.

In the parallel mode the integration time of the frame I is ongoing during readout of frame I-1. Figure 11 shows this parallel timing structure.

Figure 11: Integration and read out in parallel

The control of the readout of the frame and of the integration time are independent of each other with the only exception that the end of the integration time from frame I+1 is the beginning of the readout of frame I+1.

The LUPA-4000 sensor also can be used in sequential mode (triggered snapshot mode) where readout and integration will be sequentially. Figure 12 shows this sequential timing sequence.

Figure 12: Integration and readout sequentially

## 4.1 Timing of the pixel array

The first part of the timing is related with the timing of the pixel array. This implies the control of the integration time, the synchronous shutter operation and the sampling of the pixel information onto the memory element inside each pixel. The signals needed for this control are described in the previous paragraph 3.9 and in figure 10.

Figure 13 shows the external applied signals required to control the pixel array. At the end of the integration time from frame I+1, the signals Mem\_HL, Precharge and Sample have to be given. The reset signal controls the integration time, which is defined as the time between the falling edge of reset and the rising edge of sample.

Figure 13: Timing of the pixel array: The integration time is determined by the falling edge of the reset pulse. The longer the pulse is high, the shorter the integration time. At the end of the integration time, the information has to be stored onto the memory element for readout.

Timing specifications for each signal are:

Table 12: Timing specifications

| Symbol | Name             | Value             |

|--------|------------------|-------------------|

| a      | Mem_HL           | 5 – 8,2 $\mu$ sec |

| b      | Precharge        | 3 – 6 $\mu$ sec   |

| c      | Sample           | 5 – 8 $\mu$ sec   |

| d      | Precharge-Sample | > 2 $\mu$ sec     |

| e      | Integration time | > 1 $\mu$ sec     |

- Falling edge of Precharge is equal or later than falling edge of Vmem.

- Sample is overlapping with precharge.

- Rising edge of Vmem is more than 200nsec after rising edge of Sample.

- Rising edge of reset is equal or later than rising edge of Vmem.

---

The timing of the pixel array is straightforward. Before the frame is read, the information on the photodiode needs to be stored onto the memory element inside the pixels. This is done by means of the signals Mem\_hl, Precharge and Sample. When precharge is activated it serves as a load for the first source follower in the pixel. Sample stores the photodiode information onto the memory element. Mem\_hl pumps up this value to reduce the loss of signal in the pixel and this signal must be the envelop of Precharge and Sample. After Mem\_hl is high again, the readout of the pixel array can start. The frame blanking time or frame overhead time is thus the time that Mem\_hl is low, which is about 5 $\mu$ sec. Once the readout starts, the photodiodes can all be initialised by reset for the next integration time. The minimal integration time is the minimal time between the falling edge of reset and the rising edge of sample. Keeping the slow fall times of the corresponding internal generated signals in mind, the minimal integration time is about 2  $\mu$ sec.

An additional reset pulse of minimum 2  $\mu$ sec can be given during integration by asserting Reset\_ds to implement the double slope integration mode.

## 4.2 Read out of the image sensor

As soon as the information of the pixels is stored in to the memory element of each pixel, this information can be readout sequentially. As seen in the previous section, integration and readout can also be done in parallel.

The readout timing is straightforward and is basically controlled by means of sync and clock pulses.

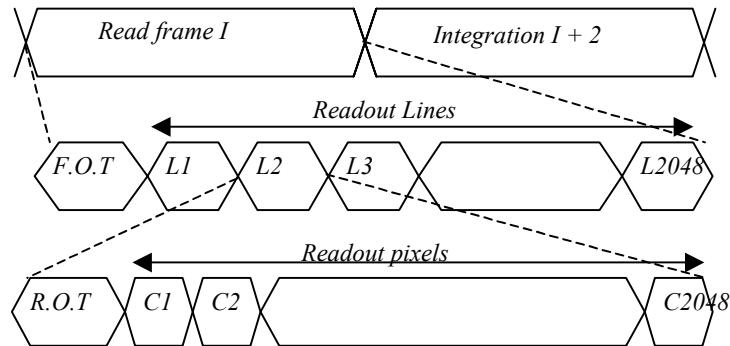

Figure 14 shows the top level concept of this timing. The readout of a frame consists of the frame overhead time, the selection of the lines sequentially and the readout of the pixels of the selected line.

Figure 14: Readout of the image sensor. F.O.T: Frame overhead time. R.O.T: Row overhead time.

L: selection of line, C: Selection of column.

The readout of an image consists of the FOT (Frame overhead time) and the sequential selection of all pixels. The FOT is the overhead time between 2 frames to transfer the information on the photodiode to the memory elements. From figure 13 it should be clear that this time is the time that Mem\_hl is low (typically 5  $\mu$ s). After the FOT the information is stored into the memory elements and a sequential selection of rows and columns makes sure the frame is read.

### 4.2.1 X- and Y-addressing

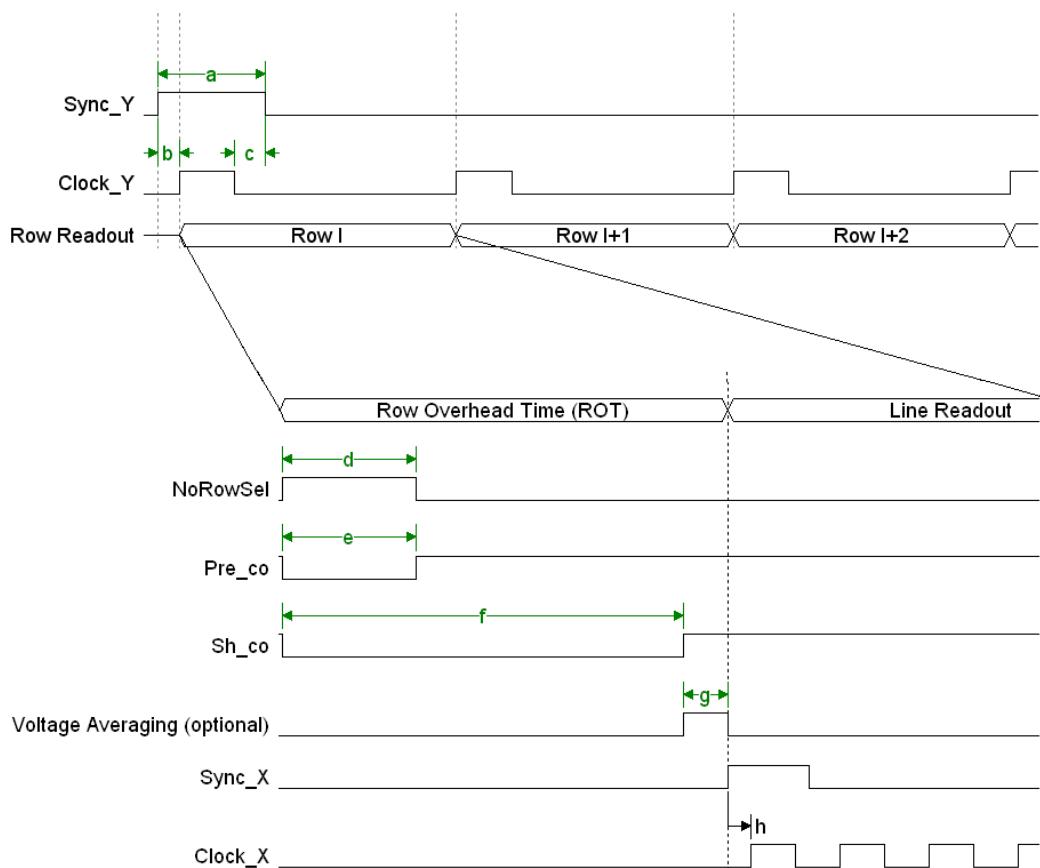

To readout a frame the lines are selected sequentially. Figure 15 gives the timing to select the lines sequentially. This is done by means of a Clock\_y and a Sync\_y signal. The Sync\_y signals synchronises the y-addressing and initialises the y-address selection registers. The start address is the address downloaded in the SPI multiplied by 2.

On the rising edge of Clock\_y the next line is selected. The Sync\_y signal is dominant and from the moment it occurs the y-address registers are initialised. If a Sync\_y pulse is given before the end of the frame is reached, only a part of the frame will be read. To obtain a correct initialisation Sync\_y must contain at least 1 rising edge of Clock\_y when it is active.

Figure 15: X- and Y-addressing

Table 13: Read-out timing specifications

| Symbol   | Name              | Value                                                                   |

|----------|-------------------|-------------------------------------------------------------------------|

| <b>a</b> | Sync_Y            | >20ns                                                                   |

| <b>b</b> | Sync_Y-Clock_Y    | >0ns                                                                    |

| <b>c</b> | Clock_Y-Sync_Y    | >0ns                                                                    |

| <b>d</b> | NoRowSel          | >50ns                                                                   |

| <b>e</b> | Pre_col           | >50ns                                                                   |

| <b>f</b> | Sh_col            | 200ns (more information on this timing can be found in section 4.2.2.a) |

| <b>g</b> | Voltage averaging | >20ns                                                                   |

| <b>h</b> | Sync_X-Clock_X    | >0ns                                                                    |

As soon as a new line is selected, it has to be read out by the output amplifiers. Before the pixels of the selected line can be multiplexed onto the output amplifiers, one has to wait a certain time, indicated as the ROT or Row overhead time shown in

figure 15. This is the time to get the data stable from the pixels to the output bus before the output stages. This ROT is in fact lost time and rather critical in a high-speed sensor. Different timings to reduce this ROT are explained in next paragraph. During the selection of 1 line, 2048 pixels are selected. These 2048 pixels have to be readout by 1 (or 2) output amplifier.

Please note that the pixel rate is the double frequency of the *Clock\_x* frequency. To obtain a pixel rate of 66 MHz, one needs to apply a pixel clock *Clock\_x* of 33MHz. When only 1 analog output is used 2 pixels are output every *Clock\_x* period. When *Clock\_x* is high, the first pixel is selected, when *Clock\_x* is low, the next pixel is selected. Consequently, during 1 complete period of *Clock\_x* 2 pixels are readout by the output amplifier.

If 2 analog outputs are used each *Clock-X* period 1 pixel is presented at each output.

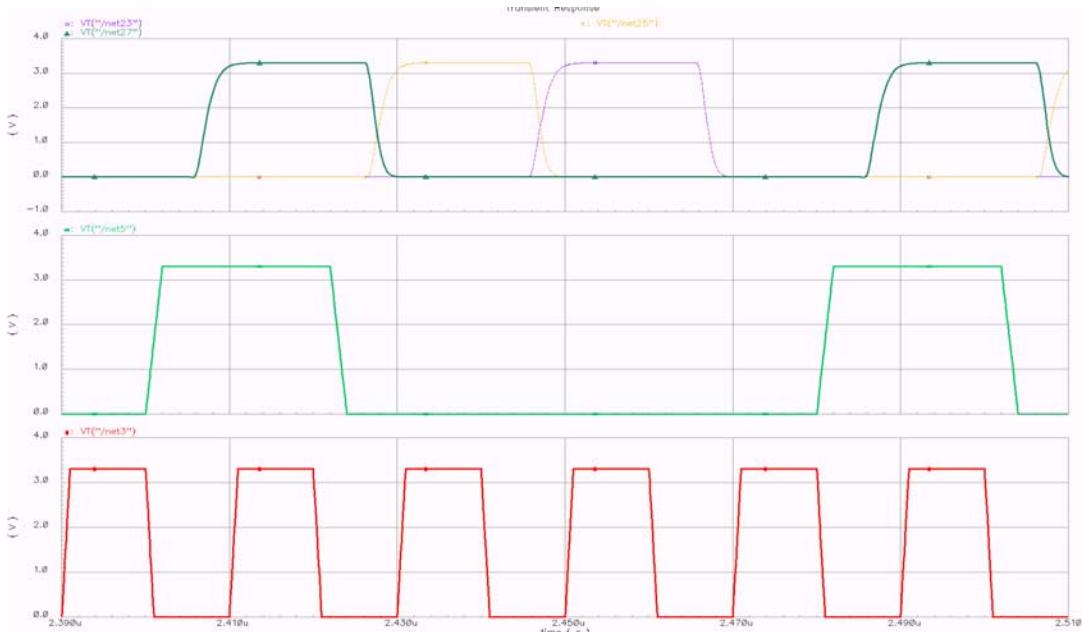

Figure 16: X-addressing. From bottom to top: *Clock\_x*, *Sync\_x*, internal selection pixel 1&2, internal selection pixel 3&4, internal selection pixel 5 & 6.

The first pixel that is selected is the x-address downloaded in the SPI. The starting address is the number downloaded into the SPI, multiplied with 2.

Windowing is achieved by a starting address downloaded in the SPI and the size of the window. In the x-direction, the size is determined by the moment a new *Clock\_y* is given. In the y-direction, the *sync\_y* pulse determines the size. Consequently, the best way to obtain a certain window is by using an internal counter in the controller.

Figure 16 is the simulation result after extraction of the layout module from a different sensor to show the principle. In this figure the pixel clock has a frequency of 50MHz, which would result in a pixel rate of 100 Msamples/sec.

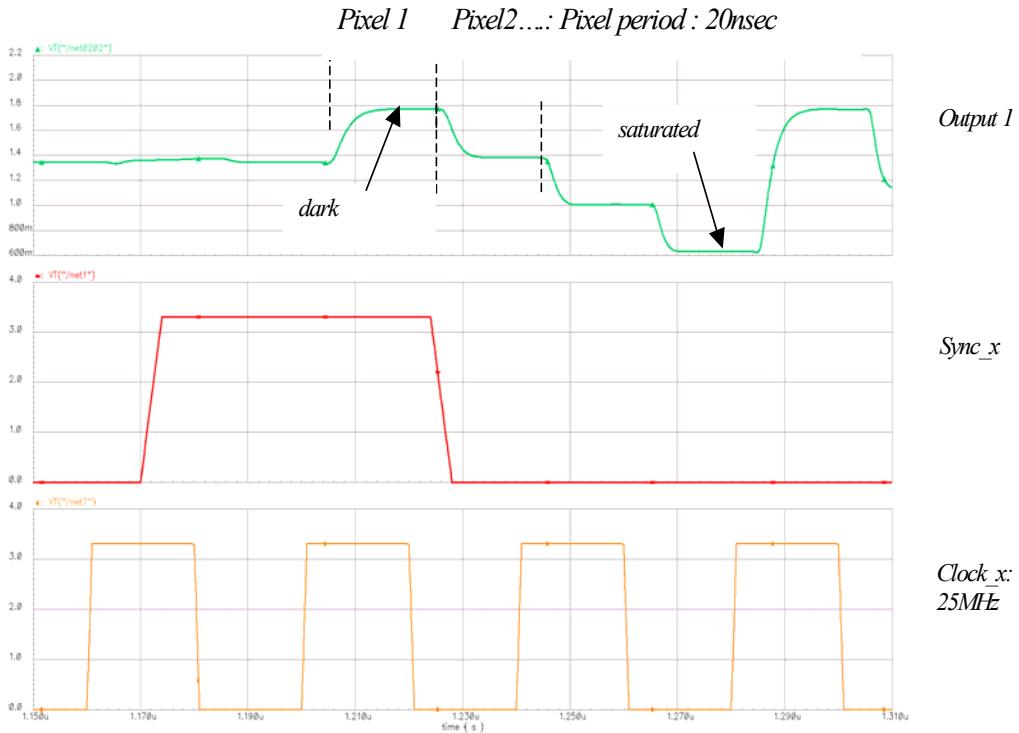

Figure 17 shows the relation between the applied *Clock\_x* and the output signal.

Figure 17: output signal related to Clock\_x signal. From bottom to top: Clock\_x, Sync\_x and output. The output level before the first pixel is the level of the last pixel of previous line.

As soon as Sync\_x is high and 1 rising edge of Clock\_x occurs, the pixels are brought to the analog outputs. This is again the simulation result of a comparable sensor to show the principle.

Please note there is a time difference between the clock edge and the moment the data is seen at the output. As this time difference is very difficult to predict in advance, it is advisable to have the ADC sampling clock flexible to set an optimal Adc sampling point. The time differences can easily vary between 5 – 15nsec and have to be tested on the real devices.

#### 4.2.2 Reduced Row Overhead Time timing

The row overhead time is the time between the selection of lines that one has to wait to get the data stable at the column amplifiers.

This row overhead time is a loss in time, which should be reduced as much as possible.

**4.2.2.a Standard timing (200ns)**

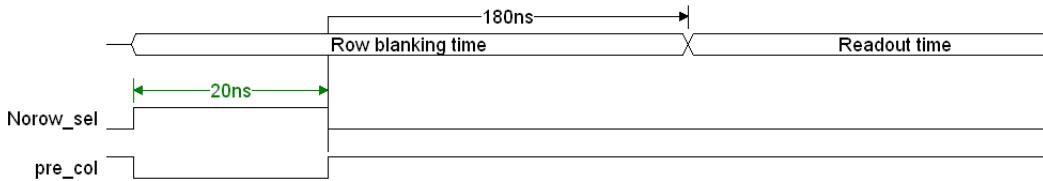

Figure 18: Standard timing for the R.O.T. Only pre\_col and Norowsel control signals are required.

In this case the control signals Norowsel and pre\_col are made active for about 20nsec from the moment the next line is selected. The time these pulses have to be active is related with the biasing resistance Pre\_load. The lower this resistance, the shorter the pulse duration of Norowsel and pre\_col may be. After these pulses are given, one has to wait for at least 180nsec before the first pixels can be sampled. For this mode Sh\_col must be made active all the time.

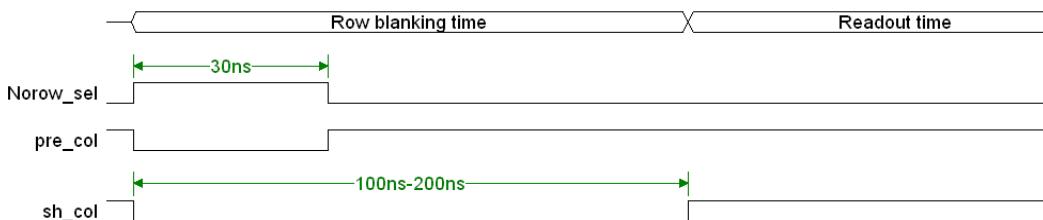

**4.2.2.b Back-up timing (ROT =100-200 ns)**

A straightforward way of reducing the R.O.T is by using a sample and hold function. By means of Sh\_col the analog data is tracked during the first 100nsec during the selection of a new set of lines. After 100nsec, the analog data is stored. The ROT is in this case reduced to 100nsec, but as the internal data was not stable yet dynamic range is lost because not the complete analog levels are reached yet after 100ns.

Figure 18 shows this principle. Sh\_col is now a pulse of 100ns-200ns starting at the same moment as pre\_col and Norowsel. The duration of Sh\_col is equal to the ROT. The shorter this time the shorter the ROT will be however this lowers also the dynamic range.

In case “voltage averaging” is required, the sensor must work in this mode with Sh\_col signal and a “voltage averaging” signal must be generated after Sh\_col drops and before the readout starts (see figure 15).

Figure 19: Reduced standard ROT by means of Sh\_col signal. pre\_col (short pulse) , Norowsel (short pulse) and Sh\_col (large pulse).

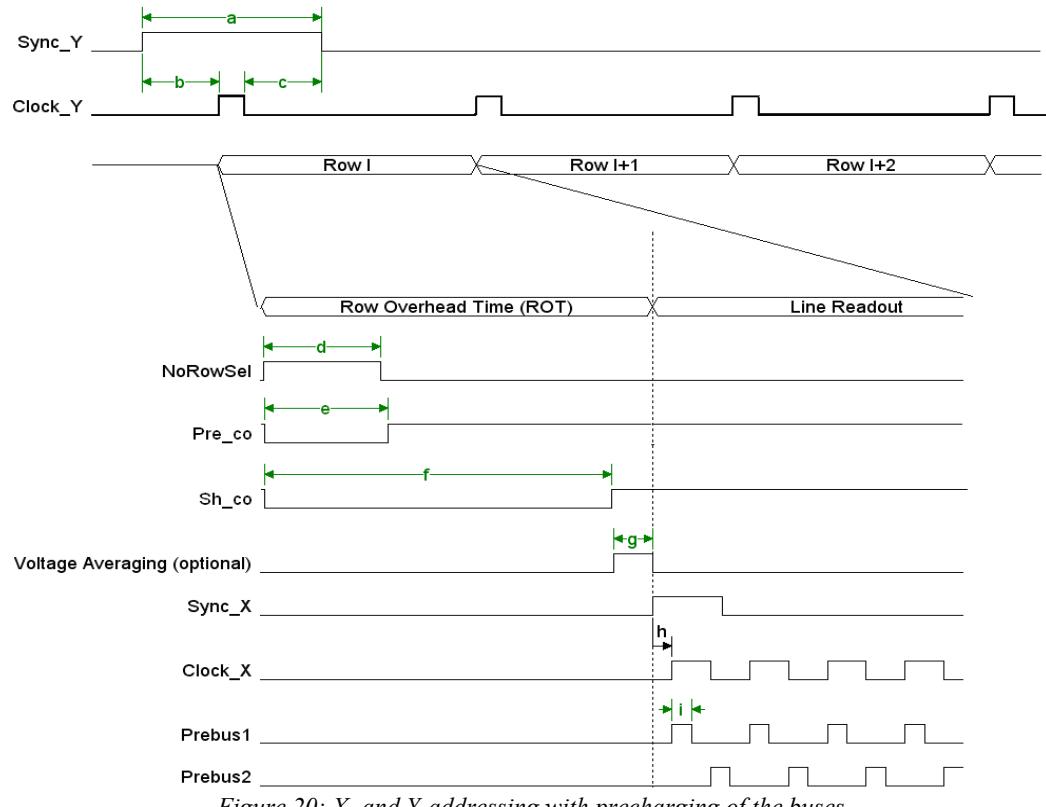

### 4.2.3 Precharging of the buses

This timing mode is exactly the same as the mode without sample and hold, except that the prebus1 and prebus2 signals are activated. It should be noticed that the precharging of the buses can be combined with all of the timing modes discussed above. The idea is to have a short pulse of about 5ns to precharge the output buses to a well-known level. This mode makes the ghosting of bad columns impossible.

In this mode, Nsf\_load must be made much larger (at least 1Mohms).

Figure 20: X- and Y-addressing with precharging of the buses

Table 14: Read-out timing specifications with precharging of the buses

| Symbol   | Name                     | Value                                         |

|----------|--------------------------|-----------------------------------------------|

| <b>a</b> | <i>Sync_Y</i>            | >20ns                                         |

| <b>b</b> | <i>Sync_Y-Clock_Y</i>    | >0ns                                          |

| <b>c</b> | <i>Clock_Y-Sync_Y</i>    | >0ns                                          |

| <b>d</b> | <i>NoRowSel</i>          | >50ns                                         |

| <b>e</b> | <i>Pre_col</i>           | >50ns                                         |

| <b>f</b> | <i>Sh_col</i>            | 200ns (or cst high, depending on timing mode) |

| <b>g</b> | <i>Voltage averaging</i> | >20ns                                         |

| <b>h</b> | <i>Sync_X-Clock_X</i>    | >0ns                                          |

| <b>i</b> | <i>Prebus pulse</i>      | As short as possible                          |

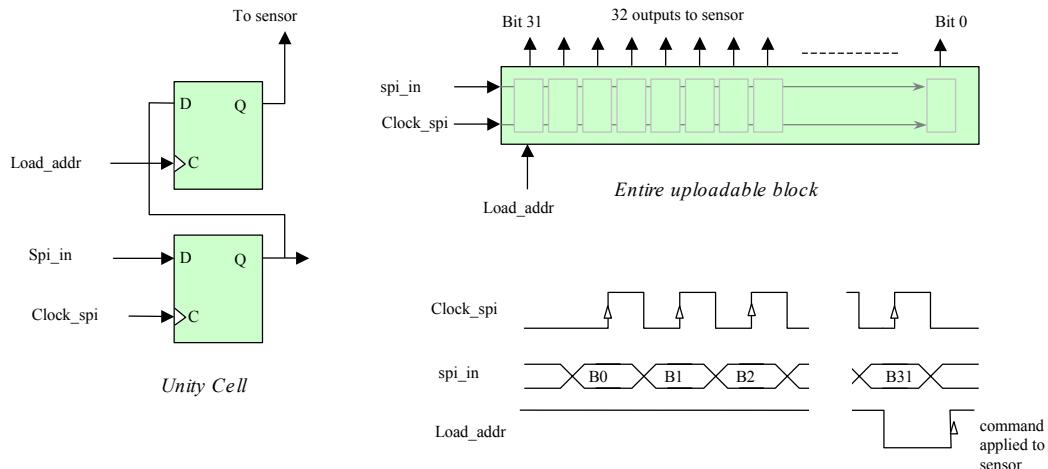

### 4.3 Serial-Parallel-Interface (SPI)

The SPI is required to upload the different modes. Table 15 shows the parameters and their bit position

Table 15: SPI parameters

| Parameter                         | Bit nr.      | Remarks                      |

|-----------------------------------|--------------|------------------------------|

| <b>Y-direction</b>                | <b>0</b>     | <i>1: from bottom to top</i> |

| <b>Y-address</b>                  | <b>1-10</b>  | <i>Bit 1 is LSB</i>          |

| <b>X-voltage averaging enable</b> | <b>11</b>    | <i>1: Enabled</i>            |

| <b>X-subsampling</b>              | <b>12</b>    | <i>1: Subsampling</i>        |

| <b>X-direction</b>                | <b>13</b>    | <i>0: From left to right</i> |

| <b>X-address</b>                  | <b>14-23</b> | <i>Bit 14 is LSB</i>         |

| <b>Nr output amplifiers</b>       | <b>24</b>    | <i>0: 1 Output</i>           |

| <b>DAC</b>                        | <b>25-31</b> | <i>Bit 25 is LSB</i>         |

When all zeros are loaded into the SPI, the sensor will start at pixel 0,0. The scanning will be from left to right and from top to bottom. There will be no sub-sampling or voltage averaging and only one output is used. The DAC will have the lowest level at its output.

When using sub sampling, only even X-addresses may be applied.

Figure 20: SPI block diagram and timing

## 5 Pin list

Table 16 is a list of all the pins and their functionalities.

Table 16: Pin list

| Pad | Pin       | Pin Name             | Pin Type       | Description                                                                                                                                                                       |

|-----|-----------|----------------------|----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1   | <i>E1</i> | <i>sync_x</i>        | <i>Input</i>   | <i>Digital input. Synchronises the X-address register.</i>                                                                                                                        |

| 2   | <i>F1</i> | <i>eos_x</i>         | <i>Testpin</i> | <i>Indicates when the end of the line is reached.</i>                                                                                                                             |

| 3   | <i>D2</i> | <i>vdd</i>           | <i>Supply</i>  | <i>Power supply digital modules.</i>                                                                                                                                              |

| 4   | <i>G2</i> | <i>clock_x</i>       | <i>Input</i>   | <i>Digital input. Determines the pixel rate.</i>                                                                                                                                  |

| 5   | <i>G1</i> | <i>eos_spi</i>       | <i>Testpin</i> | <i>Checks if the data is transferred correctly through the SPI.</i>                                                                                                               |

| 6   | <i>F2</i> | <i>spi_data</i>      | <i>Input</i>   | <i>Digital input. Data for the SPI.</i>                                                                                                                                           |

| 7   | <i>H1</i> | <i>spi_load</i>      | <i>Input</i>   | <i>Digital input. Loads data into the SPI.</i>                                                                                                                                    |

| 8   | <i>H2</i> | <i>spi_clock</i>     | <i>Input</i>   | <i>Digital input. Clock for the SPI.</i>                                                                                                                                          |

| 9   | <i>J2</i> | <i>gndo</i>          | <i>Ground</i>  | <i>Ground output stages</i>                                                                                                                                                       |

| 10  | <i>J1</i> | <i>out2</i>          | <i>Output</i>  | <i>Analog output 2.</i>                                                                                                                                                           |

| 11  | <i>K1</i> | <i>out2DC</i>        | <i>Output</i>  | <i>Reference output 2.</i>                                                                                                                                                        |

| 12  | <i>M2</i> | <i>voo</i>           | <i>Supply</i>  | <i>Power supply output stages</i>                                                                                                                                                 |

| 13  | <i>L1</i> | <i>out1DC</i>        | <i>Output</i>  | <i>Reference output 1.</i>                                                                                                                                                        |

| 14  | <i>M1</i> | <i>out1</i>          | <i>Output</i>  | <i>Analog output 1.</i>                                                                                                                                                           |

| 15  | <i>N2</i> | <i>gndo</i>          | <i>Ground</i>  | <i>Ground output stages.</i>                                                                                                                                                      |

| 16  | <i>P1</i> | <i>vaa</i>           | <i>Supply</i>  | <i>Power supply analog modules.</i>                                                                                                                                               |

| 17  | <i>P2</i> | <i>gnra</i>          | <i>Ground</i>  | <i>Ground analog modules.</i>                                                                                                                                                     |

| 18  | <i>N1</i> | <i>va3</i>           | <i>Supply</i>  | <i>Power supply column modules.</i>                                                                                                                                               |

| 19  | <i>P3</i> | <i>vpix</i>          | <i>Supply</i>  | <i>Power supply pixel array.</i>                                                                                                                                                  |

| 20  | <i>Q1</i> | <i>psf_load</i>      | <i>Input</i>   | <i>Analog reference input. Biasing for column modules. Connect with <math>R=1M\Omega</math> to <math>Vaa</math> and decouple with <math>C=100nF</math> to <math>gnra</math>.</i>  |

| 21  | <i>Q2</i> | <i>nsf_load</i>      | <i>Input</i>   | <i>Analog reference input. Biasing for column modules. Connect with <math>R=5k\Omega</math> to <math>Vaa</math> and decouple with <math>C=100nF</math> to <math>gnra</math>.</i>  |

| 22  | <i>R1</i> | <i>muxbus_load</i>   | <i>Input</i>   | <i>Analog reference input. Biasing for multiplex bus. Connect with <math>R=25k\Omega</math> to <math>Vaa</math> and decouple with <math>C=100nF</math> to <math>gnra</math>.</i>  |

| 23  | <i>R2</i> | <i>uni_load_fast</i> | <i>Input</i>   | <i>Analog reference input. Biasing for column modules. Connect with <math>R=10k\Omega</math> to <math>Vaa</math> and decouple with <math>C=100nF</math> to <math>gnra</math>.</i> |

| 24  | <i>Q3</i> | <i>pre_load</i>      | <i>Input</i>   | <i>Analog reference input. Biasing for column modules. Connect with <math>R=3k\Omega</math> to <math>Vaa</math> and decouple with <math>C=100nF</math> to <math>gnra</math>.</i>  |

| 25  | <i>Q4</i> | <i>out_load</i>      | <i>Input</i>   | <i>Analog reference input. Biasing for output stage. Connect with <math>R=60k\Omega</math> to <math>Vaa</math> and decouple with <math>C=100nF</math> to <math>gnra</math>.</i>   |

| 26  | <i>N3</i> | <i>dec_x_load</i>    | <i>Input</i>   | <i>Analog reference input. Biasing for X-addressing. Connect with <math>R=2M\Omega</math> to <math>Vdd</math> and decouple with <math>C=100nF</math> to <math>gndd</math>.</i>    |

| 27  | <i>Q5</i> | <i>uni_load</i>      | <i>Input</i>   | <i>Analog reference input. Biasing for column modules. Connect with <math>R=1M\Omega</math> to <math>Vaa</math> and decouple with <math>C=100nF</math> to <math>gnra</math>.</i>  |

| 28  | <i>Q6</i> | <i>col_load</i>      | <i>Input</i>   | <i>Analog reference input. Biasing for column modules. Connect with <math>R=1M\Omega</math> to <math>Vaa</math> and decouple with <math>C=100nF</math> to <math>gnra</math>.</i>  |

| Pad | Pin        | Pin Name            | Pin Type | Description                                                                                                                    |

|-----|------------|---------------------|----------|--------------------------------------------------------------------------------------------------------------------------------|

| 29  | <i>Q7</i>  | <i>dec_y_load</i>   | Input    | <i>Analog reference input. Biasing for Y-addressing. Connect with R=2MΩ to Vdd and decouple with C=100nF to gndd.</i>          |

| 30  | <i>R3</i>  | <i>vdd</i>          | Supply   | <i>Power supply digital modules.</i>                                                                                           |

| 31  | <i>M3</i>  | <i>gndd</i>         | Ground   | <i>Ground digital modules.</i>                                                                                                 |

| 32  | <i>L2</i>  | <i>prebus1</i>      | Input    | <i>Digital input. Control signal to reduce readout time.</i>                                                                   |

| 33  | <i>L3</i>  | <i>prebus2</i>      | Input    | <i>Digital input. Control signal to reduce readout time.</i>                                                                   |

| 34  | <i>Q8</i>  | <i>sh_col</i>       | Input    | <i>Digital input. Control signal of the column readout.</i>                                                                    |

| 35  | <i>R4</i>  | <i>pre_col</i>      | Input    | <i>Digital input. Control signal of the column readout to reduce row-blanking time.</i>                                        |

| 36  | <i>R5</i>  | <i>norowsel</i>     | Input    | <i>Digital input. Control signal of the column readout.</i>                                                                    |

| 37  | <i>R6</i>  | <i>clock_y</i>      | Input    | <i>Digital input. Clock of the Y-addressing.</i>                                                                               |

| 38  | <i>R7</i>  | <i>sync_y</i>       | Input    | <i>Digital input. Synchronises the Y-address register.</i>                                                                     |

| 39  | <i>K2</i>  | <i>eos_y_r</i>      | Testpin  | <i>Indicates when the end of frame is reached when scanning in the 'right' direction.</i>                                      |

| 40  | <i>Q9</i>  | <i>temp_diode_p</i> | Testpin  | <i>Anode of temperature diode.</i>                                                                                             |

| 41  | <i>Q10</i> | <i>temp_diode_n</i> | Testpin  | <i>Cathode of temperature diode.</i>                                                                                           |

| 42  | <i>R8</i>  | <i>vpix</i>         | Supply   | <i>Power supply pixel array.</i>                                                                                               |

| 43  | <i>R9</i>  | <i>vmem_l</i>       | Supply   | <i>Power supply Vmem drivers.</i>                                                                                              |

| 44  | <i>R10</i> | <i>vmem_h</i>       | Supply   | <i>Power supply Vmem drivers.</i>                                                                                              |

| 45  | <i>R11</i> | <i>vres</i>         | Supply   | <i>Power supply reset drivers.</i>                                                                                             |

| 46  | <i>Q11</i> | <i>vres_ds</i>      | Supply   | <i>Power supply reset drivers.</i>                                                                                             |

| 47  | <i>R12</i> | <i>ref_low</i>      | Input    | <i>Analog reference input. Low reference voltage of ADC. (see figure 7 for exact resistor value)</i>                           |

| 48  | <i>Q12</i> | <i>linear_conv</i>  | Input    | <i>Digital input. 0= linear conversion; 1= gamma correction.</i>                                                               |

| 49  | <i>P15</i> | <i>bit_9</i>        | Output   | <i>Digital output 1 &lt;9&gt; (MSB).</i>                                                                                       |

| 50  | <i>Q14</i> | <i>bit_8</i>        | Output   | <i>Digital output 1 &lt;8&gt;.</i>                                                                                             |

| 51  | <i>Q15</i> | <i>bit_7</i>        | Output   | <i>Digital output 1 &lt;7&gt;.</i>                                                                                             |

| 52  | <i>R13</i> | <i>bit_6</i>        | Output   | <i>Digital output 1 &lt;6&gt;.</i>                                                                                             |

| 53  | <i>R14</i> | <i>bit_5</i>        | Output   | <i>Digital output 1 &lt;5&gt;.</i>                                                                                             |

| 54  | <i>R15</i> | <i>bit_4</i>        | Output   | <i>Digital output 1 &lt;4&gt;.</i>                                                                                             |

| 55  | <i>P14</i> | <i>bit_3</i>        | Output   | <i>Digital output 1 &lt;3&gt;.</i>                                                                                             |

| 56  | <i>Q13</i> | <i>bit_2</i>        | Output   | <i>Digital output 1 &lt;2&gt;.</i>                                                                                             |

| 57  | <i>R16</i> | <i>bit_1</i>        | Output   | <i>Digital output 1 &lt;1&gt;.</i>                                                                                             |

| 58  | <i>Q16</i> | <i>bit_0</i>        | Output   | <i>Digital output 1 &lt;0&gt; (LSB).</i>                                                                                       |

| 59  | <i>P16</i> | <i>clock</i>        | Input    | <i>ADC clock input.</i>                                                                                                        |

| 60  | <i>N14</i> | <i>gndd</i>         | Supply   | <i>Digital GND of ADC circuitry.</i>                                                                                           |

| 61  | <i>N15</i> | <i>vddd</i>         | Supply   | <i>Digital supply of ADC circuitry (nominal 2.5V).</i>                                                                         |

| 62  | <i>L16</i> | <i>gnda</i>         | Supply   | <i>Analog GND of ADC circuitry.</i>                                                                                            |

| 63  | <i>L15</i> | <i>vdda</i>         | Supply   | <i>Analog supply of ADC circuitry (nominal 2.5V).</i>                                                                          |

| 64  | <i>N16</i> | <i>bit_inv</i>      | Input    | <i>Digital input. 0=no inversion of output bits; 1 = inversion of output bits.</i>                                             |

| 65  | <i>M16</i> | <i>CMD_SS</i>       | Input    | <i>Analog reference input. Biasing of second stage of ADC. Connect to VDDA with R=50kΩ and decouple with C=100 nF to GNDA.</i> |

| 66  | <i>L14</i> | <i>analog_in</i>    | Input    | <i>Analog input of 1<sup>st</sup> ADC.</i>                                                                                     |

| 67  | <i>M15</i> | <i>CMD_FS</i>       | Input    | <i>Analog reference input. Biasing of first stage of ADC. Connect to VDDA with R=50kΩ and decouple with C=100 nF to GNDA.</i>  |

| Pad | Pin        | Pin Name            | Pin Type       | Description                                                                                                                    |

|-----|------------|---------------------|----------------|--------------------------------------------------------------------------------------------------------------------------------|

| 68  | <i>M14</i> | <i>ref_high</i>     | <i>Input</i>   | <i>Analog reference input. High reference voltage of ADC. (see figure 7 for exact resistor value)</i>                          |

| 69  | <i>K14</i> | <i>vres_ds</i>      | <i>Supply</i>  | <i>Power supply reset drivers.</i>                                                                                             |

| 70  | <i>J14</i> | <i>vres</i>         | <i>Supply</i>  | <i>Power supply reset drivers.</i>                                                                                             |

| 71  | <i>J15</i> | <i>vpre_l</i>       | <i>Supply</i>  | <i>Power supply precharge drivers. Must be able to sink current. Can also be connected to ground.</i>                          |

| 72  | <i>J16</i> | <i>vdd</i>          | <i>Supply</i>  | <i>Power supply digital modules.</i>                                                                                           |

| 73  | <i>K15</i> | <i>vmem_h</i>       | <i>Supply</i>  | <i>Power supply Vmem drivers.</i>                                                                                              |

| 74  | <i>K16</i> | <i>vmem_l</i>       | <i>Supply</i>  | <i>Power supply Vmem drivers.</i>                                                                                              |

| 75  | <i>H15</i> | <i>ref_low</i>      | <i>Input</i>   | <i>Analog reference input. Low reference voltage of ADC. (see figure 7 for exact resistor value)</i>                           |

| 76  | <i>H16</i> | <i>linear_conv</i>  | <i>Input</i>   | <i>Digital input. 0= linear conversion; 1= gamma correction.</i>                                                               |

| 77  | <i>G16</i> | <i>bit_9</i>        | <i>Output</i>  | <i>Digital output 2 &lt;9&gt; (MSB).</i>                                                                                       |

| 78  | <i>F16</i> | <i>bit_8</i>        | <i>Output</i>  | <i>Digital output 2 &lt;8&gt;.</i>                                                                                             |

| 79  | <i>E16</i> | <i>bit_7</i>        | <i>Output</i>  | <i>Digital output 2 &lt;7&gt;.</i>                                                                                             |

| 80  | <i>G15</i> | <i>bit_6</i>        | <i>Output</i>  | <i>Digital output 2 &lt;6&gt;.</i>                                                                                             |

| 81  | <i>G14</i> | <i>bit_5</i>        | <i>Output</i>  | <i>Digital output 2 &lt;5&gt;.</i>                                                                                             |