## LM4921 Boomer® Audio Power Amplifier Series

# Low Voltage I<sup>2</sup>S 16-Bit Stereo DAC with Stereo Headphone Power Amplifiers and Volume Control

### **General Description**

The LM4921 combines a 16-bit resolution stereo I²S input digital-to-analog converter (DAC) with a stereo headphone audio power amplifier. It is primarily designed for demanding applications in mobile phones and other portable communication device applications. The LM4921 features an I²S serial interface for the digital audio information and a 16-bit SPI serial interface for internal register control and communication. With AV $_{\rm DD}$  and DV $_{\rm DD}=3.0{\rm V}_{\rm DC}$  and driving a 32 $\Omega$  single-ended load to a 26mW $_{\rm RMS}$  output level the distortion (THD+N) of the LM4921 will be less than 0.5%. The LM4921 also features a programmable 32-step digital volume control accessed through an SPI interface.

Boomer audio power amplifiers were designed specifically to provide high quality output power with a minimal amount of external components. It is, therefore, ideally suited for mobile phone and other low voltage applications where minimal power consumption is a primary requirement.

The LM4921 features a low-power consumption shutdown mode, and also has an internal thermal shutdown protection mechanism.

### **Key Specifications**

■ PSRR at 217Hz, A/DV<sub>DD</sub> = 3V, (Fig. 1) 52dB (typ)

$\blacksquare$  P<sub>OUT</sub> at AV<sub>DD</sub> = 3.0V, 32 $\Omega$

< 0.05% THD 13mW (typ) < 0.5% THD 26mW (typ)

■ Supply voltage range

$\mathrm{DV_{DD}}$  2.6V to 5.0V  $\mathrm{AV_{DD}}$  (Note 8) 2.6V to 5.5V

■ Shutdown current 1µA (typ)

#### **Features**

- 16-bit resolution stereo DAC

- I<sup>2</sup>S digital audio data serial interface

- SPI serial interface (control register)

- Volume Control (32 steps; 1.5 dB increments)

- Up to 50mW/channel stereo headphone amplifier

- Zero Crossing Detection for Silent Attenuation Steps

- 2.6V<sub>DC</sub> to 5.0V<sub>DC</sub> digital supply voltage range

- 2.6V<sub>DC</sub> to 5.5V<sub>DC</sub> analog supply voltage range (Note 8)

- Unity-gain stable headphone amplifiers

- Available in the 20-bump microSMD package

## **Applications**

- Mobile phones

- PDAs

- Portable electronic devices

Boomer® is a registered trademark of National Semiconductor Corporation.

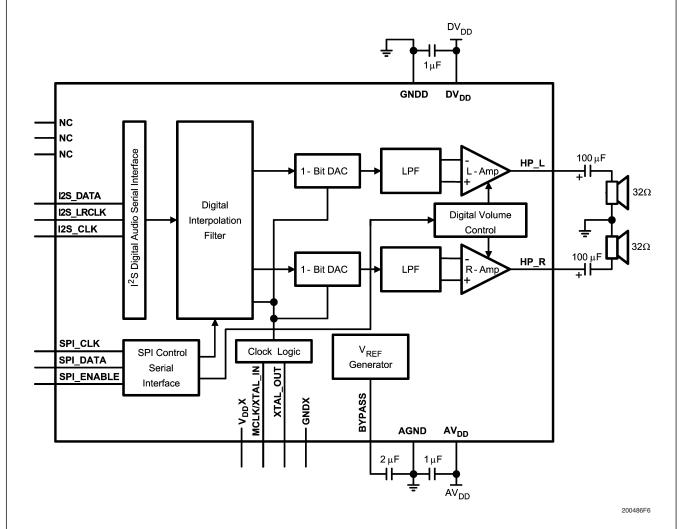

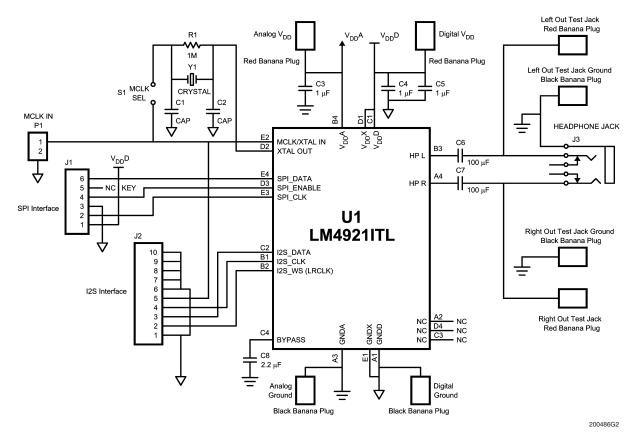

## **Typical Application**

FIGURE 1. Typical Audio Amplifier Application Circuit

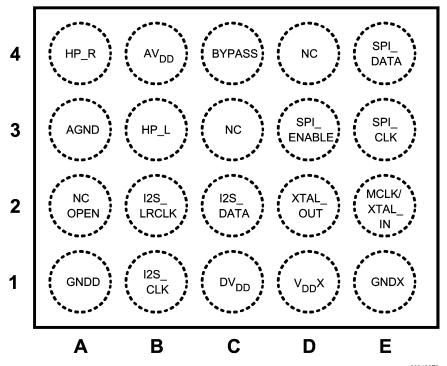

## **Connection Diagrams**

#### LM4921 Pin Configuration

200486F8

Top View

20-Bump micro SMD

Order Number LM4921ITL, LM4921ITLX

See NS Package Number TLA20JKA

NC - No Connection

#### 20-Bump micro SMD Marking

200486F9

X - Date Code T - Die Traceability G - Boomer Family B9 - LM4921ITL

## LM4921 I/O Pin Descriptions

| PIN # (ITL) | PIN NAME         | PIN TYPE<br>Input-I, Output-O,<br>Power-P, No Connect-NC | PIN DESCRIPTION                                |  |  |

|-------------|------------------|----------------------------------------------------------|------------------------------------------------|--|--|

| B1          | I2S_CLK          | I/O                                                      | I2S Clock                                      |  |  |

| C2          | I2S_DATA         | I                                                        | I2S data                                       |  |  |

| B2          | I2S_WS           | I/O                                                      | I2S L/R word select                            |  |  |

| E3          | SPI_CLK          | I                                                        | SPI clcock                                     |  |  |

| E4          | SPI_DATA         | I                                                        | SPI data                                       |  |  |

| D3          | SPI_ENABLE       | I                                                        | SPI Enable                                     |  |  |

| E2          | MCLK/XTAL_IN     | I                                                        | Master Clock / Xtal input                      |  |  |

| D2          | XTAL_OUT         | 0                                                        | Xtal output                                    |  |  |

| C4          | BYPASS           | I/O                                                      | Analog VDD/2 bypass capacitor connection point |  |  |

| B4          | AV <sub>DD</sub> | Р                                                        | Analog supply                                  |  |  |

| A3          | AGND             | Р                                                        | Analog Ground                                  |  |  |

| C1          | DV <sub>DD</sub> | Р                                                        | Digital Supply                                 |  |  |

| A1          | GNDD             | Р                                                        | Digital ground                                 |  |  |

| D1          | VDDX             | Р                                                        | XTAL Oscillator circuit supply                 |  |  |

| E1          | GNDX             | Р                                                        | XTAL Oscillator circuit ground                 |  |  |

| B3          | HP_L             | 0                                                        | HP left output                                 |  |  |

| A4          | HP_R             | 0                                                        | HP right output                                |  |  |

| A2          | No Connect       | 0                                                        | Must let float                                 |  |  |

| C3          | No Connect       | NC                                                       | NC                                             |  |  |

| D4          | No Connect       | NC                                                       | NC                                             |  |  |

Absolute Maximum Ratings (Notes 1, 2)

If Military/Aerospace specified devices are required, please contact the National Semiconductor Sales Office/ Distributors for availability and specifications.

Supply Voltage 6.0V Storage Temperature -65°C to +150°C Input Voltage -0.3V to  $V_{DD} + 0.3V$ Power Dissipation (Note 3) Internally Limited

**ESD Susceptibility**

Human body model (Note 4) 2000V Machine model (Note 5) 200V

150°C Junction Temperature Thermal Resistance

60°C/W  $\theta_{\mathsf{JA}}$

## **Operating Ratings**

Temperature Range

$-40^{\circ}\text{C} \le \text{T}_{\text{A}} \le 85^{\circ}\text{C}$  $T_{MIN} \le T_A \le T_{MAX}$

Supply Voltage

$\mathsf{DV}_\mathsf{DD}$  $2.6V \leq DV_{DD} \leq 5.0V$  $2.6V \le AV_{DD} \le 5.5V$  $\mathsf{AV}_\mathsf{DD}$

# Electrical Characteristics $DV_{DD} = 3.0V$ , $AV_{DD} = 5.0V$ , $R_L = 32\Omega$ (Notes 1, 2) The following specifications apply for the circuit shown in Figure 1 unless otherwise specified. Limits apply for $T_A = 25$ °C.

|                    |                                          |                                                                                                                               | LM       | 1124         |                  |  |

|--------------------|------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------|----------|--------------|------------------|--|

| Symbol             | Parameter                                | Conditions                                                                                                                    | Typical  | Limit        | Units            |  |

|                    |                                          |                                                                                                                               | (Note 6) | (Notes 7, 9) | (Limits)         |  |

| DV <sub>DD</sub>   | Digital Power Supply Voltage             | Note 8                                                                                                                        | 3.0      |              | V                |  |

| $AV_{DD}$          | Analog Power Supply Voltage              | Note 8                                                                                                                        | 5.0      |              | V                |  |

| $DI_DD$            | Digital Power Supply Quiescent Current   | $R_{Load} = \infty$ , $f_{MLCK} = 11.2896MHz$                                                                                 | 3.5      | 7.5          | mA (max)         |  |

| $Al_{DD}$          | Analog Power Supply Quiescent<br>Current | $R_{Load} = \infty$ , $f_{MCLK} = 0MHz$                                                                                       | 6        | 10           | mA (max)         |  |

| I <sub>SD</sub>    | Total Shutdown Power Supply<br>Current   | SHUTDOWN SPI bits 1 & 2 set to logic 0,<br>SPI, M <sub>CLK</sub> and I <sup>2</sup> S inputs at GND                           | 1        | 5            | uA(max)          |  |

| I <sub>SB</sub>    | Standby Current                          | Analog and Digital together All clocks off                                                                                    | 25       |              | uA               |  |

| V <sub>FS</sub>    | Full-Scale Output Voltage                | Gain set at max                                                                                                               | 3.5      |              | V <sub>P-P</sub> |  |

| THD+N              | Total Harmonic Distortion + Noise        | f <sub>IN</sub> = 1kHz, P <sub>OUT</sub> = 12mW<br>(Vol Control = 11111, I <sup>2</sup> S input adj<br>to get 12mW at output) | 0.03     |              | %                |  |

| Po                 | Headphone Amplifier Output Power         | THD = (0.5%), f <sub>OUT</sub> = 1kHz                                                                                         | 50       | 40           | mW (min)         |  |

| PSRR               | Power Supply Rejection Ratio             | $AV_{DD} C_{BYPASS} = 2.0 \mu F$<br>$V_{RIPPLE} = 200 mV_{P-P} 217 Hz$                                                        | 62       | 45           | dB (min)         |  |

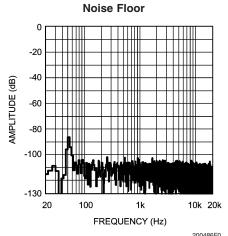

| SNR                | Signal-to-Noise Ratio                    | $f_{IN}$ = 1kHz sinewave at -60dB <sub>FS</sub> ,<br>A-weighted-f <sub>CONV</sub> = 44.1kHz                                   | 82       |              | dB               |  |

| DR                 | Dynamic Range                            | f <sub>IN</sub> = 1kHz sinewave at -60dB <sub>FS</sub> ,<br>A-weighted                                                        | 84       |              | dB               |  |

| $\Delta A_{CH-CH}$ | Channel-to-Channel Gain Mismatch         | f <sub>IN</sub> = 1kHz                                                                                                        | 0.06     |              | dB               |  |

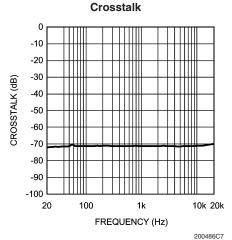

| X <sub>TALK</sub>  | Channel-to-Channel Crosstalk             | $f_{CONV} = 44.1 \text{kHz},$<br>$f_{IN} = 1 \text{kHz}$ sinewave at -3dB <sub>FS</sub>                                       | 72       |              | dB               |  |

|                    | Volume Control Range                     | Minimum Attenuation                                                                                                           | +3.0     |              | dB               |  |

|                    |                                          | Maximum Attenuation                                                                                                           | -43.5    |              | dB               |  |

|                    | Volume Control Control Step Size         |                                                                                                                               | 1.5      |              | dB               |  |

|                    | Mute Attenuation                         |                                                                                                                               | -102     |              | dB               |  |

# Electrical Characteristics $DV_{DD}=3.0V$ , $AV_{DD}=3.0V$ , $R_L=32\Omega$ (Notes 1, 2) The following specifications apply for the circuit shown in Figure 1 unless otherwise specified. Limits apply for $T_A=25^{\circ}C$ .

|                           |                                           |                                                                                                                            | LM         | 11           |                  |

|---------------------------|-------------------------------------------|----------------------------------------------------------------------------------------------------------------------------|------------|--------------|------------------|

| Symbol                    | Parameter                                 | Conditions                                                                                                                 | Typical    | Limit        | Units            |

|                           |                                           |                                                                                                                            | (Note 6)   | (Notes 7, 9) | (Limits)         |

| $DV_DD$                   | Digital Power Supply Voltage              | Note 8                                                                                                                     | 3.0        |              | V                |

| $AV_{DD}$                 | Analog Power Supply Voltage               | Note 8                                                                                                                     | 3.0        |              | V                |

| $DI_DD$                   | Digital Power Supply Quiescent<br>Current | $R_{Load} = \infty$ , $f_{MLCK} = 11.2896MHz$                                                                              | 3.5        | 7.5          | mA (max)         |

| $AI_DD$                   | Analog Power Supply Quiescent<br>Current  | $R_{Load} = \infty$ , $f_{MCLK} = 0MHz$                                                                                    | 5          | 9.0          | mA (max)         |

| I <sub>SD</sub>           | Total Shutdown Power Supply<br>Current    | SHUTDOWN SPI bits 1 & 2 set to logic 0, SPI, M <sub>CLK</sub> and I <sup>2</sup> S inputs at GND                           | 1          |              | uA(max)          |

| I <sub>SB</sub>           | Standby Current                           | Analog and Digital together All clocks off                                                                                 | 15         |              | uA               |

| V <sub>FS</sub>           | Full-Scale Output Voltage                 | Gain set at max                                                                                                            | 2.6        |              | V <sub>P-P</sub> |

| THD+N                     | Total Harmonic Distortion + Noise         | f <sub>IN</sub> = 1kHz, P <sub>OUT</sub> = 12mW<br>(Vol Cont = 11011, I <sup>2</sup> S input adj to<br>get 12mW at output) | 0.05       |              | %                |

| Po                        | Headphone Amplifier Output Power          | THD = (0.5%), f <sub>OUT</sub> = 1kHz                                                                                      | 26         |              | mW (min)         |

| PSRR                      | Power Supply Rejection Ratio              | $AV_{DD} C_{BYPASS} = 2.0 \mu F$<br>$V_{RIPPLE} = 200 m V_{P-P} 217 Hz$                                                    | 52         |              | dB (min)         |

| SNR                       | Signal-to-Noise Ratio                     | f <sub>IN</sub> = 1kHz sinewave at -60dB <sub>FS</sub> ,<br>A-weighted-f <sub>CONV</sub> = 44.1kHz                         | 79         |              | dB               |

| DR                        | Dynamic Range                             | f <sub>IN</sub> = 1kHz sinewave at -60dB <sub>FS</sub> ,<br>A-weighted                                                     | 81         |              | dB               |

| $\Delta A_{\text{CH-CH}}$ | Channel-to-Channel Gain Mismatch          | f <sub>IN</sub> = 1kHz                                                                                                     | 0.06       |              | dB               |

| X <sub>TALK</sub>         | Channel-to-Channel Crosstalk              | $f_{CONV} = 44.1 \text{kHz},$<br>$f_{IN} = 1 \text{kHz}$ sinewave at -3dB <sub>FS</sub>                                    | 72         |              | dB               |

|                           | Volume Control Range                      | Minimum Attenuation Maximum Attenuation                                                                                    | 0<br>-43.5 |              | dB<br>dB         |

|                           | Volume Control Control Step Size          |                                                                                                                            | 1.5        |              | dB               |

|                           | Mute Attenuation                          |                                                                                                                            | -100       |              | dB               |

# Electrical Characteristics-Digital Inputs $DV_{DD} = 3.0V$ (Notes 1, 2) The following specifications apply for the circuit shown in Figure 1 unless otherwise specified. Limits apply for $T_A = 25^{\circ}C$ .

| Symbol              |                                                           |                                            | LM       | LM4921                 |           |  |

|---------------------|-----------------------------------------------------------|--------------------------------------------|----------|------------------------|-----------|--|

|                     | Parameter                                                 | Conditions                                 | Typical  | Limit                  | Units     |  |

|                     |                                                           |                                            | (Note 6) | (Notes 7, 9)           | (Limits)  |  |

|                     | Resolution                                                |                                            | 16       |                        | Bits      |  |

| I <sup>2</sup> S    | Audio Data Interface Format                               | Standard, I <sup>2</sup> S, Left Justified |          |                        |           |  |

| f <sub>MCLK</sub>   | Master Clock Frequency                                    |                                            | 11.2896  |                        | MHz       |  |

|                     |                                                           |                                            | (256FS)  |                        |           |  |

| $f_{CONV}$          | Sampling Clock Frequency Range                            |                                            | 44.1     | 48                     | kHz       |  |

| $V_{IL}$            | Digital Input: Logic Low Voltage                          |                                            |          | 0.3 X DV <sub>DD</sub> | V (max)   |  |

|                     | Level                                                     |                                            |          |                        |           |  |

| $V_{IH}$            | Digital Input: Logic High Voltage                         |                                            |          | 0.7 X DV <sub>DD</sub> | V (min)   |  |

|                     | Level                                                     |                                            |          |                        |           |  |

| t <sub>ES</sub>     | SPI_ENB Setup Time                                        |                                            |          | 20                     | ns (min)  |  |

| t <sub>EH</sub>     | SPI_ENB Hold Time                                         |                                            |          | 20                     | ns (min)  |  |

| t <sub>EL</sub>     | SPI_ENB Low Time                                          |                                            |          | 30                     | ns (min)  |  |

| t <sub>DS</sub>     | SPI_Data Setup Time                                       |                                            |          | 20                     | ns (min)  |  |

| t <sub>DH</sub>     | SPI_Data Hold Time                                        |                                            |          | 20                     | ns (min)  |  |

| t <sub>CS</sub>     | SPI_CLK Setup Time                                        |                                            |          | 20                     | ns (min)  |  |

| t <sub>CH</sub>     | SPI_CLK High Pulse Width                                  |                                            |          | 100                    | ns (min)  |  |

| t <sub>CL</sub>     | SPI_CLK Low Pulse Width                                   |                                            |          | 100                    | ns (min)  |  |

| f <sub>CLK</sub>    | SPI_CLK Frequency                                         |                                            |          | 5                      | MHz (max) |  |

| $t_{CLKI}^2S$       | I <sup>2</sup> S_CLK Period                               |                                            |          | 50                     | ns (min)  |  |

| t <sub>HII</sub> 2S | I <sup>2</sup> S_CLK High Pulse Width                     |                                            |          | 20                     | ns (min)  |  |

| + 00                | I <sup>2</sup> S_CLK Low Pulse Width                      |                                            |          | 20                     | ns (min)  |  |

| t <sub>LOI</sub> 2S | I <sup>2</sup> S_LRCLK Duty Cycle                         |                                            | 50       |                        | %         |  |

| t <sub>SLRCLK</sub> | I <sup>2</sup> S_LRCLK to I <sup>2</sup> S_CLK Setup Time |                                            |          | 20                     | ns (min)  |  |

| t <sub>HLRCLK</sub> | I <sup>2</sup> S_LRCLK to I <sup>2</sup> S_CLK Hold Time  |                                            |          | 20                     | ns (min)  |  |

| t <sub>SDI</sub> 2S | I <sup>2</sup> S_Data to I <sup>2</sup> S_CLK Setup Time  |                                            |          | 20                     | ns (min)  |  |

| t <sub>HDI</sub> 2S | I <sup>2</sup> S_Data to I <sup>2</sup> S_CLK Hold Time   |                                            |          | 20                     | ns (min)  |  |

Note 1: Absolute Maximum Ratings indicate limits beyond which damage to the device may occur. Operating Ratings indicate conditions for which the device is functional, but do not guarantee specific performance limits. Electrical Characteristics state DC and AC electrical specifications under particular test conditions which guarantee specific performance limits. This assumes that the device is within the Operating Ratings. Specifications are not guaranteed for parameters where no limit is given, however, the typical value is a good indication of device performance.

Note 2: All voltages are measured with respect to the GND pin, unless otherwise specified.

Note 3: The maximum power dissipation must be derated at elevated temperatures and is dictated by  $T_{JMAX}$ ,  $\theta_{JA}$ , and the ambient temperature  $T_A$ . The maximum  $allowable \ power \ dissipation \ is \ P_{DMAX} = (T_{JMAX} - T_A)/\theta_{JA} \ or \ the \ number \ given \ in \ Absolute \ Maximum \ Ratings, \ whichever \ is \ lower.$

- Note 4: Human body model, 100pF discharged through a 1.5k $\Omega$  resistor.

- Note 5: Machine Model, 220pF 240pF discharged through all pins.

- Note 6: Typicals are measured at 25°C and represent the parametric norm.

- Note 7: Limits are guaranteed to National's AOQL (Average Outgoing Quality Level).

- **Note 8:** Best operation is achieved by maintaining  $3.0V \le AV_{DD} \le 5.0V$  and  $3.0V \le DV_{DD} \le 5.0V$ .

- Note 9: Datasheet min/max specification limits are guaranteed by design, test, or statistical analysis.

## **Typical Performance Characteristics**

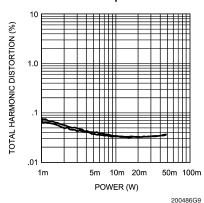

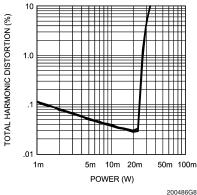

#### THD+N vs Output Power

Analog V $_{\rm DD}$  = 5V, Digital V $_{\rm DD}$  = 3V R $_{\rm L}$  = 32 $\Omega$ , 44.1 kHz Sample Rate R & L Channels, Vol = 3dB, Frequency in = 1kHz

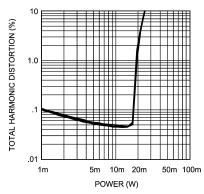

## THD+N vs Output Power

Analog  $V_{DD}$  = 3V, Digital  $V_{DD}$  = 3V  $R_L$  = 32 $\Omega$ , 44.1 kHz Sample Rate R & L Channels Shown, Vol = 3dB, Frequency in = 1kHz

#### THD+N vs Output Power

Analog  $V_{DD}$  = 2.6V, Digital  $V_{DD}$  = 2.6V  $R_L$  = 32 $\Omega$ , 44.1 kHz Sample Rate R & L Channels Shown, Vol = 3dB, Frequency in = 1kHz

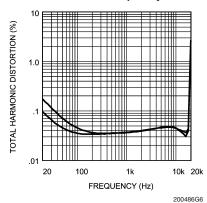

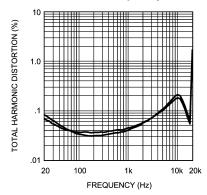

#### THD+N vs Frequency

Analog  $V_{DD}$  = 5V, Digital  $V_{DD}$  = 3V  $R_L$  = 32 $\Omega$ , Power Level = 50mW R & L Channels Shown, 44.1kHz Sample Rate

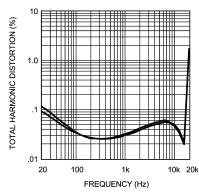

#### THD+N vs Frequency

Analog  $V_{DD}$  = 3V, Digital  $V_{DD}$  = 3V  $R_L$  = 32 $\Omega$ , Power Level = 12mW R & L Channels Shown, 44.1kHz Sample Rate

#### THD+N vs Frequency

Analog  $V_{DD}$  = 2.6V, Digital  $V_{DD}$  = 2.6V  $R_{L}$  = 32 $\Omega$ , Power Level = 12mW R & L Channels Shown, 44.1kHz Sample Rate

## Typical Performance Characteristics (Continued)

Analog  $V_{DD} = 3V$ , Digital  $V_{DD} = 3V$  $RL = 32\Omega$ , Vol = 3dB44.1kHz Sample Rate, -3dB FFS

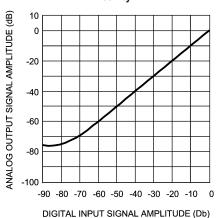

## Linearity ANALOG OUTPUT SIGNAL AMPLITUDE (dB) -20 -40 -60 -80 -90 -80 -70 -60 -50 -40 -30 -20 -10 DIGITAL INPUT SIGNAL AMPLITUDE (dB)

Analog  $V_{DD} = 5V$ , Digital  $V_{DD} = 3V$  $R_L = 32\Omega$ , 44.1kHz Sample Rate

Analog V $_{\rm DD}$  = 5V, Digital V $_{\rm DD}$  = 3V R $_{\rm L}$  = 32 $\Omega$ , Vol = 3dB, 44.1kHz Sample Rate

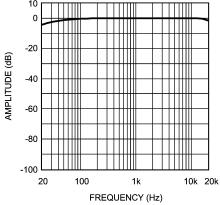

#### **Frequency Response**

200486E1

Analog  $V_{DD}$  = 5V, Digital  $V_{DD}$  = 3V  $RL = 32\Omega$ , Vol = 0dB44.1kHz Sample Rate, 0dB FFS

#### Linearity

Analog  $V_{DD} = 3V$ , Digital  $V_{DD} = 3V$  $R_L = 32\Omega$ , 44.1kHz Sample Rate

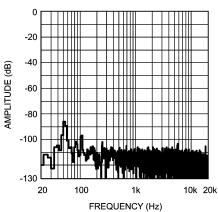

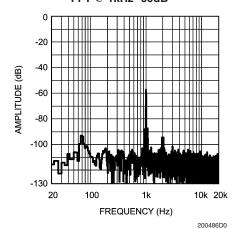

#### **Noise Floor**

Analog V $_{\rm DD}$  = 3V, Digital V $_{\rm DD}$  = 3V R $_{\rm L}$  = 32 $\Omega$ , Vol = 0dB, 44.1kHz Sample Rate

## **Typical Performance Characteristics** (Continued)

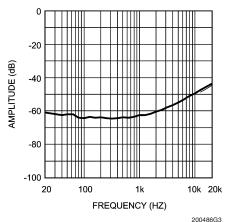

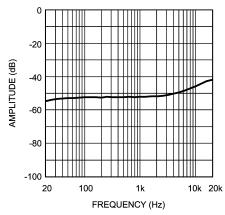

#### **PSRR vs Frequency**

Analog  $V_{DD}$  = 5V, Digital  $V_{DD}$  = 3V  $R_L$  = 32 $\Omega$ , Vol = 3dB, 44.1kHz Sample Rate

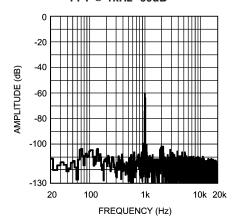

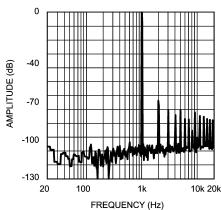

#### FFT @ 1kHz -60dB

Analog  $V_{DD}$  = 5V, Digital  $V_{DD}$  = 3V  $R_L$  = 32 $\Omega$ , Vol = 3dB, 44.1kHz Sample Rate

#### FFT @ 1kHz -60dB

Analog V $_{DD}$  = 3V, Digital V $_{DD}$  = 3V R $_{L}$  = 32 $\Omega$ , Vol = 0dB, 44.1kHz Sample Rate

#### **PSRR vs Frequency**

200486E7

Analog V $_{DD}$  = 3V, Digital V $_{DD}$  = 3V R $_{L}$  = 32 $\Omega$ , Vol = 0dB, 44.1kHz Sample Rate

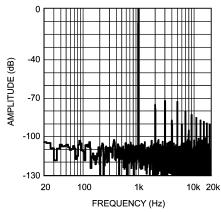

#### FFT @ 1kHz 0dB

02.101 (1.2)

Analog V $_{DD}$  = 5V, Digital V $_{DD}$  = 3V R $_{L}$  = 32 $\Omega$ , Vol = 3dB, 44.1kHz Sample Rate

#### FFT @ 1kHz 0dB

200486F

Analog V $_{DD}$  = 3V, Digital V $_{DD}$  = 3V R $_{L}$  = 32 $\Omega$ , Vol = 0dB, 44.1kHz Sample Rate

### **Application Information**

#### SPI OPERATIONAL DESCRIPTION

The serial data bits are organized into a field which contains 16 bits of data defined by TABLE 1. Bits 1 & 2 determine the output mode of the LM4921 as shown in TABLE 2. Bits 7 through 11 determine the volume level setting as illustrated by TABLE 3. Bit 12 sets the Bypass capacitor charging time.

Table 1. Bit Allocation

| BIT #    | Default Val | Function          | Description                       |

|----------|-------------|-------------------|-----------------------------------|

| 0 (LSB)  | 0           | RESET_B           | RESET_B = 0, Resets the DAC       |

|          |             |                   | Must be high for the part to run. |

| 1        | 0           | MODE CONTROL      | See Table 2                       |

| 2        | 0           | MODE CONTROL      | See Table 2                       |

| 3        | 0           | MASTER/SLAVE      | 0 = SLAVE, 1 = MASTER             |

| 4        | 0           | RESOLUTION        | 0 = 16 bit, 1 = 32 bit            |

| 5        | 0           | RESERVED          | Should always be set to '1'       |

| 6        | 0           | ZERO CROSSING SET | 0 = ZXD ENABLE, 1 = ZXD           |

|          |             |                   | DISABLE                           |

| 7        | 0           | VOLUME CONTROL    | See Table 3 - Volume Control      |

| 8        | 0           |                   | Settings                          |

| 9        | 0           |                   |                                   |

| 10       | 0           |                   |                                   |

| 11       | 0           |                   |                                   |

| 12       | 0           | BYP CHARGE RATE   | 0 = 1X, 1 = 2X                    |

| 13       | 0           | RESERVED          |                                   |

| 14       | 0           | RESERVED          |                                   |

| 15 (MSB) | 0           | RESERVED          | Should always be set to '0'       |

#### MODE CONTROL

Sets the modes as outlined in Table 2.

Table 2. Output Mode Selection (Bits 1 & 2 above)

| Output Mode # | BIT 2 | BIT 1 | MODE    |

|---------------|-------|-------|---------|

| 0             | 0     | 0     | SD      |

| 1             | 0     | 1     | STANDBY |

| 2             | 1     | 0     | MUTE    |

| 3             | 1     | 1     | ACTIVE  |

Shutdown turns off the part completely for maximum power savings. The Standby mode turns off the clock but still consumes more power than the shutdown mode. However, coming out of standby mode allows the part to turn back on faster than from shutdown. In Mute mode the clocks remain on which uses more power but allows faster recovery and the ability to supply clock signals to other devices which is important when the part is used in master mode. Active mode turns the part on for normal operation.

#### MASTER/SLAVE SELECT

Allows the part to act as a master and supply the clock for the rest of the system or be a slave to the system clock.

#### **RESOLUTION SET**

Sets the resolution to be either 16 or 32 bits of stereo audio information. For most applications this will be set at 16 bits.

#### ZERO CROSSING DETECT SET

This pin turns on the zero crossing detection circuit. With this circuit enabled the part will not allow a volume step change, or shutdown mode, or standby mode to occur until the audio input signal passes through zero. This pin should be set to on for most applications.

#### **VOLUME CONTROL**

The internal Stereo Volume Control is set by changing bits 7 through 11 in the SPI interface, as shown in table 3 below. The zero dB setting is for 3V VDD operation and the +3dB is for 5V VDD.

**Table 3. Volume Control Settings**

| Gain (dB)   | <b>D</b> 11.44 |        | Dir o |       | 5     |

|-------------|----------------|--------|-------|-------|-------|

| HP_L & HP_R | Bit 11         | Bit 10 | Bit 9 | Bit 8 | Bit 7 |

| -43.5       | 0              | 0      | 0     | 0     | 0     |

| -42.0       | 0              | 0      | 0     | 0     | 1     |

| -40.5       | 0              | 0      | 0     | 1     | 0     |

| -39.0       | 0              | 0      | 0     | 1     | 1     |

| -37.5       | 0              | 0      | 1     | 0     | 0     |

| -36.0       | 0              | 0      | 1     | 0     | 1     |

| -34.5       | 0              | 0      | 1     | 1     | 0     |

| -33.0       | 0              | 0      | 1     | 1     | 1     |

| -31.5       | 0              | 1      | 0     | 0     | 0     |

| -30.0       | 0              | 1      | 0     | 0     | 1     |

| -28.5       | 0              | 1      | 0     | 1     | 0     |

| -27.0       | 0              | 1      | 0     | 1     | 1     |

| -25.5       | 0              | 1      | 1     | 0     | 0     |

| -24.0       | 0              | 1      | 1     | 0     | 1     |

| -22.5       | 0              | 1      | 1     | 1     | 0     |

| -21.0       | 0              | 1      | 1     | 1     | 1     |

| -19.5       | 1              | 0      | 0     | 0     | 0     |

| -18.0       | 1              | 0      | 0     | 0     | 1     |

| -16.5       | 1              | 0      | 0     | 1     | 0     |

| -15.0       | 1              | 0      | 0     | 1     | 1     |

| -13.5       | 1              | 0      | 1     | 0     | 0     |

| -12.0       | 1              | 0      | 1     | 0     | 1     |

| -10.5       | 1              | 0      | 1     | 1     | 0     |

| -9.0        | 1              | 0      | 1     | 1     | 1     |

| -7.5        | 1              | 1      | 0     | 0     | 0     |

| -6.0        | 1              | 1      | 0     | 0     | 1     |

| -4.5        | 1              | 1      | 0     | 1     | 0     |

| -3.0        | 1              | 1      | 0     | 1     | 1     |

| -1.5        | 1              | 1      | 1     | 0     | 0     |

| 0.0         | 1              | 1      | 1     | 0     | 1     |

| 1.5         | 1              | 1      | 1     | 1     | 0     |

| 3.0         | 1              | 1      | 1     | 1     | 1     |

#### **BYPASS CHARGE RATE BIT 12**

This control pin allows the user to change the Bypass Capacitor's charge rate by a factor of two. Setting this bit at zero will set the circuit to it's normal 1x rate. Setting the bit to High will double the charge rate and allow the part to turn on faster with a slight degradation in turn on click/pop noise.

#### SPI CONTROL INTERFACE BUS (J1)

SPI DATA: This is the serial data pin.

SPI CLK: This is the clock input pin.

SPI ENABLE: This is the SPI enable pin.

#### BITS 5, 13,14, and 15

Bits 13, 14, and 15 are all reserve bits and must be set to low/zero/ground.

Bit 5 must be set High.

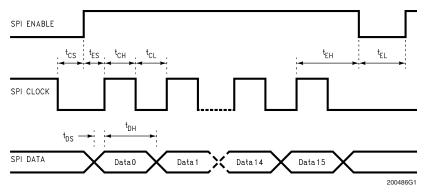

#### SPI TIMING DIAGRAM

#### SPI OPERATIONAL REQUIREMENTS

- 1. The maximum clock rate is 5MHz for the CLK pin.

- 2. CLK must remain logic-high for at least 100ns ( $t_{CH}$ ) after the rising edge of CLK, and CLK must remain logic-low for at least 100ns ( $t_{CL}$ ) after the falling edge of CLK.

- 3. Data bits are written to the DATA pin with the least significant bit (LSB) first.

- 4. The serial data bits are sampled at the rising edge of CLK. Any transition on DATA must occur at least 20ns ( $t_{DS}$ ) before the rising edge of CLK. Also, any transition on DATA must occur at least 20ns ( $t_{DH}$ ) after the rising edge of CLK and stabilize before the next rising edge of CLK.

- 5. ENABLE should be logic-high only during serial data transmission.

- 6. ENABLE must be logic-high at least 20ns ( $t_{\rm ES}$ ) before the first rising edge of CLK, and ENABLE has to remain logic-high at least 20ns ( $t_{\rm EH}$ ) after the sixteenth rising edge of CLK.

- 7. If ENABLE remains logic-low for more than 10ns before all 16 bits are transmitted then the data latch will be aborted.

- 8. If ENABLE is logic-high for more than 16 CLK pulses then only the first 16 data bits will be latched and activated at rising edge of sixteenth CLK.

- 9. ENABLE must remain logic-low for at least 30ns ( $t_{\text{EL}}$ ).

- 10. Coincidental rising or falling edges of CLK and ENABLE are not allowed. If CLK is to be held logic-high after the data transmission, the falling edge of CLK must occur at least 20ns ( $t_{\rm CS}$ ) before ENABLE transitions to logic-high for the next set of data.

#### I2S INTERFACE BUS (J2 - Fig 2)

The I2S standard provides a uni-directional serial interface designed specifically for digital audio. For the LM4921, the interface provides access to a 48kHz, 16 bit full-range stereo

audio DAC. This interface uses a three wire system of clock (I2S\_CLK), data (I2S\_DATA), and word select (I2S\_WS, sometimes called Right/Left Select).

A bit clock (I2S\_CLK) at 32 or 64 times the sample frequency is established by the I2S system master and the word select (I2S\_WS) line is driven at a frequency equal to the sampling rate of the audio data, in this case 48kHz. The word line is registered to change on the positive edge of the bit clock. The serial data (I2S\_DATA) is sent MSB first, again registers on the positive edge of the bit clock, delayed by 1 bit clock cycle relative to the changing of the word line (typical I<sup>2</sup>S format).

#### MCLK/XTAL\_IN (S1 MCLK SEL - Fig 2)

This is the input for an external Master Clock. The jumper at S1 must be removed (disconnecting the onboard crystal from the circuit) when using an external Master Clock.

#### STEREO HEADPHONE OUTPUT JACK (J3 - Fig 2)

This is the stereo headphone output. Each channel is single-ended, with 100uF DC output blocking capacitors mounted on the demo board (C6 and C7). These capacitors are necessary to block the 1/2 VDD DC bias and prevent it from flowing through the headphone speakers (DC current will destroy most audio speakers) while allowing the audio ac signal to pass through. The jack features a typical stereo headphone pinout.

#### LM4921ITL DEMO BOARD OPERATION

The LM4921ITL demo board is a complete evaluation platform (Note 10), designed to give easy access to the control pins of the part and comprise all the necessary external passive components. There are separate analog and digital supply connectors, SPI interface bus (J1) for the control lines, I<sup>2</sup>S interface bus (J2) for full-range digital audio, stereo headphone output (J3), and an external MCLK input (P1) for use in place of the crystal on the demoboard.

FIGURE 2. LM4921ITL Demo Board Schematic

Note 10: Parallel Port SPI Interface Card and control software available.

#### **DEMO BOARD BILL OF MATERIALS**

| Natio | National Semiconductor Corporation Bill of Material |                                           |     |                          |  |  |  |

|-------|-----------------------------------------------------|-------------------------------------------|-----|--------------------------|--|--|--|

| Analo | Analog Audio LM4921ITL20 Eval Board                 |                                           |     |                          |  |  |  |

| Assei | Assembly Part Number: 980011973-100                 |                                           |     |                          |  |  |  |

| Revis | ion A                                               |                                           |     |                          |  |  |  |

| Item  | Part Number                                         | Part Description                          | Qty | Ref Designator           |  |  |  |

| 1     | 551011973-001                                       | LM4921 Eval Board PCB etch                | 1   |                          |  |  |  |

| 2     |                                                     | LM4921 ITL20 micro SMD 20<br>Bumps        | 1   | U1                       |  |  |  |

| 3     |                                                     | Cer Cap 22pF 50V 10%, size 1206           | 2   | C1, C2                   |  |  |  |

| 4     |                                                     | Cer Cap 0.1pF 50V 10%, size 1206          | 1   | C4                       |  |  |  |

| 5     |                                                     | Tant Cap 1µF 16V 10%, 3216                | 3   | C3, C5, C8               |  |  |  |

| 6     |                                                     | Tant Cap 220µF 16V 10%, 7243              | 2   | C6, C7                   |  |  |  |

| 7     |                                                     | 1 meg ohm                                 | 1   | R1                       |  |  |  |

| 8     |                                                     | Crystal 11.2896MHz                        | 1   | Y1                       |  |  |  |

| 9     |                                                     | Phone Jack 3.5mm Stereo                   | 1   | J3                       |  |  |  |

| 10    |                                                     | Jumper Header 1X2                         | 2   | P1, S1                   |  |  |  |

| 11    |                                                     | Jumper Header 1X3                         | 2   | J1                       |  |  |  |

| 12    |                                                     | Jumper Header 1X5                         | 2   | J2                       |  |  |  |

| 13    |                                                     | PCB Banana Jack,<br>Black-Mouser 164-6218 | 4   | A GND, D GND, GND (2)    |  |  |  |

| 14    |                                                     | PCB Banana Jack,<br>Red-Mouser 164-6219   | 4   | A VDD, D VDD, HP L, HP R |  |  |  |

# Application Information (Continued) **DEMO BOARD ARTWORKS** A VDD A GND JЗ Stereo Headphone LM4921 ITL National Semiconductor I2S\_CLK I2S\_DATA I2S\_WS SPI Interface J2 I2S Interfacel MCLK IN D VDD D GND -3000 (m11)--3000 (mıl)-200486F3 200486F1 Silkscreen Layer **Top Layer** 200486F2 200486H1 Mid Layer 1 Mid Layer 2

**Bottom Layer**

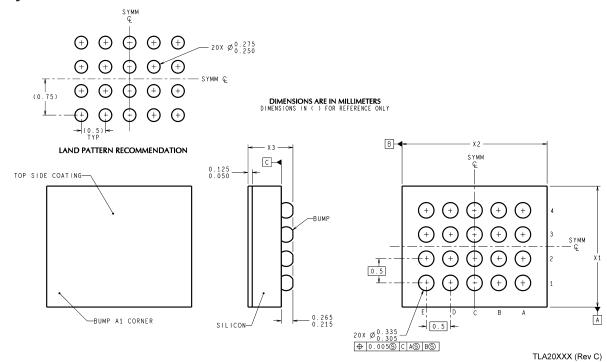

### Physical Dimensions inches (millimeters) unless otherwise noted

National does not assume any responsibility for use of any circuitry described, no circuit patent licenses are implied and National reserves the right at any time without notice to change said circuitry and specifications.

For the most current product information visit us at www.national.com.

#### LIFE SUPPORT POLICY

NATIONAL'S PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS WITHOUT THE EXPRESS WRITTEN APPROVAL OF THE PRESIDENT AND GENERAL COUNSEL OF NATIONAL SEMICONDUCTOR CORPORATION. As used herein:

- Life support devices or systems are devices or systems which, (a) are intended for surgical implant into the body, or (b) support or sustain life, and whose failure to perform when properly used in accordance with instructions for use provided in the labeling, can be reasonably expected to result in a significant injury to the user.

- A critical component is any component of a life support device or system whose failure to perform can be reasonably expected to cause the failure of the life support device or system, or to affect its safety or effectiveness.

#### **BANNED SUBSTANCE COMPLIANCE**

National Semiconductor certifies that the products and packing materials meet the provisions of the Customer Products Stewardship Specification (CSP-9-111C2) and the Banned Substances and Materials of Interest Specification (CSP-9-111S2) and contain no "Banned Substances" as defined in CSP-9-111S2.

National Semiconductor Americas Customer Support Center

Email: new.feedback@nsc.com Tel: 1-800-272-9959

www.national.com

National Semiconductor

Europe Customer Support Center

Fax: +49 (0) 180-530 85 86

Email: europe.support@nsc.com

Email: europe.support@nsc.com

Deutsch Tel: +49 (0) 69 9508 6208

English Tel: +44 (0) 870 24 0 2171

Français Tel: +33 (0) 1 41 91 8790

National Semiconductor Asia Pacific Customer Support Center Email: ap.support@nsc.com National Semiconductor Japan Customer Support Center Fax: 81-3-5639-7507 Email: jpn.feedback@nsc.com Tel: 81-3-5639-7560