- High-Performance Static CMOS Technology

- Includes the T320C2xx Core CPU

- Object-Compatible With the TMS320C2xx

- Source-Code-Compatible With TMS320C25

- Upwardly Compatible With TMS320C5x

- 50-ns Instruction Cycle Time

- Pin Compatible to Emulation Device TMS320F241 (64-Pin/68-Pin)

- Code Compatible to Emulation Devices TMS320F243 and TMS320F241

- Commercial and Industrial Temperature Available

- Memory

- 544 Words x 16 Bits of On-Chip Data/Program Dual-Access RAM (DARAM)

- 4K Words x 16 Bits of On-chip Program ROM

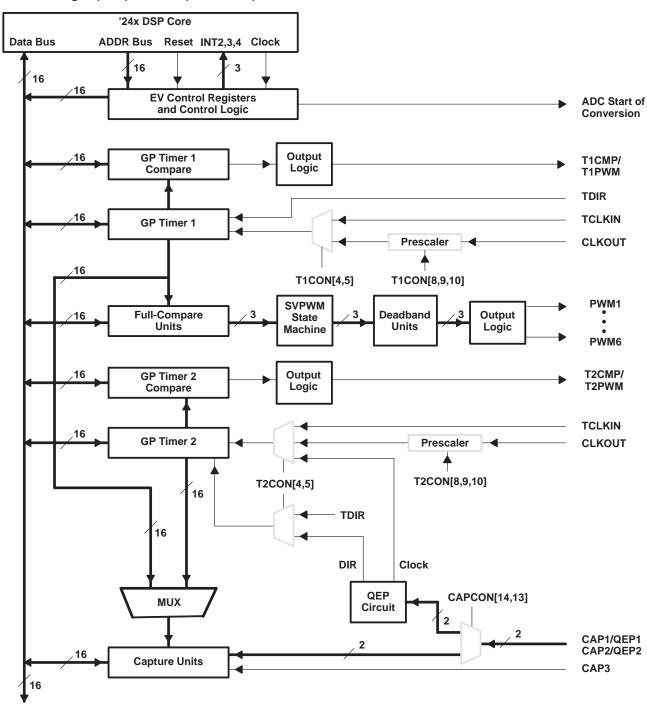

- Event-Manager Module

- Eight Compare/Pulse-Width Modulation (PWM) Channels

- Two 16-Bit General-Purpose Timers With Six Modes, Including Continuous Upand Up/Down Counting

- Three 16-Bit Full Compare Units With Deadband

- Three Capture Units (Two With Quadrature Encoder-Pulse Interface Capability)

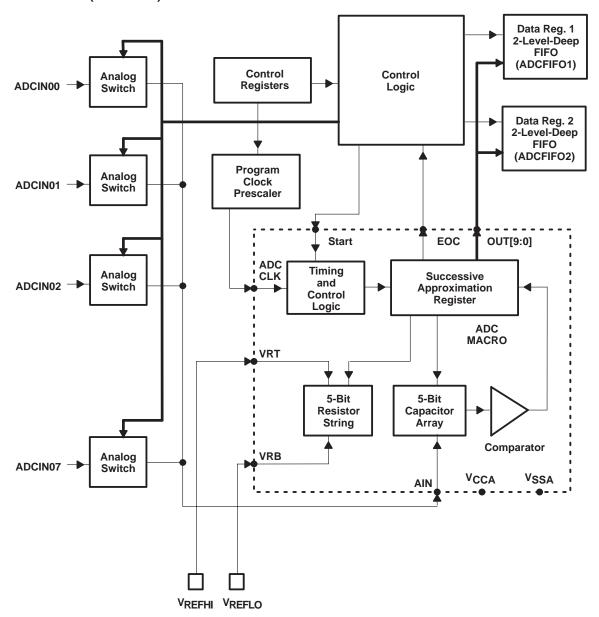

- Single 10-Bit Analog-to-Digital Converter (ADC) Module With 8 Multiplexed Input Channels

- 26 Individually Programmable, Multiplexed General-Purpose I/O (GPIO) Pins

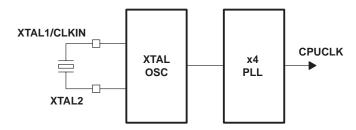

- Phase-Locked-Loop (PLL)-Based Clock

- Watchdog (WD) Timer Module

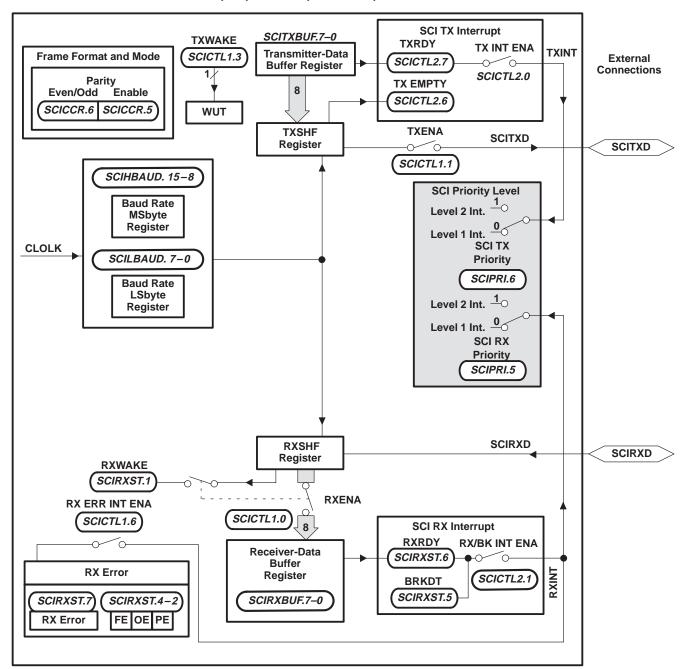

- Serial Communications Interface (SCI)

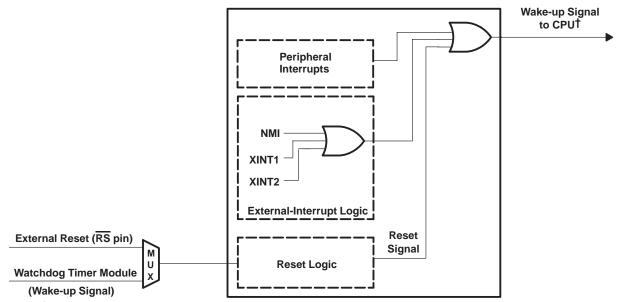

- Five External Interrupts (Power Drive Protection, Reset, NMI, and Two Maskable Interrupts)

- Three Power-Down Modes for Low-Power Operation

- Scan-Based Emulation

- Development Tools Available:

- Texas Instruments (TI™) ANSI C Compiler, Assembler/Linker, and C-Source Debugger

- Full Range of Emulation Products

Self-Emulation (XDS510™)

- Third-Party Digital Motor Control and Fuzzy-Logic Development Support

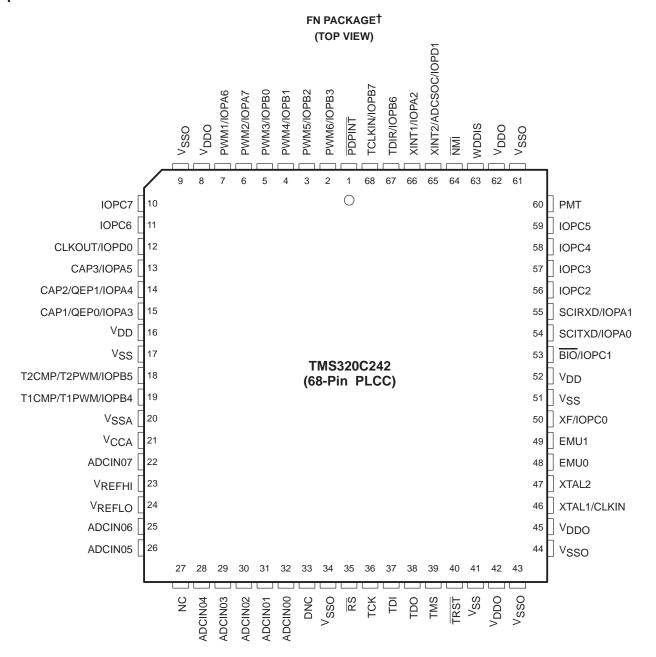

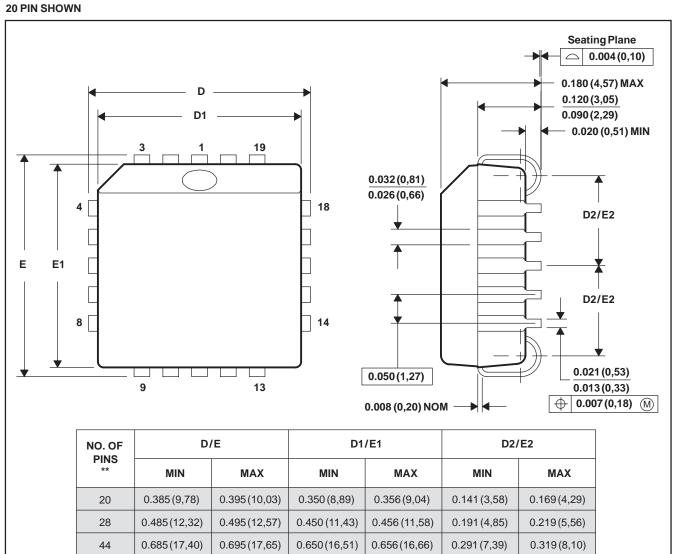

- 68-Pin PLCC FN Package

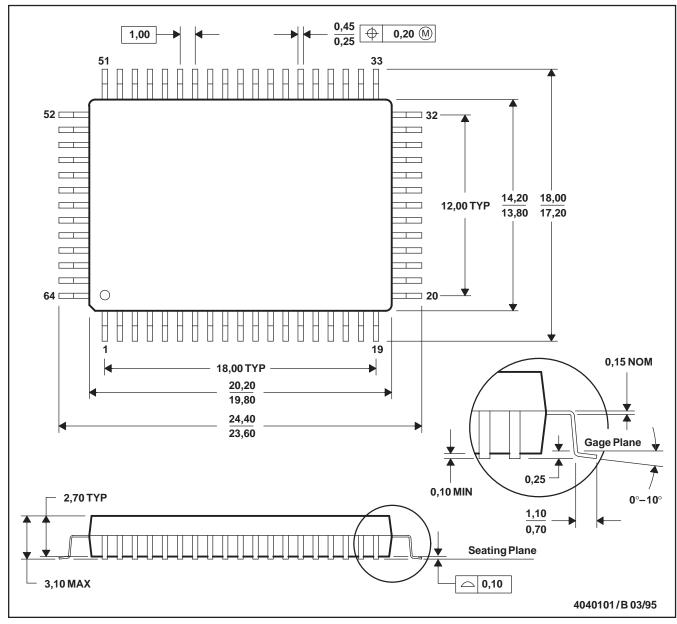

- 64-Pin QFP PG Package

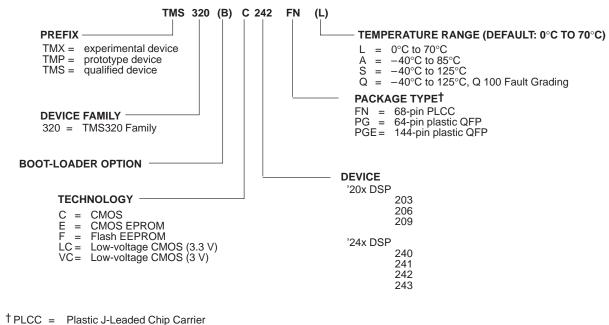

## description

The TMS320C242 device is a member of the '24x family of digital signal processor (DSP) controllers based on the TMS320C2xx generation of 16-bit fixed-point DSPs. The TMS320F241 device is fully compatible with the 'C242 to allow emulation during prototype development. (These two devices share similar core and peripherals.) This new family is optimized for digital motor/motion control applications. The DSP controllers combine the enhanced TMS320 architectural design of the 'C2xx core CPU for low-cost, high-performance processing capabilities and several advanced peripherals optimized for motor/motion control applications. These peripherals include the event manager module, which provides general-purpose timers and PWM registers to generate PWM outputs, and a single,10-bit analog-to-digital converter (ADC), which can perform conversion within 1 µs.

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

TI and XDS510 are trademarks of Texas Instruments Incorporated.

| Table of Co                                     | ntents                                               |

|-------------------------------------------------|------------------------------------------------------|

| Description                                     | Scan-Based Emulation 40                              |

| Device Features                                 | Development Support                                  |

| FN Package, 68-Pin PLCC, 'C242 4                | Nomenclature 42                                      |

| PG Package, 64-Pin QFP, '242 5                  | Documentation Support                                |

| Terminal Functions - 'C242 PG and FN Packages 6 | Absolute Maximum Ratings 44                          |

| Functional Block Diagram 9                      | Recommended Operating Conditions                     |

| Architectural Overview                          | Electrical Characteristics                           |

| System-Level Functions                          | Parameter Measurement Information                    |

| Device Memory Map                               | Signal Transition Levels                             |

| Memory Map                                      | Timing Parameter Symbology                           |

| Peripheral Memory Map                           | Clock Characteristics and Timings                    |

| Digital I/O and Shared Pin Functions            | Clock Options                                        |

| Digital I/O Control Registers                   | Ext Reference Crystal/Clock w/PLL Circuit Enabled 48 |

| Device Reset and Interrupts                     | Low-Power Mode Timings                               |

| Clock Generation                                | RS Timings                                           |

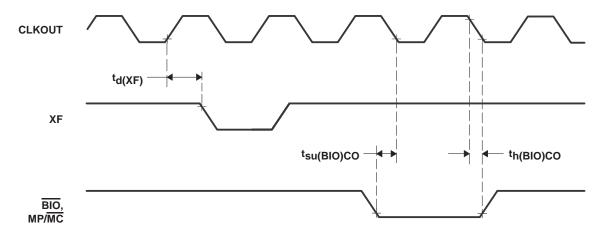

| Low-Power Modes                                 | XF, BIO, and MP/MC Timings 51                        |

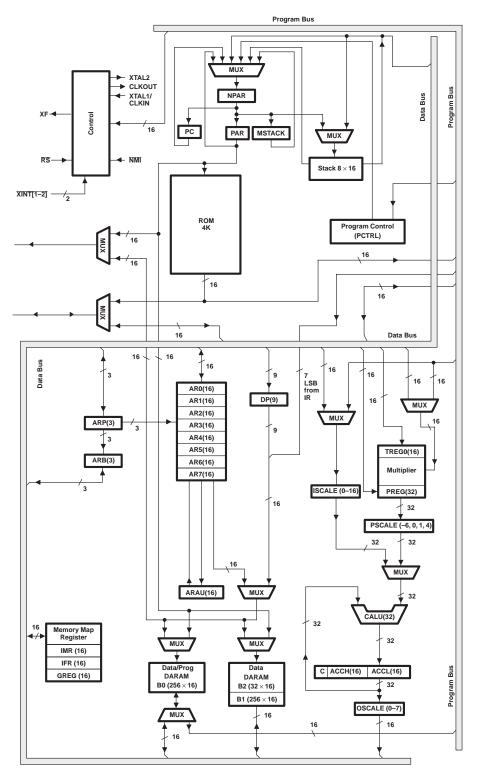

| Functional Block Diagram of the '24x DSP CPU 26 | Timing Event Manager Interface                       |

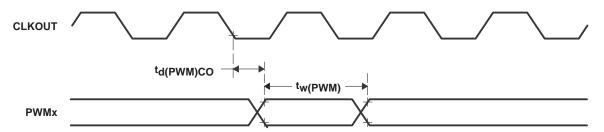

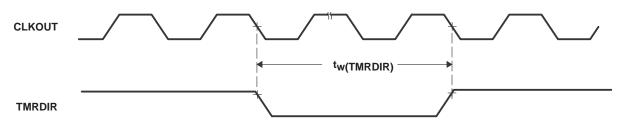

| '24x Legend for the Internal Hardware           | PWM Timings 52                                       |

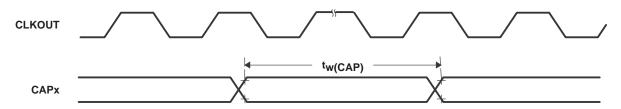

| 'C242 DSP Core CPU                              | Capture and QEP Timings 53                           |

| Internal Memory                                 | Interrupt Timings                                    |

| Peripherals                                     | General-Purpose Input/Output Timings                 |

| Event-Manager (EV2) Module                      | 10-Bit Dual Analog-to-Digital Converter (ADC)        |

| Analog-to-Digital Converter (ADC) Module        | ADC Operating Frequency                              |

| A/D Overview                                    | ADC Input Pin Circuit                                |

| Serial Communications Interface (SCI) Module 36 | Internal ADC Module Timings                          |

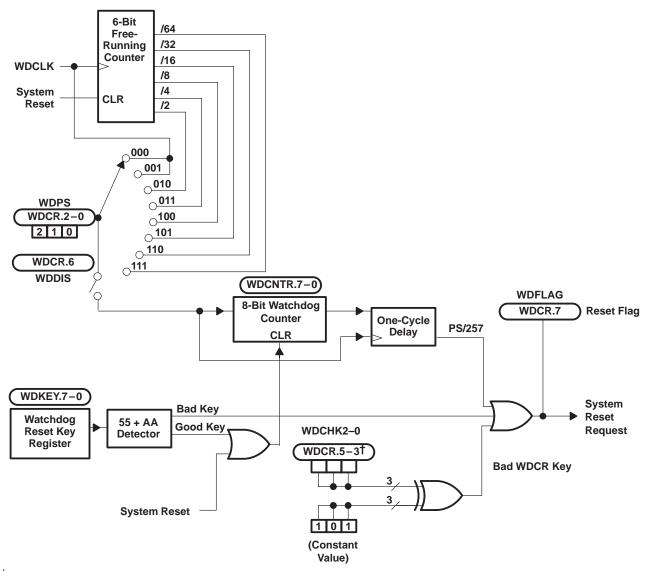

| Watchdog (WD) Timer Module                      | Mechanical Data                                      |

|                                                 |                                                      |

### device features

Table 1 and Table 2 provide a comparison of the features of the 'C242 to the 'F241. See the functional block diagram for the 'C242 peripherals and memory.

Table 1. Hardware Features of the TMS320x24x DSP Controllers

|                       | ON-CHIP MEMORY                              | (WORDS)                         |                                 |               |              |  |

|-----------------------|---------------------------------------------|---------------------------------|---------------------------------|---------------|--------------|--|

|                       | RAM                                         |                                 | EVTERNAL                        | POWER         | CYCLE        |  |

| TMS320x24x<br>DEVICES | DATA SPACE                                  | CONFIGURABLE<br>DATA/PROG SPACE | EXTERNAL<br>MEMORY<br>INTERFACE | SUPPLY<br>(V) | TIME<br>(ns) |  |

|                       | (B1 RAM - 256 WORDS)<br>(B2 RAM - 32 WORDS) | ' I (B) RAM) I                  |                                 |               |              |  |

| TMS320C242            | 000                                         | 050                             |                                 | _             | 50           |  |

| TMS320F241            | 288                                         | 256                             | _                               | 5             | 50           |  |

Table 2. Device Specifications of the TMS320x24x DSP Controllers

|                       | ON-CHIP MEM | ORY (WORDS)     |                 |           |       |      |                              |

|-----------------------|-------------|-----------------|-----------------|-----------|-------|------|------------------------------|

| TMS320x24x<br>DEVICES | ROM         | FLASH<br>EEPROM | ADC<br>CHANNELS | PERIPHI   | ERALS | GPIO | PACKAGE<br>TYPE<br>PIN COUNT |

|                       | PROG        | PROG            |                 | CAN       | SPI   |      | 1 114 000141                 |

| TMS320C242            | 4K          | -               |                 | -         | -     | 00   | FN 68-PLCC                   |

| TMS320F241            | _           | 8K              | 8               | $\sqrt{}$ | V     | 26   | PG 64-PQFP                   |

## pinouts

†NC = No connection, DNC = Do not connect

## pinouts (continued)

#### PG PACKAGET (TOP VIEW) SCITXD/IOPA0 BIO/IOPC1 SCIRXD/IOPA1 XTAL1/CLKIN VDD VSS XF/IOPC0 IOPC4 10PC3 IOPC2 XTAL2 V<sub>DDO</sub> IOPC5 EM<sub>U0</sub> EMU1 51 50 49 48 47 46 45 44 43 42 41 40 39 38 37 36 35 34 33 **WDDIS** TRST 32 NMI 53 31 **TMS** XINT2/ADCSOC/IOPD1 54 30 TDO XINT1/IOPA2 55 29 TDI TDIR/IOPB6 56 28 TCK TCLKIN/IOPB7 TMS320C242 27 57 RS **PDPINT** (64-Pin QFP) 58 26 $^{\rm V_{\rm SSO}}_{\rm DNC}$ PWM6/IOPB3 59 25 PWM5/IOPB2 60 24 ADCIN00 PWM4/IOPB1 61 23 ADCIN01 PWM3/IOPB0 62 22 ADCIN02 PWM2/IOPA7 63 21 ADCIN03 PWM1/IOPA6 64 20 [ ADCIN04 9 10 11 12 13 14 15 16 17 18 19 VREFHI VREFLO ADCIN06 ADCIN05 Vsso IOPC7 10PC6 Vpp VssA VCCA CLKOUT/IOPD0 CAP3/IOPA5 CAP2/QEP1/IOPA4 CAP1/QEP0/IOPA3 T2CMP/T2PWM/IOPB5 T1CMP/T1PWM/IOPB4 ADCIN07

† NC = No connection, DNC = Do not connect

## Terminal Functions - 'C242 PG and FN Packages

| NAME                                     | 64-PIN<br>QFP<br>NO. | 68-PIN<br>PLCC<br>NO. | TYPET | RESET<br>STATE‡ | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                    |  |  |  |  |

|------------------------------------------|----------------------|-----------------------|-------|-----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

|                                          |                      |                       | INT   | ERFACE C        | ONTROL SIGNALS                                                                                                                                                                                                                                                                                                                                                                                 |  |  |  |  |

| WDDIS                                    | 52                   | 63                    | I     | I               | Watchdog disable. Note that on ROM devices, only the WDDIS function is valid. If the input is low, the watchdog timer cannot be disabled in the software. If the input is high, the watchdog timer can be disabled in the software through the WDDIS bit in the WDCR register.                                                                                                                 |  |  |  |  |

| ANALOG-TO-DIGITAL CONVERTER (ADC) INPUTS |                      |                       |       |                 |                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |  |

| ADCIN00                                  | 24                   | 32                    |       |                 |                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |  |

| ADCIN01                                  | 23                   | 31                    |       |                 |                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |  |

| ADCIN02                                  | 22                   | 30                    |       |                 |                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |  |

| ADCIN03                                  | 21                   | 29                    | ] .   | Ι.              | Analog inputs to the ADC                                                                                                                                                                                                                                                                                                                                                                       |  |  |  |  |

| ADCIN04                                  | 20                   | 28                    | '     | 1               | Analog inputs to the ADC                                                                                                                                                                                                                                                                                                                                                                       |  |  |  |  |

| ADCIN05                                  | 19                   | 26                    |       |                 |                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |  |

| ADCIN06                                  | 18                   | 25                    |       |                 |                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |  |

| ADCIN07                                  | 15                   | 22                    |       |                 |                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |  |

| VCCA                                     | 14                   | 21                    | -     | -               | Analog supply voltage for ADC (5 V). V <sub>CCA</sub> must be isolated from digital supply voltage.                                                                                                                                                                                                                                                                                            |  |  |  |  |

| VSSA                                     | 13                   | 20                    | -     | _               | Analog ground reference for ADC                                                                                                                                                                                                                                                                                                                                                                |  |  |  |  |

| VREFHI                                   | 16                   | 23                    | -     | _               | ADC analog high-voltage reference input                                                                                                                                                                                                                                                                                                                                                        |  |  |  |  |

| VREFLO                                   | 17                   | 24                    | -     | _               | ADC analog low-voltage reference input                                                                                                                                                                                                                                                                                                                                                         |  |  |  |  |

|                                          |                      | •                     | •     | EVENT           | MANAGER                                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |  |

| T1CMP/T1PWM/ <i>IOPB4</i>                | 12                   | 19                    | I/O/Z |                 | Timer 1 compare output/general-purpose bidirectional digital I/O (GPIO).                                                                                                                                                                                                                                                                                                                       |  |  |  |  |

| T2CMP/T2PWM/ <i>IOPB5</i>                | 11                   | 18                    | I/O/Z | 1               | Timer 2 compare output/GPIO                                                                                                                                                                                                                                                                                                                                                                    |  |  |  |  |

| TDIR/ <i>IOPB6</i>                       | 56                   | 67                    | I/O   |                 | Counting direction for GP timer/GPIO. If TDIR=1, upward counting is selected. If TDIR=0, downward counting is selected.                                                                                                                                                                                                                                                                        |  |  |  |  |

| TCLKIN/IOPB7                             | 57                   | 68                    | I/O   | ]               | External clock input for GP timer/GPIO. Note that timer can also use the internal device clock.                                                                                                                                                                                                                                                                                                |  |  |  |  |

| CAP1/QEP0/ <i>IOPA3</i>                  | 8                    | 15                    | I/O   | 1               | Capture input #1/quadrature encoder pulse input #0/GPIO                                                                                                                                                                                                                                                                                                                                        |  |  |  |  |

| CAP2/QEP1/ <i>IOPA4</i>                  | 7                    | 14                    | I/O   | ] ,             | Capture input #2/quadrature encoder pulse input #1/GPIO                                                                                                                                                                                                                                                                                                                                        |  |  |  |  |

| CAP3/ <i>IOPA5</i>                       | 6                    | 13                    | I/O   | ]               | Capture input #3/GPIO                                                                                                                                                                                                                                                                                                                                                                          |  |  |  |  |

| PWM1/ <i>IOPA6</i>                       | 64                   | 7                     | I/O/Z | 1               | Compare/PWM output pin #1 or GPIO                                                                                                                                                                                                                                                                                                                                                              |  |  |  |  |

| PWM2/ <i>IOPA7</i>                       | 63                   | 6                     | I/O/Z | ]               | Compare/PWM output pin #2 or GPIO                                                                                                                                                                                                                                                                                                                                                              |  |  |  |  |

| PWM3/ <i>IOPB0</i>                       | 62                   | 5                     | I/O/Z | 1               | Compare/PWM output pin #3 or GPIO                                                                                                                                                                                                                                                                                                                                                              |  |  |  |  |

| PWM4/ <i>IOPB1</i>                       | 61                   | 4                     | I/O/Z | ]               | Compare/PWM output pin #4 or GPIO                                                                                                                                                                                                                                                                                                                                                              |  |  |  |  |

| PWM5/ <i>IOPB2</i>                       | 60                   | 3                     | I/O/Z | 1               | Compare/PWM output pin #5 or GPIO                                                                                                                                                                                                                                                                                                                                                              |  |  |  |  |

| PWM6/IOPB3                               | 59                   | 2                     | I/O/Z | ]               | Compare/PWM output pin #6 or GPIO                                                                                                                                                                                                                                                                                                                                                              |  |  |  |  |

| PDPINT                                   | 58                   | 1                     | I     | I               | Power drive protection interrupt input. This interrupt, when activated, puts the PWM output pins in the high-impedance state, should motor drive/power converter abnormalities, such as overvoltage or overcurrent, etc., arise. PDPINT is a falling-edge-sensitive interrupt. After the falling edge, this pin must be held low for two clock cycles for the core to recognize the interrupt. |  |  |  |  |

$<sup>^{\</sup>dagger}$ I = input, O = output, Z = high impedance

NOTE: Bold, italicized pin names indicate pin function after reset.

<sup>&</sup>lt;sup>‡</sup> The reset state indicates the state of the pin at reset. If the pin is an input, indicated by an I, its state is determined by user design. If the pin is an output, its level at reset is indicated.

<sup>§</sup> These pins are internally pulled high. However, these pins are not pulled high in the emulation devices ('F243/'F241).

## Terminal Functions - 'C242 PG and FN Packages (Continued)

| NAME                       | 64-PIN<br>QFP<br>NO. | 68-PIN<br>PLCC<br>NO. | TYPET   | RESET<br>STATE‡ | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                 |

|----------------------------|----------------------|-----------------------|---------|-----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                            | •                    |                       | •       | BIT I           | /O PINS                                                                                                                                                                                                                                                                                                                                                                     |

| IOPC2                      | 45                   | 56                    | I/O     |                 | GPIO                                                                                                                                                                                                                                                                                                                                                                        |

| IOPC3                      | 46                   | 57                    | I/O     |                 | GPIO                                                                                                                                                                                                                                                                                                                                                                        |

| IOPC4                      | 47                   | 58                    | I/O     | 1               | GPIO                                                                                                                                                                                                                                                                                                                                                                        |

| IOPC5                      | 48                   | 59                    | I/O     | i i             | GPIO                                                                                                                                                                                                                                                                                                                                                                        |

| IOPC6                      | 4                    | 11                    | I/O     |                 | GPIO                                                                                                                                                                                                                                                                                                                                                                        |

| IOPC7                      | 3                    | 10                    | I/O     |                 | GPIO                                                                                                                                                                                                                                                                                                                                                                        |

|                            | (                    | SERIAL CO             | OMMUNIC | ATIONS IN       | TERFACE (SCI) AND BIT I/O PINS                                                                                                                                                                                                                                                                                                                                              |

| SCITXD/IOPA0               | 43                   | 54                    | I/O     |                 | SCI asynchronous serial port transmit data or GPIO                                                                                                                                                                                                                                                                                                                          |

| SCIRXD/IOPA1               | 44                   | 55                    | I/O     | !               | SCI asynchronous serial port receive data or GPIO                                                                                                                                                                                                                                                                                                                           |

|                            | IN                   | TERRUPT,              | EXTERNA | AL ACCES        | S, AND MISCELLANEOUS SIGNALS                                                                                                                                                                                                                                                                                                                                                |

| RS                         | 27                   | 35                    | I/O     | I               | Device reset. RS causes the 'C242 to terminate execution and sets PC=0. After RS is brought to a high level, execution begins at location zero of program memory. RS affects (sets to zero) various registers and status bits. When the watchdog timer overflows, it initiates a system reset pulse that is reflected on the RS pin. This pulse is eight clock cycles wide. |

| пміŝ                       | 53                   | 64                    | I       | I               | Nonmaskable interrupt. When NMI is activated, the device is interrupted regardless of the state of the INTM bit of the status register. $\overline{\text{NMI}}$ is (falling) edge- and low-level-sensitive. To be recognized by the core, this pin must be kept low for at least one clock cycle after the falling edge.                                                    |

| XINT1/ <i>IOPA2</i>        | 55                   | 66                    | I/O     | I               | External user interrupt 1 or GPIO. Both XINT1 and XINT2 are edge-sensitive. To be recognized by the core, these pins must be kept low/high for at least one clock cycle after the edge. The edge polarity is programmable.                                                                                                                                                  |

| XINT2/ADCSOC/ <i>IOPD1</i> | 54                   | 65                    | I/O     | -               | External user interrupt 2. External "start-of-conversion" input for ADC/GPIO. Both XINT1 and XINT2 are edge-sensitive. To be recognized by the core, these pins must be kept low/high for at least one clock cycle after the edge. The edge polarity is programmable.                                                                                                       |

| XF/IOPC0§                  | 39                   | 50                    | I/O     | 0-1             | External flag output (latched software-programmable signal). XF is a general-purpose output pin. It is set/reset by the SETC XF/CLRC XF instruction. This pin is configured as an external flag output by all device resets. It can be used as a GPIO, if not used as XF.                                                                                                   |

| BIO/IOPC1§                 | 42                   | 53                    | I/O     | I               | Branch control input. BIO is polled by the BCND pma, BIO instruction. If BIO is low, a branch is executed. If BIO is not used, it should be pulled high. This pin is configured as a branch control input by all device resets. It can be used as a GPIO, if not used as a branch control input.                                                                            |

| PMT                        | 49                   | 60                    | I       | I               | Do not connect. Reserved for test.                                                                                                                                                                                                                                                                                                                                          |

|                            |                      |                       |         | CLOCK           | SIGNALS                                                                                                                                                                                                                                                                                                                                                                     |

| XTAL1/CLKIN                | 35                   | 46                    | I       | I               | PLL oscillator input pin. Crystal input to PLL/clock source input to PLL. XTAL1/CLKIN is tied to one side of a reference crystal.                                                                                                                                                                                                                                           |

| XTAL2                      | 36                   | 47                    | 0       | 0               | Crystal output. PLL oscillator output pin. XTAL2 is tied to one side of a reference crystal. This pin goes in the high-impedance state when EMU1/OFF is active low.                                                                                                                                                                                                         |

TI = input, O = output, Z = high impedance

NOTE: Bold, italicized pin names indicate pin function after reset.

<sup>&</sup>lt;sup>‡</sup> The reset state indicates the state of the pin at reset. If the pin is an input, indicated by an I, its state is determined by user design. If the pin is an output, its level at reset is indicated.

<sup>§</sup> These pins are internally pulled high. However, these pins are not pulled high in the emulation devices ('F243/'F241).

## Terminal Functions - 'C242 PG and FN Packages (Continued)

| NAME             | 64-PIN<br>QFP<br>NO. | 68-PIN<br>PLCC<br>NO. | TYPET | RESET<br>STATE‡ | DESCRIPTION                                                                                                                                                                                                                                                       |  |  |  |  |

|------------------|----------------------|-----------------------|-------|-----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

|                  |                      |                       | CL    | OCK SIGN        | ALS (CONTINUED)                                                                                                                                                                                                                                                   |  |  |  |  |

| CLKOUT/IOPD0     | 5                    | 12                    | I/O   | 0               | Clock output. This pin outputs the CPU clock (CLKOUT) only. This pin can be used as a GPIO, if it is not used as a clock output pin.                                                                                                                              |  |  |  |  |

| TEST SIGNALS     |                      |                       |       |                 |                                                                                                                                                                                                                                                                   |  |  |  |  |

| TCK              | 28                   | 36                    | I     | I               | JTAG test clock with internal pullup                                                                                                                                                                                                                              |  |  |  |  |

| TDI              | 29                   | 37                    | I     | I               | JTAG test data input (TDI) with internal pullup. TDI is clocked into the selected register (instruction or data) on a rising edge of TCK.                                                                                                                         |  |  |  |  |

| TDO              | 30                   | 38                    | 0     | 0               | JTAG scan out, test data output (TDO). The contents of the selected register (instruction or data) is shifted out of TDO on the falling edge of TCK.                                                                                                              |  |  |  |  |

| TMS              | 31                   | 39                    | I     | I               | JTAG test-mode select (TMS) with internal pullup. This serial control input is clocked into the TAP controller on the rising edge of TCK.                                                                                                                         |  |  |  |  |

| TRST             | 32                   | 40                    | I     | I               | JTAG test reset with internal pulldown. TRST, when driven high, gives the scan system control of the operations of the device. If this signal is not connected or driven low, the device operates in its functional mode, and the test reset signals are ignored. |  |  |  |  |

| EMU0             | 37                   | 48                    | I/O   | I               | Emulator I/O pin 0 with internal pullup. When TRST is driven high, this pin is used as an interrupt to or from the emulator system and is defined as input/output through the JTAG scan.                                                                          |  |  |  |  |

| EMU1             | 38                   | 49                    | I/O   | I               | Emulator I/O pin 1 with internal pullup. When TRST is driven high, this pin is used as an interrupt to or from the emulator system and is defined as input/output through JTAG scan.                                                                              |  |  |  |  |

|                  |                      |                       |       | SUPPL           | Y SIGNALS                                                                                                                                                                                                                                                         |  |  |  |  |

| V                | 9                    | 16                    | _     | _               | Digital logic supply voltage (F.V)                                                                                                                                                                                                                                |  |  |  |  |

| $V_{DD}$         | 41                   | 52                    | _     | _               | Digital logic supply voltage (5 V)                                                                                                                                                                                                                                |  |  |  |  |

|                  | _                    | 42                    | _     | _               |                                                                                                                                                                                                                                                                   |  |  |  |  |

| V <sub>DDO</sub> | 1                    | 8                     | _     | -               | Digital logic and buffer supply voltage (5 V)                                                                                                                                                                                                                     |  |  |  |  |

| <b>√</b> 000     | 34                   | 45                    | _     | -               | Digital logic and buller supply voltage (5 v)                                                                                                                                                                                                                     |  |  |  |  |

|                  | 51                   | 62                    | _     | -               |                                                                                                                                                                                                                                                                   |  |  |  |  |

|                  | _                    | 41                    | _     | _               |                                                                                                                                                                                                                                                                   |  |  |  |  |

| V <sub>SS</sub>  | 10                   | 17                    | _     | _               | Digital logic ground reference                                                                                                                                                                                                                                    |  |  |  |  |

|                  | 40                   | 51                    | _     | _               |                                                                                                                                                                                                                                                                   |  |  |  |  |

|                  |                      | 43                    | _     | _               |                                                                                                                                                                                                                                                                   |  |  |  |  |

|                  | 2                    | 9                     | _     | _               |                                                                                                                                                                                                                                                                   |  |  |  |  |

| VSSO             | 26                   | 34                    | _     | -               | Digital logic and buffer ground reference                                                                                                                                                                                                                         |  |  |  |  |

|                  | 33                   | 44                    | _     | -               |                                                                                                                                                                                                                                                                   |  |  |  |  |

|                  | 50                   | 61                    | _     | _               |                                                                                                                                                                                                                                                                   |  |  |  |  |

|                  |                      |                       |       | NO C            | CONNECT                                                                                                                                                                                                                                                           |  |  |  |  |

| NC               | -                    | 27                    |       |                 | No internal connection made to this pin                                                                                                                                                                                                                           |  |  |  |  |

| DNC              | 25                   | 33                    |       |                 | Do not connect. Reserved for test.                                                                                                                                                                                                                                |  |  |  |  |

$<sup>\</sup>dagger I = input, O = output, Z = high impedance$

NOTE: Bold, italicized pin names indicate pin function after reset.

<sup>‡</sup> The reset state indicates the state of the pin at reset. If the pin is an input, indicated by an I, its state is determined by user design. If the pin is an output, its level at reset is indicated.

<sup>§</sup> These pins are internally pulled high. However, these pins are not pulled high in the emulation devices ('F243/'F241).

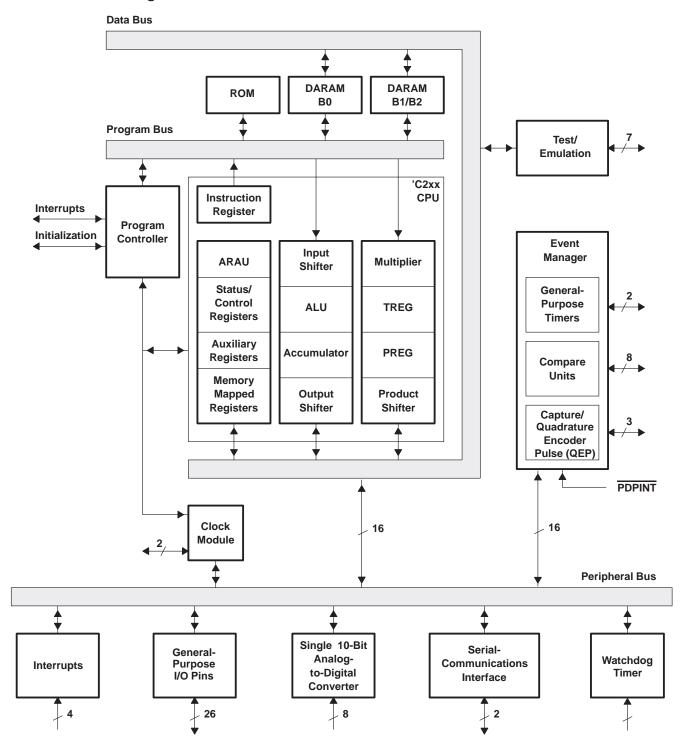

## functional block diagram of the '24x DSP controller

#### architectural overview

The functional block diagram provides a high-level description of each component in the 'C242 DSP controllers. The TMS320x24x devices are composed of three main functional units: a 'C2xx DSP core, internal memory, and peripherals. In addition to these three functional units, there are several system-level features of the 'C242 that are distributed. These system features include the memory map, device reset, interrupts, digital input/output (I/O), clock generation, and low-power operation.

### system-level functions

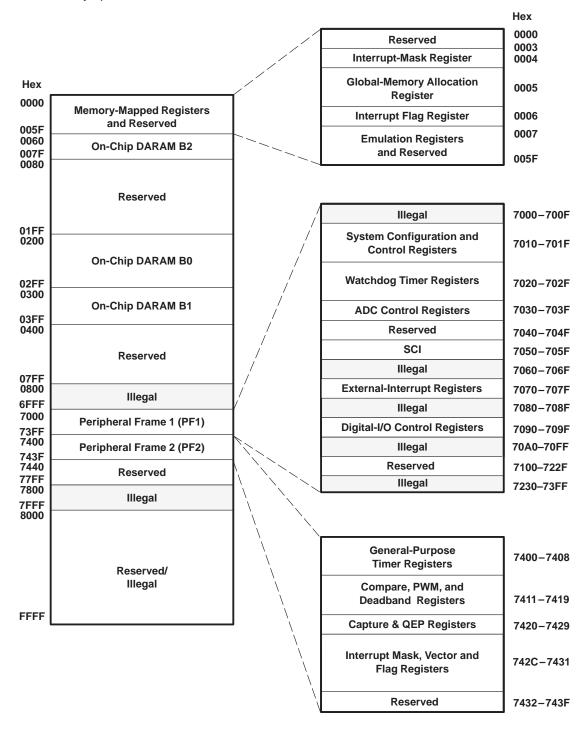

#### device memory map

The 'C242 device implements three separate address spaces for program memory, data memory, and I/O space. On the 'C242, the first 96 (0–5Fh) data memory locations are either allocated for memory-mapped registers or reserved. This memory-mapped register space contains various control and status registers, including those for the CPU.

All the on-chip peripherals of the 'C242 devices are mapped into data memory space. Access to these registers is made by the CPU instructions addressing their data memory locations. Figure 1 shows the 'C242 memory map.

### memory map

| Hex          | Program                                                                                                               | Hex                          | Data                                                                                   |

|--------------|-----------------------------------------------------------------------------------------------------------------------|------------------------------|----------------------------------------------------------------------------------------|

| 0000<br>003F | Interrupt Vectors                                                                                                     | 0000<br>005F                 | Memory-Mapped<br>Registers/Reserved<br>Addresses                                       |

| 0040         | User Code in ROM                                                                                                      | 0060<br>007F                 | On-Chip<br>DARAM B2                                                                    |

| 0FBF<br>0FC0 | Reserved                                                                                                              | 007F<br>0080<br>01FF         | Reserved                                                                               |

| 0FFF<br>1000 | 15555555555555555555555555555555555555                                                                                | 0200                         | On-Chip DARAM<br>(B0) <sup>‡</sup> (CNF = 0)<br>Reserved (CNF = 1)                     |

|              | 64444444444444444444444444444444444444                                                                                | 02FF<br>0300<br>03FF         | On-Chip<br>DARAM (B1)§                                                                 |

|              | 1868489686968868686868<br>186848686968868686<br>1868486868686868686<br>186848686868686868686<br>186848686868868868868 | 0400                         | illegal                                                                                |

|              | Reserved                                                                                                              | 6FFF<br>7000                 | Peripheral Memory-<br>Mapped Registers<br>(System,WD, ADC,<br>SCI, I/O,<br>Interrupts) |

|              |                                                                                                                       | 73FF<br>7400<br>743F         | Peripheral Memory-Mapped Registers (Event Manager)                                     |

|              | :                                                                                                                     | 7440                         | Illegal                                                                                |

|              | # # # # # # # # # # # # # # # # # # #                                                                                 | 77FF<br>7800<br>7FFF<br>8000 | Illegal                                                                                |

| FDFF<br>FE00 | Reserved <sup>†</sup>                                                                                                 | 0000                         | \$5\$5\$\$\$\$\$\$\$\$\$\$\$\$\$\$\$\$\$\$\$\$\$\$\$\$\$\$\$\$\$\$\$\$\$\$             |

| FEFF<br>FF00 | On-Chip DARAM<br>B0 <sup>†</sup> (CNF = 1)                                                                            |                              | Illegal                                                                                |

| FFFF         | Reserved (CNF = 0)                                                                                                    | FFFF                         | 57575757575757575757575757575757575757                                                 |

|              | On-Chip ROM                                                                                                           | <b>Л</b> , (4K)              |                                                                                        |

<sup>†</sup> When CNF = 1, addresses FE00h–FEFFh and FF00h–FFFFh are mapped to the same physical block (B0) in program-memory space. For example, a write to FE00h will have the same effect as a write to FF00h. For simplicity, addresses FE00h–FEFFh are referred to as reserved when CNF = 1.

Figure 1. TMS320C242 Memory Map

When CNF = 0, addresses 0100h–01FFh and 0200h–02FFh are mapped to the same physical block (B0) in data-memory space. For example, a write to 0100h will have the same effect as a write to 0200h. For simplicity, addresses 0100h–01FFh are referred to as reserved.

<sup>§</sup> Addresses 0300h–03FFh and 0400h–04FFh are mapped to the same physical block (B1) in data-memory space. For example, a write to 0400h has the same effect as a write to 0300h. For simplicity, addresses 0400h–04FFh are referred to as illegal.

NOTE A: There is no external memory space for program, data, global data, or I/O in the 'C242. The GREG register is reserved in the 'C242.

#### peripheral memory map

The system and peripheral control register frame contains all the data, status, and control bits to operate the system and peripheral modules on the device (excluding the event manager). The register frame is mapped in the data memory space.

Figure 2. Peripheral Memory Map for 'C242

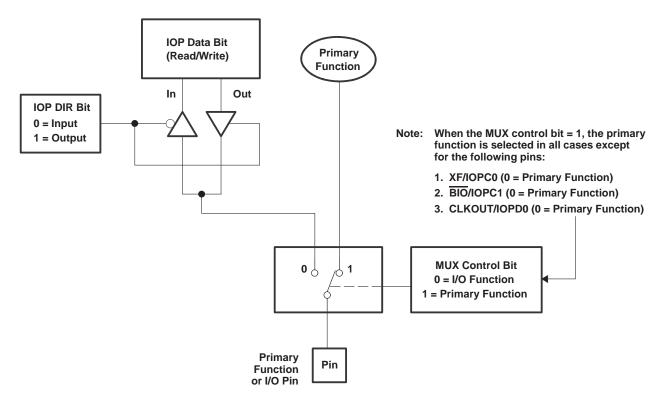

## digital I/O and shared pin functions

The 'C242 has a total of 26 general-purpose, bidirectional, digital I/O (GPIO) pins –most of which are shared between primary functions and I/O. Twenty (20) I/O pins of the 'C242 are shared with other functions. The digital I/O ports module provides a flexible method for controlling both dedicated I/O and shared pin functions. All I/O and shared pin functions are controlled using eight 16-bit registers. These registers are divided into two types:

- Output Control Registers used to control the multiplexer selection that chooses between the primary function of a pin or the general-purpose I/O function.

- Data and Control Registers used to control the data and data direction of bidirectional I/O pins.

### description of shared I/O pins

The control structure for shared I/O pins is shown in Figure 3, where each pin has three bits that define its operation:

- Mux control bit this bit selects between the primary function (1) and I/O function (0) of the pin.

- I/O direction bit if the I/O function is selected for the pin (mux control bit is set to 0), this bit determines whether the pin is an input (0) or an output (1).

- I/O data bit if the I/O function is selected for the pin (mux control bit is set to 0) and the direction selected is an input, data is read from this bit; if the direction selected is an output, data is written to this bit.

The mux control bit, I/O direction bit, and I/O data bit are in the I/O control registers.

Figure 3. Shared Pin Configuration

A summary of shared pin configurations and associated bits is shown in Table 3.

## description of shared I/O pins (continued)

**Table 3. Shared Pin Configurations**

| PIN            | PIN NO. MUX CONTROL |                          | PIN FUNCTION | SELECTED     | I/O PORT DA | ATA AND DIRECT   | ion†            |

|----------------|---------------------|--------------------------|--------------|--------------|-------------|------------------|-----------------|

| 68-PIN<br>PLCC | 64-PIN<br>QFP       | REGISTER<br>(name.bit #) | (OCRx.n = 1) | (OCRx.n = 0) | REGISTER    | DATA BIT<br>NO.‡ | DIR BIT<br>NO.§ |

|                |                     |                          |              |              | PORT A      |                  |                 |

| 54             | 43                  | OCRA.0                   | SCITXD       | IOPA0        | PADATDIR    | 0                | 8               |

| 55             | 44                  | OCRA.1                   | SCIRXD       | IOPA1        | PADATDIR    | 1                | 9               |

| 66             | 55                  | OCRA.2                   | XINT1        | IOPA2        | PADATDIR    | 2                | 10              |

| 15             | 8                   | OCRA.3                   | CAP1/QEP0    | IOPA3        | PADATDIR    | 3                | 11              |

| 14             | 7                   | OCRA.4                   | CAP2/QEP1    | IOPA4        | PADATDIR    | 4                | 12              |

| 13             | 6                   | OCRA.5                   | CAP3         | IOPA5        | PADATDIR    | 5                | 13              |

| 7              | 64                  | OCRA.6                   | PWM1         | IOPA6        | PADATDIR    | 6                | 14              |

| 6              | 63                  | OCRA.7                   | PWM2         | IOPA7        | PADATDIR    | 7                | 15              |

|                |                     |                          |              |              | PORT B      |                  |                 |

| 5              | 62                  | OCRA.8                   | PWM3         | IOPB0        | PBDATDIR    | 0                | 8               |

| 4              | 61                  | OCRA.9                   | PWM4         | IOPB1        | PBDATDIR    | 1                | 9               |

| 3              | 60                  | OCRA.10                  | PWM5         | IOPB2        | PBDATDIR    | 2                | 10              |

| 2              | 59                  | OCRA.11                  | PWM6         | IOPB3        | PBDATDIR    | 3                | 11              |

| 19             | 12                  | OCRA.12                  | T1PWM/T1CMP  | IOPB4        | PBDATDIR    | 4                | 12              |

| 18             | 11                  | OCRA.13                  | T2PWM/T2CMP  | IOPB5        | PBDATDIR    | 5                | 13              |

| 67             | 56                  | OCRA.14                  | TDIR         | IOPB6        | PBDATDIR    | 6                | 14              |

| 68             | 57                  | OCRA.15                  | TCLKIN       | IOPB7        | PBDATDIR    | 7                | 15              |

|                |                     |                          |              |              | PORT C      |                  |                 |

| 50             | 39                  | OCRB.0                   | IOPC0        | XF           | PCDATDIR    | 0                | 8               |

| 53             | 42                  | OCRB.1                   | IOPC1        | BIO          | PCDATDIR    | 1                | 9               |

| 56¶            | 45¶                 | OCRB.2                   | -            | IOPC2        | PCDATDIR    | 2                | 10              |

| 57¶            | 46¶                 | OCRB.3                   | -            | IOPC3        | PCDATDIR    | 3                | 11              |

| 58¶            | 47¶                 | OCRB.4                   | _            | IOPC4        | PCDATDIR    | 4                | 12              |

| 59¶            | 48¶                 | OCRB.5                   | -            | IOPC5        | PCDATDIR    | 5                | 13              |

| 11¶            | 4¶                  | OCRB.6                   | _            | IOPC6        | PCDATDIR    | 6                | 14              |

| 10¶            | 3¶                  | OCRB.7                   | _            | IOPC7        | PCDATDIR    | 7                | 15              |

|                |                     |                          |              |              | PORT D      |                  |                 |

| 12             | 5                   | OCRB.8                   | IOPD0        | CLKOUT       | PDDATDIR    | 0                | 8               |

| 65             | 54                  | OCRB.9                   | XINT2/ADCSOC | IOPD1        | PDDATDIR    | 1                | 9               |

<sup>†</sup> Valid only if the I/O function is selected on the pin

<sup>‡</sup> If the GPIO pin is configured as an output, these bits can be written to. If the pin is configured as an input, these bits are read from.

<sup>§</sup> If the DIR bit is 0, the GPIO pin functions as an input. For a value of 1, the pin is configured as an output.

<sup>¶</sup> Dedicated I/O pins

## digital I/O control registers

Table 4 lists the registers available in the digital I/O module. As with other 'C242 peripherals, the registers are memory-mapped to the data space.

**ADDRESS REGISTER** NAME I/O mux control register A 7090h **OCRA** 7092h OCRB I/O mux control register B 7098h **PADATDIR** I/O port A data and direction register 709Ah **PBDATDIR** I/O port B data and direction register 709Ch **PCDATDIR** I/O port C data and direction register **PDDATDIR** 709Eh I/O port D data and direction register

Table 4. Addresses of Digital I/O Control Registers

## device reset and interrupts

The TMS320x24x software-programmable interrupt structure supports flexible on-chip and external interrupt configurations to meet real-time interrupt-driven application requirements. The 'C242 recognizes three types of interrupt sources:

- Reset (hardware- or software-initiated) is unarbitrated by the CPU and takes immediate priority over any

other executing functions. All maskable interrupts are disabled until the reset service routine enables them.

- The 'C242 device has two sources of reset: an external reset pin and a watchdog timer timeout (reset).

- Hardware-generated interrupts are requested by external pins or by on-chip peripherals. There are two

types:

- External interrupts are generated by one of four external pins corresponding to the interrupts XINT1, XINT2, PDPINT, and NMI. The first three can be masked both by dedicated enable bits and by the CPU's interrupt mask register (IMR), which can mask each maskable interrupt line at the DSP core. NMI, which is not maskable, takes priority over peripheral interrupts and software-generated interrupts. It can be locked out only by an already executing NMI or a reset.

- Peripheral interrupts are initiated internally by these on-chip peripheral modules: the event manager, SCI, WD, and ADC. They can be masked both by enable bits for each event in each peripheral and by the CPU's IMR, which can mask each maskable interrupt line at the DSP core.

- Software-generated interrupts for the 'C242 include:

- The INTR instruction. This instruction allows initialization of any 'C242 interrupt with software. Its

operand indicates the interrupt vector location to which the CPU branches. This instruction globally

disables maskable interrupts (sets the INTM bit to 1).

- The NMI instruction. This instruction forces a branch to interrupt vector location 24h, the same location used for the nonmaskable hardware interrupt NMI. NMI can be initiated by driving the NMI pin low or by executing an NMI instruction. This instruction globally disables maskable interrupts.

- The TRAP instruction. This instruction forces the CPU to branch to interrupt vector location 22h. The

TRAP instruction does not disable maskable interrupts (INTM is not set to 1); therefore, when the CPU

branches to the interrupt service routine, that routine can be interrupted by the maskable hardware

interrupts.

- An emulator trap. This interrupt can be generated with either an INTR instruction or a TRAP instruction.

#### reset

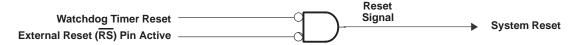

The reset operation ensures an orderly startup sequence for the device. There are two possible causes of a reset, as shown in Figure 4.

Figure 4. Reset Signals

The two possible reset signals are generated as follows:

- Watchdog timer reset. A watchdog-timer-generated reset occurs if the watchdog timer overflows or an

improper value is written to either the watchdog key register or the watchdog control register. (Note that

when the device is powered on, the watchdog timer is automatically active.) The watchdog timer reset is

reflected on the external RS pin also.

- Reset pin active. To generate an external reset pulse on the RS pin, a low-level pulse duration of at least one CPUCLK cycle is necessary to ensure that the device recognizes the reset signal.

Once watchdog reset is activated, the external  $\overline{RS}$  pin is driven (active) low for a minimum of eight CPUCLK cycles. This allows the TMS320x24x device to reset external system components.

The occurrence of a reset condition causes the TMS320x24x to terminate program execution and affects various registers and status bits. During a reset, RAM contents remain unchanged, and all control bits that are affected by a reset are initialized to their reset state.

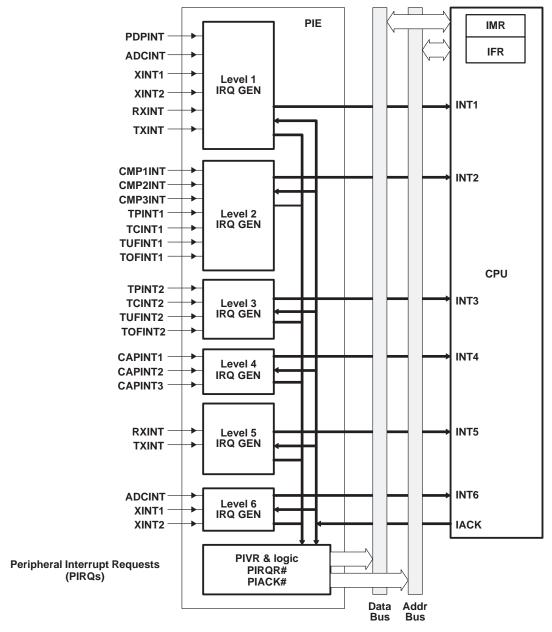

### hardware-generated interrupts

The '24x CPU supports one nonmaskable interrupt (NMI) and six maskable prioritized interrupt requests. The '24x devices have many peripherals, and each peripheral is capable of generating one or more interrupts in response to many events. The '24x CPU does not have sufficient interrupt requests to handle all these peripheral interrupt requests; therefore, a centralized interrupt controller is provided to arbitrate the interrupt requests from all the different sources. Throughout this section, refer to Figure 5.

### hardware-generated interrupts (continued)

Figure 5. Peripheral Interrupt Expansion Block Diagram

## interrupt hierarchy

The number of interrupt requests available is expanded by having two levels of hierarchy in the interrupt request system. There are two levels of hierarchy in both the interrupt request/acknowledge hardware and in the interrupt service routine software.

## interrupt request structure

- 1. At the lower level of the hierarchy, the peripheral interrupt requests (PIRQs) from several peripherals to the interrupt controller are ORed together to generate a request to the CPU. There is an interrupt flag bit and an interrupt enable bit located in the peripheral for each event that can cause a peripheral interrupt request. There is also one PIRQ for each event. If an interrupt-causing event occurs in a peripheral, and the corresponding interrupt enable bit is set, the interrupt request from the peripheral to the interrupt controller is asserted. This interrupt request simply reflects the status of the peripheral's interrupt flag gated with the interrupt enable bit. When the interrupt flag is cleared, the interrupt request is cleared. Some peripherals have the capability to make either a high-priority or a low-priority interrupt request. If a peripheral has this capability, the value of its interrupt priority bit is transmitted to the interrupt controller. The interrupt request continues to be asserted until it is either automatically cleared by an interrupt acknowledge or cleared by software.

- 2. At the upper level of the hierarchy, the ORed PIRQs generate interrupt (INT) requests to the CPU. The request to the '24x CPU is a low-going pulse of 2 CPU clock cycles. The Peripheral Interrupt Expansion (PIE) controller generates an INT pulse when any of the PIRQs controlling that INT go active. If any of the PIRQs capable of asserting that CPU interrupt request are still active in the cycle following an interrupt acknowledge for that INT, another INT pulse is generated in the PIE. Each INT request is followed by an interrupt acknowledge from the CPU, which helps to clear the interrupt-causing flag in the PIE. The interrupt controller defines which CPU interrupt requests get asserted by which peripheral interrupt requests, and the relative priority of each peripheral interrupt request. Thus, priority is determined by the interrupt controller and is not part of any of the peripherals. Table 5 lists interrupt source priority and vectors.

## interrupt request structure (continued)

Table 5. 'C242 Interrupt Source Priority and Vectors

| INTERRUPT<br>NAME | OVERALL<br>PRIORITY | CPU<br>INTERRUPT<br>AND<br>VECTOR<br>ADDRESS | BIT<br>POSITION IN<br>PIRQRX AND<br>PIACKRX | PERIPHERAL<br>INTERRUPT<br>VECTOR<br>(PIV) | MASK-<br>ABLE? | SOURCE<br>PERIPHERAL<br>MODULE | DESCRIPTION                                     |

|-------------------|---------------------|----------------------------------------------|---------------------------------------------|--------------------------------------------|----------------|--------------------------------|-------------------------------------------------|

| Reset             | 1                   | RSN<br>0000h                                 |                                             | N/A                                        | N              | RS pin,<br>Watchdog            | Reset from pin, watchdog timeout                |

| Reserved          | 2                   | _<br>0026h                                   |                                             | N/A                                        | N              | CPU                            | Emulator Trap                                   |

| NMI               | 3                   | NMI<br>0024h                                 |                                             | N/A                                        | N              | Nonmaskable<br>Interrupt       | Nonmaskable interrupt                           |

| PDPINT            | 4                   |                                              | 0.0                                         | 0020h                                      | Υ              | EV                             | Power device protection interrupt pin           |

| ADCINT            | 5                   | ]                                            | 0.1                                         | 0004h                                      | Υ              | ADC                            | ADC interrupt in high-priority mode             |

| XINT1             | 6                   | ]                                            | 0.2                                         | 0001h                                      | Υ              | External<br>Interrupt Logic    | External interrupt pins in high priority        |

| XINT2             | 7                   | INT1                                         | 0.3                                         | 0011h                                      | Υ              | External<br>Interrupt Logic    | External interrupt pins in high priority        |

| Reserved          | 8                   | 0002h                                        |                                             |                                            |                |                                |                                                 |

| RXINT             | 9                   |                                              | 0.5                                         | 0006h                                      | Y              | SCI                            | SCI receiver interrupt in high-priority mode    |

| TXINT             | 10                  |                                              | 0.6                                         | 0007h                                      | Y              | SCI                            | SCI transmitter interrupt in high-priority mode |

| Reserved          | 11                  | 1                                            |                                             |                                            |                |                                |                                                 |

| Reserved          | 12                  | 1                                            |                                             |                                            |                |                                |                                                 |

| CMP1INT           | 13                  |                                              | 0.9                                         | 0021h                                      | Υ              | EV                             | Compare 1 interrupt                             |

| CMP2INT           | 14                  | ]                                            | 0.10                                        | 0022h                                      | Υ              | EV                             | Compare 2 interrupt                             |

| CMP3INT           | 15                  |                                              | 0.11                                        | 0023h                                      | Υ              | EV                             | Compare 3 interrupt                             |

| TPINT1            | 16                  | INT2                                         | 0.12                                        | 0027h                                      | Υ              | EV                             | Timer 1 period interrupt                        |

| TCINT1            | 17                  | 0004h                                        | 0.13                                        | 0028h                                      | Υ              | EV                             | Timer 1 PWM interrupt                           |

| TUFINT1           | 18                  |                                              | 0.14                                        | 0029h                                      | Y              | EV                             | Timer 1 underflow interrupt                     |

| TOFINT1           | 19                  |                                              | 0.15                                        | 002Ah                                      | Υ              | EV                             | Timer 1 overflow interrupt                      |

| TPINT2            | 20                  |                                              | 1.0                                         | 002Bh                                      | Υ              | EV                             | Timer 2 period interrupt                        |

| TCINT2            | 21                  | INT3                                         | 1.1                                         | 002Ch                                      | Υ              | EV                             | Timer 2 PWM interrupt                           |

| TUFINT2           | 22                  | 0006h                                        | 1.2                                         | 002Dh                                      | Υ              | EV                             | Timer 2 underflow interrupt                     |

| TOFINT2           | 23                  |                                              | 1.3                                         | 002Eh                                      | Υ              | EV                             | Timer 2 overflow interrupt                      |

| CAPINT1           | 24                  | 15.17.4                                      | 1.4                                         | 0033h                                      | Υ              | EV                             | Capture 1 interrupt                             |

| CAPINT2           | 25                  | INT4<br>0008h                                | 1.5                                         | 0034h                                      | Υ              | EV                             | Capture 2 interrupt                             |

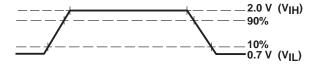

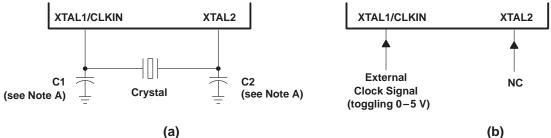

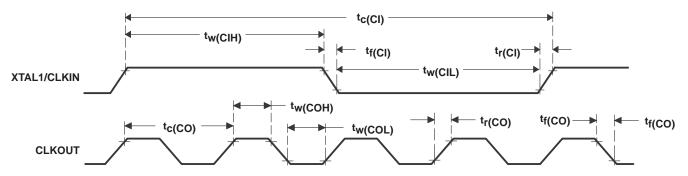

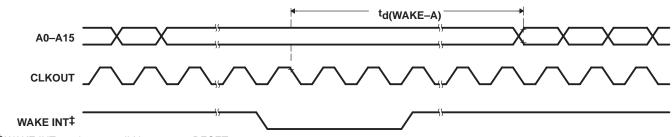

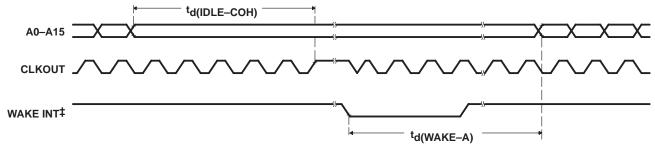

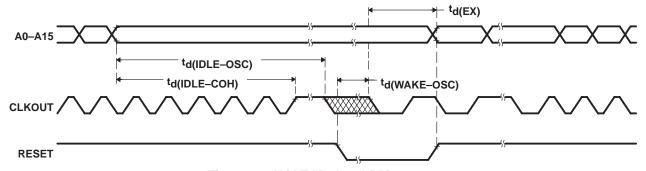

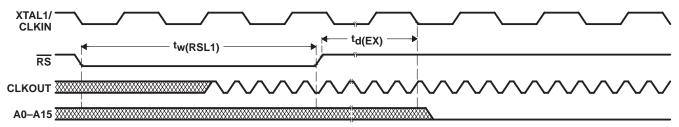

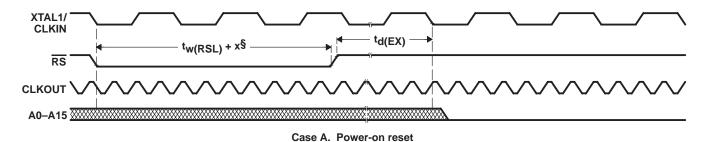

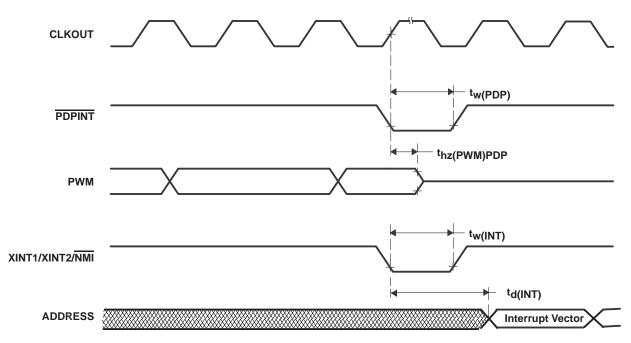

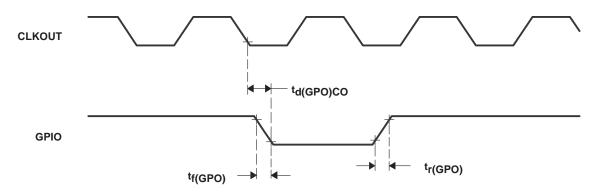

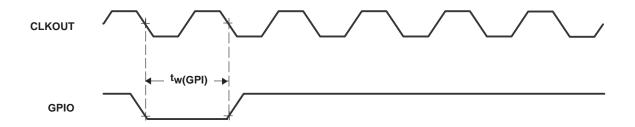

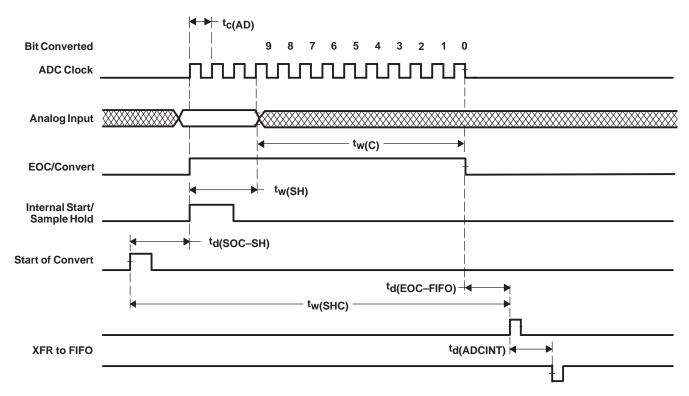

| CAPINT3           | 26                  | 000011                                       | 1.6                                         | 0035h                                      | Υ              | EV                             | Capture 3 interrupt                             |