#### **Features**

- High-density, High-performance Electrically-erasable Complex Programmable Logic Device

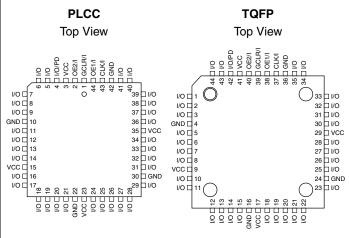

- 44-pin, 32 I/O CPLD

- 7.5 ns Maximum Pin-to-pin Delay

- Registered Operation Up to 125 MHz

- Fully Connected Input and Feedback Logic Array

- Backward Compatibility with ATF1500/L Software and Hardware

- Flexible Logic Macrocell

- D/T/Latch Configurable Flip-flops

- Global and Individual Register Control Signals

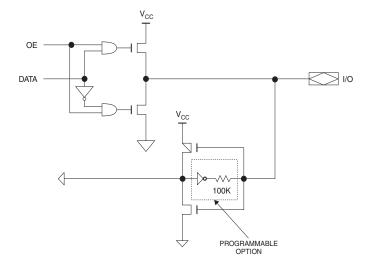

- Global and Individual Output Enable

- Programmable Output Slew Rate

- Advanced Power Management Features

- Automatic 3 mA Standby (ATF1500AL)

- Pin-controlled 10 mA Standby Mode

- Programmable Pin-keeper Inputs and I/Os

- Available in Commercial and Industrial Temperature Ranges

- Available in 44-lead PLCC and TQFP Packages

- Advanced Flash Technology

- 100% Tested

- Completely Reprogrammable

- 100 Program/Erase Cycles

- 20 Year Data Retention

- 2000V ESD Protection

- 200 mA Latch-up Immunity

- Supported by Popular third-arty Tools

- Security Fuse Feature

- Pin-compatible with the Most Commonly Used Devices

- Green (Pb/Halide-fee/RoHS Compliant) Package Options

#### **Description**

The ATF1500A is a high-performance, high-density complex PLD. Built on an advanced Flash technology, it has maximum pin-to-pin delays of 7.5 ns and supports sequential logic operation at speeds up to 125 MHz. With 32 logic macrocells and up to 36 inputs, it easily integrates logic from several TTL, SSI, MSI and classic PLDs. The ATF1500A's global input and feedback architecture simplifies logic placement and eliminates pinout changes due to design changes.

#### **Pin Configurations**

(continued)

| Pin<br>Name | Function                    |

|-------------|-----------------------------|

| CLK         | Clock                       |

| 1           | Logic Inputs                |

| I/O         | Bi-directional<br>Buffers   |

| GCLR        | Register Reset (active low) |

| OE1,<br>OE2 | Output Enable (active low)  |

| VCC         | +5V Supply                  |

| PD          | Power-down (active high)    |

# Highperformance EPLD

# **ATF1500A ATF1500AL**

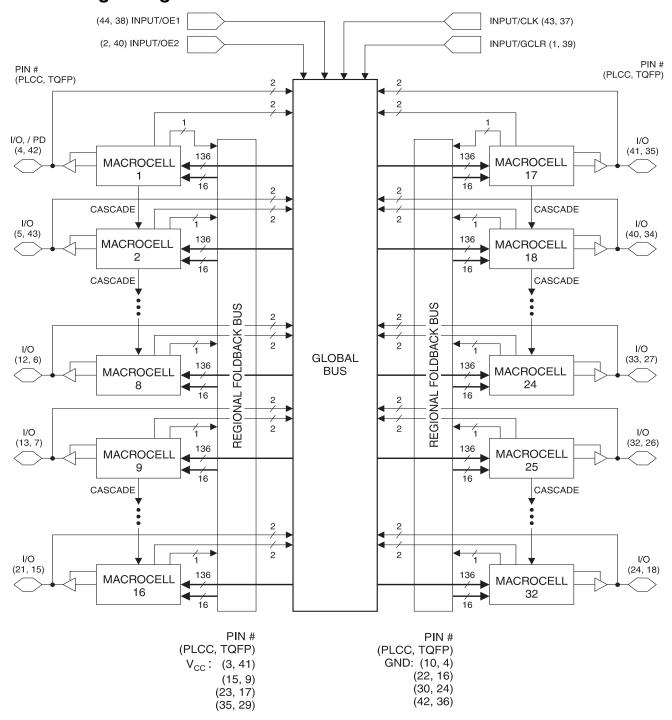

#### Functional Logic Diagram<sup>(1)</sup>

Note: 1. Arrows connecting macrocells indicate direction and groupings of CASIN/CASOUT data flow.

The ATF1500A has 32 bi-directional I/O pins and four dedicated input pins. Each dedicated input pin can also serve as a global control signal: register clock, register reset or output enable. Each of these control signals can be selected for use individually within each macrocell.

Each of the 32 logic macrocells generates a buried feed-back, which goes to the global bus. Each input and I/O pin also feeds into the global bus. Because of this global busing, each of these signals is always available to all 32 macrocells in the device.

Each macrocell also generates a foldback logic term, which goes to a regional bus. All signals within a regional bus are connected to all 16 macrocells within the region.

Cascade logic between macrocells in the ATF1500A allows fast, efficient generation of complex logic functions. The ATF1500A contains four such logic chains, each capable of creating sum term logic with a fan-in of up to 40 product terms.

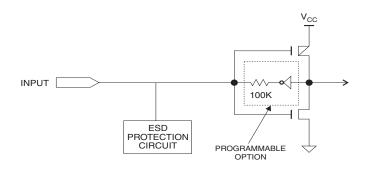

#### Bus-friendly Pin-keeper Input and I/O's

All Input and I/O pins on the ATF1500A have programmable "pin-keeper" circuits. If activated, when any pin is driven high or low and then subsequently left floating, it will stay at that previous high or low level.

This circuitry prevents unused Input and I/O lines from floating to intermediate voltage levels, which causes unnecessary power consumption and system noise. The keeper circuits eliminate the need for external pull-up resistors and eliminate their DC power consumption.

Pin-keeper circuits can be disabled. Programming is controlled in the logic design file. Once the pin-keeper circuits are disabled, normal termination procedures are required for unused inputs and I/Os.

#### **Speed/Power Management**

The ATF1500A has several built-in speed and power management features. The ATF1500A contains circuitry that automatically puts the device into a low-power standby mode when no logic transitions are occurring. This not only reduces power consumption during inactive periods, but also provides proportional power savings for most applications running at system speeds below 10 MHz.

All ATF1500As also have an optional pin-controlled power-down mode. In this mode, current drops to below 10 mA. When the power-down option is selected, the PD pin is used to power-down the part. The power-down option is selected in the design source file. When enabled, the device goes into power-down when the PD pin is high. In the power-down mode, all internal logic signals are latched and held, as are any enabled outputs. All pin transitions are ignored until the PD is brought low. When the power-down feature is enabled, the PD cannot be used as a logic input or output. However, the PD pin's macrocell may still be used to generate buried foldback and cascade logic signals.

Each output also has individual slew rate control. This may be used to reduce system noise by slowing down outputs that do not need to operate at maximum speed. Outputs default to slow switching, and may be specified as fast switching in the design file.

#### **Design Software Support**

ATF1500A designs are supported by several third-party tools. Automated fitters allow logic synthesis using a variety of high-level description languages and formats.

#### **Input Diagram**

#### I/O Diagram

#### **Absolute Maximum Ratings\***

| Temperature Under Bias40°C to +85°C                                                          |

|----------------------------------------------------------------------------------------------|

| Storage Temperature65°C to +150°C                                                            |

| Voltage on Any Pin with Respect to Ground2.0V to +7.0V <sup>(1)</sup>                        |

| Voltage on Input Pins with Respect to Ground During Programming2.0V to +14.0V <sup>(1)</sup> |

| Programming Voltage with Respect to Ground2.0V to +14.0V <sup>(1)</sup>                      |

\*NOTICE:

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

Note:

Minimum voltage is -0.6V DC, which may undershoot to -2.0V for pulses of less than 20 ns. Maximum output pin voltage is  $V_{\rm CC}$  + 0.75V DC, which may overshoot to 5.25V for pulses of less than 20 ns.

#### **DC and AC Operating Conditions**

|                                 | Commercial | Industrial   |

|---------------------------------|------------|--------------|

| Operating Temperature (ambient) | 0°C - 70°C | -40°C - 85°C |

| V <sub>CC</sub> Power Supply    | 5V ± 5%    | 5V ± 10%     |

#### **DC Characteristics**

| Symbol                          | Parameter                                                  | Condition                                                       |                           |      | Min                   | Тур | Max                 | Units |

|---------------------------------|------------------------------------------------------------|-----------------------------------------------------------------|---------------------------|------|-----------------------|-----|---------------------|-------|

| I <sub>IL</sub>                 | Input or I/O<br>Low Leakage Current                        | $0 \le V_{IN} \le V_{IL}$ (N                                    | lax)                      |      |                       |     | -10                 | μΑ    |

| I <sub>IH</sub>                 | Input or I/O<br>High Leakage Current                       | V <sub>IH</sub> , Min ≤ V <sub>IN</sub> ≤                       | ≤ V <sub>CC</sub>         |      |                       |     | 10                  | μΑ    |

|                                 |                                                            |                                                                 | ATF1500A                  | Com. |                       | 70  |                     | mA    |

| ı (1)                           | Power Supply Current,                                      | V <sub>CC</sub> = Max,                                          | AIFISUUA                  | Ind. |                       | 100 |                     | mA    |

| I <sub>CC1</sub> <sup>(1)</sup> | Standby                                                    | $V_{IN} = 0, V_{CC}$                                            | ATE 1 500 A I             | Com. |                       |     | 3                   | mA    |

|                                 |                                                            |                                                                 | ATF1500AL                 | Ind. |                       |     | 5                   | mA    |

| I <sub>CC2</sub>                | Power Supply Current,<br>Pin-Controlled Power<br>Down Mode | $V_{CC} = Max,$ $V_{IN} = 0, V_{CC}$                            |                           |      |                       | 2   | 10                  | mA    |

| I <sub>OS</sub>                 | Output Short Circuit<br>Current                            | V <sub>OUT</sub> = 0.5V                                         |                           |      |                       |     | -130                | mA    |

| V <sub>IL</sub>                 | Input Low Voltage                                          | V <sub>CC</sub> , Min < V <sub>CC</sub> < V <sub>CC</sub> , Max | ;                         |      | -0.5                  |     | 0.8                 | V     |

| V <sub>IH</sub>                 | Input High Voltage                                         |                                                                 |                           |      | 2.0                   |     | V <sub>CC</sub> + 1 | V     |

| V <sub>OL</sub>                 | Output Low Voltage                                         | V <sub>CC</sub> = Min                                           | I <sub>OL</sub> = 12 mA   |      |                       |     | 0.45                | V     |

| M                               | Outrot High Valtage                                        | N/ Min                                                          | $I_{OH} = -4 \text{ mA}$  |      | 2.4                   |     |                     | V     |

| $V_{OH}$                        | Output High Voltage                                        | V <sub>CC</sub> = Min                                           | I <sub>OH</sub> = -0.2 mA |      | V <sub>CC</sub> - 0.2 |     |                     | V     |

Note: 1. All I<sub>CC</sub> parameters measured with outputs open, and a 16-bit loadable, up/down counter programmed into each region.

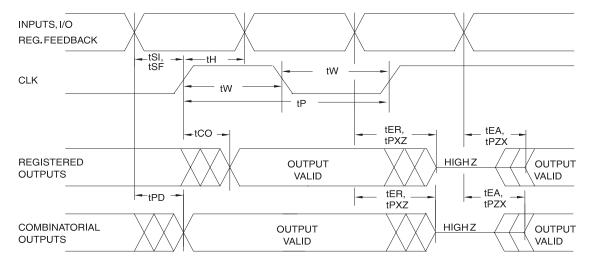

#### **AC Waveforms**

### **Register AC Characteristics, Input Pin Clock**

|                                 |                                                               |     | -7    |     | 10   | -12 |      | -15 |      | -2  | 20  | -25 |     |       |

|---------------------------------|---------------------------------------------------------------|-----|-------|-----|------|-----|------|-----|------|-----|-----|-----|-----|-------|

| Symbol                          | Parameter                                                     | Min | Max   | Min | Max  | Min | Max  | Min | Max  | Min | Max | Min | Max | Units |

| t <sub>COS</sub> <sup>(1)</sup> | Clock to Output                                               |     | 4.5   | 2   | 5    | 2   | 6    | 2   | 8    | 2   | 9   | 2   | 9   | ns    |

| t <sub>CFS</sub>                | Clock to Feedback                                             |     | 2     |     | 2    |     | 2    |     | 2    |     | 2   |     | 2   | ns    |

| t <sub>SIS</sub>                | I, I/O Setup Time                                             |     | 6     |     | 8    |     | 10   |     | 11   |     | 14  |     | 16  | ns    |

| t <sub>SFS</sub>                | Feedback Setup<br>Time                                        |     | 6     |     | 8    |     | 10   |     | 11   |     | 12  |     | 13  | ns    |

| t <sub>HS</sub>                 | Input, I/O, Feedback<br>Hold Time                             | 0   |       | 0   |      | 0   |      | 0   |      | 0   |     | 0   |     | ns    |

| t <sub>PS</sub>                 | Clock Period                                                  | 6   |       | 8   |      | 9   |      | 10  |      | 11  |     | 12  |     | ns    |

| t <sub>WS</sub>                 | Clock Width                                                   | 3   |       | 4   |      | 4.5 |      | 5   |      | 5.5 |     | 6   |     | ns    |

|                                 | External Feedback 1/(t <sub>SIS</sub> + t <sub>COS</sub> )    |     | 95    |     | 76.9 |     | 62.5 |     | 52.6 |     | 43  |     | 40  | MHz   |

| f <sub>MAXS</sub>               | Internal Feedback<br>1/(t <sub>SFS</sub> + t <sub>CFS</sub> ) |     | 125   |     | 100  |     | 83.3 |     | 76.9 |     | 71  |     | 66  | MHz   |

|                                 | No Feedback 1/(t <sub>PS</sub> )                              |     | 166.7 |     | 125  |     | 111  |     | 100  |     | 91  |     | 83  | MHz   |

| t <sub>RPRS</sub>               | Reset Pin Recovery<br>Time                                    | 2   |       | 3   |      | 3   |      | 4   |      | 5   |     | 5   |     | ns    |

| t <sub>RTRS</sub>               | Reset Term<br>Recovery Time                                   | 6   |       | 9   |      | 10  |      | 12  |      | 13  |     | 14  |     | ns    |

Note: 1. For slow slew outputs, add  $t_{\mbox{\footnotesize SSO}}$  .

## **Register AC Characteristics, Product Term Clock**

|                                 |                                                               | ,   | -7    |     | -10  |     | -12  |     | -15  |     | 20   | -25 |      |       |

|---------------------------------|---------------------------------------------------------------|-----|-------|-----|------|-----|------|-----|------|-----|------|-----|------|-------|

| Symbol                          | Parameter                                                     | Min | Max   | Min | Max  | Min | Max  | Min | Max  | Min | Max  | Min | Max  | Units |

| t <sub>COA</sub> <sup>(1)</sup> | Clock to Output                                               |     | 7.5   |     | 10   |     | 12   |     | 15   |     | 18   |     | 20   | ns    |

| t <sub>CFA</sub>                | Clock to Feedback                                             |     | 5     |     | 7    |     | 7    |     | 9    |     | 12   |     | 15   | ns    |

| t <sub>SIA</sub>                | I, I/O Setup Time                                             | 3   |       | 3   |      | 4   |      | 4   |      | 8   |      | 10  |      | ns    |

| t <sub>SFA</sub>                | Feedback Setup<br>Time                                        | 3   |       | 3   |      | 4   |      | 4   |      | 12  |      | 15  |      | ns    |

| t <sub>HA</sub>                 | Input, I/O, Feedback<br>Hold Time                             | 2   |       | 3   |      | 4   |      | 4   |      | 5   |      | 5   |      | ns    |

| t <sub>PA</sub>                 | Clock Period                                                  | 6   |       | 8   |      | 10  |      | 12  |      | 24  |      | 30  |      | ns    |

| t <sub>WA</sub>                 | Clock Width                                                   | 3   |       | 4   |      | 5   |      | 6   |      | 12  |      | 15  |      | ns    |

|                                 | External Feedback<br>1/(t <sub>SIA</sub> + t <sub>COA</sub> ) |     | 95.2  |     | 76.9 |     | 62.5 |     | 52.6 |     | 38   |     | 33.3 | MHz   |

| f <sub>MAXA</sub>               | Internal Feedback<br>1/(t <sub>SFA</sub> + t <sub>CFA</sub> ) |     | 125   |     | 100  |     | 90.9 |     | 76.9 |     | 41.7 |     | 33.3 | MHz   |

|                                 | No Feedback 1/(t <sub>PA</sub> )                              |     | 166.7 |     | 125  |     | 100  |     | 83.3 |     | 41.7 |     | 33.3 | MHz   |

| t <sub>RPRA</sub>               | Reset Pin Recovery<br>Time                                    | 0   |       | 0   |      | 0   |      | 0   |      |     | 0    | 0   |      | ns    |

| t <sub>RTRA</sub>               | Reset Term<br>Recovery Time                                   | 4   |       | 5   |      | 6   |      | 6   |      |     | 7    | 8   |      | ns    |

Note: 1. For slow slew outputs, add  $t_{SSO}$ .

#### **AC Characteristics**

|                                 |                                             |     | -7  |     | 10  |     | 12  |     | 15  | -:  | 20  | -2  | 25  |       |

|---------------------------------|---------------------------------------------|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-------|

| Symbol                          | Parameter                                   | Min | Max | Units |

| t <sub>PD</sub> <sup>(1)</sup>  | I, I/O or FB to<br>Non-Registered<br>Output | 2   | 7.5 | 3   | 10  | 3   | 12  | 3   | 15  | 3   | 20  | 3   | 25  | ns    |

| t <sub>PD2</sub>                | I, I/O to Feedback                          |     | 5   |     | 7   |     | 8   |     | 9   |     | 12  |     | 14  | ns    |

| t <sub>PD3</sub> <sup>(1)</sup> | Feedback to<br>Non-Registered<br>Output     | 2   | 7.5 | 3   | 10  | 3   | 12  | 3   | 15  | 3   | 20  | 3   | 25  | ns    |

| t <sub>PD4</sub>                | Feedback to<br>Feedback                     |     | 5   |     | 7   |     | 8   |     | 9   |     | 12  |     | 14  | ns    |

| t <sub>EA</sub> <sup>(1)</sup>  | OE Term to Output<br>Enable                 | 2   | 7.5 | 3   | 10  | 3   | 12  | 3   | 15  | 3   | 20  | 3   | 25  | ns    |

| t <sub>ER</sub>                 | OE Term to Output<br>Disable                | 2   | 7.5 | 2   | 10  | 2   | 12  | 2   | 15  | 2   | 20  | 2   | 25  | ns    |

| t <sub>PZX</sub> <sup>(1)</sup> | OE Pin to Output<br>Enable                  | 2   | 5.5 | 2   | 7   | 2   | 8   | 2   | 9   | 2   | 10  | 2   | 11  | ns    |

| t <sub>PXZ</sub>                | OE Pin to Output<br>Disable                 | 1.5 | 5.5 | 15  | 7   | 1.5 | 8   | 1.5 | 9   | 1.5 | 10  | 1.5 | 11  | ns    |

| t <sub>PF</sub>                 | Preset to Feedback                          |     | 6   |     | 9   |     | 9   |     | 12  |     | 18  |     | 20  | ns    |

| t <sub>PO</sub> <sup>(1)</sup>  | Preset to Registered<br>Output              |     | 8.5 |     | 12  |     | 14  |     | 20  |     | 23  |     | 25  | ns    |

| t <sub>RPF</sub>                | Reset Pin to<br>Feedback                    |     | 3   |     | 4   |     | 3   |     | 5   |     | 5.5 |     | 6   | ns    |

| t <sub>RPO</sub> <sup>(1)</sup> | Reset Pin to<br>Registered Output           |     | 5.5 |     | 7   |     | 8   |     | 11  |     | 13  |     | 15  | ns    |

| t <sub>RTF</sub>                | Reset Term to<br>Feedback                   |     | 6   |     | 9   |     | 9   |     | 12  |     | 15  |     | 20  | ns    |

| t <sub>RTO</sub> <sup>(1)</sup> | Reset Term to<br>Registered Output          |     | 8.5 |     | 12  |     | 14  |     | 20  |     | 23  |     | 25  | ns    |

| t <sub>CAS</sub>                | Cascade Logic Delay                         |     | 0.8 |     | 0.8 |     | 1   |     | 1   |     | 1.5 |     | 1.5 | ns    |

| t <sub>SSO</sub>                | Slow Slew Output<br>Adder                   |     | 3   |     | 3   |     | 3   |     | 4   |     | 4   |     | 4   | ns    |

| t <sub>FLD</sub>                | Foldback Term Delay                         |     | 4   |     | 5   |     | 7   |     | 8   |     | 10  |     | 12  | ns    |

Note: 1. For slow slew outputs, add  $t_{SSO}$ .

#### **Power Down AC Characteristics**

|                                  |                                              | -   | 7   | -1  | -10 |     | -12 |     | -15 |     | 20  | -25 |     |       |

|----------------------------------|----------------------------------------------|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-------|

| Symbol                           | Parameter                                    | Min | Max | Units |

| t <sub>IVDH</sub>                | Valid I, I/O Before<br>PD High               | 7   |     | 10  |     | 12  |     | 15  |     | 20  |     | 25  |     | ns    |

| t <sub>GVDH</sub>                | Valid OE <sup>(2)</sup><br>Before PD High    | 7   |     | 10  |     | 12  |     | 15  |     | 20  |     | 25  |     | ns    |

| t <sub>CVDH</sub>                | Valid Clock <sup>(2)</sup><br>Before PD High | 7   |     | 10  |     | 12  |     | 15  |     | 20  |     | 25  |     | ns    |

| t <sub>DHIX</sub>                | Input Don't Care<br>After PD High            |     | 15  |     | 20  |     | 22  |     | 25  |     | 30  |     | 35  | ns    |

| t <sub>DHGX</sub>                | OE Don't Care<br>After PD High               |     | 15  |     | 20  |     | 22  |     | 25  |     | 30  |     | 35  | ns    |

| t <sub>DHCX</sub>                | Clock Don't Care<br>After PD High            |     | 15  |     | 20  |     | 22  |     | 25  |     | 30  |     | 35  | ns    |

| t <sub>DLIV</sub>                | PD Low to Valid I, I/O                       |     | 1   |     | 1   |     | 1   |     | 1   |     | 1   |     | 1   | μs    |

| t <sub>DLGV</sub>                | PD Low to Valid<br>OE <sup>(2)</sup>         |     | 1   |     | 1   |     | 1   |     | 1   |     | 1   |     | 1   | μs    |

| t <sub>DLCV</sub>                | PD Low to Valid<br>Clock <sup>(2)</sup>      |     | 1   |     | 1   |     | 1   |     | 1   |     | 1   |     | 1   | μs    |

| t <sub>DLOV</sub> <sup>(1)</sup> | PD Low to Valid<br>Output                    |     | 1   |     | 1   |     | 1   |     | 1   |     | 1   |     | 1   | μs    |

Notes: 1. For slow slew outputs, add  $t_{\rm SSO}$ .

2. Pin or Product Term.

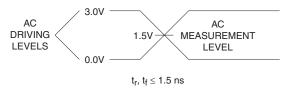

# **Input Test Waveforms and Measurement Levels**

#### **Output Test Load**

#### **Pin Capacitance**

$f = 1 \text{ MHz}, T = 25^{\circ}C^{(1)}$

|                  | Тур | Max | Units | Conditions            |

|------------------|-----|-----|-------|-----------------------|

| C <sub>IN</sub>  | 4.5 | 5.5 | pF    | $V_{IN} = 0V$         |

| C <sub>OUT</sub> | 3.5 | 4.5 | pF    | V <sub>OUT</sub> = 0V |

Note: 1. Typical values for nominal supply voltage. This parameter is only sampled and is not 100% tested.

#### **Ordering Information**

#### **Standard Package Options**

| t <sub>PD</sub> (ns) | t <sub>cos</sub><br>(ns) | f <sub>MAX</sub><br>(MHz) | Ordering Code                    | Package    | Operation Range               |

|----------------------|--------------------------|---------------------------|----------------------------------|------------|-------------------------------|

| 7.5                  | 4.5                      | 95                        | ATF1500A-7AC<br>ATF1500A-7JC     | 44A<br>44J | Commercial<br>(0°C to 70°C)   |

|                      | _                        |                           | ATF1500A-10AC<br>ATF1500A-10JC   | 44A<br>44J | Commercial<br>(0°C to 70°C)   |

| 10                   | 5                        | 76.9                      | ATF1500A-10AI<br>ATF1500A-10JI   | 44A<br>44J | Industrial<br>(-40°C to 85°C) |

| 10                   | 6                        | 60.5                      | ATF1500A-12AC<br>ATF1500A-12JC   | 44A<br>44J | Commercial<br>(0°C to 70°C)   |

| 12                   | 6                        | 62.5                      | ATF1500A-12AI<br>ATF1500A-12JI   | 44A<br>44J | Industrial<br>(-40°C to 85°C) |

| 15                   | 8                        | 52.6                      | ATF1500A-15AC<br>ATF1500A-15JC   | 44A<br>44J | Commercial<br>(0°C to 70°C)   |

| 15                   | 8                        | 52.0                      | ATF1500A-15AI<br>ATF1500A-15JI   | 44A<br>44J | Industrial<br>(-40°C to 85°C) |

| 20                   | 9                        | 40                        | ATF1500AL-20AC<br>ATF1500AL-20JC | 44A<br>44J | Commercial<br>(0°C to 70°C)   |

| 20                   | 3                        | 70                        | ATF1500AL-20AI<br>ATF1500AL-20JI | 44A<br>44J | Industrial<br>(-40°C to 85°C) |

Note:

- 1. The last time buy date is Sept. 30, 2005 for shaded parts. The replacements for fast-speed grade is the ATF1502AS (pin compatible). For others, suggested replacements are available in Green packages.

- 2. The ATF1500AL-25AC, -25AI, -25JC and -25JI were obsoleted in August 1999. The replacement was the ATF1500AL-20.

#### **Using "C" Product for Industrial**

To use commercial product for Industrial temperature ranges, down-grade one speed grade from the "I" to the "C" device (7 ns "C" = 10 ns "I") and de-rate power by 30%.

#### **Green Package Options (Pb/Halide-free/RoHS Compliant)**

| t <sub>PD</sub> (ns) | t <sub>cos</sub><br>(ns) | f <sub>MAX</sub><br>(MHz) | Ordering Code                    | Package    | Operation Range               |

|----------------------|--------------------------|---------------------------|----------------------------------|------------|-------------------------------|

| 10                   | 5                        | 76.9                      | ATF1500A-10AU<br>ATF1500A-10JU   | 44A<br>44J | Industrial<br>(-40°C to 85°C) |

| 20                   | 9                        | 40                        | ATF1500AL-20AU<br>ATF1500AL-20JU | 44A<br>44J | Industrial<br>(-40°C to 85°C) |

|     | Package Type                                             |  |  |  |  |  |  |  |  |

|-----|----------------------------------------------------------|--|--|--|--|--|--|--|--|

| 44A | 44A 44-lead, Thin Plastic Gull Wing Quad Flatpack (TQFP) |  |  |  |  |  |  |  |  |

| 44J | 44J 44-lead, Plastic J-leaded Chip Carrier (PLCC)        |  |  |  |  |  |  |  |  |

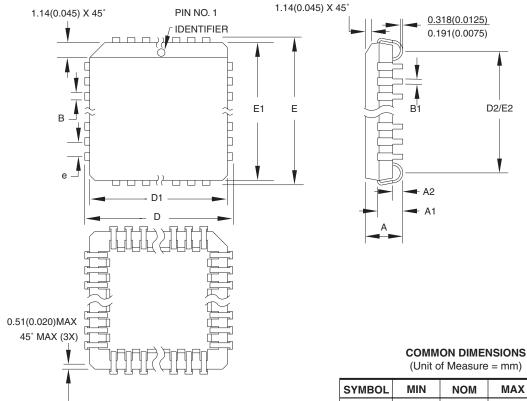

#### **44J - PLCC**

Notes:

- 1. This package conforms to JEDEC reference MS-018, Variation AC.

- Dimensions D1 and E1 do not include mold protrusion.

Allowable protrusion is .010"(0.254 mm) per side. Dimension D1 and E1 include mold mismatch and are measured at the extreme material condition at the upper or lower parting line.

- 3. Lead coplanarity is 0.004" (0.102 mm) maximum.

| NOT  | MAX    | NOM | MIN    | SYMBOL |

|------|--------|-----|--------|--------|

|      | 4.572  | _   | 4.191  | Α      |

|      | 3.048  | -   | 2.286  | A1     |

|      | _      | _   | 0.508  | A2     |

| 3    | 17.653 | _   | 17.399 | D      |

| Note | 16.662 | _   | 16.510 | D1     |

| 3    | 17.653 | -   | 17.399 | Е      |

| Note | 16.662 | _   | 16.510 | E1     |

|  | _     |           |   |        |      |

|--|-------|-----------|---|--------|------|

|  | E1    | 16.510    | - | 16.662 | Note |

|  | D2/E2 | 14.986    | _ | 16.002 |      |

|  | В     | 0.660     | - | 0.813  |      |

|  | B1    | 0.330     | _ | 0.533  |      |

|  | е     | 1.270 TYP |   |        |      |

TITLE

44J, 44-lead, Plastic J-leaded Chip Carrier (PLCC)

DRAWING NO.

44J