# W6691 Preliminary

---

## ISDN S/T Interface Transceiver

# W6691 ISDN S/T Interface Transceiver

## Data Sheet

*The information described in this document is the exclusive intellectual property of Winbond Electronics Corp and shall not be reproduced without permission from Winbond.*

*Winbond is providing this document only for reference purposes for W6691-based system design. Winbond assumes no responsibility for errors or omissions. All data and specifications are subject to change without notice.*

# Preliminary W6691

## TABLE OF CONTENTS

|                                                           |           |

|-----------------------------------------------------------|-----------|

| <b>REVISION HISTORY .....</b>                             | <b>7</b>  |

| <b>1. GENERAL DESCRIPTION .....</b>                       | <b>8</b>  |

| <b>2. FEATURES .....</b>                                  | <b>9</b>  |

| <b>3. PIN CONFIGURATIONS .....</b>                        | <b>10</b> |

| <b>4. PIN DESCRIPTION .....</b>                           | <b>13</b> |

| <b>5. SYSTEM DIAGRAM AND APPLICATIONS .....</b>           | <b>16</b> |

| <b>6. BLOCK DIAGRAM .....</b>                             | <b>18</b> |

| <b>7. FUNCTIONAL DESCRIPTIONS .....</b>                   | <b>19</b> |

| 7.1.1 Main Block Functions .....                          | 19        |

| 7.1.2 Interface and Operating Modes .....                 | 20        |

| 7.2.1 S/T Interface Transmitter/Receiver .....            | 20        |

| 7.2.2 Receiver Clock Recovery And Timing Generation ..... | 25        |

| 7.2.3 Layer 1 Activation/Deactivation .....               | 26        |

| 7.2.4 Layer 1 Activation /Deactivation in LT-S Mode ..... | 32        |

| 7.2.5 D Channel Access Control .....                      | 35        |

| 7.2.6 Frame Alignment .....                               | 36        |

| 7.2.7 Multiframe Synchronization .....                    | 38        |

| 7.2.8 Test Functions .....                                | 40        |

| 7.3 B Channel Switching .....                             | 41        |

| 7.4 PCM Port .....                                        | 42        |

| 7.5 D Channel HDLC Controller .....                       | 42        |

| 7.5.1 D Channel Message Transfer Modes .....              | 44        |

| 7.5.2 Reception of Frames in D Channel .....              | 45        |

| 7.5.3 Transmission of Frames in D Channel .....           | 46        |

| 7.6 GCI Mode Serial Interface Bus .....                   | 47        |

| 7.6.1 GCI Mode C/I Channel Handling .....                 | 49        |

| 7.6.2 GCI Mode Monitor Channel Handling .....             | 50        |

| 7.7 8-bit Microprocessor Interface .....                  | 52        |

| <b>8 REGISTER DESCRIPTIONS .....</b>                      | <b>53</b> |

| 8.1 D Channel HDLC Controller Register Address Map .....  | 53        |

| 8.2 GCI Bus Control Register Address Map .....            | 54        |

| 8.3 Miscellaneous Register Address Map .....              | 55        |

| 8.4 D Channel HDLC Controller Register Memory Map .....   | 55        |

# Preliminary W6691

---

|                                                                                   |    |

|-----------------------------------------------------------------------------------|----|

| 8.5 GCI Bus Register Memory Map.....                                              | 57 |

| 8.6 Miscellaneous Register Memory Map .....                                       | 58 |

| Table 8.6 Miscellaneous Register Memory Map .....                                 | 58 |

| 8.7 D channel HDLC Controller Register Description.....                           | 58 |

| 8.7.1 D_ch receive FIFO    D_RFIFO Read Address 00H.....                          | 58 |

| 8.7.2 D_ch transmit FIFO    D_XFIFO Write Address 01H.....                        | 59 |

| 8.7.3 D_ch command register    D_CMDR Write Address 02H .....                     | 59 |

| 8.7.4 D_ch Mode Register    D_MODE Read/Write Address 03H.....                    | 60 |

| 8.7.5 Interrupt Status Register    ISTA Read_clear Address 04H.....               | 61 |

| 8.7.6 Interrupt Mask Register    IMASK Read/Write Address 05H.....                | 63 |

| 8.7.7 D_ch Extended Interrupt Register    D_EXIR Read_clear Address 06H .....     | 63 |

| 8.7.8 D_ch Extended Interrupt Mask Register    D_EXIM Read/Write Address 07H..... | 64 |

| 8.7.9 D_ch Transmitter Status Register    D_XSTA Read Address 0AH.....            | 65 |

| 8.7.10 D_ch Receive Status Register    D_RSTA Read Address 0BH.....               | 65 |

| 8.7.11 D_ch SAPI Address Mask    D_SAM Read/Write Address 0EH .....               | 66 |

| 8.7.12 D_ch SAPI1 Register    D_SAP1 Read/Write Address 0FH.....                  | 67 |

| 8.7.13 D_ch SAPI2 Register    D_SAP2 Read/Write Address 10H.....                  | 67 |

| 8.7.14 D_ch TEI Address Mask    D_TAM Read/Write Address 11H .....                | 67 |

| 8.7.15 D_ch TEI1 Register    D_TEI1 Read/Write Address 12H.....                   | 68 |

| 8.7.16 D_ch TEI2 Register    D_TEI2 Read/Write Address 13H.....                   | 68 |

| 8.7.17 D_ch Receive Frame Byte Count High    D_RBCH Read Address 16H.....         | 69 |

| 8.7.18 D_ch Receive Frame Byte Count Low    D_RBCL    Read Address 17H.....       | 69 |

| 8.8 GCI Bus Register Description.....                                             | 70 |

| 8.8.1 Channel Selection Register    CSEL Read/Write Address 18H.....              | 70 |

| 8.8.2 Command/Indication Receive Register    CIR Read Address 1AH.....            | 70 |

| 8.8.3 Command/Indication Transmit Register    CIX Read/Write Address 1BH.....     | 71 |

| 8.8.4 S/Q Channel Receive Register    SQR Read Address 1CH .....                  | 71 |

| 8.8.5 S/Q Channel Transmit Register    SQX Read/Write Address 1DH .....           | 72 |

| 8.8.6 Monitor Receive Channel 0    MO0R Read Address 20H.....                     | 72 |

| 8.8.7 Monitor Transmit Channel 0    MO0X Read/Write Address 21H.....              | 72 |

| 8.8.8 Monitor Channel 0 Interrupt Register    MO0I Read_clear Address 22H .....   | 73 |

| 8.8.9 Monitor Channel 0 Control Register    MO0C Read/Write Address 23H .....     | 73 |

| 8.8.10 GCI Mode Control/Status Register    GCR    Read Address 26H.....           | 74 |

| 8.8.11 Monitor Receive Channel 1 Register    MO1R Read Address 27H .....          | 75 |

| 8.8.12 Monitor Transmit Channel 1 Register    MO1X    Read/Write Address 28H..... | 75 |

| 8.8.13 Monitor Channel 1 Interrupt Register    MO1I Read_clear Address 29H .....  | 76 |

| 8.8.14 Monitor Channel 1 Control Register    MO1C Read/Write Address 2AH .....    | 76 |

| 8.8.14 GCI CI1 Indication Register    CI1R Read Address 31H.....                  | 77 |

# Preliminary W6691

---

|                                                                   |                              |                              |           |

|-------------------------------------------------------------------|------------------------------|------------------------------|-----------|

| 8.8.16 GCI CI1 Command Register                                   | CI1X                         | Read/Write Address 32H.....  | 77        |

| 8.8.17 GCI Extended Interrupt Register                            | GCI_EXIR                     | Read_clear Address 34H.....  | 78        |

| 8.8.18 GCI Extended Interrupt Mask Register                       | GCI_EXIM                     | Read/Write Address 35H ..... | 78        |

| <b>8.9 Miscellaneous Register .....</b>                           |                              |                              | <b>79</b> |

| 8.9.1 Timer 1 Register                                            | TIMR1                        | Read/Write Address 38H.....  | 79        |

| 8.9.2 Timer 2                                                     | TIMR2                        | Read/ Write Address 39H..... | 80        |

| 8.9.3 Peripheral Control Register                                 | PCR                          | Read/Write Address 3AH.....  | 81        |

| 8.9.4 Peripheral I/O Data Register                                | PIODR                        | Read/Write Address 3BH ..... | 82        |

| 8.9.5 SFCTL Switch Functional Control Register                    |                              | Read/Write Address 3CH       | 83        |

| 8.9.6 ACTL1                                                       | Auxiliary Control Register 1 | Read/Write Address 3DH.....  | 84        |

| 8.9.7 ACTL2                                                       | Auxiliary Control Register2  | Read/Write Address 3EH ..... | 85        |

| 8.9.8 ACTL3                                                       | Auxiliary Control Register 3 | Read/Write Address 3FH.....  | 86        |

| <b>8.10 B1 Channel HDLC Controller Register Address MAP .....</b> |                              |                              | <b>86</b> |

| <b>8.11 B1 Channel HDLC controller Register Memory Map.....</b>   |                              |                              | <b>87</b> |

| 8.11.1 B1_ch receive FIFO                                         | B1_RFIFO                     | Read Address 50H .....       | 87        |

| 8.11.2 B1_ch transmit FIFO                                        | B1_XFIFO                     | Write Address 51H .....      | 87        |

| 8.11.3 B1_ch command register                                     | B1_CMDR                      | Read/Write Address 53H.....  | 88        |

| 8.11.4 B1_ch Mode Register                                        | B1_MODE                      | Read/Write Address 54H.....  | 89        |

| 8.11.5 B1_ch Extended Interrupt Register                          | B1_EXIR                      | Read_clear Address 56H.....  | 90        |

| 8.11.6 B1_ch Extended Interrupt Mask Register                     | B1_EXIM                      | Read/Write Address 57H ..... | 91        |

| 8.11.7 B1_ch Status Register                                      | B1_STAR                      | Read Address 58H.....        | 91        |

| 8.11.8 B1_ch Address Mask Register 1                              | B1_ADM1                      | Read/Write Address 59H ..... | 92        |

| 8.11.9 B1_ch Address Mask Register 2                              | B1_ADM2                      | Read/Write Address 5AH.....  | 93        |

| 8.11.10 B1_ch Address Register 1                                  | B1_ADR1                      | Read/Write Address 5BH ..... | 93        |

| 8.11.11 B1_ch Address Register 2                                  | B1_ADR2                      | Read/Write Address 5CH.....  | 93        |

| 8.11.12 B1_ch Receive Frame Byte Count Low                        | B1_RBCL                      | Read Address 5DH .....       | 93        |

| 8.11.13 B1_ch Receive Frame Byte Count High                       | B1_RBCH                      | Read Address 5EH .....       | 94        |

| 8.11.14 B1_ch Transmit Idle Pattern                               | B1_IDLE                      | Read/Write Address 5FH.....  | 94        |

| <b>8.12 B2 Channel HDLC Controller Register Address Map.....</b>  |                              |                              | <b>95</b> |

| <b>8.13 B2 Channel HDLC Controller Register Memory Map .....</b>  |                              |                              | <b>95</b> |

| <b>9. ELECTRICAL CHARACTERISTICS .....</b>                        |                              |                              | <b>97</b> |

| 9.1 Absolute Maximum Rating.....                                  |                              |                              | 97        |

| 9.2 Power Supply .....                                            |                              |                              | 97        |

| 9.3 DC Characteristics.....                                       |                              |                              | 97        |

| 9.4 Preliminary Switching Characteristics .....                   |                              |                              | 99        |

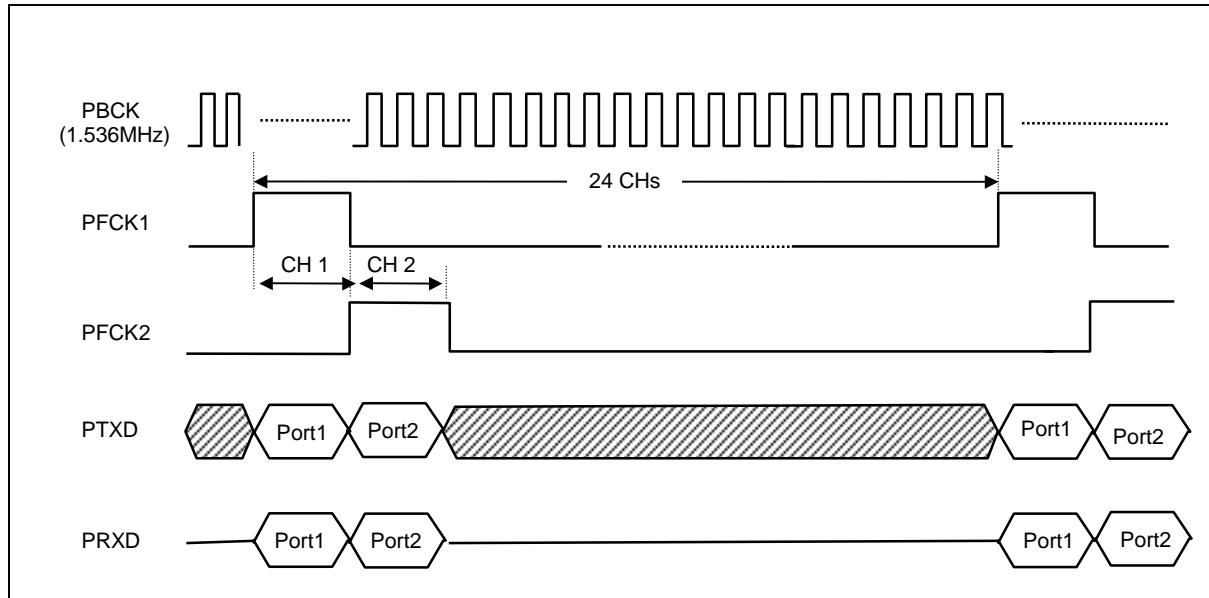

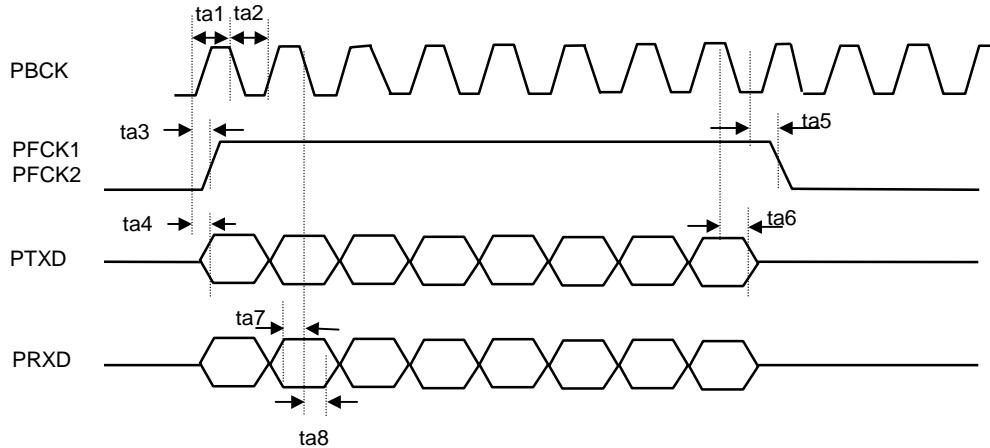

| 9.4.1 PCM Interface Timing.....                                   |                              |                              | 99        |

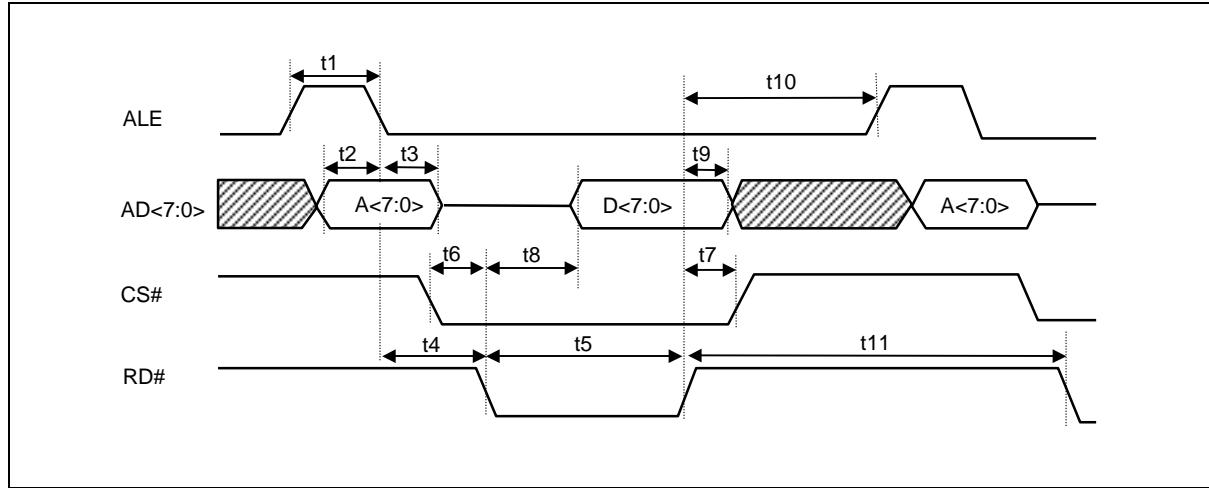

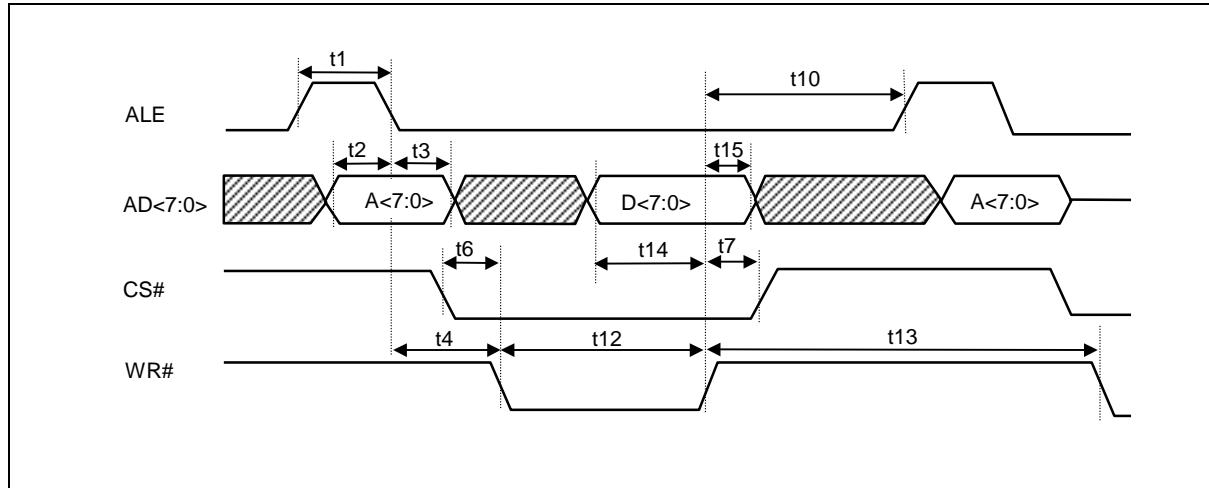

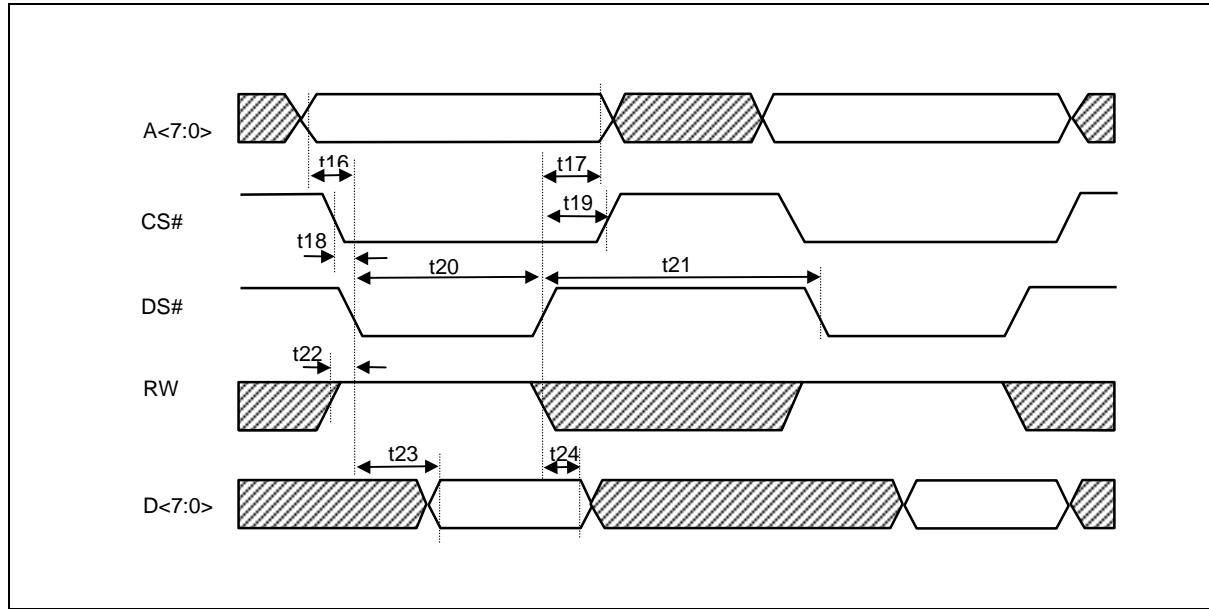

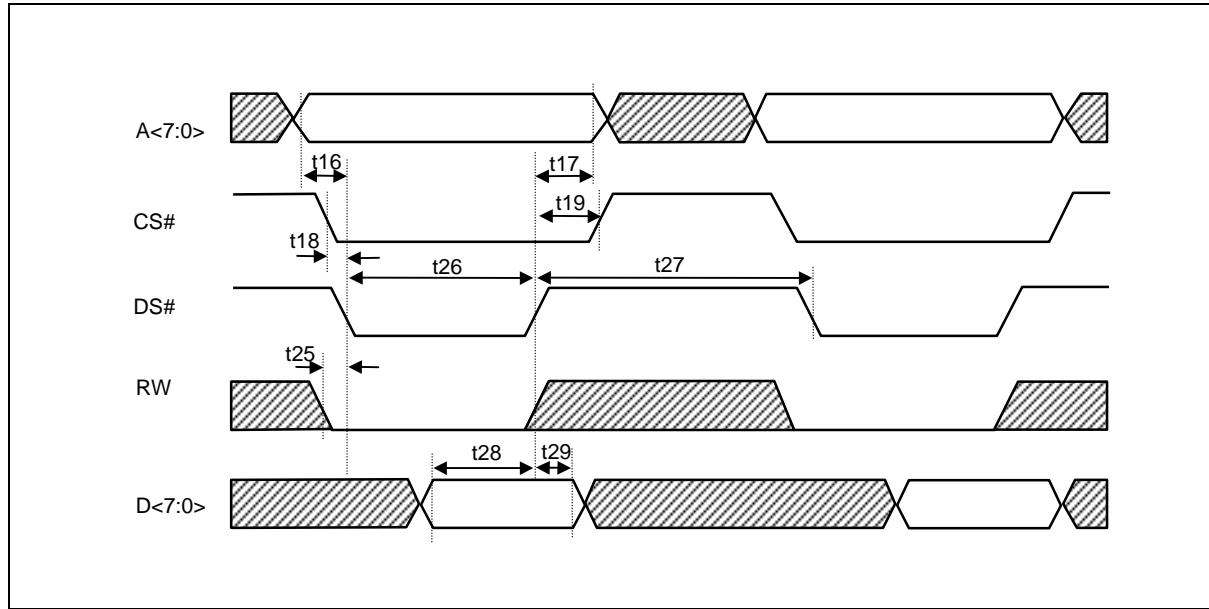

| 9.4.2 8-bit Microprocessor Timing .....                           |                              |                              | 101       |

# Preliminary W6691

---

|                                      |            |

|--------------------------------------|------------|

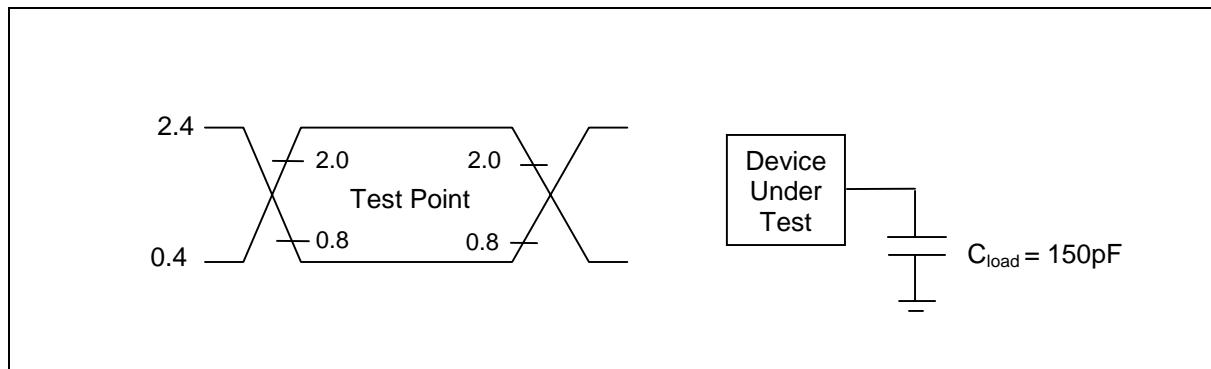

| 9.5 AC Timing Test Conditions.....   | 104        |

| <b>10. ORDERING INFORMATION.....</b> | <b>104</b> |

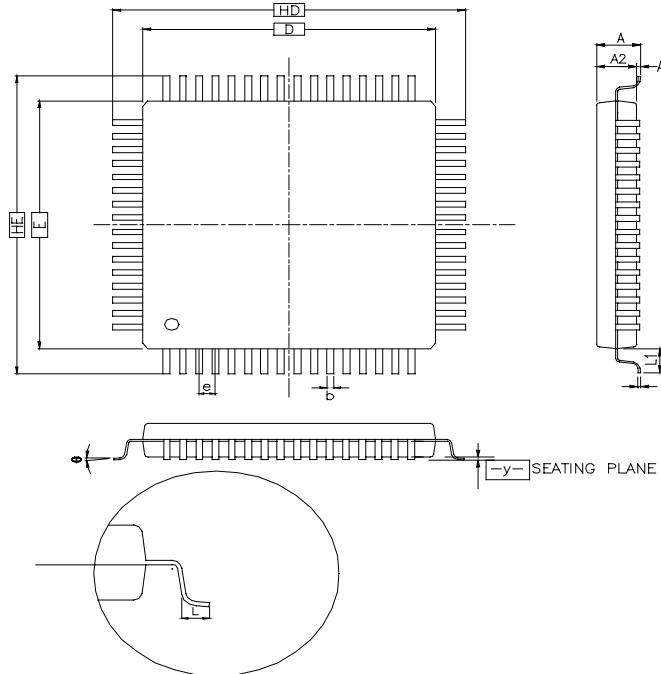

| <b>11. PACKAGE DIMENSIONS .....</b>  | <b>105</b> |

## LIST OF FIGURES

|                                                                            |    |

|----------------------------------------------------------------------------|----|

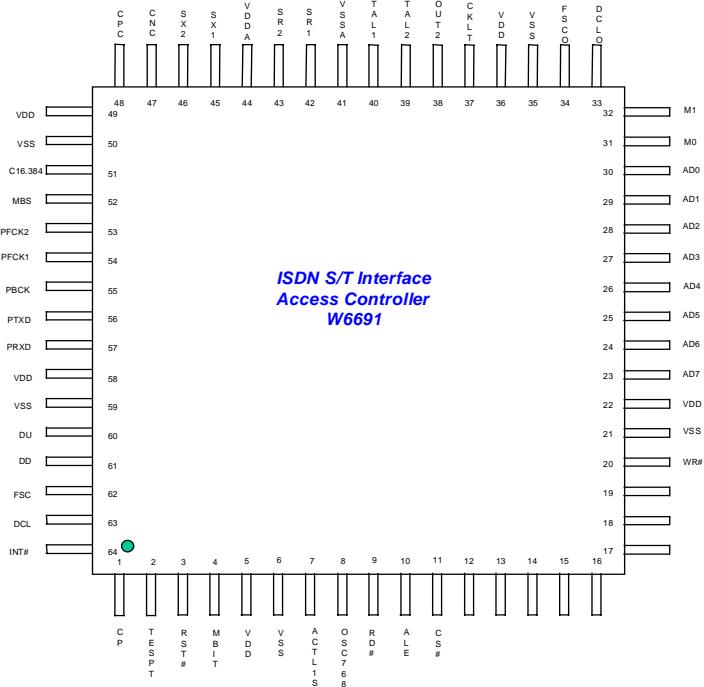

| FIG.3.1 W6691 PIN CONFIGURATION - INTEL BUS MODE .....                     | 10 |

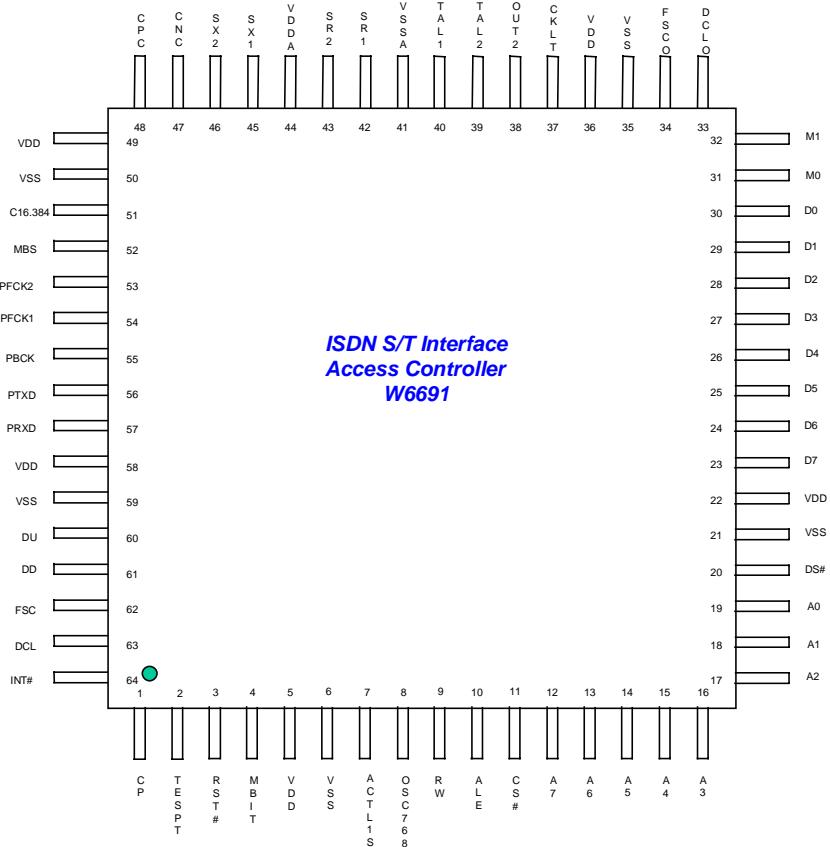

| FIG.3.2 W6691 PIN CONFIGURATION – MOTOROLA BUS MODE .....                  | 12 |

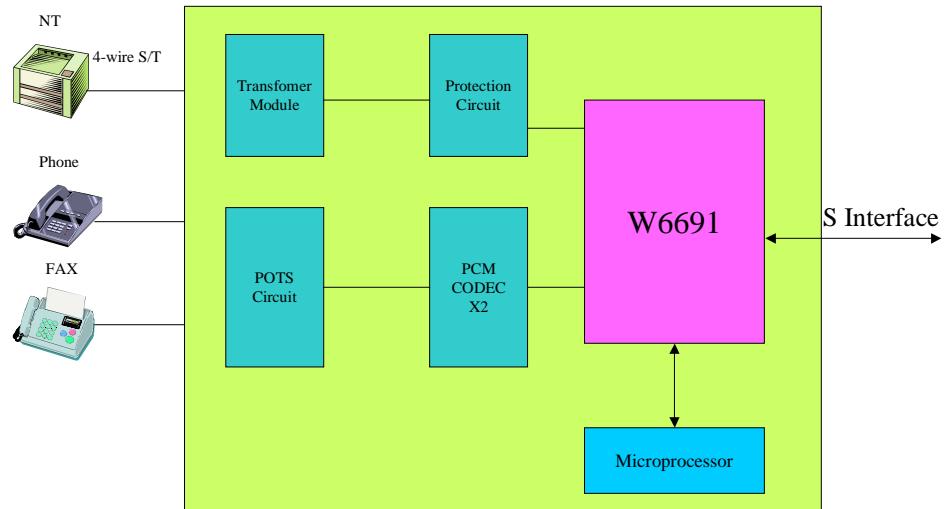

| FIG.5.1 ISDN INTERNET PASSIVE S-CARD WITH TWO POTS CONNECTIONS .....       | 16 |

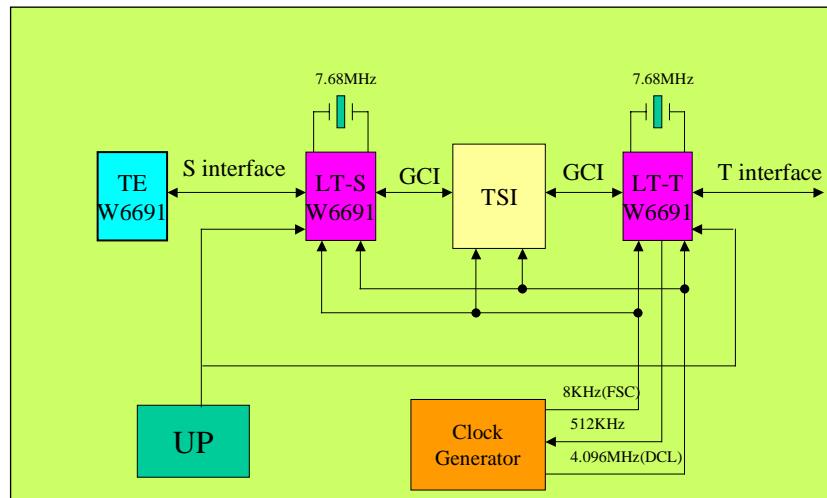

| FIG.5.2 ISDN PAXB APPLICATION .....                                        | 17 |

| FIG.6.1 W6691 FUNCTIONAL BLOCK DIAGRAM .....                               | 18 |

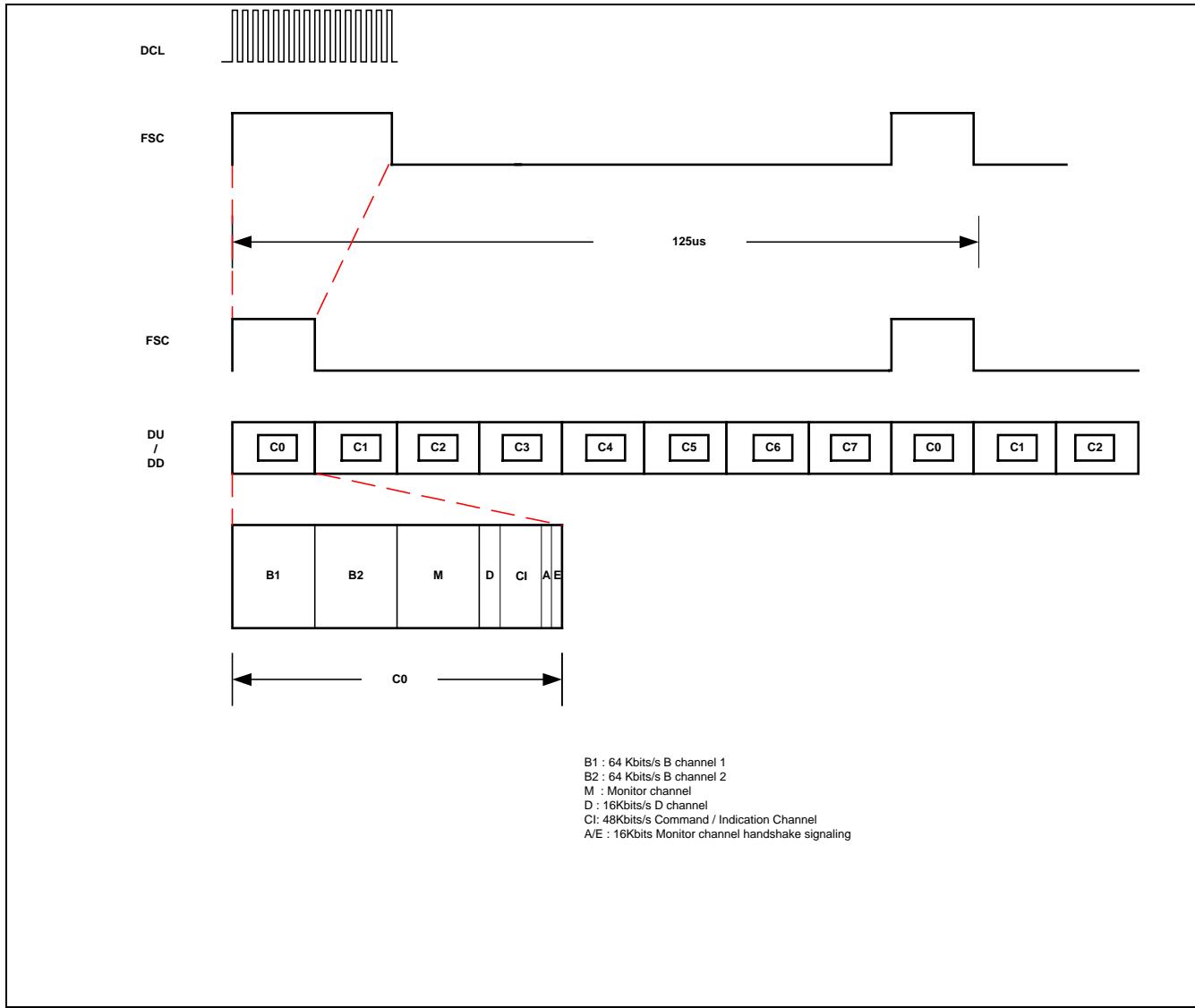

| FIG.7.1 FRAME STRUCTURE AT S/T INTERFACE .....                             | 21 |

| FIG.7.2 W6691 WIRING CONFIGURATION IN TE APPLICATIONS.....                 | 22 |

| FIG.7.3 EXTERNAL TRANSMITTER CIRCUITRY .....                               | 23 |

| FIG.7.4 EXTERNAL RECEIVER CIRCUITRY.....                                   | 24 |

| FIG.7.5 LAYER 1 ACTIVATION/DEACTION STATE DIAGRAM – NORMAL MODE .....      | 30 |

| FIG.7.6 LAYER 1 ACTIVATION/DEACTIVATION STATE DIAGRAM - SPECIAL MODE ..... | 31 |

| FIG.7.7 LAYER 1 ACTIVATION/DEACTIVATION STATE DIAGRAM IN LT-S.....         | 34 |

| FIG.7.9 SSP AND SCP TEST SIGNALS.....                                      | 41 |

| FIG.7.10 GCI TE MODE CHANNEL STRUCTURE.....                                | 48 |

| FIG.7.11 GCI NON –TERMINAL MODE CHANNEL STRUCTURE.....                     | 49 |

## LIST OF TABLES

|                                                               |    |

|---------------------------------------------------------------|----|

| TABLE 7.1 OUTPUT PHASE DELAY COMPENSATION TABLE .....         | 25 |

| TABLE 7.2 LAYER 1 COMMAND CODES.....                          | 28 |

| TABLE 7.3 LAYER 1 INDICATION CODES .....                      | 28 |

| TABLE 7.4 LAYER 1 COMMAND CODES.....                          | 33 |

| TABLE 7.5 LAYER 1 INDICATION CODES .....                      | 33 |

| TABLE 7.8 D PRIORITY CLASSES .....                            | 35 |

| TABLE 7.9 D PRIORITY COMMANDS/INDICATIONS .....               | 35 |

| TABLE 7.10 MULTIFRAME STRUCTURE IN S/T INTERFACE .....        | 39 |

| TABLE 8.1 D CHANNEL HDLC CONTROLLER REGISTER ADDRESS MAP..... | 53 |

| TABLE 8.2 GCI BUS CONTROL REGISTER ADDRESS MAP .....          | 54 |

| TABLE 8.3 MISCELLANEOUS REGISTER ADDRESS MAP .....            | 55 |

| TABLE 8.4 D CHANNEL HDLC CONTROLLER REGISTER MEMORY MAP.....  | 55 |

# Preliminary W6691

---

|                                                                 |    |

|-----------------------------------------------------------------|----|

| TABLE 8.5 GCI BUS REGISTER MEMORY MAP .....                     | 57 |

| TABLE 8.7 B1 CHANNEL HDLC CONTROLLER REGISTER ADDRESS MAP ..... | 86 |

| TABLE 8.8 B1 CHANNEL HDLC CONTROLLER REGISTER MEMORY MAP .....  | 87 |

| TABLE 8.9 B2 CHANNEL HDLC CONTROLLER REGISTER ADDRESS MAP ..... | 95 |

| TABLE 8.10 B2 CHANNEL HDLC CONTROLLER REGISTER MEMORY MAP ..... | 95 |

## LIST OF TABLES

|                                                                 |    |

|-----------------------------------------------------------------|----|

| TABLE 7.1 OUTPUT PHASE DELAY COMPENSATION TABLE .....           | 25 |

| TABLE 7.2 LAYER 1 COMMAND CODES .....                           | 28 |

| TABLE 7.3 LAYER 1 INDICATION CODES .....                        | 28 |

| TABLE 7.4 LAYER 1 COMMAND CODES .....                           | 33 |

| TABLE 7.5 LAYER 1 INDICATION CODES .....                        | 33 |

| TABLE 7.8 D PRIORITY CLASSES .....                              | 35 |

| TABLE 7.9 D PRIORITY COMMANDS/INDICATIONS .....                 | 35 |

| TABLE 7.10 MULTIFRAME STRUCTURE IN S/T INTERFACE .....          | 39 |

| TABLE 8.1 D CHANNEL HDLC CONTROLLER REGISTER ADDRESS MAP .....  | 53 |

| TABLE 8.2 GCI BUS CONTROL REGISTER ADDRESS MAP .....            | 54 |

| TABLE 8.3 MISCELLANEOUS REGISTER ADDRESS MAP .....              | 55 |

| TABLE 8.4 D CHANNEL HDLC CONTROLLER REGISTER MEMORY MAP .....   | 55 |

| TABLE 8.5 GCI BUS REGISTER MEMORY MAP .....                     | 57 |

| TABLE 8.7 B1 CHANNEL HDLC CONTROLLER REGISTER ADDRESS MAP ..... | 86 |

| TABLE 8.8 B1 CHANNEL HDLC CONTROLLER REGISTER MEMORY MAP .....  | 87 |

| TABLE 8.9 B2 CHANNEL HDLC CONTROLLER REGISTER ADDRESS MAP ..... | 95 |

| TABLE 8.10 B2 CHANNEL HDLC CONTROLLER REGISTER MEMORY MAP ..... | 95 |

# Preliminary W6691

## REVISION HISTORY

| Date     | Version | Content of Revision                                                                                                                                                                                                                                                                                                                                                                                                                              |

|----------|---------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Jan 2001 | 1.0     | The first version is edited.                                                                                                                                                                                                                                                                                                                                                                                                                     |

| Sep 2001 | 1.1     | <ol style="list-style-type: none"><li>1. W6691 Pin Configuration -- Intel Bus mode is modified on page11.</li><li>2. W6691 Pin Configuration – Motorola Bus Mode is modified on page 12</li><li>3. Pin Description is modified on page 13.</li><li>4. The chapter 7.1.2 Interface and Operating Mode description is changed on page 20.</li><li>5. The transformer ratio 1:1 is changed to 2:1 on Fig 7.3 and 7.4 page 23 and page 24.</li></ol> |

## 1. GENERAL DESCRIPTION

W6691 consists of one D channel HDLC controller and two B HDLC controller channel access. The HDLC controller facilitates efficient access to signaling, data and voice services. It provides multiplex/non- multiplexe 8- bit microprocessor interface. The interface is selected by external MBS selection. In addition, W6691 can be operated in TE, LT-S and LT-T mode programmed by external pin. In TE mode, W6691 provides PCM bus or GCI bus to connect with CODEC. In LT mode, it can be used in NT2 application. W6691 also provides various B channel switching function among PCM, GCI and Layer2. It adopts 3.3V process to manufacture. The FIFO size of D channel is 64 byte. The FIFO size of two B channel are 128bytes. Two extended external interrupt is designed for peripheral interrupt saving extra interrupt circuit design. One layer activation indication output can be programmed by microprocessor control or W6691 chip internal control. The DPLL circuit is design in chip to generate the DCL and FSC signal for NT2 application. It can eliminate extra DPLL circuit on board. In order to save a lot of crystal on board, W6691 can provide 7.68MHz OSC signal for other chip needs the clock in TE or NT2 application.

## 2. FEATURES

- Full Duplex 2B+D S/T interface transceiver compliant with ITU I.430 Recommendation

- One D channel HDLC controller

- Maskable address recognition

- Transparent (HDLC) mode

- FIFO buffer (2 \* 64)

- Two B channel HDLC controller

- Maskable address recognition

- Transparent (HDLC) mode

- FIFO buffer (2 \* 128)

- Various B channel switching capabilities and PCM intercom

- Two PCM CODEC interfaces for speech and POTS application

- GCI interface connects with other peripheral device in TE, LT-S and LT-T mode.

- Multi-frame synchronization

- 8-bits Intel mode or Motorola mode interface accesses B channel and Command/Indication channel.

- The timing clock recovery depends on operating mode.

- DPLL circuit designed in chip for NT2 application.

- Four kind of the extended interrupt trigger mode.

- Two kind of output interrupt polarity selection can be programmed.(Positive level and negative Level)

- Added reset signal to reset other chip.

- Loop back function for testing.

- Layer1 Activate Indication Output can be connected to LED

- Two of programmable timer

- 3.3 Volt power supply

- 3.3 Volt output; Maximum Input is 5.0 Volt

- Advanced CMOS technology

- 64 pin LQFP or 68 pin PLCC package

## 3. PIN CONFIGURATIONS

Fig.3.1 W6691 Pin Configuration - Intel Bus Mode

# Preliminary W6691

## Pin Configurations, continued

# Preliminary W6691

**Fig.3.2 W6691 Pin Configuration – Motorola Bus Mode**

## 4. PIN DESCRIPTION

TABLE 4.1 W6691 PIN DESCRIPTIONS

**Note:** The suffix "#" indicates an active LOW signal. In Intel or Motorola bus mode, all unspecified pins must be left unconnected.

| Pin Name                                        | Pin Number                     | Type | Functions                                                                                                                                                       |

|-------------------------------------------------|--------------------------------|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <b>Intel Bus Mode (Enabled when MBS=HIGH)</b>   |                                |      |                                                                                                                                                                 |

| MBS                                             | 52                             | I    | Microprocessor bus selector (MBS). This pin must be pulled to HIGH.                                                                                             |

| AD7-0                                           | 23, 24, 25, 26, 27, 28, 29, 30 | I/O  | Multiplexed address and data bus. During the address phase, AD7-0 contains 8-bit physical address. During the data phase, AD7-AD0 contains data.                |

| CS#                                             | 11                             | I    | Chip select.                                                                                                                                                    |

| ALE                                             | 10                             | I    | Address Latch Enable. Used to latch addresses.                                                                                                                  |

| RD#                                             | 9                              | I    | Read.                                                                                                                                                           |

| WR#                                             | 22                             | I    | Write.                                                                                                                                                          |

| RST#                                            | 3                              | I    | Reset.                                                                                                                                                          |

| INT#                                            | 64                             | O    | Interrupt. The interrupt trigger level can be programmable by ACTL2:INTOL. It provides two types of interrupt trigger level including low level and high level. |

| <b>Motorola Bus Mode (Enabled when MBS=LOW)</b> |                                |      |                                                                                                                                                                 |

| MBS                                             | 52                             | I    | Microprocessor bus selector (MBS). This pin must be pulled to LOW.                                                                                              |

| D7-D0                                           | 23, 24, 25, 26, 27, 28, 29, 30 | I/O  | Data bus.                                                                                                                                                       |

| A7-A0                                           | 12, 13, 14, 15, 16, 17, 18, 19 | I    | Address bus.                                                                                                                                                    |

| CS#                                             | 11                             | I    | Chip select.                                                                                                                                                    |

| DS#                                             | 20                             | I    | Data strobe.                                                                                                                                                    |

| RW                                              | 9                              | I    | Read/Write identify. HIGH is for read and LOW is for write.                                                                                                     |

| RST#                                            | 3                              | I    | Reset.                                                                                                                                                          |

| INT#                                            | 64                             | O    | Interrupt. The interrupt trigger level can be programmable by ACTL2:INTOL. It provides two types of interrupt trigger level including low level and high level. |

# Preliminary W6691

| <b>GCI Bus</b>                                    |    |     |                                                                                                                                                                |

|---------------------------------------------------|----|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------|

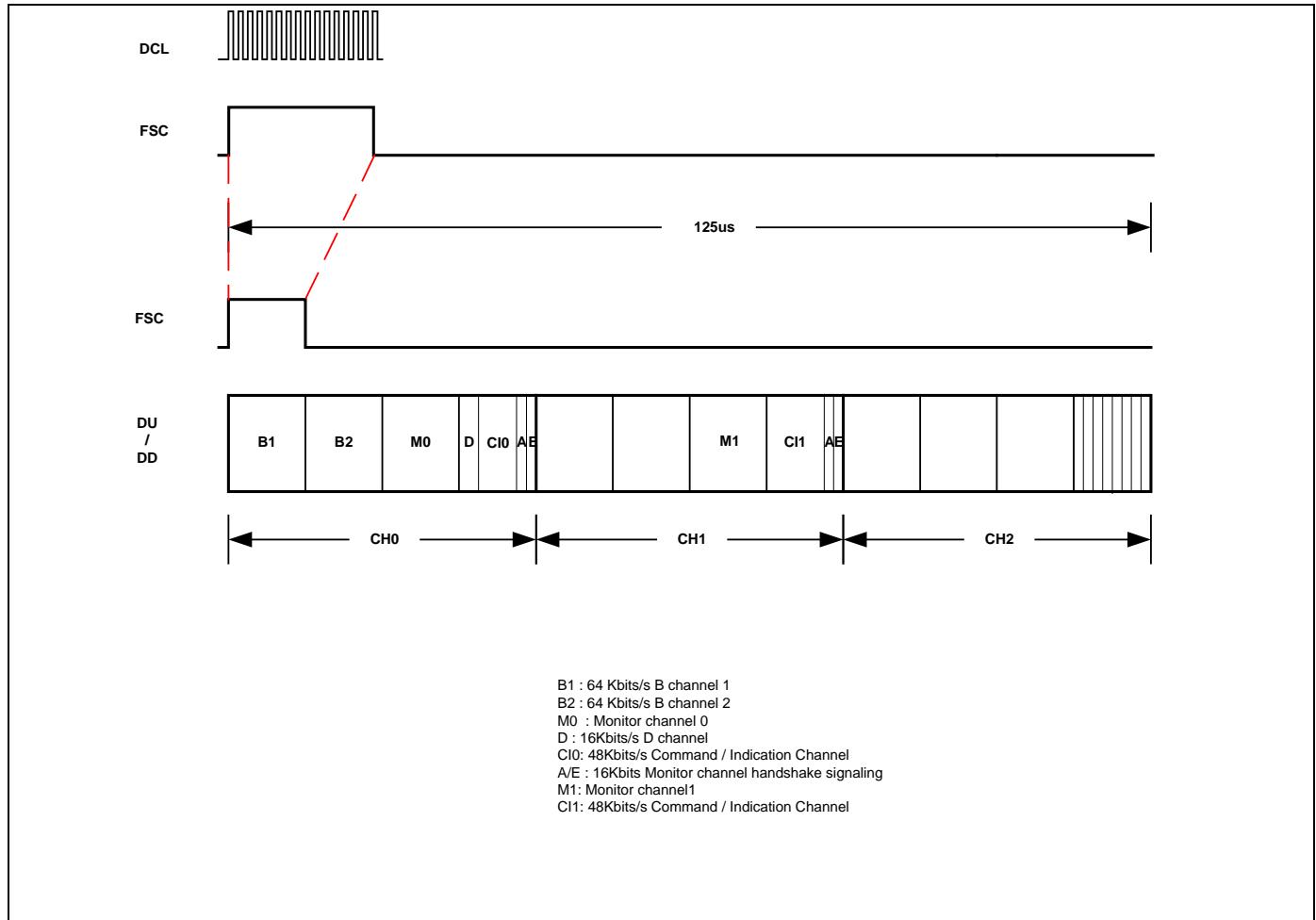

| DCL                                               | 63 | I/O | GCI Bus Data Clock : the frequency is twice data rate<br>TE mode : 1.536 MHz.<br>LT-T/LT-S mode : 4.096 MHz.<br>NT mode : 512KHz<br>It needs external pull-up. |

| FSC                                               | 62 | I/O | GCI Bus Frame Synchronization Clock: 8KHz. It needs external pull-up.                                                                                          |

| DD                                                | 61 | I/O | GCI Bus Data Downstream. It needs external pull-up.                                                                                                            |

| DU                                                | 60 | I/O | GCI Bus Data Upstream. It needs external pull-up.                                                                                                              |

| CP/BCL                                            | 1  | O   | CP – output 512KHz in LT-T mode.<br>BCL – output 768KHz in TE mode.                                                                                            |

| FSCO                                              | 34 | O   | Output FSCO clock 8KHz for LT-T/LT-S mode(NT2 application). It is synchronous to DCLO.                                                                         |

| DCLO                                              | 33 | O   | Output DPLL clock 4.096MHz for LT-T/LT-S mode(NT2 application). It is synchronous to T interface clock.                                                        |

| C16.384                                           | 51 | I   | 16.384 MHz clock input for DPLL circuit to generate FSCO and DCLO.                                                                                             |

| <b>PCM Interface( It is only used in TE Mode)</b> |    |     |                                                                                                                                                                |

| PFCK1                                             | 54 | O   | PCM port1 frame synchronization signal, with 8 KHz repetition rate and 8 bits pulse width.                                                                     |

| PFCK2                                             | 53 | O   | PCM port2 frame synchronization signal, with 8 KHz repetition rate and 8 bits pulse width.                                                                     |

| PBCK                                              | 55 | O   | PCM bit synchronization clock of 1.536 MHz.                                                                                                                    |

| PTXD                                              | 56 | O   | PCM transmit bus data output. A maximum of two channels with 64 Kbits/s data rate can be multiplexed on this signal. It needs external pull-up.                |

| PRXD                                              | 57 | I   | PCM bus receive data input. A maximum of two channels with 64 Kbits/s data rate can be multiplexed on this signal. It needs external pull-up.                  |

| <b>ISDN Signals and External Crystal</b>          |    |     |                                                                                                                                                                |

| SR1                                               | 42 | I   | S/T bus receiver input (negative).                                                                                                                             |

| SR2                                               | 43 | I   | S/T bus receiver input (positive).                                                                                                                             |

| SX1                                               | 45 | O   | S/T bus transmitter output (positive).                                                                                                                         |

# Preliminary W6691

|                                              |                   |   |                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|----------------------------------------------|-------------------|---|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SX2                                          | 46                | O | S/T bus transmitter output (negative).                                                                                                                                                                                                                                                                                                                                                                                                                  |

| XTAL1                                        | 40                | I | Crystal or Oscillator clock input. The clock frequency: 7.68MHz±100PPM.                                                                                                                                                                                                                                                                                                                                                                                 |

| XTAL2                                        | 41                | O | Crystal clock output. Left unconnected when using oscillator.                                                                                                                                                                                                                                                                                                                                                                                           |

| <b>Functional Test</b>                       |                   |   |                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| TESTP                                        | 2                 | I | Used to enable normal operation (1) or enter test mode (0).                                                                                                                                                                                                                                                                                                                                                                                             |

| Timer2 Expiration Output                     |                   |   |                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| TOUT2                                        | 38                | O | Timer 2 output. A square wave with 50 % duty cycle, 1~63 ms period can be generated.                                                                                                                                                                                                                                                                                                                                                                    |

| Clock Pulse                                  |                   |   |                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| OSC768                                       | 8                 | O | It provides output 7.68MHz clock. It does not synchronize to S interface.                                                                                                                                                                                                                                                                                                                                                                               |

| <b>Operating Mode</b>                        |                   |   |                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| M0                                           | 31                | I | Setting of operating mode                                                                                                                                                                                                                                                                                                                                                                                                                               |

| M1                                           | 32                | I | Setting of operating mode                                                                                                                                                                                                                                                                                                                                                                                                                               |

| <b>Peripheral Input Port and Output Port</b> |                   |   |                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| ACTL1S                                       | 7                 | O | <p>Activate Layer1 Status. This pin can be pulled to low level or programmed by microprocessor by ACTL2 : ACTL1S when Layer1 operates in activate.</p> <p><b>ACTL2 : ACTL1S:</b></p> <p>0: When Layer 1 operates in activate state, ACTL1S pin is pulled to low level. In contrast, if Layer 1 operates in deactivate state, ACTL1S pin is driven to high level.</p> <p>1: The ACTL1 output level is programmed by microprocessor (ACTL2 : ACTL1S).</p> |

| <b>Power and Ground</b>                      |                   |   |                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| VDD                                          | 5, 22, 36, 49, 58 | I | Digital Power Supply (3V±5%).                                                                                                                                                                                                                                                                                                                                                                                                                           |

| VDDA                                         | 44                | I | Analog Power Supply (3V±5%).                                                                                                                                                                                                                                                                                                                                                                                                                            |

| VSS                                          | 6, 21, 35, 50, 59 | I | Digital Ground.                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| VSSA                                         | 41                | I | Analog Ground.                                                                                                                                                                                                                                                                                                                                                                                                                                          |

## 5. SYSTEM DIAGRAM AND APPLICATIONS

Fig.5.1 ISDN TA with Two POTS Connections

# Preliminary W6691

Fig.5.2 ISDN PAXB Application

## 6. BLOCK DIAGRAM

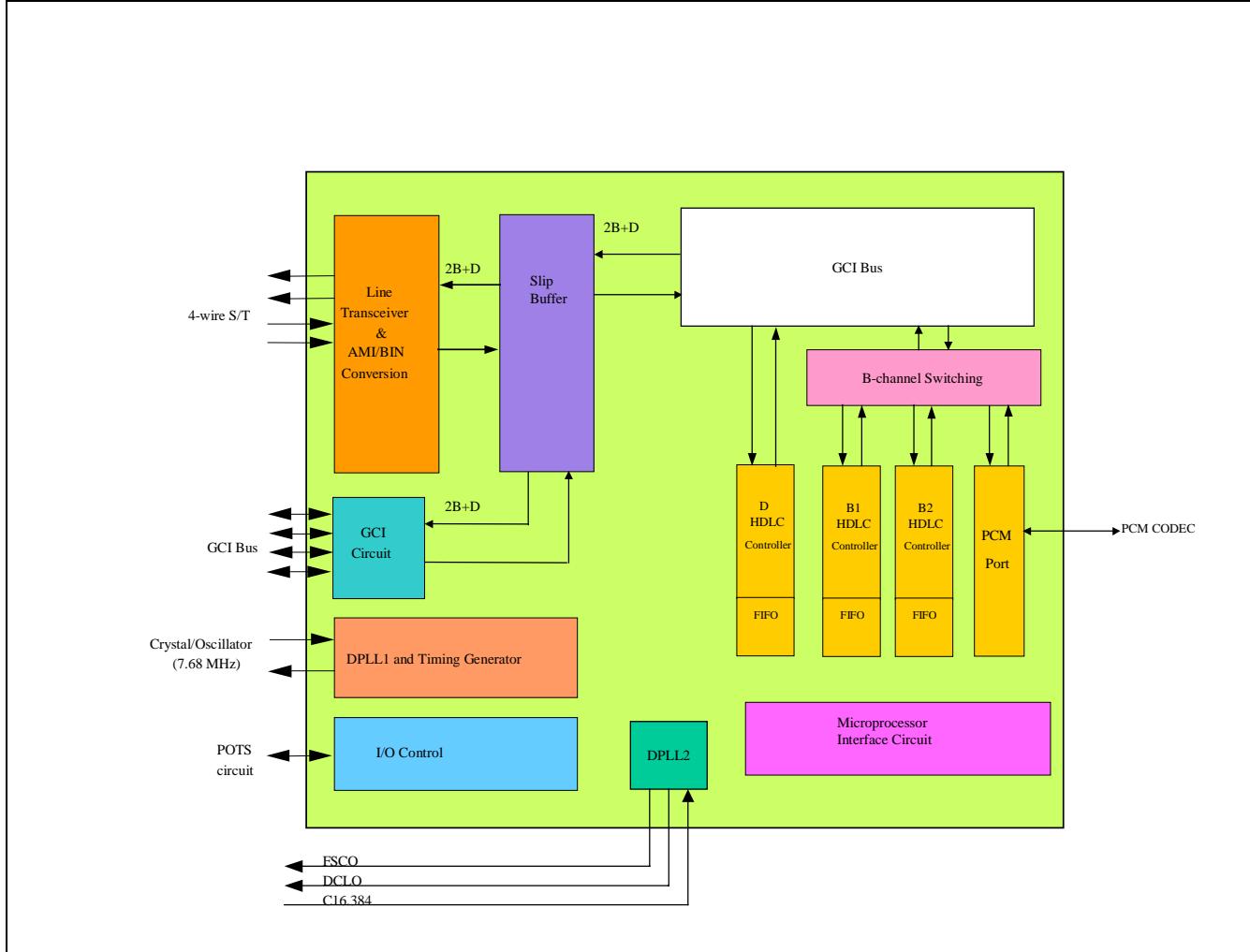

The block diagram of W6691 is shown in Figure 6.1

Fig.6.1 W6691 Functional Block Diagram

## 7. FUNCTIONAL DESCRIPTIONS

### 7.1.1 Main Block Functions

The functional block diagram of W6691 is shown in Fig.6.1. The main function blocks are:

- Layer 1 function according to ITU-T I.430

- B channel switching

- GCI bus interface

- PCM port (x 2) and internal B channel switching

- D channel HDLC controller

- DPLL 2 circuit generating 4.096 MHz clock for NT2 application

The layer 1 function includes:

- S/T bus transmitter/receiver

- Timing recovery using Digital Phase Locked Loop (DPLL) circuit

- Layer 1 activation/deactivation

- D channel access control

- Frame alignment

- Multi-frame synchronization

- Test functions

The serial interface bus performs the multiplexing/demultiplexing of D and 2B channels.

The B channel switching determines the connection between layer 1/GCI, layer 2 and PCM.

GCI bus is for TE, LT-S and LT-T mode applications.

The PCM port provides two 64 kbps clear channels to connect to PCM codec chips.

The D channel HDLC controller performs the LAPD (Link Access Procedure on the D channel) protocol according to ITU-T I.441/Q.921 recommendation.

The peripheral simple I/O is used to control other peripheral devices such as CODEC, SLIC, DTMF detector, LEDs.

## 7.1.2 Interface and Operating Modes

The W6691 can be configured for the following application:

- ISDN terminals --- TE mode (M1=0 & M0=0)

- ISDN subscriber line termination --- LT-S mode (M1=1 & M0=0)

- ISDN trunk line termination ---LT-T mode (M1=0 & M0=1)

TE , LT-S and LT-T modes are configured by setting mode pins (M1 and M0).

## 7.2.1 S/T Interface Transmitter/Receiver

According to ITU-T I.430, pseudo-ternary code with 100% pulse width is used in both directions of transmission on the S/T interface. The binary "1" is represented by no line signal (zero volt), whereas a binary "0" is represented by a positive or negative pulse.

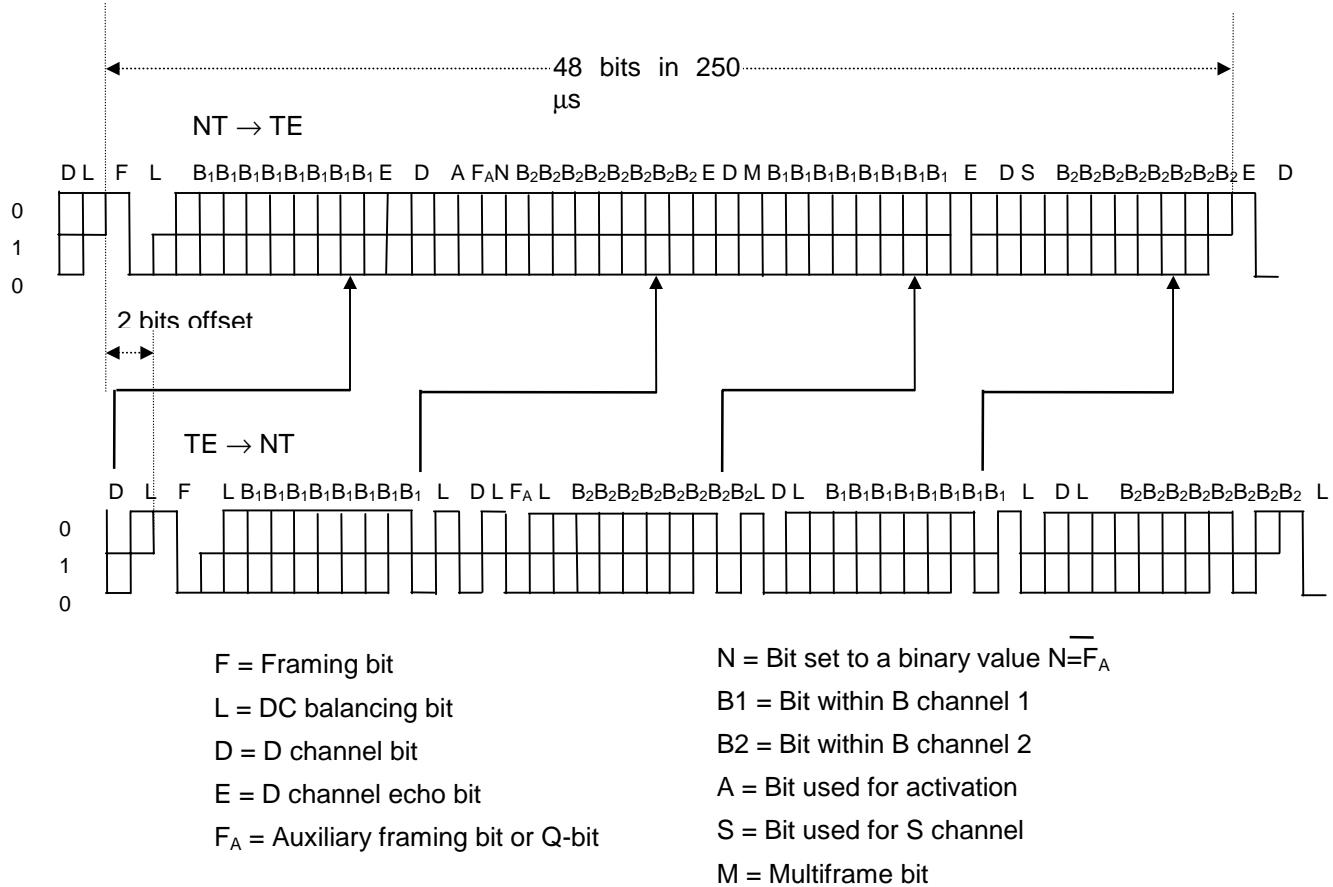

Data transmissions on the S/T interface are arranged as frame structures. The frame is 250  $\mu$ s long and consists of 48 bits, which corresponds to a 192 kbit/s line rate. Each frame carries two octets of B1 channel, two octets of B2 channel and four D channel bits. Therefore, the 2B+D data rate is 144 kbit/s. The frame structure is shown in Fig.7.1.

The frame begin is marked by a framing bit, which is followed by a DC balancing bit. The first binary "0" following the framing bit balancing bit is of the same polarity as the framing bit balancing bit, and subsequent binary zeros must alternate in polarity.

Fig.7.1 Frame structure at S/T interface

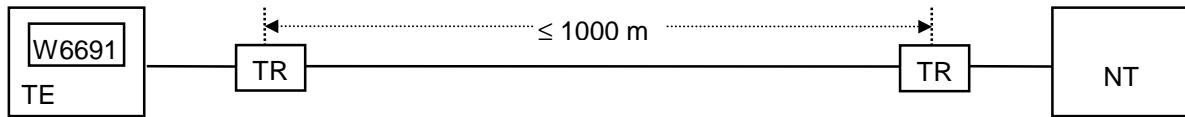

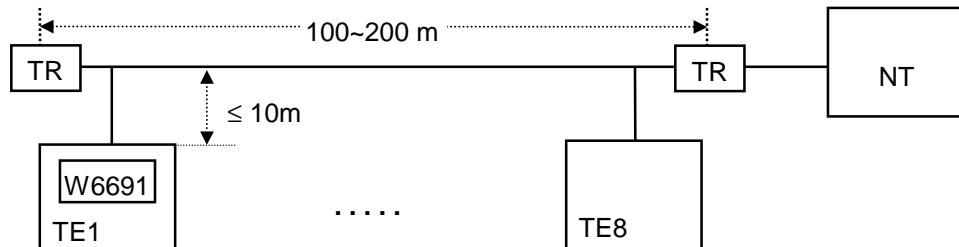

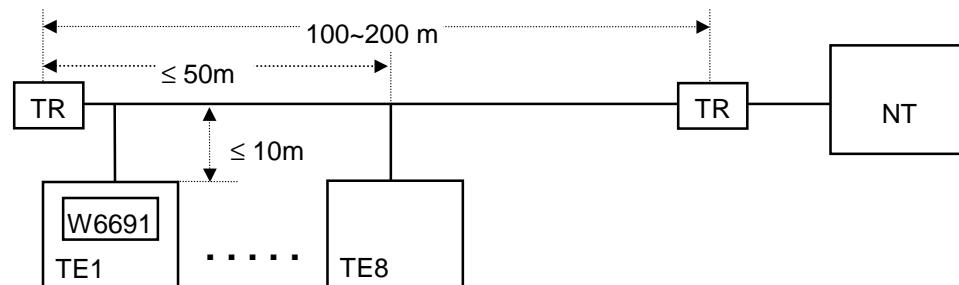

There are three wiring configurations according to I.430 : point-to-point, short passive bus and extended passive bus. They are shown in Fig.7.2.

# Preliminary W6691

(a) Point-to-point configuration

(b) Short passive bus configuration

(c) Extended passive bus configuration

TR : Terminating Resistor

Fig.7.2 W6691 wiring configuration in TE applications

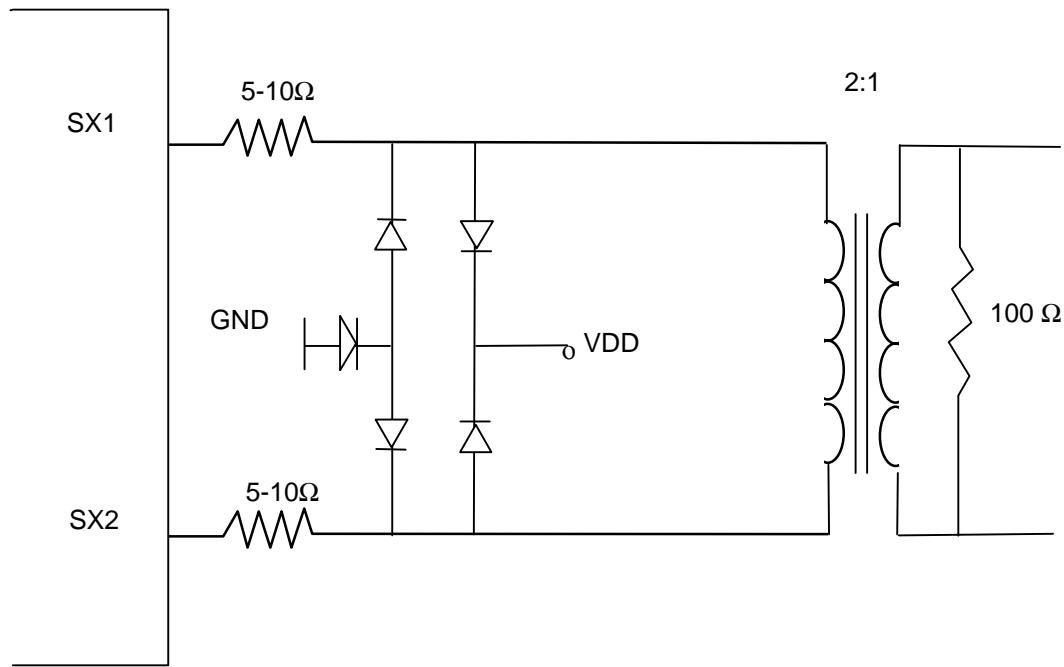

The transmitter and receiver are implemented by differential circuits to increase signal to noise ratio (SNR). The nominal differential line pulse amplitude at  $100 \Omega$  termination is 750 mV, zero to peak. Transformers with 1:1 turn ration are needed at transmitter and receiver for voltage level translation and DC isolation.

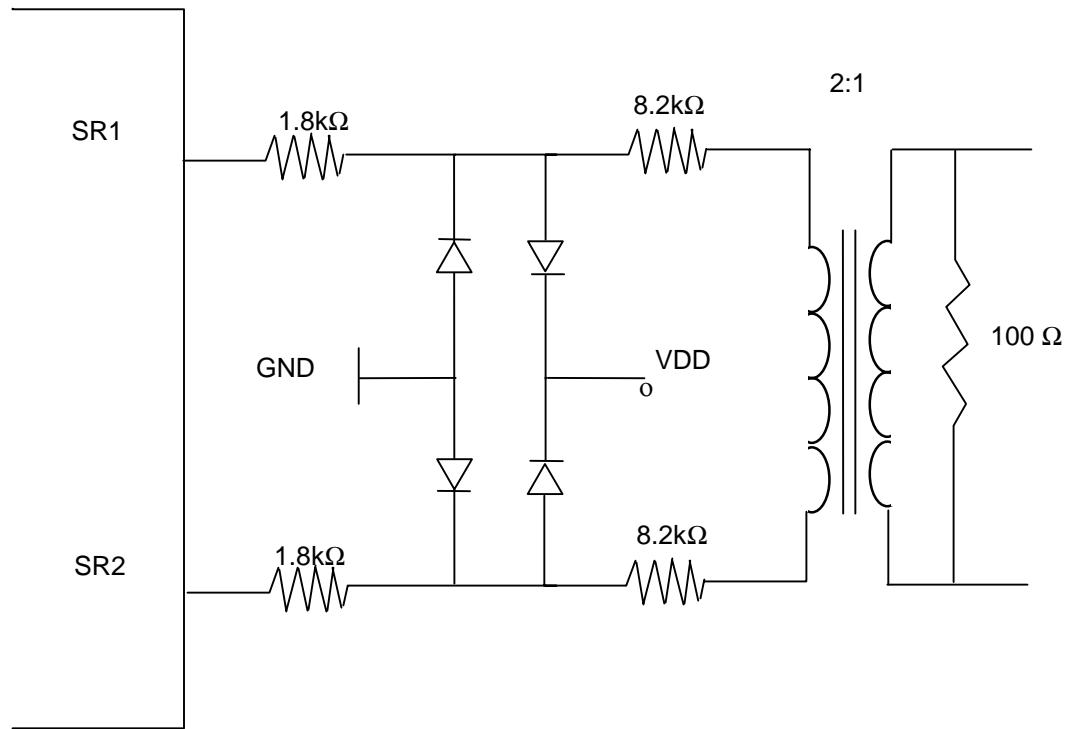

To meet the electrical characteristic requirements in I.430, some additional circuits are needed. At the transmitter side, the external resistors (5 to  $10 \Omega$ ) are used to adjust the output pulse amplitude and to meet the transmitter active impedance ( $\geq 20 \Omega$ ) when transmitting binary zeros. At the receiver side, the  $1.8 \text{ k}\Omega$

# Preliminary W6691

resistors protect the device inputs, while the  $10\text{ k}\Omega$  resistors ( $1.8\text{ k}\Omega + 8.2\text{ k}\Omega$ ) limit the peak current in impedance tests. The diode bridge is used for overvoltage protection.

Fig.7.3 External Transmitter Circuitry

Fig.7.4 External Receiver Circuitry

After hardware reset, the receiver may enter power down state in order to save power consumption. In this state, the internal clocks are turned off, but the analog level detector is still active to detect signal coming from the S interface. The power down state is left either by non-INFO 0 signal from S interface or C/I command from microprocessor.

## 7.2.2 Receiver Clock Recovery And Timing Generation

### 1) TE mode

A Digital Phase Locked Loop (DPLL) circuit is used to derive the receiving clock from the received data stream in TE mode application. This DPLL uses a 7.68 MHz clock as reference. According to I.430, the transmit clock is normally delayed by 2 bit time from the receive clock. The "total phase deviation from input to output" is -7% to +15% of a bit period. In some cases, delay compensation may be needed to meet this requirement (see OPS1-0 bits in D\_CTL register).

### 2) LT-T mode

In LT-T mode application, A Digital Phase Locked Loop (DPLL) circuit is also used to derive the receiving clock(192KHz) from the received data stream. W6691 generates a CP (Clock Pulse) derived from the 192KHz receiving clock with DPLL. CP clock rate is 512KHz or 1536KHz. If CP clock is used to synchronize NT2 clock, W6691 provide a slip buffer to avoid slipping between DCL and CP.

### 3) LT-S mode

In LT-S modes, A Digital Phase Locked Loop (DPLL) circuit is used to derive the receiving clock from the received data stream. This DPLL uses a 7.68 MHz clock as reference.

**TABLE 7.1 OUTPUT PHASE DELAY COMPENSATION TABLE**

| OPS1 | OPS0 | Effect                           |

|------|------|----------------------------------|

| 0    | 0    | No phase delay compensation      |

| 0    | 1    | Phase delay compensation 260 ns  |

| 1    | 0    | Phase delay compensation 520 ns  |

| 1    | 1    | Phase delay compensation 1040 ns |

W6691 does not need RC filter on receiver side, therefore zero delay compensation is selected normally. This is also the default setting.

The PCM output clocks (PFCK1-2, PBCK) are locked to the S-interface timing with jitter. See the electrical specification.

## 7.2.3 Layer 1 Activation/Deactivation

The layer 1 activation/deactivation procedures are implemented by a finite state machine according to TE/LT-T/LT-S mode. The state transitions are triggered by signals received at S interface or commands issued from microprocessor. The state outputs signals to S interface and indication to microprocessor. The CIX register is used by microprocessor to issue command, and the CIR register is used by microprocessor to receive indication.

Some commands are used for special purposes. They are "layer 1 reset", "analog loopback", "send continuous zeros" and "send single zero".

### 7.2.3.1 States Descriptions And Command/Indication Codes in TE/LT-T

#### F3 Deactivated without clock

This is the "deactivated" state of ITU-T I.430. The receive line awake unit is active except during a hardware reset pulse. After reset, once the indication "1111" has been read out, internal clocks will turn off and stay at this state if INFO 0 is received on the S line. The turn off time is approximate 93 ms. The ECK command must be issued to activate the clocks.

#### F3 Deactivated with clock

This state is identical to "F3 Deactivated without clock" except the internal clocks are enabled. The state is entered by the ECK command. The clocks are enabled approximately 0.5 ms to 4 ms after the ECK command, depending on the crystal capacitances. (It is about 0.5 ms for 12pF to 33pF capacitance).

#### F3 Awaiting Deactivation

The W6691 enters this state after receiving INFO 0 (in states F5 to F8) for 16ms (64 frames). This time constant prevents spurious effect on S interface. Any non-INFO 0 signal on the S interface causes transition to "F5 Identifying Input" state. If this transition does not occur in a specific time (500 - 1000 ms), the microprocessor may issue DRC or ECK command to deactivate layer 1.

#### F4 Awaiting Signal

This state is reached when an activate request command has been received. In this state, the layer 1 transmits INFO1 and INFO 0 is received from the S interface. The software starts timer T3 of I.430 when issuing activate request command. The software deactivates layer 1 if no signal other than INFO 0 has been received on S interface before expiration of T3.

## F5 Identifying Input

After the receipt of any non-INFO 0 signal from NT, the W6691 ceases to transmit INFO 1 and awaits identification of INFO 2 or INFO 4. This state is reached at most 50  $\mu$ s after a signal different from INFO 0 is present at the receiver of the S interface.

## F6 Synchronized

When W6691 receives an activation signal (INFO 2), it responds with INFO 3 and waits for normal frames (INFO 4). This state is reached at most 6 ms after an INFO 2 arrives at the S interface (in case the clocks were disabled in "F3 Deactivated without clock").

## F7 Activated

This is the normal active state with the layer 1 protocol activated in both directions. From state "F6 Synchronized", state F7 is reached at most 0.5 ms after reception of INFO 4. From state "F3 Deactivated without clock" with the clocks disabled, state F7 is reached at most 6 ms after the W6691 is directly activated by INFO 4.

## F8 Lost Framing

This is the state where the W6691 has lost frame synchronization and is awaiting resynchronization by INFO 2 or INFO 4 or deactivation by INFO 0.

### Special States:

#### Analog Loop Initiated

On Enable Analog Loop command, INFO 3 is sent by the line transmitter internally to the line receiver (INFO 0 is sent to the line). The receiver is not yet synchronized.

#### Analog Loop Activated

The receiver is synchronized on INFO 3 which is looped back internally from the transmitter. The indication 'TI' or 'ATI' is sent depending on whether or not a signal different from INFO 0 is detected on the S interface.

#### Send Continuous Pulses

A 96 kHz continuous pulse with alternating polarities is sent.

# Preliminary W6691

## Send Single Pulses

A 2 KHz , isolated pulse with alternating polarities is sent.

## Layer 1 Reset

A layer 1 reset command forces the transmission of INFO 0 and disables the S line awake detector. Thus activation from NT is not possible. There is no indication in reset state. The reset state can be left only with ECK command.

**TABLE 7.2 LAYER 1 COMMAND CODES**

| Command                         | Symbol | Code | Description                                            |

|---------------------------------|--------|------|--------------------------------------------------------|

| Enable clock                    | ECK    | 0000 | Enable internal clocks                                 |

| Layer 1 reset                   | RST    | 0001 | Layer 1 reset                                          |

| Send continuous pulses          | SCP    | 0100 | Send continuous pulses at 96 kHz                       |

| Send single pulses              | SSP    | 0010 | Send isolated pulses at 2 kHz                          |

| Activate request at priority 8  | AR8    | 1000 | Activate layer 1 and set D channel priority level to 8 |

| Activate request at priority 10 | AR10   | 1001 | Activate layer 1 and set D channel priority to 10      |

| Enable analog loopback          | EAL    | 1010 | Enable analog loopback                                 |

| Deactivate layer 1              | DRC    | 1111 | Deactivate layer 1 and disable internal clocks         |

**TABLE 7.3 LAYER 1 INDICATION CODES**

| Indication                                | Symbol | Code | Descriptions                                                              |

|-------------------------------------------|--------|------|---------------------------------------------------------------------------|

| Clock Enabled                             | CE     | 0111 | Internal clocks are enabled                                               |

| Deactivate downstream request             | DRD    | 0000 | Deactivation request by S interface, i.e INFO 0 received                  |

| Level detected                            | LD     | 0100 | Signal received, receiver not synchronous                                 |

| Activate request downstream               | ARD    | 1000 | INFO 2 received                                                           |

| Test indication                           | TI     | 1010 | Analog loopback activated or continuous zeros or single zeros transmitted |

| Awake test indication                     | ATI    | 1011 | Level detected during test function                                       |

| Activate indication with priority class 1 | AI8    | 1100 | INFO 4 received, D channel priority is 8 or 9                             |

# Preliminary W6691

|                                           |      |      |                                                   |

|-------------------------------------------|------|------|---------------------------------------------------|

| Activate indication with priority class 2 | AI10 | 1101 | INFO 4 received, D channel priority is 10 or 11   |

| Clock disabled                            | CD   | 1111 | Layer 1 deactivated, internal clocks are disabled |

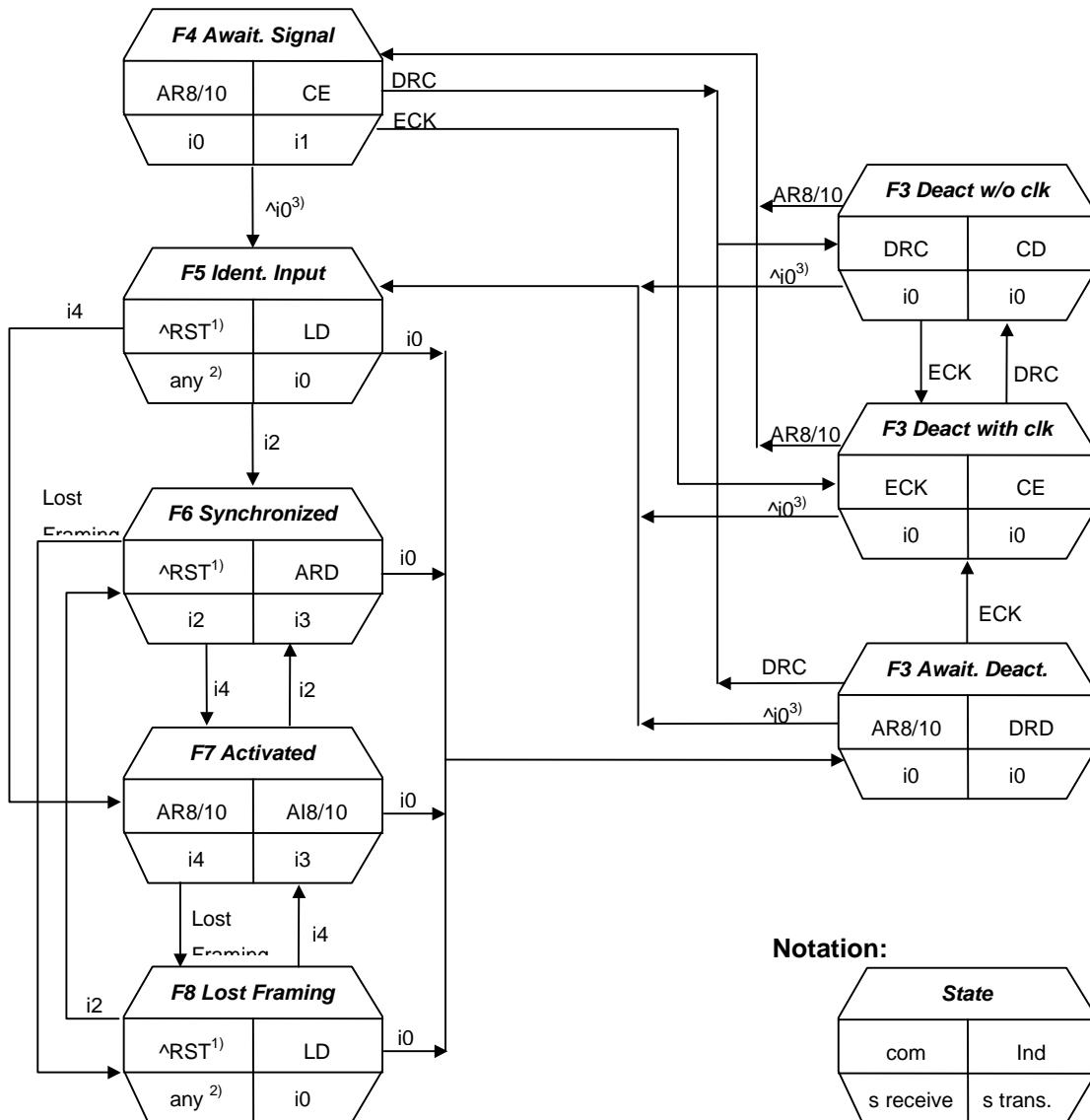

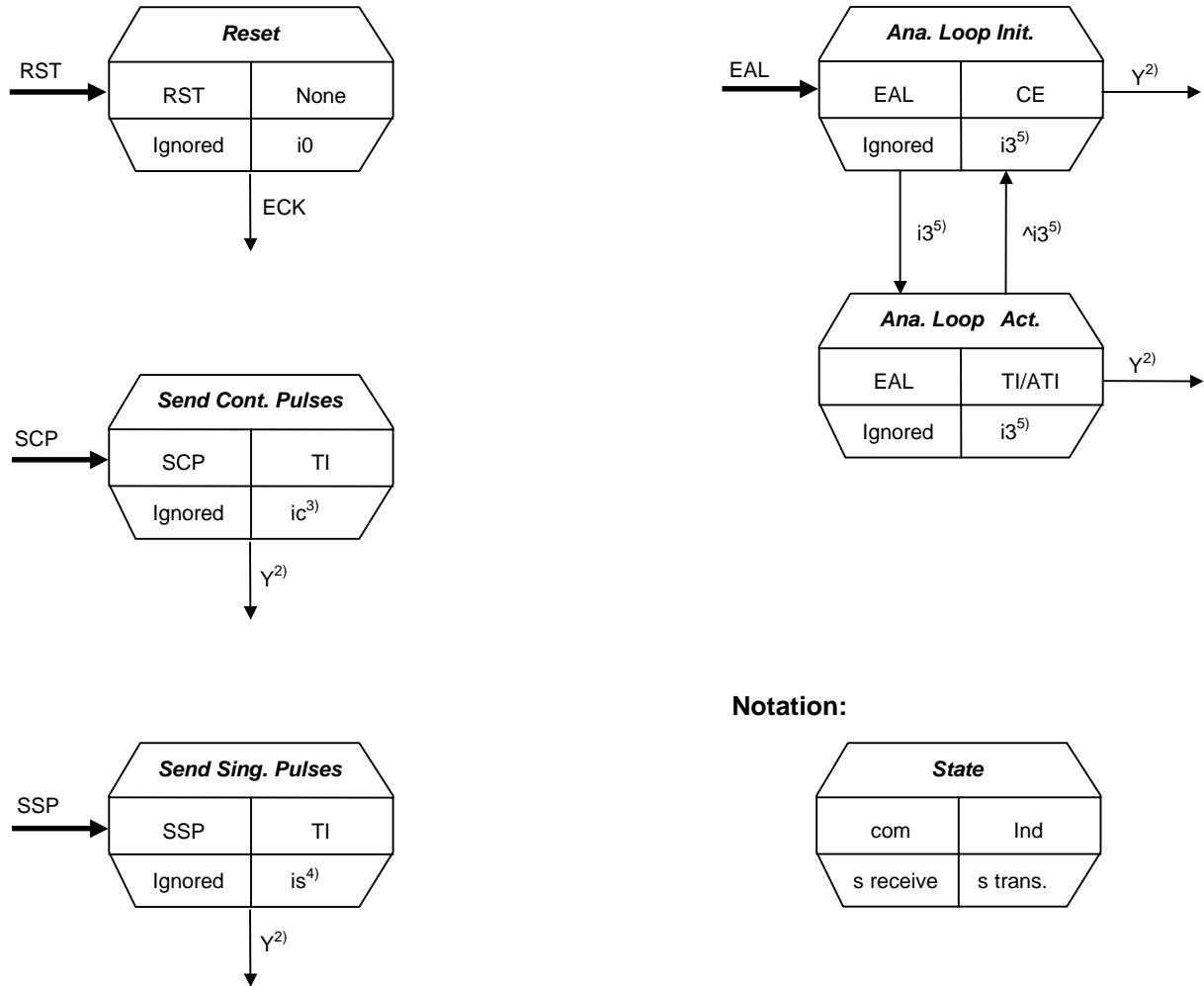

## 7.2.3.2 State Transition Diagrams in TE/LT-T

The followings are the state transition diagrams, which implement the activation/deactivation state matrix in I.430 (TABLE 5/I.430). The "command" and "s receive" entries in each state octagon keep the state, the "indication" and "s transmit" entries in each state octagon are the state outputs. For example, at "F3 Deactivated with clock" state, the layer 1 will stay at this state if the command is "ECK" and the INFO 0 is received on S interface. At this state, it provides "CE" indication to the microprocessor and transmits INFO 0 on S interface. The "AR8/10" command causes transition to F4 and non-INFO 0 signal causes transition to F5. Note that the command code written by the microprocessor in CIX register and indication code written by layer 1 in CIR register are transmitted repeatedly until a new code is written.

### Notation:

| State     |          |

|-----------|----------|

| com       | Ind      |

| s receive | s trans. |

### Note :

1. " $\wedge RST$ " means "NOT layer 1 reset command".

2. "Any" means any signal other than  $i0$ , which has not yet been determined.

3. " $\wedge i0$ " means any signal other than  $i0$  Fig.7.5 layer 1 activation/deactivation state diagram - normal mode

Fig.7.5 layer 1 activation/deactivation state diagram – TE/LT-T normal mode

# Preliminary W6691

## Note :

1. RST can be issued at any state, while SCP, SCZ and EAL can be issued only at F3 or F7.

2. Y is one of the commands : ECK, DRC, RST.

3. Continuous pulses at 96 kHz.

4. Isolated pulses at 2 kHz.

5. The INFO 3 is transmitted internally only.

Fig.7.6 layer 1 activation/deactivation state diagram – TE/LT-T SPECIAL mode

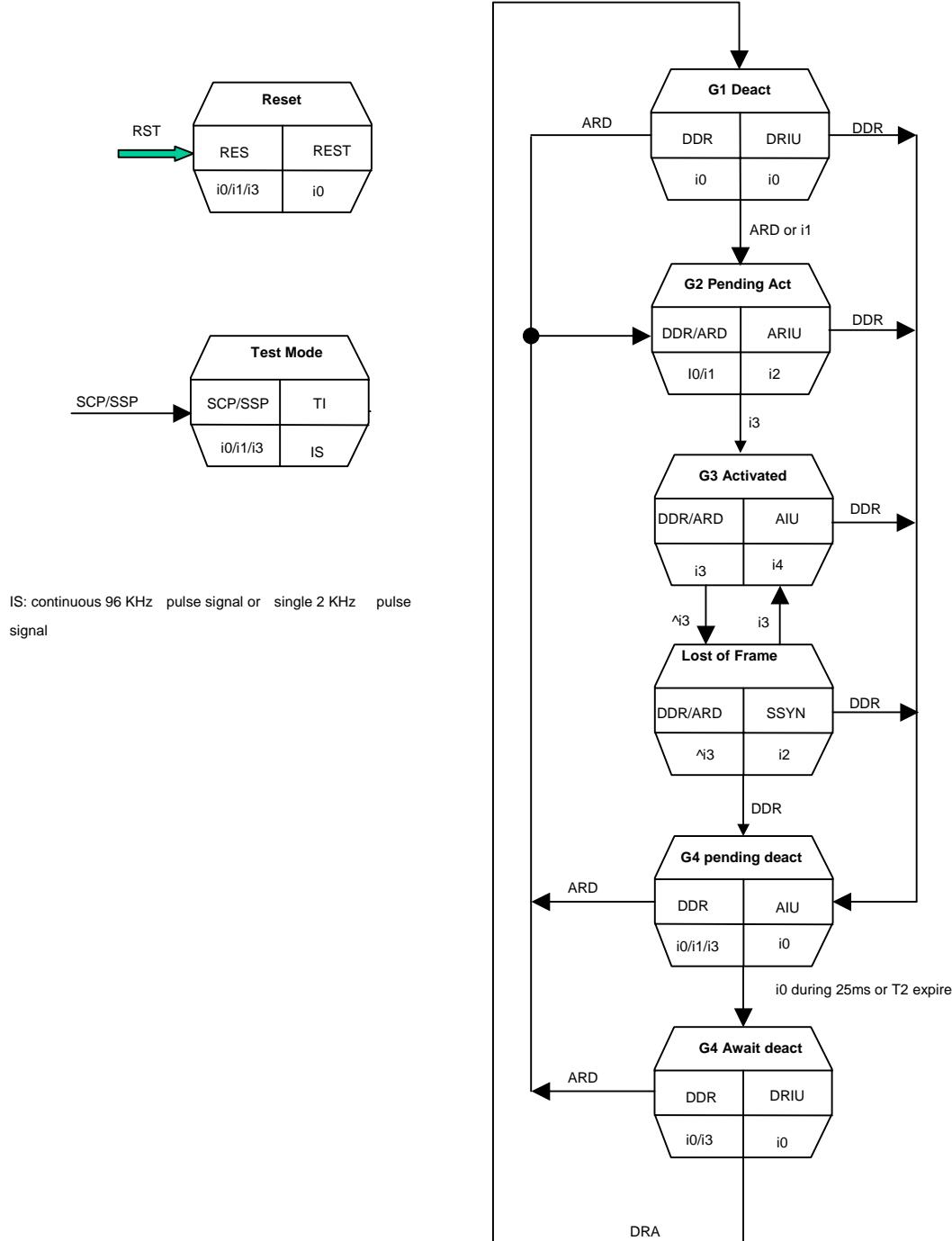

## 7.2.4 Layer 1 Activation /Deactivation in LT-S Mode

### 7.2.4.1 States Descriptions and Command/Indication Codes in LT-S Mode

G1 Deactivated

No any signal is detected on S interface and No any activation command is received in the C/I channel.

G2 Pending Activation

IF INFO1 IS DETECTED ON S INTERFACE OR AN ARD COMMAND IS RECEIVED FROM LAYER2 ,THE W6691 START TO TRANSMIT INFO2. W6691 IS WAITING FOR RECEIVING INFO3 FROM S INTERFACE. INFO2 IS SENT FROM W6691.

G3 ACTIVATED

W6691 RECEIVES INFO3 ,THEN, IT ENTERS G3 ACTIVATED STATE. THE INFO4 IS TRANSMITTED IN THIS STATE. WHEN THE SYNCHRONIZATION IS LOST, W6691 SWITCH TO TRANSMIT INFO2 INSTEAD OF INFO4 AND WAIT FOR RECEIVING INFO3 TO GET SYNCHRONIZATION AGAIN.

G4 PENDING DEACTIVATION

This state is requested by DDR (deactivate request). If INFO0 is received during 16ms or an internal timer2 expiration, the layer1 responses DRIU indication for Layer2.

G4 Await Deactivated

The W6691 stays in this state and waits for DRIU report from layer2. If W6691 receives DRA command from layer2, it enters G1 state.

Test Mode Continuous Pulses

Continuous alternating 96 KHz pulses are sent.

Test Mode Single Pulses

# Preliminary W6691

Single alternating 2KHz pulses are sent.

**TABLE 7.4 LAYER 1 COMMAND CODES**

| Command                     | Symbol | Code | Description                                                                      |

|-----------------------------|--------|------|----------------------------------------------------------------------------------|

| Deactivate down request     | DDR    | 0000 | Deactive Layer1 and disable internal clocks                                      |

| Send continuous pulses      | SCP    | 0011 | Send continuous pulses at 96 kHz                                                 |

| Send single pulses          | SSP    | 0010 | Send isolated pulses at 2 kHz                                                    |

| Activate request downstream | ARD    | 1000 | Request Layer1 activate Info2/Info4 sent                                         |

| Deactivate request assure   | DRA    | 1111 | Layer2 reponses Deactivate acknowledgement to make sure Layer1 can be deactivate |

| RESET                       | RST    | 0001 | Initialize to G4 or G1 state                                                     |

**TABLE 7.5 LAYER 1 INDICATION CODES**

| Indication                             | Symbol | Code | Descriptions                                                                           |

|----------------------------------------|--------|------|----------------------------------------------------------------------------------------|

| Signal synchronize                     | SSYU   | 0100 | Received signal is not Info3 and try to re-synchronize again                           |

| Activate request Indication upstream   | ARIU   | 1000 | the INFO 1 signal detected is responded to Layer2.                                     |

| Activate indication upstream           | AIU    | 1100 | Synchronous receiver                                                                   |

| Deactivate request indication upstream | DRIU   | 1111 | 1. Timer2 expired<br>2. info 0 received during 25ms after deactivation request command |

| RESET Indication                       | RSTI   | 0001 | Reset state indication                                                                 |

| Test Indication                        | TI     | 0000 |                                                                                        |

## 7.2.4.2 States Transition Diagram in LT-S Mode

Fig.7.7 layer 1 activation/deactivation state diagram in LT-S

## 7.2.5 D Channel Access Control

The D channel access control includes collision detection and priority management. The collision detection is always enabled. The priority management procedure as specified in ITU-T I.430 is fully implemented in W6691.

A collision is detected if the transmitted D bit and the received echo bit do not match. When this occurs, D channel transmission is immediately stopped, and the echo channel is monitored to attempt the next D channel access.

There are two priority classes: class 1 and class 2. Within each class, there are normal and lower priority levels.

**TABLE 7.8 D PRIORITY CLASSES**

|                  | Normal level | Lower level |

|------------------|--------------|-------------|

| Priority class 1 | 8            | 9           |

| Priority class 2 | 10           | 11          |

The selection of priority class is via the AR8/AR10 command. The following table summarizes the commands/indications used for setting the priority classes:

**TABLE 7.9 D PRIORITY COMMANDS/INDICATIONS**

| Command                              | Symbol | Code    | Remarks                                          |

|--------------------------------------|--------|---------|--------------------------------------------------|

| Activate request, set priority 8     | AR8    | 1000    | Activation command, set D channel priority to 8  |

| Activate request, set priority 10    | AR10   | 1001    | Activation command, set D channel priority to 10 |

| Indication                           | Abbr.  | Remarks |                                                  |

| Activate indication with priority 8  | AI8    | 1100    | Info 4 received, D channel priority is 8 or 9    |

| Activate indication with priority 10 | AI10   | 1101    | Info 4 received, D channel priority is 10 or 11  |

## 7.2.6 Frame Alignment

The following sections describe the behavior of W6691 in respect to the CTS-2 conformance test procedures for frame alignment. Please refer to ETSI-TM3 Appendix B1 for detailed descriptions.

### 7.2.6.1 FAinfA\_1fr

This test checks if TE does not lose frame alignment on receipt of one bad frame. The pattern for the bad frame is defined as IX\_96 kHz. This pattern consists of alternating pulses at 96 kHz during the whole frame.

| Device | Settings | Result |

|--------|----------|--------|

| W6691  | None     | Pass   |

### 7.2.6.2 FAinfB\_1fr

This test checks if TE does not lose frame alignment on receipt of one IX\_I4noflag frame which has no framing and balancing bit.

| Device | Settings | Result |

|--------|----------|--------|

| W6691  | None     | Pass   |

### 7.2.6.3 FAinfD\_1fr

This test checks if TE does not lose frame alignment on receipt of one IX\_I4viol16 frame. The IX\_I4viol16 frame remains at binary "1" until the first B2 bit which is bit position 16. The pulse sequences are: Framing bit, balancing bit, B2 bit, M bit, S bit, balancing bit. The TE should reflect the received  $F_A$  bit ( $F_A=1$ ) in the transmitted frame.

| Device | Settings | Result |

|--------|----------|--------|

| W6691  | None     | Pass   |

# Preliminary W6691

## 7.2.7.4 FAinfA\_kfr

This is to test the number k of IX\_96 kHz frames necessary for loss of frame alignment.

| Device | Settings | Result |

|--------|----------|--------|

| W6691  | k =2     | Pass   |

## 7.2.6.5 FAinfB\_kfr

This is to test the number k of IX\_I4noflag frames necessary for loss of frame alignment.

| Device | Settings | Result |

|--------|----------|--------|

| W6691  | k =2     | Pass   |

## 7.2.6.6 FAinfD\_kfr

This is to test the number k of IX\_I4noflag frames necessary for loss of frame alignment.

| Device | Settings | Result |

|--------|----------|--------|

| W6691  | k = 2    | Pass   |

## 7.2.6.7 Faregain

This is to test the number m of good frames necessary for regain of frame alignment. The TE regains frame alignment at m+1 frame.

The W6691 achieves synchronization after 5 frames, i.e m=4.

| Device | Settings | Result |

|--------|----------|--------|

| W6691  | m = 4    | Pass   |

## 7.2.7 Multiframe Synchronization

As specified by ITU-T I.430, the Q bit is transmitted from TE to NT in the position normally occupied by the auxiliary framing bit ( $F_A$ ) in one frame out of 5, whereas the S bit is transmitted from NT to TE. The S and Q bit positions and multiframe structure are shown in Table 7.10.

The functions provided by W6691 are:

- Multiframe synchronization: Synchronization is achieved when the M bit pattern has been correctly received during 20 consecutive frames starting from frame number 1.

Note: Criterion for multiframe synchronization is not defined in I.430 Recommendation.

- S bits receive and detect: When synchronization is achieved, the four received S bits in frames 1,6,11,16 are stored as S1 to S4 in the SQR register respectively. A change in the received four bits (S1-4) is indicated by an interrupt.

- Multiframe synchronization monitoring: Multiframe synchronization is constantly monitored. The synchronization state is indicated by the MSYN bit in the SQR register.

- Q bits transmit and  $F_A$  mirroring: When multiframe synchronization is achieved, the four bits Q1-4 stored in the SQXR register are transmitted as the four Q bits ( $F_A$ -bit position) in frames 1,6,11 and 16. Otherwise the  $F_A$  bit transmitted is a mirror of the received  $F_A$ -bit. At loss of synchronization, the mirroring is resumed at the next  $F_A$ -bit.

- The multiframe synchronization can be disabled by setting MFD bit in the D\_MODE register.

- According to I.430 Recommendation, the S/Q channel can be used as operation and maintenance signalling channel. At transmitter, a S/Q code for a message shall be repeated at least six times or as many as necessary to obtain the desired response. At receiver, a message shall be considered received only when the proper codes are received three consecutive times.

# Preliminary W6691

**TABLE 7.10 MULTIFRAME STRUCTURE IN S/T INTERFACE**

| Frame Number | NT-to-TE<br>F <sub>A</sub> -bit position | NT-to-TE<br>M bit | NT-to-TE<br>S bit | TE-to-NT<br>F <sub>A</sub> -bit position |

|--------------|------------------------------------------|-------------------|-------------------|------------------------------------------|

| 1            | ONE                                      | ONE               | S1                | Q1                                       |

| 2            | ZERO                                     | ZERO              | ZERO              | ZERO                                     |

| 3            | ZERO                                     | ZERO              | ZERO              | ZERO                                     |

| 4            | ZERO                                     | ZERO              | ZERO              | ZERO                                     |

| 5            | ZERO                                     | ZERO              | ZERO              | ZERO                                     |

| 6            | ONE                                      | ZERO              | S2                | Q2                                       |

| 7            | ZERO                                     | ZERO              | ZERO              | ZERO                                     |

| 8            | ZERO                                     | ZERO              | ZERO              | ZERO                                     |

| 9            | ZERO                                     | ZERO              | ZERO              | ZERO                                     |

| 10           | ZERO                                     | ZERO              | ZERO              | ZERO                                     |

| 11           | ONE                                      | ZERO              | S3                | Q3                                       |

| 12           | ZERO                                     | ZERO              | ZERO              | ZERO                                     |

| 13           | ZERO                                     | ZERO              | ZERO              | ZERO                                     |

| 14           | ZERO                                     | ZERO              | ZERO              | ZERO                                     |

| 15           | ZERO                                     | ZERO              | ZERO              | ZERO                                     |

| 16           | ONE                                      | ZERO              | S4                | Q4                                       |

| 17           | ZERO                                     | ZERO              | ZERO              | ZERO                                     |

| 18           | ZERO                                     | ZERO              | ZERO              | ZERO                                     |

| 19           | ZERO                                     | ZERO              | ZERO              | ZERO                                     |

| 20           | ZERO                                     | ZERO              | ZERO              | ZERO                                     |

| 1            | ONE                                      | ONE               | S1                | Q1                                       |

| 2            | ZERO                                     | ZERO              | ZERO              | ZERO                                     |

| etc.         |                                          |                   |                   |                                          |

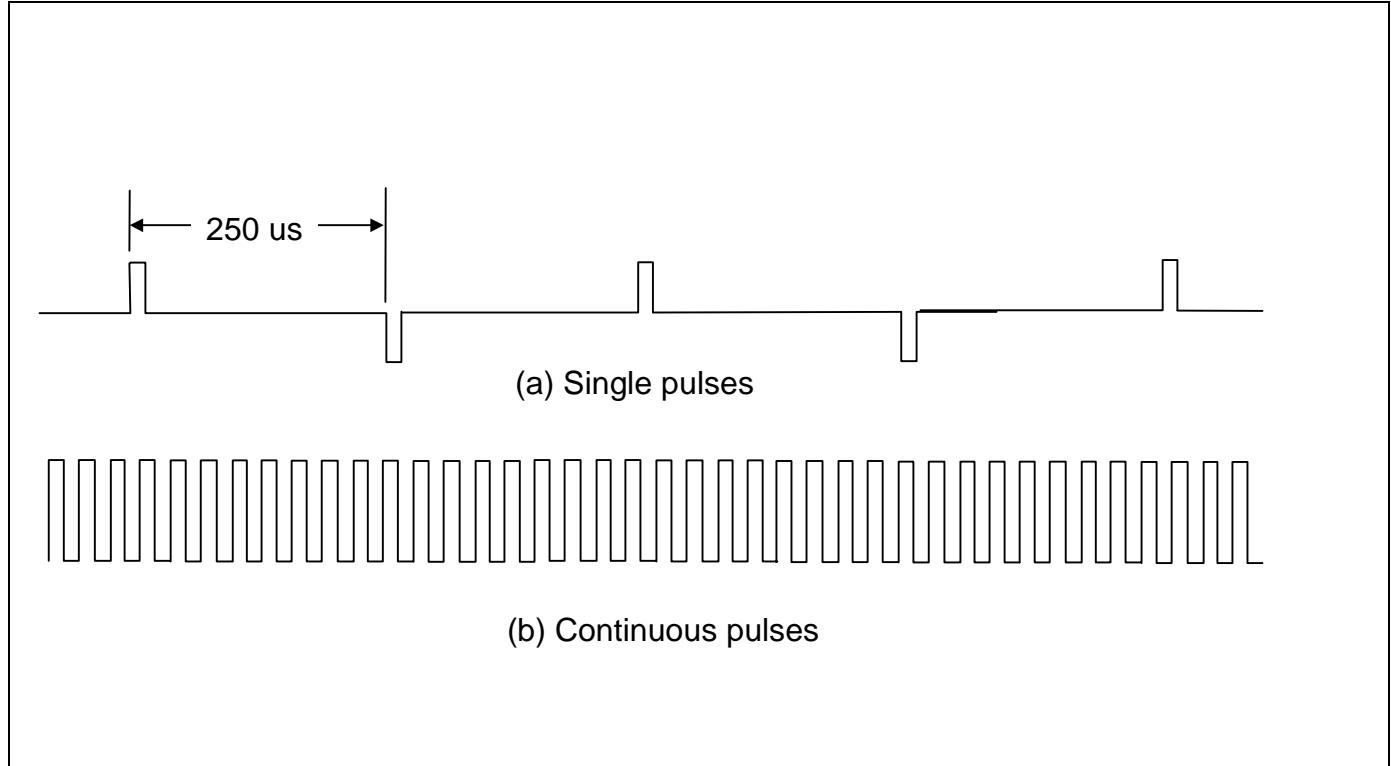

## 7.2.8 Test Functions

The W6691 provides loop and test functions as follows:

- Digital loop via DLP bit in D\_MODE register: In the layer 2 block, the transmitted 2B+D data are internally looped (from HDLC transmitter to HDLC receiver), and in the PCM ports, the transmitted B channels are internally looped (from PCM inputs to PCM outputs). The clock timings are generated internally and are independent of the S bus timing. This loop function is used for test of PCM and higher layer functions, excluding layer 1. After hardware reset, W6691 will power down if S bus is not connected or if there is no signal on the S bus. In this case, the C/I command ECK must be issued to power up the chip.

- Analog loop via the C/I command EAL: The analog S interface transmitter is internally connected to the S interface receiver. When the receiver has synchronized itself to the internal INFO 3 signal, the message "Test Indication" or "Awake Test Indication" is delivered to the CIR register. No signal is transmitted over the S interface.

In this mode, the S interface awake detector is enabled. Therefore if a level (INFO 2/ INFO 4) is detected on the S interface, this will be reported by the "Awake Test Indication (ATI)" indication.

- Remote loopback via RLP bit in D\_MODE register: The digital 2B data received from the S interface receiver is loopbacked to the S interface transmitter. The D channel is not looped. When RLP is enabled, layer 1 D channel is connected to HDLC port and DLP cannot be enabled.

- Transmission of special test signals via layer 1 command:

- \* Send Single Pulses (SSP): To send isolated single pulses of alternating polarity, with pulse width of one bit time, 250 us apart, with a repetition frequency of 2 kHz.

- \* Send Continuous Pulses (SCP): To send continuous pulses of alternating polarity, with pulse width of bit time. The repetition frequency is 96 kHz.

Fig.7.9 SSP and SCP test signals

### 7.3 B Channel Switching

W6691 provides five kinds of B channel switching function.

#### 1. PCM and GCI bus Switch (SFCTL : PGSWH) :

It determines the CODEC interface is to be operated in B channel.

1: PCM bus is selected to operate with CODEC.

0: GCI bus is selected to operate with CODEC.

#### 2. PCM Remote Loop Back (SFCTL : PCRLP)

Setting this bit activates the PCM channel remote loopback function. The transmitted PCM data to PCM channel are looped to received PCM channel.

#### 3. PXC PCM Cross-connect (SCFT : PXC)

This bit determines whether or not the PCM ports are cross-connected with the B channel ports. The setting of PXC is independent of the BSW1-0 bits.

| PXC | Connection           |

|-----|----------------------|

| 0   | PCM1 ↔ B1, PCM2 ↔ B2 |

| 1   | PCM1 ↔ B2, PCM2 ↔ B1 |

#### 4. B2SW1 / B2SW0 B2 channel Switch

These two bits determine B2 channel switch among PCM port , Layer1/GCI and Layer2.

00: Select B2 channel switch between Layer2 and Layer1/GCI.

01: Select B2 channel switch between Layer1/GCI and PCM.

10: Select B2 channel switch between PCM and Layer2.

#### 5. B1SW1 / B1SW0 B1 channel Switch

These two bits determine B1 channel switch among PCM port , Layer1/GCI and Layer2.

00: Select B1 channel switch between Layer2 and Layer1/GCI.

01: Select B1 channel switch between Layer1/GCI and PCM.

10: Select B1 channel switch between PCM and Layer2.

## 7.4 PCM Port

There are two PCM ports in W6691. Data is valid when respective PFCK is HIGH. The frame synchronization clocks (PFCK1-2) are 8 kHz and the bit synchronization clock (PBCK) is 1.536 MHz.

## 7.5 D Channel HDLC Controller

There are two HDLC protocols that are used for ISDN layer 2 functions : LAPD and LAPB. Their frame formats are shown below.

# Preliminary W6691

## LAPB modulo 8 :

|                   |                     |                     |                                |                   |                   |

|-------------------|---------------------|---------------------|--------------------------------|-------------------|-------------------|

| flag<br>(1 octet) | address<br>(1octet) | control<br>(1octet) | information<br>(0 or N octets) | FCS<br>(2 octets) | flag<br>(1 octet) |

|-------------------|---------------------|---------------------|--------------------------------|-------------------|-------------------|

| Control field bits | 7 | 6 | 5    | 4   | 3 | 2    | 1 | 0 |

|--------------------|---|---|------|-----|---|------|---|---|

| I frame            |   |   | N(R) | P   |   | N(S) |   | 0 |

| S frame            |   |   | N(R) | P/F | S | S    | 0 | 1 |

| U frame            | M | M | M    | P/F | M | M    | 1 | 1 |

## LAPB modulo 128 :

|                   |                     |                               |                                |                   |                   |

|-------------------|---------------------|-------------------------------|--------------------------------|-------------------|-------------------|

| flag<br>(1 octet) | address<br>(1octet) | control<br>(1 or 2<br>octets) | information<br>(0 or N octets) | FCS<br>(2 octets) | flag<br>(1 octet) |

|-------------------|---------------------|-------------------------------|--------------------------------|-------------------|-------------------|

| Control field bits | 1st octet |   |   |      |   |   |   |   | 2nd octet |   |      |   |     |   |   |   |

|--------------------|-----------|---|---|------|---|---|---|---|-----------|---|------|---|-----|---|---|---|

|                    | 7         | 6 | 5 | 4    | 3 | 2 | 1 | 0 | 7         | 6 | 5    | 4 | 3   | 2 | 1 | 0 |

| I frame            |           |   |   | N(S) |   |   | 0 |   |           |   | N(R) |   | P   |   |   |   |

| S frame            | X         | X | X | X    | S | S | 0 | 1 |           |   | N(R) |   | P/F |   |   |   |