## 8 V to 48 V fully programmable universal electronic fuse

## Maturity status link

STEF01

| Device summary |               |  |  |

|----------------|---------------|--|--|

| Order code     | STEF01FTR     |  |  |

| Package        | HTSSOP14      |  |  |

| Packing        | Tape and reel |  |  |

#### **Features**

- Operating input voltage range: 8 to 48 V

- Absolute maximum input voltage: 55 V

- Continuous current typ.: 4 A

- N-channel on-resistance typ.: 30 mΩ

- Enable/fault functions

- Output clamp voltage: adjustable from 10 to 52 V

- Programmable undervoltage lockout

- · Short-circuit current limit

- Programmable overload current limit

- Adjustable soft-start time

- Latch or auto-retry thermal protection

- Maximum allowable power protection

- Power Good

- Drives an optional external reverse current protection MOSFET

- Operating junction temperature -40 °C to 125 °C

- HTSSOP14 package

- UL2367 Recognized File N. E468771

- IEC 62368-1 CB certified

### **Applications**

- · Hot board insertion

- Electronic circuit breaker/power busing

- Industrial/alarm/lighting systems

- Distributed power systems

- Telecom power modules

### **Description**

The STEF01 is a universal integrated electronic fuse optimized for monitoring output current and the input voltage on DC power lines.

When connected in series to the main power rail, it is able to detect and react to overcurrent and overvoltage conditions. When an overload condition occurs, the device limits the output current to a safe value defined by the user. If the anomalous overload condition persists, the device goes into an open state, disconnecting the load from the power supply.

The device is fully programmable. UVLO, overvoltage clamp and start-up time can be set by means of external components.

The adjustable turn-on time is useful to keep the in-rush current under control during startup and hot-swap operations. The device provides either thermal latch and autoretry protection modes, which are selectable by means of a dedicated pin.

The STEF01 provides a gate driver pin for an external power MOSFET to implement a reverse-current blocking circuit. The intervention of the thermal protection is signaled to the board monitoring circuits through a signal on the fault pin.

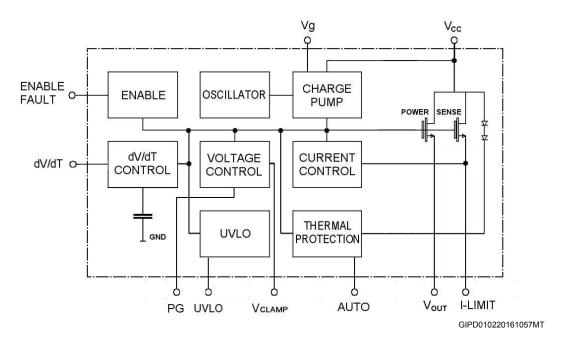

# Device block diagram

Figure 1. Block diagram

DS12147 - Rev 8 page 2/27

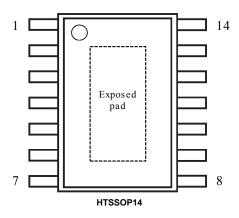

# Pin configuration

Figure 2. Pin configuration (top view)

GIPD010220161207MT

**Table 1. Pin description**

| Pin n°      | Symbol           | Note                                                                                                                                                                                                                                                                                                    |  |

|-------------|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 1           | UVLO             | A resistor divider connected between this pin, Vcc and GND sets the UVLO threshold. If left floating the UVLO is preset to 14.5 V.                                                                                                                                                                      |  |

| 2           | dv/dt            | The internal dv/dt circuit controls the slew rate of the output voltage at turn-on. The internal capacitor allows a ramp-up time of around 3 ms. An external capacitor can be added to this pin to increase the ramp-up time. If an additional capacitor is not required, this pin should be left open. |  |

| 3           | GND              | Ground pin.                                                                                                                                                                                                                                                                                             |  |

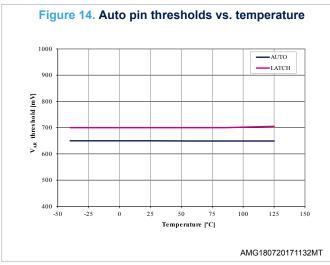

| 4           | Auto             | This pin selects the thermal protection behavior. The device is set in latched mode when this pin is left floating or connected to a voltage higher than 1 V.                                                                                                                                           |  |

|             |                  | It is set in auto-retry mode when the pin is connected to GND.                                                                                                                                                                                                                                          |  |

| 5           | Vclamp           | A resistor divider connected between this pin, $V_{OUT}$ and GND sets the overvoltag clamp level. If left floating the clamp is preset to 28 V.                                                                                                                                                         |  |

| 6, 7, 8, 9  | V <sub>OUT</sub> | Output port. All the pins must be tied together with short copper tracks.                                                                                                                                                                                                                               |  |

| 10          | I-Limit          | A resistor between this pin and V <sub>OUT</sub> sets the overload current limit level.                                                                                                                                                                                                                 |  |

| 11          | Vg               | Gate driver output for the optional external reverse-blocking MOSFET.                                                                                                                                                                                                                                   |  |

|             |                  | Tri-state, bi-directional pin. During normal operation the pin must be left floating, or it can be used to disable the output of the device by pulling it to ground using an open drain or open collector device.                                                                                       |  |

| 12          | 12 En/Fault      | If a thermal fault occurs, the voltage on this pin will go to an intermediate state to signal a monitoring circuit that the device is in thermal shutdown. It can be connected to another device of this family to cause a simultaneous shutdown during thermal events.                                 |  |

| 13          | PG               | Power Good flag. It is an open drain, to be pulled up through an external resistor.                                                                                                                                                                                                                     |  |

| 14          | V <sub>CC</sub>  | Input port. Connect this pin to the exposed pad.                                                                                                                                                                                                                                                        |  |

| Exposed pad | V <sub>CC</sub>  | Exposed pad. Input port of the device, internally connected to the power element drain.                                                                                                                                                                                                                 |  |

DS12147 - Rev 8 page 3/27

## 3 Maximum ratings

Table 2. Absolute maximum ratings

| Symbol                   | Parameter                         | Value                   | Unit |

|--------------------------|-----------------------------------|-------------------------|------|

| V <sub>CC</sub>          | Positive power supply voltage     | -0.3 to 55              | V    |

| V <sub>OUT</sub> /source | Output voltage pin                | -0.3 to V <sub>CC</sub> | V    |

| I-Limit                  | Current sense resistor pin        | -0.3 to V <sub>CC</sub> | V    |

| I <sub>D</sub>           | Continuous current                | 6                       | Α    |

| PG                       | Power good flag pin               | -0.3 to V <sub>CC</sub> | V    |

| Vclamp, UVLO             | Vclamp, UVLO pins                 | -0.3 to 7               | V    |

| En/Fault                 | Enable/Fault pin                  | -0.3 to 7               | V    |

| dv/dt                    | Startup time selection pin        | -0.3 to 7               | V    |

| Auto                     | Auto retry selection pin          | -0.3 to 7               | V    |

| Vg                       | Gate driver pin                   | -0.3 to 65              | V    |

| T <sub>J</sub>           | Maximum junction temperature (1)  | 150                     | °C   |

| T <sub>STG</sub>         | Storage temperature range         | -65 to 150              | °C   |

| T <sub>LEAD</sub>        | Lead temperature (soldering) 10 s | 260                     | °C   |

<sup>1.</sup> The thermal limit is set above the maximum thermal rating. It is not recommended to operate the device at temperatures greater than the maximum ratings for extended periods of time.

Note:

Absolute maximum ratings are those values beyond which damage to the device may occur. Functional operation under these conditions is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

Table 3. Recommended operating condition

| Symbol             | Parameter                                     | Value      | Unit |

|--------------------|-----------------------------------------------|------------|------|

| V <sub>CC</sub>    | Operating power supply voltage, steady state  |            | V    |

| ▼CC                | Maximum power supply voltage, clamping active | 52         | V    |

| R <sub>Limit</sub> | Current sense resistor range (1)              | 8 to 1000  | Ω    |

| I <sub>D</sub>     | Continuous current                            | 4          | Α    |

| TJ                 | Operating junction temperature                | -40 to 125 | °C   |

<sup>1.</sup> Important: The R<sub>Limit</sub> resistor is mandatory in the application. Very low values of the R<sub>Limit</sub> or lack of connection of R<sub>Limit</sub> may lead to malfunction of current limiting circuit and to device damage.

Table 4. Thermal data

| Symbol            | Parameter                                        | HTSSOP14 | Unit |

|-------------------|--------------------------------------------------|----------|------|

| D                 | Thermal resistance junction-ambient, 2 layer PCB | 140      | °C/W |

| R <sub>thJA</sub> | Thermal resistance junction-ambient, 4 layer PCB | 40       | C/VV |

| R <sub>thJC</sub> | Thermal resistance junction-case                 | 4        | °C/W |

DS12147 - Rev 8 page 4/27

### **Table 5. ESD performance**

| Symbol                     | Parameter                  | Test conditions | Value | Unit |

|----------------------------|----------------------------|-----------------|-------|------|

| ESD ESD protection voltage | НВМ                        | 2               | kV    |      |

| LSD                        | ESD ESD protection voltage | CDM             | 500   | V    |

DS12147 - Rev 8 page 5/27

# 4 Electrical characteristics

$V_{CC}$  = 24 V,  $V_{EN}$  = floating,  $C_I$  = 10  $\mu$ F,  $C_O$  = 47  $\mu$ F,  $T_J$  = 25  $^{\circ}C$  (unless otherwise specified).

Table 6. Electrical characteristics for STEF01

| Symbol                         | Parameter                                                | Test conditions                                                                       | Min.                      | Тур. | Max. | Unit  |

|--------------------------------|----------------------------------------------------------|---------------------------------------------------------------------------------------|---------------------------|------|------|-------|

| Under/ov                       | er voltage protection                                    |                                                                                       |                           |      |      |       |

|                                | Output clamping voltage                                  | V <sub>2.2</sub> = 36 V <sub>2</sub> V <sub>2.2</sub> = floating                      |                           | 28   |      | V     |

| $V_{Clamp}$                    | Accuracy                                                 | V <sub>CC</sub> = 36 V, V <sub>Clamp</sub> = floating                                 | -5                        |      | +5   | %     |

| Siamp                          | Output clamping voltage range                            | With external resistor divider on Vclamp pin                                          | 10                        |      | 52   | V     |

| V                              | Under voltage lockout threshold                          | Turn on, voltage going up, UVLO = floating                                            | 13                        | 14.5 | 16   | V     |

| V <sub>ON</sub>                | Under voltage lockout range                              | With external resistor divider on UVLO pin                                            | 8                         |      | 45   | V     |

| V <sub>Hyst</sub>              | UVLO hysteresis                                          |                                                                                       |                           | 10   |      | %     |

| Power MC                       | OSFET                                                    |                                                                                       |                           |      |      |       |

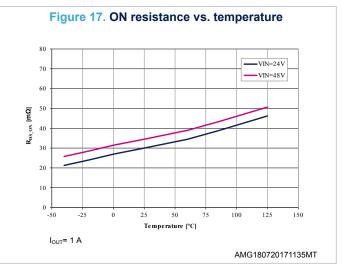

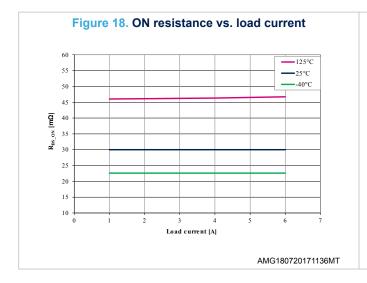

|                                |                                                          | I <sub>D</sub> = 1 A <sup>(1)</sup>                                                   |                           | 30   | 50   | _     |

| R <sub>DSon</sub>              | ON resistance                                            | -40 °C < T <sub>J</sub> < 125 °C <sup>(2)</sup>                                       |                           |      | 70   | mΩ    |

| V <sub>OFF</sub>               | Off state output voltage                                 | V <sub>CC</sub> = 36 V, V <sub>GS</sub> = 0, R <sub>L</sub> = infinite                |                           | 1    | 20   | mV    |

| Current li                     | mit                                                      |                                                                                       |                           |      |      |       |

| I <sub>Short</sub>             | Short circuit current limit                              | $R_{Limit}$ = 22 $\Omega$ , $V_{OUT}$ = gnd                                           |                           | 1.5  |      | Α     |

| I <sub>Lim</sub>               | Overload current limit                                   | $R_{Limit} = 22 \Omega$ , $V_{OUT} = V_{CC} - 2 V$ , $V_{CC} > 8 V$                   | 3.2                       | 4    | 4.8  | Α     |

| dv/dt circ                     | uit                                                      |                                                                                       |                           |      |      |       |

| dv/dt Output voltage ramp time | Enable to V <sub>OUT</sub> = 22 V, No C <sub>dv/dt</sub> |                                                                                       | 3                         |      |      |       |

|                                | Output voltage ramp time                                 | Enable to V <sub>OUT</sub> = 46 V, V <sub>CC</sub> = 48 V, V <sub>Clamp</sub> = 52 V, |                           |      |      | ms    |

|                                |                                                          | no C <sub>dv/dt</sub>                                                                 |                           | 3.6  |      |       |

| I <sub>dv/dt</sub>             | dv/dt source pin current                                 |                                                                                       |                           | 100  |      | nA    |

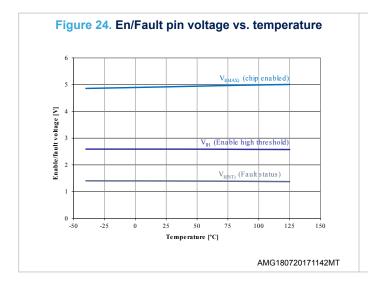

| Enable/Fa                      | ault                                                     |                                                                                       |                           |      |      |       |

| V <sub>IL</sub>                | Low level input voltage                                  | Output disabled                                                                       | 0                         |      | 0.4  | V     |

| V <sub>I(INT)</sub>            | Intermediate level input voltage                         | Thermal fault, output disabled                                                        |                           | 1.4  |      | V     |

| V <sub>IH</sub>                | High level input voltage                                 | Output enabled                                                                        | 2.8                       |      | 5    | V     |

| V <sub>I(MAX)</sub>            | High state maximum voltage                               | Pin floating                                                                          | 4.7                       | 5    | 5.3  | V     |

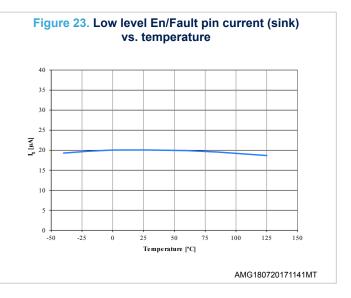

| I <sub>IL</sub>                | Low level input current (sink)                           | V <sub>Enable</sub> = 0 V                                                             | / <sub>Enable</sub> = 0 V |      | -40  | μA    |

|                                | Maximum fan-out for fault signal                         | Total number of chips that can be connected to this pin for simultaneous shutdown     |                           |      | 5    | Units |

| Power Go                       | ood                                                      |                                                                                       |                           |      |      |       |

| V <sub>D</sub>                 | Power Good output                                        | V <sub>CC</sub> - V <sub>OUT</sub> value for Power Good                               |                           | 1    |      | V     |

| • ט                            | threshold                                                | Hysteresis                                                                            |                           | 0.1  |      | v     |

| V <sub>L</sub>                 | Power Good output voltage low                            | I <sub>sink</sub> = 6 mA open drain output                                            |                           |      | 0.4  | V     |

|                                | -                                                        |                                                                                       | -                         |      |      |       |

DS12147 - Rev 8 page 6/27

| Symbol                                | Parameter                 | Test conditions                   | Min. | Тур. | Max. | Unit |

|---------------------------------------|---------------------------|-----------------------------------|------|------|------|------|

| External                              | MOS gate driver           |                                   | '    |      |      |      |

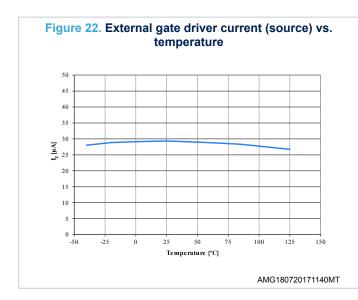

| lg                                    | Sourcing current          | Device on                         |      | 30   |      | μA   |

| R <sub>p</sub>                        | Strong pull down          | V <sub>EN</sub> = 0 V             |      | 450  |      | Ω    |

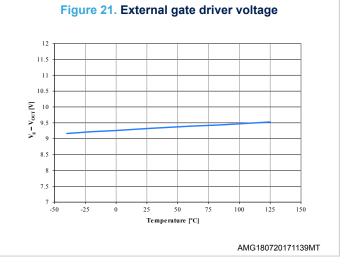

| Vg                                    | Gate driver voltage       | $V_g$ - $V_{OUT}$                 | 8.5  | 9.5  | 10.5 | V    |

| Auto-retr                             | y function                |                                   |      | ı    | ı    |      |

| V <sub>AR</sub> Autoretry logic level | Autorotmulonio lovol      | Auto-retry activated              |      |      | 0.4  | W    |

|                                       | Autoretry logic level     | Latched protection activated      | 1    |      |      | V    |

| Total dev                             | rice consumption          |                                   | '    | 1    |      |      |

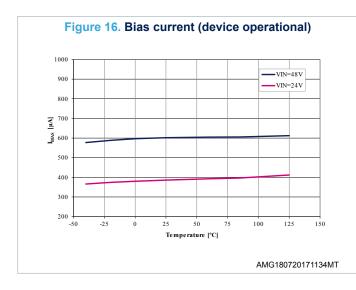

|                                       |                           | Device operational                |      | 0.4  |      |      |

| I <sub>Bias</sub>                     | Bias current              | Thermal shutdown (2)              |      | 0.1  |      | mA   |

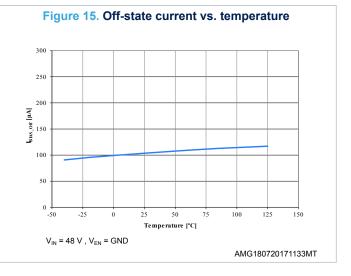

|                                       |                           | Off state (V <sub>EN</sub> = GND) |      | 0.1  |      |      |

| $V_{min}$                             | Minimum operating voltage |                                   |      |      | 8    | V    |

| Thermal                               | shutdown                  |                                   | '    |      |      |      |

| TCD                                   | Shutdown temperature (2)  |                                   |      | 175  |      | °C   |

| TSD Hysteresis                        |                           | Only in auto-retry mode           |      | 25   |      | C    |

<sup>1.</sup> Pulsed test.

DS12147 - Rev 8 page 7/27

<sup>2.</sup> Guaranteed by design, but not tested in production.

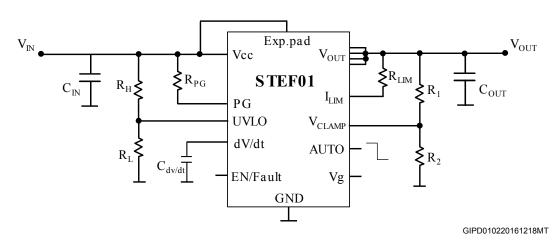

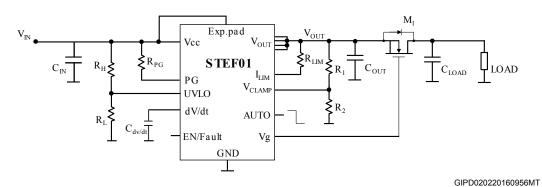

## 5 Typical application

Figure 3. Application circuit

## 5.1 Operating modes

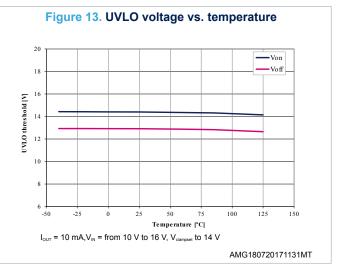

#### 5.1.1 Turn-on and UVLO

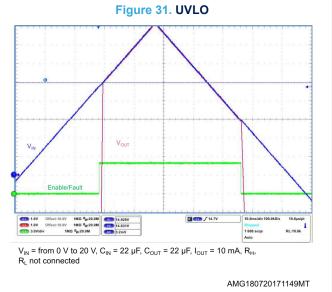

The device features a programmable UVLO block. If the input voltage exceeds the UVLO ON threshold (V<sub>ON</sub>), the power pass element is turned on and the Enable/Fault pin goes up to the high state.

Figure 4. UVLO block simplified diagram shows the simplified diagram of the UVLO circuit. The voltage at the UVLO pin is compared to an internal 1 V reference (0.9 V during turn OFF).

The default ON threshold is set by internal divider ( $R_{HD}$ ,  $R_{LD}$ ) to 14.5 V; the  $I_D$  current flowing through the internal divider is set to ~ 3  $\mu$ A.

The UVLO threshold can be modified in accordance with power rail needs by adding the R<sub>H</sub>-R<sub>L</sub> resistor divider, as shown in Figure 4. UVLO block simplified diagram. The external divider is in parallel with the internal default one, therefore the threshold can be changed within the 8 V to 45 V range.

$V_{IN}$   $V_{CC}$   $R_{HD}$  UVLO  $I_{D}$   $R_{LD}$   $V_{Ref}$

Figure 4. UVLO block simplified diagram

GIPD010220161241MT

When the external divider is used, the ratio between external current  $I_E$  and the internal current  $I_D$  should be kept as high as possible, to guarantee maximum linearity of the circuit with respect to temperature and process variations.

DS12147 - Rev 8 page 8/27

Setting  $I_E/I_D > 10$  provides sufficient UVLO linearity, at the same time keeping overall current consumption at acceptable levels. Given the desired  $V_{ON}$  threshold, for a fixed value of the lower resistor  $R_L$ , **Equation 1** can be used to calculate the upper resistor  $R_H$ .

#### **Equation 1**

$$R_{\rm H} = \frac{1}{\frac{(1/R_{\rm L} + 1/333)}{(V_{\rm ON} - 1)} - \frac{1}{4500}}$$

(resistor values are expressed in  $k\Omega$ )

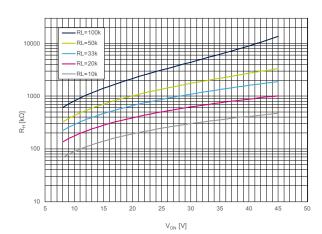

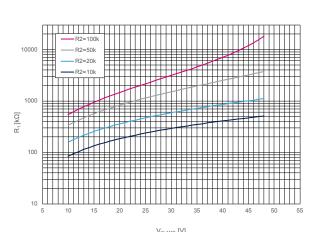

Figure 5. UVLO threshold ( $V_{ON}$ ) vs.  $R_H$ ,  $R_L$  shows the relationship between  $R_H$  and the UVLO turn ON threshold, for some fixed values of  $R_I$ .

Figure 5. UVLO threshold (VON) vs. RH, RL

The resistor divider approach described above guarantees the best UVLO performance in terms of accuracy and temperature dependance.

In order to reduce the application B.O.M., the 1-resistor approach can be used also, at the expenses of overall UVLO circuit accuracy.

In this case, the  $R_H$  resistor can be omitted for  $V_{ON}$  thresholds higher than 14.5 V, or  $R_L$  for  $V_{ON}$  lower than 14.5 V.

In any case it is recommended to check that in all operating conditions, the UVLO threshold is never lower than 8 V, in order to guarantee correct operation.

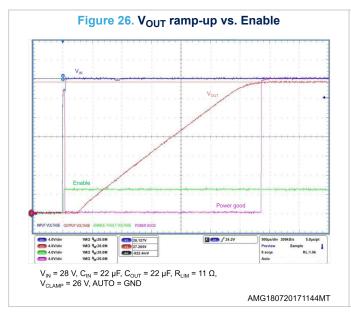

After an initial delay time of typically 170  $\mu$ s, the output voltage is supplied with a slope defined by the internal dv/dt circuitry. If no additional capacitor is connected to the dv/dt pin, the total time from the Enable signal going high and the output voltage reaching the nominal value is around 3 ms.

#### 5.1.2 Normal operating condition

The STEF01 E-fuse provides the circuitry on its output with the same voltage shown at its input, with a small voltage fall due to the N-channel MOSFET RDS-on.

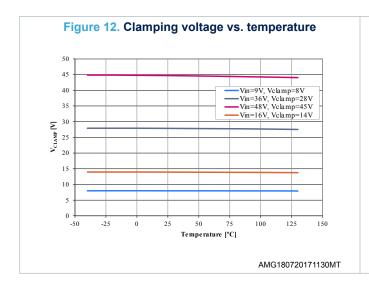

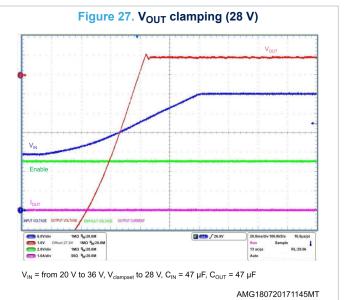

#### 5.1.3 Output voltage clamp

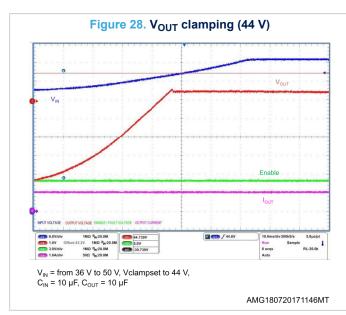

If the input voltage exceeds the  $V_{clamp}$  value, the internal protection circuit clamps the output voltage to  $V_{clamp}$ . The overvoltage clamp threshold is preset to 28 V if the  $V_{clamp}$  pin is left floating, otherwise it can be externally adjusted in the range of 10 to 52 V by connecting a resistor divider ( $R_1,R_2$ ) of appropriate value between the  $V_{clamp}$  pin,  $V_{OUT}$  and GND.

The setting procedure is similar to that of UVLO, the internal divider current being fixed to 10 µA.

Given the desired  $V_{clamp}$  threshold, for a fixed value of the lower resistor  $R_2$ , **Equation 2** can be used to calculate the upper resistor  $R_1$

DS12147 - Rev 8 page 9/27

#### **Equation 2**

$$R_1 = \frac{1}{\frac{(1/R_2 + 10^{-2})}{(V_{\text{clamp}} - 1)} - \frac{1}{2700}}$$

(resistor values are expressed in  $k\Omega$ )

Figure 6. Clamping voltage ( $V_{clamp}$ ) vs.  $R_1$ ,  $R_2$  shows the relation between  $R_1$  and the clamping voltage, for some fixed values of  $R_2$ .

Figure 6. Clamping voltage (V<sub>clamp</sub>) vs. R<sub>1</sub>, R<sub>2</sub>

#### 5.1.4 Current limit

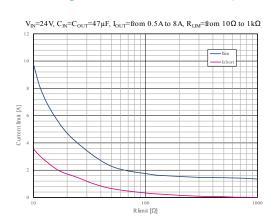

The STEF01 embeds an overcurrent sensing circuit, based on an internal N-channel Sense FET with a fixed ratio, used to monitor the output current (Figure 1. Block diagram).

The current limiting circuit responds to overcurrent events by reducing the conductivity of the power MOSFET, in order to clamp the output current at a safe value.

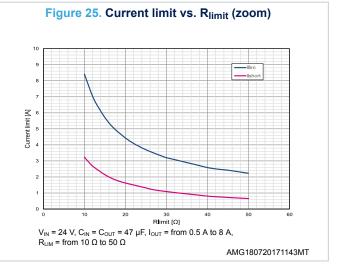

The overcurrent protection trip-point can be selected externally by means of the limiting resistor  $R_{Limit}$ , according to the graphs in Section 5.1.4 Current limit and Figure 25. Current limit vs.  $R_{limit}$  (zoom).

The circuit features two levels of current limitation, each one valid for a certain range of output voltage (V<sub>OUT</sub>).

In case of overload, when the input current surpasses the programmed overload current limit ( $I_{LIM}$ ), but the output voltage is still higher than 5.5 V (typ.), the device clamps the current to the  $I_{LIM}$  value.

If case of strong overload or short circuit, when the output voltage decreases to less than 3.5 V, the device enters the foldback current limit, with the current limited to a lower value ( $I_{SHORT}$ ) that is typically 1.5 A when  $R_{Limit}$  = 22  $\Omega$ .

DS12147 - Rev 8 page 10/27

Figure 7. Current limit vs. Rlimit

AMG180720171100MT

During startup, the foldback current limit is disabled and the current is limited by the overcurrent protection at the  $I_{LIM}$  value. Please refer also to Section 5.4 Maximum load at startup for more details.

It is important to note that the  $R_{Limit}$  is mandatory for the current limiting circuit to function properly. It is recommended to use  $R_{Limit}$  value according to Section 3 Maximum ratings and to the package power dissipation.

Important: very low values of R<sub>Limit</sub> or failure to connect it may lead to malfunctioning of the current limiting circuit and to device damage.

### 5.2 Protection circuits

Since the power dissipation can reach remarkable levels during startup into heavy capacitive loads, large load transients and short-circuit during operation at high voltage, the STEF01 is protected by means of two circuits: the absolute thermal protection and the maximum power dissipation protection.

### 5.2.1 Thermal protection

The thermal protection is a standard thermal shutdown feature, which acts when the die temperature exceeds the absolute shutdown threshold, set typically to 175  $^{\circ}$ C.

The behavior of the STEF01 at thermal protection intervention can be changed by the user through the external Auto pin. This pin is internally pulled up.

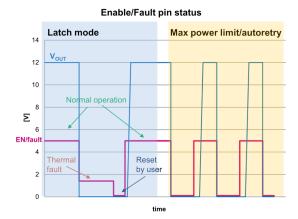

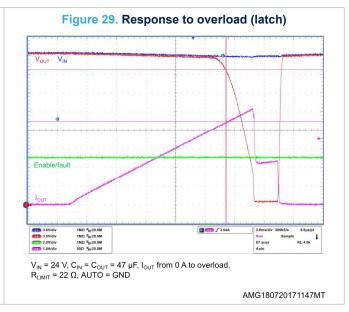

When the Auto pin is left floating or connected to a voltage higher than 1 V, the thermal protection works as latched. If the device temperature exceeds the thermal shutdown threshold, the thermal shutdown circuitry turns the power MOSFET off, disconnecting the load. The EN/Fault pin of the device will be automatically set at an intermediate voltage, typically 1.4 V, in order to signal the overtemperature event.

The E-fuse can be reset either by cycling the supply voltage or by pulling down the EN pin below the  $V_{IL}$  threshold and then releasing it.

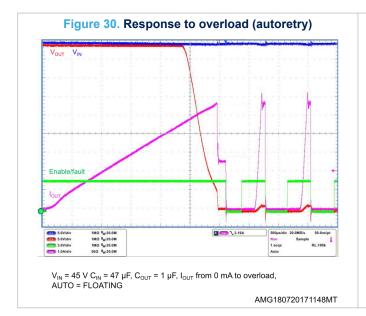

When the AUTO pin is connected to GND or to a voltage lower than 0.4 V, the thermal protection works as auto-retry. Once the thermal protection threshold is reached, the power is turned off and remains in an off state until the die temperature drops below the hysteresis value. Once this occurs, the internal auto-retry circuit initiates a new startup cycle, with controlled dv/dt. During the shutdown period, the EN/Fault pin of the device will be automatically set to 0 V.

#### 5.2.2 Maximum dissipated power protection

Besides the standard thermal shutdown described in Section 5.2.1 Thermal protection, which acts when the die temperature surpasses the absolute shutdown threshold, the STEF01 is equipped with advanced thermal protection, which limits the thermal power dissipated into the device. When the power dissipation is higher than the internal limit, the power transistor is turned off.

The power protection always acts in auto-retry mode, regardless of the Auto pin status. Its intervention is signaled on the EN/FAULT pin with a LOW logic state. If the fault persists, the die temperature may reach the thermal protection limit. If this happens, the device behavior is the one fixed by the user through the Auto pin signal.

The maximum dissipated power protection is able to protect the device from very fast overheating events, such as those caused by a short circuit on the output during operation.

DS12147 - Rev 8 page 11/27

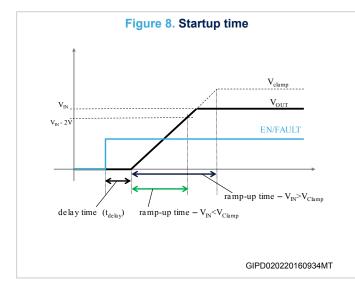

#### 5.3 Soft start function

The inrush current profile is controlled through a dedicated soft-start circuit. The startup time is set by default at 3 ms (typ.) and it can be prolonged by connecting a capacitor between the  $C_{dv/dt}$  pin and GND. Figure 8. Startup time illustrates the turn-on sequence.

The turn-on time is defined as the time interval  $t_{ON}$  between assertion of the enable signal and the Vout reaching the  $(V_{OUT(NOM)}-2\ V)$  voltage. The turn-on time is a function of the  $C_{dv/dt}$  capacitor, the input voltage  $V_{CC}$  and the clamping voltage  $V_{Clamp}$ .

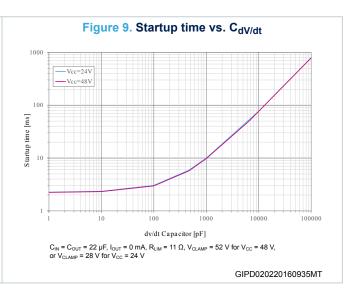

Given the  $C_{dv/dt}$  external capacitor value, the turn-on time can be estimated using **Equation 3** and the graph in Figure 9. Startup time vs.  $C_{dV/dt}$ , valid for normal operating conditions ( $V_{CC} < V_{Clamp}$ ). In case the startup occurs with power supply voltage higher than the clamping voltage ( $V_{CC} > V_{Clamp}$ ), the total startup time will be longer. The equation is meant as a theoretical aid in choosing the  $C_{dv/dt}$  capacitor, and does not take into account the capacitor tolerance, temperature and process variations.

#### **Equation 3**

$$t_{ON} = 0.952 \cdot \frac{V_{CC}}{V_{Clamp}} \cdot \frac{(300 + C_{dvdt})}{113000} + t_{delay}$$

where time is expressed in [s] and the capacitor in [pF]; tdelay  $\sim 170 \, \mu s$ , is the initial delay time.

#### 5.4 Maximum load at startup

The power limiting function described in Section 5.2.2 Maximum dissipated power protection is designed to provide fast and effective protection for the internal FET.

Depending on supply voltage and load, it is possible that during startup the power dissipation is such that the maximum power protection is triggered and the output is shut down before the startup is complete. The EN/Fault signal is set according to Table 7. Enable/Fault pin behavior during thermal protection events.

In case of strong capacitive loads, the total startup time may be longer than the programmed startup time, since it is dependent also on the limitation current, the output load and the output capacitance value. In such a situation, the foldback current limit could activate, so that the startup is longer or eventually interrupted by the intervention of thermal protection.

To avoid this occurrence, a longer startup time should be set by the appropriate selection of the C<sub>dv/dt</sub> capacitor.

### 5.5 Enable-fault pin

The Enable/Fault pin has the dual function of enabling/disabling the device and, at the same time, providing information about the device status to the application. The EN/Fault signal can be provided to a monitoring circuit to control the status of device.

It can be used as a standard Enable pin, (HI = enable, LO = disable) or connected to an external open-drain or open-collector device.

DS12147 - Rev 8 page 12/27

The EN/fault pin is internally pulled up to 5 V, therefore the device is enabled if the pin is left floating. In case of a thermal fault, the pin is pulled to an intermediate state, with a voltage of 1.4 V (typ.) (see Section 5.1.1 Turn-on and UVLO).

The EN/Fault signal can be directly connected to the Enable/Fault pins of other STEF01 devices on the same application in order to implement a simultaneous enable/disable feature.

When a thermal fault occurs, the latch version can be reset either by cycling the supply voltage or by pulling down the Enable pin below the  $V_{IL}$  threshold and then releasing it.

In the auto-retry operating mode, the power MOSFET remains in an off state until the die temperature drops below the hysteresis value. The EN/Fault pin is set to a low logic level and the auto-retry circuit attempts to restart the device with soft start.

In case of power limit intervention, the EN/Fault pin is set to low logic level also. The following truth table and the graph in Figure 10. Enable/Fault pin status summarize the device behavior and the EN/Fault signal in all conditions.

| Auto pin logic level | Thermal protection status | Maximum power protection status | EN/Fault pin status | Output voltage |

|----------------------|---------------------------|---------------------------------|---------------------|----------------|

| High                 | 0                         | 0                               | 5 V                 | ON             |

| High                 | 1                         | X                               | 1.4 V               | OFF            |

| High                 | 0                         | 1                               | 0 V                 | OFF            |

| Low                  | 0                         | 0                               | 5 V                 | ON             |

| Low                  | 1                         | X                               | 0 V                 | OFF            |

| Low                  | 0                         | 1                               | 0 V                 | OFF            |

Table 7. Enable/Fault pin behavior during thermal protection events

Note:

Maximum power protection always auto-retries (see Section 5.2.2 Maximum dissipated power protection).

Figure 10. Enable/Fault pin status

GIPD020220160952MT

#### 5.6 Power Good function

Most applications require a flag showing that the output voltage is in the correct range. This function is achieved through the Power Good (PG) pin. The Power Good function on the STEF01 is accomplished by monitoring the voltage drop on the power pass element,  $V_d = V_{CC}-V_{OUT}$ .

Whenever the  $V_D$  is lower than 1 V, the PG pin is in high impedance. If  $V_D$  is higher than 1 V, the PG pin goes to low impedance; therefore if either the device is functioning well or the EN pin is in low state, the PG pin is at high impedance.

The PG pin is an open drain pin, so it requires an external pull-up resistor, which must be connected between the PG pin and the desired high level voltage reference. The typical current capability of the PG pin is up to 6 mA. If the Power Good function is not used, the PG pin must remain floating.

DS12147 - Rev 8 page 13/27

### 5.7 Gate driver for reverse current blocking FET

Many applications require reverse current blocking (from load to input source) to permit the completion of important system activities or writing data to non-volatile memory prior to power down or during brownout. The STEF01 provides a  $V_g$  pin suitable to control an external blocking N-channel FET, connected back-to-back with the internal one, as shown in Figure 11. STEF01 with external reverse blocking FET.

Figure 11. STEF01 with external reverse blocking FET

As  $V_{IN}$  drops during input power removal, the internal logic pulls the gate of the external MOSFET down, therefore both the internal pass element and the external MOSFET are turned off, blocking any current flow from the load to the power supply. In this case, the  $C_{LOAD}$  value is chosen according to the charge needed to complete the required operations.

The typical sourcing current of the Vg driver is 30  $\mu$ A, with a voltage of 10 V compared to V<sub>OUT</sub>. Therefore, when a low threshold MOSFET is used, the V<sub>q</sub> must be clamped by means of a suitable external clamping diode.

When the EN pin is low, the external M1 FET is kept off by a 40  $\Omega$  internal pull-down so that the device is disabled by the user or by internal protection circuits.

### 5.8 External capacitors and application suggestions

Input and output capacitors are mandatory to guarantee device control loop stability and reduce the transient effects of stray inductances which may be present on the input and output power paths. In fact, when the STEF01 interrupts the current flow, input inductance generates a positive voltage spike on the input, and output inductance generates a negative voltage spike on the output. To reduce the effects of such transients, a  $C_{IN}$  capacitor of at least 10  $\mu$ F must be connected between the input pin and GND, and located as close as possible to the device. For the same reason, a  $C_{OLIT}$  capacitor of at least 47  $\mu$ F must be connected at the output port.

In the event of a voltage clamp, with certain combinations of parasitic elements on the application, some small oscillations may be visible on the output voltage. This phenomenon does not affect device operation and can be mitigated by using an electrolytic capacitor for the C<sub>IN</sub>.

When the device is powered via a power line made up of very long wires, where input inductance is higher than  $3-4 \mu H$ , the input capacitor should be increased to  $47 \mu F$  or more.

Additional protections and methods for addressing these transients are:

- Minimizing inductance of the input and output tracks

- TVS diodes on the input to absorb inductive spikes

- Schottky diode on the output to absorb negative spikes

- Combination of ceramic and electrolytic capacitors on the input and output

DS12147 - Rev 8 page 14/27

# 6 Typical performance characteristics

(The following plots are referred to the typical application circuit and, unless otherwise noted, at T<sub>A</sub> = 25 °C)

DS12147 - Rev 8 page 15/27

Figure 19. dv/dt pin current vs. temperature

140

130

120

100

90

80

70

60

-50

-25

0

25

50

75

100

125

150

Temperature [\*C]

Figure 20. External gate driver pull-down resistance

DS12147 - Rev 8 page 16/27

DS12147 - Rev 8 page 17/27

DS12147 - Rev 8 page 18/27

7256412

## 7 Package information

In order to meet environmental requirements, ST offers these devices in different grades of ECOPACK packages, depending on their level of environmental compliance. ECOPACK specifications, grade definitions and product status are available at: www.st.com. ECOPACK is an ST trademark.

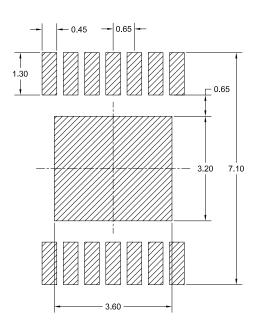

## 7.1 HTSSOP14 package information

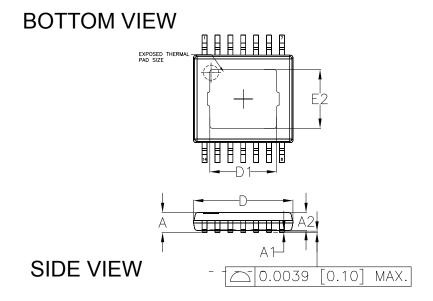

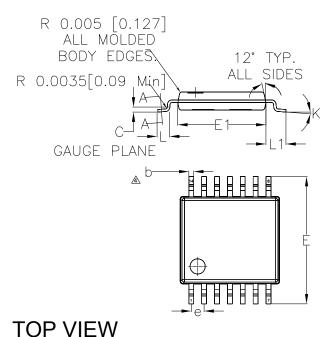

Figure 34. HTSSOP14 package outline

DS12147 - Rev 8 page 19/27

Table 8. HTSSOP14 mechanical data

| Dim.   |      | mm       |      |

|--------|------|----------|------|

| Dilli. | Min. | Тур.     | Max. |

| Α      | 1.00 | 1.10     | 1.20 |

| A1     | 0.05 | 0.10     | 0.15 |

| A2     | 0.80 | 1.00     | 1.05 |

| b      | 0.19 | 0.25     | 0.30 |

| С      | 0.09 |          | 0.25 |

| D      | 4.90 | 5.00     | 5.10 |

| D1     | 3.00 |          | 3.20 |

| E      | 6.20 | 6.40     | 6.60 |

| E1     | 4.30 | 4.40     | 4.50 |

| E2     | 3.00 |          | 3.20 |

| е      |      | 0.65 BSC |      |

| L      | 0.45 | 0.60     | 0.75 |

| L1     | 0.95 | 1.00     | 1.05 |

| k      | 0    |          | 8    |

| aaa    |      |          | 0.10 |

Figure 35. HTSSOP14 recommended footprint

DS12147 - Rev 8 page 20/27

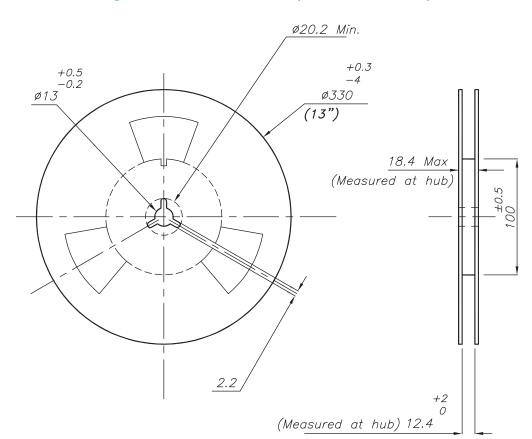

## 7.2 HTSSOP14 packing information

Do 81.55±0.05 X P0 4.0±0.1(II) F(III) W

R0.5

Typical X P1 REF0.5

SECTION X-X REF0.4

Figure 36. HTSSOP14 carrier tape outline

Table 9. HTSSOP14 carrier tape mechanical data

| Dim. | Value (mm) |

|------|------------|

| Ao   | 6.8 ±0.1   |

| Во   | 5.4 ±0.1   |

| Ко   | 1.6 ±0.1   |

| Ki   | 1.3 ±0.1   |

| F    | 5.5 ±0.05  |

| P1   | 8.0 ±0.1   |

| W    | 12.0 ±0.3  |

DS12147 - Rev 8 page 21/27

Figure 37. HTSSOP14 reel outline (dimensions are in mm)

DS12147 - Rev 8 page 22/27

## **Revision history**

Table 10. Document revision history

| Date        | Revision | Changes                                                                                                |

|-------------|----------|--------------------------------------------------------------------------------------------------------|

| 04-Aug-2017 | 1        | Initial release.                                                                                       |

| 15-Feb-2018 | 2        | Update: I <sub>D</sub> value Table 2. Absolute maximum ratings.                                        |

| 24-May-2018 | 3        | Updated maturity status link on the cover page.                                                        |

| 13-Jul-2018 | 4        | Updated pin 11 note Table 1. Pin description.                                                          |

| 01-Oct-2018 | 5        | Updated $V_{IL}$ , $V_{IH}$ and $V_{I(MAX)}$ values in Table 5. Electrical characteristics for STEF01. |

| 19-May-2020 | 6        | Added new Figure 37. HTSSOP14 reel outline (dimensions are in mm). Updated Figure 5 and Figure 6.      |

| 29-Apr-2022 | 7        | Updated Note in Table 2 Added new Table 5. ESD performance.                                            |

| 23-May-2023 | 8        | Added new features on the cover page.                                                                  |

DS12147 - Rev 8 page 23/27

## **Contents**

| 1   | Dev                 | evice block diagram2                          |                                            |    |  |  |  |

|-----|---------------------|-----------------------------------------------|--------------------------------------------|----|--|--|--|

| 2   | Pin                 | Pin configuration                             |                                            |    |  |  |  |

| 3   |                     | aximum ratings                                |                                            |    |  |  |  |

| 4   |                     | lectrical characteristics6                    |                                            |    |  |  |  |

| 5   | Typical application |                                               |                                            |    |  |  |  |

|     | 5.1                 | Operating modes                               |                                            |    |  |  |  |

|     |                     | 5.1.1                                         | Turn-on and UVLO                           |    |  |  |  |

|     |                     | 5.1.2                                         | Normal operating condition                 | 9  |  |  |  |

|     |                     | 5.1.3                                         | Output voltage clamp                       | 9  |  |  |  |

|     |                     | 5.1.4                                         | Current limit                              | 10 |  |  |  |

|     | 5.2                 | Protec                                        | ction circuits                             | 11 |  |  |  |

|     |                     | 5.2.1                                         | Thermal protection                         | 11 |  |  |  |

|     |                     | 5.2.2                                         | Maximum dissipated power protection        | 11 |  |  |  |

|     | 5.3                 | Soft st                                       | tart function                              | 12 |  |  |  |

|     | 5.4                 | Maximum load at startup                       |                                            |    |  |  |  |

|     | 5.5                 | Enable-fault pin                              |                                            |    |  |  |  |

|     | 5.6                 | Power Good function                           |                                            |    |  |  |  |

|     | 5.7                 | Gate driver for reverse current blocking FET1 |                                            |    |  |  |  |

|     | <b>5.8</b>          | Extern                                        | nal capacitors and application suggestions | 14 |  |  |  |

| 6   | Турі                | cal per                                       | formance characteristics                   | 15 |  |  |  |

| 7   | Package information |                                               |                                            |    |  |  |  |

|     | 7.1                 | HTSS                                          | OP14 package information                   | 19 |  |  |  |

|     | 7.2                 |                                               | OP14 packing information                   |    |  |  |  |

| Rev | vision              | history                                       | ,<br>,                                     | 23 |  |  |  |

## **List of tables**

| Table 1.  | Pin description                                            | . 3 |

|-----------|------------------------------------------------------------|-----|

| Table 2.  | Absolute maximum ratings                                   | . 4 |

| Table 3.  | Recommended operating condition                            | . 4 |

| Table 4.  | Thermal data                                               | . 4 |

| Table 5.  | ESD performance                                            | . 5 |

| Table 6.  | Electrical characteristics for STEF01                      | . 6 |

| Table 7.  | Enable/Fault pin behavior during thermal protection events | 13  |

| Table 8.  | HTSSOP14 mechanical data                                   | 20  |

| Table 9.  | HTSSOP14 carrier tape mechanical data                      | 21  |

| Table 10. | Document revision history                                  | 23  |

# **List of figures**

| Figure 1.  | Block diagram                                                         | . 2 |

|------------|-----------------------------------------------------------------------|-----|

| Figure 2.  | Pin configuration (top view )                                         | . 3 |

| Figure 3.  | Application circuit                                                   |     |

| Figure 4.  | UVLO block simplified diagram                                         | . 8 |

| Figure 5.  | UVLO threshold (V <sub>ON</sub> ) vs. R <sub>H</sub> , R <sub>L</sub> | . 9 |

| Figure 6.  | Clamping voltage ( $V_{clamp}$ ) vs. $R_1$ , $R_2$                    |     |

| Figure 7.  | Current limit vs. R <sub>limit</sub>                                  | 11  |

| Figure 8.  | Startup time                                                          | 12  |

| Figure 9.  | Startup time vs. C <sub>dV/dt</sub>                                   | 12  |

| Figure 10. | Enable/Fault pin status                                               | 13  |

| Figure 11. | STEF01 with external reverse blocking FET                             | 14  |

| Figure 12. | Clamping voltage vs. temperature                                      | 15  |

| Figure 13. | UVLO voltage vs. temperature                                          | 15  |

| Figure 14. | Auto pin thresholds vs. temperature                                   | 15  |

| Figure 15. | Off-state current vs. temperature                                     | 15  |

| Figure 16. | Bias current (device operational)                                     | 15  |

| Figure 17. | ON resistance vs. temperature                                         | 15  |

| Figure 18. | ON resistance vs. load current                                        | 16  |

| Figure 19. | dv/dt pin current vs. temperature                                     |     |

| Figure 20. | External gate driver pull-down resistance                             |     |

| Figure 21. | External gate driver voltage                                          |     |

| Figure 22. | External gate driver current (source) vs. temperature                 |     |

| Figure 23. | Low level En/Fault pin current (sink) vs. temperature                 |     |

| Figure 24. | En/Fault pin voltage vs. temperature                                  |     |

| Figure 25. | Current limit vs. R <sub>limit</sub> (zoom)                           | 17  |

| Figure 26. | V <sub>OUT</sub> ramp-up vs. Enable                                   |     |

| Figure 27. | V <sub>OUT</sub> clamping (28 V)                                      |     |

| Figure 28. | V <sub>OUT</sub> clamping (44 V)                                      | 17  |

| Figure 29. | Response to overload (latch)                                          |     |

| Figure 30. | Response to overload (autoretry)                                      |     |

| Figure 31. | UVLO                                                                  |     |

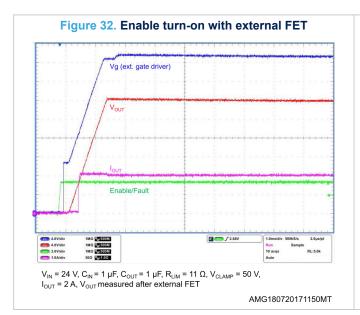

| Figure 32. | Enable turn-on with external FET                                      |     |

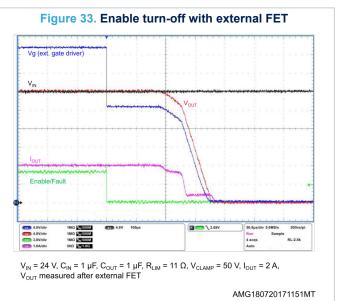

| Figure 33. | Enable turn-off with external FET                                     |     |

| Figure 34. | HTSSOP14 package outline                                              |     |

| Figure 35. | HTSSOP14 recommended footprint                                        |     |

| Figure 36. | HTSSOP14 carrier tape outline                                         |     |

| Figure 37. | HTSSOP14 reel outline (dimensions are in mm)                          | 22  |

#### **IMPORTANT NOTICE - READ CAREFULLY**

STMicroelectronics NV and its subsidiaries ("ST") reserve the right to make changes, corrections, enhancements, modifications, and improvements to ST products and/or to this document at any time without notice. Purchasers should obtain the latest relevant information on ST products before placing orders. ST products are sold pursuant to ST's terms and conditions of sale in place at the time of order acknowledgment.

Purchasers are solely responsible for the choice, selection, and use of ST products and ST assumes no liability for application assistance or the design of purchasers' products.

No license, express or implied, to any intellectual property right is granted by ST herein.

Resale of ST products with provisions different from the information set forth herein shall void any warranty granted by ST for such product.

ST and the ST logo are trademarks of ST. For additional information about ST trademarks, refer to <a href="https://www.st.com/trademarks">www.st.com/trademarks</a>. All other product or service names are the property of their respective owners.

Information in this document supersedes and replaces information previously supplied in any prior versions of this document.

© 2023 STMicroelectronics – All rights reserved

DS12147 - Rev 8 page 27/27