## **CC1070** Single Chip Low Power RF Transmitter for Narrowband Systems

## **Applications**

- Narrowband low power UHF wireless data transmitters

- 402 / 424 / 426 / 429 / 433 / 447 / 449 / 469 / 868 and 915 MHz ISM/SRD band systems

- TPMS Tire Pressure Monitoring Systems

- AMR Automatic Meter Reading

- Wireless alarm and security systems

- Home automation

- Low power telemetry

## **Product Description**

*cc1070* is a true single-chip UHF transmitter designed for very low power and very low voltage wireless applications. The circuit is mainly intended for the ISM (Industrial, Scientific and Medical) and SRD (Short Range Device) frequency bands at 402, 424, 426, 429, 433, 447, 449, 469, 868 and 915 MHz, but can easily be programmed for multi-channel operation at other frequencies in the 402 - 470 and 804 - 940 MHz range.

The *CC1070* is especially suited for narrowband systems with channel spacings of 12.5 or 25 kHz complying with ARIB STD T-67 and EN 300 220.

The *CC1070* main operating parameters can be programmed via a serial bus, thus making *CC1070* a very flexible and easy to use transmitter. In a typical application

*CC1070* will be used together with a microcontroller and a few external passive components.

#### **Features**

- True single chip UHF RF transmitter

- Frequency range 402 470 MHz and 804 - 940 MHz

- Programmable output power

- Low supply voltage (2.3 to 3.6 V)

- Very few external components required

- Small size (QFN 20 package)

- · Pb-free package

- Data rate up to 153.6 kBaud

- OOK, FSK and GFSK data modulation

- Fully on-chip VCO

- Programmable frequency makes crystal temperature drift compensation possible without TCXO

- Suitable for frequency hopping systems

- Suited for systems targeting compliance with EN 300 220, FCC CFR47 part 15 and ARIB STD T-67

- Development kit available

- Easy-to-use software for generating the *CC1070* configuration data

## **Table of Contents**

| 1  | Abbı  | reviations                                          | 4  |

|----|-------|-----------------------------------------------------|----|

| 2  | Abso  | olute Maximum Ratings                               | 5  |

| 3  | Oper  | rating Conditions                                   | 5  |

| 4  | Elect | trical Specifications                               | 5  |

|    | 4.1   | RF Transmit Section                                 | 6  |

|    | 4.2   | Crystal Oscillator Section                          | 8  |

|    | 4.3   | Frequency Synthesizer Section                       | 9  |

|    | 4.4   | Digital Inputs / Outputs                            | 10 |

|    | 4.5   | Current Consumption                                 | 11 |

| 5  | Pin A | Assignment                                          | 12 |

| 6  | Circ  | uit Description                                     | 13 |

| 7  | Appl  | ication Circuit                                     | 13 |

| 8  | Conf  | figuration Overview                                 | 16 |

|    | 8.1   | Configuration Software                              | 16 |

| 9  | Micro | ocontroller Interface                               | 17 |

|    | 9.1   | 4-wire Serial Configuration Interface               | 18 |

|    | 9.2   | Signal Interface                                    | 20 |

| 10 | Data  | Rate Programming                                    | 22 |

| 11 | Freq  | uency Programming                                   | 23 |

|    | 11.1  | Dithering                                           | 24 |

| 12 | Tran  | smitter                                             | 24 |

|    | 12.1  | FSK Modulation Formats                              | 24 |

|    | 12.2  | OOK Modulation                                      | 24 |

|    | 12.3  | Output Power Programming                            | 25 |

|    | 12.4  | TX Data Latency                                     | 26 |

|    | 12.5  | Reducing Spurious Emission and Modulation Bandwidth | 26 |

| 13 | Outp  | out Matching and Filtering                          | 26 |

| 14 | Freq  | uency Synthesizer                                   | 29 |

|    | 14.1  | VCO, Charge Pump and PLL Loop Filter                | 29 |

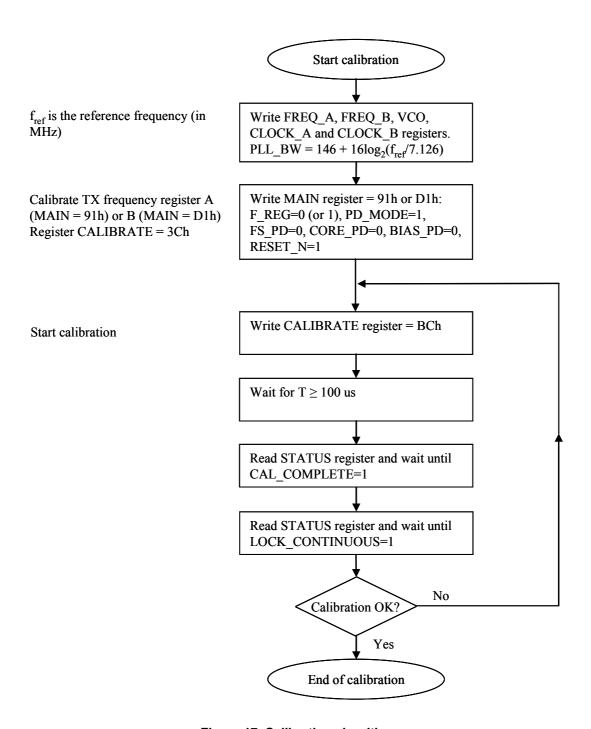

|    | 14.2  | VCO and PLL Self-Calibration                        | 30 |

|    | 14.3  | PLL Turn-on Time versus Loop Filter Bandwidth       | 31 |

|    | 14.4  | PLL Lock Time versus Loop Filter Bandwidth          | 32 |

| 15 | vco   | Current Control                                     | 32 |

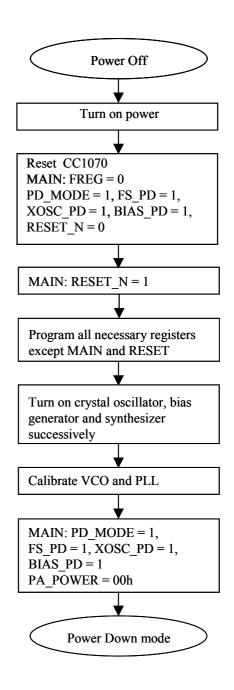

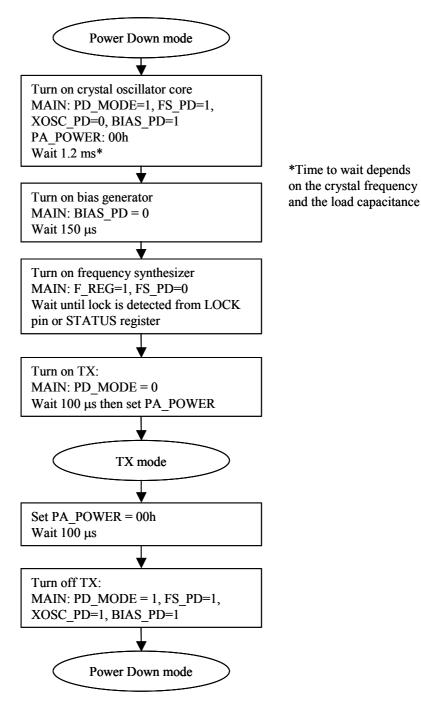

| 16 | Pow   | er Management                                       | 33 |

| 17 | Crys  | tal Oscillator                                      | 34 |

| 18 | Built | -in Test Pattern Generator                          | 36 |

# CC1070

| 19 | Interru | upt upon PLL Lock                   | 36 |

|----|---------|-------------------------------------|----|

| 20 | PA_EI   | N Digital Output Pin                | 36 |

|    | 20.1    | Interfacing an External PA          | 36 |

|    | 20.2    | General Purpose Output Control Pins | 36 |

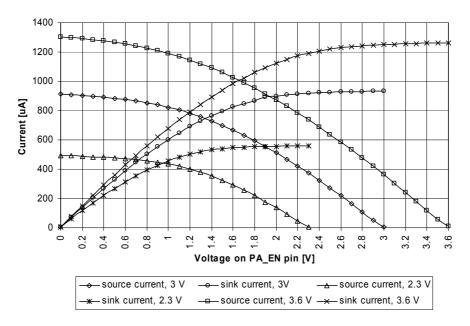

|    | 20.3    | PA_EN Pin Drive                     | 37 |

| 21 | Syste   | m Considerations and Guidelines     | 37 |

| 22 | PCB L   | _ayout Recommendations              | 39 |

| 23 | Anten   | na Considerations                   | 39 |

| 24 | Config  | guration Registers                  | 40 |

|    | 24.1    | CC1070 Register Overview            | 41 |

| 25 | Packa   | age Marking                         | 52 |

|    | 25.1    | Soldering Information               | 52 |

|    | 25.2    | Tray Specification                  | 52 |

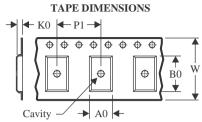

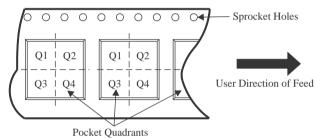

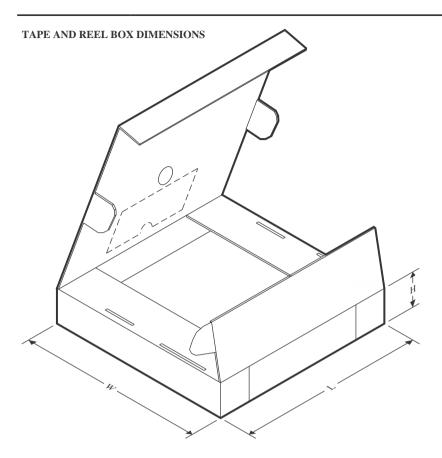

|    | 25.3    | Carrier Tape and Reel Specification | 52 |

| 26 | Order   | ing Information                     | 53 |

| 27 | Gener   | ral Information                     | 54 |

#### 1 Abbreviations

ACP Adjacent Channel Power

AMR Automatic Meter Reading

ASK Amplitude Shift Keying

ROM Bill Of Materials

BOM Bill Of Materials bps bits per second

BT Bandwidth-Time product (for GFSK)

CW Continuous Wave DNM Do Not Mount

ESR Equivalent Series Resistance

FHSS Frequency Hopping Spread Spectrum

FM Frequency Modulation FS Frequency Synthesizer FSK Frequency Shift Keying

GFSK Gaussian Frequency Shift Keying

IC Integrated Circuit

ISM Industrial Scientific Medical

kbps kilo bits per second

MCU Micro Controller Unit

NA Not Applicable

NRZ Non Return to Zero

OOK On-Off Keying

PA Power Amplifier

PD Phase Detector / Power Down

PCB Printed Circuit Board

PN9 Pseudo-random Bit Sequence (9-bit)

PLL Phase Locked Loop

PSEL Program Select

RF Radio Frequency

SPI Serial Peripheral Interface

SRD Short Range Device

TBD To Be Decided/Defined

TX Transmit (mode)

UHF Ultra High Frequency

VCO Voltage Controlled Oscillator

XOSC Crystal oscillator

XTAL Crystal

## 2 Absolute Maximum Ratings

The absolute maximum ratings given Table 1 should under no circumstances be violated. Stress exceeding one or more of the limiting values may cause permanent damage to the device

| Parameter                 | Min  | Max              | Unit | Condition                                  |

|---------------------------|------|------------------|------|--------------------------------------------|

| Supply voltage, VDD       | -0.3 | 5.0              | V    | All supply pins must have the same voltage |

| Voltage on any pin        | -0.3 | VDD+0.3, max 5.0 | V    |                                            |

| Storage temperature range | -50  | 150              | °C   |                                            |

| Package body temperature  |      | 260              | °C   | Norm: IPC/JEDEC J-STD-020C 1               |

| Humidity non-condensing   | 5    | 85               | %    |                                            |

| ESD                       |      | 500              | V    | CDM model                                  |

**Table 1. Absolute maximum ratings**

<sup>&</sup>lt;sup>1</sup> The reflow peak soldering temperature (body temperature) is specified according to IPC/JEDEC J-STD-020 "Moisture/Reflow Sensitivity Classification for Nonhermetic Solid State Surface Mount Devices".

Caution! ESD sensitive device. Precaution should be used when handling the device in order to prevent permanent damage.

## 3 Operating Conditions

The operating conditions for *CC1070* are listed in Table 2.

| Parameter                           | Min        | Тур | Max        | Unit       | Condition / Note                                                                                                                                                                     |

|-------------------------------------|------------|-----|------------|------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| RF Frequency Range                  | 402<br>804 |     | 470<br>940 | MHz<br>MHz | Programmable in <300 Hz steps<br>Programmable in <600 Hz steps                                                                                                                       |

| Operating ambient temperature range | -40        |     | 105        | °C         |                                                                                                                                                                                      |

| Supply voltage                      | 2.3        | 3.0 | 3.6        | V          | The same supply voltage should be used for digital (DVDD) and analog (AVDD) power.  A 3.0 ±0.1 V supply is recommended to meet the ARIB STD T-67 output power tolerance requirement. |

**Table 2. Operating conditions**

#### 4 Electrical Specifications

Table 3 to Table 7 gives the *CC1070* electrical specifications. All measurements were performed using the 2 layer PCB CC1070EM reference design. This is the same test circuit as shown in Figure 3. Temperature =  $25^{\circ}$ C, supply voltage = AVDD = DVDD = 3.0 V if nothing else stated. Crystal frequency = 14.7456 MHz.

The electrical specifications given for 868 MHz are also applicable for the 902 – 928 MHz frequency range.

## 4.1 RF Transmit Section

| Parameter                                                                                | Min.   | Тур.       | Max.       | Unit       | Condition / Note                                                                                                                                                                     |

|------------------------------------------------------------------------------------------|--------|------------|------------|------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Transmit data rate                                                                       | 0.45   |            | 153.6      | kBaud      | The data rate is programmable.<br>See section 10 on page 22 for<br>details.                                                                                                          |

|                                                                                          |        |            |            |            | NRZ or Manchester encoding can<br>be used. 153.6 kBaud equals<br>153.6 kbps using NRZ coding<br>and 76.8 kbps using Manchester<br>coding. See section 9.2 on page<br>20 for details. |

| Binary FSK frequency separation                                                          | 0<br>0 |            | 108<br>216 | kHz<br>kHz | in 402 - 470 MHz range<br>in 804 - 940 MHz range                                                                                                                                     |

|                                                                                          |        |            |            |            | 108/216 kHz is the maximum<br>separation at 1.84 MHz reference<br>frequency. Larger separations<br>can be achieved at higher<br>reference frequencies.                               |

| Output power                                                                             |        |            |            |            | Delivered to 50 $\Omega$ single-ended                                                                                                                                                |

| 433 MHz                                                                                  |        | -20 to +10 |            | dBm        | load. The output power is programmable and should not be                                                                                                                             |

| 868 MHz                                                                                  |        | -20 to +8  |            | dBm        | programmed to exceed +10/+8<br>dBm at 433/868 MHz under any<br>operating conditions. See section<br>13 on page 26 for details.                                                       |

| Output power tolerance                                                                   |        | -4<br>+3   |            | dB<br>dB   | At maximum output power<br>At 2.3 V, +105°C<br>At 3.6 V, -40°C                                                                                                                       |

| Harmonics, radiated CW                                                                   |        |            |            |            | Harmonics are measured as                                                                                                                                                            |

| 2 <sup>nd</sup> harmonic, 433 MHz, +10 dBm<br>3 <sup>rd</sup> harmonic, 433 MHz, +10 dBm |        | -50<br>-60 |            | dBc<br>dBc | EIRP values according to EN 300 220. The antenna (SMAFF-433 and SMAFF-868 from R.W.                                                                                                  |

| 2 <sup>nd</sup> harmonic, 868 MHz, +8 dBm<br>3 <sup>rd</sup> harmonic, 868 MHz, +8 dBm   |        | -50<br>-57 |            | dBc<br>dBc | Badland) plays a part in attenuating the harmonics.                                                                                                                                  |

| Adjacent channel power (GFSK)                                                            |        |            |            |            | For 12.5 kHz channel spacing ACP is measured in a ±4.25 kHz                                                                                                                          |

| 12.5 kHz channel spacing, 433 MHz                                                        |        | -47        |            | dBc        | bandwidth at ±12.5 kHz offset.  Modulation: 2.4 kBaud NRZ PN9                                                                                                                        |

| 25 kHz channel spacing, 868 MHz                                                          |        | -50        |            | dBc        | sequence, ±2.025 kHz frequency deviation.                                                                                                                                            |

|                                                                                          |        |            |            |            | For 25 kHz channel spacing ACP is measured in a ±8.5 kHz bandwidth at ±25 kHz offset. Modulation: 4.8 kBaud NRZ PN9 sequence, ±2.475 kHz frequency deviation.                        |

| Occupied bandwidth (99.5%,GFSK)                                                          |        |            |            |            | Bandwidth for 99.5% of total                                                                                                                                                         |

| 12.5 kHz channel spacing, 433 MHz                                                        |        | 7          |            | kHz        | average power.  Modulation for 12.5 channel                                                                                                                                          |

| 25 kHz channel spacing, 868 MHz                                                          |        | 10         |            | kHz        | spacing: 2.4 kBaud NRZ PN9 sequence, ±2.025 kHz frequency deviation.                                                                                                                 |

|                                                                                          |        |            |            |            | Modulation for 25 kHz channel spacing: 4.8 kBaud NRZ PN9 sequence, ±2.475 kHz frequency deviation.                                                                                   |

| Parameter                                                               | Min. | Тур.                             | Max. | Unit | Condition / Note                                                                                                                                                                                                                                                                                                                                                |

|-------------------------------------------------------------------------|------|----------------------------------|------|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Modulation bandwidth, 868 MHz  19.2 kBaud, ±9.9 kHz frequency deviation |      | 48                               |      | kHz  | Bandwidth where the power<br>envelope of modulation equals<br>–36 dBm. Spectrum analyzer<br>RBW = 1 kHz.                                                                                                                                                                                                                                                        |

| 38.4 kBaud, ±19.8 kHz frequency deviation                               |      | 106                              |      | kHz  |                                                                                                                                                                                                                                                                                                                                                                 |

| Spurious emission, radiated CW                                          |      |                                  |      |      | At maximum output power,<br>+10/+8 dBm at 433/868 MHz.                                                                                                                                                                                                                                                                                                          |

| 47-74, 87.5-118,<br>174-230, 470-862 MHz                                |      |                                  | -54  | dBm  | To comply with EN 300 220,<br>FCC CFR47 part 15 and ARIB                                                                                                                                                                                                                                                                                                        |

| 9 kHz – 1 GHz                                                           |      |                                  | -36  | dBm  | STD T-67 an external (antenna)                                                                                                                                                                                                                                                                                                                                  |

| 1 – 4 GHz                                                               |      |                                  | -30  | dBm  | filter, as implemented in the application circuit in Figure 14, must be used and tailored to each individual design to reduce out-of-band spurious emission levels.                                                                                                                                                                                             |

|                                                                         |      |                                  |      |      | Spurious emissions can be measured as EIRP values according to EN 300 220. The antenna (SMAFF-433 and SMAFF-868 from R.W. Badland) plays a part in attenuating the spurious emissions.                                                                                                                                                                          |

|                                                                         |      |                                  |      |      | If the output power is increased using an external PA, a filter must be used to attenuate spurs below 862 MHz when operating in the 868 MHz frequency band in Europe. Application Note ANO36 CC1020/1021 Spurious Emission presents and discusses a solution that reduces the TX mode spurious emission close to 862 MHz by increasing the REF_DIV from 1 to 7. |

| Optimum load impedance                                                  |      |                                  |      |      | Transmit made. For matching                                                                                                                                                                                                                                                                                                                                     |

| 433 MHz<br>868 MHz<br>915 MHz                                           |      | 91 + j16<br>34 + j25<br>28 + j21 |      | Ω    | Transmit mode. For matching details see section 13 on page 26.                                                                                                                                                                                                                                                                                                  |

| O TO IVII IZ                                                            |      | 20 . 12 1                        |      | Ω    |                                                                                                                                                                                                                                                                                                                                                                 |

Table 3. RF transmit parameters

# 4.2 Crystal Oscillator Section

| Parameter                                                      | Min.           | Тур.                         | Max.           | Unit                 | Condition / Note                                                                                                                                                                                    |

|----------------------------------------------------------------|----------------|------------------------------|----------------|----------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Crystal Oscillator Frequency                                   | 4.9152         | 14.7456                      | 19.6608        | MHz                  |                                                                                                                                                                                                     |

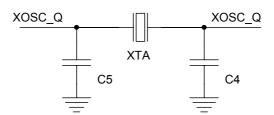

| Crystal operation                                              |                | Parallel                     |                |                      | C4 and C5 are loading capacitors. See section 17 on page 34 for details.                                                                                                                            |

| Crystal load capacitance                                       | 12<br>12<br>12 | 22<br>16<br>16               | 30<br>30<br>16 | pF<br>pF<br>pF       | 4-6 MHz, 22 pF recommended<br>6-8 MHz, 16 pF recommended<br>8-20 MHz, 16 pF recommended                                                                                                             |

| Crystal oscillator start-up time                               |                | 1.55<br>0.90<br>0.95<br>0.63 |                | ms<br>ms<br>ms<br>ms | 4.9152 MHz, 12 pF load<br>9.8304 MHz, 12 pF load<br>14.7456 MHz, 16 pF load<br>19.6608 MHz, 12 pF load                                                                                              |

| External clock signal drive, sine wave                         |                | 300                          |                | mVpp                 | The external clock signal must be connected to XOSC_Q1 using a DC block (10 nF). Set XOSC_BYPASS = 0 in the INTERFACE register when using an external clock signal with low amplitude or a crystal. |

| External clock signal drive, full-swing digital external clock |                | 0 - VDD                      |                | V                    | The external clock signal must be connected to XOSC_Q1. No DC block shall be used. Set XOSC_BYPASS = 1 in the INTERFACE register when using a full-swing digital external clock                     |

| Reference frequency accuracy requirement                       |                | +/- 5.7<br>+/- 2.8           |                | ppm<br>ppm           | 433 MHz (EN 300 220)<br>868 MHz (EN 300 220)<br>Must be less than ±5.7 / ±2.8<br>ppm to comply with EN 300 220<br>25 kHz channel spacing at<br>433/868 MHz.                                         |

|                                                                |                | +/- 4                        |                | ppm                  | Must be less than ±4 ppm to comply with Japanese 12.5 kHz channel spacing regulations (ARIB STD T-67). NOTE: This imposes special requirements on the receiver of the signal.                       |

|                                                                |                | +/- 7                        |                | ppm                  | Must be less than ±7 ppm to comply with Korean 12.5 kHz channel spacing regulations. NOTE: This imposes special requirements on the receiver of the signal.                                         |

|                                                                |                |                              |                |                      | NOTE: The reference frequency accuracy (initial tolerance) and drift (aging and temperature dependency) will determine the frequency accuracy of the transmitted signal.                            |

|                                                                |                |                              |                |                      | Crystal oscillator temperature compensation can be done using the fine frequency programmability.                                                                                                   |

Table 4. Crystal oscillator parameters

# 4.3 Frequency Synthesizer Section

| Parameter                                                               | Min. | Тур.                               | Max. | Unit                                           | Condition / Note                                                                                                                                                                                                                                                                       |

|-------------------------------------------------------------------------|------|------------------------------------|------|------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Phase noise, 402 – 470 MHz                                              |      |                                    |      |                                                | Unmodulated carrier                                                                                                                                                                                                                                                                    |

| 12.5 kHz channel spacing                                                |      | -87<br>-95<br>-100<br>-105<br>-114 |      | dBc/Hz<br>dBc/Hz<br>dBc/Hz<br>dBc/Hz<br>dBc/Hz | At 12.5 kHz offset from carrier At 25 kHz offset from carrier At 50 kHz offset from carrier At 100 kHz offset from carrier At 1 MHz offset from carrier  Measured using loop filter components given in Table 10. The phase noise will be higher for larger PLL loop filter bandwidth. |

| Phase noise, 804 - 940 MHz                                              |      |                                    |      |                                                | Unmodulated carrier                                                                                                                                                                                                                                                                    |

| 25 kHz channel spacing                                                  |      | -81<br>-89<br>-96<br>-103<br>-122  |      | dBc/Hz<br>dBc/Hz<br>dBc/Hz<br>dBc/Hz<br>dBc/Hz | At 12.5 kHz offset from carrier At 25 kHz offset from carrier At 50 kHz offset from carrier At 100 kHz offset from carrier At 1 MHz offset from carrier Measured using loop filter components given in Table 10. The phase noise will be higher for larger PLL loop filter bandwidth.  |

| PLL loop bandwidth                                                      |      |                                    |      |                                                |                                                                                                                                                                                                                                                                                        |

| 12.5 kHz channel spacing, 433 MHz                                       |      | 5                                  |      | kHz                                            | After PLL and VCO calibration. The PLL loop bandwidth is programmable                                                                                                                                                                                                                  |

| 25 kHz channel spacing, 868 MHz                                         |      | 7                                  |      | kHz                                            | programmable                                                                                                                                                                                                                                                                           |

| PLL lock time (TX_1 / TX_2 turn time)                                   |      |                                    |      |                                                | One channel frequency step to                                                                                                                                                                                                                                                          |

| 12.5 kHz channel spacing, 433 MHz                                       |      | 180                                |      | us                                             | RF frequency within ±10% of channel spacing. Depends on                                                                                                                                                                                                                                |

| 25 kHz channel spacing, 868 MHz                                         |      | 270                                |      | us                                             | loop filter component values and<br>PLL_BW register setting. See                                                                                                                                                                                                                       |

| 500 kHz channel spacing                                                 |      | 14                                 |      | us                                             | Table 20 on page 32 for more details.                                                                                                                                                                                                                                                  |

| PLL turn-on time. From power down mode with crystal oscillator running. |      |                                    |      |                                                | Time from writing to registers to RF frequency within ±10% of channel spacing. Depends on                                                                                                                                                                                              |

| 12.5 kHz channel spacing, 433 MHz                                       |      | 3.2                                |      | ms                                             | loop filter component values and<br>PLL_BW register setting. See                                                                                                                                                                                                                       |

| 25 kHz channel spacing, 868 MHz                                         |      | 2.5                                |      | ms                                             | Table 19 on page 32 for more details.                                                                                                                                                                                                                                                  |

| 500 kHz channel spacing                                                 |      | 700                                |      | us                                             | uciails.                                                                                                                                                                                                                                                                               |

Table 5. Frequency synthesizer parameters

# 4.4 Digital Inputs / Outputs

| Parameter                                                       | Min         | Тур                          | Max         | Unit                 | Condition / Note                                                                                                              |

|-----------------------------------------------------------------|-------------|------------------------------|-------------|----------------------|-------------------------------------------------------------------------------------------------------------------------------|

| Logic "0" input voltage                                         | 0           |                              | 0.3*<br>VDD | V                    |                                                                                                                               |

| Logic "1" input voltage                                         | 0.7*<br>VDD |                              | VDD         | V                    |                                                                                                                               |

| Logic "0" output voltage                                        | 0           |                              | 0.4         | V                    | Output current -2.0 mA, 3.0 V supply voltage                                                                                  |

| Logic "1" output voltage                                        | 2.5         |                              | VDD         | V                    | Output current 2.0 mA,<br>3.0 V supply voltage                                                                                |

| Logic "0" input current                                         | NA          |                              | -1          | μА                   | Input signal equals GND.  PSEL has an internal pull-up resistor and during configuration the current will be -350 µA.         |

| Logic "1" input current                                         | NA          |                              | 1           | μА                   | Input signal equals VDD                                                                                                       |

| DIO setup time                                                  | 20          |                              |             | ns                   | TX mode, minimum time DIO must be ready before the positive edge of DCLK. Data should be set up on the negative edge of DCLK. |

| DIO hold time                                                   | 10          |                              |             | ns                   | TX mode, minimum time DIO must be held after the positive edge of DCLK. Data should be set up on the negative edge of DCLK.   |

| Serial interface (PCLK, PDI, PDO and PSEL) timing specification |             |                              |             |                      | See Table 11 on page 20 for more details                                                                                      |

| PA_EN pin drive                                                 |             | 0.90<br>0.87<br>0.81<br>0.69 |             | mA<br>mA<br>mA<br>mA | Source current 0 V on PA_EN pin 0.5 V on PA_EN pin 1.0 V on PA_EN pin 1.5 V on PA_EN pin                                      |

|                                                                 |             | 0.93<br>0.92<br>0.89<br>0.79 |             | mA<br>mA<br>mA<br>mA | Sink current 3.0 V on PA_EN pin 2.5 V on PA_EN pin 2.0 V on PA_EN pin 1.5 V on PA_EN pin                                      |

Table 6. Digital inputs / outputs parameters

## 4.5 Current Consumption

| Parameter                                                     | Min. | Тур.      | Max. | Unit | Condition / Note                              |

|---------------------------------------------------------------|------|-----------|------|------|-----------------------------------------------|

| Power Down mode                                               |      | 0.2       | 1    | μА   | Oscillator core off                           |

| Current consumption,<br>433/868 MHz:                          |      |           |      |      |                                               |

| P = -20 dBm                                                   |      | 12.3/13.9 |      | mA   | The output power is delivered to a            |

| P = -5 dBm                                                    |      | 14.7/16.8 |      | mA   | 50 $\Omega$ single-ended load.                |

| P = 0 dBm                                                     |      | 17.5/20.5 |      | mA   | See section 12.3 on page 25 for more details. |

| P = +5 dBm                                                    |      | 21.5/25.3 |      | mA   |                                               |

| P = +8 dBm                                                    |      | 25.5/33.1 |      | mA   |                                               |

| P = +10 dBm                                                   |      | 31/NA     |      | mA   |                                               |

| Current consumption, crystal oscillator                       |      | 65        |      | μА   | 14.7456 MHz, 16 pF load crystal               |

| Current consumption, crystal oscillator and bias              |      | 500       |      | μА   | 14.7456 MHz, 16 pF load crystal               |

| Current consumption, crystal oscillator, bias and synthesizer |      | 7.5       |      | mA   | 14.7456 MHz, 16 pF load crystal               |

**Table 7. Current consumption**

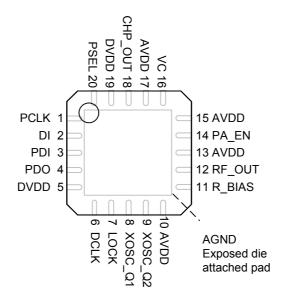

## 5 Pin Assignment

Table 8 provides an overview of the *CC1070* pinout.

The *CC1070* comes in a QFN20 type package.

Figure 1. CC1070 package (top view)

| Pin no. | Pin name | Pin type        | Description                                                                |

|---------|----------|-----------------|----------------------------------------------------------------------------|

| -       | AGND     | Ground (analog) | Exposed die attached pad. Must be soldered to a solid ground               |

|         |          |                 | plane as this is the ground connection for all analog modules See          |

|         |          |                 | page 39 for more details.                                                  |

| 1       | PCLK     | Digital input   | Programming clock for SPI configuration interface                          |

| 2       | DI       | Digital input   | Data input in transmit mode                                                |

| 3       | PDI      | Digital input   | Programming data input for SPI configuration interface                     |

| 4       | PDO      | Digital output  | Programming data output for SPI configuration interface                    |

| 5       | DVDD     | Power (digital) | Power supply (3 V typical) for digital modules and digital I/O             |

| 6       | DCLK     | Digital output  | Clock for transmit data                                                    |

| 7       | LOCK     | Digital output  | PLL Lock indicator, active low. Output is asserted (low) when PLL          |

|         |          |                 | is in lock. The pin can also be used as a general digital output.          |

| 8       | XOSC_Q1  | Analog input    | Crystal oscillator or external clock input                                 |

| 9       | XOSC_Q2  | Analog output   | Crystal oscillator                                                         |

| 10      | AVDD     | Power (analog)  | Power supply (3 V typical) for crystal oscillator and bias generator       |

|         |          |                 | (double bonded).                                                           |

| 11      | R_BIAS   | Analog output   | Connection for external precision bias resistor (82 k $\Omega$ , $\pm$ 1%) |

| 12      | RF_OUT   | RF output       | RF signal output to antenna                                                |

| 13      | AVDD     | Power (analog)  | Power supply (3 V typical) for LO buffers, prescaler and PA first          |

|         |          |                 | stage                                                                      |

| 14      | PA_EN    | Digital output  | General digital output. Can be used for controlling an external PA,        |

|         |          |                 | if higher output power is needed.                                          |

| 15      | AVDD     | Power (analog)  | Power supply (3 V typical) for VCO                                         |

| 16      | VC       | Analog input    | VCO control voltage input from external loop filter                        |

| 17      | AVDD     | Power (analog)  | Power supply (3 V typical) for charge pump and phase detector              |

| 18      | CHP_OUT  | Analog output   | PLL charge pump output to external loop filter                             |

| 19      | DVDD     | Power (digital) | Power supply connection (3 V typical) for digital modules                  |

| 20      | PSEL     | Digital input   | Programming chip select, active low, for configuration interface.          |

|         |          |                 | Internal pull-up resistor.                                                 |

Table 8. Pin assignment overview

#### Note:

DCLK, DI and LOCK are high-impedance (3-state) in power down (*BIAS\_PD* = 1 in the *MAIN* register).

The exposed die attached pad **must** be soldered to solid ground plane as this is the main ground connection for the chip.

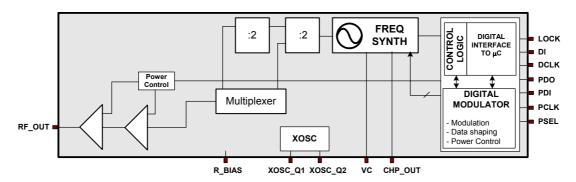

## 6 Circuit Description

Figure 2. CC1070 simplified block diagram

A simplified block diagram of *CC1070* is shown in Figure 2. Only signal pins are shown.

During transmit operation, the synthesized RF frequency is fed directly to the power amplifier (PA). The RF output is frequency shift keyed (FSK) by the digital bit stream that is fed to the DI pin. Optionally, the internal Gaussian filter can be enabled for Gaussian FSK (GFSK).

The frequency synthesizer includes a completely on-chip LC VCO. The VCO operates in the frequency range 1.608-1.880 GHz. The CHP\_OUT pin is the charge pump output and VC is the control node of the on-chip VCO. The external loop filter is placed between these pins. A crystal is to be connected between XOSC\_Q1 and XOSC\_Q2. A lock signal is available from the PLL.

The 4-wire SPI serial interface is used for configuration.

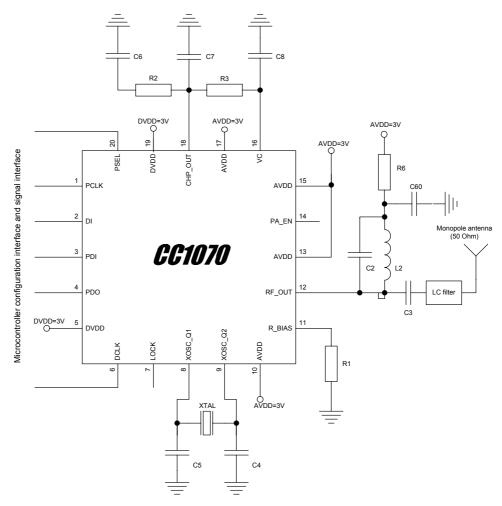

## 7 Application Circuit

Very few external components are required for the operation of *CC1070*. A typical application circuit is shown in Figure 3. The external components are described in Table 9 and values are given in Table 10.

#### **Output matching**

L2, C2 and C3 are used to match the transmitter to 50  $\Omega$ . See section 13 on page 26 for details. Component values for the matching network are easily calculated using the SmartRF® Studio software.

#### Bias resistor

The precision bias resistor R1 is used to set an accurate bias current.

#### **PLL loop filter**

The loop filter consists of two resistors (R2 and R3) and three capacitors (C6-C8). C7 and C8 may be omitted in applications where high loop bandwidth is desired. The values shown in Table 10 can be used for

data rates up to 4.8 kBaud. Component values for higher data rates are easily found using the SmartRF<sup>®</sup> Studio software.

#### Crystal

An external crystal with two loading capacitors (C4 and C5) is used for the crystal oscillator. See section 17 on page 34 for details.

## **Additional filtering**

Additional external components (e.g. RF LC or SAW filter) may be used in order to improve the performance in specific applications. See section 13 on page 26 for further information.

#### Power supply decoupling and filtering

Power supply decoupling and filtering must be used (not shown in the application circuit). The placement and size of the decoupling capacitors and the power supply filtering are very important to

achieve the optimum performance for narrowband applications. TI provides a

reference design that should be followed very closely.

Figure 3. Typical application and test circuit (power supply decoupling not shown)

| Ref  | Description                                                           |

|------|-----------------------------------------------------------------------|

| C2   | PA match, see page 26                                                 |

| C3   | PA output match and dc block, see page 26                             |

| C4   | Crystal load capacitor, see page 34                                   |

| C5   | Crystal load capacitor, see page 34                                   |

| C6   | PLL loop filter capacitor                                             |

| C7   | PLL loop filter capacitor (may be omitted for highest loop bandwidth) |

| C8   | PLL loop filter capacitor (may be omitted for highest loop bandwidth) |

| C60  | Decoupling capacitor                                                  |

| L2   | PA match and DC bias (supply voltage), see page 26                    |

| R1   | Precision resistor for current reference generator                    |

| R2   | PLL loop filter resistor                                              |

| R3   | PLL loop filter resistor                                              |

| R6   | PA output match, see page 26                                          |

| XTAL | Crystal, see page 34                                                  |

Table 9. Overview of external components (excluding supply decoupling capacitors)

| Item | 433 MHz                | 868 MHz                | 915 MHz                |

|------|------------------------|------------------------|------------------------|

| C2   | 2.2 pF, 5%, NP0, 0402  | 1.5 pF, 5%, NP0, 0402  | 1.5 pF, 5%, NP0, 0402  |

| C3   | 5.6 pF, 5%, NP0, 0402  | 10 pF, 5%, NP0, 0402   | 10 pF, 5%, NP0, 0402   |

| C4   | 22 pF, 5%, NP0, 0402   | 22 pF, 5%, NP0, 0402   | 22 pF, 5%, NP0, 0402   |

| C5   | 12 pF, 5%, NP0, 0402   | 12 pF, 5%, NP0, 0402   | 12 pF, 5%, NP0, 0402   |

| C6   | 220 nF, 10%, X7R, 0603 | 100 nF, 10%, X7R, 0603 | 100 nF, 10%, X7R, 0603 |

| C7   | 8.2 nF, 10%, X7R, 0402 | 3.9 nF, 10%, X7R, 0402 | 3.9 nF, 10%, X7R, 0402 |

| C8   | 2.2 nF, 10%, X7R, 0402 | 1.0 nF, 10%, X7R, 0402 | 1.0 nF, 10%, X7R, 0402 |

| C60  | 220 pF, 5%, NP0, 0402  | 220 pF, 5%, NP0, 0402  | 220 pF, 5%, NP0, 0402  |

| L2   | 22 nH, 5%, 0402        | 6.8 nH, 5%, 0402       | 6.8 nH, 5%, 0402       |

| R1   | 82 kΩ, 1%, 0402        | 82 kΩ, 1%, 0402        | 82 kΩ, 1%, 0402        |

| R2   | 1.5 kΩ, 5%, 0402       | 2.2 kΩ, 5%, 0402       | 2.2 kΩ, 5%, 0402       |

| R3   | 4.7 kΩ, 5%, 0402       | 6.8 kΩ, 5%, 0402       | 6.8 kΩ, 5%, 0402       |

| R6   | 82 Ω, 5%, 0402         | 82 Ω, 5%, 0402         | 82 Ω, 5%, 0402         |

| XTAL | 14.7456 MHz crystal,   | 14.7456 MHz crystal,   | 14.7456 MHz crystal,   |

|      | 16 pF load             | 16 pF load             | 16 pF load             |

Note: Items shaded vary for different frequencies. For 433 MHz, 12.5 kHz channel, a loop filter with lower bandwidth is used to improve adjacent and alternate channel rejection.

Table 10. Bill of materials for the application circuit in Figure 3

#### Note:

The PLL loop filter component values in Table 10 (R2, R3, C6-C8) can be used for data rates up to 4.8 kBaud. The SmartRF® Studio software provides component values for other data rates using the equations on page 29.

In the CC1070EM reference design LQG15HS series inductors from Murata have been used.

## 8 Configuration Overview

**CC1070** can be configured to achieve optimum performance for different applications. Through the programmable configuration registers the following key parameters can be programmed:

- · RF output power

- Frequency synthesizer key parameters: RF output frequency, FSK

- frequency separation, crystal oscillator reference frequency

- Power-down / power-up mode

- Crystal oscillator power-up / power down

- Data rate and data format (NRZ, Manchester coded or UART interface)

- · Synthesizer lock indicator mode

- FSK / GFSK / OOK modulation

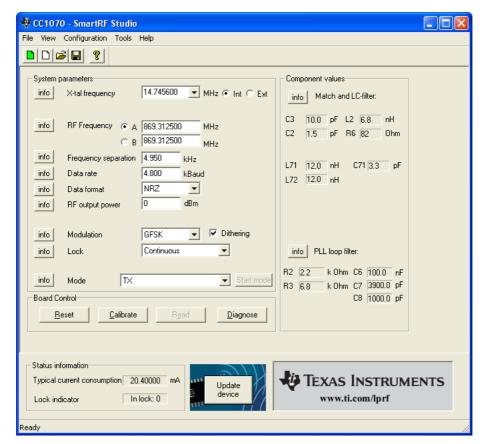

## 8.1 Configuration Software

TI provides users of *CC1070* with a software program, SmartRF® Studio (Windows interface) that generates all necessary *CC1070* configuration data based on the user's selections of various parameters. These hexadecimal numbers will then be the necessary input to the microcontroller for the configuration of

*CC1070.* In addition, the program will provide the user with the component values needed for the output matching circuit, the PLL loop filter and the LC filter.

Figure 4 shows the user interface of the *CC1070* configuration software.

Figure 4. SmartRF® Studio user interface

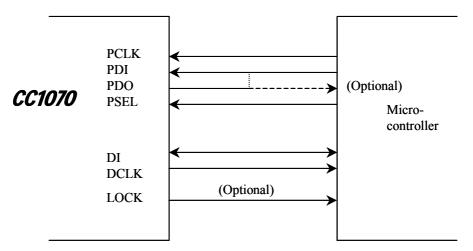

#### 9 Microcontroller Interface

Used in a typical system, *CC1070* will interface to a microcontroller. This microcontroller must be able to:

- Program CC1070 into different modes via the 4-wire serial configuration interface (PDI, PDO, PCLK and PSEL)

- Interface to the synchronous data signal interface (DI and DCLK)

- Optionally, the microcontroller can do data encoding

- Optionally, the microcontroller can monitor the LOCK pin for frequency lock status or other status information.

#### Configuration interface

The microcontroller interface is shown in Figure 5. The microcontroller uses 3 or 4 I/O pins for the configuration interface (PDI, PDO, PCLK and PSEL). PDO should be connected to a microcontroller input. PDI, PCLK and PSEL must be microcontroller outputs. One I/O pin can be saved if PDI and PDO are connected together and a bi-directional pin is used at the microcontroller.

The microcontroller pins connected to PDI, PDO and PCLK can be used for other

purposes when the configuration interface is not used. PDI, PDO and PCLK are high impedance inputs as long as PSEL is not activated (active low).

PSEL has an internal pull-up resistor and should be left open (tri-stated by the microcontroller) or set to a high level during power down mode in order to prevent a trickle current flowing in the pull-up.

#### Signal interface

The DI pin is used for data to be transmitted. DCLK providing the data timing should be connected to a microcontroller input.

#### PLL lock signal

Optionally, one microcontroller pin can be used to monitor the LOCK signal. This signal is at low logic level when the PLL is in lock. It can also be used to monitor other internal test signals.

Figure 5. Microcontroller interface

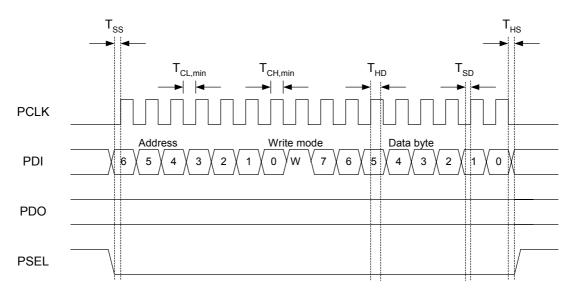

## 9.1 4-wire Serial Configuration Interface

CC1070 is configured via a simple 4-wire SPI-compatible interface (PDI, PDO, PCLK and PSEL) where CC1070 is the slave. There are 22 8-bit configuration registers and 6 8-bit test-only registers, each addressed by a 7-bit address. A Read/Write bit initiates a read or write operation. A full configuration of CC1070 requires sending 22 data frames of 16 bits each (7 address bits, R/W bit and 8 data bits). The time needed for a full configuration depends on the PCLK frequency. With a PCLK frequency of 10 MHz the full configuration is done in less than 36 µs. Setting the device in power down mode requires sending one frame only and will in this case take less than 2 us. All registers are also readable.

In each write-cycle, 16 bits are sent on the PDI-line. The seven most significant bits of each data frame (A6:0) are the address-bits. A6 is the MSB (Most Significant Bit) of the address and is sent as the first bit. The next bit is the R/W bit (high for write, low for read). The 8 data-bits are then transferred (D7:0). During address and data transfer the PSEL (Program SELect) must be kept low. See Figure 6.

The timing for the programming is also shown in Figure 6 with reference to Table 11. The clocking of the data on PDI is done on the positive edge of PCLK. Data should be set up on the negative edge of PCLK by the microcontroller. When the last bit, *D0*, of the 8 data-bits has been loaded, the data word is loaded in the internal configuration register.

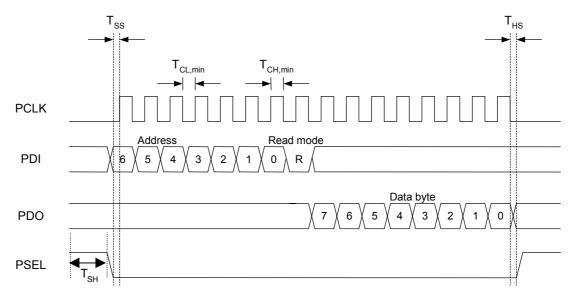

The configuration data will be retained during a programmed power-down mode, but not when the power-supply is turned off. The registers can be programmed in any order.

The configuration registers can also be read by the microcontroller via the same configuration interface. The seven address bits are sent first, then the R/W bit set <u>low</u> to initiate the data read-back. *CC1070* then returns the data from the addressed register. PDO is used as the data output and must be configured as an input by the microcontroller. The PDO is set at the negative edge of PCLK and should be sampled at the positive edge. The read operation is illustrated in Figure 7.

PSEL must be set high between each read/write operation.

There are also 5 read-only status registers.

Figure 6. Configuration registers write operation

Figure 7. Configuration registers read operation

| Parameter                      | Symbol            | Min | Max | Unit | Conditions                                                                          |

|--------------------------------|-------------------|-----|-----|------|-------------------------------------------------------------------------------------|

| PCLK, clock frequency          | F <sub>PCLK</sub> |     | 10  | MHz  |                                                                                     |

| PCLK low<br>pulse<br>duration  | $T_{CL,min}$      | 50  |     | ns   | The minimum time PCLK must be low.                                                  |

| PCLK high<br>pulse<br>duration | $T_{CH,min}$      | 50  |     | ns   | The minimum time PCLK must be high.                                                 |

| PSEL setup time                | T <sub>SS</sub>   | 25  |     | ns   | The minimum time PSEL must be low before positive edge of PCLK.                     |

| PSEL hold time                 | T <sub>HS</sub>   | 25  |     | ns   | The minimum time PSEL must be held low after the <i>negative</i> edge of PCLK.      |

| PSEL high time                 | T <sub>SH</sub>   | 50  |     | ns   | The minimum time PSEL must be high.                                                 |

| PDI setup<br>time              | $T_{SD}$          | 25  |     | ns   | The minimum time data on PDI must be ready before the <i>positive</i> edge of PCLK. |

| PDI hold time                  | $T_{HD}$          | 25  |     | ns   | The minimum time data must be held at PDI, after the <i>positive</i> edge of PCLK.  |

| Rise time                      | T <sub>rise</sub> |     | 100 | ns   | The maximum rise time for PCLK and PSEL                                             |

| Fall time                      | $T_{fall}$        |     | 100 | ns   | The maximum fall time for PCLK and PSEL                                             |

Note: The setup and hold times refer to 50% of VDD. The rise and fall times refer to 10% / 90% of VDD. The maximum load that this table is valid for is 20 pF.

Table 11. Serial interface, timing specification

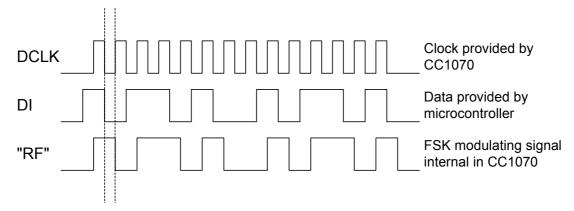

#### 9.2 Signal Interface

The *CC1070* can be used with NRZ (Non-Return-to-Zero) data or Manchester (also known as bi-phase-level) encoded data. The data format is controlled by the *DATA\_FORMAT[1:0]* bits in the *MODEM* register.

*CC1070* can be configured for three different data formats:

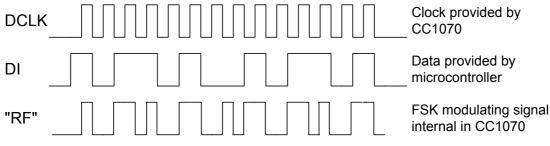

#### Synchronous NRZ mode

During transmit operation, the *CC1070* provides the data clock at DCLK and DI is used as data input. Data is clocked into *CC1070* at the rising edge of DCLK. The data is modulated at RF without encoding. See Figure 8.

# Synchronous Manchester encoded mode

During transmit operation, the *CC1070* provides the data clock at DCLK and DI is used as data input. Data is clocked into *CC1070* at the rising edge of DCLK and should be in NRZ format. The data is modulated at RF with Manchester code. The encoding is done by *CC1070*. In this mode the effective bit rate is half the baud rate due to the coding. As an example, 19.2 kBaud Manchester encoded data corresponds to a 9.6 kbps. See Figure 9.

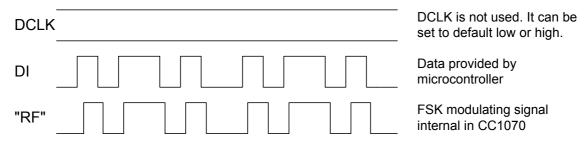

# Transparent Asynchronous UART mode

During transmit operation, DI is used as data input. The data is modulated at RF without synchronization or encoding. In this mode, the DCLK pin is not active and can be set to a high or low level by DATA FORMAT[0]. See Figure 10.

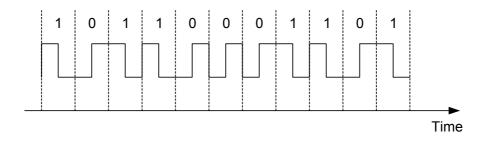

#### Manchester encoding and decoding

In the Synchronous Manchester encoded mode CC1070 uses Manchester coding when modulating the data. The Manchester code is based on transitions; a "0" is encoded as a low-to-high transition, a "1" is encoded as a high-to-low transition. See Figure 11.

The Manchester code ensures that the signal has a constant DC component, which is necessary in some FSK receivers/demodulators. Using this mode also ensures compatibility with e.g. CC400/CC900 designs.

Figure 8. Synchronous NRZ mode

Figure 9. Synchronous Manchester encoded mode

Figure 10. Transparent Asynchronous UART mode

Figure 11. Manchester encoding

## 10 Data Rate Programming

The data rate (baud rate) is programmable and depends on the crystal frequency and the programming of the CLOCK (CLOCK A and CLOCK B) registers.

The baud rate (B.R) is given by

$$B.R. = \frac{f_{xosc}}{8 \cdot (REF\_DIV + 1) \cdot DIV1 \cdot DIV2}$$

where DIV1 and DIV2 are given by the value of *MCLK\_DIV1* and *MCLK\_DIV2*.

Table 14 shows some possible data rates as a function of crystal frequency in synchronous mode. In asynchronous transparent UART mode any data rate up to 153.6 kBaud can be used.

| MCLK_DIV1[2:0] | DIV1 |

|----------------|------|

| 000            | 2.5  |

| 001            | 3    |

| 010            | 4    |

| 011            | 7.5  |

| 100            | 12.5 |

| 101            | 40   |

| 110            | 48   |

| 111            | 64   |

Table 12. DIV1 for different settings of MCLK\_DIV1

| MCLK_DIV2[1:0] | DIV2 |

|----------------|------|

| 00             | 1    |

| 01             | 2    |

| 10             | 4    |

| 11             | 8    |

Table 13. DIV2 for different settings of MCLK\_DIV2

| Data rate | Crystal frequency [MHz] |        |        |        |         |         |         |  |  |

|-----------|-------------------------|--------|--------|--------|---------|---------|---------|--|--|

| [kBaud]   | 4.9152                  | 7.3728 | 9.8304 | 12.288 | 14.7456 | 17.2032 | 19.6608 |  |  |

| 0.45      |                         | Х      |        |        | Х       |         |         |  |  |

| 0.5       |                         |        |        | Х      |         |         |         |  |  |

| 0.6       | Х                       | X      | Х      | Х      | Х       | Х       | Х       |  |  |

| 0.9       |                         | Х      |        |        | Х       |         |         |  |  |

| 1         |                         |        |        | Х      |         |         |         |  |  |

| 1.2       | Х                       | Х      | Х      | Х      | Х       | Х       | Х       |  |  |

| 1.8       |                         | Х      |        |        | Х       |         |         |  |  |

| 2         |                         |        |        | X      |         |         |         |  |  |

| 2.4       | Х                       | Х      | Х      | Х      | Х       | Х       | Х       |  |  |

| 3.6       |                         | Х      |        |        | Х       |         |         |  |  |

| 4         |                         |        |        | Х      |         |         |         |  |  |

| 4.096     |                         |        | Х      |        |         |         | Х       |  |  |

| 4.8       | Х                       | Х      | Х      | Х      | X       | Х       | Х       |  |  |

| 7.2       |                         | Х      |        |        | Х       |         |         |  |  |

| 8         |                         |        |        | Х      |         |         |         |  |  |

| 8.192     |                         |        | X      |        |         |         | X       |  |  |

| 9.6       | Х                       | Х      | Х      | Х      | Х       | Х       | Х       |  |  |

| 14.4      |                         | Х      |        |        | Х       |         |         |  |  |

| 16        |                         |        |        | Х      |         |         |         |  |  |

| 16.384    |                         |        | X      |        |         |         | X       |  |  |

| 19.2      | Х                       | Х      | Х      | Х      | Х       | Х       | Х       |  |  |

| 28.8      |                         | Х      |        |        | Х       |         |         |  |  |

| 32        |                         |        |        | Х      |         |         |         |  |  |

| 32.768    |                         |        | Х      |        |         |         | Х       |  |  |

| 38.4      | Х                       | Х      | Х      | Х      | Х       | Х       | Х       |  |  |

| 57.6      |                         | Х      |        |        | Х       |         |         |  |  |

| 64        |                         |        |        | Х      |         |         |         |  |  |

| 65.536    |                         |        |        |        |         |         | Х       |  |  |

| 76.8      | Х                       | Х      | Х      | Х      | Х       | Х       | Х       |  |  |

| 115.2     |                         | X      |        |        | Х       |         |         |  |  |

| 128       |                         |        |        | Х      |         |         |         |  |  |

| 153.6     | Х                       | Х      | Х      | Х      | Х       | Х       | Х       |  |  |

Table 14. Some possible data rates versus crystal frequency

## 11 Frequency Programming

Programming the frequency word in the configuration registers sets the operation frequency. There are two frequency words registers, termed *FREQ\_A* and *FREQ\_B*, which can be programmed to two different frequencies. They can be used for two different channels. The F\_REG bit in the MAIN register selects frequency word A or B.

The frequency word is located in FREQ\_2A:FREQ\_1A:FREQ\_0A and FREQ\_2B:FREQ\_1B:FREQ\_0B for the FREQ\_A and FREQ\_B word respectively. The LSB of the FREQ\_0 registers are used to enable dithering, section 11.1.

The PLL output frequency is given by:

$$f_c = f_{ref} \cdot \left( \frac{3}{4} + \frac{FREQ + 0.5 \cdot DITHER}{32768} \right)$$

in the frequency band 402 - 470 MHz, and

$$f_c = f_{ref} \cdot \left(\frac{3}{2} + \frac{FREQ + 0.5 \cdot DITHER}{16384}\right)$$

in the frequency band 804 – 940 MHz.

The BANDSELECT bit in the ANALOG register controls the frequency band used. BANDSELECT = 0 gives 402 – 470 MHz, and BANDSELECT = 1 gives 804 - 940 MHz.

The reference frequency is the crystal oscillator clock frequency divided by *REF\_DIV* (3 bits in the *CLOCK\_A* or *CLOCK\_B* register), a number between 1 and 7:

$$f_{ref} = \frac{f_{xosc}}{REF\_DIV + 1}$$

FSK frequency deviation is programmed in the *DEVIATION* register. The deviation programming is divided into a mantissa (*TXDEV\_M[3:0]*) and an exponent (*TXDEV\_X[2:0]*).

Generally *REF\_DIV* should be as low as possible but the following requirements must be met

$$9.8304 \ge f_{ref} > \frac{f_c}{256} [MHz]$$

in the frequency band 402 - 470 MHz, and

$$9.8304 \ge f_{ref} > \frac{f_c}{512} [MHz]$$

in the frequency band 804 – 940 MHz.

The PLL output frequency equation above gives the carrier frequency,  $f_{\text{c}}$ , in transmit mode (center frequency). The two FSK modulation frequencies are given by:

$$f_0 = f_c - f_{dev}$$

$$f_1 = f_c + f_{dev}$$

where  $f_{dev}$  is set by the *DEVIATION* register:

$$f_{dev} = f_{ref} \cdot TXDEV \ M \cdot 2^{(TXDEV \ X-16)}$$

in the frequency band 402 - 470 MHz, and

$$f_{dev} = f_{ref} \cdot TXDEV \ M \cdot 2^{(TXDEV \ X-15)}$$

in the frequency band 804 - 940 MHz.

OOK (On-Off Keying) is used if  $TXDEV\_M[3:0] = 0000$ .

The *TX\_SHAPING* bit in the *DEVIATION* register controls Gaussian shaping of the modulation signal.

## 11.1 Dithering

Spurious signals will occur at certain frequencies depending on the division ratios in the PLL. To reduce the strength of these spurs, a common technique is to use a dithering signal in the control of the

frequency dividers. Dithering is activated by setting the *DITHER* bit in the *FREQ\_0* registers. It is recommended to use the dithering in order to achieve the best possible performance.

#### 12 Transmitter

#### 12.1 FSK Modulation Formats

The data modulator can modulate FSK, which is a two level FSK (Frequency Shift Keying), or GFSK, which is a Gaussian filtered FSK with BT = 0.5. The purpose of the GFSK is to make a more bandwidth efficient system. The modulation and the

Gaussian filtering are done internally in the chip. The *TX\_SHAPING* bit in the *DEVIATION* register enables the GFSK. GFSK is recommended for narrowband operation.

#### 12.2 OOK Modulation

The data modulator can also do OOK (On-Off Keying) modulation. OOK is an ASK (Amplitude Shift Keying) modulation using 100% modulation depth.

OOK modulation is enabled by setting  $TXDEV\_M[3:0] = 0000$  in the DEVIATION register.

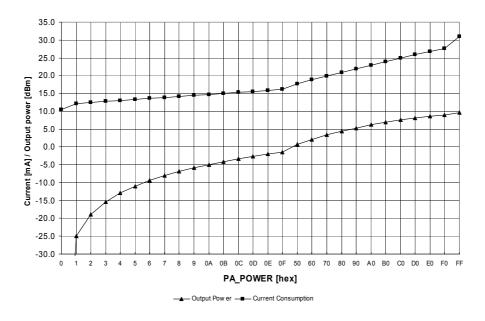

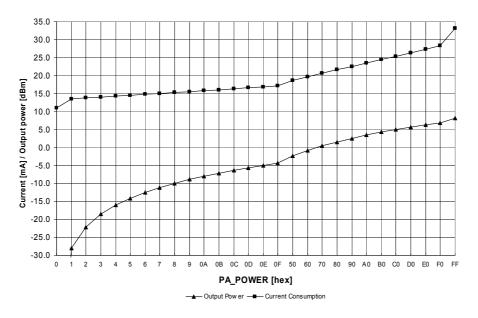

## 12.3 Output Power Programming

The RF output power from the device is programmable by the 8-bit PA\_POWER register. Figure 12 and Figure 13 shows the output power and total current consumption as a function of the PA\_POWER register setting. It is more efficient in terms of current consumption to

use either the lower or upper 4-bits in the register to control the power, as shown in the figures. However, the output power can be controlled in finer steps using all the available bits in the *PA\_POWER* register.

Figure 12. Output power settings and typical current consumption, 433 MHz

Figure 13. Output power settings and typical current consumption, 868 MHz

## 12.4 TX Data Latency

The transmitter will add a delay due to the synchronization of the data with DCLK and further clocking into the modulator. The user should therefore add a delay

equivalent to at least 2 bits after the data payload has been transmitted before switching off the PA (i.e. before stopping the transmission).

## 12.5 Reducing Spurious Emission and Modulation Bandwidth

Modulation bandwidth and spurious emission are normally measured with the PA continuously on and a repeated test sequence.

In cases where the modulation bandwidth and spurious emission are measured with the *CC1070* switching from power down mode to TX mode, a **PA ramping** sequence could be used to minimize modulation bandwidth and spurious emission.

PA ramping should then be used both when switching the PA on and off. A linear PA ramping sequence can be used where register PA\_POWER is changed from 00h to 0Fh and then from 50h to the register setting, which gives the desired output power (e.g. C0h for +5 dBm output power at 868 MHz operation). The longer the time per PA ramping step the better, but setting the total PA ramping time equal to 2 bit periods is a good compromise between performance and PA ramping time

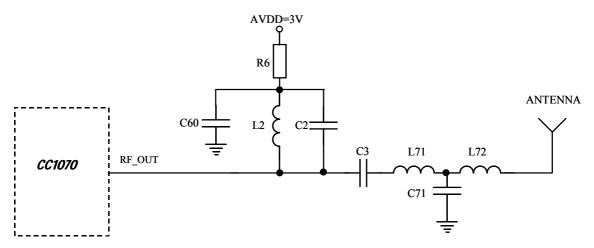

## 13 Output Matching and Filtering

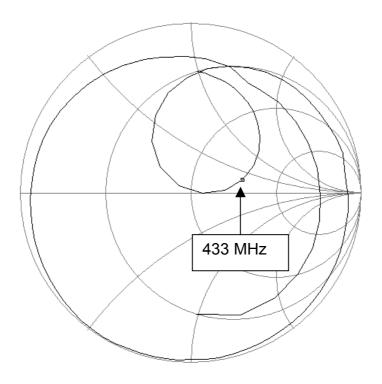

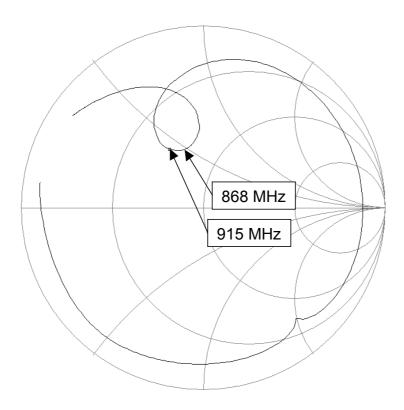

When designing the impedance matching network for the *CC1070* the circuit must be matched correctly at the harmonic frequencies as well as at the fundamental tone. A recommended matching network is shown in Figure 14. Component values for various frequencies are given in Table 15. Component values for other frequencies can be found using the SmartRF® Studio software.

It is important to remember that the physical layout and the components used contribute significantly to the reflection

coefficient, especially at the higher harmonics. For this reason, the frequency response of the matching network should be measured and compared to the response of the TI reference design. Refer to Figure 15 and Table 16 as well as Figure 16 and Table 17.

A recommended application circuit is available from the TI web site (CC1070EM).

| Item | 433 MHz               | 868 MHz               | 915 MHz               |

|------|-----------------------|-----------------------|-----------------------|

| C2   | 2.2 pF, 5%, NP0, 0402 | 1.5 pF, 5%, NP0, 0402 | 1.5 pF, 5%, NP0, 0402 |

| C3   | 5.6 pF, 5%, NP0, 0402 | 10 pF, 5%, NP0, 0402  | 10 pF, 5%, NP0, 0402  |

| C60  | 220 pF, 5%, NP0, 0402 | 220 pF, 5%, NP0, 0402 | 220 pF, 5%, NP0, 0402 |

| C71  | 4.7 pF, 5%, NP0, 0402 | 3.3 pF, 5%, NP0, 0402 | 3.3 pF, 5%, NP0, 0402 |

| L2   | 22 nH, 5%, 0402       | 6.8 nH, 5%, 0402      | 6.8 nH, 5%, 0402      |

| L70  | 47 nH, 5%, 0402       | 12 nH, 5%, 0402       | 12 nH, 5%, 0402       |

| L71  | 47 nH, 5%, 0402       | 12 nH, 5%, 0402       | 12 nH, 5%, 0402       |

| R6   | 82 Ω, 5%, 0402        | 82 Ω, 5%, 0402        | 82 Ω, 5%, 0402        |

Table 15. Component values for the matching network described in Figure 14 (DNM = Do Not Mount).

Figure 14. Output matching network

Figure 15. Typical optimum PA load impedance, 433 MHz. The frequency is swept from 300 MHz to 2500 MHz. Values are listed in Table 16

| Frequency (MHz) | Real (Ohms) | Imaginary (Ohms) |

|-----------------|-------------|------------------|

| 433             | 91          | 16               |

| 866             | 80          | -323             |

| 1299            | 1.1         | -54              |

| 1732            | 0.4         | -23              |

| 2165            | 1.3         | -5.3             |

Table 16. Impedances at the first 5 harmonics (433 MHz matching network)

Figure 16. Typical optimum PA load impedance, 868/915 MHz. The frequency is swept from 300 MHz to 2800 MHz. Values are listed in Table 17

| Frequency (MHz) | Real (Ohms) | Imaginary (Ohms) |

|-----------------|-------------|------------------|

| 868             | 34          | 25               |

| 915             | 28          | 21               |

| 1736            | 84          | -232             |

| 1830            | 31          | -130             |

| 2604            | 3.3         | -4.7             |

| 2745            | 2.6         | 2.3              |

Table 17. Impedances at the first 3 harmonics (868/915 MHz matching network)

## 14 Frequency Synthesizer

## 14.1 VCO, Charge Pump and PLL Loop Filter

The VCO is completely integrated and operates in the 1608 – 1880 MHz range. A frequency divider is used to get a frequency in the UHF range (402 – 470 and 804 – 940 MHz). The *BANDSELECT* bit in the *ANALOG* register selects the frequency band.

The VCO frequency is given by:

$$f_{VCO} = f_{ref} \cdot \left(3 + \frac{FREQ + 0.5 \cdot DITHER}{8192}\right)$$

The VCO frequency is divided by 2 and by 4 to generate frequencies in the two bands, respectively.

The VCO sensitivity (sometimes referred to as VCO gain) varies over frequency and operating conditions. Typically the VCO sensitivity varies between 12 and 36 MHz/V. For calculations the geometrical mean at 21 MHz/V can be used. The PLL calibration (explained below) measures the actual VCO sensitivity and adjusts the charge pump current accordingly to achieve correct PLL loop gain and bandwidth (higher charge pump current when VCO sensitivity is lower).

The following equations can be used for calculating PLL loop filter component values, see Figure 3, for a desired PLL loop bandwidth, BW:

C7 = 3037 (

$$f_{ref}$$

/ BW<sup>2</sup>) –7 [pF]

R2 = 7126 (BW /  $f_{ref}$ ) [kΩ]

C6 = 80.75 ( $f_{ref}$  / BW<sup>2</sup>) [nF]

R3 = 21823 (BW /  $f_{ref}$ ) [kΩ]

C8 = 839 ( $f_{ref}$  / BW<sup>2</sup>) –6 [pF]

Define a minimum PLL loop bandwidth as  ${\rm BW_{min}} = \sqrt{80.75 \cdot f_{ref} / 220}$ . If  ${\rm BW_{min}} > {\rm Baud\ rate/3}$  then set  ${\rm BW} = {\rm BW_{min}}$  and if  ${\rm BW_{min}} < {\rm Baud\ rate/3}$  then set  ${\rm BW} = {\rm Baud}$

There are two special cases when using the recommended 14.7456 MHz crystal:

rate/3 in the above equations.

1) If the data rate is 4.8 kBaud or below and the RF operating frequency is in the 402 – 470 MHz frequency range the following loop filter components are recommended:

C6 = 220 nF C7 = 8200 pF C8 = 2200 pF  $R2 = 1.5 \text{ k}\Omega$  $R3 = 4.7 \text{ k}\Omega$

2) If the data rate is 4.8 kBaud or below and the RF operating frequency is in the 804 – 940 MHz frequency range the following loop filter components are recommended:

C6 = 100 nF C7 = 3900 pF C8 = 1000 pF R2 = 2.2 k $\Omega$ R3 = 6.8 k $\Omega$

After calibration the PLL bandwidth is set by the *PLL\_BW* register in combination with the external loop filter components calculated above. The *PLL\_BW* can be found from

$$PLL_BW = 146 + 16 \log_2(f_{ref}/7.126)$$

where f<sub>ref</sub> is the reference frequency (in MHz). The PLL loop filter bandwidth increases with increasing *PLL\_BW* setting.

After calibration the applied charge pump current (CHP\_CURRENT[3:0]) can be read in the STATUS1 register. The charge pump current is approximately given by:

$$I_{CHP} = 16 \cdot 2^{CHP} - \frac{CURRENT}{4} \left[ uA \right]$$