## MOS INTEGRATED CIRCUIT

# $\mu$ PD168117A

# 7-CHANNEL H-BRIDGE DRIVER WITH A MICRO STEP FUNCTION SUPPORTING PULSE INPUT

#### **DESCRIPTION**

The  $\mu$  PD168117A is a 7-channel H-bridge driver with a micro step function supporting pulse input that consists of a CMOS control circuit and a MOS output stage. It can reduce the current consumption and the voltage loss at the output stage compared with a conventional driver using bipolar transistors, thanks to employment of a MOS process. Moreover, at the  $\mu$  PD168117A, micro step control of 128 divisions can perform stepping motor drive by the pulse input, and motor can be driven by low noise and low vibration.

The package is a 64-pin FLGA that helps reduce the mounting area and height.

The  $\mu$  PD168117A can be used to drive two stepping motors, or two DC motors and one coil.

#### **FEATURES**

- Seven H-bridge circuits employing power MOS FET

- · Low-voltage driving

$V_{DD} = 2.7 \text{ to } 3.6 \text{ V}$

$V_M = 2.7 \text{ to } 5.5 \text{ V}$

- Output on-state resistance: 1.0  $\Omega$  TYP., 1.5  $\Omega$  MAX. (sum of top and bottom stage, ch1 to ch4, and ch7) 1.5  $\Omega$  TYP., 2.0  $\Omega$  MAX. (sum of top and bottom stage, ch5 and ch6)

- PWM output (ch1 to ch6), linear output (ch7)

- Output current

<ch1 to ch6>

DC current: 0.4 A/ch (when each channel is used independently)

Peak current: 0.7 A/ch (when each channel is used independently)

<ch7>

DC current: 0.5 A/ch (when used independently)

Peak current: 0.7 A/ch (when used independently)

- Input logic frequency: 150 kHz supported

- Under-voltage lockout circuit

Shuts down the internal circuit at VDD = 1.7 V TYP.

• Overheat protection circuit

Operates at 150°C or more and shuts down internal circuitry.

• Mounted on 64-pin FLGA (□6 mm, 0.65 mm pitch)

#### **ORDERING INFORMATION**

| Part Number                 | Package                     | Packing Type         |

|-----------------------------|-----------------------------|----------------------|

| μ PD168117AFC-BA2-E1-A Note | 64-pin plastic FLGA (6 x 6) | Embossed-type taping |

Note Pb-free (This product does not contain Pb in external electrode and other parts.)

The information in this document is subject to change without notice. Before using this document, please confirm that this is the latest version. Not all products and/or types are available in every country. Please check with an NEC Electronics sales representative for availability and additional information.

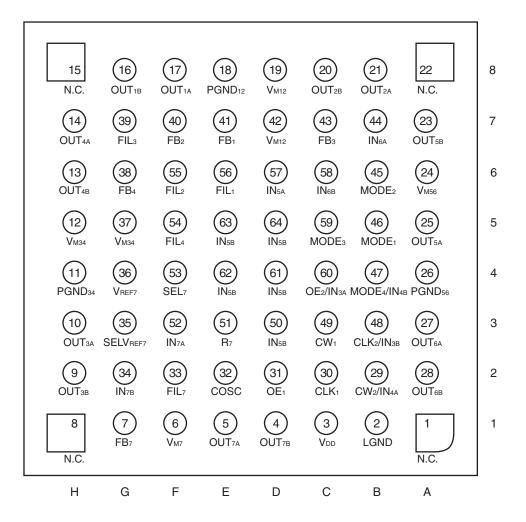

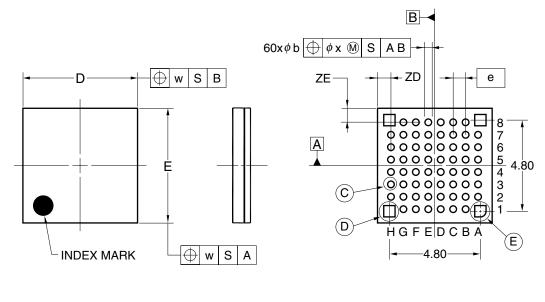

## 1. PIN CONFIGURATION (Bottom View)

Package: 64-pin plastic FLGA (6 x 6)

Cautions Be sure to connect all of the pins which have more than one.

2

## 2. PIN FUNCTIONS

(1/2)

3

|    |         | 1                    | (1/2)                                                                     |

|----|---------|----------------------|---------------------------------------------------------------------------|

| F  | Pin No. | Pin Name             | Function                                                                  |

| 1  | A1      | N.C.                 | -                                                                         |

| 2  | B1      | LGND                 | Logic block GND pin                                                       |

| 3  | C1      | V <sub>DD</sub>      | Logic block power supply pin                                              |

| 4  | D1      | OUT <sub>7B</sub>    | H-bridge 7 output pin B                                                   |

| 5  | E1      | OUT <sub>7A</sub>    | H-bridge 7 output pin A                                                   |

| 6  | F1      | V <sub>M7</sub>      | H-bridge 7 power supply pin                                               |

| 7  | G1      | FB <sub>7</sub>      | Current detection resistor connection pin 7                               |

| 8  | H1      | N.C.                 | -                                                                         |

| 9  | H2      | ОUТзв                | H-bridge 3 output pin B                                                   |

| 10 | H3      | ОUТза                | H-bridge 3 output pin A                                                   |

| 11 | H4      | PGND34               | H-bridge 3, H-bridge 4 GND pin                                            |

| 12 | H5      | V <sub>M34</sub>     | H-bridge 3, H-bridge 4 power supply pin                                   |

| 13 | H6      | OUT <sub>4B</sub>    | H-bridge 4 output pin B                                                   |

| 14 | H7      | OUT <sub>4A</sub>    | H-bridge 4 output pin A                                                   |

| 15 | H8      | N.C.                 | -                                                                         |

| 16 | G8      | OUT <sub>1B</sub>    | H-bridge 1 output pin B                                                   |

| 17 | F8      | OUT <sub>1A</sub>    | H-bridge 1 output pin A                                                   |

| 18 | E8      | PGND <sub>12</sub>   | H-bridge 1, H-bridge 2 GND pin                                            |

| 19 | D8      | V <sub>M12</sub>     | H-bridge 1, H-bridge 2 power supply pin                                   |

| 20 | C8      | OUT <sub>2B</sub>    | H-bridge 2 output pin B                                                   |

| 21 | В8      | OUT <sub>2A</sub>    | H-bridge 2 output pin A                                                   |

| 22 | A8      | N.C.                 | _                                                                         |

| 23 | A7      | OUT <sub>5B</sub>    | H-bridge 5 output pin B                                                   |

| 24 | A6      | V <sub>M56</sub>     | H-bridge 5, H-bridge 6 power supply pin                                   |

| 25 | A5      | OUT5A                | H-bridge 5 output pin A                                                   |

| 26 | A4      | PGND <sub>56</sub>   | H-bridge 5, H-bridge 6 GND pin                                            |

| 27 | A3      | OUT <sub>6A</sub>    | H-bridge 6 output pin A                                                   |

| 28 | A2      | OUT <sub>6B</sub>    | H-bridge 6 output pin B                                                   |

| 29 | B2      | CW2/IN4A             | H-bridge 3, H-bridge 4 driving direction input pin/H-bridge 4 input pin A |

| 30 | C2      | CLK <sub>1</sub>     | H-bridge 1, H-bridge 2 CLK input pin                                      |

| 31 | D2      | OE <sub>1</sub>      | H-bridge 1, H-bridge 2 output enable pin                                  |

| 32 | E2      | cosc                 | Chopping frequency setting capacitor connection pin                       |

| 33 | F2      | FIL <sub>7</sub>     | Amplifier operation stabilizing filter connection pin                     |

| 34 | G2      | IN <sub>7B</sub>     | H-bridge 7 input pin B                                                    |

| 35 | G3      | SELV <sub>REF7</sub> | ch7 reference voltage setup selection pin                                 |

| 36 | G4      | V <sub>REF7</sub>    | ch7 reference voltage external input pin                                  |

| 37 | G5      | V <sub>M34</sub>     | H-bridge 3, H-bridge 4 power supply pin                                   |

| 38 | G6      | FB4                  | Current detection resistor connection pin 4                               |

(2/2)

|    |        |                                     | (2/2)                                                           |

|----|--------|-------------------------------------|-----------------------------------------------------------------|

| Р  | in No. | Pin Name                            | Function                                                        |

| 39 | G7     | FIL <sub>3</sub>                    | Filter capacitor connection pin 3                               |

| 40 | F7     | FB <sub>2</sub>                     | Current detection resistor connection pin 2                     |

| 41 | E7     | FB <sub>1</sub>                     | Current detection resistor connection pin 1                     |

| 42 | D7     | V <sub>M12</sub>                    | H-bridge 1, H-bridge 2 power supply pin                         |

| 43 | C7     | FB₃                                 | Current detection resistor connection pin 3                     |

| 44 | В7     | IN <sub>6A</sub>                    | H-bridge 6 input pin A                                          |

| 45 | В6     | MODE <sub>2</sub>                   | Mode selection pin 2                                            |

| 46 | B5     | MODE <sub>1</sub>                   | Mode selection pin 1                                            |

| 47 | B4     | MODE <sub>4</sub> /IN <sub>4B</sub> | Mode selection pin 4/H-bridge 4 input pin B                     |

| 48 | В3     | CLK <sub>2</sub> /IN <sub>3B</sub>  | H-bridge 3, H-bridge 4 CLK input pin/H-bridge 3 input pin B     |

| 49 | C3     | CW <sub>1</sub>                     | H-bridge 1, H-bridge 2 driving direction input pin              |

| 50 | D3     | IN <sub>5B</sub>                    | H-bridge 5 input pin B                                          |

| 51 | E3     | R <sub>7</sub>                      | Amplifier operation stabilizing resistor connection pin         |

| 52 | F3     | IN <sub>7A</sub>                    | H-bridge 7 input pin A                                          |

| 53 | F4     | SEL <sub>7</sub>                    | ch7 excitation mode selection pin                               |

| 54 | F5     | FIL4                                | Filter capacitor connection pin 4                               |

| 55 | F6     | FIL <sub>2</sub>                    | Filter capacitor connection pin 2                               |

| 56 | E6     | FIL <sub>1</sub>                    | Filter capacitor connection pin 1                               |

| 57 | D6     | IN <sub>5A</sub>                    | H-bridge 5 input pin A                                          |

| 58 | C6     | IN <sub>6B</sub>                    | H-bridge 6 input pin B                                          |

| 59 | C5     | MODE <sub>3</sub>                   | Mode selection pin 3                                            |

| 60 | C4     | OE2/IN3A                            | H-bridge 3, H-bridge 4 output enable pin/H-bridge 3 input pin A |

| 61 | D4     | IN <sub>5B</sub>                    | H-bridge 5 input pin B                                          |

| 62 | E4     | IN <sub>5B</sub>                    | H-bridge 5 input pin B                                          |

| 63 | E5     | IN <sub>5B</sub>                    | H-bridge 5 input pin B                                          |

| 64 | D5     | IN <sub>5B</sub>                    | H-bridge 5 input pin B                                          |

4

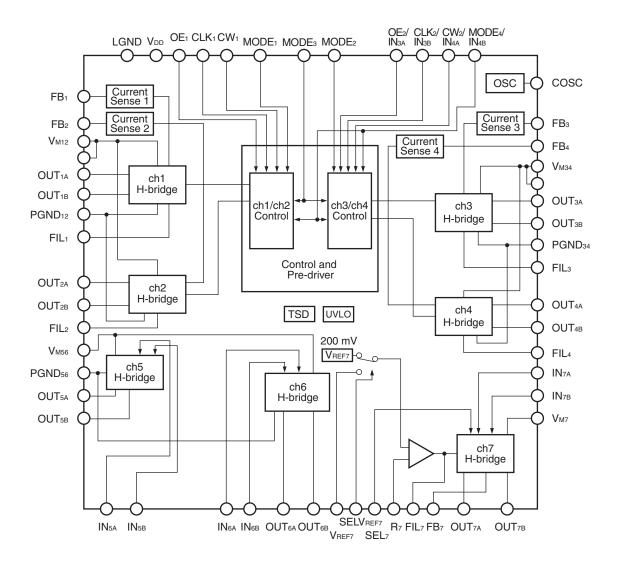

## 3. BLOCK DIAGRAM

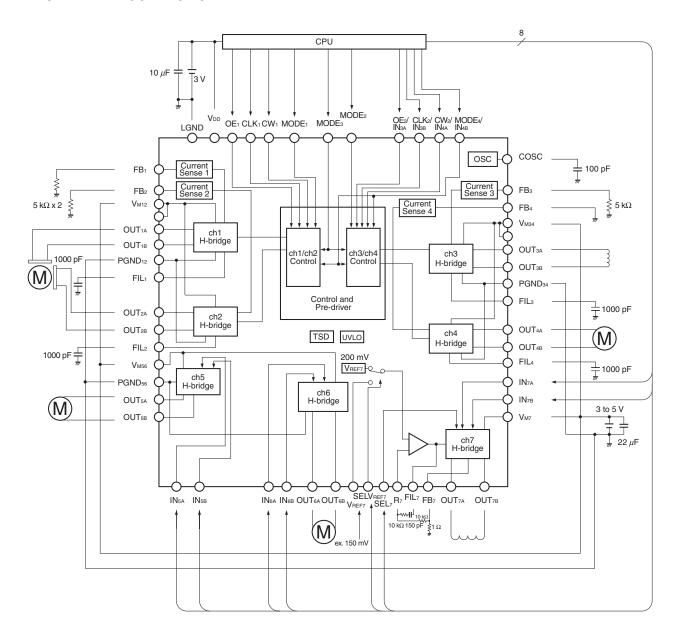

## 4. STANDARD CONNECTION EXAMPLE

Cautions 1. Be sure to connect all of the pins which have more than one.

2. The constants shown in the above diagram are provided as examples only. Perform design based on thorough evaluation with the actual machine.

## 5. FUNCTION OPERATION TABLE

#### 5.1 Power Save Function

This IC can be placed in the power-save mode by making MODE<sub>1</sub>, MODE<sub>2</sub>, MODE<sub>3</sub>, and MODE<sub>4</sub> high level.

This function allows holding of the excitation position when the stepping motor mode is selected and the operation to be started from where the excitation position is held when the power-save mode is cleared. In the power-save mode, the current consumption is reduced to 20  $\mu$ A TYP. because the internal circuits other than UVLO are stopped.

The operation modes of ch1 to ch4 can be set by a combination of MODE<sub>1</sub> to MODE<sub>4</sub>. For the combination of the MODE pins, refer to **Table 5–1. MODE Pin Truth Table**.

Table 5-1. Mode Pin Truth Table

| MODE <sub>1</sub> | MODE <sub>2</sub> | MODE₃ | MODE <sub>4</sub>      | Operation Mode              |                             |

|-------------------|-------------------|-------|------------------------|-----------------------------|-----------------------------|

|                   |                   |       | (/IN <sub>4B</sub> )   | ch1, ch2                    | ch3, ch4                    |

| L                 | L                 | L     | IN <sub>4B</sub> input | 2-phase excitation          | General-purpose driving     |

| L                 | L                 | Н     |                        | 1-2 phase excitation        | (current limiting)          |

| L                 | Н                 | L     |                        | Micro step                  |                             |

| L                 | Н                 | Н     | L                      | 2-phase excitation          | 2-phase excitation          |

| L                 | Н                 | Н     | Н                      | 1-2 phase excitation        | 1-2 phase excitation        |

| н                 | L                 | L     | L                      | 2-phase excitation (current | 2-phase excitation (current |

|                   |                   |       |                        | limiting)                   | limiting)                   |

| Н                 | L                 | L     | Н                      | 1-2 phase excitation        | 1-2 phase excitation        |

|                   |                   |       |                        | (current limiting)          | (current limiting)          |

| Н                 | L                 | Н     | L                      | 2-phase excitation          | Micro step                  |

| Н                 | L                 | Н     | Н                      | 1-2 phase excitation        | Micro step                  |

| Н                 | Н                 | L     | L                      | Micro step                  | 2-phase excitation          |

| Н                 | Н                 | L     | Н                      | Micro step                  | 1-2 phase excitation        |

| Н                 | Н                 | Н     | L                      | Micro step                  | Micro step                  |

| Н                 | Н                 | Н     | Н                      | Power save mode             |                             |

Remark H: High level, L: Low level

## 5.2 ch1, ch2 (Dedicated to Stepping Motor)

| CLK <sub>1</sub> | CW <sub>1</sub> | OE <sub>1</sub> | Operation Mode                                        |

|------------------|-----------------|-----------------|-------------------------------------------------------|

| ſ                | L               | Н               | Pulse progress, CW mode                               |

| ¬_               | L               | Н               | Pulse progress, CW mode                               |

|                  | Н               | Н               | Pulse progress, CCW mode                              |

| 7_               | Н               | Н               | Pulse progress, CCW mode                              |

| х                | х               | L               | Output Hi-Z (The internal follows the above-mentioned |

|                  |                 |                 | mode of operation)                                    |

Remark x: High level or low level, Hi-Z: High impedance

## 5.3 ch3, ch4 (Selecting Stepping Motor, DC Motor and Coil Driving)

<Stepping motor drive mode>

| CLK <sub>2</sub> | CW <sub>2</sub> | OE <sub>2</sub> | Operation Mode                                        |

|------------------|-----------------|-----------------|-------------------------------------------------------|

|                  | L               | Н               | Pulse progress, CW mode                               |

| Ţ                | L               | Н               | Pulse progress, CW mode                               |

| ſ                | Н               | Н               | Pulse progress, CCW mode                              |

| Ţ                | Н               | Н               | Pulse progress, CCW mode                              |

| х                | х               | L               | Output Hi-Z (The internal follows the above-mentioned |

|                  |                 |                 | mode of operation)                                    |

<General-purpose drive mode>

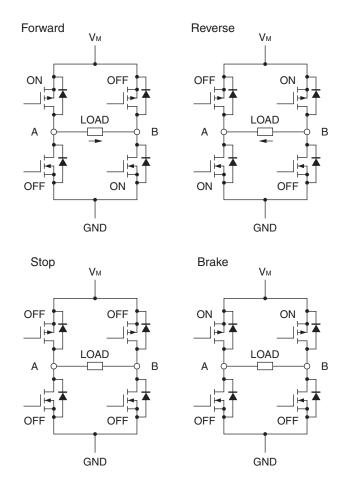

| IN3A/IN4A | IN <sub>3B</sub> /IN <sub>4B</sub> | OUT3A/OUT4A | OUT3B/OUT4B | Operation Mode |

|-----------|------------------------------------|-------------|-------------|----------------|

| L         | L                                  | Z           | Z           | Stop           |

| L         | Н                                  | L           | H Note      | Reverse        |

| Н         | L                                  | H Note      | L           | Forward        |

| Н         | Н                                  | Н           | Н           | Brake          |

**Note** When the  $\mu$  PD168117A is used for constant-current driving (when a sense resistor is connected to the FB pin), chopping driving is performed.

Remark Z: Output high impedance

## 5.4 ch5, ch6

| IN5A/IN6A | IN <sub>5B</sub> /IN <sub>6B</sub> | OUT5A/OUT6A | OUT5B/OUT6B | Operation Mode |

|-----------|------------------------------------|-------------|-------------|----------------|

| L         | L                                  | Z           | Z           | Stop           |

| L         | Н                                  | L           | Н           | Reverse        |

| Н         | L                                  | Н           | L           | Forward        |

| Н         | Н                                  | Н           | Н           | Brake          |

Data Sheet S17486EJ1V0DS

9

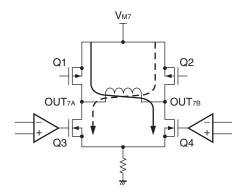

5.5 ch7

| IN <sub>7A</sub> | IN <sub>7B</sub> | OUT7A    | OUT <sub>7B</sub> | H-bridge Output State |     |          |          |

|------------------|------------------|----------|-------------------|-----------------------|-----|----------|----------|

|                  |                  |          |                   | Q1                    | Q2  | Q3       | Q4       |

| L                | L                | Z        | Z                 | OFF                   | OFF | OFF      | OFF      |

| L                | Н                | L        | Н                 | OFF                   | ON  | ON       | OFF      |

|                  |                  | (linear) |                   |                       |     | (linear) |          |

| Н                | L                | Н        | L                 | ON                    | OFF | OFF      | ON       |

|                  |                  |          | (linear)          |                       |     |          | (linear) |

| Н                | Н                | Н        | Н                 | ON                    | ON  | OFF      | OFF      |

## 5.6 SEL7 Pin

The current that flows into ch7 can be changed by setting the SEL7 pin.

| SEL <sub>7</sub> | Operation Mode                                                      |

|------------------|---------------------------------------------------------------------|

| L                | Weak excitation mode (Current 2/3 of the normal setting flows.)     |

| Н                | Normal operation mode (Comparison operation with reference voltage) |

#### 5.7 Reference Voltage Settings

The external setting mode, in which the reference voltage is input to VREF7 externally, and the internal setting mode, in which the internal reference voltage is used, can be switched using the SELVREF7 pin.

When using the external setting mode, the voltage which will become reference voltage must be applied to the VREF7 pin.

The functions for the  $SEL_7$  pin will be enabled, regardless of the external/internal setting mode. The voltage (when external setting mode is set), and the 200 mV (when the internal setting mode is set) that are applied to the  $V_{REF7}$  pin are equivalent to normal operation mode ( $SEL_7 = H$ ).

| SELV <sub>REF7</sub> | Operation Mode                                           |

|----------------------|----------------------------------------------------------|

| L                    | External setting mode (Voltage must be applied to VREF7) |

| Н                    | Internal setting mode (200 mV setting)                   |

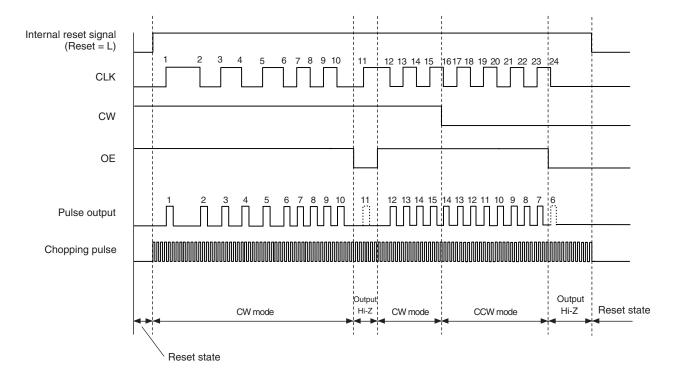

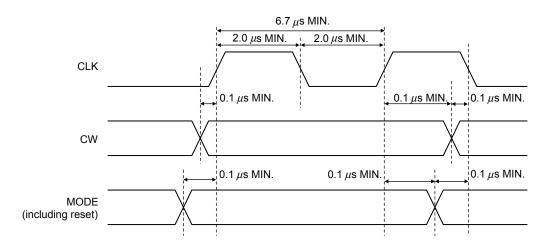

#### 6. COMMAND INPUT TIMING CHART

Figure 6-1. In The Micro Step Mode

**Remark** The motor excitation output is equivalent to the pulse output. The excitation position of the motor is changed by the rising edge timing of the pulse output (equals the rising or falling edges of CLK).

#### 7. FUNCTIONAL DEPLOYMENT

#### 7.1 Reset Function

This whole IC can be changed into a reset state by setting all of MODE<sub>1</sub> to MODE<sub>4</sub> to H, and all of IN<sub>5A</sub>, IN<sub>5B</sub>, IN<sub>6A</sub>, IN<sub>6B</sub>, IN<sub>7A</sub>, and IN<sub>7B</sub> to L. In the state of reset, an output will be in Hi-Z state, and since it stops operation of an internal circuit, it can make self-consumption current below 1  $\mu$ A.

Be sure to perform a reset operation.

In the reset operation, the internal circuitry is stopped whenever possible, so that the self current consumption can be reduced. When the external input signal is stopped, the current consumption can be lowered to 1  $\mu$ A MAX. Immediately after release of reset, excitation is started from the position where the current of ch1 is 100% and the current of ch2 is 0%, in the micro step drive mode and 1-2 phase excitation drive mode. In the 2-phase excitation drive mode, excitation is started from the position where the currents of ch1 and ch2 are 100%.

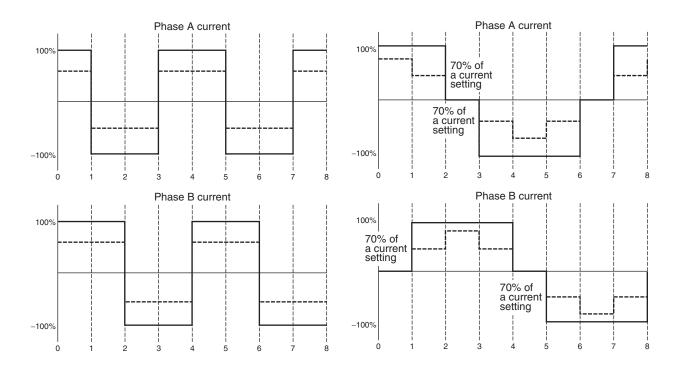

## 7.2 2-phase Excitation Drive Mode and 1-2 Phase Excitation Drive Mode

In the 2-phase excitation drive mode, current of  $\pm 100\%$  is allowed to flow into ch1 and ch2 simultaneously. In the 1-2 phase excitation drive mode, the motor can be driven at a higher torque by allowing a current to flow so that the synthesized torque of ch1 and ch2 is the same as the torque at phase 1 position. The 2-phase excitation, 1-2 phase excitation, and micro step driving modes are selected by the MODE<sub>1</sub> to MODE<sub>4</sub> pins.

Note that 100% (= saturation drive mode) and a mode in which the current set by the sense resistor is used can be selected by the MODE pin. Current control is performed by chopping drive.

## 7.3 Micro Step Drive Mode of Stepping Motor

The current flowing into the H-bridge is constant by using a vector value so that one period can be stopped in 1/128 steps. This function is provided to realize high-accuracy positioning control of a stepping motor.

To realize this micro step driving, the following functions are internally realized by the driver.

- Detection of current flowing into each channel by sense resistor as voltage value

- Synthesizing half the dummy sine waveform generated by the internal D/A with PWM oscillation waveform for chopping operation

- Driver stage performing PWM drive based on result of comparing detected voltage and synthesized waveform

Because the internal dummy sine wave consists of 128 steps per period, it can be used to drive a stepping motor using 128 divisions. The micro step drive mode, 2-phase excitation drive mode, and 1-2 phase excitation drive mode can be selected by using external pins.

Figure 7-1. Concept of Micro Step Drive Operation

#### 7.4 Input Signals (CLK, OE and CW pins, stepping motor control methods)

The motor is driven by the pulses input to the CLK<sub>1</sub> (CLK<sub>2</sub>) pin. The pulses advance by one at the rising and falling edges of the CLK<sub>1</sub> (CLK<sub>2</sub>) signal.

When the CLK<sub>1</sub> (CLK<sub>2</sub>) pin is fixed to low levels, the internal excitation positions do not progress, regardless of the input status of the OE<sub>1</sub> (OE<sub>2</sub>) pin.

Since 1 electrical angle cycle is divided by 128, it equals 1 electrical angle cycle because of the 64-clock input.

Since both edges are used for control, the pulse intervals that are output rely on the pulse duty which is input. It is suggested that pulses with a duty of 50% should be input.

The rotational direction of the motor is set by CW<sub>1</sub> (CW<sub>2</sub>).

In CW mode, the current for ch2 (ch4) is output delayed by a 90° phase in relation to the current for ch1 (ch3).

In CCW mode, the current for ch2 (ch4) is output advanced by a 90° phase in relation to the current for ch1 (ch3).

## 7.5 Output Enable (OE) Pin

The OE1 (OE2) pin can be used to forcibly stop pulse output of ch1 and ch2 (or ch3 and ch4).

When  $OE_1$  ( $OE_2$ ) = L, the output is forcibly made to go into Hi-Z. Moreover, since an internal excitation position can make it go on also at  $OE_1$  ( $OE_2$ ) pin = L, an internal excitation position advances in inputting a pulse into  $CLK_1$  ( $CLK_2$ ) pin.

The internal information will be held if  $OE_1$  ( $OE_2$ ) = L and  $CLK_1$  ( $CLK_2$ ) pin are fixed to low level. Motor position information is memorized unless it is reset. In performing stepping motor control, be sure to give as  $OE_1$  ( $OE_2$ ) = H.

#### 7.6 Current Detection Resistor Connection (FB) Pin

#### (1) ch1 to ch4

The current detection resistor is connected when current driving is necessary. It is used for micro step driving and solenoid driving. The peak value (at 100% current of ch1 (ch3) or ch2 (ch4)) of output current is decided by the resistance R<sub>FB</sub> linked to FB<sub>1</sub> (FB<sub>3</sub>) and FB<sub>2</sub> (FB<sub>4</sub>). This IC contains the reference power supply V<sub>REF</sub> for current value comparison (500 mV TYP.) in the internal, and performs the drive which makes the current value acquired from R<sub>FB</sub> and V<sub>REF</sub> an output current peak value.

The current that flows into the output is {500 mV (reference voltage) /FB pin resistance x 1000}.

Peak output current:  $I_{MAX}(A) \cong V_{REF}(V) \div R_{FB}(\Omega) \times 1000$

Example) Where FB = 4.7 k $\Omega$  Output current = 500 (mV) /4.7 (k $\Omega$ ) x 1000  $\cong$  106.4 (mA)

This means constant current driving of about 106.4 mA.

When current driving is not performed, connect the FB pin to GND.

## (2) ch7

Connect the current detection circuit between the source of the driver low side and GND. Because the circuit is configured to detect current directly, connect a detection resistor of low resistance (1  $\Omega$  maximum).

The current that flows into the output is  $\{200 \text{ mV (reference voltage) /FB}_7 \text{ pin resistance} \}$  (when  $SEL_7 = H$ ).

Output current:  $I_{MAX}(A) \cong V_{REF}(V) \div R_{FB}(\Omega)$

Example) Where FB7 = 0.5  $\Omega$  Output current = 200 (mV) /0.5 ( $\Omega$ ) = 400 (mA)

This means constant current driving of 400 mA.

Because only ch7 employs the linear drive mode and directly detects the output current, the current accuracy is determined only by the external resistor and the offset of the current control amplifier.

The above example shows (SELVREF7 = H) using the internal reference voltage. When applying reference voltage externally, set SELVREF7 to L, then apply voltage to the VREF7 pin. The output current can be calculated by transposing 200 mV in the computational expression.

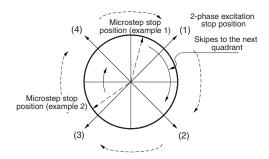

## 7.7 Selecting 2-phase Excitation/Micro Step Drive Mode

The 2-phase excitation, 1-2 phase excitation, or micro step drive mode can be selected by using the MODE<sub>1</sub> to MODE<sub>4</sub> pins. Refer to **Table 5–1. Mode Pin Truth Table** for details.

Immediately after release of reset, the IC is initialized. In the 1-2 phase excitation and micro step drive mode, excitation is started from the position where the output current of ch1 (ch3) is 100% and output current of ch2 (ch4) is 0%. In the 2-phase excitation drive mode, excitation is started from the position where the currents of both ch1 (ch3) and ch2 (ch4) are +100%.

When the mode is changed from the micro step driving to the 2-phase excitation (or 1-2 phase excitation), the position of micro step is held until CLK is input.

When the rotation direction does not change, pulse output is started by the first CLK input, the position is skipped to the 2-phase position of the next quadrant (or to the closest 1-2 phase position at the rotation direction destination), and driving is started.

When the rotation direction changes, it is skipped to 2-phase position of the next quadrant, or 1-2-phase position to the direction which changed, and a drive is started.

Figure 7–2. Concept of Change Operation, Micro Step Driving ↔ 2-phase Excitation (1-2 Phase Excitation)

#### 7.8 Under-voltage Lockout (UVLO) Circuit

This function is to forcibly stop the operation of the IC to prevent malfunctioning if V<sub>DD</sub> drops. When UVLO operates, the IC is in the reset status. If V<sub>DD</sub> drops abruptly in the order of several  $\mu$ s, this function may not operate.

## 7.9 Overheat Protection (TSD) Circuit

This function is to forcibly stop the operation of the IC to protect it from destruction due to overheating if the chip temperature of the IC rises.

The overheat protection circuit operates when the chip temperature rises to 150°C or more. When overheat is detected, all the circuits are stopped. When reset state or when UVLO is detected, the overheat protection circuit does not operate.

## 7.10 Power Up Sequence

This IC has a circuit that prevents current from flowing into the  $V_M$  pin when  $V_{DD} = 0$  V. Therefore, the current that flows into the  $V_M$  pin is cut off 1  $\mu$ A MAX. when  $V_{DD} = 0$  V.

## 8. NOTE ON CORRECT USE

## 8.1 Transmitting Data

Data input at reset state is ignored.

## 8.2 Pin Processing of Unused Circuit

The input/output pins of an unused circuit must be processed as specified below.

A V<sub>M</sub> power supply pin is provided for each output circuit. The current consumption of the internal circuit can be reduced by dropping the V<sub>M</sub> power of the unused circuit to GND. However, if there are multiple power supply pins, be sure to connect all of them to the same potential.

## <ch1, ch2>

Lower OE<sub>1</sub>, CLK<sub>1</sub>, and CW<sub>1</sub>.

Open FIL1, FIL2, OUT1A, OUT1B, OUT2A, and OUT2B.

Connect FB1 and FB2 to GND.

#### <ch3, ch4>

Set the general-purpose drive mode.

Lower OE2/IN3A, CLK2/IN3B, CW2/IN4A.

Higher MODE<sub>4</sub>/IN<sub>4B</sub>.

Open FIL3, FIL4, OUT3A, OUT3B, OUT4A, and OUT4B.

Connect FB3 and FB4 to GND.

## <ch5, ch6>

Lower IN5A (IN6A) and IN5B (IN6B).

Open OUT5A (OUT6A) and OUT5B (OUT6B).

#### <ch7>

Lower SEL7, SELVREF7, IN7A, and IN7B.

Open OUT7A and OUT7B.

Connect VREF7, FIL7, FB7, and R7 to GND.

## 8.3 Input Pin Processing

The signal input pins for this IC are not equipped with on-chip pull down/pull up resistors. When the V<sub>DD</sub> power is on, the logic for all of the input pins must be set to either H or L.

16

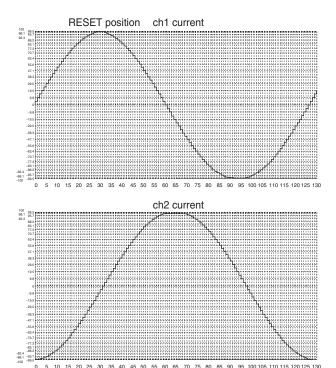

## 9. STEPPING MOTOR DRIVING WAVEFORM

Figure 9-1. 2-phase Excitation Output Mode

Figure 9–2. 1-2 Phase Excitation Output Mode

**Remark** Solid line: Output duty 100% drive, Dotted line: Current control drive (The current is in accordance with the current setting.)

$\mu$  PD168117A

Figure 9-3. Micro Step Drive Mode

**Remark** The horizontal axis of the above charts indicates the number of steps. The above charts show an example in the CW (forward) mode.

The current flowing into phases A and B is positive in the direction from OUT pin A to OUT pin B, and negative in the direction from OUT pin B to OUT pin A. Because the micro step drive mode is in 128 steps, it equals 1 electrical angle cycle.

## 10. ELECTRICAL SPECIFICATIONS

Absolute Maximum Ratings (T<sub>A</sub> = 25°C, glass epoxy 4-layer board of 100 mm x 100 mm x 1.6 mm with copper foil area of 50%)

|                                | ion area              | 01 30%)                                  |                              |      |

|--------------------------------|-----------------------|------------------------------------------|------------------------------|------|

| Parameter                      | Symbol                | Condition                                | Rating                       | Unit |

| Power supply voltage           | V <sub>DD</sub>       | Control block                            | -0.5 to +6.0                 | V    |

|                                | VM                    | Motor block                              | -0.5 to +6.0                 | V    |

| Input voltage                  | Vin                   |                                          | -0.5 to V <sub>DD</sub> +0.5 | V    |

| Output pin voltage             | Vout                  | Motor block                              | 6.2                          | V    |

| DC output current (ch1 to 6ch) | I <sub>D(DC)</sub>    | DC (during output independent operation) | ±0.4                         | A/ch |

| DC output current (ch7)        | I <sub>D(DC)</sub>    | DC (during output independent operation) | ±0.5                         | A/ch |

| Instantaneous output current   | I <sub>D(pulse)</sub> | PW < 10 ms, Duty Cycle ≤ 20%             | ±0.7                         | A/ch |

|                                |                       | (during output independent operation)    |                              |      |

| Power consumption              | Рт                    |                                          | 1.5                          | W    |

| Peak junction temperature      | Tch(MAX)              |                                          | 150                          | °C   |

| Storage temperature            | T <sub>stg</sub>      |                                          | -55 to +150                  | °C   |

**Remark** The overheat protection circuit operates at T<sub>ch</sub> > 150°C. When overheat is detected, all the circuits are stopped. The overheat protection circuit does not operate at reset or on detection of ULVO.

Caution Product quality may suffer if the absolute maximum rating is exceeded even momentarily for any parameter. That is, the absolute maximum ratings are rated values at which the product is on the verge of suffering physical damage, and therefore the product must be used under conditions that ensure that the absolute maximum ratings are not exceeded.

Recommended Operating Conditions (T<sub>A</sub> = 25°C, glass epoxy 4-layer board of 100 mm x 1.6 mm with copper foil area of 50%)

| Parameter                      | Symbol                | Condition                                | MIN. | TYP. | MAX.            | Unit |

|--------------------------------|-----------------------|------------------------------------------|------|------|-----------------|------|

| Power supply voltage           | V <sub>DD</sub>       | Control block                            | 2.7  |      | 3.6             | ٧    |

|                                | Vм                    | Motor block                              | 2.7  |      | 5.5             | V    |

| Input voltage                  | VIN                   |                                          | 0    |      | V <sub>DD</sub> | V    |

| DC output current (ch1 to 6ch) | I <sub>D(DC)</sub>    | DC (during output independent operation) | -0.3 |      | +0.3            | A/ch |

| DC output current (ch7)        | I <sub>D(DC)</sub>    | DC (during output independent operation) | -0.4 |      | +0.4            | A/ch |

| Instantaneous output current   | I <sub>D(pulse)</sub> | PW < 10 ms, Duty Cycle ≤ 20%             | -0.6 |      | +0.6            | A/ch |

|                                |                       | (during output independent operation)    |      |      |                 |      |

| Capacitor capacitance          |                       | COSC (during 300 kHz TYP. oscillation)   |      | 100  |                 | pF   |

| ch7 reference voltage input    | V <sub>REF7</sub>     |                                          | 0.1  |      | 0.7             | ٧    |

| range                          |                       |                                          |      |      |                 |      |

| Logic input frequency          | fin                   |                                          |      |      | 150             | kHz  |

| Operating temperature range    | TA                    |                                          | -10  |      | 75              | °C   |

Figure 10-1. AC timing waveform

Electrical Characteristics (Unless otherwise specified,  $T_A = 25$ °C,  $V_{DD} = 3.0 \text{ V}$ ,  $V_M = 3.0 \text{ V}$ )

| Parameter                                       | Symbol              | Condition                                              | MIN.                  | TYP. | MAX.                  | Unit |

|-------------------------------------------------|---------------------|--------------------------------------------------------|-----------------------|------|-----------------------|------|

| V <sub>DD</sub> pin current in standby mode     | IDD(STB)            | During reset                                           |                       |      | 1.0                   | μΑ   |

| V <sub>DD</sub> pin current in during operation | IDD(ACT)            | During non-reset                                       |                       |      | 5.0                   | mA   |

| High-level input current                        | Іін                 | VIN = VDD                                              |                       |      | 1.0                   | μΑ   |

| Low-level input current                         | lıL                 | Vin = 0 V                                              | -1.0                  |      |                       | μΑ   |

| High-level input voltage                        | VIH                 |                                                        | 0.7 x V <sub>DD</sub> |      |                       | V    |

| Low-level input voltage                         | VIL                 |                                                        |                       |      | 0.3 x V <sub>DD</sub> | V    |

| COSC oscillation frequency                      | fosc                | COSC = 150 pF                                          |                       | 200  |                       | kHz  |

| H-bridge on-state resistance                    | Ron                 | I <sub>M</sub> = 0.3 A, sum of upper and lower         |                       | 1.0  | 1.5                   | Ω    |

|                                                 |                     | stages (ch1 to ch4, and ch7)                           |                       |      |                       |      |

|                                                 | Ron56               | I <sub>M</sub> = 0.3 A, sum of upper and lower         |                       | 1.5  | 2.0                   | Ω    |

|                                                 |                     | stages (ch5 and ch6)                                   |                       |      |                       |      |

| Output leakage current Note1                    | I <sub>M(off)</sub> | Per V <sub>M</sub> pin, All control pin: low level     |                       |      | 1.0                   | μΑ   |

| Low-voltage detection voltage                   | V <sub>DDS</sub>    |                                                        |                       | 1.7  | 2.5                   | V    |

| Internal reference voltage Note2                | VREF                | ch1 to ch4                                             | 450                   | 500  | 550                   | mV   |

|                                                 | V <sub>REF7</sub>   | ch7, during SELV <sub>REF7</sub> = H                   | 180                   | 200  | 220                   | mV   |

| Current detection ratio Note2                   |                     | $I_{M} = 0.1$ A, with sense resistor of 5 k $\Omega$ , | 900                   | 1000 | 1100                  |      |

|                                                 |                     | ch1 to ch4                                             |                       |      |                       |      |

| Output turn-on time                             | ton                 | $R_L = 20 \Omega$ , ch1 to ch6                         | 0.02                  | 0.35 | 1.0                   | μs   |

| Output turn-off time                            | <b>t</b> off        |                                                        | 0.02                  | 0.35 | 1.0                   | μs   |

Notes 1. This IC has a circuit that prevents current from flowing into the  $V_M$  pin when  $V_{DD} = 0$  V.

2. The accuracy of the output current for ch1 to ch4 depends upon the motor that is actually used, but the current fluctuations of the IC are determined by reference voltage and current detection ratios. Assume that the total of the reference voltage VREF and current sense circuit errors are equal to ±10%.

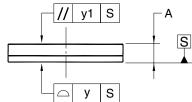

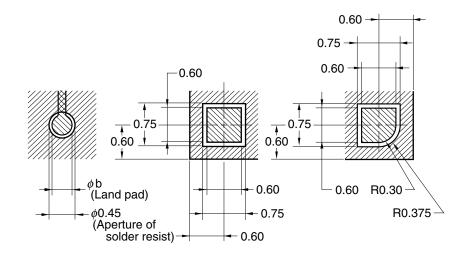

## 11. PACKAGE DRAWING

## 64-PIN PLASTIC FLGA (6x6)

DETAIL OF © PART

DETAIL OF (D) PART

DETAIL OF (E) PART

|      | (UNIT:mm)    |

|------|--------------|

| ITEM | DIMENSIONS   |

| D    | 6.00±0.10    |

| Е    | 6.00±0.10    |

| w    | 0.20         |

| е    | 0.65         |

| Α    | 0.91±0.07    |

| b    | 0.35±0.05    |

| ×    | 0.08         |

| у    | 0.10         |

| y1   | 0.20         |

| ZD   | 0.725        |

| ZE   | 0.725        |

|      | P64FC-65-BA2 |

## 12. RECOMMENDED SOLDERING CONDITIONS

The  $\mu$  PD168117A should be soldered and mounted under the following recommended conditions.

For soldering methods and conditions other than those recommended below, contact an NEC Electronics sales representative.

For technical information, see the following website.

Semiconductor Device Mount Manual (http://www.necel.com/pkg/en/mount/index.html)

## **Type of Surface Mount Device**

$\mu$  PD168117AFC-BA2-E1-A Note1: 64-pin plastic FLGA (6 x 6)

| Process         | Conditions                                                                                                                                                                                                                                                                                                                                                                                                                     | Symbol     |

|-----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|

| Infrared reflow | Package peak temperature: 260°C, Time: 60 seconds MAX. (at 220°C or higher), Count: Three times or less, Exposure limit: 3 days Note2 (after that, prebake at 125°C for 10 hours), Flux: Rosin flux with low chlorine (0.2 Wt% or below) recommended. <pre> </pre> Products other than in heat-resistant trays (such as those packaged in a magazine, taping, or non-thermal-resistant tray) cannot be baked in their package. | IR60-103-3 |

Notes 1. Pb-free (This product does not contain Pb in external electrode and other parts.)

2. After opening the dry pack, store it a 25°C or less and 65% RH or less for the allowable storage period.

Caution Do not use different soldering methods together (except for partial heating) .

#### NOTES FOR CMOS DEVICES —

#### 1 VOLTAGE APPLICATION WAVEFORM AT INPUT PIN

Waveform distortion due to input noise or a reflected wave may cause malfunction. If the input of the CMOS device stays in the area between  $V_{\rm IL}$  (MAX) and  $V_{\rm IH}$  (MIN) due to noise, etc., the device may malfunction. Take care to prevent chattering noise from entering the device when the input level is fixed, and also in the transition period when the input level passes through the area between  $V_{\rm IL}$  (MAX) and  $V_{\rm IH}$  (MIN).

## (2) HANDLING OF UNUSED INPUT PINS

Unconnected CMOS device inputs can be cause of malfunction. If an input pin is unconnected, it is possible that an internal input level may be generated due to noise, etc., causing malfunction. CMOS devices behave differently than Bipolar or NMOS devices. Input levels of CMOS devices must be fixed high or low by using pull-up or pull-down circuitry. Each unused pin should be connected to VDD or GND via a resistor if there is a possibility that it will be an output pin. All handling related to unused pins must be judged separately for each device and according to related specifications governing the device.

#### ③ PRECAUTION AGAINST ESD

A strong electric field, when exposed to a MOS device, can cause destruction of the gate oxide and ultimately degrade the device operation. Steps must be taken to stop generation of static electricity as much as possible, and quickly dissipate it when it has occurred. Environmental control must be adequate. When it is dry, a humidifier should be used. It is recommended to avoid using insulators that easily build up static electricity. Semiconductor devices must be stored and transported in an anti-static container, static shielding bag or conductive material. All test and measurement tools including work benches and floors should be grounded. The operator should be grounded using a wrist strap. Semiconductor devices must not be touched with bare hands. Similar precautions need to be taken for PW boards with mounted semiconductor devices.

#### (4) STATUS BEFORE INITIALIZATION

Power-on does not necessarily define the initial status of a MOS device. Immediately after the power source is turned ON, devices with reset functions have not yet been initialized. Hence, power-on does not guarantee output pin levels, I/O settings or contents of registers. A device is not initialized until the reset signal is received. A reset operation must be executed immediately after power-on for devices with reset functions.

#### (5) POWER ON/OFF SEQUENCE

In the case of a device that uses different power supplies for the internal operation and external interface, as a rule, switch on the external power supply after switching on the internal power supply. When switching the power supply off, as a rule, switch off the external power supply and then the internal power supply. Use of the reverse power on/off sequences may result in the application of an overvoltage to the internal elements of the device, causing malfunction and degradation of internal elements due to the passage of an abnormal current.

The correct power on/off sequence must be judged separately for each device and according to related specifications governing the device.

## **6** INPUT OF SIGNAL DURING POWER OFF STATE

Do not input signals or an I/O pull-up power supply while the device is not powered. The current injection that results from input of such a signal or I/O pull-up power supply may cause malfunction and the abnormal current that passes in the device at this time may cause degradation of internal elements. Input of signals during the power off state must be judged separately for each device and according to related specifications governing the device.

#### **Reference Documents**

NEC Semiconductor Device Reliability/Quality Control System (C10983E)

Quality Grades On NEC Semiconductor Devices (C11531E)

- The information in this document is current as of May, 2005. The information is subject to change

without notice. For actual design-in, refer to the latest publications of NEC Electronics data sheets or

data books, etc., for the most up-to-date specifications of NEC Electronics products. Not all

products and/or types are available in every country. Please check with an NEC Electronics sales

representative for availability and additional information.

- No part of this document may be copied or reproduced in any form or by any means without the prior

written consent of NEC Electronics. NEC Electronics assumes no responsibility for any errors that may

appear in this document.

- NEC Electronics does not assume any liability for infringement of patents, copyrights or other intellectual property rights of third parties by or arising from the use of NEC Electronics products listed in this document or any other liability arising from the use of such products. No license, express, implied or otherwise, is granted under any patents, copyrights or other intellectual property rights of NEC Electronics or others.

- Descriptions of circuits, software and other related information in this document are provided for illustrative

purposes in semiconductor product operation and application examples. The incorporation of these

circuits, software and information in the design of a customer's equipment shall be done under the full

responsibility of the customer. NEC Electronics assumes no responsibility for any losses incurred by

customers or third parties arising from the use of these circuits, software and information.

- While NEC Electronics endeavors to enhance the quality, reliability and safety of NEC Electronics products, customers agree and acknowledge that the possibility of defects thereof cannot be eliminated entirely. To minimize risks of damage to property or injury (including death) to persons arising from defects in NEC Electronics products, customers must incorporate sufficient safety measures in their design, such as redundancy, fire-containment and anti-failure features.

- NEC Electronics products are classified into the following three quality grades: "Standard", "Special" and "Specific".

- The "Specific" quality grade applies only to NEC Electronics products developed based on a customer-designated "quality assurance program" for a specific application. The recommended applications of an NEC Electronics product depend on its quality grade, as indicated below. Customers must check the quality grade of each NEC Electronics product before using it in a particular application.

- "Standard": Computers, office equipment, communications equipment, test and measurement equipment, audio and visual equipment, home electronic appliances, machine tools, personal electronic equipment and industrial robots.

- "Special": Transportation equipment (automobiles, trains, ships, etc.), traffic control systems, anti-disaster systems, anti-crime systems, safety equipment and medical equipment (not specifically designed for life support).

- "Specific": Aircraft, aerospace equipment, submersible repeaters, nuclear reactor control systems, life support systems and medical equipment for life support, etc.

The quality grade of NEC Electronics products is "Standard" unless otherwise expressly specified in NEC Electronics data sheets or data books, etc. If customers wish to use NEC Electronics products in applications not intended by NEC Electronics, they must contact an NEC Electronics sales representative in advance to determine NEC Electronics' willingness to support a given application.

## (Note)

- (1) "NEC Electronics" as used in this statement means NEC Electronics Corporation and also includes its majority-owned subsidiaries.

- (2) "NEC Electronics products" means any product developed or manufactured by or for NEC Electronics (as defined above).