## MC12000

# DIGITAL MIXER/TRANSLATOR (D Flip-Flop w/Translator)

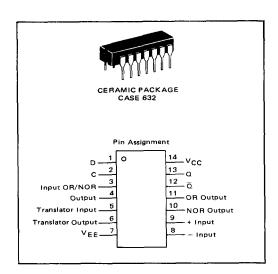

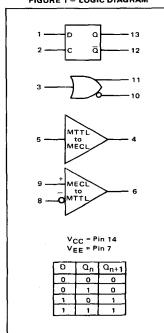

The MC12000 is intended for use as a digital mixer in phase-locked loop frequency synthesizers and other applications where a MECL "D" flip-flop with translators is required. Toggle frequency is typically 250 MHz. MTTL to MECL and MECL to MTTL translators are provided to facilitate interfacing with MECL or MTTL circuits.

The MC12000 is designed to operate from a single power supply of either +5.0 Vdc or -5.2 Vdc.

## FIGURE 1 - LOGIC DIAGRAM

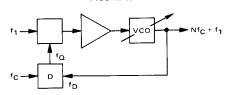

FIGURE 2 - TYPICAL DIGITAL MIXER

Note: All MECL outputs have 510-ohm internal pulldown resistors.

|                            |                  | _             |       |             |            |       |            |          |         | 75°C | +4.280   | +3,170   | +3.955  | +3.550    | 10.5       | ¥2.4  | +5.0     | +4.5 | 72.0     | 70.6   | 75.0  | -2.5 | 10            | -1.6          | 1          |

|----------------------------|------------------|---------------|-------|-------------|------------|-------|------------|----------|---------|------|----------|----------|---------|-----------|------------|-------|----------|------|----------|--------|-------|------|---------------|---------------|------------|

|                            | · -              | Pin           |       |             |            | MC1   | 2000       |          |         |      |          |          | TEST VO | LTAGE/CUR | RENT.      | APPLI | ED TO    | PINS | LISTE    | D BELO | ow:   |      |               |               |            |

| Characteristic             | Symbol           | Under<br>Test | Min   | Max         | Min        | +25°C | Max        | Hin      | Max Max | Unit | VIHmax   | Vilmin   | VIHAmin | VILAmax   | l v        | Iv    | VIHH     | 1/-  | V        | V      | Vaa   | IL.  | loL           | юн            | (VEE       |

|                            |                  |               |       | <del></del> |            |       |            |          |         |      |          |          | -       |           | _          | _     |          | _    | VIR I    | _      |       |      | $\overline{}$ | $\overline{}$ | 7          |

| Power Supply Drain Current | - IE             | 7             |       | -           |            | 85    |            |          |         | mAdc | -        | -        |         |           |            | -     | -        | 1    | _        |        | 14    | -    | -             |               |            |

| Input Current              | INH1             | 1             | -     | -           | -          | -     | 200        | - 1      | -       | μAdc | 1        | 2        | -       | _         | -          | -     | -        | _    | -        | -      | 14    | _    | -             | -             | 7          |

|                            |                  | 2             |       | _           |            | _     | 200<br>200 | -        | _       |      | 2 3      | 1 1      | _       | _         | _          | _     | _        | _    |          | -      |       | _    | 1 I I         | -             |            |

|                            | Linning          | 5             |       | 4.0         | _          | _     | 40         |          | 40      | 1    | _        | _        | _       | _         | _          | _     | 5        | _    |          |        |       | _    | _             | _             |            |

|                            | INH2             | 8             | _     |             | 3.8        |       | 6.5        | _        | -       | mAde | g.       | 8        |         | _         | _          | _     | _        | -    | -        | l _    |       | _    | l _ l         | -             | 1          |

|                            | INH3             | 9             | _     | _           | 3.8        | _     | 6.5        |          |         | MAGC | 9        | 8        | -       |           | _          | -     |          | 1    | 1        | -      | •     | -    |               |               | <u> </u>   |

|                            | INLI             | 1             | -     | -           | -          | -     | 2.0        | _        | _       | μAdc | -        | -        | -       | -         | -          | -     | -        | -    | -        | -      | 14    | -    | -             | -             | 1,7        |

|                            | (Leak age        | 2             | -     | - 1         | -          | -     | 2.0        | - '      | -       | 1 1  | -        | -        | -       | -         | -          | -     | -        | [ -  | - 1      | _      |       | -    | -             | -             | 2,7<br>3,7 |

|                            | Current)         | 3             | -     | ) - i       |            | -     | 2.0        | i -      | i -     | ) ¥  | i -      | -        | -       | -         | -          | -     | - '      | !    | ] - '    | 1      | 1 1 1 | -    | -             | -             | 3,1        |

|                            | INL2             | 5             | -     | -1.6        | -          | -     | -1.6       | -        | ~1.6    | mAdc | -        | -        | -       | -         | 5          | -     |          | -    | -        | -      |       | -    | -             | _             | Lί         |

|                            | INL3             | 8             | -     | -           | 3.8<br>2.0 | _     | 6.5<br>4.0 | _        | -       | 1 1  | 8 8      | 9        | _       |           | _          | _     | _        | -    |          | -      | †     | I -  | -             | _             |            |

| Logic "1"                  | Von1             | 4             | 4.000 | 4,160       | 4.040      | -     | 4.190      | 4.100    | 4.280   | Vdc  | <u> </u> | <u> </u> |         | -         | -          | 5     | _        | -    | _        | _      | 14    | 4    |               |               | 7          |

| Output Voltage             | 1001             | 10            | 1.000 | 1 100       | 1.01.0     | _     | 1          | 1        | 1       | ii   | -        | 3        | -       | _         | -          | -     | -        | - 1  | . –      | -      | l i i | 10   | -             | -             | 1.1        |

| · -                        |                  | 11            |       |             |            | -     | ]          | 1 1      |         |      | 3        | -        | -       | - 1       | - 1        | -     | -        | -    | i -      | -      |       | 11   | -             | -             | 1 1        |

|                            | İ                | 12†<br>13†    | †     | 1           | †          | _     | ·          | <b>*</b> | *       | †    | 1        | 1 -      | _       | _         | _          | -     | _        | -    | _        |        | †     | 12   | -             |               |            |

|                            | V <sub>OH2</sub> | 6             | 2.400 |             | 2.400      | -     |            | 2.400    | _       | Vdc  | 9        | 8        |         |           |            | -     |          | Ē    |          | _      | 14    | _    | _             | 6             | 7          |

| Logic "0"                  | V <sub>OL1</sub> | 4             | 3.130 | 3.370       | 3.150      | -     | 3.380      | 3.170    | 3.410   | Vdc  |          |          |         | -         | 5          | -     |          | -    | -        | -      | 14    | 4    | -             |               | ?          |

| Output Voltage             |                  | 10            |       |             |            | -     | 1          |          |         | 1    | 3        | 3        | - 1     | _         | _          | _     | _        | -    |          | _      |       | 10   | - 1           | _             | ıl         |

|                            | 1                | 11<br>121     | 1 1   |             | 1 1        | _     | i I        | 1 1      |         | 1 1  | -        | 3        | _       | _         |            | _     | _        | -    |          | _      |       | 12   | 1 - 1         | _             | ı          |

|                            |                  | 131           | 1     | , ,         | 7          | -     | Ţ          | 1        |         | 1    |          | 1        |         | _         |            |       | -        |      | <u> </u> |        |       | 13   |               |               | ,          |

|                            | V <sub>OL2</sub> | 6             | -     | 0.500       |            | -     | 0.500      | -        | 0.500   | Vdc  | 8        | 9        |         |           | -          | -     | <u> </u> |      |          |        | 14    | -    | 6             |               | 7          |

| Logic "1"                  | VOHA             | 4             | 3.980 | -           | 4.020      | -     | -          | 4.080    | -       | Vdc  | -        | -        | -       | _         | -          | -     | -        | -    | 5        | -      | 14    | 4    | -             | -             | 7          |

| Threshold Voltage          |                  | 10<br>11      | 1     | -           |            | -     | -          | 1 1      | -       | 1 1  | _        | -        | 3       | 3         |            | _     | -        | _    | _        | _      |       | 10   | _             | 1             |            |

|                            | 1                | 121           | 1 1   | 1           |            | _     | _          |          | _       | 1 1  | _        | _        | _       | 1 1       | ļ <u>-</u> | -     | -        |      | _        | ~      | ΙI    | 12   | _             | _             | 11         |

|                            |                  | 13t           | , ,   | _           | 1          | _     | -          | 1        |         | 7    | L        |          | 1       |           | -          | 1 –   | -        |      | -        | _      | _ 7   | 13   |               | l             |            |

| Logic "0"                  | VOLA             | 4             | -     | 3.390       | -          |       | 3.400      | -        | 3.430   | Vdc  | -        | -        | -       |           | -          | -     | -        | -    | -        | 5      | 14    | 4    | -             | -             | 7          |

| Threshold Voltage          |                  | 10            | -     | 11.         | -          | -     |            | -        | L       |      | -        | -        | 3       | _         | -          | -     | -        | -    | -        | -      |       | 10   | -             | -             |            |

|                            |                  | 11<br>12†     |       |             | _          | _     |            | -        | i I     |      | 1 -      | _        | 1       | 3         | _          | [ _   | 1 -      | -    | _        | _      |       | 12   | _             | -             | 11         |

|                            |                  | 131           | _     | 1           | -          | _     |            | _        | *       | *    | _        | _        | -       | 1         | _          | _     | -        | -    | -        | l      | 1     | 13   | ~-            |               | 1          |

| Short Circuit Current      | isc              | 6             | -20   | -65         | -20        |       | -65        | -20      | -65     | mAdc | 9        | 8        | -       | -         | -          | -     | -        | -    | -        | -      | 14    | -    | -             | -             | 6,7        |

tOutput Level to be measured after a clock pulse has been applied to the C input (pin 2) VIHmax

# ELECTRICAL CHARACTERISTICS Supply Voltage = -5.2 V

|                                |                              | Pin                         |        |             |                 | MC12      | 2000              |             |           |      |                  |                  | TEST VO          | LTAGE/CUF        | DENT   | ADDII            | ED TO | DING      | LICTE       | DEL              |                   |                           |      |         | . '   |

|--------------------------------|------------------------------|-----------------------------|--------|-------------|-----------------|-----------|-------------------|-------------|-----------|------|------------------|------------------|------------------|------------------|--------|------------------|-------|-----------|-------------|------------------|-------------------|---------------------------|------|---------|-------|

|                                |                              | Under                       |        | ·c          |                 | 25°C      |                   | +7          | 5°C       |      | L                | :                | 1231 40          | LIAGE/COF        | THE HI | MITCI            | ED 10 | FIRE      |             | J BELL           | J#1.              |                           |      |         | (VCC) |

| Characteristic                 | Symbol                       | Test                        | Min    | Max         | Min             | Тур       | Max               | Min         | Max       | Unit | VIHmax           | VILmin           | VIHAmin          | VILAmax          | VIL    | VIH              | VIHH  | VR        | VIHT        | VILT             | VEE               | 1L                        | lOL  | tor     | Gnd   |

| Power Supply Drain Current     | 1E                           | 7                           | _      |             |                 | 90        | -                 | -           |           | mAdc |                  | -                |                  | -                | -      | -                | -     |           | -           | -                | 7                 | -                         | -    |         | 14    |

| Input Current                  | INHI                         | 2                           | -      | -           | 1.1.            | 1 1 1     | 200<br>200<br>200 | -           | -         | μAdc | 2 3              | 1                | =                | -                | -      | -                |       | -         | _           | -                | 7                 | 1 1 1                     | -    | -       | 14    |

|                                | INH2                         | 5                           | ~      | 40          | -               | -         | 40                | l           | 40        |      | -                | -                | -                | -                | -      | -                | 5     | -         | -           | -                |                   | -                         | -    | -       | П     |

|                                | 1INH3                        | 9                           |        | _ =         | 3.8<br>3.8      |           | 6.5<br>6.5        | _           |           | mAdc | 9                | 8<br>8           |                  |                  | -      | _                | 1     | Ŀ         | _           | _                | •                 | _                         |      | _       | 1     |

|                                | INL1<br>(Leakage<br>Current) | 1<br>2<br>3                 | -      | -<br>-<br>- | -               | -         | 2.0<br>2.0<br>2.0 | -<br>-<br>- | =         | μAdc | -<br>-<br>-      | -                | -<br>-<br>-      | -                | -      | -<br>-           | 111   | -         | -           | -                | 1,7<br>2,7<br>3,7 | -                         | -    | -<br>-  | 14    |

|                                | INL2                         | 5<br>8                      | -<br>- | -1.6<br>-   | -<br>3.8<br>2.0 |           | -1.6<br>6.5       | -<br>-      | -1.6<br>- | mAdc | <br>8<br>8       | 9                | -                | -                | . 5    | <br>-            | -     | -         | -           | -                | 7                 | -<br>                     | -    | -       |       |

| Logic "1"<br>Output Voltage    | V <sub>ОН1</sub>             | 4<br>10<br>11<br>121<br>131 | -1.000 | -0.840      | -0.960          | 1111      | -0.810            | -0.900      | -0.720    | Vdc  | <br>3<br>-       | 3 - 1 -          |                  |                  |        | 5<br>-<br>-<br>- | 11111 |           | -           |                  | 1                 | 4<br>10<br>11<br>12<br>13 |      |         | 14    |

|                                | V <sub>OH2</sub>             | - 6                         | -2.800 | _           | -2.800          |           | -                 | -2.800      |           | Vdc  | 9                | 8                |                  | _                | -      | -                | -     | -         | _           | -                | 7                 | -                         | -    | 6       | 14    |

| Logic "0"<br>Output Voltage    | V <sub>OL1</sub>             | 4<br>10<br>11<br>12t<br>13t | -1.870 | -1.635      | -1.850          | 1111      | -1.620            | -1.830      | -1.595    | Vdc  | -<br>3<br>-<br>1 | -<br>3<br>-<br>1 | -<br>-<br>-<br>- | -                | 5      |                  | 11111 | 1 - 1 - 1 |             |                  | 7                 | 4<br>10<br>11<br>12<br>13 |      | 1111    | 14    |

|                                | VOL2                         | 6                           | _      | -4.700      | ~               | -         | -4.700            | -           | -4.700    | Vdc  | 8                | 9                | _                |                  | -      | -                | -     | T -       | -           | -                | 7                 | -                         | 6    | - 1     | 14    |

| Logic "1"<br>Threshold Voltage | VOHA                         | 4<br>10<br>11<br>121<br>131 | -1.020 | 1111        | -0.980          | 1111      | 11111             | -0.920      | -         | Vdc  | -                | -                | -<br>3<br>-<br>1 | 3<br>-<br>1      | 1111   |                  | 11111 |           | 5<br>-<br>- |                  | 7                 | 4<br>10<br>11<br>12<br>13 | 1111 | 11111   | 14    |

| Logic "0"<br>Threshold Voltage | VOLA                         | 4<br>10<br>11<br>121<br>131 | 11111  | -1.615      | 1111            | 1 1 1 1 1 | -1.600            | 11111       | -1.575    | Vdc  | -<br>-<br>-<br>- | -<br>-<br>-      | -<br>3<br>-<br>1 | -<br>3<br>-<br>1 |        | -                | 1111  | -         |             | 5<br>-<br>-<br>- | 1                 | 4<br>10<br>11<br>12<br>13 |      | 1 1 1 1 | Ĭ     |

| Short Circuit Current          | Isc                          | 6                           | -20    | -65         | -20             | 7         | -65               | -20         | -65       | mAdc | 9                | 8                | -                | _                | _      | -                |       | -         | _           | -                | 6,7               | Γ-                        | -    |         | 14    |

†Output Level to be measured after a clock pulse has been applied to the C input (pin 2) Vilmax VILmin

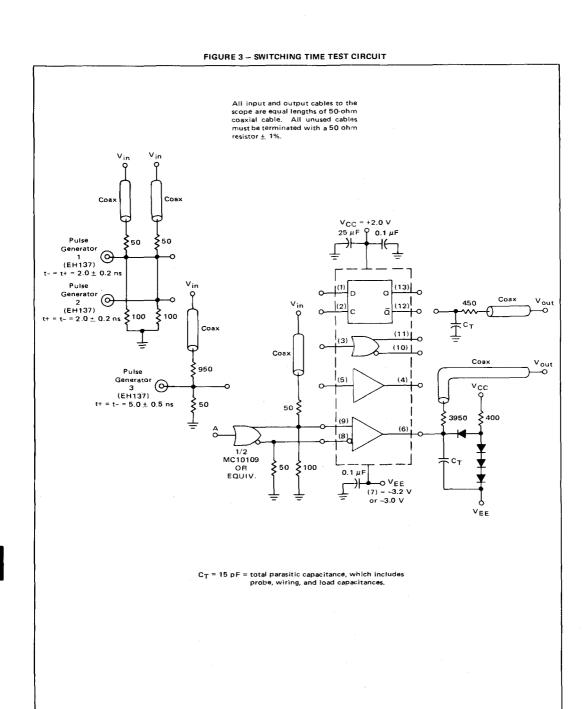

## AC ELECTRICAL CHARACTERISTICS

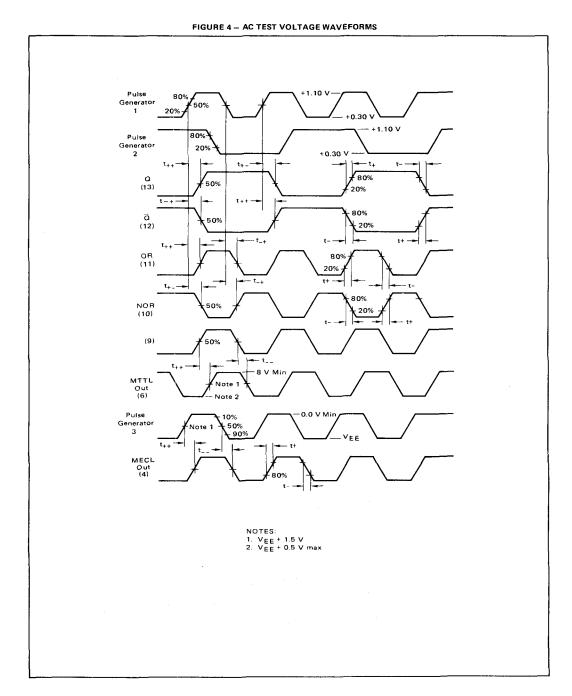

|                                    | 1                  | Pin   | L   |     |     |       | MC1  |     |           |      | TEST VOLTAGES/WAVEFORMS APPLIED TO PINS LISTED BELOW: |              |              |           |                  |     |  |  |

|------------------------------------|--------------------|-------|-----|-----|-----|-------|------|-----|-----------|------|-------------------------------------------------------|--------------|--------------|-----------|------------------|-----|--|--|

|                                    | İ                  | Under | 00  | _   | _   | +25°C | ,    | +75 |           | ļ    |                                                       | Ĭ            |              |           | VEE              | Vcc |  |  |

| Characteristic                     | Symbol             | Test  | Min | Max | Min | Тур   | Max  | Min | Max       | Unit | Pulse Gen. 1                                          | Pulse Gen. 2 | Pulse Gen. 3 | Pulse Out | -3.2 V or -3.0 V |     |  |  |

| Propagation Delay                  | t2+13+             | 2,13  | -   | -   | 1.5 | 2.4   | 4.0  |     | -         | ns   | 2                                                     | 1            | -            | 13        | 7                | 1,4 |  |  |

| (See Figure 4)                     | t2+13-             | 2,13  | -   | -   | 1.5 | 2.4   | 4.0  | -   | -         | ns   | 2                                                     | 1            | -            | 13        | 7                | 14  |  |  |

|                                    | <sup>‡</sup> 2+12+ | 2,12  | -   | -   | 1.5 | 2.4   | 4.0  | -   | -         | ns   | 2                                                     | 1            | -            | 12        | 7                | 14  |  |  |

|                                    | t2+12-             | 2,12  | ] - | -   | 1.5 | 2.4   | 4.0  | -   | -         | ns   | 2                                                     | 1            | -            | 12        | 7                | 14  |  |  |

|                                    | t3+11+             | 3,11  | -   | -   | 1.0 | 1.5   | 3.0  | -   | -         | ns   | 3                                                     |              | - 1          | 11        | 7                | 14  |  |  |

|                                    | t3-11-             | 3,11  | -   | -   | 1.0 | 1.5   | 3.0  | -   | -         | ns   | 3                                                     | _            | _            | 11        | 7                | 14  |  |  |

|                                    | t3+10-             | 3,10  | -   | -   | 1.0 | 1.5   | 3.0  | _   | _         | ns   | 3                                                     | -            |              | 10        | 7                | 14  |  |  |

|                                    | t3-10+             | 3,10  | -   | -   | 1.0 | 1.5   | 3.0  | -   | -         | ns   | 3                                                     | _            | <del>.</del> | 10        | 7                | 14  |  |  |

|                                    | t5+4+              | 5,4   | -   | -   | 2.0 | 3     | 5.0  | -   | -         | ns   | -                                                     | _            | 5            | 4         | 7                | 14  |  |  |

|                                    | t5-4-              | 5,4   | -   | -   | 1.0 | 1.5   | 3.0  | -   | -         | ns   | -                                                     |              | 5            | 4         | 7                | 14  |  |  |

|                                    | t9+6+              | 9,6   | -   | -   | 4.0 | 8.0   | 12.0 | -   | -         | ns   | A                                                     | _            | -            | 6         | 7                | 14  |  |  |

|                                    | t9-6-              | 9,6   | -   | -   | 3.0 | 5.0   | 10.0 | -   | -         | ns   | Α                                                     | -            | -            | 6         | 7                | 14  |  |  |

| Output Rise Time                   | t13+               | 13    | -   | _   | _   | 2.8   | T-   | -   | _         | ns   | 2                                                     | 1            | _            | 13        | 7                | 14  |  |  |

| (See Figure 4)                     | t12+               | 12    |     | -   | _   | 2.8   | -    | _   | _         | ns   | 2                                                     | 1            | -            | 12        | 7                | 14  |  |  |

|                                    | t <sub>11+</sub>   | 11    | -   | -   | -   | 2.0   | -    | -   | -         | ns   | 3                                                     | -            | -            | 11        | 7                | 14  |  |  |

|                                    | t10+               | 10    | -   | -   | -   | 2.0   | -    | -   | · <u></u> | ns   | 3                                                     | -            | -            | 10        | 7                | 14  |  |  |

|                                    | t4+                | 4     | -   | -   | -   | 2.4   | ~    | -   | -         | ns   | -                                                     |              | 5            | 4         | 7                | 14  |  |  |

| Output Fall Time                   | t13-               | 13    | -   | -   | -   | 2.8   | -    | -   | _         | ns   | 2                                                     | 1            | -            | 13        | 7                | 14  |  |  |

| (See Figure 4)                     | t <sub>12-</sub>   | 12    | -   |     | -   | 2.8   | -    | -   | -         | ns   | 2                                                     | 1 1          | <u> </u>     | 12        | 7                | 14  |  |  |

|                                    | t11-               | 11    | -   | -   | -   | 2.0   | -    | -   | . –       | ns   | 3                                                     | -            | _            | 11        | 7                | 14  |  |  |

|                                    | t10-               | 10    |     | -   |     | 2.0   | -    |     | -         | ns   | 3                                                     | -            | _            | 10        | 7                | 14  |  |  |

|                                    | t4_                | 4     | -   | -   | -   | 2.4   | -    | -   | - '       | ns   |                                                       | ~-           | 5            | 4         | 7                | 14  |  |  |

| Setup Time                         | tsetup"1"          | 13    |     | -   | _   | 0.2   | -    | -   | -         | ns   | 2                                                     | 1            | _            | -         | 7                | 14  |  |  |

| (See Figure 5)                     | tsetup"0"          | 13    |     | -   | -   | 0.7   | -    | -   | -         | ns   | 2                                                     | 1            | -            | -         | 7                | 14  |  |  |

| Hold Time<br>(See Figure 5)        | thold"1"           | 13    | -   | -   | -   | 0.0   | -    | -   | -         | ns   | 2                                                     | 1            | -            | _         | 7                | 14  |  |  |

|                                    | thold"0"           | 13    | -   | -   | -   | 1.0   | -    | -   | -         | ns   | 2                                                     | 1            | -            | _         | 7                | 14  |  |  |

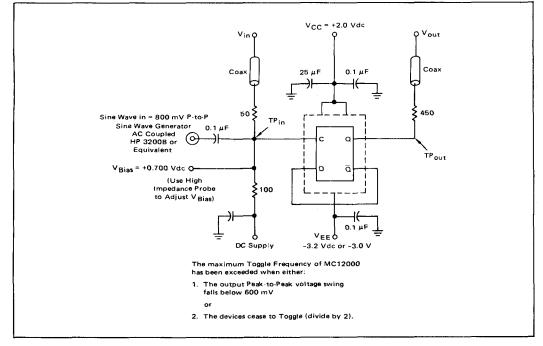

| Toggle Frequency<br>(See Figure 6) | ftog               | 13    | -   | -   | -   | 250   | -    | -   | -         | MHz  | _                                                     | -            | -            | -         | 7                | 14  |  |  |

6-16

– 20 ns Generator +1.10 V 50% 20% Clock +0.30 tsetup"1" Pulse +1.10 V Generator <sub>6</sub>80% 20% 2 D 30 ns 50% <sup>t</sup>hold"1" Q (13) tsetup''0'' Pulse Generator 2 D – <sup>t</sup>hold"<u>0</u>" Q (13)

FIGURE 5 - SETUP AND HOLD TIME WAVEFORMS (See Figure 3)

### MC12000 DIGITAL MIXER

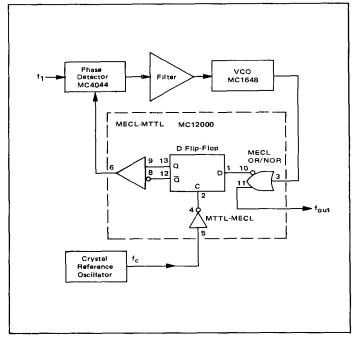

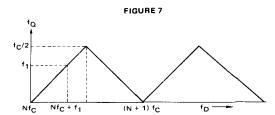

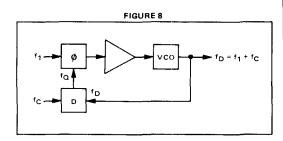

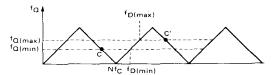

This device is a digital mixer designed to operate with logic levels at its input and output ports. In operation it is an MECL type "D" flip-flop with level translators to and from MTTL to accomodate most interfacing demands. Output frequency (fQ) as a function of "D" and clock inputs is shown in Figure 7. It can be seen that either direct or harmonic mixing may be employed, that is, fQ may be either the difference between fD and fC or the difference between fD and the Nth harmonic of fC.

One particular advantage of mixing in phase locked loops (PLL) is that lower frequencies may be generated for use in portions of the circuit where digital processing is done (with divide-by-P network and/or phase detector). Lower frequency operation often reduces overall system cost since a less expensive logic form may be utilized. However use of the mixing technique is not a panacea for all VHF applications and the design of such synthesizer systems must be approached with care.

Use of the MC12000 in a non-harmonic PLL is straightforward (Figure 8). Output frequency is the sum of both input quantities ( $f_1 + f_C$ ) as long as  $f_1$  is less than  $f_C/2$  (See Figure 7), since  $f_Q$  can go no higher than that. Unless VCO output range is restricted somewhat there is a chance also that the loop may operate at the second harmonic of  $f_C$ . This problem is minimal in the loop of Figure 8, however, since the output frequency would have to vary more than 2:1.

Mixing is used because the digital phase detector has an upper frequency limit of about 10 MHz and many loops require direct locks at 20 MHz or more. Direct down-mixing does not change any loop characteristics except the sampling rate which restricts loop natural frequency to about fc/10 in practical circuits. Although

output frequency may be changed by varying either f<sub>1</sub> or f<sub>C</sub>, the clock input is usually crystal controlled since it is of the same magnitude as f<sub>D</sub> and more difficult to stabilize.

FIGURE 9  $f_D = Pf_1 + f_C$   $f_C = Pf_1 + f_C$

Combining a standard synthesis configuration with the mixer yields a circuit capable of high frequency operation at low cost (Figure 9), if the output frequency range is relatively small ( $P_{max}-P_{min}$ )  $f_1 < f_C/2$ . In fact the choice of harmonic or non-harmonic mixing is largely based on the availability of a suitable crystal or other reference source for  $f_C$  versus the needed frequency coverage. Considering all the restrictions on  $f_C$ , its value (and the maximum harmonic number N) are dictated by the following expressions:

$$N < \frac{f_D(min) - f_1}{2 \Delta f_D} \tag{1}$$

$$N_{fc} = f_{D(min)} - f_1 \tag{2}$$

where  $\triangle f_D$  = change in output frequency.

$f_{D} = Pf_{1} + Nf_{C}$   $f_{D} = Pf_{1} + Nf_{C}$

FIGURE 10

Using Equations (1) and (2) above the minimum value of f<sub>C</sub> may be found for the circuit of Figure 10 and still get adequate frequency coverage. In this minimum configuration all necessary output frequencies may be generated by programming the "P" count string. But the divide number might bear no obvious relation to the output frequency such as often happens with non-mixing synthesizers.

6

## 6

#### DESIGN EXAMPLES

## Example #1

Output Frequency: 48-54 MHz Frequency Increments: 10 kHz

Using Equations (1) and (2), a minimum frequency (fc) version can be designed:

$$N < \frac{48 \text{ MHz} - 10 \text{ kHz}}{2 (54-48) \text{ MHz}}$$

Let N = 3

NfC = 47.99 MHz

$$f_C = \frac{Nf_C}{N} = \frac{47.99}{3} = 15.99666 \text{ MHz}$$

fc = 15.996666 MHz

$$P_{\text{max}} = \frac{\Delta f_{\text{D}}}{10 \, \text{kHz}} + P_{\text{min}} \tag{3}$$

$$P_{max} = \frac{6 \text{ MHz}}{10 \text{ kHz}} + P_{min}$$

$$P_{\text{max}} = 601$$

$$f_{Q(max)} = P_{max} f_1$$

= 6.01 MHz (4)

Equation (4) above puts the divider string (divide-by-P) into a medium frequency situation where devices such as the MC4016/4316 may be utilized. Note that the divider number now indicates the channel selected rather than output frequency. That is, at  $f_D=48.000 \ \text{MHz}$ , P=1; at  $f_D=54.000 \ \text{MHz}$ , P=601. If "proper" divide-by-P readings are desired for direct

If "proper" divide-by-P readings are desired for direct frequency readout a slight circuit modification is necessary. To enable a division at 48.000 MHz the first divide-by-P must be 100 rather than 1, and  $P_{max}$  would then be 700 to cover all 6 MHz. Recalculating  $f_{Q(max)}$  from Equation 4 we still find that the 7 MHz maximum value allows use of the same components. The next question concerns the allowable range of  $f_Q$  in relation to  $f_C$  ( $f_Q < f_C/2$ ). Since  $f_C$  is nearly 16 MHz, the range of  $f_Q$  can be contained. A cosmetic change to the most significant digit switch completes the design. Instead of reading 1 through 7 it must be modified to display 48 through 54.

### Example #2

Output Frequency: 144-148 MHz Frequency Increments: 10 kHz

$$N < \frac{144.00 - 0.01}{2(4)}$$

$$Nf_C = 144.00 - 0.01 MHz$$

$$f_C = \frac{Nf_C}{N} = 8.470 \text{ MHz}$$

$$P_{\text{max}} = \frac{4 \text{ MHz}}{10 \text{ kHz}} + 1$$

$$fQ(max) = P_{max} f_1 = 4.01 MHz$$

Maximum frequency seen by the divide-by-P chain is still well within the MC4016 rating.

When converting this synthesizer to one that reads frequency directly, a "1" is again added to the most significant digit (MSD). This results in a  $P_{min}$  of 100 to  $P_{max}$  of 500. In this example, however,  $f_{Q(max)}$  is 5 MHz which easily exceeds  $f_{C}/2$ . To alleviate this difficulty, the "N" factor must be decreased in order to raise  $f_{C}$  to at least 10 MHz.

$$N < \frac{f_D(min) - f_1}{f_C}$$

Let fc = 10 MHz

Let N = 14

NfC = 143.99 (from above)

$$f_C = \frac{Nf_C}{N} = \frac{143.99}{14}$$

$$f_C = 10.28500 \text{ MHz}$$

(5)

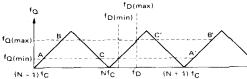

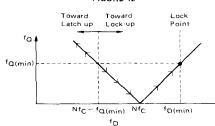

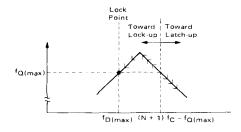

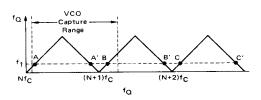

As in all harmonically locked PLL's, it is possible for the loop to lock on the wrong harmonic if there is too wide a range in the VCO. This situation is shown in Figure 11 where the possible false lock areas are indicated near the (N - 1) and (N + 1) harmonic points. The problem of VCO restraint however is more than just making sure that output frequency fp isn't able to go to B or A' (the closeest false lock points). Actual operating limits are C and C', symmetrically placed frequencies corresponding to fp(min) about NfC and fD(max) about (Nf+1/2) fC. If the VCO drops below C while the feedback counter is at Pmin the phase detector will try to push fp even lower, toward the stable condition at A (Figure 12). Likewise, at C' (when P = P<sub>max</sub>) the tendency is for the loop to accelerate toward lockup at B' (Figure 13). When C or C' are exceeded the loop will "hang up" and not attain the proper lock.

The VCO frequency constraints may be quite severe if the minimum  $f_{\rm C}$  formulation is followed and the Nth harmonic is quite high. Where VCO constraint may pose a problem, decrease N below the maximum indicated by Equation (1) until sufficient room is generated by placing the operating range of  $f_{\rm C}$  on only a small part of the  $f_{\rm D}$  slope (Figure 14). Note that  $f_{\rm C}$  goes up as we approach the more idealized case (Equation 5).

FIGURE 14

The most likely reasons for a "latched up" state in a harmonic loop are turn-on transients and loop overshoot when changing frequency abruptly from one end of the range to the other.

# FIGURE 11

## FIGURE 12

FIGURE 13

## SUMMARY OF SYNTHESIS PROCEDURE

1. Compute harmonic number N

$$N < \frac{f_{D(min)} - f_1}{2 \, \Delta f_D}$$

where  $\Delta f_D$  = change in output frequency  $f_1$  = channel spacing

2. Compute minimum mixing frequency fc

$$f_C = \frac{f_D(min) - f_1}{N}$$

3. Calculate feedback divider's maximum value

$$P_{max} = \frac{\Delta f_D}{f_1} + P_{min}$$

where Pmin = 1 for minimum fC

4. Find maximum divide-by-P frequency

$$fQ(max) = \Delta fD + f1$$

5. Calculate allowable VCO swing

$$Nf_{C} - f_{1} < f_{VCO} < (N + 1) f_{C} - f_{Q(max)}$$

If the above constraints are too tight choose the next lower number for N and repeat steps 2 and 5 until satisfied.

### SKIP-LOCK TUNING

Harmonic mixing provides an alternate means to frequency synthesis without the feedback divide-by-P network. In this instance the design objective is to provide a large frequency coverage with a set (and relatively wide) channel spacing. The configuration is identical to a single frequency PLL (Figure 15) except it operates in the harmonic mode and tuning is accomplished at the VCO. Output frequency is fixed as being f1 above all harmonics of fC. As the VCO is tuned through its range, the loop will acquire and lose signals spaced fC apart. Since these must be some frequency for the phase detector to operate with, the output frequency cannot be a direct harmonic of fC. This facet of the circuit often causes users to refer to f1 as the "offset" frequency.

The value of f<sub>1</sub> is often dictated by output frequency and channel spacing requirements. However the relation-

ship of  $f_1$  to  $f_C$  has a large effect on the tunability both up and down the frequency range. If, for example, the loop were locked at point A (Figure 16) and B were the next desired point, then the VCO must be "dragged" from A to A' before lock can be achieved. This frequency adjustment may be quite critical since the frequency difference between A' and B is only  $2f_1$ . If the VCO is tuned past B the opportunity for lock has been passed.

On the other hand, in going from B to A, the upper end of the VCO control range must only cross A' before the loop acquires frequency A. In either case it's apparent that the loop will not "jump" from one lock point to another and some indication of loop lock should be added. This is normally done by monitoring the VCO dc control line with a pair of comparators and noting when the line reaches its limits.

FIGURE 15

FIGURE 16

## **MAXIMUM RATINGS**

| Characteristic                             | Symbol           | Rating             | Unit |

|--------------------------------------------|------------------|--------------------|------|

| Ratings above which device life may be     | impaired:        |                    |      |

| Power Supply Voltage (V <sub>CC</sub> = 0) | VEE              | -8.0               | Vdc  |

| Input Voltage (V <sub>CC</sub> = 0)        | V <sub>in</sub>  | 0 to VIL min       | Vdc  |

| Output Source Current                      | 10               | 40                 | mAdc |

| Storage Temperature Range                  | T <sub>stg</sub> | -55 to +125        | °c   |

| Recommended maximum ratings above          | which performanc | e may be degraded: |      |

| Operating Temperature Range                | TA               | 0 to +75           | °C   |

70

DC Fan-Out\* (Gates and Flip-Flops)

<sup>\*</sup>AC fan-out is limited by desired system performance.