Document Number: MC34929 Rev. 7.0, 11/2006

**VRoHS**

# Brushless DC 1.0 AMP 28 VOLT Motor Driver IC

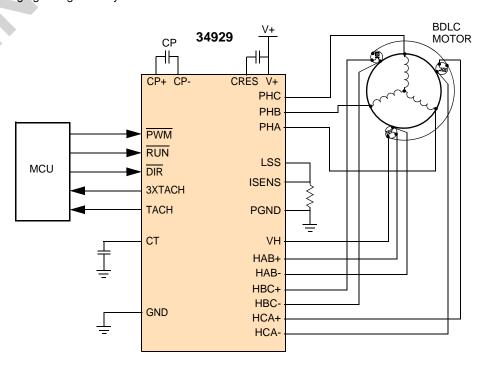

The 34929 Brushless DC (BLDC) Motor Driver IC is a complete BLDC motor driver system in one chip. It is designed to efficiently drive three-phase BLDC motors up to 1A and 28V, and has built in protection features making it ideal for a variety of consumer, portable, and office applications containing small motors. It incorporates digital I/O, making it easy to use with an MCU in a closed-loop motor control system. It has a built-in Hall-effect sensors interface and a Hall sensors voltage supply, so it can operate BLDC motors as a stand-alone controller/driver. Its sophisticated analog/mixed-signal state machine accommodates several modes of operation, including: Forward (CW), Reverse (CCW), Run/Stop, Braking, Variable Speed (External PWM), and Torque Limit (maximum-current-limit) modes.

#### **Features**

- Single-Supply Operation (8V–28V)

- Built-in Hall Sensors Controlled-Supply (VH)

- 3-Phase Hall Sensors Interface

- Two Tachometer Outputs (1X and 3X Hall Frequency)

- Adjustable Maximum Current Limit (Torque Limiting)

- · Adjustable Stalled Rotor Detection and Protection

- · Short Circuit Detection and Protection

- Over-Temperature Detection and Thermal Shutdown

- · Undervoltage Detection and Shutdown

- · Pb-Free Packaging Designated by Suffix Code EP.

# 34929

#### **BRUSHLESS DC MOTOR DRIVER**

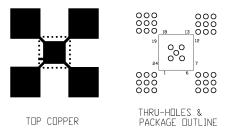

QFN SUFFIX 98ARH99033A 24-PIN QFN (4X4X1)

| ORDERING INFORMATION |                                        |         |  |  |  |  |

|----------------------|----------------------------------------|---------|--|--|--|--|

| Device               | Temperature<br>Range (T <sub>A</sub> ) | Package |  |  |  |  |

| MC34929EP            | -0°C to 85°C                           | 24 QFN  |  |  |  |  |

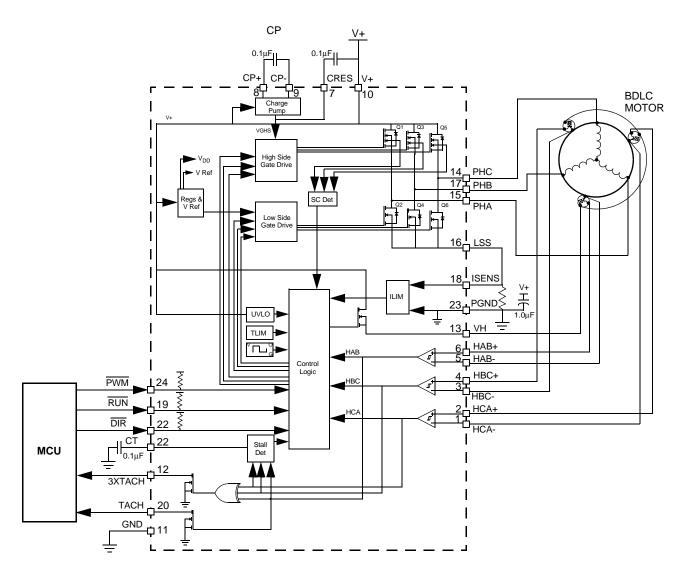

Figure 1. 34929 Simplified Application Diagram

<sup>\*</sup> This document contains certain information on a new product.

Specifications and information herein are subject to change without notice.

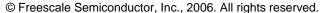

# INTERNAL BLOCK DIAGRAM

Figure 2. 34929 Simplified Internal Block Diagram

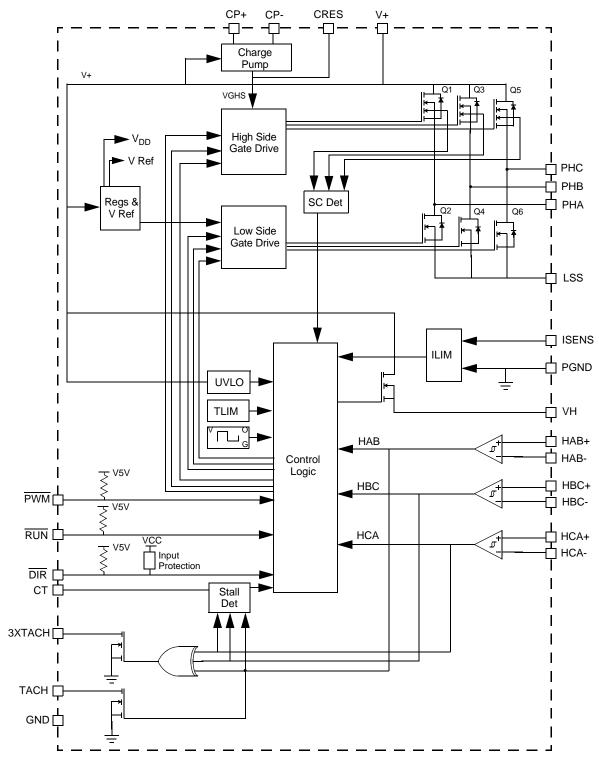

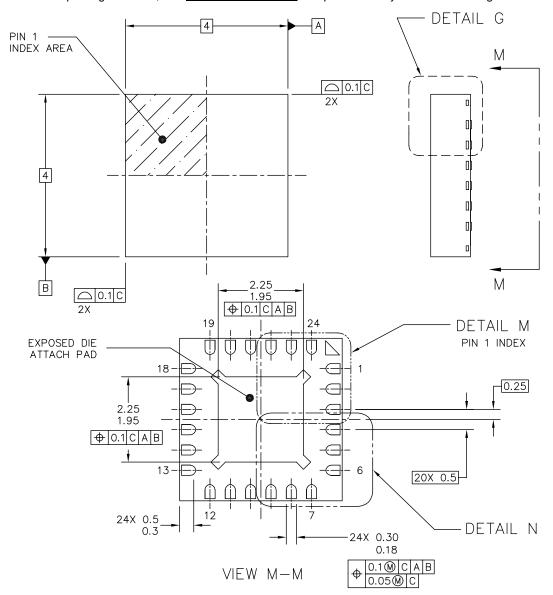

# **PIN CONNECTIONS**

Figure 3. 34929 Pin Connections

Table 1. 34929 Pin Definitions

| Pin Number | Pin Name | Pin Function | Formal Name      | Definition                                                              |

|------------|----------|--------------|------------------|-------------------------------------------------------------------------|

| 1          | HCA-     | INPUT        | HALL CA NEG      | RECEIVES NEGATIVE OUTPUT FROM SENSOR LOCATED BETWEEN 'C' AND 'A' PHASES |

| 2          | HCA+     | INPUT        | HALL CA POS      | RECEIVES POSITIVE OUTPUT FROM SENSOR LOCATED BETWEEN 'C' AND 'A' PHASES |

| 3          | HBC-     | INPUT        | HALL BC NEG      | RECEIVES NEGATIVE OUTPUT FROM SENSOR LOCATED BETWEEN 'B' AND 'C' PHASES |

| 4          | HBC+     | INPUT        | HALL BC POS      | RECEIVES POSITIVE OUTPUT FROM SENSOR LOCATED BETWEEN 'B' AND 'C' PHASES |

| 5          | HAB-     | INPUT        | HALL AB NEG      | RECEIVES NEGATIVE OUTPUT FROM SENSOR LOCATED BETWEEN 'A' AND 'B' PHASES |

| 6          | HAB+     | INPUT        | HALL AB POS      | RECEIVES POSITIVE OUTPUT FROM SENSOR LOCATED BETWEEN 'A' AND 'B' PHASES |

| 7          | CRES     | COMPONENT    | RESERVOIR CAP    | EXTERNAL CHARGE PUMP RESEVOIR CAP                                       |

| 8          | CP+      | COMPONENT    | CHARGE PUMP POS  | POSITIVE SIDE OF CHARGE PUMPING CAP                                     |

| 9          | CP-      | COMPONENT    | CHARGE PUMP NEG  | NEGATIVE SIDE OF CHARGE PUMPING CAP                                     |

| 10         | V+       | SUPPLY       | POSITIVE SUPPLY  | MAIN SUPPLY INPUT FOR DEVICE AND MOTOR                                  |

| 23         | PGND     | RETURN       | POWER GROUND     | POWER GROUND                                                            |

| 12         | СТ       | COMPONENT    | TIMING CAP       | EXTERNAL CAP FOR STALL DETECT TIMING                                    |

| 13         | VH       | OUTPUT       | HALL VOLTAGE     | SUPPLY VOLTAGE FOR THE EXTERNAL HALL SENSORS                            |

| 14         | PHC      | OUTPUT       | PHASE C OUTPUT   | HALF BRIDGE OUTPUT FOR PHASE "C" MOTOR WINDING                          |

| 15         | PHA      | OUTPUT       | PHASE A OUTPUT   | HALF BRIDGE OUTPUT FOR PHASE "A" MOTOR WINDING                          |

| 16         | LSS      | RETURN       | LOW SIDE SOURCES | COMMON SOURCE PIN FOR LOWER HALF OF BRIDGE                              |

| 17         | PHB      | OUTPUT       | PHASE B OUTPUT   | HALF BRIDGE OUTPUT FOR PHASE "B" MOTOR WINDING                          |

# Table 1. 34929 Pin Definitions (continued)

| Pin Number | Pin Name | Pin Function | Formal Name    | Definition                                               |

|------------|----------|--------------|----------------|----------------------------------------------------------|

| 19         | RUN      | INPUT        | RUN            | RUN/STOP CONTROL INPUT (ACTIVE LOW = MOTOR RUNNING)      |

| 20         | TACH     | OUTPUT       | TACH OUTPUT    | OPEN-DRAIN-BUFFERED OUTPUT OF SENSOR 'AB'                |

| 21         | 3XTACH   | OUTPUT       | 3X TACH OUTPUT | OPEN-DRAIN-BUFFERED, EXOR'ED OUTPUT OF ALL THREE SENSORS |

| 22         | DIR      | INPUT        | DIRECTION      | DIRECTION CONTROL INPUT (ACTIVE LOW = CW ROTATION)       |

| 11         | GND      | RETURN       | SIGNAL GROUND  | SIGNAL GROUND FOR DEVICE                                 |

| 24         | PWM      | INPUT        | PWM OR ENABLE  | PWM SIGNAL INPUT (ACTIVE LOW = OUTPUTS ENABLED)          |

| 18         | ISENS    | INPUT        | CURRENT SENSE  | CURRENT LIMITING SENSE RESISTOR INPUT                    |

#### **ELECTRICAL CHARACTERISTICS**

#### **MAXIMUM RATINGS**

#### **Table 2. Maximum Ratings**

All voltages are with respect to ground. Exceeding these ratings may cause a malfunction or permanent damage to the device.

| Ratings                                                              | Symbol               | Value             | Unit |

|----------------------------------------------------------------------|----------------------|-------------------|------|

| ELECTRICAL RATINGS                                                   | <u>'</u>             |                   |      |

| Power Supply Transient Voltage                                       | V+ <sub>TRANS</sub>  | 42                | V    |

| Signal I/O Pins                                                      | V <sub>I/O</sub>     | -0.6 to 5.5       | V    |

| Open Drain Outputs (TACH and 3XTACH)                                 | TACH <sub>OUT</sub>  | 42                | V    |

| Bridge Output Continuous Current                                     | I <sub>O(CONT)</sub> | 1.0               | Α    |

| Bridge Output Peak Current                                           | I <sub>O(PK)</sub>   | 1.5               | Α    |

| Bridge Output Voltage                                                | Vo                   | -1.0 to (V+) +1.0 | V    |

| Hall Voltage Supply Current                                          | I <sub>VH</sub>      | 30                | mA   |

| ESD Voltage <sup>(1)</sup> Human Body Model (HBM) Machine Model (MM) | V <sub>ESD</sub>     | 2000<br>200       | V    |

| THERMAL RATINGS                                                      | -                    |                   | !    |

| Operating Ambient Temperature                                        | T <sub>A</sub>       | -0 to 85          | °C   |

| Maximum Junction Temperature                                         | T <sub>J-MAX</sub>   | 150               | °C   |

| Storage Temperature                                                  | T <sub>STG</sub>     | -0 to 150         | °C   |

| THERMAL RESISTANCE                                                   |                      |                   |      |

| Junction to Ambient <sup>(2)</sup>                                   | $R_{	heta JA}$       | <125              | °C/W |

| Power Dissipation (3)                                                | P <sub>D</sub>       | 1.0               | W    |

| Peak Package Reflow Temperature During Reflow (4), (5)               | T <sub>PPRT</sub>    | Note 5            | °C   |

|                                                                      | 1                    |                   |      |

#### Notes

- 1. ESD testing is performed in accordance with the Human Body Model (HBM) ( $C_{ZAP} = 100 \text{ pF}$ ,  $R_{ZAP} = 1500 \Omega$ ), the Machine Model (MM) ( $C_{ZAP} = 200 \text{ pF}$ ,  $R_{ZAP} = 0 \Omega$ ), and the Charge Device Model (CDM), Robotic ( $C_{ZAP} = 4.0 \text{pF}$ ).

- With PCB Layout comparable top copper and vias as shown in <u>Figure 4</u>, and bottom thermal ground plane of > 9 cm<sup>2</sup>.

- 3. With specified PCB Layout shown in Figure 4 under forced convection airflow condition.

- 4. Pin soldering temperature limit is for 10 seconds maximum duration. Not designed for immersion soldering. Exceeding these limits may cause malfunction or permanent damage to the device.

- Freescale's Package Reflow capability meets Pb-free requirements for JEDEC standard J-STD-020C. For Peak Package Reflow Temperature and Moisture Sensitivity Levels (MSL),

- > Go to www.freescale.com

- > Search by part number [e.g. remove prefixes/suffixes and enter the core ID to view all orderable parts. (i.e. MC33xxxD enter 33xxx)]

- > Locate your Part Number and in the Details column, select "View"

- > Select "Environmental and Compliance Information"

Figure 4. Printed Circuit Board Layout for Maximum Thermal Performance

#### STATIC ELECTRICAL CHARACTERISTICS

#### **Table 3. Static Electrical Characteristics**

Characteristics noted under conditions 8.0 V  $\leq$  V<sub>SUP</sub>  $\leq$  28 V, -0°C  $\leq$  T<sub>A</sub>  $\leq$  85°C, GND = 0 V unless otherwise noted. Typical values noted reflect the approximate parameter means at T<sub>A</sub> = 25°C under nominal conditions unless otherwise noted.

| Characteristic                              | Symbol              | Min | Тур | Max       | Unit |

|---------------------------------------------|---------------------|-----|-----|-----------|------|

| Power Supply Voltage Range                  | V+                  | 8.0 | 12  | 28        | V    |

| Suspend Power Supply Current <sup>(6)</sup> | I <sub>SA</sub>     | _   | 2.0 | 3.0       | mA   |

| Operation Power Supply Current (7)          | IQ                  | _   | 4.0 | 6.0       | mA   |

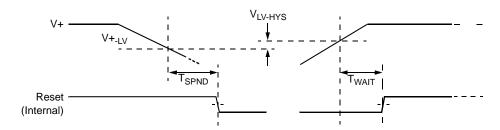

| Low V+ Detect Voltage                       | V+ <sub>-LV</sub>   | 5.0 | 5.5 | 6.0       | V    |

| Low V+ Detect Hysteresis                    | V <sub>LV-HYS</sub> | _   | 100 | _         | mV   |

| Logic Inputs Threshold Low <sup>(8)</sup>   | V <sub>IL</sub>     | _   | _   | 0.8       | V    |

| Logic Inputs Threshold High <sup>(8)</sup>  | V <sub>IH</sub>     | 2.0 | _   | _         | V    |

| Logic Inputs Hysteresis Voltage (8)         | V <sub>I-HYS</sub>  | 50  | 300 | _         | mV   |

| Logic Input Current Low (9)                 | I <sub>IL</sub>     | _   | -50 | _         | μΑ   |

| Logic Input Pull-Up Resistance (10)         | R <sub>PULLUP</sub> | _   | 100 | _         | kΩ   |

| Hall Inputs Voltage Sensitivity (11)        | V <sub>H-SENS</sub> | 50  | _   | _         | mV   |

| Hall Inputs Common Mode Voltage Range (11)  | V <sub>H-CMM</sub>  | 0.0 | _   | 3.0       | V    |

| Hall Inputs Hysteresis Voltage (11)         | V <sub>H-HYS</sub>  | _   | 15  | _         | mV   |

| Hall Input Current (11)                     | I <sub>H</sub>      | -10 | _   | 10        | μΑ   |

| Charge Pump Output Voltage                  | $V_{GHS}$           | _   | _   | (V+) +12  | V    |

| Charge Pump Reservoir Capacitor             | C <sub>CRES</sub>   | _   | 0.1 | _         | μF   |

| Charge Pump Capacitor                       | C <sub>CP</sub>     | _   | 0.1 | _         | μF   |

| Logic Output Voltage Low (12)               | V <sub>OL</sub>     | _   | _   | 0.4       | V    |

| Logic Output Leakage Current High (13)      | I <sub>OH</sub>     | _   | _   | 10        | μΑ   |

| Hall Sensors Supply Voltage <sup>(14)</sup> | V <sub>H</sub>      | _   | _   | (V+) -1.0 | V    |

#### Notes

- 6. With device in suspend mode (RUN command = False).

- 7. The current consumed internal to the IC, but not including current output for motor drive.

- 8. PWM, RUN, and DIR pins.

- 9. PWM, RUN, and DIR pins with R-pullup = 100  $k\Omega.$

- 10. Internal Pullup resistance value can vary by 20%.

- 11. HCA-, HCA+, HBC-, HBC+, HAB-, HAB+ pins.

- 12. TACH and 3XTACH pins @  $I_{OL}$  = 5.0 mA.

- 13. TACH and 3XTACH pins @  $V_{OH} = 24 \text{ V}$ .

- 14. VH pin @ I<sub>o</sub>-hall = 10 mA.

#### **Table 3. Static Electrical Characteristics (continued)**

Characteristics noted under conditions 8.0 V  $\leq$  V<sub>SUP</sub>  $\leq$  28 V, -0°C  $\leq$  T<sub>A</sub>  $\leq$  85°C, GND = 0 V unless otherwise noted. Typical values noted reflect the approximate parameter means at T<sub>A</sub> = 25°C under nominal conditions unless otherwise noted.

| Characteristic                                                    | Symbol                | Min  | Тур  | Max  | Unit |

|-------------------------------------------------------------------|-----------------------|------|------|------|------|

| High Side R <sub>DS-ON</sub> <sup>(15)</sup>                      | R <sub>ON-T</sub>     | _    | 0.25 | 0.5  | Ω    |

| Low Side R <sub>DS-ON</sub> (15)                                  | R <sub>ON-B</sub>     | _    | 0.25 | 0.5  | Ω    |

| High Side R <sub>DS-ON</sub> (hot) <sup>(16)</sup>                | R <sub>ON-T_REF</sub> | _    | 0.3  | 0.6  | Ω    |

| Low Side R <sub>DS-ON</sub> (hot) <sup>(16)</sup>                 | R <sub>ON-B_REF</sub> | _    | 0.3  | 0.6  | Ω    |

| H-bridge MOSFETs' Body-Diode Forward Voltage Drop <sup>(17)</sup> | V <sub>F-LD</sub>     | _    | 1.2  | _    | V    |

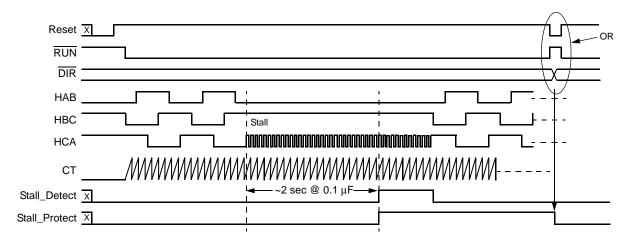

| Stall Detection Timer Output Current                              | I <sub>O-LDC</sub>    | _    | 128  | _    | μΑ   |

| Stall Detection Timer Detection Voltage                           | V-CT <sub>DET</sub>   | _    | 2.5  | _    | V    |

| Current Limit Sense Voltage Threshold                             | V <sub>ISENS</sub>    | 0.09 | 0.1  | 0.11 | V    |

| Thermal Shutdown Temperature                                      | T <sub>SD</sub>       | 150  | 165  | 180  | °C   |

| T <sub>SD</sub> Hysteresis                                        | T <sub>SD-HYS</sub>   | _    | 30   | _    | °C   |

#### Notes

- 15. @  $T_A = 25^{\circ}C$ , 14 V =< V+ =< 28 V,  $I_O = 1.0$  A.

- 16. Typical value (for reference only) @  $85^{\circ}$ C =<  $T_J$  =<  $150^{\circ}$ C, 8.0 V =< V+ =< 14 V. Not tested; not guaranteed.

- 17.  $@ I_F = 1.0 \text{ A for each output MOSFET (measured from source to drain).}$

#### **DYNAMIC ELECRTICAL CHARACTERISTICS**

#### **Table 4. Dynamic Electrical Characteristics**

Characteristics noted under conditions 7.0 V  $\leq$  V<sub>SUP</sub>  $\leq$  18 V, -0°C  $\leq$  T<sub>A</sub>  $\leq$  85°C, GND = 0 V unless otherwise noted. Typical values noted reflect the approximate parameter means at T<sub>A</sub> = 25°C under nominal conditions unless otherwise noted.

| Characteristic                                              | Symbol              | Min | Тур   | Max   | Unit |

|-------------------------------------------------------------|---------------------|-----|-------|-------|------|

| Charge Pump Switching Frequency                             | F <sub>CP</sub>     | _   | 250   | _     | kHz  |

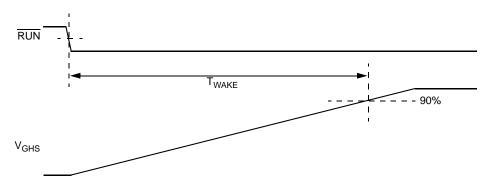

| High-Side Gate-Drive Supply Wake-Up Time                    | T <sub>WAKE</sub>   | _   | 1.0   | 2.0   | ms   |

| Controlled Braking Period                                   | T <sub>CBRK</sub>   | _   | 20    | _     | ms   |

| Low V+ Detect Suspend Time                                  | T <sub>SPND</sub>   | _   | 100   | _     | μs   |

| Power-On Reset Wait Time                                    | T <sub>WAIT</sub>   | _   | 1.0   | _     | ms   |

| Maximum PWM Input Frequency                                 | F <sub>PWM</sub>    | _   | _     | 100   | kHz  |

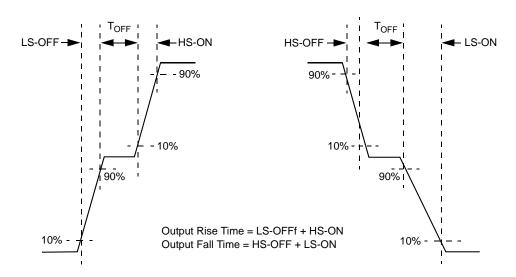

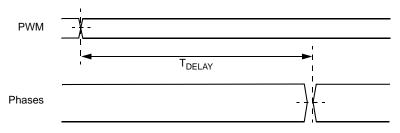

| Propagation Delay Time <sup>(18)</sup>                      | T <sub>DELAY</sub>  | _   | _     | (1.0) | μs   |

| Output Low Side Off Time (Rise) (18)                        | T <sub>LS-OFF</sub> | _   | (25)  | _     | ns   |

| Output High Side On Time (Rise) (18)                        | T <sub>HS-ON</sub>  | _   | (25)  | _     | ns   |

| Output High Side Off Time (Fall) (18)                       | T <sub>HS-OFF</sub> | _   | (25)  | _     | ns   |

| Output Low Side On Time (Fall) (18)                         | T <sub>LS-ON</sub>  | _   | (175) | _     | ns   |

| Shoot Through Prevention Time (Output H-bridge High-Z) (18) | T <sub>OFF</sub>    | _   | (100) | _     | ns   |

#### Notes

18. Load condition: Star connected 5.6  $\Omega$  load resistances (approximates 1.0 A output current at 12V V+).

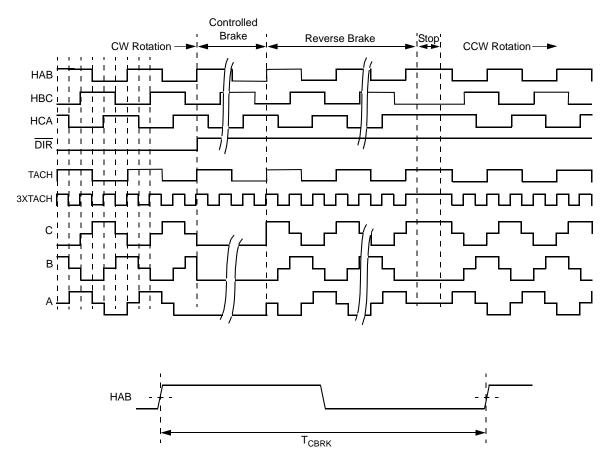

#### **TIMING DIAGRAMS**

Figure 5. High-Side Gate-Drive Supply Wake-Up Time "Twake"

Figure 6. Timing for Reset on Low V+ Detect

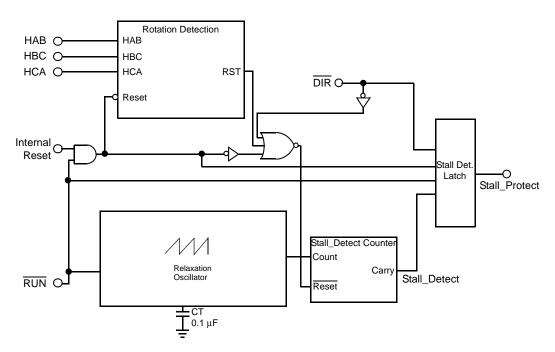

Figure 7. Stall Detection/Protection Timing

Figure 8. Rise Time, Fall Time, Shoot Through Prevention Timing

Figure 9. Controlled Brake Mode Timing

Figure 10. Stalled Rotor Detection Logic Diagram

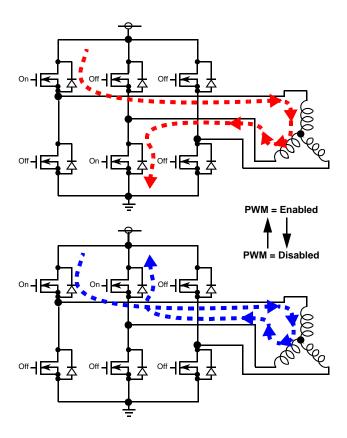

Figure 11. Synchronous Rectification "Slow-Decay Current" Example

Figure 12. PWM Switching Waveforms

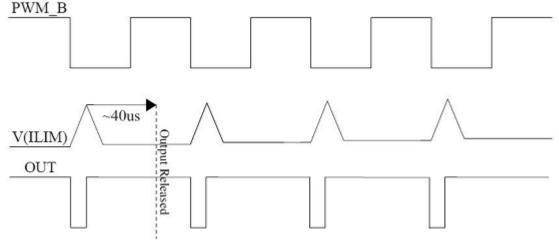

Figure 13. ISENS Current Limit Waveforms

Figure 14. Propagation Delay

#### **FUNCTIONAL DESCRIPTION**

#### INTRODUCTION

The MC34929 Brushless DC Motor Driver IC is a complete BLDC motor driver system in one chip. It is designed to efficiently drive three-phase BLDC motors up to 1.0 A and 28 V, and has built in protection features making it ideal for a variety of consumer and office applications containing small motors. Because it has a built-in Hall-sensors interface and

Hall sensors bias supply, it can operate motors either standalone (e.g., with pushbutton/switch interface), or under the control of an external MCU. Its sophisticated analog/mixedsignal state machine accommodates several modes of operation, including: clockwise, counterclockwise, run/stop, brake, variable speed (PWM), and torque limit (current limit).

#### **FUNCTIONAL PIN DESCRIPTION**

#### HAL CA NEG (HCA-)

Receives negative output from sensor located between 'c' and 'a' phases.

#### HAL CA POS (HCA+)

Receives positive output from sensor located between 'c' and 'a' phases.

#### **HAL BC NEG (HBC-)**

Receives negative output from sensor located between 'b' and 'c' phases.

#### HAL BC POS (HBC+)

Receives positive output from sensor located between 'b' and 'c' phases.

#### HAL AB NEG (HAB-)

Receives negative output from sensor located between 'a' and 'b' phases.

#### HAL AB POS (HAB+)

Receives positive output from sensor located between 'a' and 'b' phases.

#### **RESERVOIR CAP (CRES)**

External charge pump resevoir cap.

#### **CHARGE PUMP POS (CP+)**

Positive side of charge pumping cap.

#### **CHARGE PUMP NEG (CP-)**

Negative side of charge pumping cap.

#### **POSITIVE SUPPLY (V+)**

Main supply input for device and monitor.

#### **SIGNAL GROUND (GND)**

Signal ground for the device.

#### **TIMING CAP (CT)**

External cap for stall detect timing.

#### **HALL VOLTAGE (VH)**

Supply voltage for the external hall sensors.

#### PHASE C OUTPUT (PHC)

Half bridge output for phase "c" motor winding.

#### PHASE A OUTPUT (PHC)

Half bridge output for phase "a" motor winding.

#### LOW SIDE SOURCES (LSS)

Common source pin for lower half of bridge.

#### PHASE B OUTPUT (PHB)

Half bridge output for phase "b" motor winding.

#### **CURRENT SENSE (ISENS)**

Current limiting sense resistor input.

#### **RUN (RUN)**

Run/stop control input (active low = motor running).

#### TACH OUTPUT (TACH)

Open-drain-buffered output of sensor 'ab'.

#### 3X TACH OUTPUT (3XTACH)

Open-drain-buffered, exor'ed output of all three sensors.

#### **DIRECTION (DIR)**

Direction control input (active low = cw rotation).

#### **POWER GROUND (PGND)**

Power ground.

#### **PWM OR ENABLE (PWM)**

Pwm signal input (active low = outputs enabled).

#### **FUNCTIONAL DEVICE OPERATION**

The following paragraphs describe the internal function of the 34929 as shown in Figure 2.

#### **CHARGE PUMP**

This charge pump provides the VGHS and internal power supply for the high side power MOSFET gate drive. Its output voltage is limited to V+ +10V to prevent damage to the driver circuits or MOSFET gates. However, VGHS will be below V+ +10V if V+ supply voltage is below 12V. The switching frequency of this charge pump is ~250 kHz. The VGHS supply wakes up typically 1ms after the RUN command is initiated.

#### REGULATORS AND VOLTAGE REFERENCE

Internal regulators provide operating and reference voltages for use by the analog/mixed-signal circuitry. This function also includes providing the drive voltage for the low-side gate drivers. The regulators for the internal logic and analog circuits comprise regulators for the logic circuits, and regulators for the analog circuits (including input/output buffering, but excepting the power outputs). A bandgap circuit generates the internal precision reference voltage (1.25 V). This is used for biasing the comparators and other analog circuits. (Note: this reference voltage is not externally available.)

#### INTERNAL CLOCK

The internal clock generates a stable pulse-train for use by the IC's logic circuits. Its output frequency is 1.0 MHz ±30%. The clock circuit also includes frequency-dividers to derive lower frequency pulse trains for use by circuits such as the charge pump and various internal timers, etc.).

#### **INPUT LOGIC**

All logic input pins have internal 100K  $\Omega$  pull-ups connected to the internal Vdd logic supply. The logic input circuitry includes the following inputs:

- PWM input controls the speed of motor. Output = "Enable" when PWM = "L", and then Output = "Disable" (means "Z": High Impedance) when PWM = "H".

- RUN input controls the start and stop function. When RUN

= "H", this IC will go to suspend mode via controlled brake

state and suspend unnecessary circuits (Internal OSC,

Counters, Charge pump, Stall detection and protection).

- DIR input controls the direction of motor. When DIR is flipped, the motor will be reverse, brake through controlled brake, and then rotate to reverse direction. This DIR pin has capability to be applied to V+ + VF.

#### HALL COMPARATORS

The Hall comparators square-up the signals from the Hall sensors.

#### HALL SWITCH

A high side switch to turn-on and turn-off the Hall supply current.

#### TACH, 3XTACH OUTPUT

The TACH outputs are as follows: TACH is the inverted HAB signal. 3XTACH is from inverted EXOR with all three Hall sensor signals. These outputs are both open drain type.

#### LOW V+ DETECT

The low V+ voltage detection circuit monitors V+; if the V+ voltage falls below the threshold, the IC will reset after  $T_{SPND}$  time. This circuitry will not respond to negative-going transients on V+ within the  $T_{SPND}$  time period. Once placed in suspend mode, V+ must return to a level greater than the detection threshold plus and additional 100mv (typical) hysteresis, and stay there for the  $T_{WAIT}$  period, before the IC will come out of suspend mode.

#### **RESET**

The reset function works as follows: when an error condition, such as V+ falling below the V+ $_{\text{-LV}}$  threshold, is detected, the IC will be in placed in suspend mode (all output MOSFETs set to a high impedance state) by way of a controlled-braking transition state. This will occur regardless of RUN command status. Note, the error condition must exist for a time period greater than  $T_{\text{SPND}}$  before the internal reset will be generated. When the error condition resolves, suspend mode will be released after the  $T_{\text{WAIT}}$  period. (See Figure 6.)

#### STALL DETECTION AND PROTECTION

The stall detection and protection circuit actively monitors operation for a stalled rotor event while the RUN command is set = "True". A stall is detected as follows (see <a href="Figure 7">Figure 7</a>):

- 1) A sawtooth waveform generated at the timing capacitor, TC, is monitored by the stall-detect counter which is counting the sawtooth cycles.

- 2) The stall-detect counter is being reset (cleared) every time there is a transition on any of the outputs from the Hall comparators (HAB, HBC, or HCA).

- 3) A "stall condition" is assumed anytime the stall-detect counter is allowed to overflow, (i.e., anytime the counter is not cleared back to zero by the EXOR'ed output of the HAB, HBC, and HCA comparators). This can only occur when at least two of the signals (HAB, HBC, or HCA) have become static (fixed to "H" or "L").

- 4) Once the internal Stall-Detect signal is asserted, an internal Stall-Protect signal is latched. The Stall-Protect latch keeps the IC in suspend-mode even if the stall condition is subsequently resolved.

- 5) The Stall-Protect Latch can only be reset by Toggling V+,  $\overline{RUN}$  or  $\overline{DIR}$ .

#### **PWM CONTROL**

The phase outputs can be controlled with a PWM input. During PWM'ing, the freewheeling currents generated by the motor's windings are synchronously rectified by the output H-bridge to produce a slow decay waveform and avoid dissipating excess power in the IC (see Figure 12).

#### **CURRENT LIMIT**

The current limit function provides the means to set the maximum allowed motor current, and thus effectively sets the maximum possible torque the motor can apply to its load. The function is implemented via an external sense resistance  $R_{\mbox{\scriptsize ISENSE}}$  through which flows the return current of the 3-phase H-bridge. The voltage drop across  $R_{\mbox{\scriptsize ISENSE}}$  is monitored by the ISENS pin, and whenever the threshold of 0.1V is exceeded, the phase that is currently low will be brought high. The output will be released ~40  $\mu s$  later. The output will then follow the PWM input once again.

#### **CONTROLLED BRAKE MODE**

The controlled brake mode prevents high Back-EMF voltages from being created when decelerating the motor to change direction. When the DIR command changes state, all three phases are held low for the time period "T<sub>CBRK</sub>" (~20 msec @ 500 rpm with a 12-pole rotor). See Figure 12.

#### SHORT CIRCUIT PROTECTION

The short circuit protection function utilizes sense-FETs in the H-bridge high-side MOSFETs. If a short circuit occurs the sense-FET portion of the affected high-side MOSFET's cells will provide an output to the short-circuit detection circuitry that exceeds the preset threshold, and the short-circuit detection circuitry will immediately set all phase output to LOW (i.e., all low-side MOSFETs will be turned on).

#### THERMAL SHUTDOWN

The thermal shutdown protection function utilizes an onchip temperature sensor and a threshold comparator with preset hysteresis. If the die temperature exceeds the  $T_{SD}$  temperature threshold, the protection circuitry will immediately set all phase outputs to OFF (i.e., all H-bridge MOSFETs will be set to a high-impedance state). Thermal shutdown reacts to any cause of over-temperature, including that resulting from prolonged running at high currents with insufficient cooling.

#### **LOGIC COMMANDS AND REGISTERS**

Table 5. 3 Phase Motor Drive Truth Table

| DIR | Hall AB | Hall BC | Hall CA | PWM | С | В | Α | TACH | ЗХТАСН |

|-----|---------|---------|---------|-----|---|---|---|------|--------|

| Х   | L       | L       | L       | Х   | Z | Z | Z | Н    | Н      |

| Х   | Н       | Н       | Н       | Х   | Z | Z | Z | L    | L      |

| L   | L       | L       | Н       | L   | Z | Н | L | Н    | Н      |

| L   | L       | Н       | L       | L   | Н | L | Z | Н    | Н      |

| L   | L       | Н       | Н       | L   | Н | Z | L | Н    | L      |

| L   | Н       | L       | L       | L   | L | Z | Н | L    | Н      |

| L   | Н       | L       | Н       | L   | L | Н | Z | L    | L      |

| L   | Н       | Н       | L       | L   | Z | L | Н | L    | L      |

| Н   | L       | L       | Н       | L   | Z | L | Н | Н    | Н      |

| Н   | L       | Н       | L       | L   | L | Н | Z | Н    | Н      |

| Н   | L       | Н       | Н       | L   | L | Z | Н | Н    | L      |

| Н   | Н       | L       | L       | L   | Н | Z | L | L    | Н      |

| Н   | Н       | L       | Н       | L   | Н | L | Z | L    | L      |

| Н   | Н       | Н       | L       | L   | Z | Н | L | L    | L      |

| L   | L       | L       | Н       | Н   | Z | Н | Н | Н    | Н      |

| L   | L       | Н       | L       | Н   | Н | Н | Z | Н    | Н      |

| L   | L       | Н       | Н       | Н   | Н | Z | Н | Н    | L      |

| L   | Н       | L       | L       | Н   | Н | Z | Н | L    | Н      |

| L   | Н       | L       | Н       | Н   | Н | Н | Z | L    | L      |

| L   | Н       | Н       | L       | Н   | Z | Н | Н | L    | L      |

| Н   | L       | L       | Н       | Н   | Z | Н | Н | Н    | Н      |

| Н   | L       | Н       | L       | Н   | Н | Н | Z | Н    | Н      |

| Н   | L       | Н       | Н       | Н   | Н | Z | Н | Н    | L      |

| Н   | Н       | L       | L       | Н   | Н | Z | Н | L    | Н      |

| Н   | Н       | L       | Н       | Н   | Н | Н | Z | L    | L      |

| Н   | Н       | Н       | L       | Н   | Z | Н | Н | L    | L      |

#### Notes

DIR: L = CW, H = CCW; Hall Signals: L = (Hx + < Hx-), H = (Hx + > Hx-); PWM: L = Enable, H = Disable

RUN = L, Internal Reset = H, All protections = "L" (Negated).

When PWM is Disabled (H), the output will be in slow decay mode on the high-side with Synchronous Rectification.

Table 6. Suspend Mode and Protection Modes Truth Table

| RUN      | DIR                     | Under<br>Voltage | Stall<br>Detect | Current<br>Limit | Short<br>Circuit | TSD | Reset | Stall<br>Protect | PHASES  | TACH<br>3XTACH | НВ  |

|----------|-------------------------|------------------|-----------------|------------------|------------------|-----|-------|------------------|---------|----------------|-----|

| SUSPEND  | SUSPEND MODE            |                  |                 |                  |                  |     |       |                  |         |                |     |

| Н        | Х                       | Х                | Х               | Х                | Х                | Х   | Х     | Х                | L->Z    | Н              | Off |

| THERMAL  | SHUTDOW                 | N                |                 |                  |                  |     |       |                  |         |                |     |

| L        | Х                       | Х                | Х               | Х                | Х                | Н   | Х     | Х                | Z       | Н              | Off |

| SHORT CI | RCUIT PRO               | TECTION          |                 |                  |                  |     |       |                  |         |                |     |

| L        | Х                       | Х                | Х               | Х                | Н                | L   | Н     | Х                | L       | Н              | Off |

| CURRENT  | LIMIT DETE              | CTION            |                 |                  |                  |     |       |                  |         |                |     |

| L        | Х                       | Х                | Х               | Н                | L                | L   | Н     | Х                | Int.PWM | Run            | On  |

| STALL DE | TECTION A               | ND PROTEC        | TION            |                  |                  |     |       |                  |         |                |     |

| L        | Х                       | L                | Н               | L                | L                | L   | Н     | Н                | Z       | Stall          | On  |

| L        | Х                       | L                | L               | L                | L                | L   | Н     | Н                | Z       | Run            | On  |

| H->L     | Х                       | L                | L               | L                | L                | L   | Н     | L                | Run     | Run            | On  |

| L        | Flip                    | L                | L               | L                | L                | L   | Н     | L                | Run     | Run            | On  |

| L        | Х                       | H->L             | L               | L                | L                | L   | Н     | L                | Run     | Run            | On  |

| UNDER VO | INDER VOLTAGE DETECTION |                  |                 |                  |                  |     |       |                  |         |                |     |

| X        | Х                       | Н                | Х               | Х                | X                | Х   | L     | L                | L->Z    | Н              | Off |

| L        | Х                       | H->L             | L               | L                | L                | L   | Н     | L                | Run     | Run            | On  |

| NORMAL I | MODE                    |                  |                 |                  |                  |     |       |                  |         |                |     |

| L        | Х                       | L                | L               | L                | L                | L   | Н     | L                | Run     | Run            | On  |

#### Notes

RUN: Start at "L" and Stop at "H". "H->L" indicates input is toggled.

DIR: CW direction at "L" and CCW direction at "H" and "Flip" indicates change of logic level to opposite state.

"Under Voltage", "Stall Detect", "Current Llmit", Short Circuit", "TSD", and "Stall Protect" are "High" active internal signals. "Reset" is a "Low" active internal signal.

Under Voltage: H->L indicates removing then re-applying power (V+).

"Run" status indicates operation in 3-phase commutation mode.

Commanding a "Stop" state from a "Run" state will always result in a transition through the "Controlled Brake" state (to prevent high voltage Back-EMF), before changing to OFF (high-Z).

# **TYPICAL APPLICATIONS**

Figure 15. Simple Application Circuit

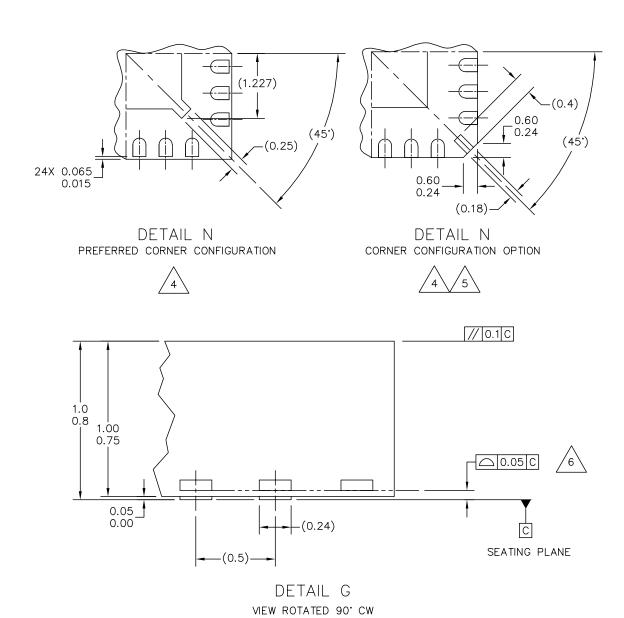

### **PACKAGING**

#### **PACKAGE DIMENSIONS**

For the most current package revision, visit www.freescale.com and perform a keyword search using the "98A" listed below.

| © FREESCALE SEMICONDUCTOR, INC.<br>ALL RIGHTS RESERVED. | L OUTLINE  | PRINT VERSION NO               | T TO SCALE        |        |

|---------------------------------------------------------|------------|--------------------------------|-------------------|--------|

| TITLE: THERMALLY ENHANCED                               | QUAD       | DOCUMENT NO                    | ): 98ARH99033A    | REV: C |

| FLAT NON-LEADED PACK                                    |            | CASE NUMBER: 1307-01 06 SEP 20 |                   |        |

| 24 TERMINAL, 0.5 PITCH (                                | 4 X 4 X 1) | STANDARD: JE                   | DEC MO-220 VGGD-2 |        |

QFN SUFFIX 24-PIN PLASTIC PACKAGE 98ARH99033A ISSUE C

| © FREESCALE SEMICONDUCTOR, INC. ALL RIGHTS RESERVED.  MECHANICAL |                               | L OUTLINE                     | PRINT VERSION NO | T TO SCALE |

|------------------------------------------------------------------|-------------------------------|-------------------------------|------------------|------------|

| TITLE: THERMALLY ENHANCED                                        | QUAD                          | DOCUMENT NO                   | ): 98ARH99033A   | REV: C     |

| FLAT NON-LEADED PACKAG                                           | GE (QFN)                      | CASE NUMBER: 1307-01 06 SEP 2 |                  |            |

| 24 TERMINAL, 0.5 PITCH (4                                        | STANDARD: JEDEC MO-220 VGGD-2 |                               |                  |            |

QFN SUFFIX 24-PIN PLASTIC PACKAGE 98ARH99033A ISSUE C

# **REVISION HISTORY**

| REVISION | DATE   | DESCRIPTION OF CHANGES                                                                                                            |

|----------|--------|-----------------------------------------------------------------------------------------------------------------------------------|

| 6.0      | 7/2005 | <ul> <li>Implemented Revision History page</li> <li>Updated to the Freescale format</li> <li>Changed status to Advance</li> </ul> |

#### How to Reach Us:

**Home Page:**

www.freescale.com

support@freescale.com

**USA/Europe or Locations Not Listed:**

Freescale Semiconductor Technical Information Center, CH370 1300 N. Alma School Road Chandler, Arizona 85224 +1-800-521-6274 or +1-480-768-2130 support@freescale.com

**Europe, Middle East, and Africa:** Freescale Halbleiter Deutschland GmbH Technical Information Center Schatzbogen 7 81829 Muenchen, Germany +44 1296 380 456 (English) +46 8 52200080 (English) +49 89 92103 559 (German) +33 1 69 35 48 48 (French) support@freescale.com

Freescale Semiconductor Japan Ltd. Headquarters ARCO Tower 15F 1-8-1, Shimo-Meguro, Meguro-ku, Tokyo 153-0064 Japan 0120 191014 or +81 3 5437 9125 support.japan@freescale.com

#### Asia/Pacific:

Freescale Semiconductor Hong Kong Ltd. **Technical Information Center** 2 Dai King Street

Tai Po Industrial Estate Tai Po, N.T., Hong Kong +800 2666 8080 support.asia@freescale.com

For Literature Requests Only:

Freescale Semiconductor Literature Distribution Center P.O. Box 5405 Denver, Colorado 80217 1-800-441-2447 or 303-675-2140 Fax: 303-675-2150 LDCForFreescaleSemiconductor@hibbertgroup.com

Information in this document is provided solely to enable system and software implementers to use Freescale Semiconductor products. There are no express or implied copyright licenses granted hereunder to design or fabricate any integrated circuits or integrated circuits based on the information in this document.

Freescale Semiconductor reserves the right to make changes without further notice to any products herein. Freescale Semiconductor makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does Freescale Semiconductor assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation consequential or incidental damages. "Typical" parameters that may be provided in Freescale Semiconductor data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals", must be validated for each customer application by customer's technical experts. Freescale Semiconductor does not convey any license under its patent rights nor the rights of others. Freescale Semiconductor products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other applications intended to support or sustain life, or for any other application in which the failure of the Freescale Semiconductor product could create a situation where personal injury or death may occur. Should Buyer purchase or use Freescale Semiconductor products for any such unintended or unauthorized application, Buyer shall indemnify and hold Freescale Semiconductor and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that Freescale Semiconductor was negligent regarding the design or manufacture of the part.

Freescale™ and the Freescale logo are trademarks of Freescale Semiconductor, Inc. All other product or service names are the property of their respective owners. © Freescale Semiconductor, Inc., 2006. All rights reserved.