## Description

The PAM8303C is a 3W mono, filterless Class-D amplifier with high PSRR and differential input that eliminate noise and RF rectification. Features like 90% efficiency and small PCB area make the PAM8303C Class-D amplifier ideal for cellular handsets. The filterless architecture requires no external output filter, fewer external components, less PCB area, and lower system costs. The filterless architecture also simplifies application design. The PAM8303C features short-circuit protection and thermal shutdown. The PAM8303C is available in MSOP-8 and DFN 3030 8-pin packages.

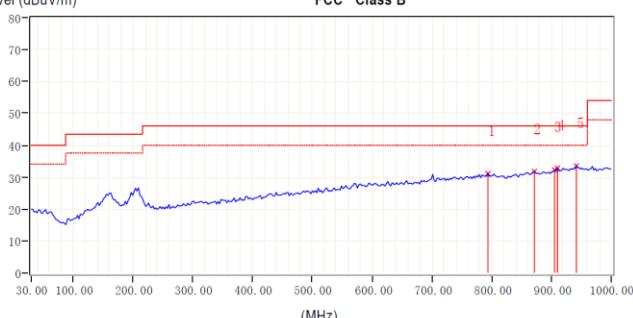

Level (dBuV/m)

FCC Class B

## Features

- Ultra-Low EMI, -20dB Better than FCC Class-B @ 300MHz

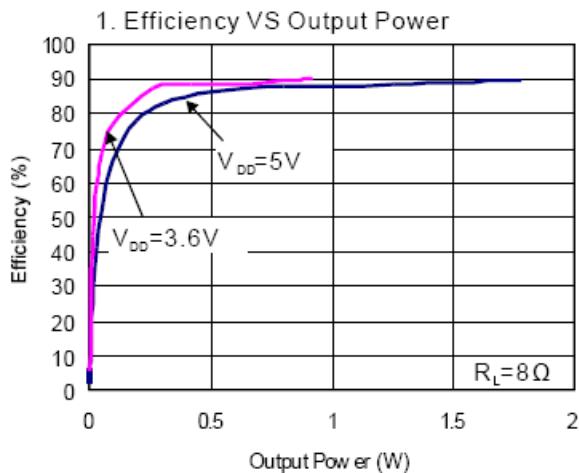

- High Efficiency up to 90% @1W with an 8Ω Speaker

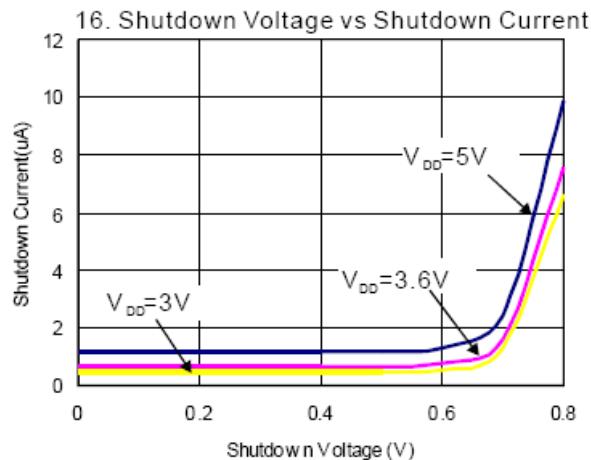

- Shutdown Current <1µA

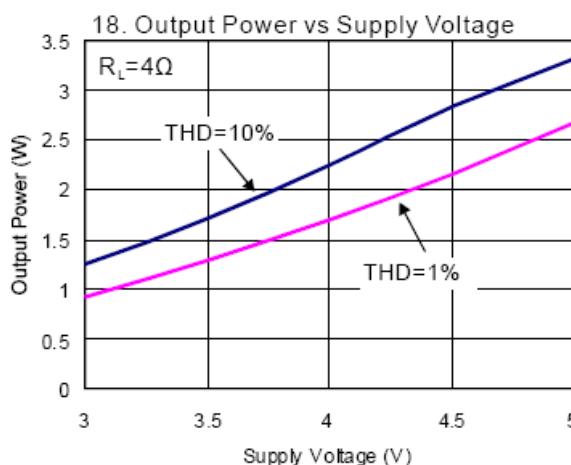

- 3W@10% THD Output with a 4Ω Load at 5V Supply

- Demanding Few External Components

- Superior Low Noise Without Input

- Supply Voltage from 2.8V to 5.5V

- Short-Circuit Protection

- Thermal Shutdown

- **MSOP-8 and DFN 3030 8-pin Packages Totally Lead-Free & Fully RoHS Compliant (Notes 1 & 2)**

- **Halogen and Antimony Free "Green" Device (Note 3)**

## Applications

- Cellular Phones/Smart Phones

- MP4/MP3

- GPS

- Digital Photo Frame

- Electronic Dictionary

- Portable Game Machines

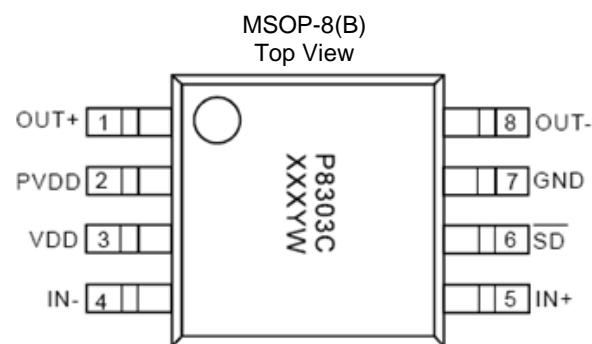

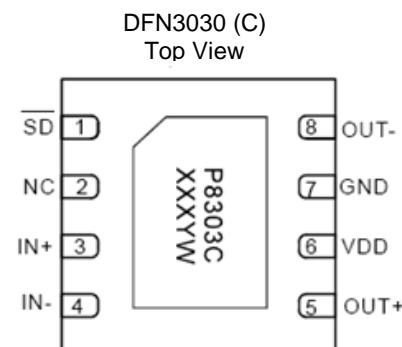

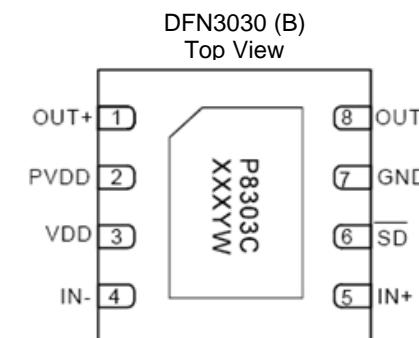

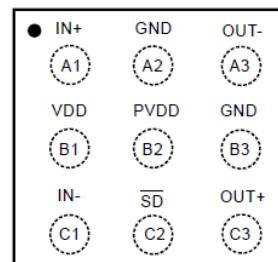

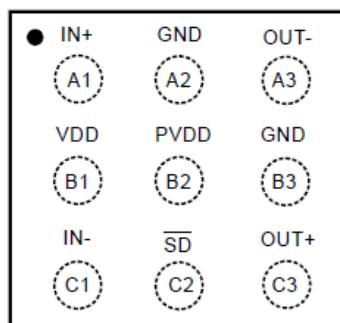

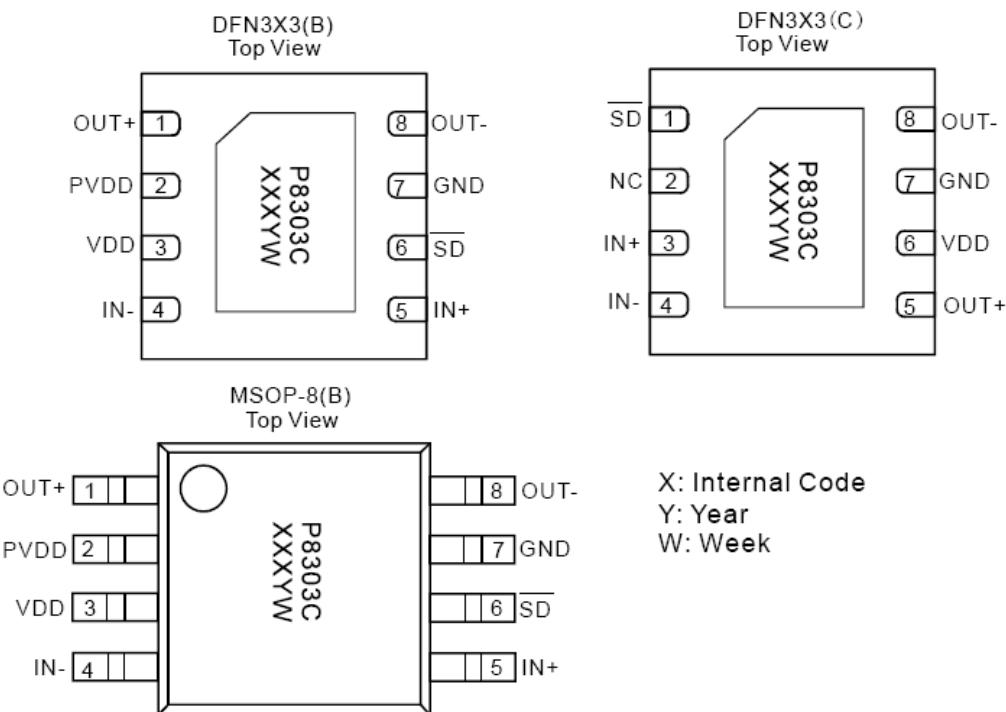

## Pin Assignments

9 Ball W CSP (A) (EOL)

Top View

Notes:

1. No purposely added lead. Fully EU Directive 2002/95/EC (RoHS), 2011/65/EU (RoHS 2) & 2015/863/EU (RoHS 3).compliant.

2. See <https://www.diodes.com/quality/lead-free/> for more information about Diodes Incorporated's definitions of Halogen- and Antimony-free, "Green" and Lead-free.

3. Halogen- and Antimony-free "Green" products are defined as those which contain <900ppm bromine, <900ppm chlorine (<1500ppm total Br + Cl) and <1000ppm antimony compounds.

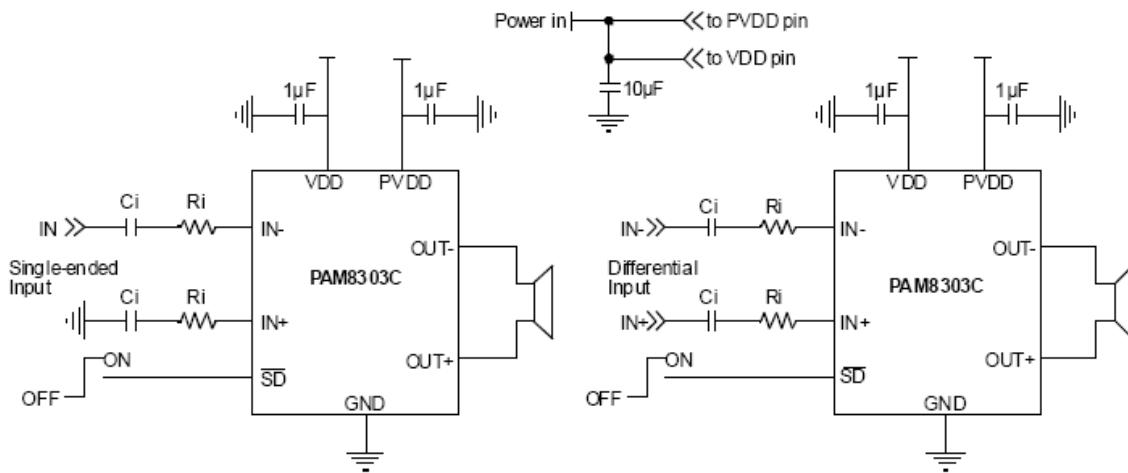

## Typical Applications Circuit

## Pin Descriptions

| Pin Name | Pin Name     |               |               |            | Function                       |

|----------|--------------|---------------|---------------|------------|--------------------------------|

|          | WCSP(A)(EOL) | DFN3030-8 (B) | DFN3030-8 (C) | MSOP-8 (B) |                                |

| OUT+     | C3           | 1             | 5             | 1          | Positive BTL Output            |

| PVDD     | B2           | 2             | —             | 2          | Power Supply                   |

| VDD      | B1           | 3             | 6             | 3          | Analog Power Supply            |

| IN-      | C1           | 4             | 4             | 4          | Negative Differential Input    |

| IN+      | A1           | 5             | 3             | 5          | Positive Differential Input    |

| SD       | C2           | 6             | 1             | 6          | Shutdown Terminal (Active Low) |

| GND      | A2, B3       | 7             | 7             | 7          | Ground                         |

| OUT-     | A3           | 8             | 8             | 8          | Negative BTL Output            |

| NC       | —            | —             | 2             | —          | —                              |

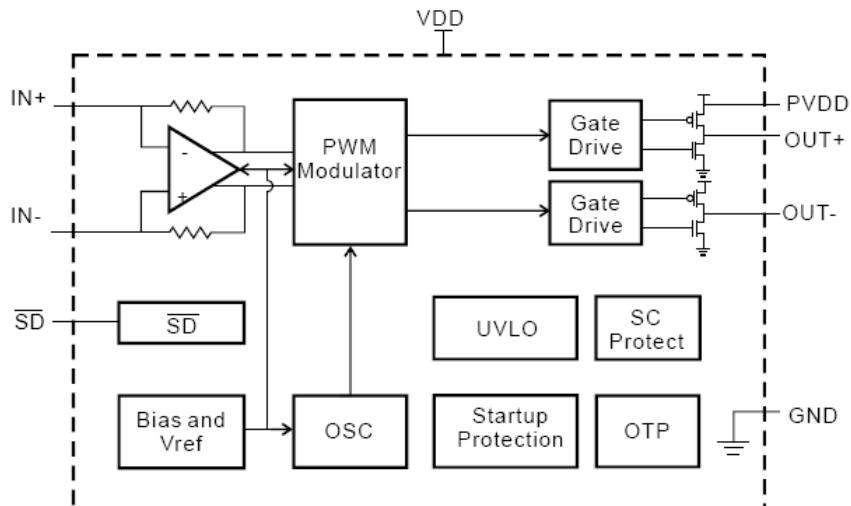

## Functional Block Diagram

## Absolute Maximum Ratings (@ $T_A = +25^\circ\text{C}$ , unless otherwise specified.)

The following parameters are stress ratings only, and functional operation is not implied. Exposure to absolute maximum ratings for prolonged time periods can affect device reliability. All voltages are with respect to ground.

| Parameter                    | Rating                 | Unit             |

|------------------------------|------------------------|------------------|

| Supply Voltage               | 6.0                    | V                |

| Input Voltage                | -0.3 to $V_{DD} + 0.3$ |                  |

| Maximum Junction Temperature | 150                    | $^\circ\text{C}$ |

| Storage Temperature          | -65 to +150            |                  |

| Soldering Temperature        | +250, 10 sec           |                  |

## Recommended Operating Conditions (@ $T_A = +25^\circ\text{C}$ , unless otherwise specified.)

| Parameter                  | Rating      | Unit             |

|----------------------------|-------------|------------------|

| Supply Voltage Range       | 2.8 to 5.5  | V                |

| Ambient Temperature Range  | -40 to +85  | $^\circ\text{C}$ |

| Junction Temperature Range | -40 to +125 | $^\circ\text{C}$ |

## Thermal Information (Note 4)

| Parameter                                | Package   | Symbol        | Max  | Unit                      |

|------------------------------------------|-----------|---------------|------|---------------------------|

| Thermal Resistance (Junction to Ambient) | MSOP-8    | $\Theta_{JA}$ | 180  | $^\circ\text{C}/\text{W}$ |

|                                          | DFN3030-8 |               | 47.9 |                           |

| Thermal Resistance (Junction to Case)    | MSOP-8    | $\Theta_{JC}$ | 75   |                           |

Note: 4. For the 9-pin CSP package, the thermal resistance is highly dependent on the PCB heat sink area. For example, the  $\Theta_{ja}$  can equal to  $195^\circ\text{C}/\text{W}$  with  $50\text{mm}^2$  total area or  $135^\circ\text{C}/\text{W}$  with  $500\text{mm}^2$  area. When using ground and power planes, the value is approximately  $90^\circ\text{C}/\text{W}$ .

**Electrical Characteristics** (@ $T_A = +25^\circ\text{C}$ ,  $V_{DD} = 5\text{V}$ , Gain = 2V/V,  $R_L = L(33\mu\text{H}) + R + L(33\mu\text{H})$ , unless otherwise specified.)

| Symbol       | Parameter                                | Test Conditions                                                          |                        |      | Min  | Typ                         | Max              | Units         |

|--------------|------------------------------------------|--------------------------------------------------------------------------|------------------------|------|------|-----------------------------|------------------|---------------|

| $V_{DD}$     | Supply Voltage                           |                                                                          |                        |      | 2.8  |                             | 5.5              | V             |

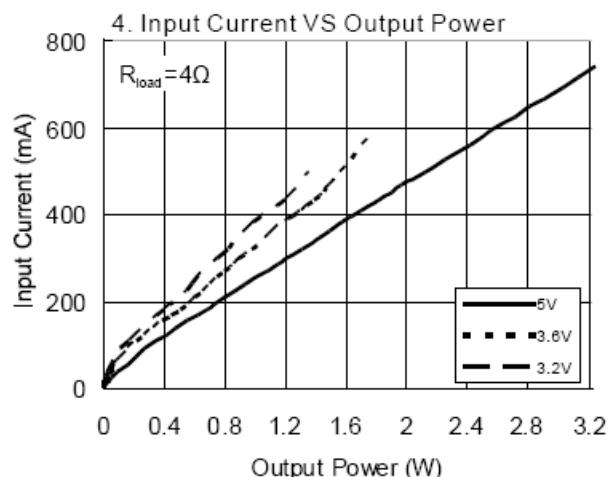

| $P_O$        | Output Power                             | THD+N = 10%, $f = 1\text{kHz}$ , $R = 4\Omega$                           | $V_{DD} = 5.0\text{V}$ | 2.85 | 3.00 | —                           | W                | W             |

|              |                                          |                                                                          | $V_{DD} = 3.6\text{V}$ | 1.65 | 1.80 | —                           |                  |               |

|              |                                          |                                                                          | $V_{DD} = 3.2\text{V}$ | 1.20 | 1.35 | —                           |                  |               |

|              |                                          | THD+N = 1%, $f = 1\text{kHz}$ , $R = 4\Omega$                            | $V_{DD} = 5.0\text{V}$ | 2.50 | 2.66 | —                           | W                | W             |

|              |                                          |                                                                          | $V_{DD} = 3.6\text{V}$ | 1.15 | 1.30 | —                           |                  |               |

|              |                                          |                                                                          | $V_{DD} = 3.2\text{V}$ | 0.85 | 1.0  | —                           |                  |               |

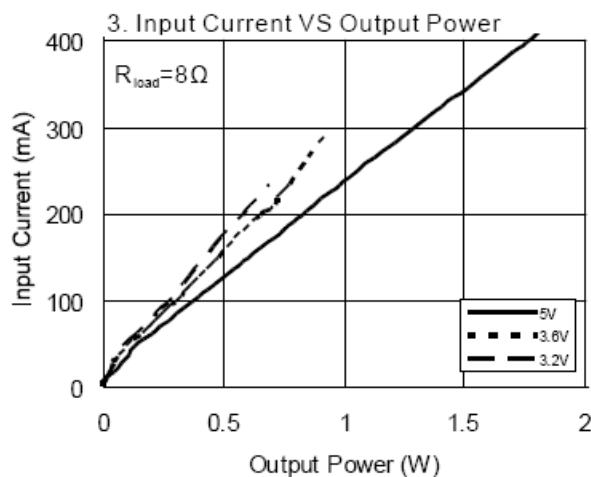

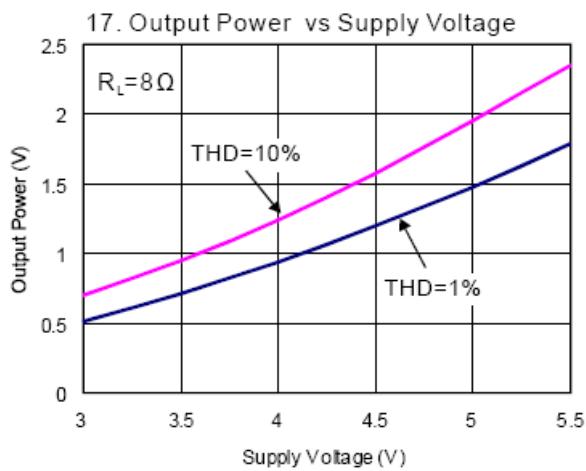

|              |                                          | THD+N = 10%, $f = 1\text{kHz}$ , $R = 8\Omega$                           | $V_{DD} = 5.0\text{V}$ | 1.65 | 1.8  | —                           | W                | W             |

|              |                                          |                                                                          | $V_{DD} = 3.6\text{V}$ | 0.75 | 0.9  | —                           |                  |               |

|              |                                          |                                                                          | $V_{DD} = 3.2\text{V}$ | 0.55 | 0.7  | —                           |                  |               |

|              |                                          | THD+N = 1%, $f = 1\text{kHz}$ , $R = 8\Omega$                            | $V_{DD} = 5.0\text{V}$ | 1.3  | 1.5  | —                           | W                | W             |

|              |                                          |                                                                          | $V_{DD} = 3.6\text{V}$ | 0.55 | 0.72 | —                           |                  |               |

|              |                                          |                                                                          | $V_{DD} = 3.2\text{V}$ | 0.40 | 0.55 | —                           |                  |               |

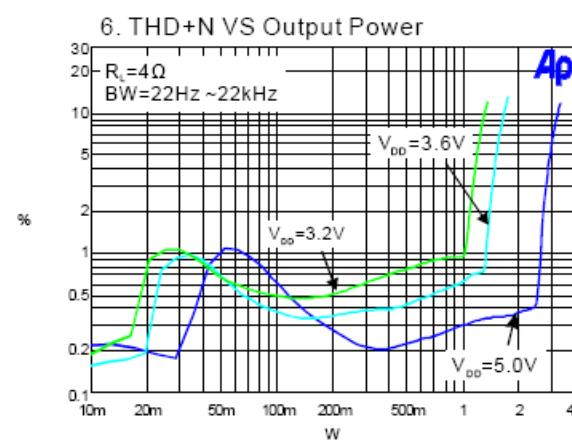

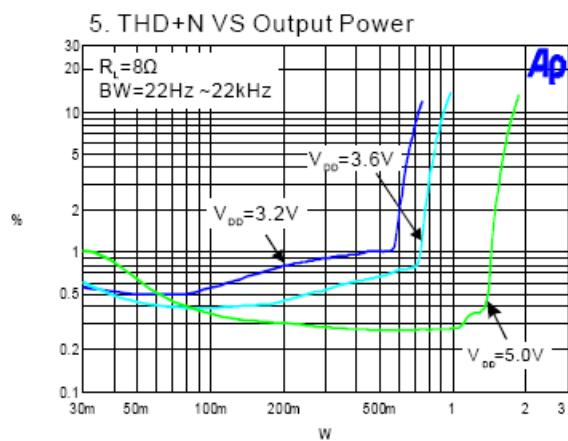

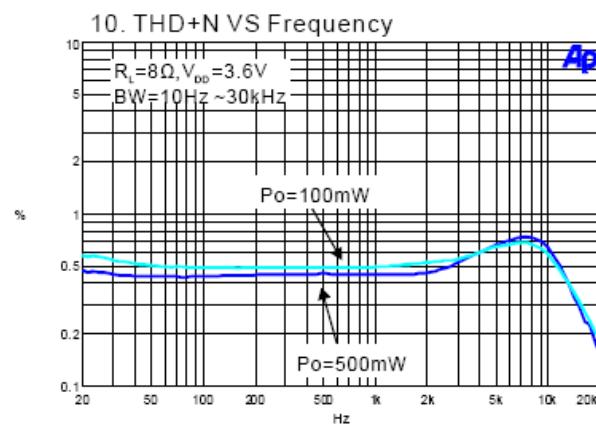

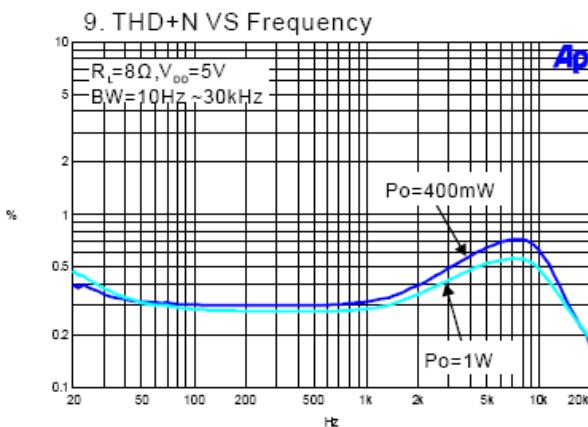

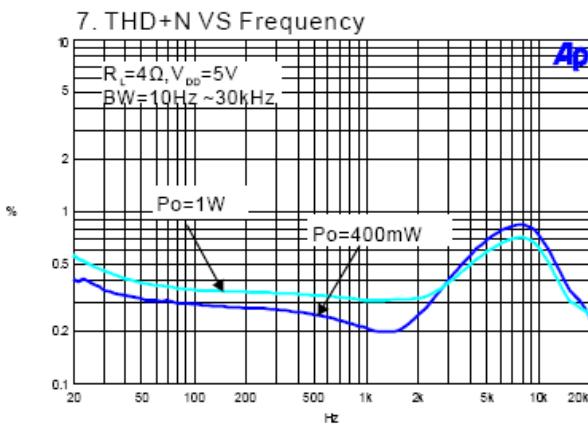

| THD+N        | Total Harmonic Distortion Plus Noise     | $V_{DD} = 5.0\text{V}$ , $P_O = 1\text{W}$ , $R = 8\Omega$               | $f = 1\text{kHz}$      | —    | 0.28 | 0.35                        | %                | %             |

|              |                                          | $V_{DD} = 3.6\text{V}$ , $P_O = 0.1\text{W}$ , $R = 8\Omega$             |                        | —    | 0.40 | 0.45                        |                  |               |

|              |                                          | $V_{DD} = 3.2\text{V}$ , $P_O = 0.1\text{W}$ , $R = 8\Omega$             |                        | —    | 0.55 | 0.60                        |                  |               |

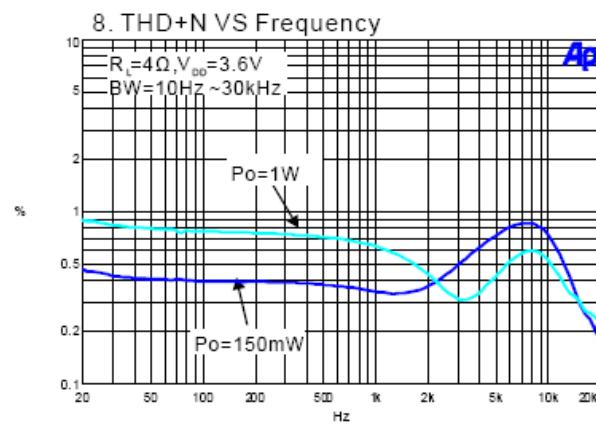

|              |                                          | $V_{DD} = 5.0\text{V}$ , $P_O = 0.5\text{W}$ , $R = 4\Omega$             | $f = 1\text{kHz}$      | —    | 0.20 | 0.25                        | %                | %             |

|              |                                          | $V_{DD} = 3.6\text{V}$ , $P_O = 0.2\text{W}$ , $R = 4\Omega$             |                        | —    | 0.35 | 0.40                        |                  |               |

|              |                                          | $V_{DD} = 3.2\text{V}$ , $P_O = 0.1\text{W}$ , $R = 4\Omega$             |                        | —    | 0.5  | 0.55                        |                  |               |

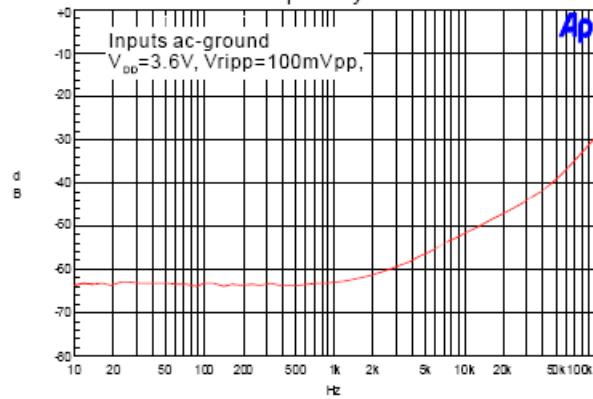

| PSRR         | Power Supply Ripple Rejection            | $V_{DD} = 3.6\text{V}$ , Inputs AC-Grounded with $C_{IN} = 1\mu\text{F}$ | $f = 217\text{Hz}$     | —    | -63  | -55                         | dB               | dB            |

|              |                                          |                                                                          | $f = 1\text{kHz}$      | —    | -62  | -55                         |                  |               |

|              |                                          |                                                                          | $f = 10\text{kHz}$     | —    | -52  | -40                         |                  |               |

| Dyn          | Dynamic Range                            | $V_{DD} = 5\text{V}$ , THD = 1%, $R = 8\Omega$                           | $f = 1\text{kHz}$      | 85   | 95   | —                           |                  |               |

| $V_N$        | Output Noise                             | Inputs AC-Grounded                                                       | No A-Weighting         | —    | 50   | 100                         | $\mu\text{V}$    | $\mu\text{V}$ |

|              |                                          |                                                                          | A-Weighting            | —    | 30   | 60                          |                  |               |

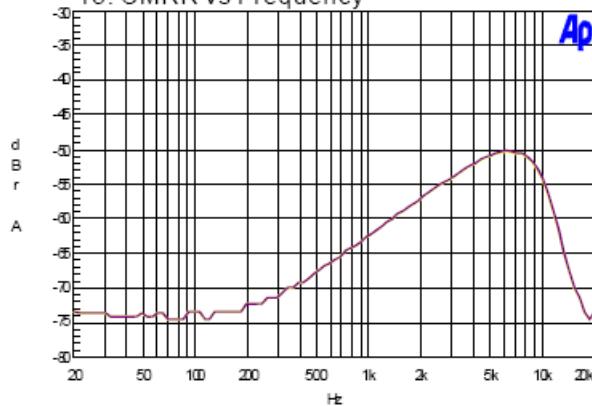

| CMRR         | Common-Mode Rejection Ratio              | $V_{IC} = 100\text{mV}$ , $V_{PP}$ , $f = 1\text{kHz}$                   |                        | 40   | 63   | —                           |                  |               |

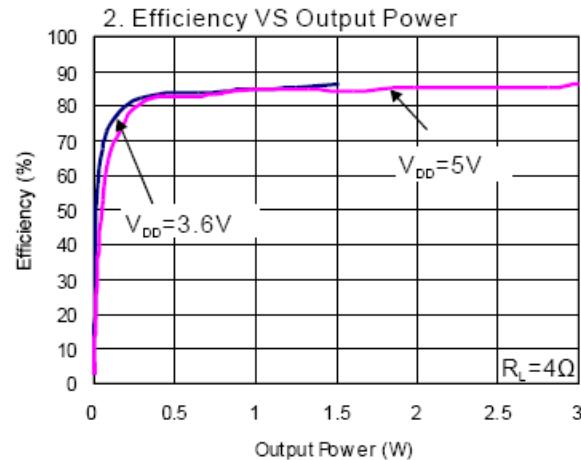

| $\eta$       | Peak Efficiency                          | $R_L = 8\Omega$ , THD = 10%                                              | $f = 1\text{kHz}$      | 85   | 90   | —                           | %                | %             |

|              |                                          | $R_L = 4\Omega$ , THD = 10%                                              |                        | 80   | 86   | —                           |                  |               |

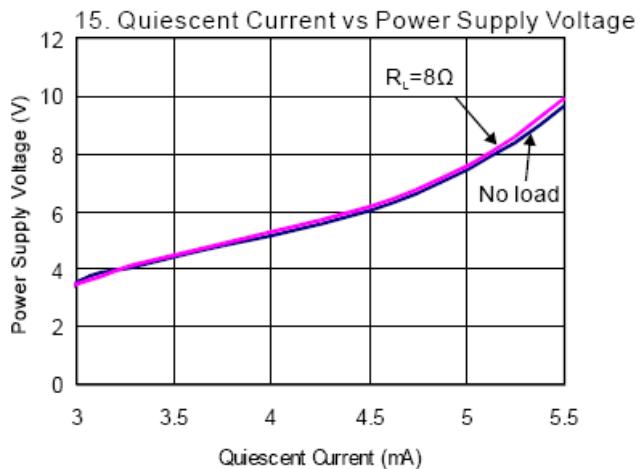

| $I_Q$        | Quiescent Current                        | $V_{DD} = 5.0\text{V}$                                                   | $R = 8\Omega$          | —    | 7.5  | 10                          | mA               | mA            |

|              |                                          | $V_{DD} = 3.6\text{V}$                                                   |                        | —    | 4.6  | 7                           |                  |               |

|              |                                          | $V_{DD} = 3.0\text{V}$                                                   |                        | —    | 3.6  | 5                           |                  |               |

| $I_{SD}$     | Shutdown Current                         | $V_{DD} = 3.0\text{V}$ to $5.0\text{V}$                                  | $V_{SD} = 0.3\text{V}$ | —    | 0.5  | 2                           | $\mu\text{A}$    |               |

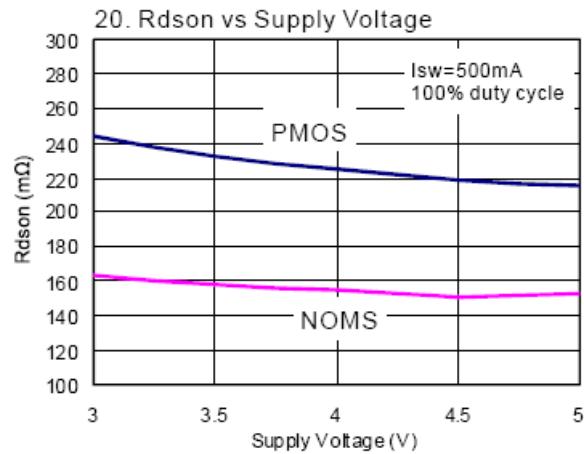

| $R_{DS(ON)}$ | Static Drain-to-Source On-State Resistor | CSP Package, High Side PMOS plus Low Side NMOS, $I = 500\text{mA}$       | $V_{DD} = 5.0\text{V}$ | —    | 280  | 350                         | —                | —             |

|              |                                          |                                                                          | $V_{DD} = 3.6\text{V}$ | —    | 300  | 375                         |                  |               |

|              |                                          |                                                                          | $V_{DD} = 3.0\text{V}$ | —    | 325  | 400                         |                  |               |

|              |                                          | MSOP/DFN package, High-Side PMOS plus Low-Side NMOS, $I = 500\text{mA}$  | $V_{DD} = 5.0\text{V}$ | —    | 365  | 420                         | —                | —             |

|              |                                          |                                                                          | $V_{DD} = 3.6\text{V}$ | —    | 385  | 450                         |                  |               |

|              |                                          |                                                                          | $V_{DD} = 3.0\text{V}$ | —    | 410  | 500                         |                  |               |

| $R_{IN}$     | Input Resistance                         | —                                                                        |                        | —    | 150  | —                           | $\text{k}\Omega$ |               |

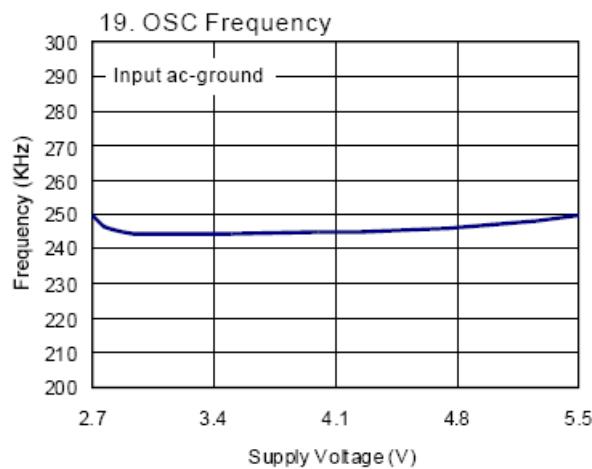

| fsw          | Switching Frequency                      | $V_{DD} = 3\text{V}$ to $5\text{V}$                                      |                        | 200  | 250  | 300                         | $\text{kHz}$     |               |

| Gv           | Closed Loop Gain                         | $V_{DD} = 3\text{V}$ to $5\text{V}$                                      |                        | —    | 300  | $\text{k}\Omega/\text{R}_I$ | —                | $\text{dB}$   |

| Vos          | Output Offset Voltage                    | Input AC-Ground, $V_{DD} = 5\text{V}$                                    |                        | —    | 10   | 50                          | $\text{mV}$      |               |

| $V_{IH}$     | Enable Input High Voltage                | $V_{DD} = 5\text{V}$                                                     |                        | 1.5  | —    | —                           | $\text{V}$       |               |

| $V_{IL}$     | Enable Input Low Voltage                 | $V_{DD} = 5\text{V}$                                                     |                        | —    | —    | 0.3                         | $\text{V}$       |               |

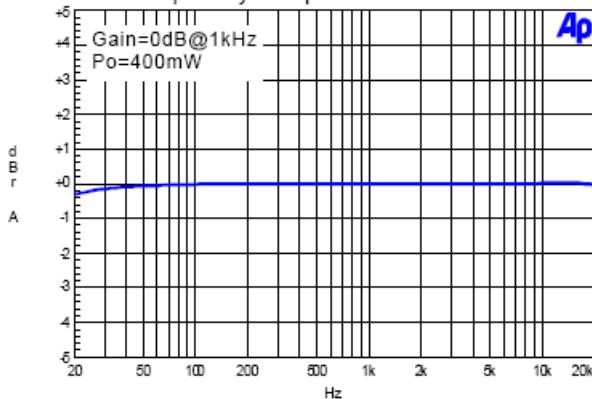

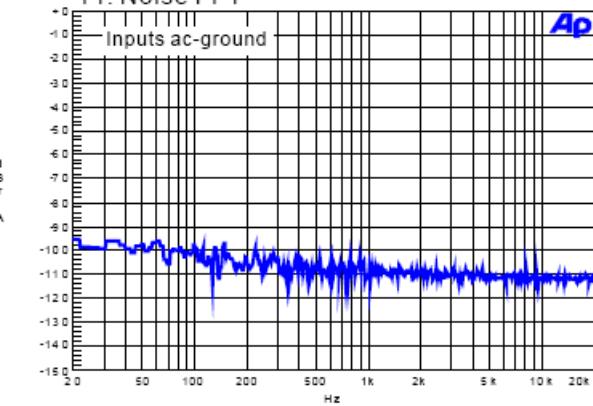

**Typical Performance Characteristics** (@ $T_A = +25^\circ\text{C}$ ,  $V_{DD} = 5\text{V}$ ,  $f = 1\text{kHz}$ , Gain = 2V/V, unless otherwise specified.)

**Typical Performance Characteristics** (continued) (@ $T_A = +25^\circ\text{C}$ ,  $V_{DD} = 5\text{V}$ ,  $f = 1\text{kHz}$ , Gain = 2V/V, unless otherwise specified.)

**Typical Performance Characteristics** (cont.) (@ $T_A = +25^\circ\text{C}$ ,  $V_{DD} = 5\text{V}$ ,  $f = 1\text{kHz}$ , Gain = 2V/V, unless otherwise specified.)

11. Frequency Response

12. PSRR VS Frequency

13. CMRR vs Frequency

14. Noise FFT

**Typical Performance Characteristics** (cont.) (@ $T_A = +25^\circ\text{C}$ ,  $V_{DD} = 5\text{V}$ ,  $f = 1\text{kHz}$ , Gain = 2V/V, unless otherwise specified.)

**Typical Performance Characteristics** (cont.) (@ $T_A = +25^\circ\text{C}$ ,  $V_{DD} = 5\text{V}$ ,  $f = 1\text{kHz}$ , Gain = 2V/V, unless otherwise specified.)

## Application Information

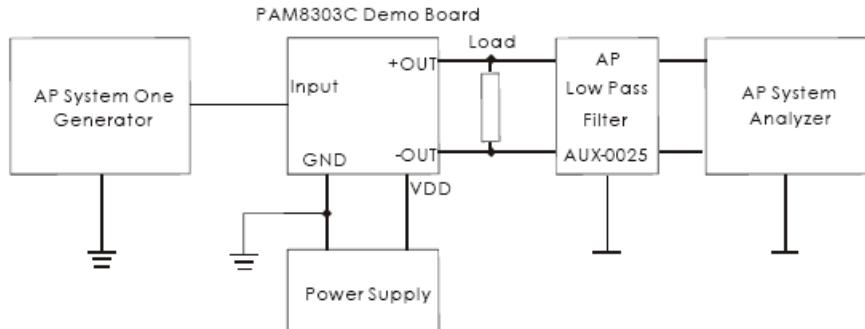

### Test Setup for Performance Testing (Notes 5 & 6)

Notes:

- 5. The AP AUX-0025 low-pass filter is necessary for Class-D amplifier measurement with AP analyzer.

- 6. Two 22 $\mu$ H inductors are used in series with load resistor to emulate the small speaker for efficiency measurement.

### Input Resistance ( $R_I$ )

The input resistors ( $R_I$ ) set the gain of the amplifier according to the following equation.

$$\text{Gain} = \frac{2 \times 150\text{k}\Omega}{R_I} \left( \frac{V}{V} \right)$$

Resistor matching is very important in fully differential amplifiers. The balance of the output on the reference voltage depends on matched ratios of the resistors. CMRR, PSRR, and cancellation of the second harmonic distortion diminish if resistor mismatch occurs. Therefore, it is recommended to use 1% tolerance resistors or better to keep the performance optimized. Matching is more important than overall tolerance. Resistor arrays with 1% matching can be used with a tolerance greater than 1%.

Place the input resistors very close to the PAM8303C to limit noise injection on the high-impedance nodes.

For optimal performance the gain must be set to  $2 \times (R_I = 150\text{k})$  or lower. Lower gain allows the PAM8303C to operate at its best and keeps a high voltage at the input, which makes the inputs less susceptible to noise. In addition to these features, higher value of  $R_I$  minimizes pop noise.

### Input Capacitors ( $C_I$ )

In the typical application, an input capacitor,  $C_I$ , is required to allow the amplifier to bias the input signal to the proper DC level for optimum operation. In this case,  $C_I$  and the minimum input impedance,  $R_I$ , form a high-pass filter with the corner frequency determined in the following equation.

$$f_C = \frac{1}{2\pi R_I C_I}$$

It is important to consider how the value of  $C_I$  as the capacitor directly affects the low-frequency performance of the circuit. For example, when  $R_I$  is  $150\text{k}\Omega$ , and the specification calls for a flat bass, response is down to 150Hz. The equation is reconfigured as follows.

$$C_I = \frac{1}{2\pi R_I f_C}$$

When input-resistance variation is considered, the  $C_I$  is  $7\text{nF}$ , so one would choose a value of  $10\text{nF}$ . A further consideration for this capacitor is the leakage path from the input source through the input network ( $C_I$ ,  $R_I + R_F$ ) to the load. This leakage current creates a DC offset voltage at the input to the amplifier that reduces useful headroom, especially in high-gain applications.

For this reason, a low-leakage tantalum or ceramic capacitor is the best choice. When polarized capacitors are used, the positive side of the capacitor should face the amplifier input in most applications as the DC level is held at  $V_{DD}/2$ , which is likely higher than the source DC level. Note that it is important to confirm the capacitor polarity in the application.

## Application Information (cont.)

### Decoupling Capacitor (Cs)

The PAM8303C is a high-performance CMOS audio amplifier that requires adequate power-supply decoupling to ensure the output total harmonic distortion (THD) as low as possible. Power-supply decoupling also prevents the oscillations caused by long lead length between the amplifier and the speaker.

The optimum decoupling is achieved by using two different types of capacitors that target on different types of noise on the power supply leads. For higher-frequency transients, spikes, or digital hash on the line, a good low equivalent series resistance (ESR) ceramic capacitor, typically 1 $\mu$ F, is placed as close as possible to the device near each V<sub>DD</sub> and P<sub>VDD</sub> pin for the best operation. For filtering lower-frequency noise signals, a large ceramic capacitor of 10 $\mu$ F or greater placed near the audio power amplifier is recommended.

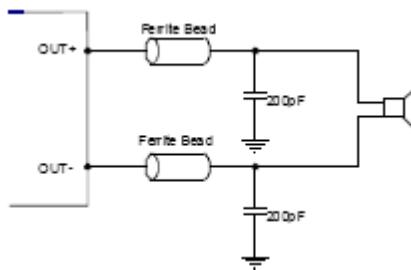

### How to Reduce EMI

Most applications require a ferrite bead filter for EMI elimination as shown in Figure 1. The ferrite filter reduces EMI around 1MHz and higher. When selecting a ferrite bead, choose one with high impedance at high frequencies but with low impedance at low frequencies.

Figure 1: Ferrite Bead Filter to Reduce EMI

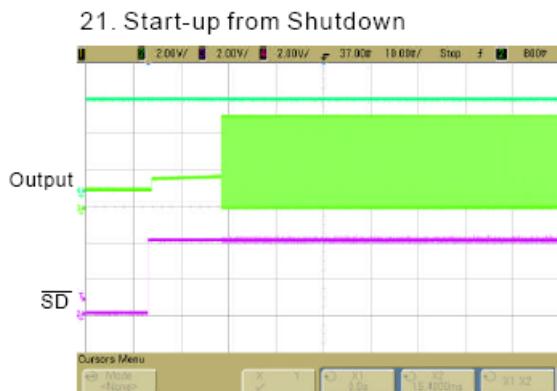

In order to reduce power consumption while not in use, the PAM8303C contains shutdown circuitry that is used to turn off the amplifier's bias circuitry. This shutdown feature turns the amplifier off when logic low is placed on the SD pin. By switching the shutdown pin connected to GND, the PAM8303C supply current draw is minimized in idle mode.

### Shutdown Operation

In order to reduce power consumption while not in use, the PAM8303C contains shutdown circuitry that is used to turn off the amplifier's bias circuitry. This shutdown feature turns the amplifier off when logic low is placed on the pin. By switching the shutdown pin connected to GND, the PAM8303C supply-current draw will be minimized in idle mode.

### Undervoltage Lockout (UVLO)

The PAM8303C incorporates circuitry designed to detect low supply voltage. When the supply voltage drops to 2.3V or below, the PAM8303C goes into a state of shutdown, and the device comes out of its shutdown state and restores to normal function only when reset the power supply or SD pin.

Thermal protection on the PAM8303C prevents the device from damage when the internal die temperature exceeds +135°C. There is a 15°C tolerance on this trip point from device to device. Once the die temperature exceeds the set point, the device enters the shutdown state, and the outputs are disabled. This is not a latched fault. The thermal fault is cleared once the temperature of the die decreases by 30°C. This large hysteresis prevents motor-boating sound, and the device begins normal operation at this point with no external system interaction.

### Pop and Click Circuitry

The PAM8303C contains circuitry to minimize turn-on and turn-off transients, or *click and pops*, where turn-on refers to either power supply turn on or device recovery from shutdown mode. When the device is turned on, the amplifiers are internally muted. An internal current source ramps up the internal reference voltage. The device remains in mute mode until the reference voltage reaches half-supply voltage, 1/2 V<sub>DD</sub>. As soon as the reference voltage is stable, the device begins full operation. For the best power-off pop performance, the amplifier should be set in shutdown mode prior to removing the power-supply voltage.

---

**Application Information** (cont.)

---

**PCB Layout Guidelines****Grounding**

It is recommended to use plain grounding or separate grounds. Do not use one-line connecting-power GND and analog GND. Noise currents in the output power stage must be returned to output noise ground and nowhere else. When these currents circulate elsewhere, the currents can get into the power supply, the signal ground, and so on, or even worse, the currents can form a loop and radiate noise. Any of these instances results in degraded-amplifier performance. The output-noise ground that the logical returns for the output noise currents associated with Class-D switching must tie to system ground at the power exclusively. Signal currents for the inputs' reference must be returned to quiet ground. This ground only ties to the signal components and the GND pin. GND then ties to system ground.

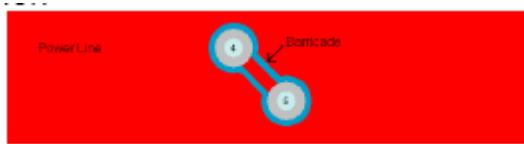

**Power Supply Line**

Similar to the ground,  $V_{DD}$  and  $PV_{DD}$  must be separately connected to the system power supply. It is recommended that all of the trace be routed as short and thick as possible. For the power-line layout, a water stream, or any barricade, placed in the trace can result in the bad performance of the amplifier (as shown in Figure 2).

**Figure 2. Power Line**

**Components Placement**

Decoupling capacitors—as previously described, the high-frequency,  $1\mu F$  decoupling capacitors should be placed as close to the power supply terminals ( $V_{DD}$  and  $PV_{DD}$ ) as possible. Large bulk power supply decoupling capacitors ( $10\mu F$  or greater) must be placed near the PAM8303C on the  $PV_{DD}$  terminal.

Input resistors and capacitors must be placed very close to input pins.

Output filter—the ferrite EMI filter must be placed as close to the output terminals as possible for the best EMI performance, and the capacitors used in the filters must be grounded to system ground.

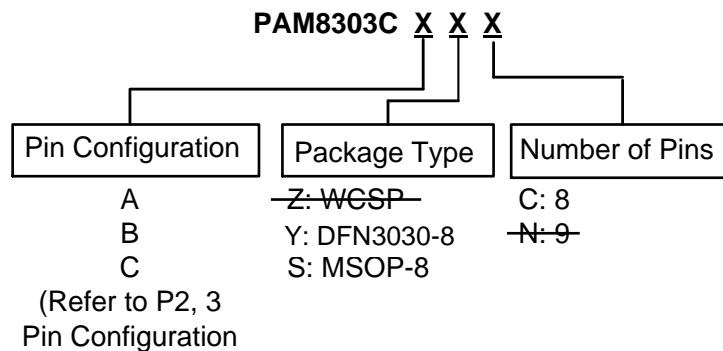

## Ordering Information

| Part Number | Package<br>(Note 8) | Part Marking    | Tape and Reel Quantity | Status<br>(Note 7) |

|-------------|---------------------|-----------------|------------------------|--------------------|

| PAM8303CBYC | DFN3030-8           | P8303C<br>XXXXW | 3000                   | In production      |

| PAM8303CBSC | MSOP-8              | P8303C<br>XXXXW | 2500                   | In production      |

Notes:

- 7. PAM8303CAZN (in package WCSP) is End of Life without any alternatives. PAM8303CCYC is End of Life, and the recommended alternative is PAM8303CBYC.

- 8. For packaging details, see <https://www.diodes.com/design/support/packaging/diodes-packaging/diodes-package-outlines-and-pad-layouts/>

## Marking Information

9 Ball WCSP (A) (EOL)

Top View

### Marking

BH

YW

BH: Product Code of PAM8303C

Y: Year

W: Week

## Marking Information (continued)

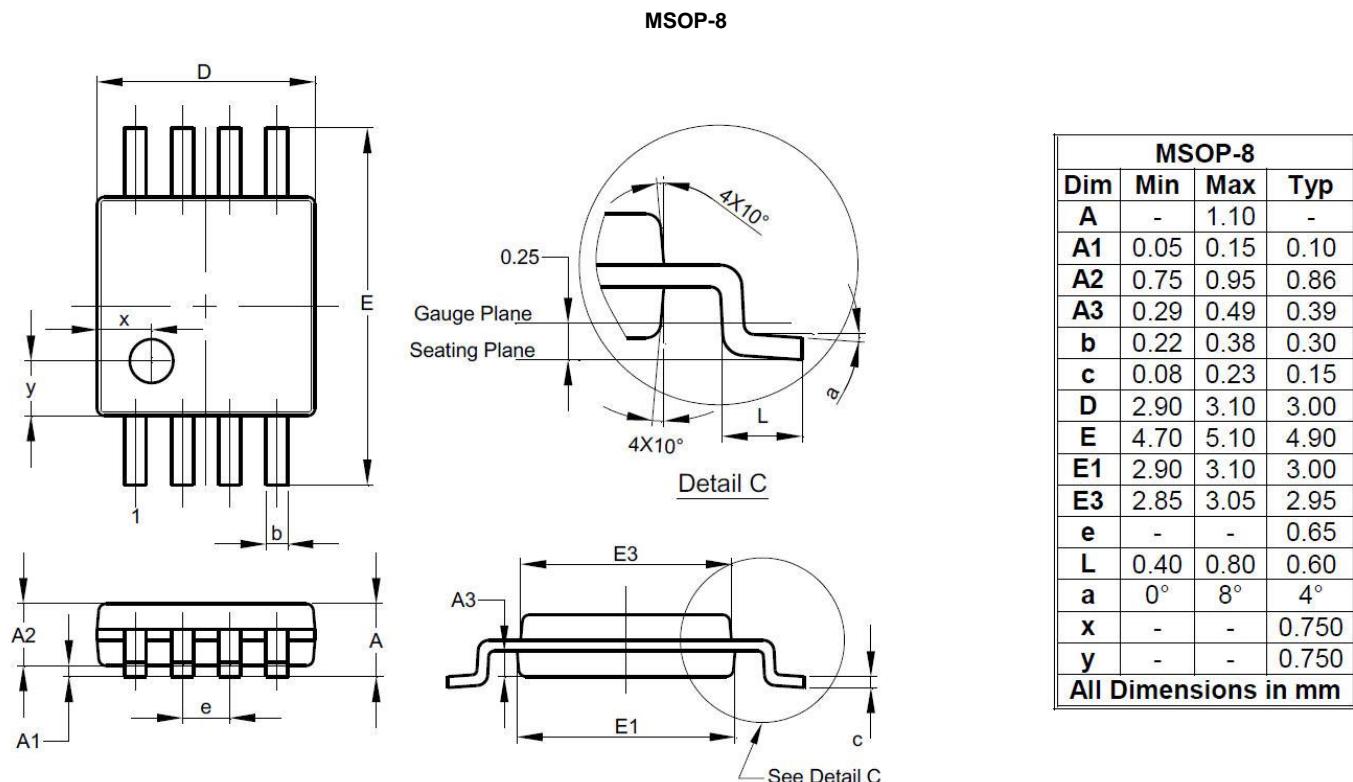

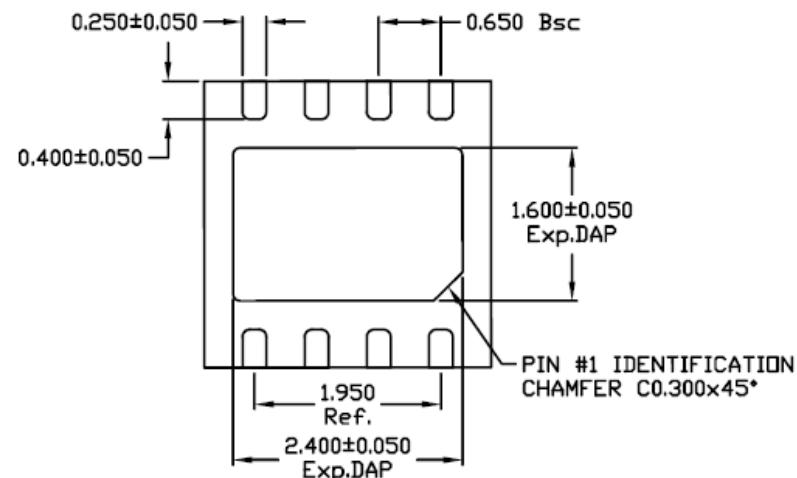

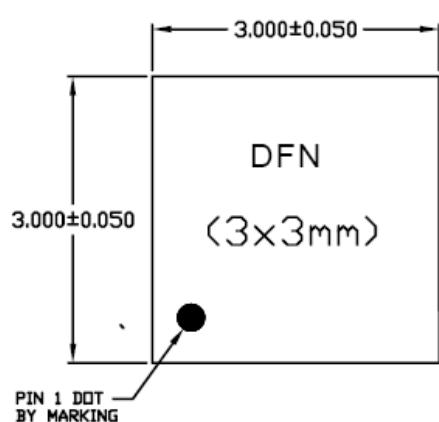

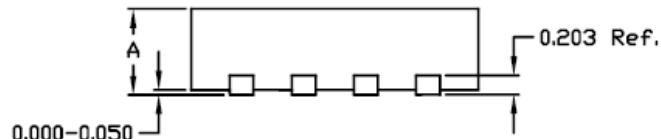

## Package Outline Dimensions (All dimensions in mm)

**Package Outline Dimensions** (All dimensions in mm) (continued)

**DFN3030-8**

|          |      |       |

|----------|------|-------|

| <b>A</b> | MAX. | 0.800 |

|          | NOM. | 0.750 |

|          | MIN. | 0.700 |

Unit: Millimeter

**IMPORTANT NOTICE**

DIODES INCORPORATED MAKES NO WARRANTY OF ANY KIND, EXPRESS OR IMPLIED, WITH REGARDS TO THIS DOCUMENT, INCLUDING, BUT NOT LIMITED TO, THE IMPLIED WARRANTIES OF MERCHANTABILITY AND FITNESS FOR A PARTICULAR PURPOSE (AND THEIR EQUIVALENTS UNDER THE LAWS OF ANY JURISDICTION).

Diodes Incorporated and its subsidiaries reserve the right to make modifications, enhancements, improvements, corrections or other changes without further notice to this document and any product described herein. Diodes Incorporated does not assume any liability arising out of the application or use of this document or any product described herein; neither does Diodes Incorporated convey any license under its patent or trademark rights, nor the rights of others. Any Customer or user of this document or products described herein in such applications shall assume all risks of such use and will agree to hold Diodes Incorporated and all the companies whose products are represented on Diodes Incorporated website, harmless against all damages.

Diodes Incorporated does not warrant or accept any liability whatsoever in respect of any products purchased through unauthorized sales channel. Should Customers purchase or use Diodes Incorporated products for any unintended or unauthorized application, Customers shall indemnify and hold Diodes Incorporated and its representatives harmless against all claims, damages, expenses, and attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized application.

Products described herein may be covered by one or more United States, international or foreign patents pending. Product names and markings noted herein may also be covered by one or more United States, international or foreign trademarks.

This document is written in English but may be translated into multiple languages for reference. Only the English version of this document is the final and determinative format released by Diodes Incorporated.

**LIFE SUPPORT**

Diodes Incorporated products are specifically not authorized for use as critical components in life support devices or systems without the express written approval of the Chief Executive Officer of Diodes Incorporated. As used herein:

A. Life support devices or systems are devices or systems which:

1. are intended to implant into the body, or

2. support or sustain life and whose failure to perform when properly used in accordance with instructions for use provided in the labeling can be reasonably expected to result in significant injury to the user.

B. A critical component is any component in a life support device or system whose failure to perform can be reasonably expected to cause the failure of the life support device or to affect its safety or effectiveness.

Customers represent that they have all necessary expertise in the safety and regulatory ramifications of their life support devices or systems, and acknowledge and agree that they are solely responsible for all legal, regulatory and safety-related requirements concerning their products and any use of Diodes Incorporated products in such safety-critical, life support devices or systems, notwithstanding any devices- or systems-related information or support that may be provided by Diodes Incorporated. Further, Customers must fully indemnify Diodes Incorporated and its representatives against any damages arising out of the use of Diodes Incorporated products in such safety-critical, life support devices or systems.

Copyright © 2018, Diodes Incorporated

[www.diodes.com](http://www.diodes.com)