8201, 8202, 8203, 8204

**Acceleration Processor**

**Data Sheet**

DS-0157-05 © April 16, 2012, Exar<sup>®</sup>, Inc. All rights reserved. 04/12

No part of this publication may be reproduced, transmitted, transcribed, stored in a retrieval system, or translated into any language in any form by any means without the written permission of Exar Corporation.

#### Licensing and Government Use

Any Exar software ("Licensed Programs") based on Hifn Technology described in this document is furnished under a license and may be used and copied only in accordance with the terms of such license and with the inclusion of this copyright notice. Distribution of this document or any copies thereof and the ability to transfer title or ownership of this document's contents are subject to the terms of such license.

Such Licensed Programs and their documentation may contain public open-source software that would be licensed under open-source licenses. Refer to the applicable product release notes for open-source licenses and proprietary notices. Use, duplication, disclosure, and acquisition by the U.S. Government of such Licensed Programs is subject to the terms and definitions of their applicable license.

#### **Disclaimer**

Exar reserves the right to make changes to its products, including the contents of this document, or to discontinue any product or service without notice. Exar advises its customers to obtain the latest version of relevant information to verify, before placing orders, that information being relied upon is current. Every effort has been made to keep the information in this document current and accurate as of the date of this document's publication or revision.

#### **Limited Warranty**

Exar warrants Products based on the Hifn Technology, including cards, against defects in materials and workmanship for a period of twelve (12) months from the delivery date. Exar's sole liability shall be limited to either, replacing, repairing or issuing credit, at its option, for the Product if it has been paid for. Exar will not be liable under this provision unless: (a) Exar is promptly notified in writing upon discovery of claimed defects by Buyer; (b) The claimed defective Product is returned to Exar, insurance and transportation charges prepaid, by Buyer; (c) The claimed defective Product is received within twelve (12) months from the delivery date; and (d) Exar's examination of the Product discloses to its satisfaction that the alleged defect was not caused by misuse, neglect, improper installation, repair, alteration, accident or other hazard. THIS WARRANTY DOES NOT COVER PRODUCT DAMAGE WHICH RESULTS FROM ACCIDENT, MISUSE, ABUSE, IMPROPER LINE VOLTAGE, FIRE, FLOOD, LIGHTNING OR OTHER ACTS OF GOD OR DAMAGE RESULTING FROM ANY MODIFICATIONS, REPAIRS OR ALTERATIONS PERFORMED OTHER THAN BY EXAR OR EXAR'S AUTHORIZED AGENT OR RESULTING FROM FAILURE TO STRICTLY COMPLY WITH EXAR'S WRITTEN OPERATING AND MAINTENANCE INSTRUCTIONS. BUYER ACKNOWLEDGES THAT THE PRODUCT ARE HIGHLY SENSITIVE ELECTRONIC PRODUCT REQUIRING SPECIAL HANDLING AND THAT THIS WARRANTY DOES NOT APPLY TO IMPROPERLY HANDLED PRODUCT. PRODUCT MANUFACTURED TO MEET BUYER'S SPECIFIC PERFORMANCE SPECIFICATIONS ACCEPTED BY EXAR ARE WARRANTED ONLY TO PERFORM IN CONFORMITY WITH SUCH SPECIFICATIONS, AND ARE WARRANTED ONLY AGAINST DEFECTS NOT RELATED TO SUCH SPECIFICATIONS IN ACCORDANCE WITH THE TERMS AND CONDITIONS SET FORTH HEREIN ABOVE.

#### **Life Support Policy**

Exar's Product are not authorized for use as critical components in life support devices or systems. Life support devices or systems are devices or systems which, (a) are intended for surgical implant into the body, or (b) support or sustain life, and whose failure to perform, when properly used in accordance with instructions for use provided in the labeling, can be reasonably expected to result in a significant injury or death to human life. A critical component is any component of a life support device or system whose failure to perform can be reasonably expected to cause the failure of the life support device or system, or to affect its safety or effectiveness. Buyer agrees to indemnify, defend and hold Exar harmless for any cost, loss, liability, or expense (including without limitation attorneys' fees and other costs of litigation or threatened litigation) arising out of violation of the above prohibition by Buyer or any person or entity receiving Exar's Product through Buyer. through Buyer.

#### **Patent Infringement - Indemnification**

Exar agrees, at its own expense, to defend Buyer from and against any claim, suit or proceeding, and to pay all judgments and costs finally awarded against Buyer by reason of claim, suit or proceeding insofar as it is based upon an allegation that the Product as furnished by Exar infringes any United States letter patent, provided that Exar is notified promptly of such claim in writing and is given authority and full and proper information and assistance (at Exar's expense) for defense of same. In case such Product are finally constituted an infringement and the use of Product is enjoined, Exar shall at its sole discretion and at its own expense: (1) procure for Buyer the right to continue using the Product; (2) replace or modify the same so that it becomes non-infringing; or (3) remove such Product and grant Buyer a credit for the depreciated value of the same

Buyer shall have the right to employ separate counsel in any claim, suit or proceeding and to participate in the defense thereof, but the fees and expenses of Buyer's counsel shall not be borne by Exar unless: (1) Exar specifically so agrees; or (2) Exar, after written request and without cause, does not assume such defense. Exar shall not be liable to indemnify Buyer for any settlement effected without Exar's written consent, unless Exar failed, after notice and without cause, to defend such claim, suit or proceeding.

The indemnification shall not apply and Buyer shall indemnify Exar and hold it harmless from all liability or expense (including costs of suit and attorney's fees) if the infringement arises from, or is based upon Exar's

compliance with particular requirements of Buyer or Buyer's customer that differ from Exar's standard specifications (Custom Product) for the Product, or modifications or alterations of the Product, or a combination of the Product with other items not furnished or manufactured by Exar.

Buyer agrees that Exar shall not be liable for any collateral, incidental or consequential damages arising out of patent infringement.

The foregoing states the entire liability of Exar for patent infringement.

#### Motorola

The use of this product in stateful compression protocols (for example, PPP or multi-history applications) with certain configurations may require a license from Motorola. In such cases, a license agreement for the right to use Motorola patents (US05,245,614, US05,130,993) may be obtained directly from Motorola.

#### **Patents**

May include one or more of the following United States patents: 4,930,142; 4,996,690; 4,701,745; 5,003,307; 5,016,009; 5,126,739; 5,146,221; 5,414,425; 5,414,850; 5,463,390; 5,506,580; 5,532,694; 6,320,846; 6,816,459; 6,651,099; 6,665,725; 6,771,646; 6,789,116; 6,954,789; 6,839,751; 7,299,282; 7,260,558. Other patents pending.

#### **Trademarks**

$Hi/fn^{\&}$ ,  $MeterFlow^{\&}$ ,  $MeterWorks^{\&}$ , and  $LZS^{\&}$ , are registered trademarks of Exar Corporation.  $Hifn^{TM}$ ,  $Hifn^{TM}$

IBM, IBM Logo, and IBM PowerPC are trademarks of International Business Machines Corporation in the United States, or other countries.

Microsoft, Windows, Windows XP, Windows Vista, Windows Server 2003, Windows Server 2008 and the Windows logo are trademarks of Microsoft Corporation in the United States, and/or other countries.

Intel QuickAssist is a trademark of Intel Corporation in the United States and in other countries.

#### **Exporting**

This product may only be exported from the United States in accordance with applicable Export Administration Regulations. Diversion contrary to United States laws is prohibited.

#### **Exar Confidential**

If you have signed a Exar Confidential Disclosure Agreement that includes this document as part of its subject matter, please use this document in accordance with the terms of the agreement. If not, please destroy the document.

# **Table of Contents**

| Li | st of I | Figures  | ·       |       | • •   |      |            |     |      | • • |      | •   |     |      | •   | ٠.   |      |     | •   |     | <br>• | <br>• |  | <br>14   |

|----|---------|----------|---------|-------|-------|------|------------|-----|------|-----|------|-----|-----|------|-----|------|------|-----|-----|-----|-------|-------|--|----------|

| Li | st of   | Tables   |         |       |       |      |            |     |      |     |      |     |     |      |     |      |      |     |     |     |       |       |  | <br>17   |

| Pı | reface  | <b></b>  |         |       |       |      |            |     |      |     |      |     |     |      |     |      |      |     |     |     |       |       |  | <br>19   |

| G  | lossa   | ry       |         |       |       |      |            |     |      |     |      |     |     |      |     |      |      |     |     |     |       |       |  | <br>21   |

| 1  | Prod    | luct De  | scri    | pti   | on    |      |            |     |      |     |      |     |     |      |     |      |      |     |     |     |       |       |  | <br>23   |

|    | 1.1     | Features | S       |       |       |      |            |     |      |     |      |     |     |      |     |      |      |     |     |     |       |       |  | <br>23   |

|    |         | 1.1.1    | Hig     | h P   | erfo  | rma  | ano        | ce. |      |     |      |     |     |      |     |      |      |     |     |     |       |       |  | <br>23   |

|    |         | 1.1.2    | Flex    | xibl  | e De  | sig  | n f        | for | Pa   | cke | et I | Pro | ce  | essi | ing |      |      |     |     |     |       | <br>  |  | <br>24   |

|    |         | 1.1.3    | Eng     | jine  | Fea   | tur  | es         |     |      |     |      |     |     |      |     |      |      |     |     |     |       |       |  | <br>24   |

|    |         | 1.1.4    | Con     | nm    | and   | and  | <b>d</b> C | Dat | a E  | nd  | iar  | n C | or  | ıve  | rsi | on   | Μ    | od  | es  |     |       |       |  | <br>25   |

|    |         | 1.1.5    | DM      | A F   | eatu  | res  |            |     |      |     |      |     |     |      |     |      |      |     |     |     |       |       |  | <br>25   |

|    |         | 1.1.6    | Dat     | a I   | nteg  | rity | F          | eat | ure  | es  |      |     |     |      |     |      |      |     |     |     |       |       |  | <br>25   |

|    |         | 1.1.7    | Oth     | er i  | featı | ure  | s.         |     |      |     |      |     |     |      |     |      |      |     |     |     |       |       |  | <br>25   |

|    | 1.2     | NIST Ce  | ertific | ate   | s     |      |            |     |      |     |      |     |     |      |     |      |      |     |     |     |       |       |  | <br>26   |

|    | 1.3     | Ordering | g Info  | orm   | atio  | n.   |            |     |      |     |      |     |     |      |     |      |      |     |     |     |       | <br>  |  | <br>26   |

| 2  | Oper    | ration . |         |       |       |      |            |     |      |     |      |     |     |      |     |      |      |     |     |     |       |       |  | <br>27   |

|    | 2.1     | Data Int | tegrit  | ty.   |       |      |            |     |      |     |      |     |     |      |     |      |      |     |     |     |       |       |  | <br>30   |

|    |         | 2.1.1    |         |       | Pari  |      |            |     |      |     |      |     |     |      |     |      |      |     |     |     |       |       |  |          |

|    |         | 2.1.2    | CRO     | C Pr  | oted  | ctio | n.         |     |      |     |      |     |     |      |     |      |      |     |     |     |       |       |  | <br>30   |

|    |         | 2.1.3    | Rea     | al Ti | ime   | Ver  | ific       | cat | ion  |     |      |     |     |      |     |      |      |     |     |     |       |       |  | <br>30   |

|    |         | 2.1.     | 3.1     | Сс    | mpr   | ess  | io         | n E | ng   | ine | R    | ea  | ΙT  | im   | e ۱ | /er  | ific | cat | ior | n . |       |       |  | <br>. 31 |

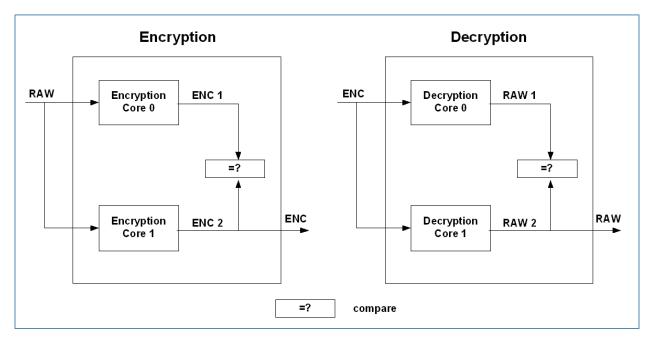

|    |         | 2.1.     | 3.2     | En    | cryp  | tio  | n E        | Eng | jine | e R | ea   | ΙT  | im  | e١   | /er | rifi | cat  | io  | n.  |     |       |       |  | <br>. 33 |

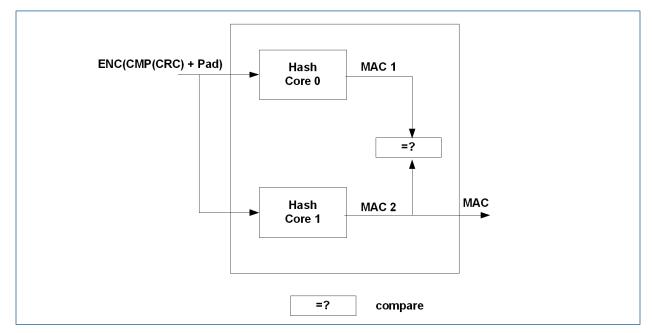

|    |         | 2.1.     | 3.3     | На    | sh E  | ng   | ine        | e R | eal  | Ti  | me   | e V | er  | ific | ati | on   | ٠    |     |     |     |       |       |  | <br>. 34 |

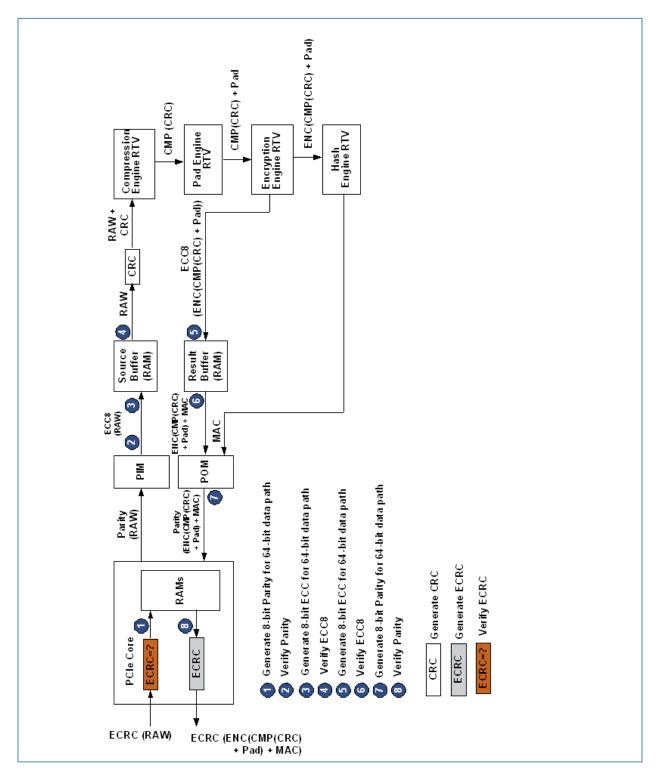

|    |         | 2.1.4    | Dat     | a I   | nteg  | rity | M          | lod | el f | for | Er   | nco | de  | O    | ре  | rat  | tioi | าร  |     |     |       |       |  | <br>35   |

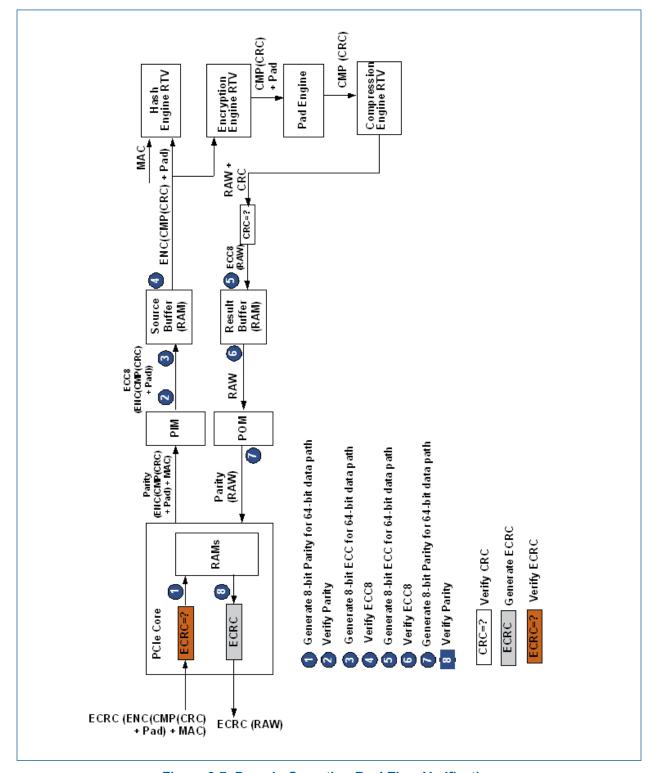

|    |         | 2.1.5    | Dat     | a I   | nteg  | rity | M          | lod | el f | for | De   | ecc | ode | e O  | ре  | ra   | tio  | ns  |     |     |       |       |  | <br>37   |

|   | 2.2  | Clock Domains                                                                 |

|---|------|-------------------------------------------------------------------------------|

|   | 2.3  | Clock Gating                                                                  |

| 3 | Data | Structures 41                                                                 |

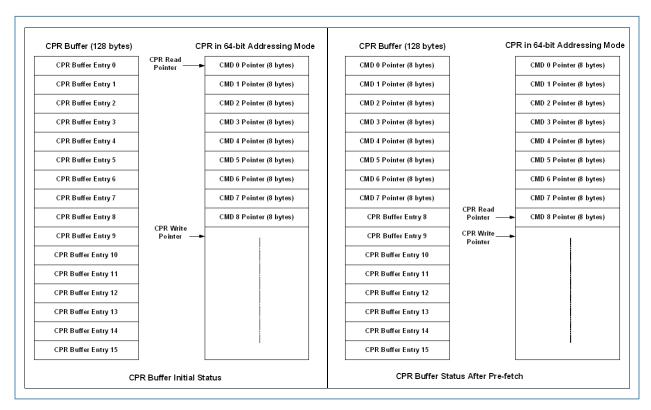

|   | 3.1  | Command Pointer Ring41                                                        |

|   |      | 3.1.1 Command Structure                                                       |

|   |      | 3.1.2 Command Descriptor Format                                               |

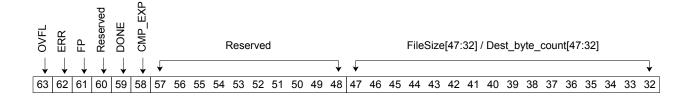

|   |      | 3.1.2.1 Desc_result                                                           |

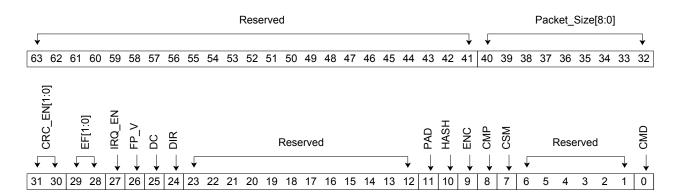

|   |      | 3.1.2.2 Desc_cmd_base                                                         |

|   |      | 3.1.2.3 Desc_cmd_cmp                                                          |

|   |      | 3.1.2.4 Desc_cmd_enc                                                          |

|   |      | 3.1.2.5 Desc_cmd_hash                                                         |

|   |      | 3.1.2.6 Desc_cmd_pad 63                                                       |

|   |      | 3.1.2.7 Desc_srcX and Desc_dstX                                               |

|   |      | 3.1.3 Command Structure Conventions                                           |

|   |      | 3.1.3.1 Initial Hash engine Value (IHV)                                       |

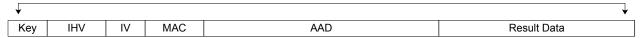

|   |      | 3.1.3.2 MAC                                                                   |

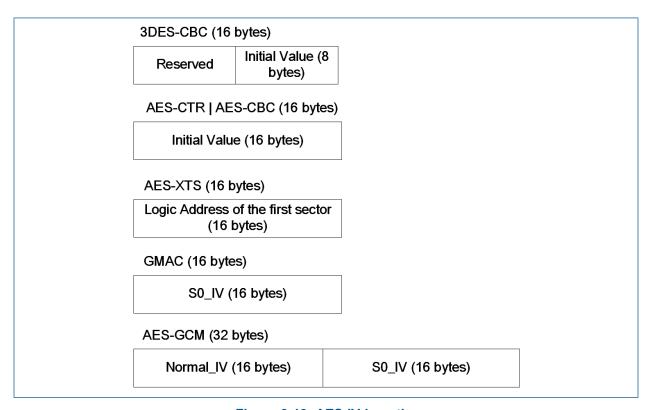

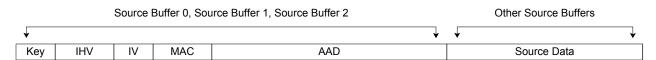

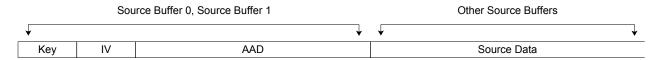

|   |      | 3.1.3.3 Initialization Vector (IV) and Additional Authenticated Data (AAD) 77 |

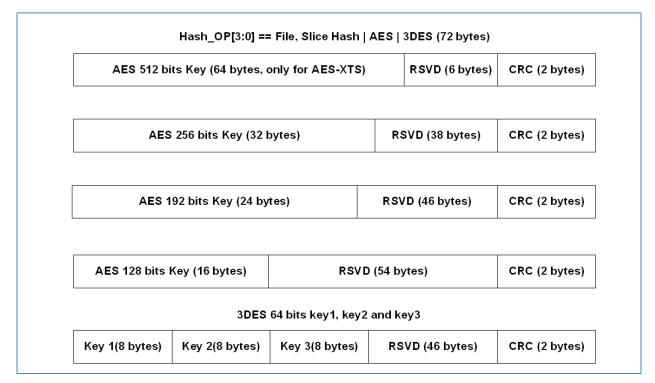

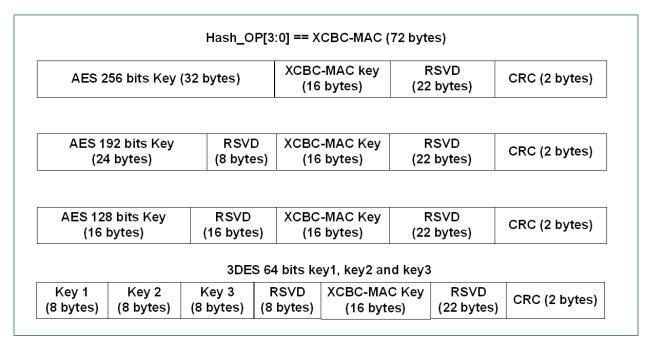

|   |      | 3.1.3.4 Key Format                                                            |

|   |      | 3.1.3.5 Data Stream Information Fields 82                                     |

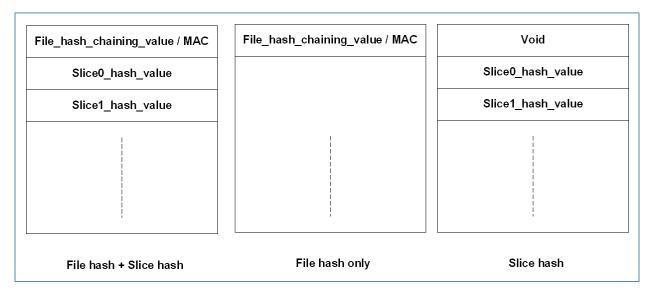

|   |      | 3.1.3.6 Hash Buffer                                                           |

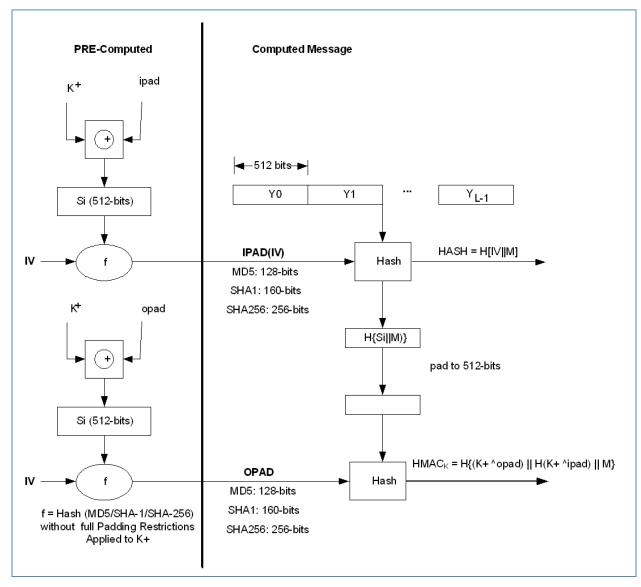

|   |      | 3.1.3.7 IPAD & OPAD for HMAC & SSL3.0-MAC (SHA256   MD5) 85                   |

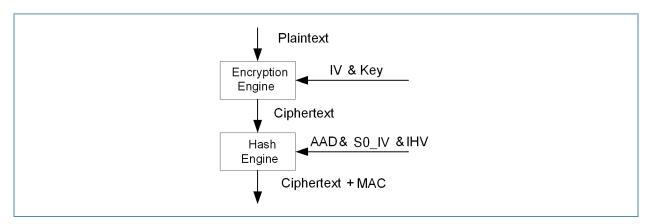

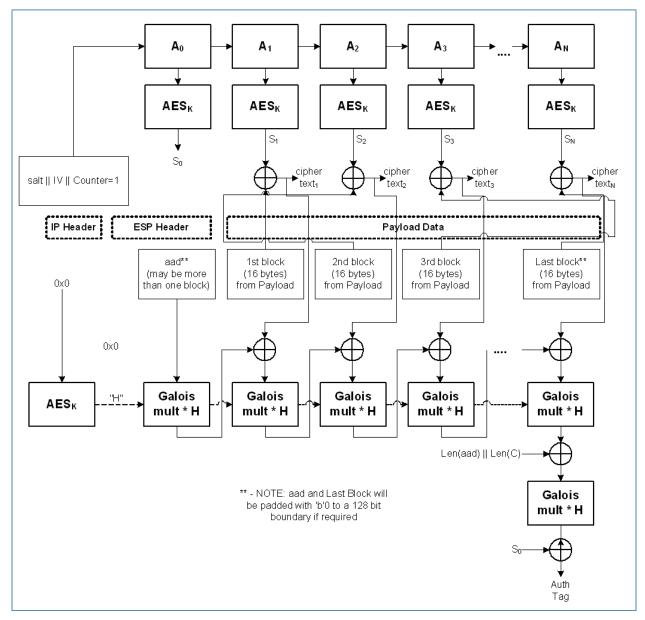

|   |      | 3.1.3.8 AES-GCM and GMAC Operations 86                                        |

|   |      | 3.1.3.9 MAC Operations                                                        |

|   |      | 3.1.3.10 IPsec Packet Processing                                              |

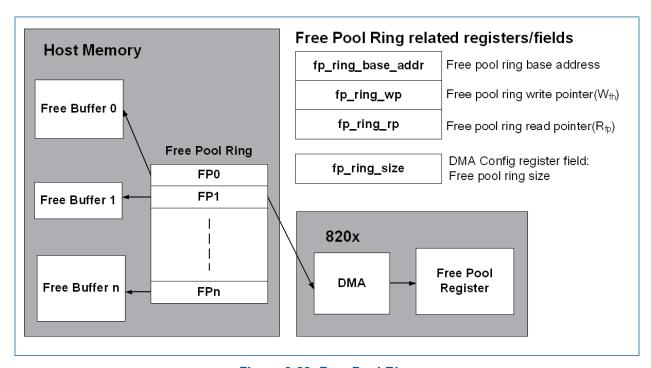

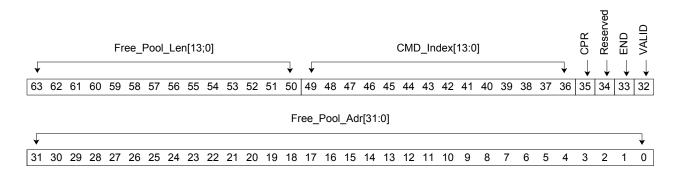

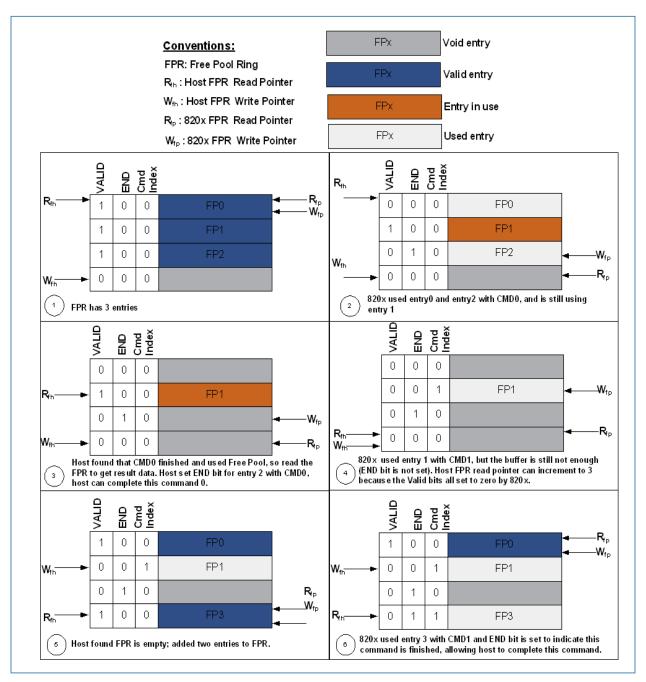

|   |      | 3.1.4 Free Pool Ring                                                          |

|   | 3.2  | Result Ring                                                                   |

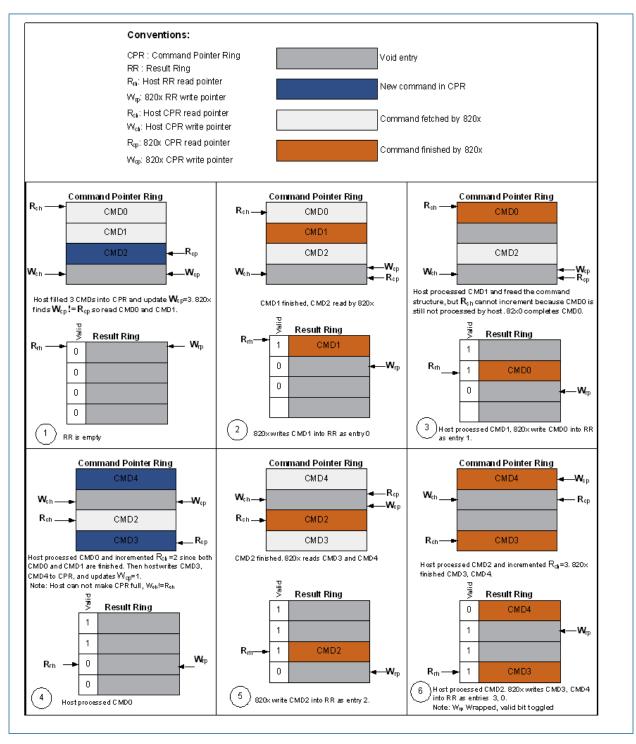

|   | 3.3  | Command Operation Sequence                                                    |

| 4 | Data | Flow                                                                          |

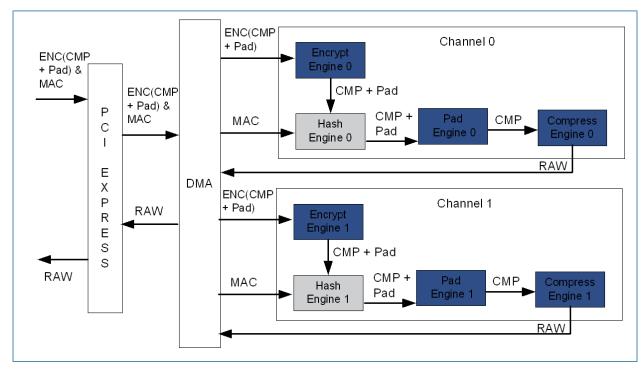

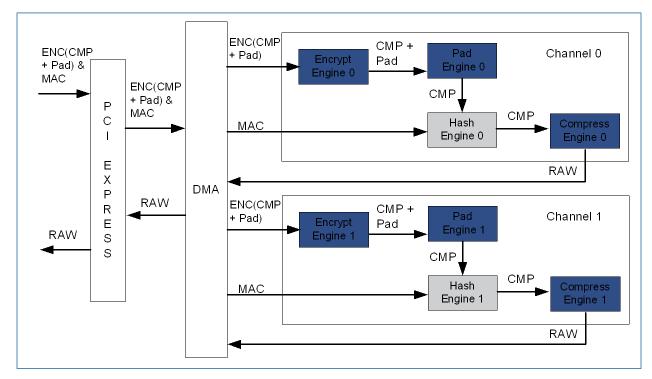

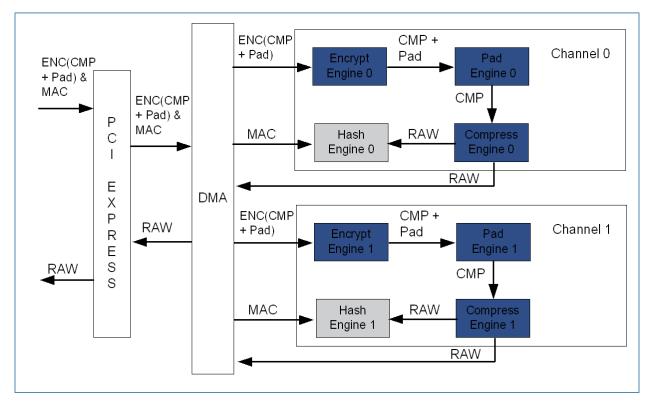

|   | 4.1  | Encode Operations Data Flow                                                   |

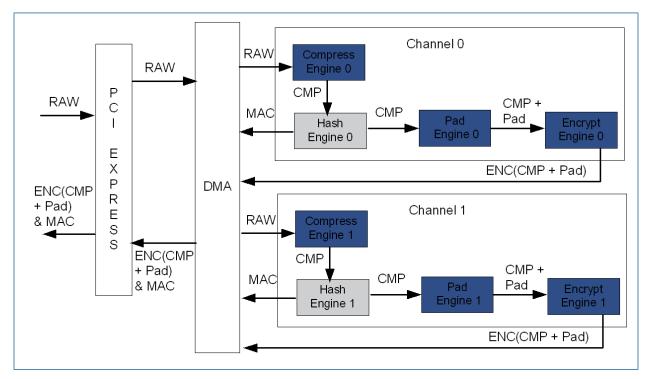

|   | 1.4  | 4.1.1 Hash Engine before Compression Engine                                   |

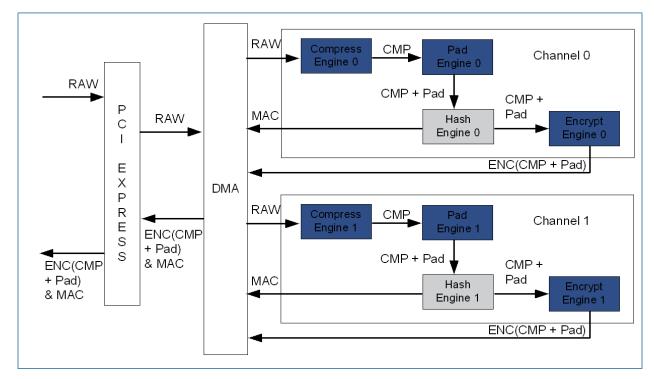

|   |      | 4.1.2 Hash Engine after Compression Engine                                    |

|   |      | 4.1.3 Hash Engine after Pad Engine                                            |

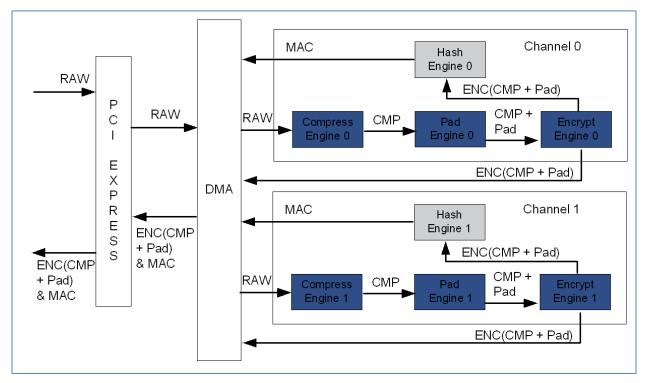

|   |      | 4.1.5 Hash Engine arter rad Engine                                            |

|   |     | 4.1.4    | Hash Engine after Encryption Engine      | 106   |

|---|-----|----------|------------------------------------------|-------|

|   | 4.2 | Decode   | Operations Data Flow                     | . 107 |

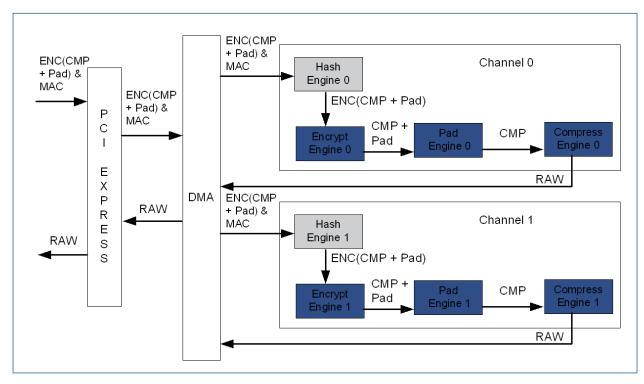

|   |     | 4.2.1    | Hash Engine before Encryption Engine     | 107   |

|   |     | 4.2.2    | Hash Engine after Encryption Engine      | 108   |

|   |     | 4.2.3    | Hash Engine after Pad Engine             | 109   |

|   |     | 4.2.4    | Hash Engine after Compression Engine     | 110   |

| 5 | Mod | ules     |                                          | 112   |

|   | 5.1 | DMA      |                                          | 112   |

|   | 5.1 | 5.1.1    | PCIe Outbound Manager                    | 112   |

|   |     | 5.1.2    | PCIe Inbound Manager                     | 112   |

|   |     | 5.1.3    | Command Pointer Ring Prefetch            | 112   |

|   |     | 5.1.4    | Read Request Controller                  | 113   |

|   |     | 5.1.5    | Write Request Controller                 | 114   |

|   |     | 5.1.6    | Completion Controller                    | 114   |

|   |     |          |                                          |       |

|   | 5.2 | Configur | ration Registers                         | . 114 |

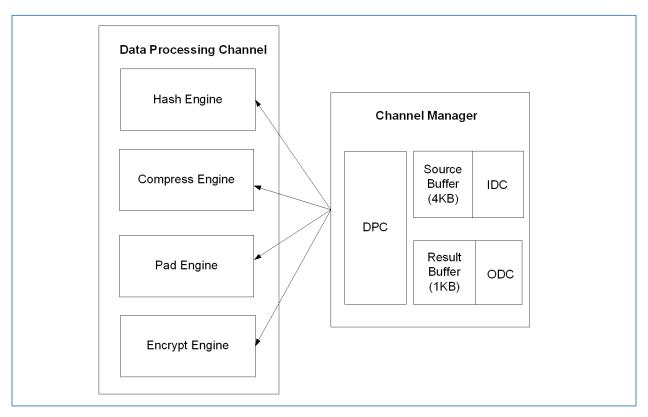

|   | 5.3 | Channel  | Manager                                  | . 115 |

|   |     | 5.3.1    | Channel Manager Inbound Data Controller  | 115   |

|   |     | 5.3.2    | Channel Manager Source Buffer            | 116   |

|   |     | 5.3.3    | Channel Manager Outbound Data Controller | 116   |

|   |     | 5.3.4    | Channel Manager Result Buffer            | 117   |

|   |     | 5.3.5    | Channel Manager Data Process Controller  | 117   |

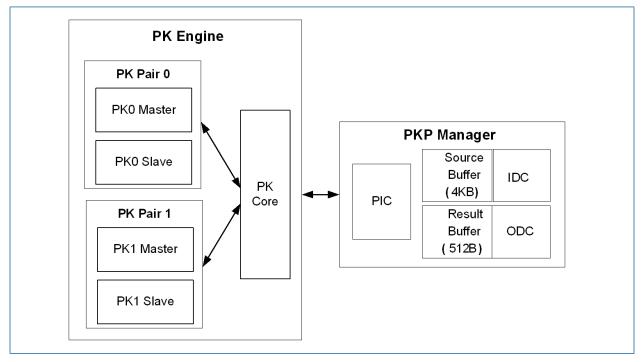

|   | 5.4 | PKP Mar  | nager                                    | . 117 |

|   |     | 5.4.1    | PKP Inbound Data Controller              | 118   |

|   |     | 5.4.2    | PKP Source Buffer                        | 118   |

|   |     | 5.4.3    | PKP Outbound Data Controller             | 118   |

|   |     | 5.4.4    | PKP Result Buffer                        | 119   |

|   |     | 5.4.5    | PKP Interface Controller                 | 119   |

|   |     | 5.4.6    | PKP Core                                 | 119   |

|   | 5.5 | RNG Eng  | gine                                     | . 119 |

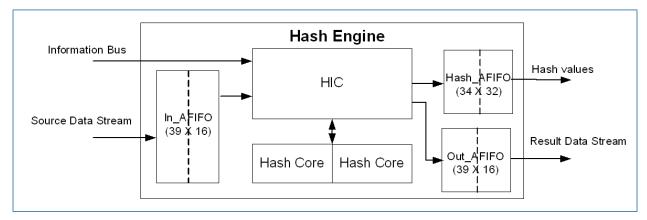

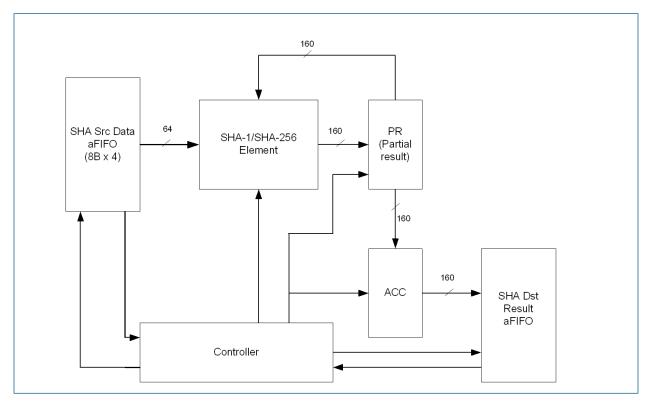

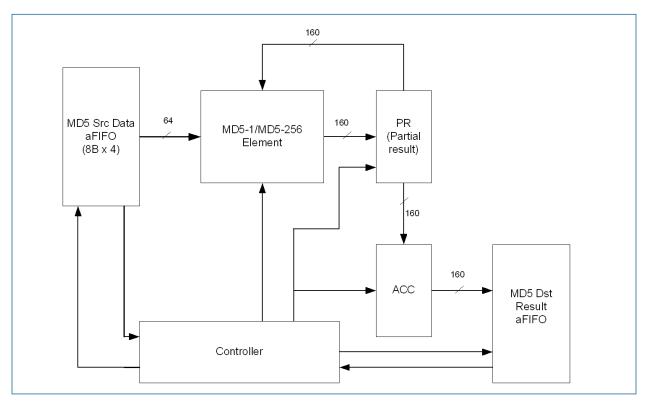

|   | 5.6 | Hash En  | gine                                     | . 119 |

|   |     | 5.6.1    | Hash In_AFIFO & Out_AFIFO                | 120   |

|   |     | 5.6.2    | Hash_AFIFO                               | 120   |

|   |     | 5.6.3    | Hash Interface Controller                | 120   |

|   |      | 5.6.4     | Hash Core                                     | 121   |

|---|------|-----------|-----------------------------------------------|-------|

|   |      | 5.6.      | •                                             |       |

|   |      | 5.6.      | 4.2 Hash Core Algorithms                      | . 124 |

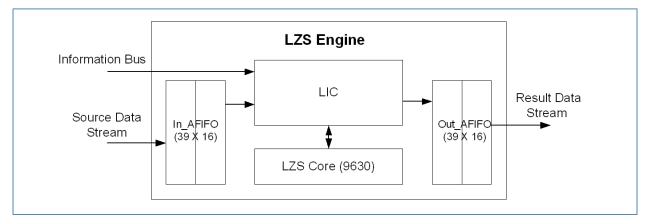

|   | 5.7  | LZS Eng   | jine                                          | . 126 |

|   |      | 5.7.1     | LZS In_AFIFO & Out_AFIFO                      | 127   |

|   |      | 5.7.2     | LZS Core Interface Controller                 | 127   |

|   |      | 5.7.3     | LZS Core                                      | 127   |

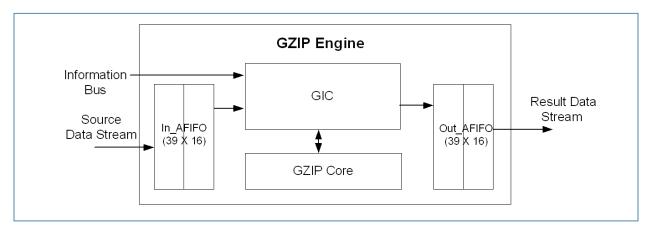

|   | 5.8  | GZIP En   | gine                                          | . 128 |

|   |      | 5.8.1     | GZIP In_AFIFO & Out_AFIFO                     | 128   |

|   |      | 5.8.2     | GZIP Core Interface Controller                | 128   |

|   |      | 5.8.3     | GZIP Core                                     | 129   |

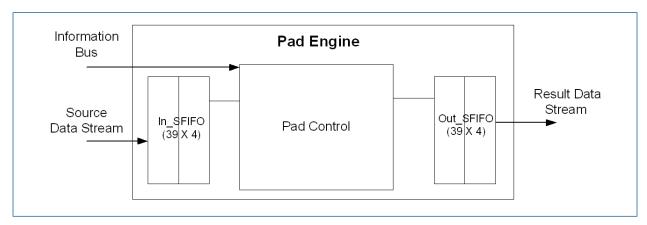

|   | 5.9  | Pad Eng   | ine                                           | 129   |

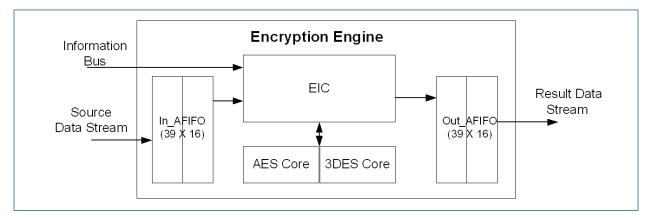

|   | 5.10 | Encrypti  | ion Engine                                    | . 129 |

|   |      | 5.10.1    | Encryption In_AFIFO & Out_AFIFO               | 130   |

|   |      | 5.10.2    | Encryption Interface Controller               | 130   |

|   |      | 5.10.3    | Encryption AES and 3DES Cores                 | 130   |

|   | 5.11 | Clock ar  | nd Reset Generator                            | 131   |

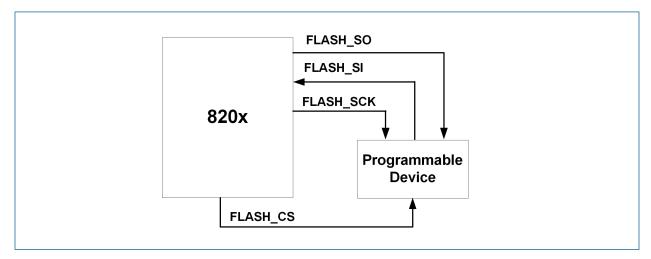

|   | 5.12 | Serial Pe | eripheral Interface                           | . 131 |

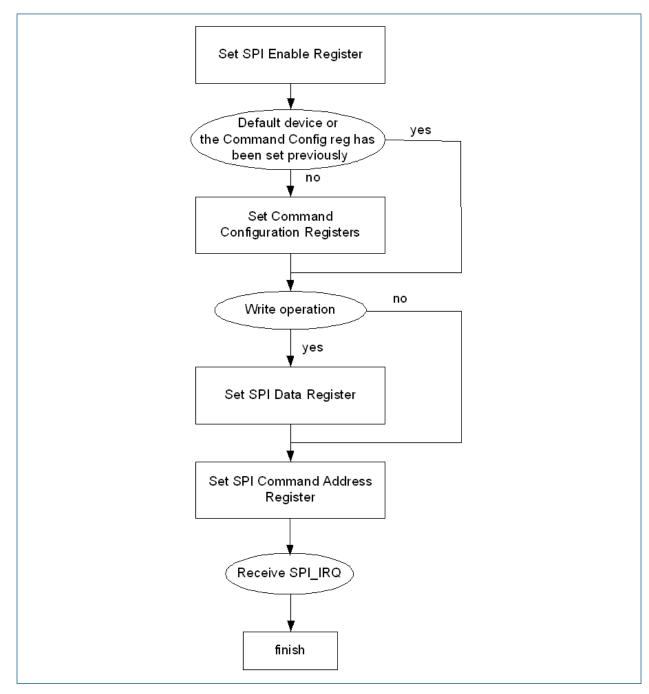

|   |      | 5.12.1    | SPI Register Operation Flow                   | 135   |

|   | 5.13 | Tempera   | ature Sensor Controller                       | 138   |

| 6 | Regi | ster De   | efinition                                     | 141   |

|   | 6.1  |           | ration Registers                              | 142   |

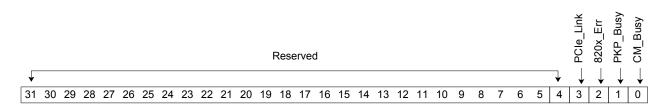

|   | 0.1  | 6.1.1     | Status Register                               | 142   |

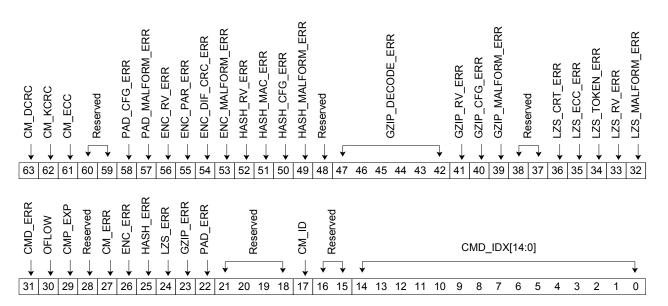

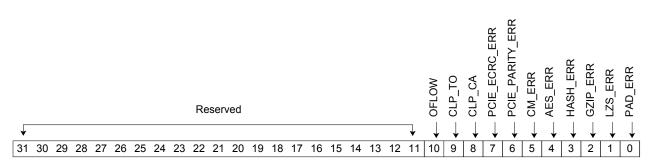

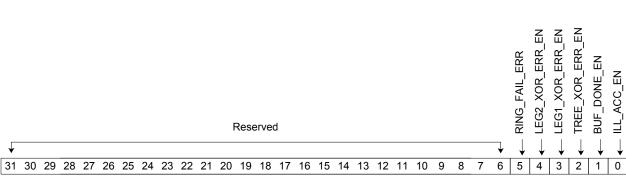

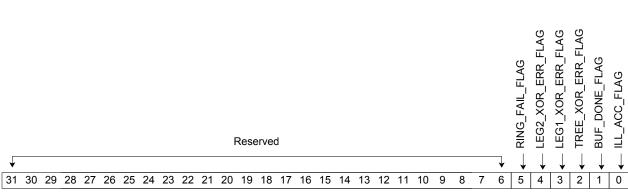

|   |      | 6.1.2     | 820x Error Register                           | 143   |

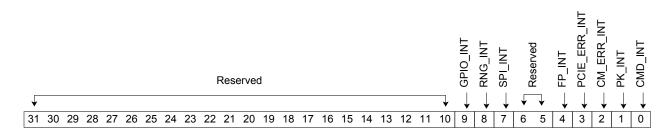

|   |      | 6.1.3     | 820x Interrupt Status Register                | 145   |

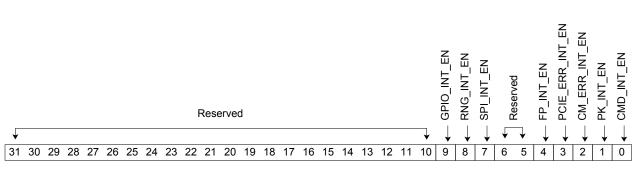

|   |      | 6.1.4     | 820x Interrupt Enable Register                | 147   |

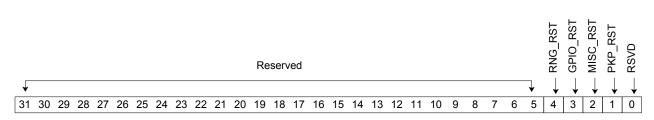

|   |      | 6.1.5     | Soft Reset Register                           | 149   |

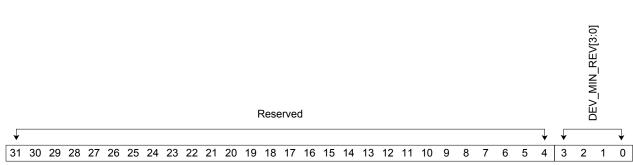

|   |      | 6.1.6     | Device Minor Revision Register                | 150   |

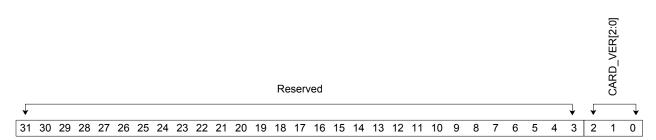

|   |      | 6.1.7     | Card Version Register                         | 151   |

|   | 6.2  | DMA Co    | ntrol Registers                               | . 152 |

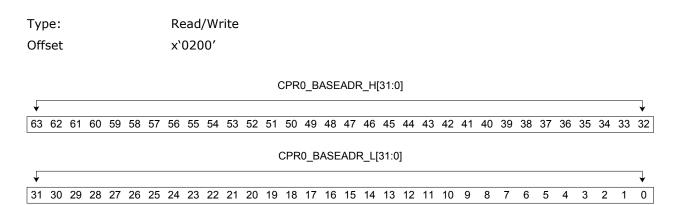

|   |      | 6.2.1     | Command Pointer Ring 0 Base Address Register  | 152   |

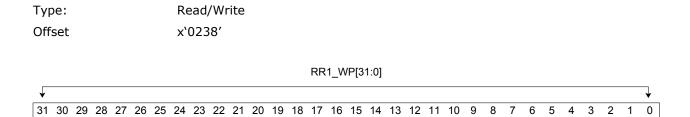

|   |      | 6.2.2     | Command Pointer Ring 0 Write Pointer Register | 153   |

|     | 6.2.3    | Command Pointer Ring 0 Read Pointer Register         |

|-----|----------|------------------------------------------------------|

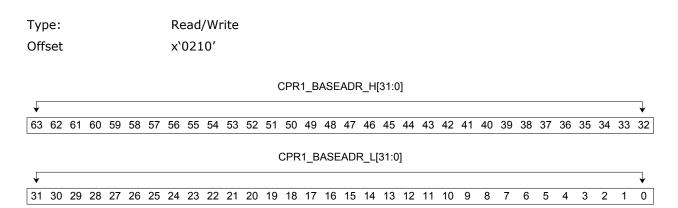

|     | 6.2.4    | Command Pointer Ring 1 Base Address Register 154     |

|     | 6.2.5    | Command Pointer Ring 1 Write Pointer Register        |

|     | 6.2.6    | Command Pointer Ring 1 Read Pointer Register         |

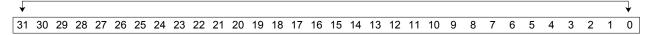

|     | 6.2.7    | Result Ring 0 Base Address Register                  |

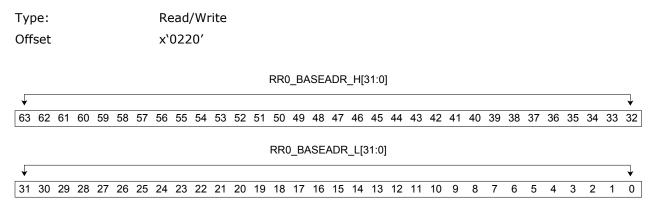

|     | 6.2.8    | Result Ring 0 Write Pointer Register                 |

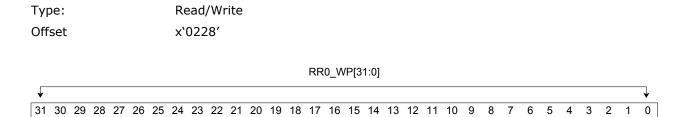

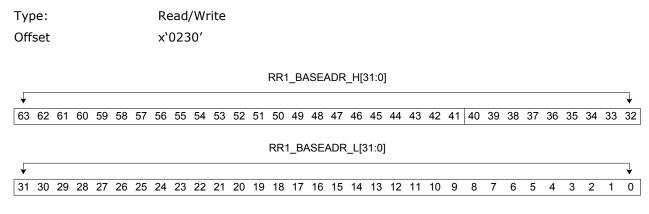

|     | 6.2.9    | Result Ring 1 Base Address Register                  |

|     | 6.2.10   | Result Ring 1 Write Pointer Register                 |

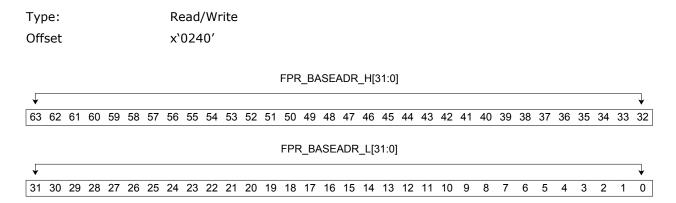

|     | 6.2.11   | Free Pool Ring Base Address Register                 |

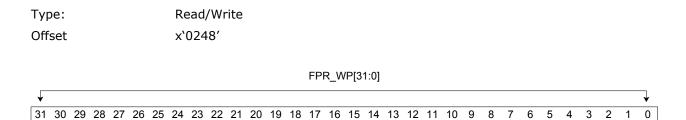

|     | 6.2.12   | Free Pool Write Pointer Register                     |

|     | 6.2.13   | Free Pool Read Pointer Register                      |

|     | 6.2.14   | DMA Configuration Register                           |

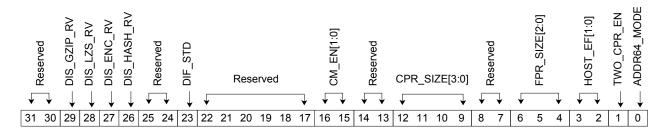

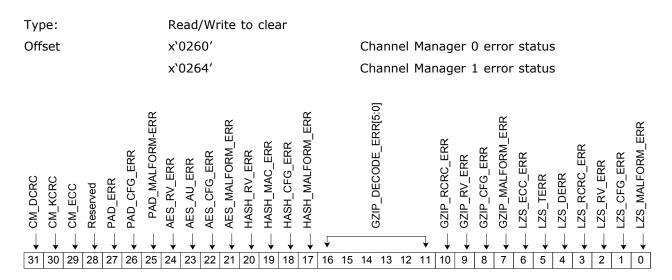

|     | 6.2.15   | Channel Manager 0-1 Error Status Register            |

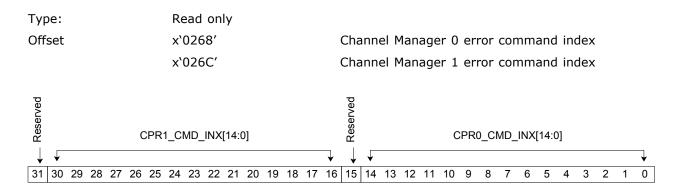

|     | 6.2.16   | Channel Manager 0-1 Error Command Index Register 167 |

| 6.3 | Engine ( | Configuration Registers                              |

|     | 6.3.1    | Hash Engine Mute Table Entry Registers               |

| 6.4 | Public K | ey Processor Control Registers                       |

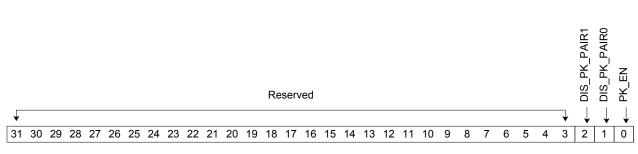

|     | 6.4.1    | Public Key Enable Register                           |

|     | 6.4.2    | Public Key Command Entry Registers                   |

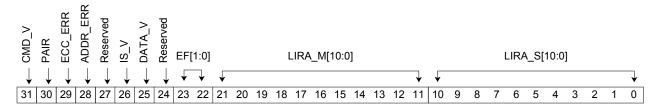

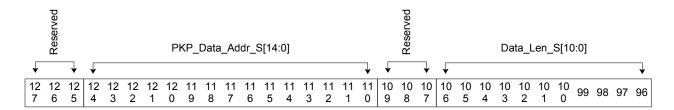

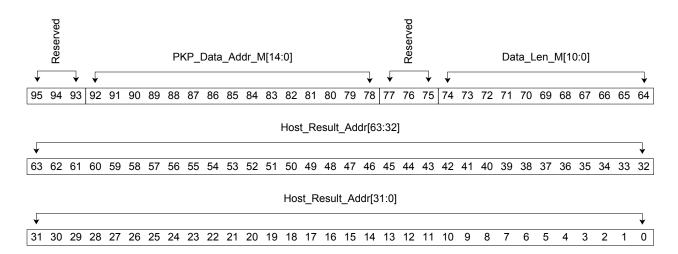

|     | 6.4.     | 2.1 Public Key Command Register Format               |

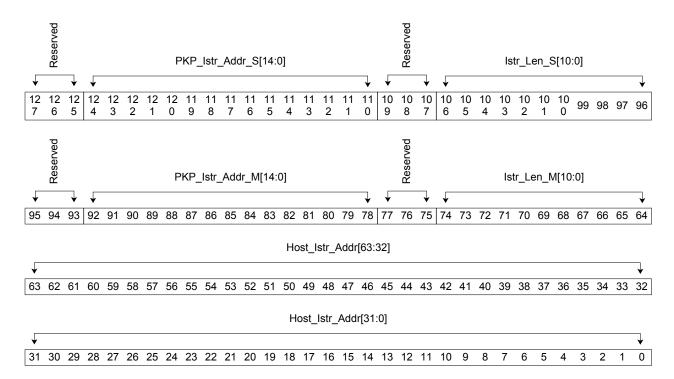

|     | 6.4.     | 2.2 Public Key Instruction Register Format           |

|     | 6.4.     | 2.3 Public Key Data Register Format                  |

|     | 6.4.     | 2.4 Public Key Result Register                       |

|     | 6.4.3    | Public Key Internal Registers                        |

| 6.5 | RNG Co   | ntrol Registers                                      |

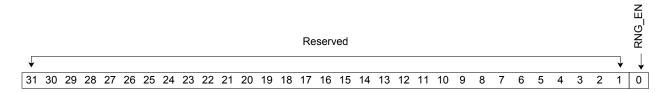

|     | 6.5.1    | RNG Enable Register                                  |

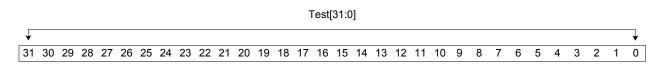

|     | 6.5.2    | RNG Test Register                                    |

|     | 6.5.3    | RNG Interrupt Enable Register                        |

|     | 6.5.4    | RNG Interrupt Control/Status Register                |

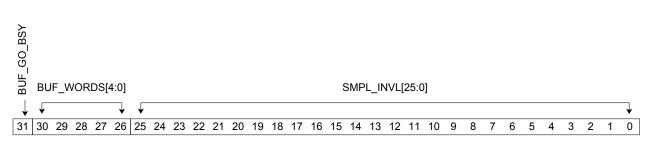

|     | 6.5.5    | RNG Buffer Control/Status Register                   |

|     | 6.5.6    | RNG Buffer Data Register                             |

|     | 6.5.7    | RNG Configuration Register                           |

| 6.6 | GPIO Re  | egisters                                             |

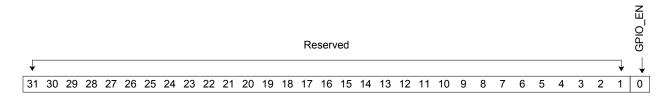

|     | 6.6.1    | GPIO Enable Register                                 |

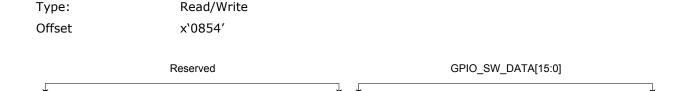

|     | 6.6.2    | GPIO Software Data Register                          |

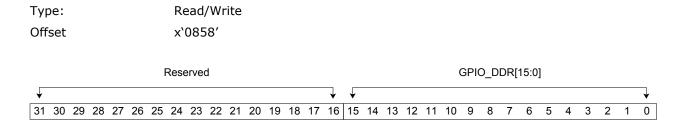

|   |      | 6.6.3     | GPIO Data Direction Register         | 190 |

|---|------|-----------|--------------------------------------|-----|

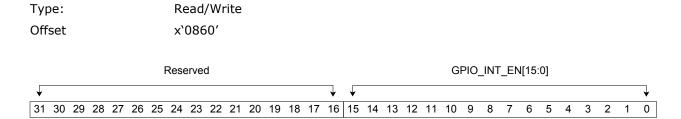

|   |      | 6.6.4     | GPIO Interrupt Enable Register       | 191 |

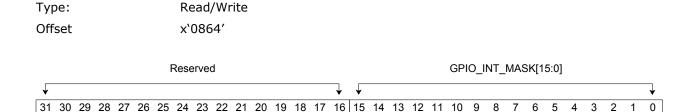

|   |      | 6.6.5     | GPIO Interrupt Mask Register         | 192 |

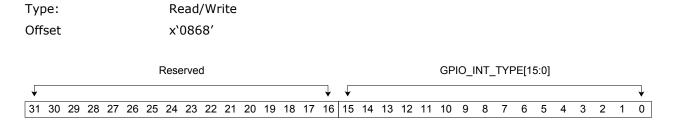

|   |      | 6.6.6     | GPIO Interrupt Type Register         | 192 |

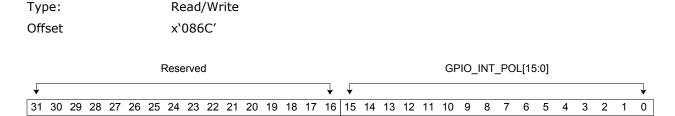

|   |      | 6.6.7     | GPIO Interrupt Polarity Register     | 193 |

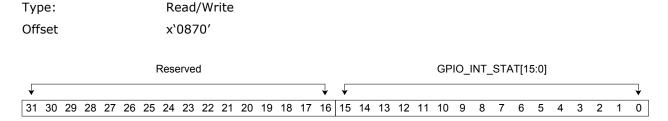

|   |      | 6.6.8     | GPIO Interrupt Status Register       | 193 |

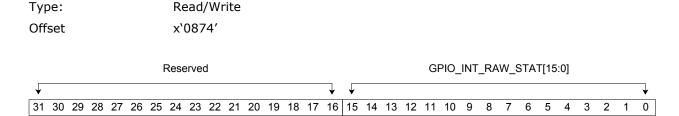

|   |      | 6.6.9     | GPIO Interrupt Raw Status Register   | 194 |

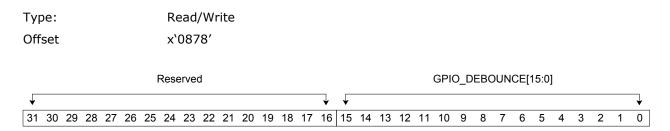

|   |      | 6.6.10    | GPIO De-Bounce Register              | 194 |

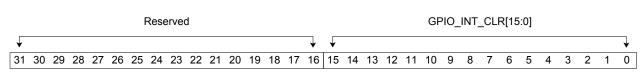

|   |      | 6.6.11    | GPIO Interrupt Clear Register        | 195 |

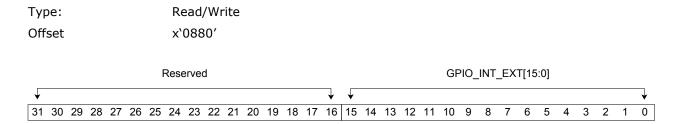

|   |      | 6.6.12    | GPIO Interrupt Ext Register          | 195 |

|   |      | 6.6.13    | GPIO Interrupt Sync Register         | 196 |

|   | 6.7  | Serial Pe | eripheral Interface Registers        | 197 |

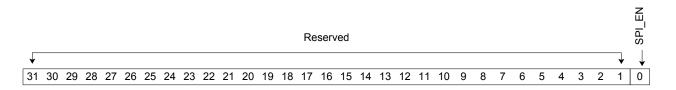

|   |      | 6.7.1     | SPI Enable Register                  | 197 |

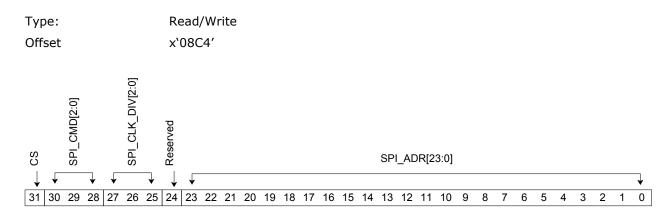

|   |      | 6.7.2     | SPI Command Address Register         | 198 |

|   |      | 6.7.3     | SPI Data Register                    | 199 |

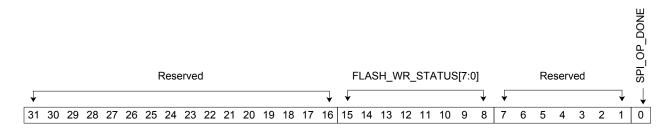

|   |      | 6.7.4     | SPI Status Register                  | 200 |

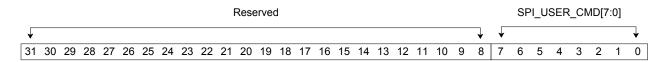

|   |      | 6.7.5     | SPI User Defined Register            | 201 |

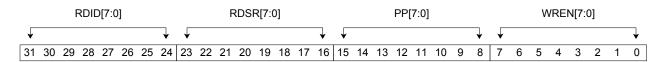

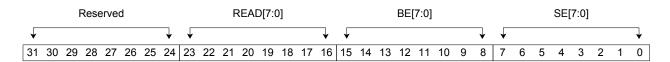

|   |      | 6.7.6     | SPI Command Configuration 0 Register | 202 |

|   |      | 6.7.7     | SPI Command Configuration 1 Register | 203 |

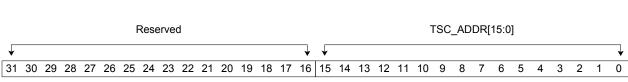

|   | 6.8  | Tempera   | ature Sensor Controller Registers    | 204 |

|   |      | 6.8.1     | TSC Address Register                 | 204 |

|   |      | 6.8.2     | TSC Data Register                    | 205 |

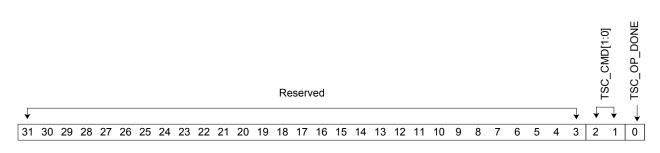

|   |      | 6.8.3     | TSC Command Register                 | 206 |

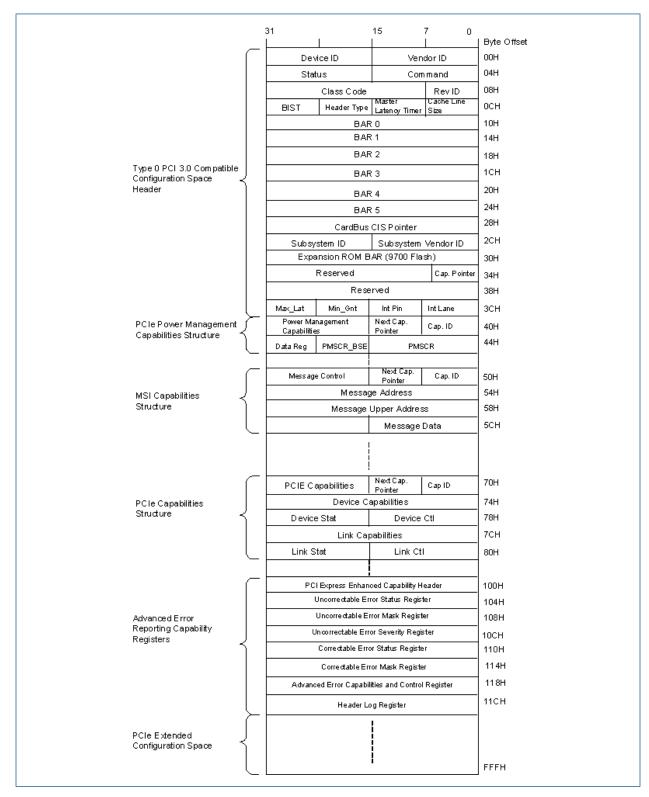

| 7 | PCle | Confid    | juration Register Definition         | 207 |

|   |      |           |                                      |     |

|   | 7.1  | 7.1.1     | PCIe Compatible Configuration Space  | 209 |

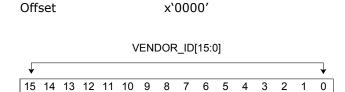

|   |      | 7.1.1     | Vendor ID Register                   | 209 |

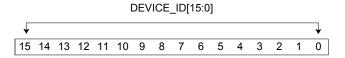

|   |      | 7.1.2     | -                                    | 210 |

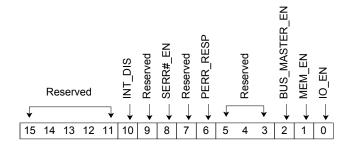

|   |      | 7.1.3     | Command Register                     | 210 |

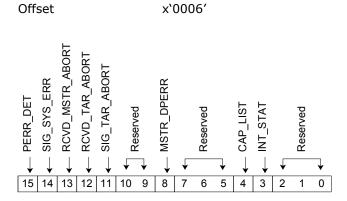

|   |      | 7.1.5     | Status Register                      | 212 |

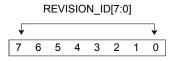

|   |      | 7.1.5     | Revision ID Register                 | 214 |

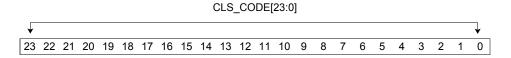

|   |      | 7.1.6     | Class Code Register                  | 214 |

|   |      | 7.1.7     | Cache Line Size Register             | 214 |

|   |      | 7.1.6     | Master Latency Timer Register        | 215 |

|   |      | 7.1.9     | Header Type Register                 | 215 |

|   |      | 7.1.10    | BIST Register                        | 213 |

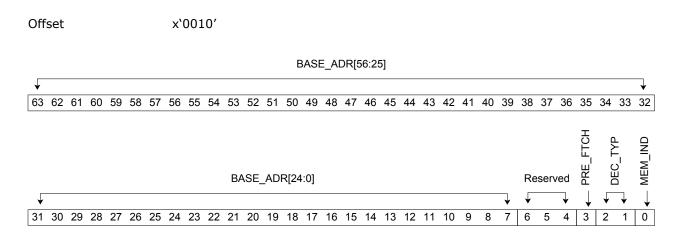

|     | 7.1.11  | Base Address Register 0, 1               | 216   |

|-----|---------|------------------------------------------|-------|

|     | 7.1.12  | Base Address Register 2-5                | 217   |

|     | 7.1.13  | Cardbus CIS Pointer Register             | 217   |

|     | 7.1.14  | Sub-System Vendor ID Register            | 217   |

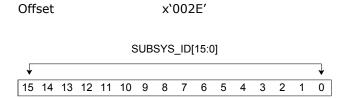

|     | 7.1.15  | Sub-System ID Register                   | 218   |

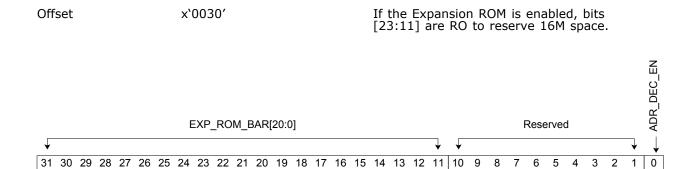

|     | 7.1.16  | Expansion ROM Base Address Register      | 219   |

|     | 7.1.17  | Capabilities Pointer Register            | 219   |

|     | 7.1.18  | Interrupt Line Register                  | 219   |

|     | 7.1.19  | Interrupt Pin Register                   | 220   |

|     | 7.1.20  | Min_Gnt Register                         | 220   |

|     | 7.1.21  | Max_Lat Register                         | 220   |

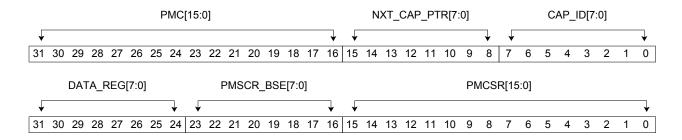

| 7.2 | Power M | lanagement Capabilities Registers        | . 221 |

|     | 7.2.1   | Capability ID Register                   | 221   |

|     | 7.2.2   | Next Capabilities Pointer Register       | 221   |

|     | 7.2.3   | Power Management Capabilities Register   | 222   |

|     | 7.2.4   | Power Management Control/Status Register | 223   |

|     | 7.2.5   | PMCSR-BSE Register                       | 224   |

|     | 7.2.6   | Data Register                            | 224   |

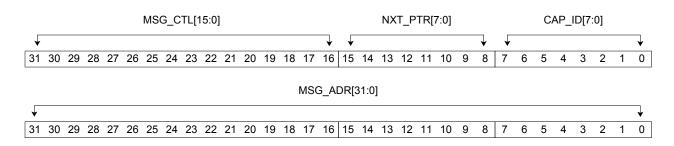

| 7.3 | MSI Cap | oability Registers                       | . 225 |

|     | 7.3.1   | Capability ID Register                   | 225   |

|     | 7.3.2   | Next Capabilities Pointer Register       | 226   |

|     | 7.3.3   | Message Control Register                 | 227   |

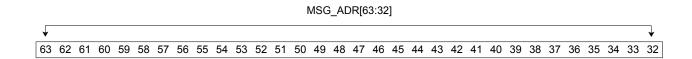

|     | 7.3.4   | Message Address Register                 | 228   |

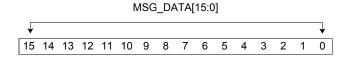

|     | 7.3.5   | Message Data Register                    | 228   |

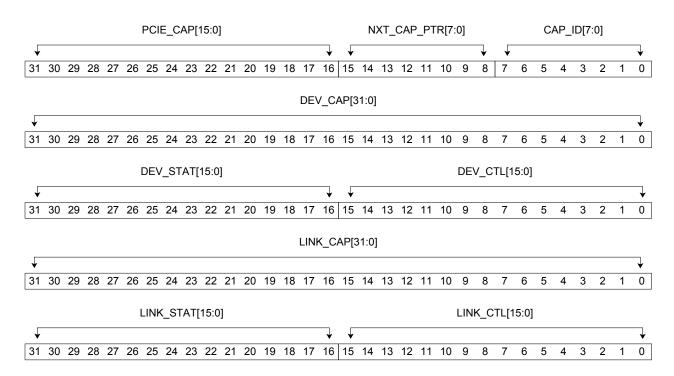

| 7.4 | PCI Exp | ress Capability Registers                | . 229 |

|     | 7.4.1   | Capability ID Register                   | 229   |

|     | 7.4.2   | Next Capabilities Pointer Register       | 230   |

|     | 7.4.3   | PCIe Capabilities Register               | 230   |

|     | 7.4.4   | Device Capabilities (DEV_CAP) Register   | 231   |

|     | 7.4.5   | Device Control (DEV_CTL) Register        | 234   |

|     | 7.4.6   | Device Status Register                   | 236   |

|     | 7.4.7   | Link Capabilities Register               | 238   |

|     | 7.4.8   | Link Control Register                    | 239   |

|     | 7.4.9   | Link Status Register                     | 240   |

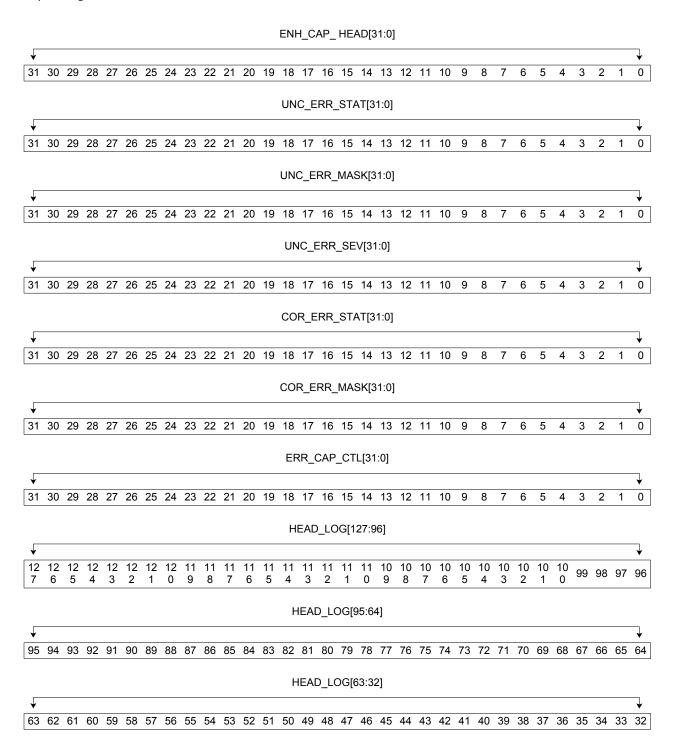

| 7.5 | Advance | ed Error Reporting Capability Registers  | . 241 |

|   |                                                   | 7.5.1                                                                                                        | Enhanced Capability Header Register                                                                                                                              | 243                                                                       |

|---|---------------------------------------------------|--------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------|

|   |                                                   | 7.5.2                                                                                                        | Uncorrectable Error Status Register                                                                                                                              | 244                                                                       |

|   |                                                   | 7.5.3                                                                                                        | Uncorrectable Error Mask Register                                                                                                                                | 245                                                                       |

|   |                                                   | 7.5.4                                                                                                        | Uncorrectable Error Severity Register                                                                                                                            | 246                                                                       |

|   |                                                   | 7.5.5                                                                                                        | Correctable Error Status Register                                                                                                                                | 247                                                                       |

|   |                                                   | 7.5.6                                                                                                        | Correctable Error Mask Register                                                                                                                                  | 248                                                                       |

|   |                                                   | 7.5.7                                                                                                        | Advanced Error Capabilities and Control Register                                                                                                                 | 249                                                                       |

| 8 | Sian                                              | al Doc                                                                                                       | cription                                                                                                                                                         | 250                                                                       |

| 0 | Sign                                              | ai Dest                                                                                                      | Stiption                                                                                                                                                         | 250                                                                       |

|   | 8.1                                               | PCI Exp                                                                                                      | ress Interface                                                                                                                                                   | . 250                                                                     |

|   | 8.2                                               | Miscella                                                                                                     | neous Interface                                                                                                                                                  | . 252                                                                     |

|   | 8.3                                               | GPIO/Pr                                                                                                      | robe Interface                                                                                                                                                   | . 253                                                                     |

|   | 8.4                                               | SPI Inte                                                                                                     | erface                                                                                                                                                           | . 253                                                                     |

|   | 8.5                                               | JTAG In                                                                                                      | terface                                                                                                                                                          | . 254                                                                     |

|   | 8.6                                               | Power a                                                                                                      | and Ground Interface                                                                                                                                             | . 254                                                                     |

|   |                                                   |                                                                                                              |                                                                                                                                                                  |                                                                           |

| 9 | Frro                                              | r Handl                                                                                                      | lina                                                                                                                                                             | 256                                                                       |

| 9 |                                                   |                                                                                                              | ling                                                                                                                                                             | 256                                                                       |

| 9 | <b>Erro</b> 9.1                                   |                                                                                                              | ling                                                                                                                                                             |                                                                           |

| 9 |                                                   | Error De                                                                                                     |                                                                                                                                                                  | . 256                                                                     |

| 9 | 9.1                                               | Error De                                                                                                     | etection Methods                                                                                                                                                 | . 256                                                                     |

|   | <ul><li>9.1</li><li>9.2</li><li>9.3</li></ul>     | Error De<br>Error Ca<br>Error Ha                                                                             | etection Methods                                                                                                                                                 | . 256<br>. 256<br>. 256                                                   |

|   | 9.1<br>9.2<br>9.3                                 | Error De Error Ca Error Ha                                                                                   | etection Methods                                                                                                                                                 | . 256<br>. 256<br>. 256<br>. 258                                          |

|   | <ul><li>9.1</li><li>9.2</li><li>9.3</li></ul>     | Error De Error Ca Error Ha                                                                                   | etection Methods                                                                                                                                                 | . 256<br>. 256<br>. 256<br>. 258                                          |

|   | 9.1<br>9.2<br>9.3                                 | Error De Error Ca Error Ha Specific Absolute                                                                 | etection Methods                                                                                                                                                 | . 256<br>. 256<br>. 256<br><b>258</b><br>. 258                            |

|   | 9.1<br>9.2<br>9.3<br>DC S                         | Error De Error Ha  Error Ha  Absolute Recomn                                                                 | etection Methods                                                                                                                                                 | . 256<br>. 256<br>. 256<br>. 258<br>. 258                                 |

|   | 9.1<br>9.2<br>9.3<br>DC S<br>10.1<br>10.2         | Error De Error Ha  Error Ha  Absolute Recomn                                                                 | etection Methods                                                                                                                                                 | . 256<br>. 256<br>. 256<br>. 258<br>. 258                                 |

|   | 9.1<br>9.2<br>9.3<br>DC S<br>10.1<br>10.2         | Error De Error Ha  Specific Absolute Recomn                                                                  | etection Methods                                                                                                                                                 | . 256<br>. 256<br>. 256<br>. 258<br>. 258<br>. 258<br>. 259               |

|   | 9.1<br>9.2<br>9.3<br>DC S<br>10.1<br>10.2         | Error De<br>Error Ca<br>Error Ha<br>Specific<br>Absolute<br>Recomn<br>Power S<br>10.3.1<br>10.3.2            | etection Methods                                                                                                                                                 | . 256<br>. 256<br>. 256<br>. 258<br>. 258<br>. 259<br>. 259<br>. 259      |

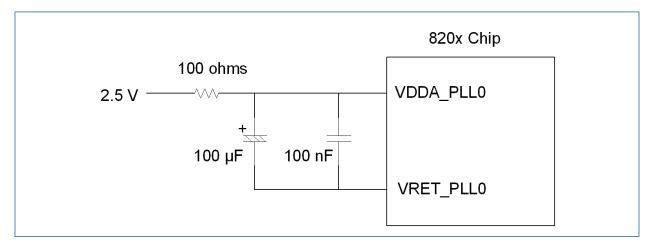

|   | 9.1<br>9.2<br>9.3<br>DC S<br>10.1<br>10.2<br>10.3 | Error De<br>Error Ca<br>Error Ha<br>Specific<br>Absolute<br>Recomm<br>Power S<br>10.3.1<br>10.3.2<br>Power S | etection Methods  ategories  andling Mechanism  cations  e Maximum Ratings  nended Operating Conditions  Supplies  Digital Power Supplies  Analog Power Supplies | . 256<br>. 256<br>. 258<br>. 258<br>. 258<br>. 259<br>259<br>259<br>. 260 |

| 11 | AC S | pecifications                                            | 264   |

|----|------|----------------------------------------------------------|-------|

|    | 11.1 | Reset Timing                                             | . 264 |

|    | 11.2 | PLL Clock Input                                          | . 264 |

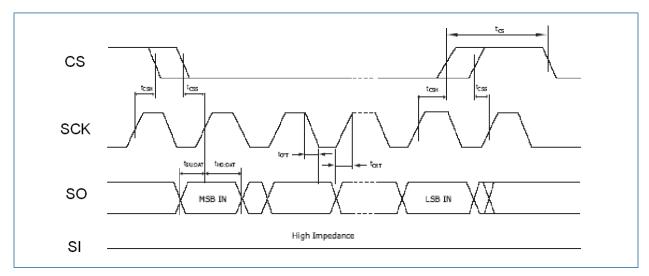

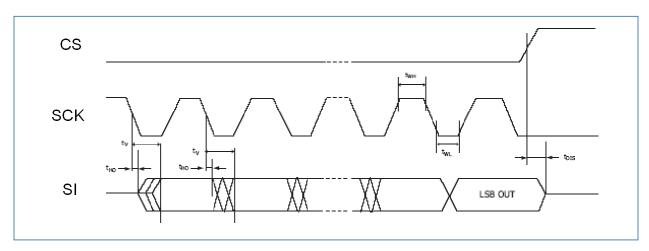

|    | 11.3 | SPI Interface Timing                                     | . 264 |

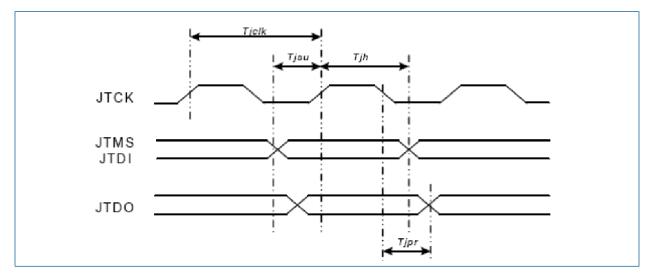

|    | 11.4 | JTAG Interface Timing                                    | . 266 |

|    | 11.5 | PCIe Interface Timing                                    | . 267 |

| 12 | Ther | mal Specifications                                       | 268   |

|    | 12.1 | Thermal Sensor Controller                                | . 268 |

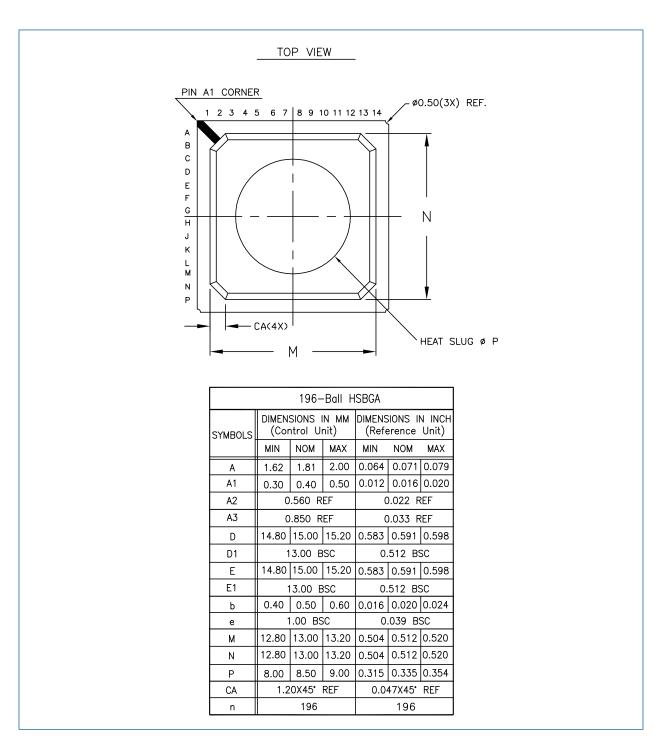

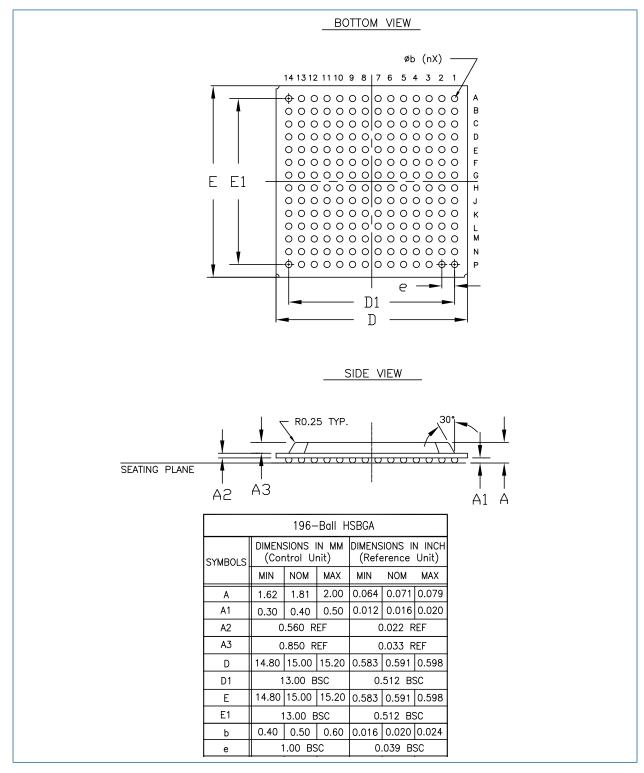

| 13 | Pack | age Specifications                                       | 269   |

|    | 13.1 | General Information                                      | . 269 |

|    | 13.2 | Mechanical Information                                   | . 269 |

| Αŗ | pend | lix A: IPsec Encapsulating Security Payload (ESP) Format | 280   |

| Αŗ | pend | lix B: CRC Algorithms                                    | 282   |

|    | B.1  | Key CRC and XTS DIF                                      | . 282 |

|    | B.2  | Data CRC                                                 | . 282 |

| Αŗ | pend | lix C: AES CBC/XTS FK Generation                         | 284   |

|    | C.1  | Key Expansion                                            | . 284 |

|    | C.2  | Encryption Algorithm                                     | . 284 |

|    | C.3  | Decryption Algorithm                                     | . 285 |

| Αŗ | pend | lix D: MAC and IPAD and OPAD                             | 288   |

|    | D.1  | MAC in SSL3.0                                            | . 288 |

|    | D.2  | MAC in TLS1.0                                            | . 288 |

|    | D.3  | MAC in DTLS 1.0                                          | 280   |

| D.4  | 4 IPAD & OPAD Generation |          | <br>289 |

|------|--------------------------|----------|---------|

| Docu | ıment Revision History   | <i>,</i> | <br>291 |

| I.1  | Document Revision A      |          | <br>291 |

| I.2  | Document Revision B      |          | <br>291 |

| I.3  | Document Revision C      |          | <br>292 |

| I.4  | Document Revision D      |          | <br>292 |

| I.5  | Document Revision 00 .   |          | <br>292 |

| I.6  | Document Revision 01 .   |          | <br>293 |

| I.7  | Document Revision 02 .   |          | <br>293 |

| I.8  | Document Revision 03 .   |          | <br>293 |

| I.9  | Document Revision 04 .   |          | <br>294 |

| Т 1  | 0 Document Povision 05   |          | 204     |

# **List of Figures**

| Figure 1-1. Application Example                                           |

|---------------------------------------------------------------------------|

| Figure 2-1. 820x Block Diagram                                            |

| Figure 2-2. Compression Engine LZS Real Time Verification                 |

| Figure 2-3. Compression Engine GZIP/Deflate Real Time Verification33      |

| Figure 2-4. Encryption Engine Real Time Verification34                    |

| Figure 2-5. Hash Engine Real Time Verification35                          |

| Figure 2-6. Encode Operation Real Time Verification                       |

| Figure 2-7. Decode Operation Real Time Verification                       |

| Figure 2-8. 820x Modules that can be Clock Gated                          |

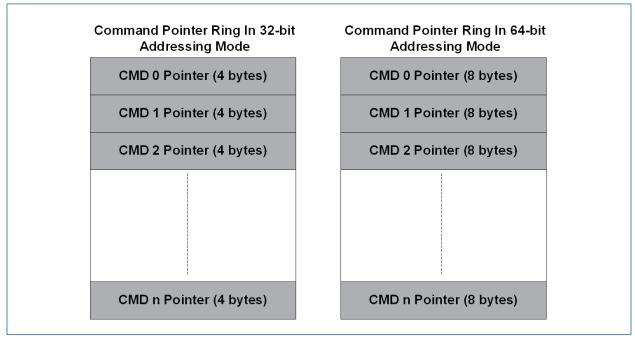

| Figure 3-1. Command Pointer Ring Format                                   |

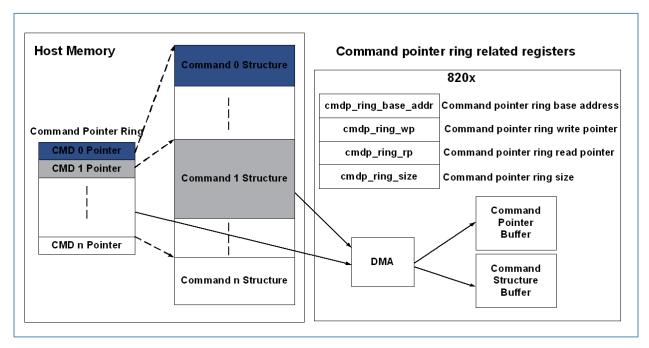

| Figure 3-2. Command Pointer Ring                                          |

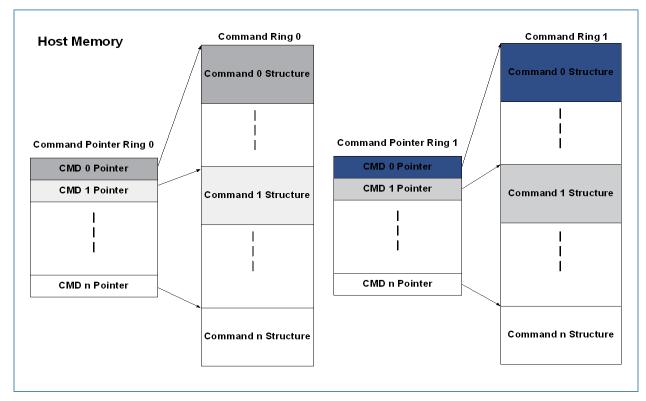

| Figure 3-3. Dual Command Ring Mode                                        |

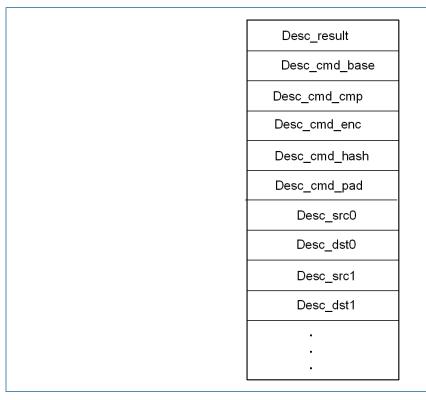

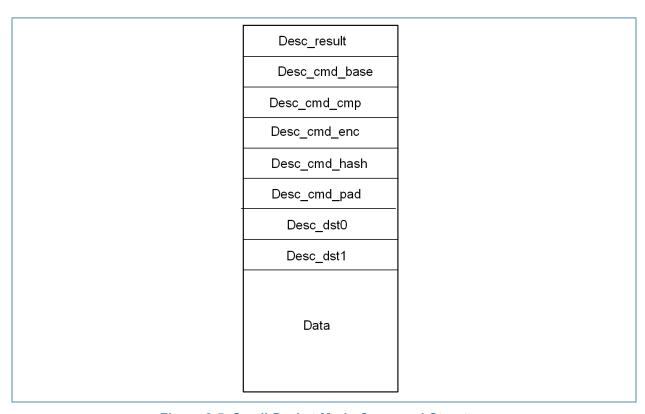

| Figure 3-4. Normal Mode Command Structure                                 |

| Figure 3-5. Small Packet Mode Command Structure                           |

| Figure 3-6. Endian Format Field Swap Options                              |

| Figure 3-7. Basic Data Sequence                                           |

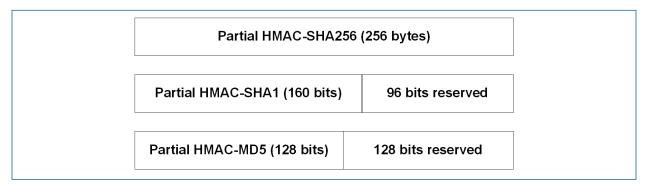

| Figure 3-8. Partial IHV Field for a Stateful HMAC Operations              |

| Figure 3-9. Partial IHV Field for a Stateful XCBC-MAC Operations          |

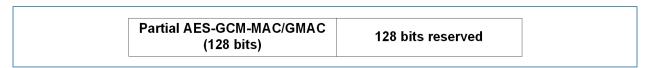

| Figure 3-10. Partial IHV Field for a Stateful AES-GCM-MAC/GMAC Operations |

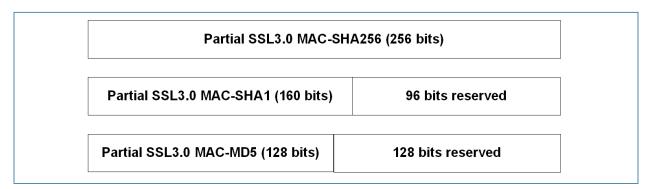

| Figure 3-11. Partial IHV Field for a Stateful SSL3.0-MAC Operations       |

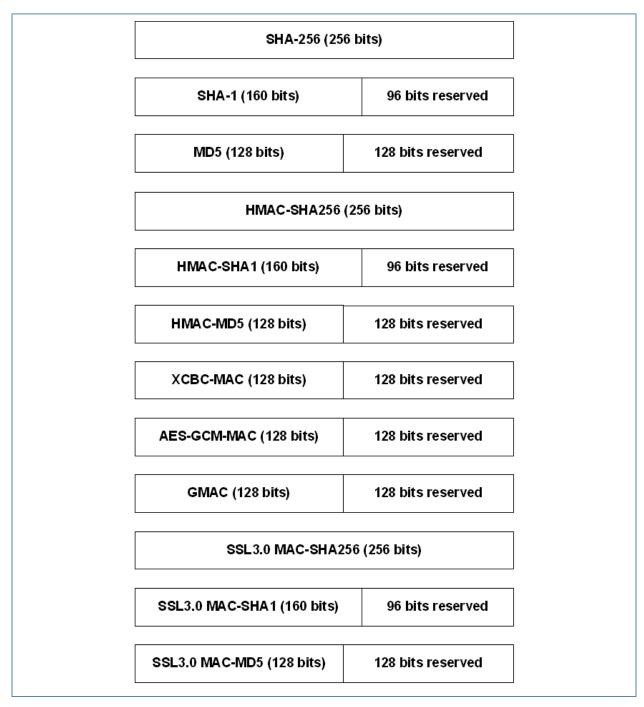

| Figure 3-12. MAC Field Format                                             |

| Figure 3-13. AES IV Lengths                                               |

| Figure 3-14. Key Format 1 (72 bytes)                                      |

| Figure 3-15. Key Format 2                                                 |

| Figure 3-16. Key Format 3                                                 |

| Figure 3-17. Key Format 482                                               |

| Figure 3-18. Hash Entry Format                                            |

| Figure 3-19. Hash Buffer Format                                           |

| Figure 3-20. AES-GCM Implementation Illustration                          |

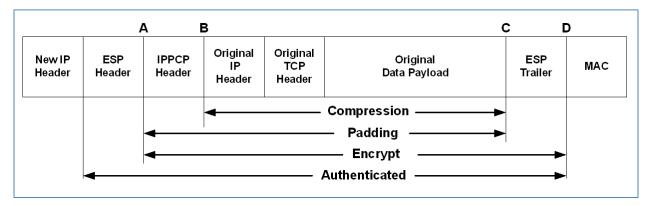

| Figure 3-21. IPsec Example: Applying IPPCP and ESP in Tunnel Mode         |

| Figure 3-22. Free Pool Ring                                               |

| Figure 3-23. Free Pool Usage Example                                      |

| Figure 3-24. Result Ring Example                                          |

| Figure 3-25. Command Process Flow Example                                 |

| Figure 4-1. Encode Operation: Hash Engine before Compression Engine       |

| Figure 4-2. Encode Operation: Compression Engine before Hash Engine | 105 |

|---------------------------------------------------------------------|-----|

| Figure 4-3. Encode Operation: Hash Engine after Pad Engine          | 106 |

| Figure 4-4. Encode Operation: Hash Engine after Encryption Engine   | 107 |

| Figure 4-5. Decode Operation: Hash Engine before Encryption Engine  | 108 |

| Figure 4-6. Decode Operation: Hash Engine after Encryption Engine   | 109 |

| Figure 4-7. Decode Operation: Hash Engine after Pad Engine          | 110 |

| Figure 4-8. Decode Operation: Hash Engine after Compression Engine  | 111 |

| Figure 5-1. DMA Command Pointer Prefetch Example                    | 113 |

| Figure 5-2. Channel Manager Block Diagram                           | 115 |

| Figure 5-3. PKP Manager Block Diagram                               | 118 |

| Figure 5-4. Hash Engine Block Diagram                               | 120 |

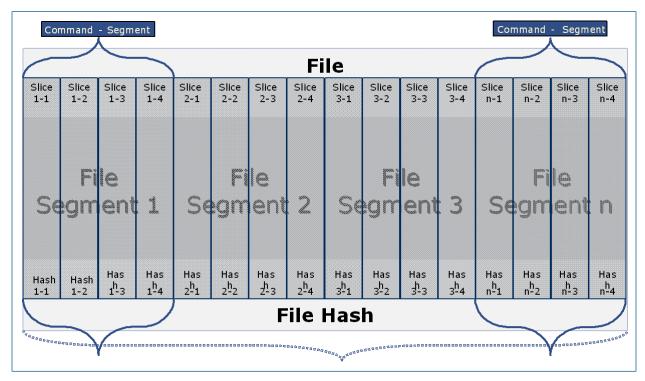

| Figure 5-5. Application Example of Slice Hash + File Hash           | 122 |

| Figure 5-6. SHA Core Block Diagram                                  | 125 |

| Figure 5-7. MD5 Core Block Diagram                                  | 126 |

| Figure 5-8. LZS Engine Block Diagram                                | 127 |

| Figure 5-9. GZIP Engine Block Diagram                               | 128 |

| Figure 5-10. Pad Engine Block Diagram                               | 129 |

| Figure 5-11. Encryption Engine Block Diagram                        | 130 |

| Figure 5-12. SPI Example Usage                                      | 132 |

| Figure 5-13. SPI Operation Example from Host Point of View          | 136 |

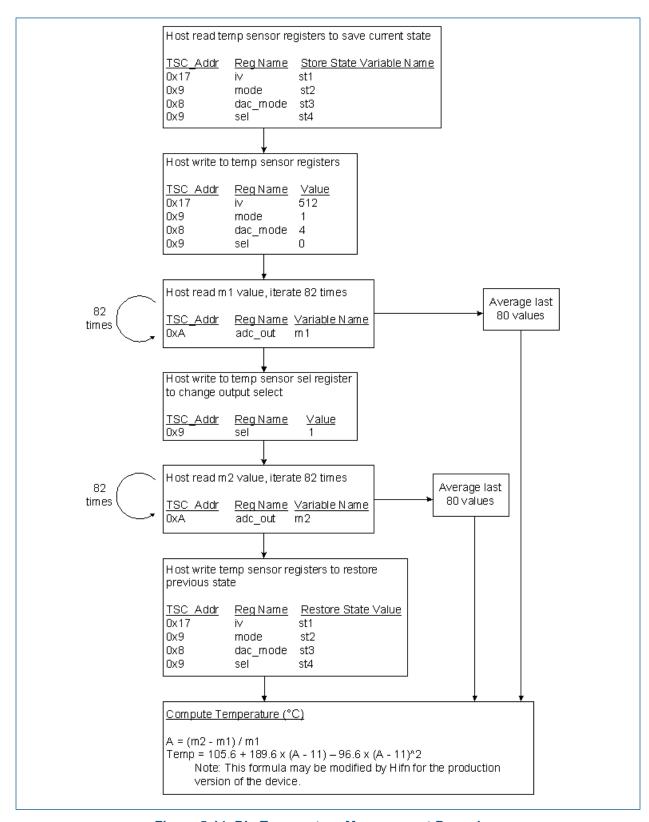

| Figure 5-14. Die Temperature Measurement Procedure                  | 139 |

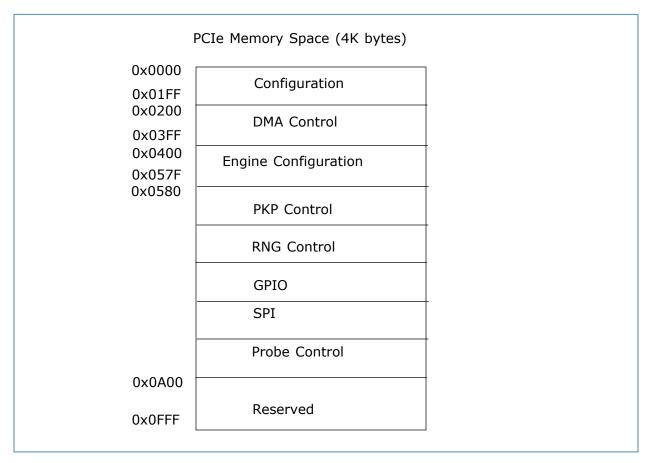

| Figure 6-1. PCIe Memory Map                                         | 141 |

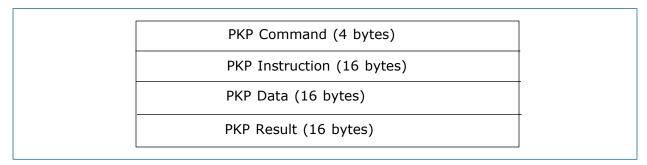

| Figure 6-2. PKP Command Entry Format                                | 171 |

| Figure 7-1. 820x PCI-Express Configuration Space                    | 208 |

| Figure 8-1. Example PLL Circuit                                     | 253 |

| Figure 11-1. SPI Write Timing                                       | 265 |

| Figure 11-2. SPI Read Timing                                        | 265 |

| Figure 11-3. JTAG Timing                                            | 266 |

| Figure 13-1. Top View Package Dimensions                            | 270 |

| Figure 13-2. Bottom View and Side View Package Dimensions           | 271 |

| Figure 13-3. Ball Map Drawing - Top View - Upper Left Quadrant      | 272 |

| Figure 13-4. Ball Map Drawing - Top View - Upper Right Quadrant     | 273 |

| Figure 13-5. Ball Map Drawing - Top View - Lower Left Quadrant      | 274 |

| Figure 13-6. Ball Map Drawing - Top View - Lower Right Quadrant     | 275 |

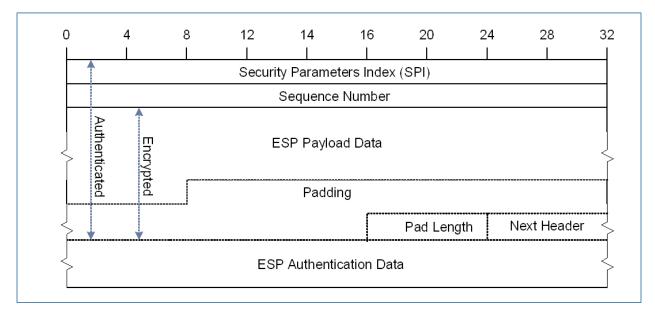

| Figure A-1. IPsec ESP Packet Format                                 | 281 |

| Figure C-1. GCM Mode                                                | 286 |

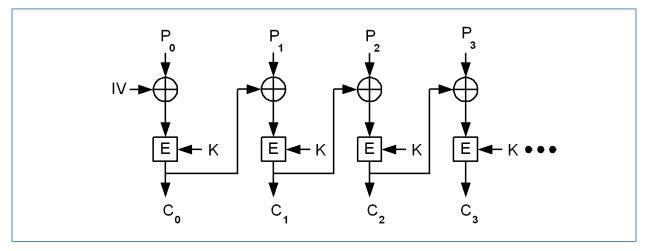

| Figure C-2. CBC Mode                                                | 287 |

# **List of Tables**

| Table 1-1. 820x Engine Features24                                                      |

|----------------------------------------------------------------------------------------|

| Table 1-2. Part Numbers                                                                |

| Table 2-1. Description of 820x Major Blocks29                                          |

| Table 3-1. CRC Enable Behavior for all Commands except AES-XTS51                       |

| Table 3-2. PAD_AG[3:0] Field Decoding                                                  |

| Table 3-3. MAC Operation Table                                                         |

| Table 3-4. Command Structure Values for IPsec Example                                  |

| Table 3-5. GZIP Decode Error Table                                                     |

| Table 5-1. Behavior of PCIE_PHY_CFG and EXT_FLASH_CFG_EN Pins during Initialization133 |

| Table 5-2. Programmable Device Memory Map                                              |

| Table 5-3. Temperature Sensor Register Map                                             |

| Table 7-1. Register Type Definitions                                                   |

| Table 8-1. PCIe Interface Signal Definition250                                         |

| Table 8-2. Miscellaneous Interface Signal Definition                                   |

| Table 8-3. Miscellaneous Interface Signal Definition                                   |

| Table 8-4. SPI Interface Signal Definition253                                          |

| Table 8-5. JTAG Interface Signal Definition                                            |

| Table 8-6. Power and Ground Interface Description                                      |

| Table 10-1. Absolute maximum ratings                                                   |

| Table 10-2. Recommended operating conditions                                           |

| Table 10-3. VDD_25_33 Power Supply Requirements                                        |

| Table 10-4. VDD_10 Power Supply Requirements                                           |

| Table 10-5. VDD_25A Power Supply Requirements                                          |

| Table 10-6. VDD_10A Power Supply Requirements260                                       |

| Table 10-7. VDDA_PLL0, VDDA_PLL1 Power Supply Requirements260                          |

| Table 10-8. 8204 Current and Power Per Power Domain260                                 |

| Table 10-9. 8203 Current and Power Per Power Domain                                    |

| Table 10-10. 8202 Current and Power Per Power Domain261                                |

| Table 10-11. Commercial 8201 Current and Power Per Power Domain262                     |

| Table 10-12. Industrial 8201 Current and Power Per Power Domain 262                    |

| Table 10-13. Normal IO Characteristics                                                 |

| Table 10-14. PCIe PHY Transmitter Characteristics                                      |

| Table 10-15. PCIe PHY Receiver Characteristics                                         |

| Table 11-1. PLL0 and PLL1 Reference Clock Requirements264                              |

| Table 11-2. SPI Interface AC Characteristics                                           |

| Table 11-3. JTAG Interface AC Characteristics           | . 266 |

|---------------------------------------------------------|-------|

| Table 12-1. Thermal operating conditions                | . 268 |

| Table 12-2. Thermal Specifications for Commercial Parts | . 268 |

| Table 13-1. General Package Information                 | . 269 |

| Table 13-2. Alphabetical Ball List                      | . 276 |

| Table 13-3. Numeric Ball List                           | . 278 |

| Table A-1. IPsec ESP Packet Field Description           | . 280 |

# **Preface**

Welcome to the Data Sheet for Exar's 8201, 8202, 8203, 8204 (820x), a high performance, low power, compression/encryption/hash acceleration processor. This document describes the 820x operation, data structures, data flow and specifications.

Please refer to the 8201, 8202, 8203, 8204 Errata for release specific errata for the 820x device.

## **Audience**

This document is intended for:

- Project managers

- System engineers

- Hardware and software development engineers

- Marketing and product managers

# **Prerequisite**

Before proceeding, you should generally understand:

- PCI Express

- GZIP/Deflate, eLZS and AES algorithms

- Hash, MAC algorithms

- General networking concepts

# **Document Organization**

This document is organized as follows:

<u>Chapter 1, "Product Description"</u> provides an overview of the 820x processor.

Chapter 2, "Operation" describes key features of the 820x operations.

Chapter 3, "Data Structures" defines the format of the data structures used by the 820x.

Chapter 4, "Data Flow" gives examples of the typical data flows within the 820x.

Chapter 5, "Modules" describes the internal 820x modules in more detail.

<u>Chapter 6, "Register Definition"</u> details the syntax and usage of the internal 820x registers.

<u>Chapter 7, "PCIe Configuration Register Definition"</u> details the syntax and usage of the PCIe registers.

Chapter 8, "Signal Description" defines the external interfaces for the 820x device.

Chapter 9, "Error Handling" describes the 820x error handling features.

Chapter 10, "DC Specifications" defines the 820x DC specifications.

Chapter 11, "AC Specifications" defines the 820x AC specifications.

Chapter 12, "Thermal Specifications" defines the 820x thermal specifications.

Chapter 13, "Package Specifications" defines the 820x package specifications.

<u>Appendix A</u> through <u>Appendix D</u> provide detailed information on how the algorithms are calculated. This material is included for reference only. Exar's SDK automatically implements these algorithms.

### **Related Documents**

The following documents can be used as a reference to this document.

UG-0211 8201, 8202, 8203, 8204 Hardware Design User Guide

AN-0206 Raw Acceleration API Performance Application Note

AN-0207 QuickAssist API Performance Application Note

AN-0205 Data Offload API Performance Application Note

ER-0015 8201, 8202, 8203, 8204 and DX 1845, 1835, 1825, 1710, 1720, 1730, 1740 Errata

# **Customer Support**

For technical support about this product, please contact your local Exar sales office, representative, or distributor.

For general information about Exar and Exar products refer to: www.exar.com

# **Glossary**

Term Definition

AAD Additional Authentication Data

AES Advanced Encryption Standard

CBC Cipher Block Chaining

CM Channel Manager

CPR Command Pointer Ring

CRC Cyclic Redundancy Check

CTR Counter Mode

**DES** Data Encryption Standard

**DH** Diffie-Hellman key exchange protocol

**DIF** Data Integrity Field for AES-XTS

**DPC** Data Process Channel

DSADigital Signature AlgorithmDSSDigital Signature Standard

ECC Electronic Codebook

ECC Error correction code

**ECDH** Elliptic-Curve Diffie-Hellman

ECDSA Elliptic-Curve Digital Signature Algorithm

ECRC End-to-End cyclic Redundancy Check

**eLZS** Enhanced LZS

**ESP** Encapsulating Security Payload

**GMAC** Galois Message Authentication Code

**GZIP** GNU ZIP

**HMAC** Hash Message Authentication Code

IHV Initial Hash Value

IPAD Inner Padding

IPPCP IP Payload Compression Protocol

IPsec IP Security Protocol

IV Initial Vector

JTAG Joint Test Action Group

LZS Lempel-Ziv Stac

MAC Message Authentication Code

**OPAD** Outer Padding

PHY Physical-Layer interface - usually for PCI express

Term Definition

PKP Public Key Processor

PLL Phase-Locked Loop

RC PCIe Root Complex

**RNG** Random Number Generator

**RSA** Ron Rivest, Adi Shamir and Leonard Adleman

**SO** Initial Value for Hash Engine GCM-MAC and GMAC calculation

**SPI** Serial Peripheral Interface

SSL Security Socket Layer

TLS Transport Layer Security

**UEFI** Unified Extensible Firmware Interface

XTS XES-based Tweaked CodeBook mode with Cipher Text Stealing

# 1 Product Description

Exar's 820x is a high-performance, low-power, look-aside acceleration device that is ideal for both storage and networking markets. The 820x provides hardware acceleration of compression, encryption and hashing algorithms including GZIP/Deflate, LZS, AES, 3DES, SHA, MAC and some public key algorithms such as DH, RSA, ECC. The 820x has a PCIe 2.0 Gen1 compliant interface to communicate with the host system.

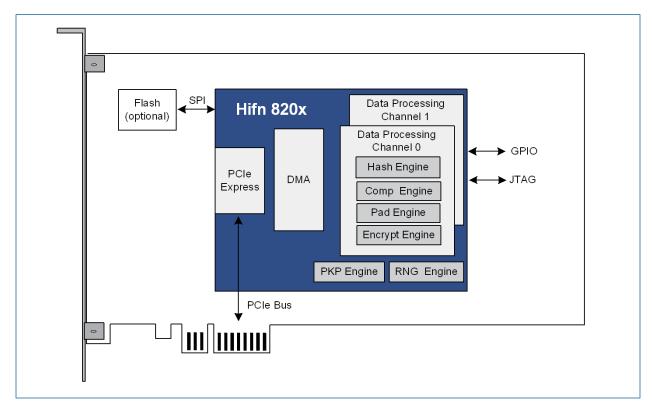

<u>Figure 1-1</u> shows a typical 820x application example. The 820x can be employed on a half-height PCIe card to accelerate encryption, hash and LZS/GZIP/Deflate compression.

Figure 1-1. Application Example

## 1.1 Features

## 1.1.1 High Performance

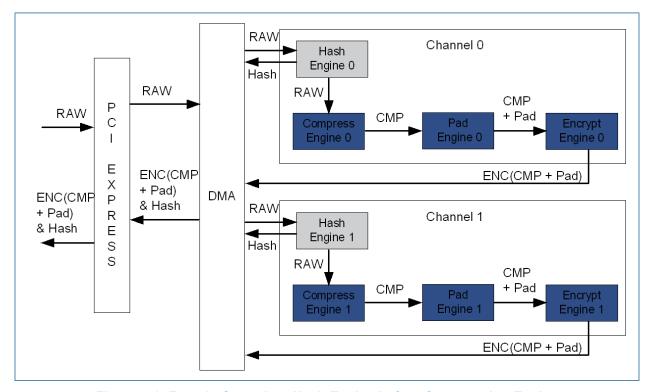

- Dual channel compression, encryption, pad, and hash engines

- Compression/Decompression engine with LZS and GZIP/Deflate algorithms

- Encryption/Decryption engine supports:

- AES-GCM, CBC, CTR and ECB with 128, 192 or 256 bit keys

- AES-XTS with 256 or 512 bit keys

- 3DES

- DES (supported via 3DES with K1=K2=K3)

- Hash engine supports:

- SHA1, SHA256

- MD5

- HMAC, GMAC, X-CBC-MAC and SSL3.0 MAC

- Public Key Processor

- Random Number Generator

- Compression, Encryption, Padding, MAC (Hash) in single pass

- Low Power

- Static clock gating of channels

- Dynamic clock gating for unused processing engines

- Dynamic clock gating of unused algorithm core in processing engine

## 1.1.2 Flexible Design for Packet Processing

- Position of the Hash engine for calculating MAC is programmable

- Truncated data stream head and tail pointers in each processing engine for packet processing

- Programmable mute table to null the 16 byte packet header

- Programmable length MAC inserted into data stream

## 1.1.3 Engine Features

Table 1-1. 820x Engine Features

| Engine       | Features                                                      |

|--------------|---------------------------------------------------------------|

| LZS          | Industry-standard LZS algorithm                               |

|              | Enhanced LZS (eLZS) algorithm with anti-expansion compression |

| GZIP/Deflate | Complies with RFC 1951 (Deflate), and RFC 1952 (GZIP)         |

|              | Supports Static Huffman algorithm                             |

|              | Supports Dynamic Huffman algorithm for high compression ratio |

| Encryption   | Supports multiple algorithms:                                 |

|              | AES-GCM, -XTS, -CBC, -CTR and -ECB and 3DES                   |

|              | Supports 128, 192 and 256 bit keys for AES (except XTS mode)  |

|              | Supports 256 and 512 bit keys for AES-XTS                     |

|              | Supports stateful encryption operation                        |

#### Table 1-1. 820x Engine Features

| Engine | Features                                                                            |

|--------|-------------------------------------------------------------------------------------|

| Hash   | Algorithms supported: HMAC-SHA1, HMAC-SHA256, HMAC-MD5, GMAC, X-CBC-MAC, SSL3.0-MAC |

|        | Slice and file hash operation                                                       |

|        | MAC inserted into the data stream                                                   |

|        | Stateful hash and MAC operation                                                     |

| Pad    | Supports padding with multiple algorithm in encode operation                        |

|        | Remove padding in decode operation                                                  |

| PKP    | RSA, DSA, DH, ECDH and ECDSA (elliptic curve) operations                            |

|        | Support up to 8K-bits modular arithmetic and exponentiation                         |

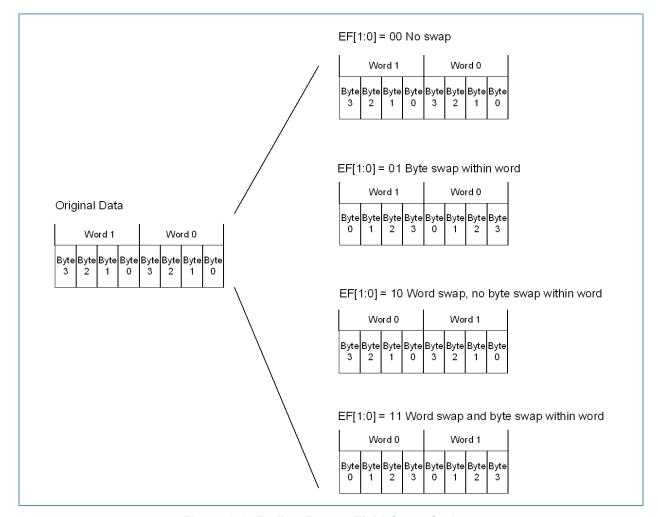

### 1.1.4 Command and Data Endian Conversion Modes

- No swap

- Byte swap in word

- Word swap, no byte swap in word

- Word swap, and byte swap in word

### 1.1.5 DMA Features

- · Indirect command addressing

- Unlimited scatter-gather

- Maximum 16K commands in command pointer ring

- Two command pointer rings with round-robin arbitration (the priority of command pointer rings is handled by host software)

- Free pool ring to avoid result data overflow

- Small packet command structure mode

# 1.1.6 Data Integrity Features

- Input CRC32 check, output CRC32 generator

- ECRC protection through PCIe bus (requires host RC support)

- ECC or Parity protection for data path RAMs

- Real time verification for all data transformation (Encryption and Compression engines), and hash or MAC calculation (Hash engine)

### 1.1.7 Other features

PCI Express x4, PCI Express x1 or PCI Express x2 interface

- JTAG support

- ACJTAG support for PCIe interface

- GPIO interface

- SPI interface to access a programmable device

- Thermal diode on chip to manage and prevent device overheating

- 196 ball HSBGA package (15 x 15 mm body, 1 mm ball pitch)

## 1.2 NIST Certificates

The 820x has passed the following NIST validation tests.

3DES: certificate #967

AES: certificate #1414

DSA: certificate #457

ECDSA: certificate #181

DRBG: certificate #53

HMAC: certificate #834

SHA: certificate #1284

# 1.3 Ordering Information

There are four speed variations and two process variations of the 820x device. The 8201 device is available for industrial applications.

**Table 1-2. Part Numbers**

| Part Number                                                        | Process                      | Speed                         |

|--------------------------------------------------------------------|------------------------------|-------------------------------|

| 8201CB                                                             | Commercial                   | 0.8 Gbits/sec, 100 MBytes/sec |

| 8201CB-F                                                           | Commercial, RoHS 6 compliant | 0.8 Gbits/sec, 100 MBytes/sec |

| 8201IB                                                             | Industrial                   | 0.8 Gbits/sec, 100 MBytes/sec |

| 8201IB-F                                                           | Industrial, RoHS 6 compliant | 0.8 Gbits/sec, 100 MBytes/sec |

| 8202CB                                                             | Commercial                   | 1.6 Gbits/sec, 200 MBytes/sec |

| 8202CB-F                                                           | Commercial, RoHS 6 compliant | 1.6 Gbits/sec, 200 MBytes/sec |

| 8203CB                                                             | Commercial                   | 3.2 Gbits/sec, 400 MBytes/sec |

| 8203CB-F                                                           | Commercial, RoHS 6 compliant | 3.2 Gbits/sec, 400 MBytes/sec |

| 8204CB                                                             | Commercial                   | 6.4 Gbits/sec, 800 MBytes/sec |

| 8204CB-F                                                           | Commercial, RoHS 6 compliant | 6.4 Gbits/sec, 800 MBytes/sec |

| Note: The speed is based on measured AES-GCM and eLZS performance. |                              |                               |

# 2 Operation

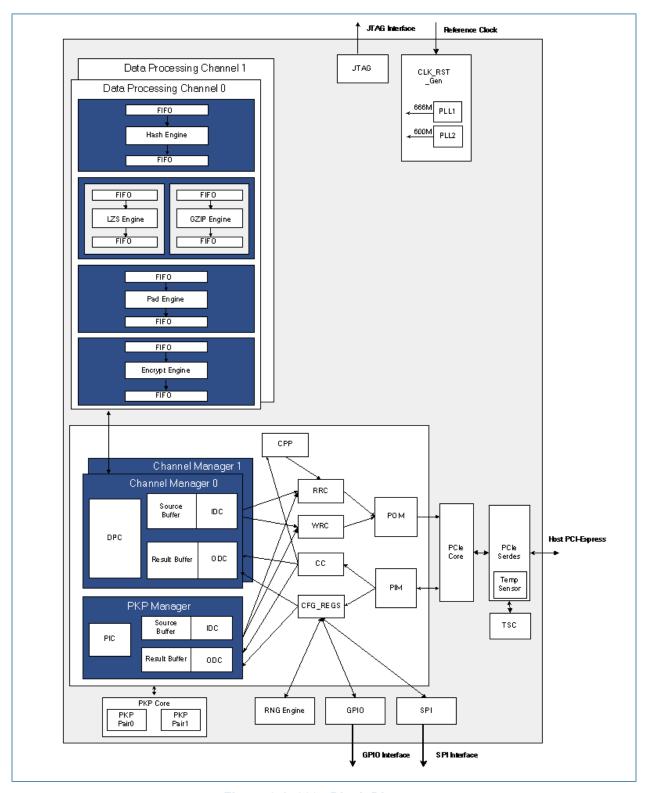

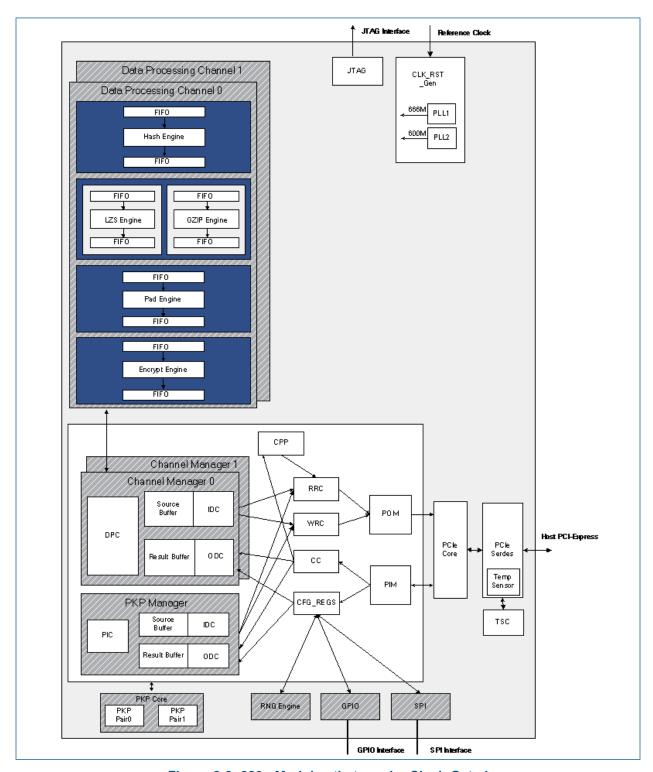

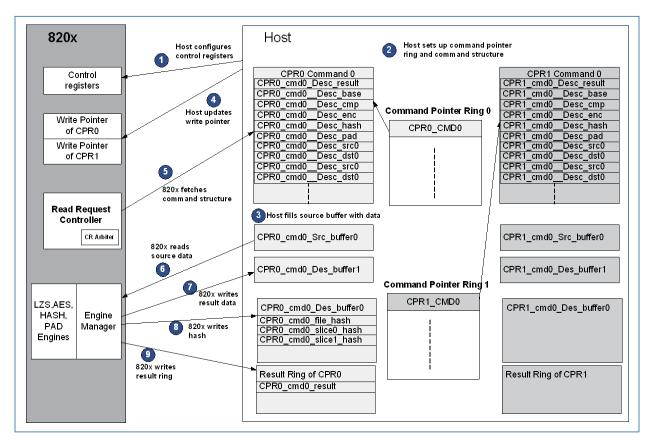

Figure 2-1 shows a block diagram of the 820x. Each block is defined in Table 2-1.

Figure 2-1. 820x Block Diagram

Table 2-1. Description of 820x Major Blocks

| Block Name      | Description                                                                                                                                                                |  |

|-----------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| CC              | Completion Controller                                                                                                                                                      |  |

|                 | Receives the completion data from the PCIe Inbound Manager, and then allocates the data to the proper Channel/PKP Manager according to the tags.                           |  |

| CFG_REGS        | Configuration Registers                                                                                                                                                    |  |

| Channel Manager | Channel Manager 0 and Channel Manager 1                                                                                                                                    |  |

| 0/1             | Controls all command processing: fetching command structures and data from host memory into the source buffer, transmitting results from the result buffer to host memory. |  |

| CLK_RST_Gen     | Clock and Reset Generation                                                                                                                                                 |  |

|                 | Generates the clock and reset signals for all modules.                                                                                                                     |  |

| CPP             | Command Pointer Ring Prefetch                                                                                                                                              |  |

|                 | Prefetches the command pointer from the command ring.                                                                                                                      |  |

| Encrypt Engine  | Encryption Engine                                                                                                                                                          |  |

|                 | Encrypts/Decrypts the data stream using the AES or 3DES algorithm.                                                                                                         |  |

| GPIO            | General Purpose IO                                                                                                                                                         |  |

| GZIP Engine     | GZIP Engine                                                                                                                                                                |  |

|                 | Compresses/Decompresses the data stream using the GZIP/Deflate algorithms.                                                                                                 |  |

| Hash Engine     | Hash Engine                                                                                                                                                                |  |

|                 | Calculates the hash value or MAC value of the data stream.                                                                                                                 |  |

| LZS Engine      | LZS Engine                                                                                                                                                                 |  |

|                 | Compresses/Decompresses the data stream using the LZS or enhanced LZS (eLZS) algorithm.                                                                                    |  |

| Pad Engine      | Pad Engine                                                                                                                                                                 |  |

|                 | Adds/Removes padding data from the data stream.                                                                                                                            |  |

| PCIe Core       | PCI express end point controller                                                                                                                                           |  |

| PCIe Serdes     | PCI express physical layer                                                                                                                                                 |  |

| PIM             | PCIe Inbound Manager                                                                                                                                                       |  |

|                 | Receives the PCIe completion from the PCIe Core, and sends/receives memory read/memory write to/from the PCIe Core.                                                        |  |

| PKP Engine      | Public Key Processor Engine                                                                                                                                                |  |

|                 | The PKP engine consists of two pairs of public key processors.                                                                                                             |  |

| PKP Manager     | PKP Manager                                                                                                                                                                |  |

|                 | Controls instruction and operand data fetching from host memory to the PKP engine, and transmits the calculated result from the PKP engine to host memory.                 |  |

| POM             | PCIe Outbound Manager                                                                                                                                                      |  |

|                 | Sends the PCIe write data and read requests to the PCIe Core.                                                                                                              |  |

| RNG             | Random Number Generator                                                                                                                                                    |  |

| RRC             | Read Request Controller                                                                                                                                                    |  |

|                 | Arbitrates read requests from the CPP, Channel Manager 0, Channel Manager 1 and PKP Manager, and sends read requests to the PCIe Outbound Manager.                         |  |

Table 2-1. Description of 820x Major Blocks

| Block Name | Description                                                                                                                                         |

|------------|-----------------------------------------------------------------------------------------------------------------------------------------------------|

| SPI        | SPI interface that connects to an external programmable device                                                                                      |

| TSC        | Temperature Sensor Controller                                                                                                                       |

|            | Provides host software access to the temperature sensor parameters.                                                                                 |

| WRC        | Write Request Controller                                                                                                                            |

|            | Arbitrates the write requests from Channel Manager 0, Channel Manager 1 and PKP Manager, and sends the write requests to the PCIe Outbound Manager. |

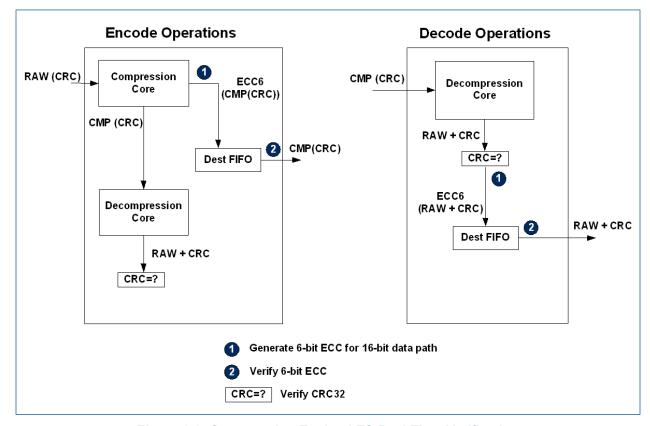

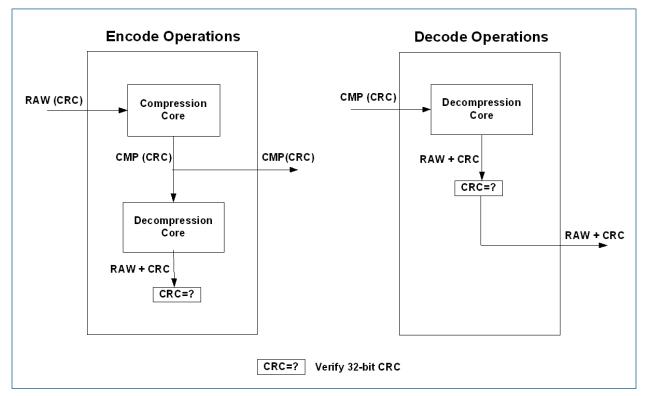

# 2.1 Data Integrity

The 820x provides robust data integrity with a combination of Error Code Correction (ECC), CRC, and Real Time Verification (RTV). These features combine to create strong data protection for encode and decode operations.

## 2.1.1 ECC & Parity Protection

All data in RAM is protected with 6-bit Error Code Correction (ECC6), 8-bit Error Code Correction (ECC8) and parity.

- ECC6 is used to protect 16 bit width RAM

- ECC8 is used to protect 64 bit width RAM

- Parity is used to protect the PCIe Core RAMs

ECC6 and ECC8 provide detection of all single, double, and triple bit errors.

### 2.1.2 CRC Protection

The host may configure the PCIe configuration register to either enable/disable ECRC protection. If enabled, the PCIe Core will generate the ECRC on the fly to protect data on the PCIe bus.

Data CRC can be generated by the host or by the 820x, depending on the configuration settings in the command structure. Please refer to the "CRC\_EN" field of the Command Structure for more information (Section 3.1.2.2). The CRC will be verified by the 820x, and may be sent to the host or stripped from the data stream.

## 2.1.3 Real Time Verification

The Compression, Encryption and Hash engines contain internal real time verification logic that ensures all transforms are completed successfully and any detected errors are reported prior to the command completing.

Real time verification may be enabled or disabled via software. If enabled, real time verification will reduce the performance of small packet (< 2K bytes) LZS and GZIP/Deflate compression operations. Enabling real time verification will slightly increase the 820x power consumption (< 0.05W).

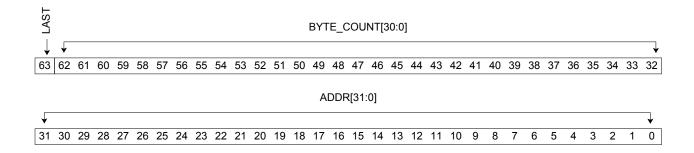

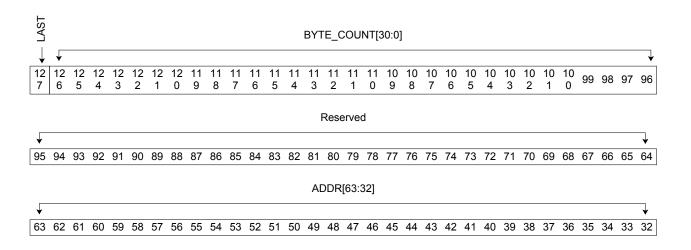

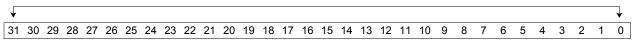

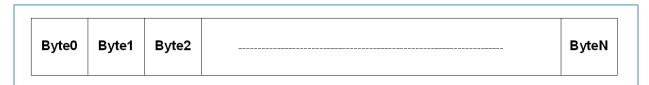

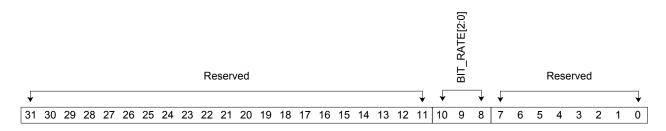

### 2.1.3.1 Compression Engine Real Time Verification