# 128M-bit (×16/×32) Dual-Operation Flash Memory with Page Mode MBM29PDL1280F

This flash memory can simultaneously read/program/erase data with a single 3V power supply. It possesses fast access performance with an initial access time of 70ns/80ns and a page access time of 25ns/30ns under low voltage.

## **Product Overview**

As an industry first, FUJITSU has developed a 128M-bit dual-operation page mode flash memory with 32-bit data transfer width for use in applications such as mobile phones, laser printers, and car navigation systems.

Remarkably, the faster speed is needed and the functionality and density of electronic devices have been increased, as seen in the new generation of faster/larger-density mobile phones, faster laser printers, and improved map-searching and communicative functions in car navigation. Speedup in the microprocessors mounted in these devices is inevitable, and their data transfer width is shifting from a conventional  $\times 8/\times 16$ -bit to  $\times 16/\times 32$ -bit or even 64-bit. At the same time, speedup, enlarged data transfer width, and larger density are also demanded in the flash memory for these devices.

This product was developed with the focus on fast access speed, and achieves a high-speed loading of 25ns-the fastest page mode access currently available. Furthermore, by enlarging the data transfer width from a conventional ×8/×16-bit to ×16/×32-bit, the consistency of the microprocessor at system is improved and huge amounts of data can be transacted at one time and at high speed. Using a dual-operation memory capable of simultaneously reading/programming/erasing data, the apparent memory operation time can also be shortened. This device also has a Hi-ROM function to prevent large-scale illegal copying, write hardware protection for the boot block

Photo 1 External View

Photo 2 Chip

that stores the system program, and an acceleration function that enables high-speed programming at system.

#### **Product Features**

#### ■ High-Speed Read Operation

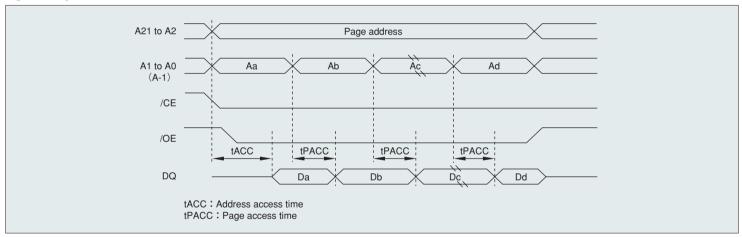

Fig.1 shows the page read mode.

The page mode reads an optional page (8 words or 4 double-words) initially by selecting high-order addresses (A21 to A2). Then, data within the page can be read at high speed in single- or double-words unit by selecting low-order addresses (A1 to A-1, or A1 to A0).

This product is available with initial access time of 70ns or 80ns, with corresponding page access time of 25ns or 30ns,

respectively.

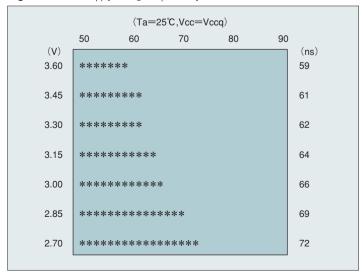

**Fig.2** shows the power supply voltage dependency of the access time, and **Fig.3** shows the power supply voltage dependency of the page read access time.

## ■ Dual-Operation Function

The address space is divided into 4 regions called "Bank" (Bank A, B, C and D). For example, data can be read from a sector in the bank B, C or D while programming/erasing data on a sector in Bank A.

#### ■ Single 3V Power Supply Operation

Data can be read/programmed/erased with a single 3V power supply. Since no 12V power supply is needed, the system can be configured without using a voltage converter or

Figure 1 Page Read Mode

Figure 2 Power Supply Voltage Dependency of Access Time

Figure 3 Power Supply Voltage Dependency of Page Read Access Time

| (Ta=25°C,Vcc=Vccq) |                  |                            |               |            |    |               |  |  |

|--------------------|------------------|----------------------------|---------------|------------|----|---------------|--|--|

| (1.1)              | 10               | 15                         | 20            | 25         | 30 |               |  |  |

| (V)<br>3.60        | ****             | *****                      | · <b>.</b>    |            |    | (ns)<br>19    |  |  |

| 3.60               | ****             | ******                     | of the        |            |    | 13            |  |  |

| 3.45               | ****             | *****                      | ***           |            |    | 20            |  |  |

|                    |                  |                            |               |            |    |               |  |  |

| 3.30               | ****             | *****                      | ***           |            |    | 20            |  |  |

| 3.15               | ****             | *****                      | ****          |            |    | 21            |  |  |

| 3.13               | at to the to the | ate ate ate ate ate ate at | . Se Se Se Se |            |    | 21            |  |  |

| 3.00               | ****             | *****                      | ****          |            |    | 22            |  |  |

|                    |                  |                            |               |            |    |               |  |  |

| 2.85               | ****             | *****                      | *****         | k          |    | 23            |  |  |

| 2.70               | ****             | *****                      | ****          | le sle sle |    | 24            |  |  |

| 2.70               | ****             | ~ ~ ~ ~ ~ ~ ~ ~            | *****         | to als als |    | <del>24</del> |  |  |

|                    |                  |                            |               |            |    |               |  |  |

48

2002

other additional parts.

#### Compatibility with Conventional Products

The command of program/erase is the same sequence as that of the single 3V power supply flash memory already commercialized.

#### ■ ×16-bit or ×32-bit Configuration

When the DW/ $\overline{W}$ pin is set to "H" the device operates in double-words mode to read/program data through DQ31-DQ0. When the DW/ $\overline{W}$ pin is set to "L", the device operates in word mode. In this mode, DQ31/A-1 will be the lowest address bit and data is read/programmed through DQ0-DQ15, with DQ16-DQ30 being ignored.

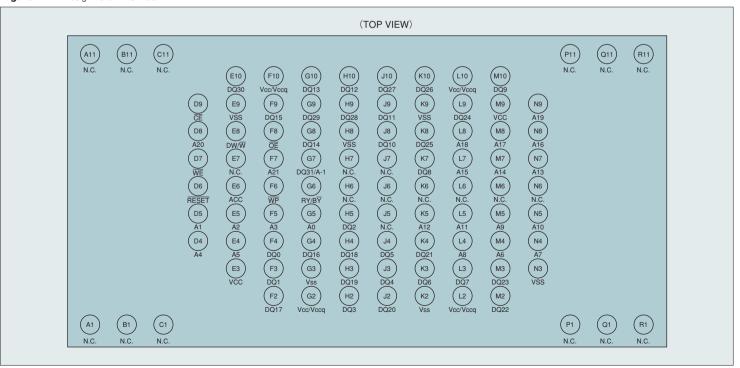

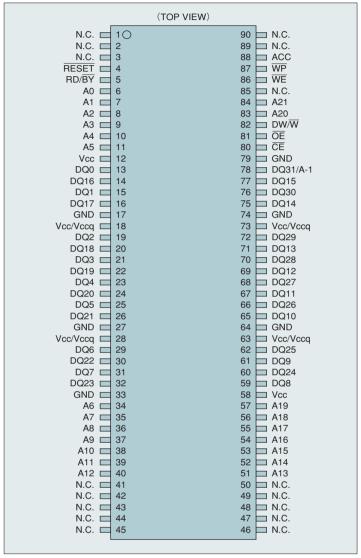

Fig.4 and 5 show the pin assignment.

#### ■ Hi-ROM Function

In addition to the normal memory region, a special 256bytes region is offered as an area where data can be programmed only once. Programming special data (for example, unique ID number) provides a highly advanced security function by the combination with an application.

#### Write Protection Function

This function is easily realized by the hardware method.

Write Protection Function provides the protection of the 2 outmost 8Kbytes sector on both end of boot sectors by setting the  $\overline{WP}$  pin to "L", regardless of whether normal sector protection is used.

#### Acceleration Function

This function is effective when a large amount of flash memory embedded into the system are programmed at shipment. When a high voltage (VHH) is applied to the ACC pin, the device enters the Acceleration mode, which enables faster programming than the normal mode. With this function, the programming time can be shortened 60% as much as that of the normal mode.

**Table 1** shows the product line up.

# **Advantages and Effects**

#### No External ROM/RAM Required

Since this product offers a dual-operation function, erase/program on itself is possible while executing a program for reprogramming directly from itself without loading in other memories. Therefore, the cost, mounting area, and power consumption of the system can be drastically reduced.

Figure 4 Pin Assignment (FBGA-96)

# Effective Use of Programming Time and Erasing Time

When addresses are changed to those of other Bank while erase/program in one sector, the system can be read the stored data at the address without canceling the erase/program operation. Changing the addresses of a Bank to those of other releases the data bus from the status information and enables it to output the data stored in the memory. Therefore, the apparent programming/erasing time can be reduced to almost 0 by the smart design of software, which improves the process speed of the products mounted the dual-operation flash memory.

# **Purpose**

The followings are sample applications for 128M-bit dualoperation page mode flash memory with the above characteristics.

- A system requiring a large-density flash memory due to high functionality or complex functions

- High-performance, external memory for a high-performance  $\times 32/\times 64$ -bit micro-controller

- A system in which program/code is upgraded

# **Future Development**

This article introduced a new product, MBM29PDL1280F, to meet the new demands for high speed and high functionality mainly in mobile phones, laser printers, and car navigation devices.

To meet customer's demands, FUJITSU will provide its lineup of families which realize multi-functionality, high functionality and larger density.

Figure 5 Pin Assignment (SSOP-90)

Table 1 Product Line Up

50

| Part number               |                           |             | MBM29PDL1280F                                                                   |       |  |

|---------------------------|---------------------------|-------------|---------------------------------------------------------------------------------|-------|--|

| Speed option              |                           |             | 70                                                                              | 80    |  |

| Bank architecture         |                           |             | 4-bank architecture<br>Bank A: 16Mb, Bank B: 48Mb<br>Bank C: 48Mb, Bank D: 16Mb |       |  |

| Access time               |                           | Initial     | 70ns                                                                            | 80ns  |  |

|                           |                           | Page        | 25ns                                                                            | 30ns  |  |

| Power supply voltage      |                           |             | 2.7V to 3.6V                                                                    |       |  |

| Power consumption (Max.)  | Read                      | Word        | 252mW                                                                           |       |  |

|                           | Erase/program in progress |             | 126mW                                                                           |       |  |

|                           | CMOS standby              |             | 18 μ W                                                                          |       |  |

| Erase time (Typ.)*1       |                           |             | 0.2s/sector                                                                     |       |  |

| Programming time (Typ.)*2 |                           | Word        | 6 µ s                                                                           |       |  |

|                           |                           | Double Word | 12                                                                              | 12 µs |  |

| Package                   |                           |             | SSOP-90, FBGA-96                                                                |       |  |

<sup>\*1:</sup>  $Ta=25^{\circ}C$ , Vcc=2.9V \*2:  $Ta=25^{\circ}C$ , Vcc=2.9V programming data is checker.