# IA3222/23 DAA CHIPSET WITH ANALOG INTERFACE

#### **Features**

- Programmable worldwide telecom compliance with one hardware build

- V.92 (56 kb/s) performance

- Virtually unlimited high-voltage isolation

- Highly-competitive BOM cost

- Lowest pin count chipset

- High common-mode RF immunity

- Continuous dc and audio snooping with >5 M $\Omega$  Tip to Ring

- Parallel pick-up, line-in-use, ring, and "911" detection

- -86 dBm receiver noise floor

- +6.5 dBm transmit power

- 120 dB Caller ID common-mode rejection at 120 Hz

#### **Applications**

- Low-cost fax-engine DAA retrofits PBX FXO/IP telephony

- Point-of-sale terminals

- Metering devices

- Alarm systems

- Cordless telephones

- Speaker phones

#### **Description**

The IA3222 and IA3223 integrated V.92 (56K) capable direct access arrangement (DAA) chipset is suitable for worldwide telephone line interface requirements. The patented isolation bridge technology eliminates the need for usual telecom isolation components, such as transformers or optocouplers. Innovative techniques reduce the number of discrete components, reducing overall solution cost.

The chipset can be programmed by software to pass PTT certification worldwide. The integrated V.92 DAA offers an easy-to-use analog interface with an internal or external dc reference for seamlessly interfacing to a variety of systems. It allows easy building-block integration where audio codecs are either separate or integrated into DSPs. It is also ideal for non-modem systems requiring isolated DAAs. such as alarm systems, VoIP, and PBX FXO interfaces.

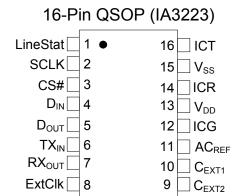

| Pin Assignments                                              |                                                                                                                                         |  |  |  |  |

|--------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| 16-Pin QSOF                                                  | P (IA3223)                                                                                                                              |  |  |  |  |

| LineStat                                                     | 16 ICT 15 V <sub>SS</sub> 14 ICR 13 V <sub>DD</sub> 12 ICG 11 AC <sub>REF</sub> 10 C <sub>EXT1</sub> 9 C <sub>EXT2</sub>                |  |  |  |  |

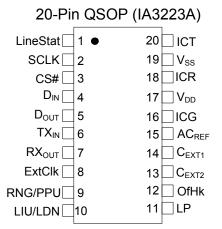

| 20-Pin QSOP                                                  | (IA3223A)                                                                                                                               |  |  |  |  |

| LineStat                                                     | 20 ICT 19 V <sub>SS</sub> 18 ICR 17 V <sub>DD</sub> 16 ICG 15 AC <sub>REF</sub> 14 C <sub>EXT1</sub> 13 C <sub>EXT2</sub> 12 OfHk 11 LP |  |  |  |  |

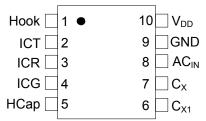

| 10-Pin MSOF  Hook ☐ 1 ●  ICT ☐ 2  ICR ☐ 3  ICG ☐ 4  HCap ☐ 5 | 9 (IA3222B)  10 V <sub>DD</sub> 9 GND 8 AC <sub>IN</sub> 7 C <sub>X</sub> 6 C <sub>X1</sub>                                             |  |  |  |  |

U.S. Patent # 7,031,458

U.S. Patent #7,139,391

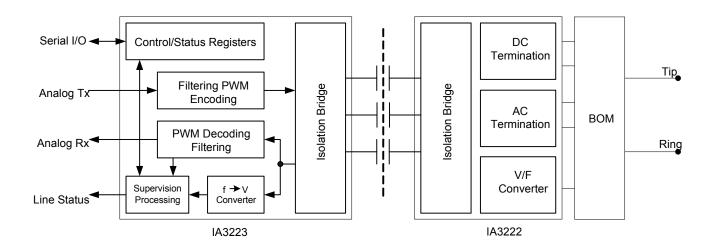

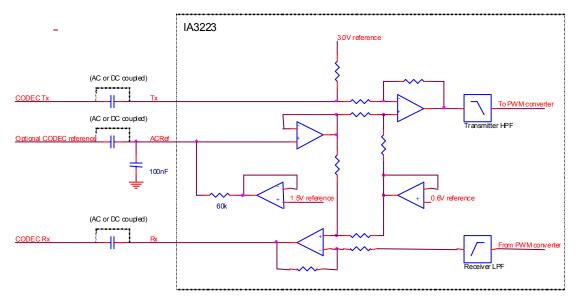

# **Functional Block Diagram**

# TABLE OF CONTENTS

| <u>Section</u>                                                         | <u>Page</u> |

|------------------------------------------------------------------------|-------------|

| 1. Electrical Specifications                                           | 4           |

| 2. Typical Performance Characteristics                                 |             |

| 3. Applications                                                        |             |

| 3.1. IA3222B for Worldwide Telecom Compliance                          |             |

| 3.2. Bill of Materials                                                 |             |

| 3.3. Application Schematic (Legacy TBR21 Current-Limit Support)        | 20          |

| 3.4. Bill of Materials (Legacy TBR21 Current-Limit Support)            | 21          |

| 4. Overview                                                            | 23          |

| 4.1. Analog Interface                                                  | 23          |

| 4.2. Isolation Barrier                                                 | 23          |

| 4.3. International Compliance                                          | 23          |

| 4.4. Serial Interface                                                  | 23          |

| 4.5. International Programming Sequence                                | 24          |

| 4.6. Hook Switch Control                                               |             |

| 4.7. Line Overload Protection                                          | 24          |

| 4.8. DC Termination (Voltage Drop vs. Loop Current)                    | 24          |

| 4.9. AC Termination (Line Impedance Matching)                          |             |

| 4.10. DTMF Dialing                                                     |             |

| 4.11. Pulse Dialing                                                    |             |

| 4.12. Caller ID                                                        |             |

| 4.13. Power-Down Mode                                                  | 24          |

| 5. Functional Description                                              |             |

| 5.1. Component Discussion                                              |             |

| 5.2. Sample Layout                                                     |             |

| 5.3. Layout Guidelines                                                 |             |

| 5.4. Interfacing the IA3223                                            |             |

| 5.5. Interfacing Examples                                              |             |

| 6. Line Monitoring                                                     | 29          |

| 6.1. On-Hook Line Status Theory of Operation                           |             |

| 6.2. Ringing                                                           |             |

| 6.3. Line Reversal                                                     |             |

| 6.4. Line Activity                                                     |             |

| 6.5. Line in Use and Line Disconnect                                   |             |

| 6.6. The LineStat Pin as Interrupt (On Hook)                           |             |

| 6.7. Audio Snooping                                                    |             |

| 6.8. Theory of Operation- Off-Hook Line Status                         | 32          |

| 6.9. Line Drop                                                         |             |

| 6.10. Parallel Pickup                                                  |             |

| 6.11. The LineStat Pin as Interrupt (Off Hook)                         |             |

| 6.12. Measuring Loop-Current Changes through the Received Audio Signal |             |

| 6.13. Surges, Isolation, and EMC                                       |             |

# IA3222/23

| 6.14. Lightning Surges                          | 33  |

|-------------------------------------------------|-----|

| 6.15. ESD Surges                                | 35  |

| 6.16. Overvoltage Surges                        | 35  |

| 6.17. Power-Line Cross                          | 36  |

| 6.18. Common-Mode Noise from the Mains Supply   | 36  |

| 6.19. EMC                                       | 37  |

| 6.20. RF Susceptibility                         | 37  |

| 6.21. Return Loss                               | 37  |

| 7. Registers                                    | 38  |

| 7.1. Register Map*                              | 38  |

| 7.2. Control Register                           | 38  |

| 7.3. Line-Side Programming Registers            | 39  |

| 7.4. Threshold Register                         |     |

| 7.5. Line Status Register (Read Only)*          | 40  |

| 7.6. Divider Register                           | 41  |

| 8. Suggested Country Settings                   |     |

| 9. Pin Description—IA3223 System-Side QSOP-16   | 44  |

| 10. Pin Description—IA3223A System-Side QSOP-20 |     |

| 11. Pin Description—IA3222B Line-Side MSOP-10   | 46  |

| 12. Ordering Guide                              |     |

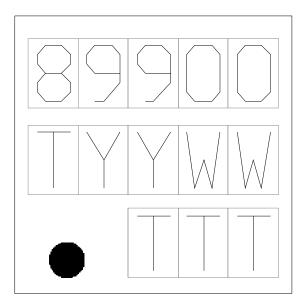

| 13. Package Markings (Top Markings)             |     |

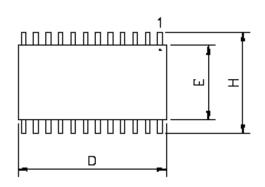

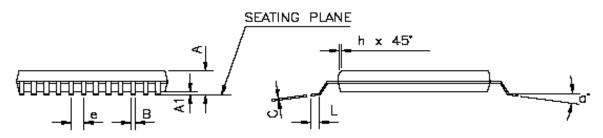

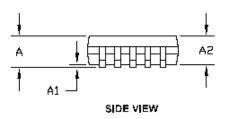

| 14. Package Outline: QSOP-16 and QSOP-20        |     |

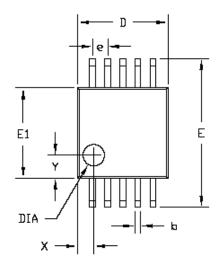

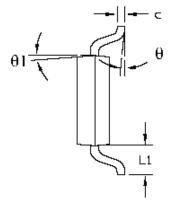

| 15. Package Outline: MSOP-10                    |     |

| Document Change List                            |     |

| Contact Information                             | .54 |

# 1. Electrical Specifications

**Table 1. Recommended Operating Conditions**

| Symbol             | Parameter                                               | Min  | Тур | Max    | Unit              |

|--------------------|---------------------------------------------------------|------|-----|--------|-------------------|

|                    | Operating temperature                                   | -25  |     | 85     | °C                |

| V <sub>DD</sub>    | Power-supply voltage                                    | 3.0  | 3.3 | 3.6    | V                 |

| V <sub>IL</sub>    | Logic-low input voltage                                 | 0    | _   | 35     | % V <sub>DD</sub> |

| V <sub>IH</sub>    | Logic-high input voltage                                | 65   | _   | 100    | % V <sub>DD</sub> |

| V <sub>ACREF</sub> | Optional AC <sub>REF</sub> pin reference voltage*       | 1.2  | _   | 1.8    | V                 |

|                    | AC reference capacitor (pin left open)*                 | _    | 100 | _      | nF                |

| C1                 | External capacitor #1                                   | _    | 10  | _      | nF                |

| C2                 | External capacitor #2                                   | _    | 220 | _      | nF                |

|                    | RX <sub>OUT</sub> load resistance                       | 2    | _   | _      | kΩ                |

|                    | RX <sub>OUT</sub> load capacitance                      | _    | _   | 200    | pF                |

|                    | Loop current                                            | 20   | _   | 120    | mA                |

|                    | Loop current, degraded performance                      | 14   | _   | 130    | mA                |

|                    | Line voltage for Caller ID power                        | 15   | _   | 70     | V                 |

|                    | Internal sampling rate based on external clock          | 57.6 | _   | 83.333 | kHz               |

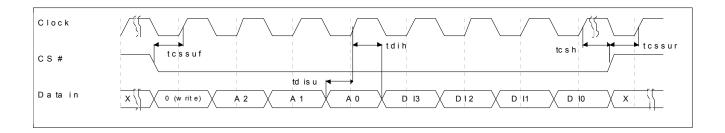

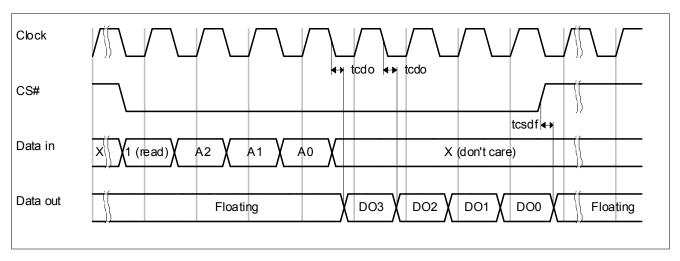

| tck                | Serial clock period                                     | 25   | _   | _      | ns                |

| tcssuf             | Chip Select fall to clock rising edge setup time        | 12   | _   | _      | ns                |

| tcssur             | Chip Select rise to clock rising edge setup time        | 12   | _   | _      | ns                |

| tcsh               | Chip Select rise or fall to clock rising edge hold time | 8    | _   | _      | ns                |

| tdisu              | Data in to clock rising edge setup time                 | 12   | _   | _      | ns                |

| tdih               | Data in to clock rising edge hold time                  | 8    | _   | _      | ns                |

|                    | IA3222 power derating over 25 °C ambient                | _    | 6   | _      | mW/ °C            |

\*Note: The ACREF pin may be left open, in which case this internal bias voltage needs to be decoupled to the audio ground by means of a 100 nF capacitor. Refer to Table 3, "DC Characteristics," on page 6 for more information on driving the ACREF pin. Also refer to "5.5. Interfacing Examples" for alternate ways of driving the ACREF pin.

**Table 2. Absolute Maximum Ratings**

| Parameter                                    | Min  | Max                   | Units |

|----------------------------------------------|------|-----------------------|-------|

| Junction operating and storage temperature   | -40  | 150                   | °C    |

| ESD (human body model)                       | _    | 2                     | kV    |

| Power-supply voltage                         | -0.5 | 7                     | V     |

| Voltage at any pin                           | -0.5 | V <sub>DD</sub> + 0.5 | V     |

| Current at any input or output (System Side) | -100 | 100                   | mA    |

| Loop Current (IA3222)                        | _    | 150                   | mA    |

**Table 3. DC Characteristics**

| Parameter                          | Conditions                                           | Min  | Тур  | Max  | Unit             |

|------------------------------------|------------------------------------------------------|------|------|------|------------------|

| Logic input current                |                                                      | -10  | _    | 10   | μA               |

| Logic input hysteresis             |                                                      | _    | 240  | _    | mV               |

| Logic output low voltage           | I <sub>OL</sub> = -4 mA                              | _    | _    | 0.4  | V                |

| Logic output high voltage          | I <sub>OH</sub> = 4 mA                               | 0.8  | _    | _    | V <sub>DD</sub>  |

|                                    | RTH[1:0] = 00                                        | 10   | _    | 20   | V <sub>RMS</sub> |

| Diam data stian through ald        | RTH[1:0] = 01                                        | 12.5 | _    | 25   | V <sub>RMS</sub> |

| Ring-detection threshold           | RTH[1:0] = 10                                        | 15   | _    | 30   | V <sub>RMS</sub> |

|                                    | RTH[1:0] = 11                                        | 20   | _    | 40   | V <sub>RMS</sub> |

| Voltage at AC <sub>REF</sub> pin   | Pin left open                                        | 1.42 | 1.50 | 1.58 | V                |

| AC <sub>REF</sub> input resistance | Small signal                                         | 42   | 60   | 78   | kΩ               |

| AC <sub>REF</sub> input current    | Sink or source                                       | _    | 10   | _    | μA               |

| Pull-down resistance               | ExtClk, OfHk inputs, V = 0.65 V <sub>DD</sub>        | 80   | _    | 300  | kΩ               |

| Pull-up resistance                 | LineStat open-drain output, V = 0.35 V <sub>DD</sub> | 80   | _    | 300  | kΩ               |

|                                    | Off hook, internal clock                             | _    | 7.9  | _    | mA               |

|                                    | Off hook, external clock                             | _    | 6.2  | _    | mA               |

| Power supply current               | On hook                                              | _    | 3.4  | _    | mA               |

|                                    | Power down, no external clock                        | _    | 2    | _    | μΑ               |

|                                    | Normal headroom, TBR21 mode                          | _    | 0.95 | _    | mV/mA            |

| Loop-current sensor gain           | All other headroom and impedance modes               | _    | 1.15 | _    | mV/mA            |

**Table 4. AC Characteristics**

| Symbol     | Parameter                                                           | Min  | Тур  | Max  | Unit |

|------------|---------------------------------------------------------------------|------|------|------|------|

| tcdo       | Clock falling edge to Data Out valid from driven or floating state* | _    | 12   | 20   | ns   |

| tcsdf      | Chip Select disabled to Data Out floating*                          | _    | 12   | 20   | ns   |

|            | Internal sampling rate based on internal clock                      | 67.2 | 73.4 | 82.8 | kHz  |

| *Note: Loa | id = 50 pF                                                          |      |      |      |      |

Figure 1. Serial Interface Write-Cycle Timing Diagram (Data Output Pin Floating)

Figure 2. Serial Interface Read-Cycle Timing Diagram

**Table 5. Off-Hook Receiver Performance**

| Parameter                                       | Conditions                                                          | Min.       | Тур. | Max. | Unit            |

|-------------------------------------------------|---------------------------------------------------------------------|------------|------|------|-----------------|

| Idle channel noise referred to Tip and Ring     | 300–3400 Hz, 600 $\Omega$ , internal clock                          | _          | -85  | _    | dBm             |

| Total harmonic distortion                       | 1 kHz, –7 dBm, normal or high headroom                              | _          | -76  | _    | dB              |

| Gain from Tip and Ring to RX <sub>OUT</sub> pin | 1 kHz (symmetrical around AC <sub>REF</sub> ), high headroom        | _          | -3   | _    | dB              |

| Gain from Tip and Ring to RX <sub>OUT</sub> pin | 1 kHz (symmetrical around AC <sub>REF</sub> ), other headrooms      | _          | 0    | _    | dB              |

|                                                 | Sine wave, high headroom, referenced to 600 $\boldsymbol{\Omega}$   | 0          | _    | _    | dBm             |

| Description of the second                       | Sine wave, normal headroom, referenced to 600 $\boldsymbol{\Omega}$ | -3         | _    | _    | dBm             |

| Receiver power headroom                         | Sine wave, low headroom, referenced to 600 $\boldsymbol{\Omega}$    | -3         | _    | _    | dBm             |

|                                                 | Sine wave, lowest headroom, referenced to 600 $\boldsymbol{\Omega}$ | <b>-</b> 5 | _    | _    | dBm             |

| Maximum level at RX <sub>OUT</sub> pin          | 1 kHz (symmetrical around AC <sub>REF</sub> )                       | _          | 1.55 | _    | V <sub>PP</sub> |

|                                                 | 1 kHz, 100 mV $_{\rm PP}$ at V $_{ m DD}$ , high headroom           | _          | -84  | _    | dBV             |

| Power-supply induced noise referred             | 1 kHz, 100 mV $_{\rm PP}$ at V $_{\rm DD}$ , other headrooms        | _          | -87  | _    | dBV             |

| to Tip and Ring                                 | f > 3400 Hz, dc coupled, high headroom                              | _          | -66  | _    | dBV             |

|                                                 | f > 3400 Hz, dc coupled, other headrooms                            | _          | -69  | _    | dBV             |

| Longitudinal balance                            | f = 1000 Hz                                                         | _          | 99   | _    | dB              |

| Longitudinal balance                            | f = 3000 Hz                                                         | _          | 93   | _    | dB              |

Table 6. On-Hook Receiver (Caller ID) Performance at 48  ${

m V}_{

m DC}$

| Parameter                                         | Conditions                                                            | Min | Тур         | Max | Unit            |

|---------------------------------------------------|-----------------------------------------------------------------------|-----|-------------|-----|-----------------|

| Caller ID noise referred to Tip and Ring          | 400–3000 Hz, internal clock                                           | _   | -48         | _   | dBV             |

| Caller ID distortion                              | 1 kHz, 100 mV <sub>RMS</sub> ,<br>normal or high headroom             | _   | -37         | _   | dB              |

| Calley ID agin. The and Dinaste AC                | 1 kHz, high gain setting                                              | _   | 0.5         | _   | dB              |

| Caller ID gain, Tip and Ring to AC <sub>REF</sub> | 1 kHz, low gain setting                                               | _   | -4.5        | _   | dB              |

| M · 1 / T 15:                                     | 1 kHz, high gain setting                                              | _   | -3          | _   | dBm             |

| Maximum level at Tip and Ring                     | 1 kHz, low gain setting                                               | _   | +3          | _   | dBm             |

| Maximum level at Rx pin                           | 1 kHz, high or low gain setting                                       | _   | 1.55        | _   | V <sub>PP</sub> |

| Power-supply induced noise referred to            | 1 kHz, 100 mV <sub>PP</sub> at V <sub>DD</sub> ,<br>high gain setting | _   | <b>–</b> 55 | _   | dBV             |

| Tip and Ring                                      | 1 kHz, 100 mV <sub>PP</sub> at V <sub>DD</sub> ,<br>low gain setting  | _   | -50         | _   | dBV             |

| Common-mode rejection                             | 120 Hz                                                                | 120 | _           | _   | dB              |

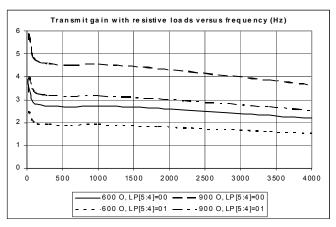

**Table 7. Transmitter Performance**

| Parameter                                                         | Conditions                                                                                                           | Min.       | Тур. | Max. | Unit |

|-------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------|------------|------|------|------|

| Idle channel noise referred to Tip and Ring                       | 300–3400 Hz, 600 $\Omega$ , internal clock                                                                           | _          | -82  | l    | dBm  |

| Total harmonic distortion                                         | 1 kHz, 3 dB below clipping level, normal or high headroom                                                            |            | -78  |      | dB   |

| Gain from TX <sub>IN</sub> pin to Tip and Ring                    | 1 kHz, 600 $\Omega$ , referenced to AC <sub>REF</sub> , high headroom                                                |            | 9    |      | dB   |

| Gair from TAIN pinto Tip and King                                 | 1 kHz, 600 $\Omega$ , referenced to AC <sub>REF</sub> , other headrooms                                              | _          | 6    |      | dB   |

| Part-to-part gain variation at 1 kHz,                             | Transmitter gain                                                                                                     |            | 0.5  |      | ±dB  |

| 600 $\Omega$ mode, normal headroom                                | Product of transmitter gain times receiver gain                                                                      |            | 0.5  | 1    | ±dB  |

|                                                                   | LP[5:4] = 00, 600 $\Omega$ load                                                                                      | 6.5        | _    | 1    | dBm  |

| Transmitter power headroom, sine wave*                            | LP[5:4] = 00, 900 $\Omega$ load                                                                                      | 5.5        | _    | _    | dBV  |

|                                                                   | LP[5:4] = 01, 600 Ω load                                                                                             | 3          | _    | _    | dBm  |

|                                                                   | LP[5:4] = 01, 900 Ω load                                                                                             | 2          | _    | _    | dBV  |

|                                                                   | LP[5:4] = 01, Australia or TBR21 load                                                                                | 2          | _    | _    | dBV  |

|                                                                   | LP[5:4] = 01, New Zealand load                                                                                       | 1          | _    | _    | dBV  |

|                                                                   | LP[5:4] = 10, 600 Ω load, 400–3400 Hz                                                                                | <b>–</b> 5 | _    |      | dBm  |

|                                                                   | LP[5:4] = 10, 600 $\Omega$ load with bootstrap,<br>400–3400 Hz                                                       | -1         | _    | _    | dBm  |

|                                                                   | LP[5:4] = 11, 600 Ω load, 400–3400 Hz                                                                                | <b>-</b> 9 | _    | _    | dBm  |

|                                                                   | LP[5:4] = 11, 600 $\Omega$ load with bootstrap,<br>400–3400 Hz                                                       | -3         | _    |      | dBm  |

|                                                                   | LP[5:4] = 11, 600 $\Omega$ load with bootstrap, DTMF tones                                                           | -1         | _    |      | dBm  |

| TX <sub>IN</sub> pin input resistance                             |                                                                                                                      | 35         | 50   | 65   | kΩ   |

| Input common-mode rejection,                                      | 300-3400 Hz, dc-coupled                                                                                              | _          | 40   | _    | dB   |

| defined as:<br>(V(TX <sub>IN</sub> ) + V(AC <sub>REF</sub> )) / 2 | f > 3400 Hz, dc-coupled                                                                                              | 40         | _    |      | dB   |

|                                                                   | 1 kHz, 100 mV $_{\rm PP}$ at V $_{ m DD}$ , high headroom                                                            | _          | -86  | _    | dBV  |

| Power-supply-induced noise referred to Tip and Ring (SGAIN = 0)   | 1 kHz, 100 mV $_{\mbox{\footnotesize{PP}}}$ at $\mbox{\footnotesize{V}}_{\mbox{\footnotesize{DD}}},$ other headrooms |            | -89  |      | dBV  |

|                                                                   | f > 3400 Hz, dc-coupled, high headroom                                                                               | -56        | _    | _    | dBV  |

|                                                                   | f > 3400 Hz, dc-coupled, other headrooms                                                                             | -59        | _    |      | dBV  |

| Longitudinal balance                                              | f = 1000 Hz or f = 3000 Hz                                                                                           | 90         | _    | _    | dB   |

\*Note: The bootstrap circuit shown in the application circuit (R18, C16, and Q6) is optional. Its function is to increase the transmit headroom voltage at the low and lowest headroom settings. Those settings should be used only when the dc voltage needs to be minimized for low-voltage countries, such as Japan, Malaysia, etc.

**Table 8. Line-Side Characteristics**

| Parameter                                               | Conditions                                            | Min | Тур  | Max | Unit |

|---------------------------------------------------------|-------------------------------------------------------|-----|------|-----|------|

| Self-regulated supply voltage                           |                                                       | _   | 2.47 |     | V    |

| Current protection threshold                            |                                                       | 130 | 170  | 210 | mA   |

| On-hook voltage-protection threshold                    |                                                       | 110 | 145  | 210 | V    |

| Temperature-shutdown threshold                          | Loop current = 130 mA                                 | 136 | 146  | 156 | °C   |

| On-hook dc resistance, Tip to Ring                      | 5.6 M $\Omega$ voltage-sensing resistors              | 5   |      |     | МΩ   |

| Ringer equivalent load                                  |                                                       | _   | _    | 0.1 | REN  |

|                                                         | 600 $\Omega$ impedance mode and reference load        | 20  | 30   | l   | dB   |

|                                                         | $600~\Omega$ + 1 μF impedance mode and reference load | 20  | 30   | _   | dB   |

| Return loss at 1 kHz (typical) or 300–3400 Hz (minimum) | 900 $\Omega$ impedance mode and reference load        | 20  | 30   | _   | dB   |

|                                                         | 900 $\Omega$ + 1 μF impedance mode and reference load | 20  | 30   | _   | dB   |

|                                                         | Australia impedance mode and reference load           | 17  | 27   |     | dB   |

|                                                         | New Zealand impedance mode and reference load         | 20  | 26   | _   | dB   |

|                                                         | TBR21 impedance mode and reference load               | 17  | 27   | _   | dB   |

|                                                         | 600 $\Omega$ impedance mode and reference load        | 20  | 30   | _   | dB   |

|                                                         | 600 Ω + 1 μF impedance mode and reference load        | 20  | 30   | _   | dB   |

|                                                         | 900 $\Omega$ impedance mode and reference load        | 20  | 30   | _   | dB   |

| Echo return loss, ITU-T G.122 method                    | 900 Ω + 1 μF impedance mode and reference load        | 20  | 28   | _   | dB   |

|                                                         | Australia impedance mode and reference load           | 20  | 25   | _   | dB   |

|                                                         | New Zealand impedance mode and reference load         | 20  | 26   | _   | dB   |

|                                                         | TBR21 impedance mode and reference load               | 20  | 25   | _   | dB   |

# IA3222/23

**Table 8. Line-Side Characteristics (Continued)**

| Parameter                               | Conditions                                                       | Min | Тур         | Max  | Unit |

|-----------------------------------------|------------------------------------------------------------------|-----|-------------|------|------|

| Transhybrid distortion referred to line | 600 $\Omega$ load, –10 dBm signal, normal or high headroom       | _   | <b>-</b> 91 | _    | dBm  |

| Tip-Ring voltage                        | I <sub>DD</sub> = 20 mA, no current limit,<br>lowest headroom    | _   | 5.85        | 6    | ٧    |

|                                         | I <sub>DD</sub> = 20 mA, no current limit,<br>low headroom       | _   | 6.4         | 7    | ٧    |

|                                         | I <sub>DD</sub> = 20 mA, no current limit,<br>normal headroom    | _   | 7.8         | 9    | ٧    |

|                                         | I <sub>DD</sub> = 20 mA, no current limit,<br>high headroom      | _   | 9           | 10   | ٧    |

|                                         | I <sub>DD</sub> = 42 mA, TBR21 current limit,<br>normal headroom | _   | _           | 14.5 | ٧    |

|                                         | I <sub>DD</sub> = 50 mA, TBR21 current limit,<br>normal headroom | _   | _           | 40   | V    |

| Loop-current limit                      | TBR21 legacy mode, 50 V, 230 $\Omega$ feed                       | _   |             | 60   | mA   |

# 2. Typical Performance Characteristics

Figure 3. Transmit Gain with Resistive Loads

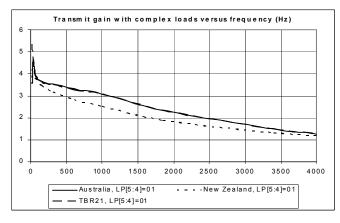

Figure 6. Transmit Gain with Complex Loads

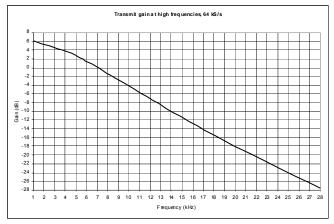

Figure 4. Transmit Gain at High Frequencies (600  $\Omega$ )

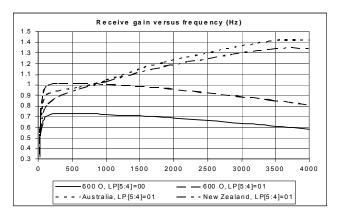

Figure 7. Receive Gain versus Frequency

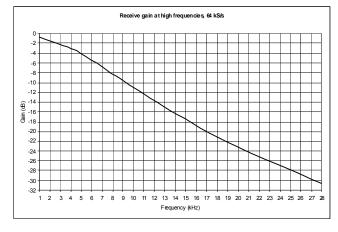

Figure 5. Receive Gain at High Frequencies (600 W)

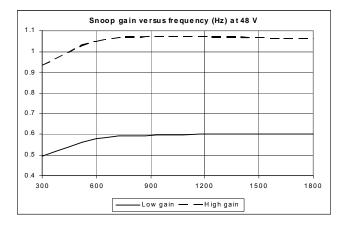

Figure 8. Snoop Gain versus Frequency

Figure 9. Snoop Gain vs. Line DC Voltage

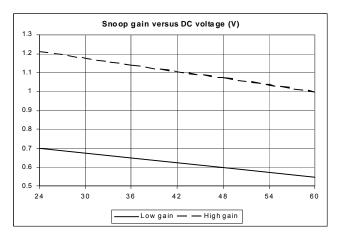

Figure 10. DC Voltage vs. Current, No Regulation

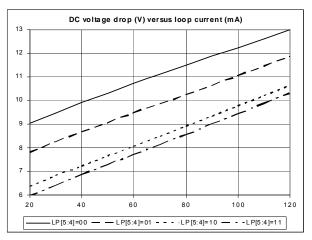

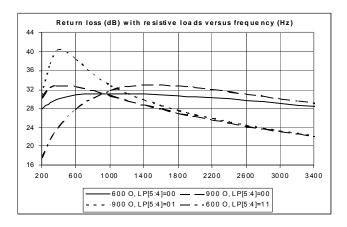

Figure 11. Return Loss for Resistive Modes

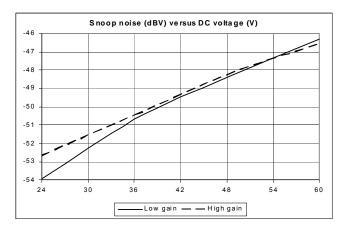

Figure 12. Snoop Noise vs. Line DC Voltage

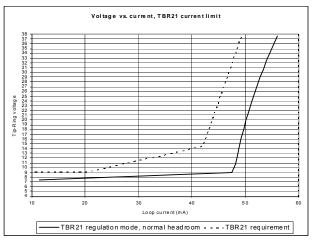

Figure 13. DC Voltage vs. Current, TBR21 Regulation

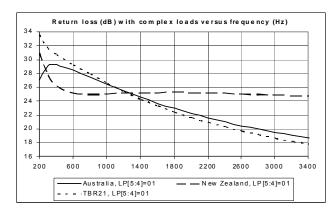

Figure 14. Return Loss for Complex Modes

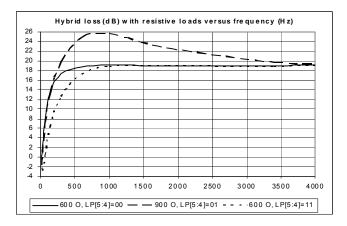

Figure 15. Transhybrid Loss for Resistive Modes

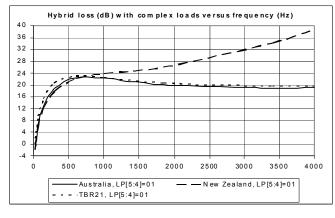

Figure 18. Transhybrid Loss for Complex Modes

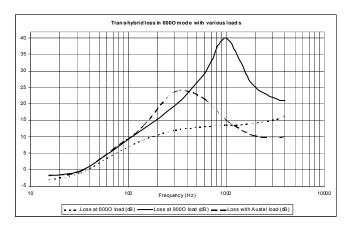

Figure 16. Transhybrid Loss in 600  $\Omega$  Mode with Various Loads

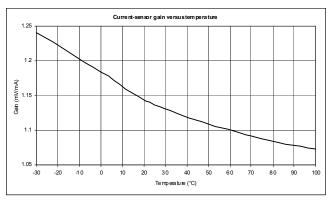

Figure 19. Current Sensor Gain vs. Temperatures

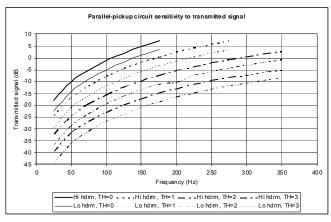

Figure 17. Parallel Pickup Sensitivity to Transmitted Signals

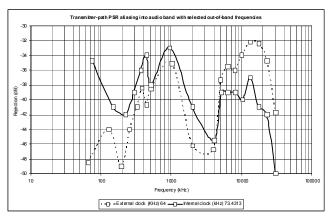

Figure 20. Transmitter-Path PSR Aliasing into Audio Band with Selected Out-of-Band Frequencies

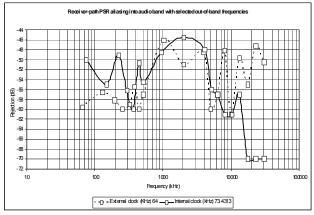

Figure 21. Receiver Path PSR Aliasing into Audio Band with Selected Out-of-Band Frequencies

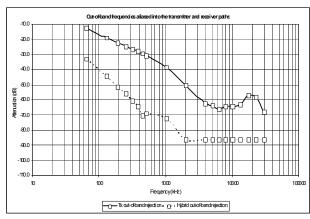

Figure 24. Aliasing into Audio Band (Signals at Selected Out-of-Band Frequencies Injected into TX Pin)

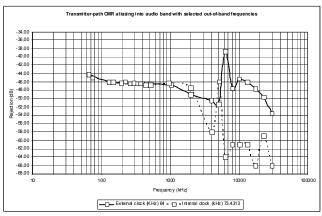

Figure 22. Transmitter-Path CMR Aliasing into Audio Band with Selected Out-of-Band Frequencies

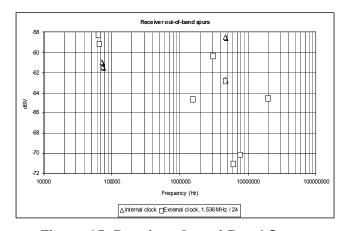

Figure 25. Receiver Out-of-Band Spurs

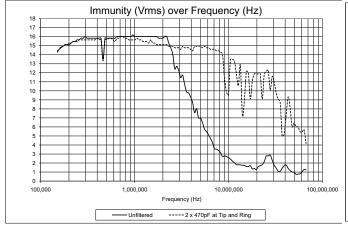

Figure 23. Immunity (Vrms) Over Frequency (Hz)

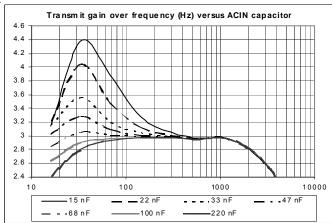

Figure 26. Transmit Gain vs. ACIN Capacitor

# 3. Applications

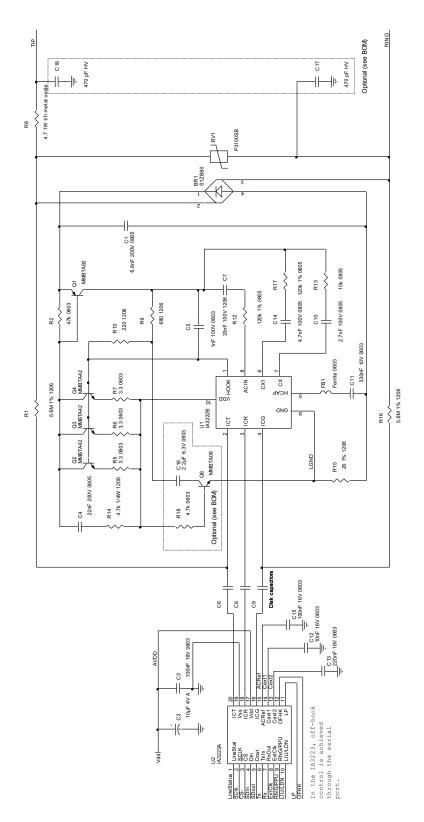

# 3.1. IA3222B for Worldwide Telecom Compliance

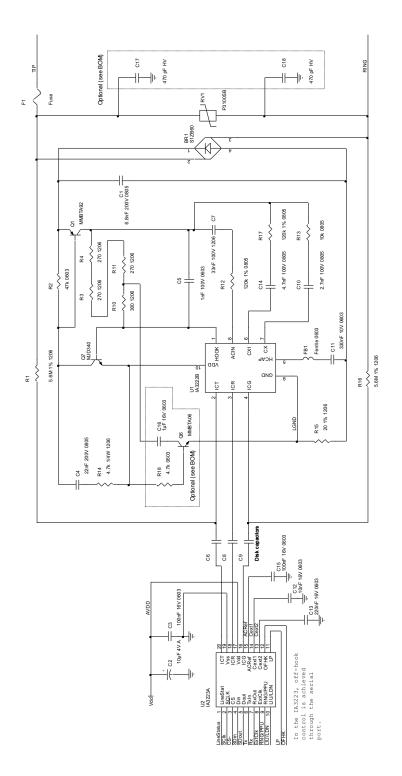

Figure 27. IA3222B Application Schematic

#### 3.2. Bill of Materials

Table 9. IA3222/23 Bill of Materials

| Qty | Ref        | Ref Part                                              |                        | Mfr        |  |

|-----|------------|-------------------------------------------------------|------------------------|------------|--|

| 1   | BR1        | Rectifier bridge 400 V                                | S1ZB60                 | Shindengen |  |

| 1   | C1         | 6.8 nF 200 V 0805                                     | MCCI682K2NR            | SMEC       |  |

| 1   | C2         | 10 μF 4 V                                             | EEE-1CA100SR           | Panasonic  |  |

| 2   | C3, C15    | 100 nF 16 V 0603                                      | C0603X7R160-<br>104MNP | Venkel     |  |

| 1   | C4         | 22 nF 200 V 0805 C0805X<br>223K                       |                        | Venkel     |  |

| 1   | C5         | 1 nF 100 V 0603 C0603X7R101-<br>102MNP                |                        | Venkel     |  |

| 3   | C6, C8, C9 | isolation bridge capacitors, drawn on PCB             |                        |            |  |

| 1   | C7         | 33 nF 100 V 1206 C1206X7R10<br>333KNP                 |                        | Venkel     |  |

| 1   | C11        | 330 nF 10 V 0603 <sup>1</sup>                         | C0603X7R100-<br>334KNP | Venkel     |  |

| 1   | C12        | 10 nF 16 V 0603 C0603X7F<br>103MN                     |                        | Venkel     |  |

| 1   | C13        | 220 nF 16 V 0603                                      | C0603X7R160-<br>224MNP | Venkel     |  |

| 1   | Q1         | PNP, 100 mA, 300 V, SOT23-BEC MMBTA92LT1              |                        | On Semi    |  |

| 3   | Q2, Q3, Q4 | NPN, 200mA, 300V, SOT23-BEC <sup>2,3</sup> MMBTA42LT1 |                        | On Semi    |  |

| 1   | RV1        | Sidactor, 275 V, D0-214AA P3100SBL                    |                        | Littelfuse |  |

| 2   | R1, R16    | 5.6 M Ω 1% 1206 CR1206-8W-<br>5904FT                  |                        | Venkel     |  |

| 1   | R2         | 47 kΩ 0603                                            | CR0603-16W-<br>473JT   | Venkel     |  |

| 3   | R5, R6, R7 | $3.3~\Omega~0603^{2,3}$                               | CR0603-16W-<br>3R3JT   | Venkel     |  |

| 1   | R9         | 680 Ω 1206                                            | CR1206-8W-<br>681JT    | Venkel     |  |

#### Notes

- 1. For optimal audio performance, C11 (0.33 uF & V>=10) should be an aluminum electrolytic capacitor with the positive end connected to HCAP through FB1. This is due to micro phonic noise that can be generated by a ceramic cap when the PCB is less than the typical 0.062" thickness and there are vibration sources in the application. EKMG500ELLR33ME11D is an appropriate alternative in this case.

- 2. If the loop current is never more than 60 mA, Q4 and R7 may be omitted, and R5 and R6 may be  $2.2 \Omega$ .

- 3. Do not replace Q2, Q3, Q4, R5, R6, and R7 with a single transistor of PZTA42 type. Power transistors with a higher gain-bandwidth product may be used, but often they are not cost-effective. Refer to the component discussion for more details.

- **4.** C10 and C14 need to be NPO if V.90 modem performance is required. Otherwise, it is more cost-effective to use X7R ceramic capacitors. Refer to "7.3. Line-Side Programming Registers" to determine whether C10 or C14 is required.

Table 9. IA3222/23 Bill of Materials (Continued)

| Qty    | ry Ref Part |                                                                                                                                                                                                   | Part #                | Mfr          |

|--------|-------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------|--------------|

| 1      | R10         | 220 Ω 1206                                                                                                                                                                                        | CR1206-8W-<br>221JT   | Venkel       |

| 1      | R12         | 120 kΩ 1% 0805                                                                                                                                                                                    | CR0805-10W-<br>1203FT | Venkel       |

| 1      | R14         | 4.7 kΩ 1206                                                                                                                                                                                       | CR1206-8W-<br>472JT   | Venkel       |

| 1      | R15         | 20 Ω 1% 1206                                                                                                                                                                                      | CR1206-8W-<br>20R0FT  | Venkel       |

| 2      | U1, U2      | DAA chipset                                                                                                                                                                                       | IA3222B, IA3223A      | Silicon Labs |

| Option | C16         | 2.2 µF 6.3 V 0603 (only if more signal headroom is needed at the low or lowest headroom setting)  C0603X7R6R 225KNP                                                                               |                       | Venkel       |

| Option | Q6          | MMBTA06 (only if more signal headroom is needed at the low or lowest headroom setting)  MMBTA06LT1                                                                                                |                       | On Semi      |

| Option | R18         | $\begin{array}{ccc} 4.7 \text{ k}\Omega  0603 & \text{CR0603-16W} \\ \text{(only if more signal headroom is needed at the low or} & 472 \text{JT} \\ \text{lowest headroom setting)} \end{array}$ |                       | Venkel       |

| Option | R8          | 4.7 $\Omega$ through-hole metal-oxide or other fusible resistor (only for UL 60950 or equivalent requirement)                                                                                     |                       | Panasonic    |

| Option | C10         | 2.7 nF 100V 0805 (Use only if C <sub>X</sub> is required.) <sup>4</sup> C0805X7R101-<br>272KNP                                                                                                    |                       | Venkel       |

| Option | R13         | 10 k $\Omega$ 0805 (Use only if C $_{\rm X}$ is required.) $^4$ CR0805-10W-103JT                                                                                                                  |                       | Venkel       |

| Option | C14         | 4.7 nF 100 V 0805 (Use only if C <sub>X1</sub> is required) <sup>4</sup> C0805X7R101-<br>472MNP                                                                                                   |                       | Venkel       |

| Option | R17         | 120 kΩ 1% 0805 (Use only if $C_{X1}$ is required.) <sup>4</sup> CR0805-1203F                                                                                                                      |                       | Venkel       |

| Option | FB1         | Ferrite bead, 0603, 600 $\Omega$ at 100 MHz (required for EN 55024 and equivalent immunity requirements)                                                                                          |                       | Taiyo Yuden  |

| Option | C17,C18     | 470 pF (required for EN 55024 and equivalent immunity requirements; voltage rating depends on safety requirements)  CS85-B2GA471KYNS                                                              |                       | TDK          |

#### Notes:

- 1. For optimal audio performance, C11 (0.33 uF & V>=10) should be an aluminum electrolytic capacitor with the positive end connected to HCAP through FB1. This is due to micro phonic noise that can be generated by a ceramic cap when the PCB is less than the typical 0.062" thickness and there are vibration sources in the application. EKMG500ELLR33ME11D is an appropriate alternative in this case.

- 2. If the loop current is never more than 60 mA, Q4 and R7 may be omitted, and R5 and R6 may be  $2.2~\Omega$ .

- **3.** Do not replace Q2, Q3, Q4, R5, R6, and R7 with a single transistor of PZTA42 type. Power transistors with a higher gain-bandwidth product may be used, but often they are not cost-effective. Refer to the component discussion for more details.

- **4.** C10 and C14 need to be NPO if V.90 modem performance is required. Otherwise, it is more cost-effective to use X7R ceramic capacitors. Refer to "7.3. Line-Side Programming Registers" to determine whether C10 or C14 is required.

## 3.3. Application Schematic (Legacy TBR21 Current-Limit Support)

TBR21 current limiting is no longer required in Europe but may still be required for certain countries, e.g. Algeria, Bahrain, Croatia, Estonia, Ghana, Ivory Coast, Lebanon, Morocco, and Turkey. This application circuit is also suitable for all other countries.

Figure 28. Legacy TBR21 Current-Limit Support Application Schematic

SILICON LABS

## 3.4. Bill of Materials (Legacy TBR21 Current-Limit Support)

Table 10. Legacy TBR21 Current-Limit Support Bill of Materials

| Qty | Ref         | Part                                      | Part #                 | Mfr        |  |

|-----|-------------|-------------------------------------------|------------------------|------------|--|

| 1   | BR1         | Rectifier bridge 400 V                    | S1ZB60                 | Shindengen |  |

| 1   | C1          | 6.8 nF 200 V 0805                         | MCCI682K2NR            | SMEC       |  |

| 1   | C2          | 10 μF 4 V                                 | EEE-1CA100SR           | Panasonic  |  |

| 2   | C3, C15     | 100 nF 16 V 0603                          | C0603X7R160-<br>104MNP | Venkel     |  |

| 1   | C4          | 22 nF 200 V 0805 C0805X7F<br>223KN        |                        | Venkel     |  |

| 1   | C5          | 1 nF 100 V 0603 C0603X7R101<br>102MNP     |                        | Venkel     |  |

| 3   | C6, C8, C9  | isolation bridge capacitors, drawn on PCB |                        |            |  |

| 1   | C7          | 33 nF 100 V 1206                          | C1206X7R101-<br>333KNP | Venkel     |  |

| 1   | C11         | 330 nF 10 V 0603 <sup>1</sup>             | C0603X7R100-<br>334KNP | Venkel     |  |

| 1   | C12         | 10 nF 16 V 0603                           | C0603X7R160-<br>103MNP | Venkel     |  |

| 1   | C13         | 220 nF 16 V 0603                          | C0603X7R160-<br>224MNP | Venkel     |  |

| 1   | Q1          | PNP, 100 mA, 300V, SOT23-BEC              | MMBTA92LT1             | On Semi    |  |

| 1   | Q7          | NPN, 300 V, D-PAK                         | MJD340                 | Fairchild  |  |

| 1   | RV1         | Sidactor, 275 V, DO-214AA P3100SBL        |                        | Littelfuse |  |

| 2   | R1, R16     | 5.6 MΩ 1% 1206 CR1206-8W-5904FT           |                        | Venkel     |  |

| 1   | R2          | 47 kΩ 0603                                | CR0603-16W-473JT       | Venkel     |  |

| 3   | R3, R4, R11 | 270 Ω 1206                                | CR1206-8W-271JT        | Venkel     |  |

| 1   | R10         | 300 Ω 1206                                | CR1206-8W-301JT        | Venkel     |  |

| 1   | R12         | 120 kΩ 1% 0805 CR0805-10W-<br>1203FT      |                        | Venkel     |  |

| 1   | R14         | 4.7 kΩ 1206 CR1206-8W-472JT               |                        | Venkel     |  |

#### Notes:

- 1. For optimal audio performance, C11 (0.33 uF & V>=10) should be an aluminum electrolytic capacitor with the positive end connected to HCAP through FB1. This is due to micro phonic noise that can be generated by a ceramic cap when the PCB is less than the typical 0.062" thickness and there are vibration sources in the application. United Chemi-Con EKMG500ELLR33ME11D is an appropriate alternative in this case.

- **2.** C10 and C14 need to be NPO if V.90 modem performance is required. Otherwise, it is more cost effective to use X7R ceramic capacitors. Refer to "7.3. Line-Side Programming Registers" to determine whether C10 or C14 is required.

Table 10. Legacy TBR21 Current-Limit Support Bill of Materials (Continued)

| Qty Ref |         | Part                                                                                                               | Part #                 | Mfr         |  |

|---------|---------|--------------------------------------------------------------------------------------------------------------------|------------------------|-------------|--|

| 1       | R15     | 20 Ω 1% 1206                                                                                                       | CR1206-8W-20R0FT       | Venkel      |  |

| 2       | U1, U2  | DAA Chipset                                                                                                        | IA3222B, IA3223A       | Siicon Labs |  |

| Option  | C16     | 1 µF 16 V 0603 (only if more signal headroom is needed at the low or lowest headroom setting)                      | C0603X7R160-<br>105KNP | Venkel      |  |

| Option  | Q6      | MMBTA06 (only if more signal headroom is needed at the low or lowest headroom setting)                             | MMBTA06LT1             | On Semi     |  |

| Option  | R18     | 4.7 k $\Omega$ 0603 (only if more signal headroom is needed at the low or lowest headroom setting)                 |                        | Venkel      |  |

| Option  | F1      | Fuse (only for UL 60950 or equivalent requirement)                                                                 |                        |             |  |

| Option  | C10     | 2.7 nF 100 V 0805 (Use only if $C_X$ is required) <sup>2</sup>                                                     | C0805X7R101-<br>272KNP | Venkel      |  |

| Option  | R13     | 10 kΩ 0805 (Use only if $C_X$ is required.) <sup>2</sup>                                                           | CR0805-10W-103JT       | Venkel      |  |

| Option  | C14     | 4.7 nF 100 V 0805 (Use only if C <sub>X1</sub> is required.) <sup>2</sup> C0805X7F 472MN                           |                        | Venkel      |  |

| Option  | R17     | 120 kΩ 1% 0805 (Use only if $C_{X1}$ is required.) <sup>2</sup> CR0805-1 1203F                                     |                        | Venkel      |  |

| Option  | FB1     | Ferrite bead, 0603, 600 $\Omega$ at 100 MHz (required for EN 55024 and equivalent immunity requirements)           | BK1608HS601-T          | Taiyo Yuden |  |

| Option  | C17,C18 | 470 pF (required for EN 55024 and equivalent immunity requirements; voltage rating depends on safety requirements) | CS85-<br>B2GA471KYNS   | TDK         |  |

#### Notes:

- 1. For optimal audio performance, C11 (0.33 uF & V>=10) should be an aluminum electrolytic capacitor with the positive end connected to HCAP through FB1. This is due to micro phonic noise that can be generated by a ceramic cap when the PCB is less than the typical 0.062" thickness and there are vibration sources in the application. United Chemi-Con EKMG500ELLR33ME11D is an appropriate alternative in this case.

- **2.** C10 and C14 need to be NPO if V.90 modem performance is required. Otherwise, it is more cost effective to use X7R ceramic capacitors. Refer to "7.3. Line-Side Programming Registers" to determine whether C10 or C14 is required.

## 4. Overview

The chipset provides a low-cost, worldwide-compliant telephone line interface. Due to its high level of integration, only a few external components are required for operation. Its patented isolation bridge technology eliminates the need for costly and bulky transformers yet still ensures a high level of isolation between the phone line and the system side.

## 4.1. Analog Interface

The DAA is easily interfaced using single-ended transmitters and receivers. An extra input pin can be used to set the dc reference, thus facilitating an interface with or without coupling capacitors. Refer to the applications section below for more details.

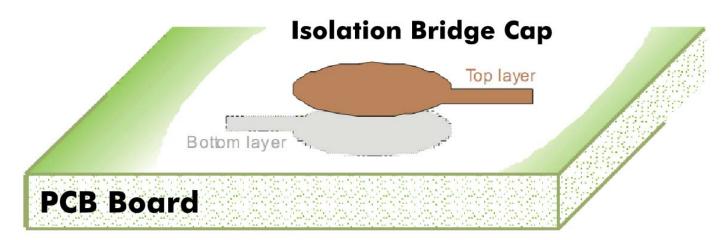

#### 4.2. Isolation Barrier

In most cases, equipment meant to be connected to the Public Switch Telephone Network must comply with specific safety requirements, including the implementation of a high-voltage isolation barrier between the telephone line side and the system side. Various standards require the isolation barrier to withstand from 1000 to 3000VAC. The chipset implements a high-voltage isolation barrier between the IA3223 codec and its IA3222 line-side device by means of its patented isolation bridge technology. Where typical designs use costly transformers or optocouplers, isolation bridge reduces the total bill of materials cost by embedding high-voltage capacitors in the PCB. This unique technique allows for virtually zero-cost capacitors.

PCB board material, thickness, trace width, and pad dimensions determine the capacitance achieved by this technique. The IA3222/IA3223 requires three 0.7 pF (nominal) capacitors and is designed to operate over the wide variations seen in standard PCB materials.

The application requires three PCB capacitors whose diameters range typically from 140 to 190 mils depending on the thickness of the board.

### 4.3. International Compliance

The chipset can be programmed to meet the variety of telecommunication requirements and standards worldwide through the serial loading of two registers.

#### 4.4. Serial Interface

The IA3222/IA3223 can be programmed using a simple asynchronous serial protocol independent of the audio path.

When  $\overline{CS}$  is low (active), the first clock rising edge latches the read or write command. The next three clock edges latch a three-bit register address. The next four clock rising edges serially shift a four-bit data word in, or the next four clock falling edges serially shift a four-bit data word out, depending on the status of the read/write command. Refer to the timing diagrams in the specification section for more details on the serial interface.

## 4.5. International Programming Sequence

International programming options are loaded into the system side and updated to the line side upon any of the following events:

- Register loading if the line side is in the off-hook state

- When the line side is made to go off hook

- When the line side recovers from a line interruption

#### 4.6. Hook Switch Control

The DAA is set to on-hook or off-hook by writing the OFH bit in the control register through the serial interface or through the use of the OFHK pin if using the IA3223A (QSOP-20).

#### 4.7. Line Overload Protection

The chipset provides a built-in line-overload protection circuit to protect the IA3222 line-side device from unusual telephone line conditions, which can result in excessive voltage or current conditions. If the IA3222 senses an excessive line voltage (about 100 V) when on-hook, it will not go off-hook even when an off-hook state is set in the control register. If the IA3222 senses an excessive loop current (about 170 mA) when off-hook, it will immediately go on-hook. This results in oscillation since, in this case, the IA3222 still sees an off-hook command and, therefore, keeps trying to go back off-hook. While a fault condition exists, the LD status bit is high.

## 4.8. DC Termination (Voltage Drop vs. Loop Current)

The chipset offers four main dc termination modes and current-limiting support specific for legacy TBR21 countries. Since TBR21 has been superseded by ES 203 021, European countries no longer require on-current limiting. The four main dc termination modes ensure that any country's I/V curve requirement can be met. The maximum transmit level is different for each setting.

Legacy TBR21 (current limiting) support is possible but not recommended since so few countries require it and the standard has been superseded. In order to meet TBR21 current limiting requirements, a DAA needs to dissipate 2 W safely. In the IA3222/3223 application, about half of this power is dissipated in R3, R4, R10, and R11, and the other half in the NPN transistor.

## 4.9. AC Termination (Line Impedance Matching)

The chipset offers several different ac terminations selectable through the serial port. These ac terminations can be combined with any dc termination selected to address a country's loop interface requirements.

#### 4.10. DTMF Dialing

DTMF dialing is controlled by the host, and only a few parameters in the IA3223, such as the gain and maximum transmission level, need to be set prior to dialing.

#### 4.11. Pulse Dialing

Pulse dialing is accomplished by going on-hook and off-hook repeatedly to generate make and break pulses. It is the host's responsibility to implement the timing related to pulse dialing, such as make/break times and ratio, interdigit pause, and pulses per second. The IA3222 meets international "spark quenching" requirements.

#### 4.12. Caller ID

When the device is on-hook, the Caller ID audio signal is available at the receiver output pin of the IA3223. This function is achieved while maintaining the high on-hook impedance required by telecom regulations. The gain can be set high (0 dB) for normal operation or low (–6 dB) for DTMF monitoring.

#### 4.13. Power-Down Mode

In order to reduce power consumption, it is possible to set the IA3223 to power-down mode. In this state, the device will not go off-hook or monitor the line.

# 5. Functional Description

## 5.1. Component Discussion

The application schematic shown in Figure 27 on page 17 is intended as a high-density surface-mount solution. When using through-hole components, some changes may be possible in the design.

The main hook switch is composed of three parallel NPN transistors (Q2–Q4) and three emitter ballasting resistors (R5–R7). This structure is necessary when using low-cost, generic 300 V transistors in order to keep these transistors out of their quasi-saturation region at high loop currents.

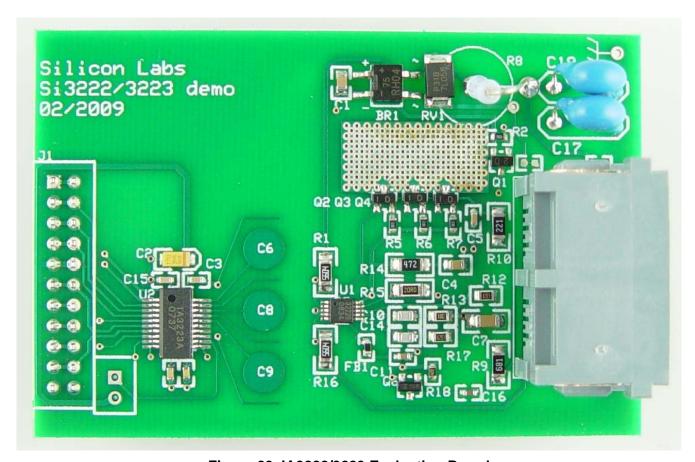

Figure 29. IA3222/3223 Evaluation Board

# 5.2. Sample Layout

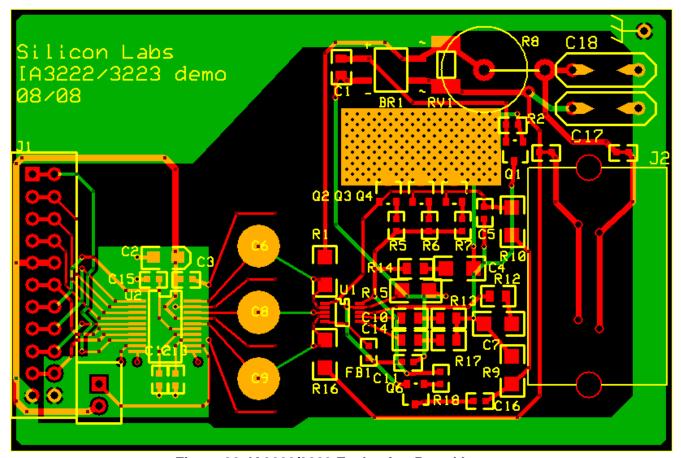

Figure 30. IA3222/3223 Evaluation Board Layout

## 5.3. Layout Guidelines

- Minimize trace lengths between U1, R1, and R15.

- Disc capacitors and their connecting traces should be drawn exactly as shown, with 4.95 mm (195 mils) diameters, 2.5 mm (98.5 mils) spacing and 10 mil traces in between on the system side only. All dimensions must match. This assumes a standard board thickness (0.062") and FR-4 material. Contact Silicon Labs for other board thicknesses or materials.

- Carefully observe the required creepage distance (surface distance over isolation) for surge rating. There must be at least 2.5 mm (98.5 mils) between any line-side conductive trace and any system-side conductive trace, including the mounting holes if they are electrically connected. Because of PCB manufacturing tolerances, the minimum drawn distances should be about 2% larger, or 2.55 mm (100.5 mils). It is a good practice to designate a "preferred arc path" between the Tip and Ring lines and the chassis, e.g. at the RJ-11 connector, by drawing those at the minimum required distance, while all other spacings between Line Side and System Side are drawn lightly larger, e.g. 2.8 mm (110 mils).

- Put no metal markings in the area of the disk capacitors. This must be watched closely, since PCB manufacturers routinely add markings wherever they find it convenient, possibly shortening the creepage distance.

- Place a ground plane under U2 and all capacitors connected directly to it as shown in the sample layout. Note the separation between chassis ground and system ground.

- Q2, Q3, and Q4 should be laid out with plenty of extra copper on both sides of the board with thermal vias in order to facilitate heat dissipation. Provide details, such as copper area, via density, etc.

## 5.4. Interfacing the IA3223

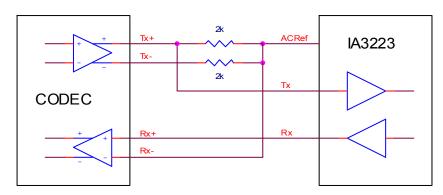

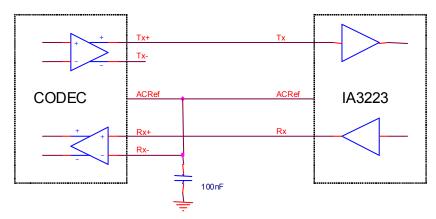

The simplified block diagrams in Figures 31, 32, and 33 show a single-ended interface to the A/D and D/A. The analog interface consists of three pins:

- TX—audio input

- RX—audio output

- ACREF—AC voltage reference

There are two ways to interface to the A/D and D/A: dc coupling and ac coupling.

#### 5.4.1. DC Coupling

All three pins, TX, RX, and ACREF, are connected to the codec directly. The ACREF pin has a weak internal buffer (see Table 3, "DC Characteristics," on page 6), which can easily be overdriven with an external reference. The external reference voltage must be in the 1.2 to 1.8 V range. Connecting the codec's ac reference to the ACREF pin will ensure good common-mode rejection.

One of the advantages of dc coupling is an alternative way for the host processor to detect parallel pick-up (PPU). PPU may be detected using the LINESTAT pin, as described in the next section. The alternative way is to monitor the dc offset at the RX pin. (Line-Side programming bit LP1 must be set to zero.) The dc loop current is added to the RX signal as a dc offset with a gain of about 1 mV/mA. Applying a digital low-pass filter to the RX channel audio enables the detection of a drop in the dc loop current, thus indicating a PPU event.

#### 5.4.2. AC Coupling

All three pins, TX, RX, and ACREF, may also be connected to the codec using coupling capacitors. For the ACREF pin, a capacitor of at least 100 nF is recommended. All coupling capacitors should be selected so that they will not cause any significant attenuation at low frequencies (taking input resistances into account). The TX pin is internally biased at 1.5 V.

# 5.5. Interfacing Examples

Figure 31. Single-Ended Interface

Figure 32. Differential interface (Without Reference)

Figure 33. Differential Interface (With Reference)

## 6. Line Monitoring

## 6.1. On-Hook Line Status Theory of Operation

The IA3222/3223 chipset was designed to provide ac and dc information about the telephone line and allow intelligent line management and automatic telephone devices to share the line with human-controlled applications. Automatic DAA applications may be found in set-top boxes, alarm systems, fax machines, meter readers, remote-diagnostic modems, answering machines, VoIP boxes, etc. A key feature of the IA3223 is the LineStat pin, which can be programmed to generate an interrupt if the line status changes either while in the on-hook or off-hook state. This reduces the need for continuous polling of the line-status bits.

In the on-hook state, the IA3222 Line Side chip converts the line voltage to a frequency at the rate of 2 kHz per volt. The voltage-to-frequency converter (V-to-f) operating range is from  $\pm 3$  to over  $\pm 150$  V. This frequency is sent as pulses across the capacitor isolation barrier. The pulse duty cycle contains line-polarity information. The V-to-f converter's signal is sufficient to allow the IA3223 System Side to decode all dc line voltage, ring signals, line reversals, and audio information (Caller ID, DTMF, and other tone monitoring). While monitoring the line in the on-hook state, the Line Side is greater than 5 M $\Omega$  dc resistance. This allows continuous monitoring while exceeding regulatory minimum idle-line resistance requirements.

The IA3223 System Side chip receives the frequency-encoded voltage information and converts it back to a continuous representation of the line voltage. The voltage difference between the ac pin and the CExt2 pin is about 1/200th of the line voltage. The dc source resistance of CExt2 is about 75 k $\Omega$ . Measuring this voltage requires a high impedance (>10 M $\Omega$ ) to prevent excessive loading.

CExt1 is part of a gyrator circuit that separates the large dc line voltage from the low-level ac voltage; so, the line audio signal may be amplified without excessive offset. CExt1 sets the low-frequency corner on this gyrator. With CE x t1 = 10 nF, the –3 dB corner is around 240 Hz, and the slope is 6 dB per octave. The upper-frequency corner is around 4 kHz set by internal RC values and rolls off at approximately 18 dB per octave.

In the on-hook state, CExt2 filters the line voltage analog with a time constant of CExt2 times 75 k $\Omega$ , for separating the ac ring signal from the dc line voltage. With a CExt2 of 220 nF, the corner frequency is about 10 Hz. The ring-detection circuit compares the voltage on CExt2 with an internal unfiltered signal. If the CE x t2 voltage exceeds one of the four programmable thresholds in one direction, a ring-detection condition occurs. This produces a standard half-wave ring-detection signal that works similarly to a standard opto-isolator ring-detection circuit.

In addition to ring detection, the other on-hook functions are line-polarity (LP) detection, line-in-use detection (LIU), and line-activity (LACT) detection. The LIU detector measures whether the line voltage exceeds one of four programmed voltage levels. The LACT detector output is activated if the line voltage changes by more than 10 to 20 V, thus acting like a sensitive full-wave ring detector. All of these signals can be read from IA3223 registers. Depending on the setting of the LSR bit, either the ring-detection signal or the LACT signal can be output to the LineStat (line status) pin.

### 6.2. Ringing

The IA3223 supports conventional ring-detection algorithms that produce an on-off digital output when the ac ring signal exceeds a preset threshold. The period between cycles is measured by the host to within 1–2 ms to qualify ring signals and differentiate them from other line signals, such as on/off-hook transients, dial pulses, and test signals sent by the telephone company. The ring-detection state is presented on the RNG bit and may optionally be multiplexed to the LineStat pin. The width of the ring-detection pulse is always at least 20% of the ring period for sine-wave ring signals.

Many regulatory ring requirements have disappeared in the last fifteen years, and the use of pulse dialing has also decreased. Years ago, when telephone companies were monopolies,  $10 \, V_{RMS}$  signals were sent down telephone lines in order to determine how many ringer loads were present. Although this probably no longer occurs, conventional wisdom is that ring detectors should not trip below  $10 \, V_{RMS}$ . Many country-specific regulations and EIA/TIA recommendations still support this requirement.

The most common spurious ring detection is due to pulse dialing. Most countries use 10 pulses per second (pps) for pulse dialing. Japan uses both 10 and 20 pps. The simple way to prevent spurious ring detection from dial pulses is to set a sufficiently high ring-detection threshold.

# IA3222/23

In countries that have strong ring signals, setting one of the upper two thresholds (22.5 or  $30 \, V_{RMS}$ ) will prevent ring detection of most dial pulses. The first pulse may still be detected because the initial dial pulse or off-hook transient may present a large signal to the ring-detection circuit. Subsequent dial pulses will fall below the ring threshold as the dc-averaging circuit centers the ac waveform. This problem can be seen with all conventional ring detectors. This is why ring-detection algorithms always need to qualify at least two ring cycles by ensuring they fall within the time limits that correspond to the ring frequency.

In some countries, such as the UK and Australia, low ring thresholds are desired. Rather than setting ring threshold, period, and number of valid cycles for every country, it is simpler to divide the whole world into a few separate ring qualification groups. Valid ring signals are between 15 and 68 Hz. Ring cadences are usually less than 2 seconds on but may be on as little as 0.2 seconds for distinctive ringing. If a 1 ms period resolution is available, and assuming a tolerance of  $\pm 10\% \pm 1$  ms, the valid period range is 12 to 74 ms. These period limits screen out 10 pps but not 20 pps pulse dialers. An example of two ring qualifier groups would be:

- Set lowest ring threshold (15 V<sub>RMS</sub>), qualify ring period 12 to 74 ms, require at least two to three valid periods in a row (disqualify if any period falls outside this range). This works worldwide except for 20 pps pulse dialing.

- For strong ringer countries (e.g., North America and Japan), use the same criteria, but set the ring threshold to 30 V<sub>RMS</sub>.

Line reversal (LR), line in use (LIU), or line activity (LACT) may also be used for ring detection in limited circumstances. Line reversal is probably safe in high-ringer-threshold countries and would reject 20 pps dial pulses effectively. In low-ringer-threshold countries, it may not reliably detect weak ring signals since the ringer signal typically rides on top of the dc line voltage. If the ringer ac peaks are less than the line voltage, line reversal will not occur.

LACT and LIU will almost always be triggered on any ring signal, but qualifying the ring frequency is a problem because both detectors may produce more than one pulse per ring period. Although LACT is a sensitive full-wave ring detector, full-wave ring detectors are less accurate with period because ring signals can be asymmetric either because of origination or because of loading. In addition, the LACT detector is not as precise as the ring detector. Its threshold may vary from 10 to 20 V peak.

Another ring-detection scheme makes use of the snoop audio output available at the RxOut pin. If the –6 dB snoop gain is set (SGAIN bit set to zero) and if the CExt1 corner is placed correctly, the ring signal will be available in the snoop audio path with sufficient attenuation to avoid clipping. A CExt1 of 10 nF will work well for typical 20 Hz ring signals. If the ring signal is expected to be around 50 Hz, CExt1 should be reduced to 4.7 nF. This will increase the –3 dB high-pass corner of the snoop audio path to about 700 Hz, which is normally acceptable for Caller ID signals.

#### 6.3. Line Reversal

On-hook line reversal (not to be confused with off-hook loop current reversal) occurs in some countries instead of the first ring cadence before the Caller ID message. Line reversal may also be used for other signaling. Typically, many DAAs with line-reversal detection capability can only detect the transient and not the actual line polarity, making it difficult to differentiate a line reversal from an off-hook transient. The IA3223 has a true line-polarity detector. Line polarity is directly sensed in the IA3222 Line-Side chip, and this information is sent across the isolation barrier to the IA3223 System-Side chip. Line polarity reversal may take up to 50 ms. Through this transition, all three detectors, Line In Use, Line Activity, and Ring, may be triggered. A line reversal can be qualified by determining if the change in polarity is stable for 50 to 100 ms.

### 6.4. Line Activity

The LACT detector can be programmed to drive the LineStat interrupt pin. This avoids the need for continuous polling of either the LP (line polarity) or RNG (ring detection) bit. LACT detects 10 to 20 V changes in either direction, also triggering on any ring, line reversal, or hook status change. When a LineStat interrupt occurs, the system polls the RNG, LP, and LIU bits and applies qualification algorithms for about 100 ms or until line activity stops.

#### 6.5. Line in Use and Line Disconnect

The LIU detector is a dc line-voltage threshold detector. One of four levels (~2.5, 15, 22.5, and 30 V) can be selected. Unfortunately, line-in-use status is ambiguous for voltages between 12 V and 19 V. Central Office lines and short-range digital loop carrier systems always provide at least 21 V of on-hook voltage. Some PBXs and VoIP boxes may supply less. Telephone devices will generally work with less than 12 V at a loop current of 20–30 mA. Users sometimes add in-line Zener devices (available at Radio Shack®) in series with answering machines in order to improve parallel-pickup disconnect performance. These in-line Zener devices increase the answering machine's off hook voltage by 6 to 8 V, often pushing the total off-hook voltage above 15 V. On short loops with 60 mA capability, some telephone devices may drop over 12 V when off hook. European telephone devices with TBR-21 current limiting may even exceed 32 V when off hook on short lines.

For most situations, the 15 V LIU threshold setting should be the default. A simple technique to reduce ambiguity is to use both LIU and snoop audio detection. A more sophisticated method is to have the system learn normal on and off hook voltages by stepping through the LIU levels of 15, 22.5 and 30 V while using the snoop circuit to monitor audio.

The 2.5 V threshold setting is intended to differentiate a disconnected line (not plugged in) from a powered line without attempting to distinguish on hook from off hook. A disconnected line may create erratic 2.5 V and line-reversal detection. Generally, a valid line is present only if the voltage is stable above 3 V and not reversing. If it is below 2 V or reversing, the line should be considered disconnected. Off-hook loop-current reversal (if available on a trunk) occurs only after dialing to indicate far party answer (toll call).

## 6.6. The LineStat Pin as Interrupt (On Hook)

The LineStat pin is an active-low interrupt output. Because it has an open-drain output with a weak internal pull-up resistor, it can be wire-ORed with other interrupts in the system. When LineStat is active, the system must determine the cause of the interrupt based on history and the state of the DAA. Table 11 suggests criteria for qualifying the interrupt when the DAA is on-hook.

| LSR Required<br>Setting | Possible Cause of<br>Interrupt | Criterion                                                      |

|-------------------------|--------------------------------|----------------------------------------------------------------|

| High                    | Ringing                        | Expected ring cadence both at LineStat pin and at RNG bit      |

| Low                     | Line reversal                  | LP bit changed compared to before interrupt, stable for 100 ms |

|                         | Line in use                    | LIU bit high if previously low, stable for 100 ms              |

|                         | Line no longer in use          | LIU bit low if previously high, stable for 100 ms              |

|                         | Line activity                  | No ring cadence or change in LP or LIU bits                    |

Table 11. Interrupt Qualifying Criteria (On-Hook)

## 6.7. Audio Snooping

The snoop circuit does not have the same audio performance as the off-hook receiver path, but it is adequate for Caller ID decoding and line monitoring. Snoop audio recovers from all high voltage line signals in less than 10 ms and is continuously present. Besides Caller ID, snooping can be used to monitor the line for call logging or used for voice/fax steering. If a fax calling tone or a specific DTMF sequence is detected, the DAA may be instructed to seize the line. Since DTMF signals normally have higher amplitude than Caller ID signals, a –6 dB gain setting exists for the snoop path (SGAIN set to zero), which allows monitoring of up to 4 VPP signals without clipping.

## 6.8. Theory of Operation- Off-Hook Line Status

In the off-hook state, the same gyrator circuit that is used for on-hook line-status monitoring is reconfigured to filter audio signals from the line-current change circuit (parallel-pickup detector) so that changes in loop current can be measured without spurious parallel-pickup signals from normal audio. Capacitor CExt2 with an internal 1.2  $M\Omega$  resistor forms a large time constant that stores the average dc value of the received signal. This dc value is compared with short-term changes to detect loop current drops caused by a parallel phone on the line going off-hook. Sensitivity to parallel pickup is also affected by the IA3222 Line-Side's holding and ac-input capacitor values. There are four levels of parallel-pickup sensitivity programmed by register bits LTH0 and LTH1. Each setting is about twice as sensitive as the previous. When a parallel-pickup event occurs, it causes a temporary active state both at the PPU (Parallel Pick Up) bit and at the LineStat pin.

## 6.9. Line Drop

Line drop or wink is a complete drop in loop current from the Central Office switch, usually indicating call disconnect or call waiting depending on the duration of the drop. Drops over 500 ms indicate disconnect, while shorter drops indicate call waiting. Consequently, it is important to time the duration of line drops with at least 10 ms resolution. Line drop is detected by the IA3223 System Side and flagged as the LD (Line Drop) status bit when the IA3222 Line Side receives insufficient loop current to keep it operational (less than 10 mA).

## 6.10. Parallel Pickup

Generally, the primary reason for parallel-pickup detection is to allow automatic telephone devices (set-top box modems, fax machines, etc.) to drop the line if a parallel telephone device attempts to dial. When a parallel telephone device goes off-hook, the loop current into the IA3222 Line Side decreases. The parallel-pickup circuit detects the low-frequency (less than 100 Hz) transients associated with a parallel pickup or hang up. To prevent spurious detects due to large, low-frequency audio signals, the parallel-pickup circuit attenuates audio-band signals. At the most sensitive setting, the parallel-pickup circuit will spuriously detect maximum amplitude voice and DTMF signals but not modem signals. Parallel pickup dl/dt may be very low either because the parallel phone has a high off-hook voltage relative to Line Side IC or because the parallel phone holding circuit (electronic inductor) may turn on slowly. The parallel-pickup circuit must, therefore, be very sensitive.

In a modem or fax application, lower parallel-pickup sensitivity can be set when dialing DTMF tones to prevent a spurious detection. A higher sensitivity can then be set after dialing. Typically, a –10 dBm modem signal transmitted from the DAA will not trigger the parallel-pickup detector on its most sensitive setting. One method for setting the levels is to raise the sensitivity until spurious detects occur and then reducing the sensitivity by one step. Each step has about a 6 dB difference in sensitivity.

Because the transmit-to-receive transhybrid return loss is poor at frequencies below 100 Hz, it is important that there be no low-frequency transients in the transmitted audio signal to prevent spurious parallel-pickup detections. Modem software can create low-frequency settling transients when switching modes, typically during training or DTMF dialing. These may cause spurious parallel-pickup detections. If adjusting the modem software is not possible, another solution is to put a low-frequency blocking capacitor in the transmit path.

## 6.11. The LineStat Pin as Interrupt (Off Hook)