## **PROCELERANT**<sup>TM</sup>

# **ENDURA Q35 MOTHERBOARD**PRODUCT MANUAL

**PL35Q**

#### Release history

| Release | Date          | Description    |

|---------|---------------|----------------|

| -0000   | December 2007 | First release. |

Copyright © 2007 by RadiSys Corporation. All rights reserved.

Portions of this manual are copyrighted by the PCI Industrial Computer Manufacturers Group, and are reprinted with permission.

RadiSys is a registered trademark and Procelerant is a trademark of RadiSys Corporation. Intel and Celeron are registered trademarks and Intel Core is a trademark of Intel Corporation. Microsoft, Windows, and Windows XP are registered trademarks of Microsoft Corporation. Red Hat and Red Hat Linux are registered trademarks of Red Hat, Inc. Linux is a registered trademark of Linus Torvalds. Phoenix is a registered trademark and TrustedCore is a trademark of Phoenix Technologies.

All other trademarks, registered trademarks, service marks, and trade names are the property of their respective owners.

## TABLE OF CONTENTS

| Adout this manual                             |        |

|-----------------------------------------------|--------|

| Safety notices                                |        |

| Electrostatic discharge                       | 7      |

| Lithium cell battery                          |        |

| Where to get more product information         | 7      |

| Chapter 1: Product Overview                   | 9      |

| Product codes                                 |        |

|                                               |        |

| Board layout                                  |        |

| Chapter 2: Product Specification              | 11     |

| Mechanical specifications                     |        |

| Motherboard                                   | 11     |

| I/O shield                                    | 12     |

| Thermal specifications                        | 12     |

| Electrical specifications                     |        |

| Motherboard power consumption                 | 12     |

| Power delivery to expansion slots             | 16     |

| Power budget                                  |        |

| Environmental specifications                  |        |

| Compliance                                    |        |

| EMC compliance                                |        |

| Safety compliance<br>Environmental compliance | 18<br> |

| Industry compliance                           |        |

| MTBF reliability predictions                  | 19     |

|                                               |        |

| Chapter 3: Hardware Reference                 | 21     |

| General specifications                        | 21     |

| Block diagram                                 | 23     |

| Power supply                                  |        |

| Voltage requirements                          |        |

| Processor                                     |        |

| Voltage requirements                          | 25     |

| Thermal requirements                          | 25     |

| Memory                                        | 26     |

| Chipset                                       |        |

|-----------------------------------------------|--------|

| Graphics and Memory Controller Hub            | 2      |

| I/O Controller Hub                            |        |

| Video                                         |        |

| System memory allocation                      | 2      |

| PCI Express graphics                          | 2<br>2 |

| VGA<br>Dual DVI MEC                           |        |

| DVI-D                                         |        |

| S-Video                                       | 2      |

| Audio                                         | 3      |

| Network                                       | 3      |

| I/O                                           |        |

| , SATA                                        |        |

| UART                                          |        |

| USB                                           | 3      |

| PS/2 mouse and keyboard                       | 3      |

| Super I/O                                     | 3<br>3 |

| Expansion interfaces                          |        |

| IDE<br>PCI                                    |        |

| PCI Express                                   |        |

| CMOS RAM and RTC                              |        |

| Firmware hub (FWH)                            |        |

| Power management                              |        |

| ACPI power states                             |        |

| ACPI wake-up                                  |        |

| System management                             |        |

| Voltage monitoring                            | 3      |

| Temperature monitoring                        |        |

| Fan control                                   | 3      |

| Front panel connections and indicators        |        |

| Power switch                                  |        |

| Reset switchPower LED                         |        |

| Hard disk LED                                 |        |

| Overheat/fan failure LED                      |        |

| LAN activity LED                              | 3      |

| and a ploc coding of a property of the second | -      |

| napter 4: BIOS Configuration and OS Support   | 3      |

| BIOS overview                                 | 3      |

| POST and boot process                         |        |

| BIOS setup                                    |        |

| Update and recovery                           |        |

| RIOS cuctomization                            |        |

| BIOS customization                            |        |

| Operating system support                      |        |

| Drivers and utilities                         | 4      |

| Appendix A: Connector Description                                  | 4 <sup>-</sup> |

|--------------------------------------------------------------------|----------------|

| Onboard connector part numbers                                     |                |

| Jumper settings                                                    |                |

| Speaker (J9)                                                       |                |

| CMOS clear (JRTC1)                                                 |                |

| PCI slots to system management bus speeds (JI2C1)                  | 4              |

| PCI Express slots to system management bus speeds (JI2C2)          | 4              |

| Watch dog (JWD)                                                    | 4              |

| Audio (JP5)                                                        | 4              |

| Gigabit LAŃ (JPL1, JPL2)                                           | 4<br>4         |

| ITE IDE (JP2)Internal device connectors                            |                |

|                                                                    |                |

| ATX power connector (24-pin, 12V))ATX power connector (4-pin, 12V) | 4<br>4         |

| CD-ROM header                                                      | 4              |

| Clear CMOS jumper                                                  | 4              |

| Fan header                                                         | 4              |

| Front panel I/O header                                             | 4              |

| IDE connector                                                      |                |

| PCI Express x1 slot                                                | 4<br>4         |

| PCI Express x4 slot<br>PCI Express x16 slot                        |                |

| PCI slot                                                           |                |

| SATA header                                                        |                |

| SMBus header                                                       | 5              |

| UART port (internal)                                               | 5              |

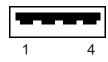

| USB header (internal)                                              | 5              |

| External Device Connectors                                         | 5              |

| Audio jacks (triple, build option)                                 | 5              |

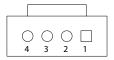

| PS/2 mouse and keyboard                                            | 5              |

| RJ45 Gigabit Ethernet port                                         |                |

| USB ports (rear I/O)                                               | 5              |

| VGA connector                                                      | 5              |

|                                                                    |                |

| Appendix B: System resources                                       | 59             |

| I/O map                                                            |                |

|                                                                    |                |

| PCI bus topology                                                   |                |

| SMBus resource allocation                                          |                |

| ISA interrupt allocation                                           | 6              |

| ISA DMA channel allocation                                         | 62             |

| POST checkpoint codes                                              |                |

| POST 80 codes                                                      | 6              |

| Error message codes                                                | 6              |

|                                                                    |                |

| Annendix C: Industry Standard References                           | 7              |

#### **PREFACE**

#### About this manual

This manual is written for engineers and technicians who will integrate the Procelerant™ Endura Q35 motherboards into their own products. For instructions on setting up an Endura Q35 motherboard, refer to the *Procelerant Endura Q35 Motherboard Quick Start Guide* available on the RadiSys® Web site, www.radisys.com.

#### Safety notices

#### Electrostatic discharge

**WARNING!** This product contains static-sensitive components and should be handled with care. Failure to employ adequate anti-static measures can cause irreparable damage to components.

To avoid electrostatic discharge (ESD) damage, the following precautions are strongly recommended.

- Keep each module/PCB in its ESD shielding bag until you are ready to install it.

- Before touching a module, attach an ESD wrist strap to your wrist and connect its other end to a known ground.

- Handle the module only in an area that has its working surfaces, floor coverings, and chairs connected to a known ground.

- Hold modules only by their edges and mounting hardware. Avoid touching PCB components and connector pins.

For further information on ESD, visit www.esda.org.

#### Lithium cell battery

#### WARNING!

- When replacing the battery on the motherboard, use only lithium cell battery type CR2032. Using any other battery may damage the board.

- Do not use a conductive instrument to remove the battery.

- Dispose of the spent battery promptly. Do not recharge, disassemble, or incinerate the battery.

- Keep the battery away from children.

#### Where to get more product information

For additional product information, visit the motherboard product pages on the RadiSys Web site at <a href="https://www.radisys.com">www.radisys.com</a> for access to datasheets, product documentation, BIOS releases, and drivers.

#### **PRODUCT OVERVIEW**

The Procelerant Endura Q35 ATX and microATX motherboards are designed for use in a variety of commercial products, such as medical imaging, gaming, test and measurement, industrial automation, and transaction terminals. All Endura Q35 motherboard models are RoHS compliant and Energy Star compliant.

Major features of the Q35 microATX motherboard include:

- Integrated Intel Graphics Memory Accelerator (GMA) 3100 graphics controller

- PCI Express x16 graphics slot that can support PCI Express graphics acceleration cards

- Integrated DVI-D for flat panel displays

- Integrated S-Video port

- PCI Express x4 slot for high-bandwidth data-capture devices

- Single Gigabit Ethernet for high-bandwidth data communications

- Media expansion card support (model PLV03-0-0 only)

#### Product codes

Table 1. Endura Q35 product codes

| Product code | ICH chipset | Gigabit<br>Ethernet | Onboard video     | GPIO and watchdog timer | I/O shield |

|--------------|-------------|---------------------|-------------------|-------------------------|------------|

| PLV03-0-0    | ICH9        | 1                   | VGA               | No                      | IOSHLD-PL  |

| PLVDS03-0-0  | ICH9        | 1                   | VGA, S-Video, DVI | No                      | IOSHLD-PL  |

Note: Processors and memory modules are not included with product codes ending in -0-0.

#### **Board layout**

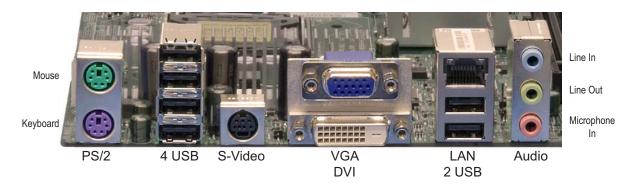

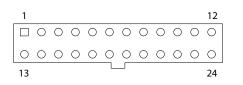

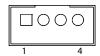

Figure 1. PL35Q board layout: rear I/O panel

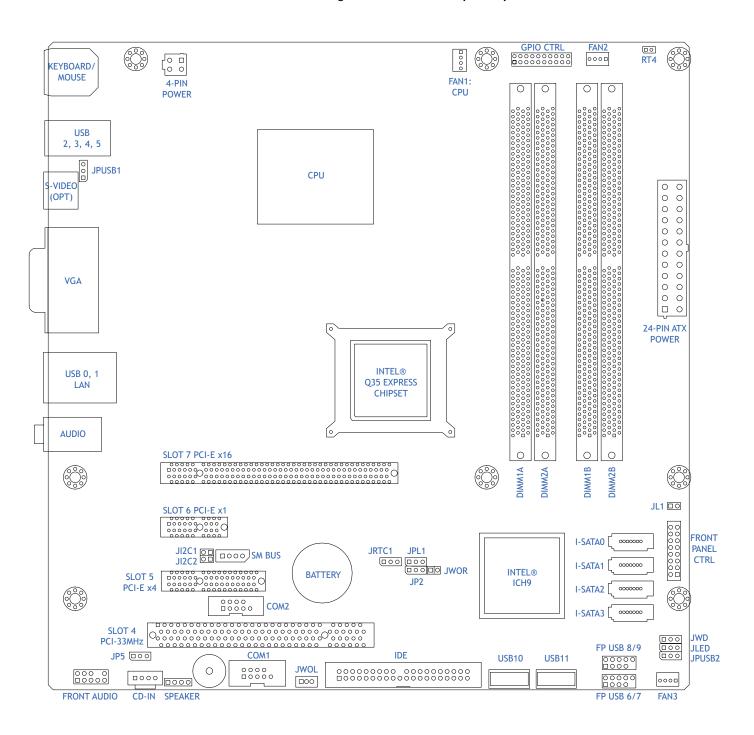

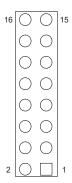

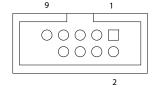

Figure 2. PL35Q board layout: top view

## **PRODUCT SPECIFICATION**

## **Mechanical specifications**

#### Motherboard

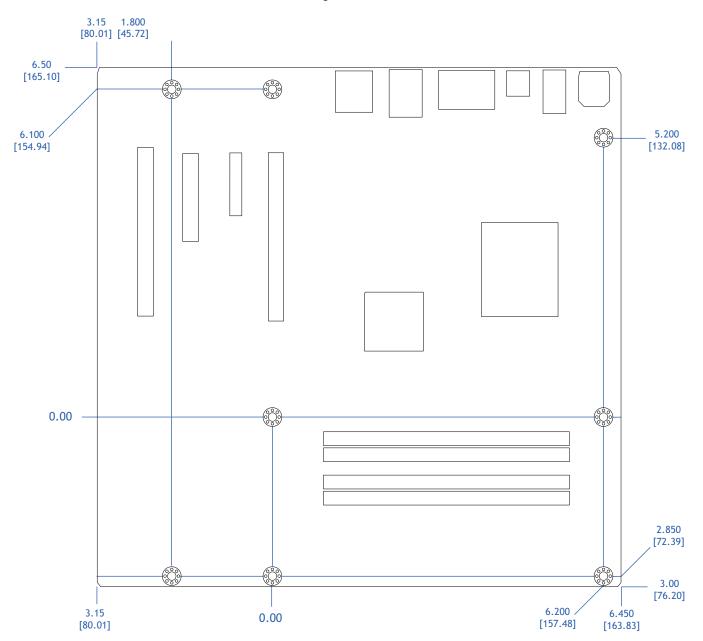

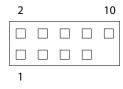

Figure 3. PL35Q board dimensions

#### I/O shield

29.63 21.74 21.13 12.63 6.50 4.13 28.50 23.32 20.88 21.74 21.13 0.00 MB MOUNTING HOLES

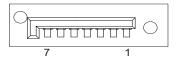

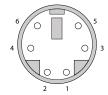

Figure 4. I/O shield for the PL35Q motherboard

#### Thermal specifications

When designing a custom thermal solution, it is helpful to know the Q35 motherboard thermal requirements, such as the thermal design power (TDP) of the processor (see *Processor* on page 25).

It is recommended that you perform thermal tests under the maximum ambient temperature, 55°C. Suitable airflow is required to maintain an ambient temperature that does not exceed the maximum thermal performance for each processor and its thermal solution.

**WARNING!** Always test the final system configuration to ensure the ambient temperature does not exceed the maximum. Failure to do so can lead to unstable operation, motherboard or processor damage, and shortened life.

#### **Electrical specifications**

#### Motherboard power consumption

The Q35 motherboards support soft-switched and hard-switched ATX power supplies via a standard 24-pin ATX power connector for main power supplies, and an extra 4-pin 12V ATX power connector for CPU use. For information about power supply selections, see *General specifications* on page 21.

Power consumption is highly dependent on the processor, memory, devices attached, running software, and the power state that the motherboard is in. Based on measurements of a real system, the following examples show the power requirements to expect under select conditions. They should not be interpreted as maximum requirements.

## Test configuration

| Component        | Description                                                  |

|------------------|--------------------------------------------------------------|

| CPU              | Code name: E6400                                             |

|                  | Part #: HH80557PH0462M                                       |

|                  | Speed: 2.13 GHz                                              |

|                  | FSB: 1066 MHz                                                |

|                  | Quantity: 1                                                  |

| Memory           | Manufacturer: ATP                                            |

|                  | Part #: AJ28K72G8BHE7S                                       |

|                  | Type: ECC                                                    |

|                  | Speed: DDR2-800                                              |

|                  | Quantity: 1                                                  |

|                  | Size: 1GB                                                    |

| Power supply     | Manufacturer: Ablecom                                        |

|                  | Model: SP423-1S, Rev 3.1                                     |

|                  | Max Power: 420 W                                             |

|                  | Max Current:                                                 |

|                  | +3.3V: 20A                                                   |

|                  | +5V: 30A                                                     |

|                  | +12V: 15A                                                    |

|                  | -12V: 1A                                                     |

|                  | +5V Standby: 2A                                              |

|                  | Max allowable DC voltage drop: 2%                            |

|                  | Max allowable leakage: 0.3V                                  |

|                  | Stress software: Intel/AMD CPU Maxpower, Memtest for Windows |

| Operating System | Microsoft® Windows® XP                                       |

#### PL35Q motherboard power consumption

These tests were run on a revision 1.01 PL35Q motherboard.

Table 2. PL35Q power consumption – DOS (stable)

|              | AC     | 4-pin | 8-pin | 2     | 20/24-pin main power connector |      |       |                     |      | al (HDD) | Consumption (W) |

|--------------|--------|-------|-------|-------|--------------------------------|------|-------|---------------------|------|----------|-----------------|

|              | Input  | +12V  | +12V  | +12V  | -12V                           | +5V  | +3.3V | +5V <sub>STBY</sub> | +5V  | +12V     | 46              |

| Voltage (V)  | 118.90 | 12.22 |       | 12.22 | 11.93                          | 5.12 | 3.36  | 5.08                | 5.12 | 12.22    | 1 10            |

| Current (A)  | 0.62   | 2.01  |       | 0.25  | 0.02                           | 0.98 | 2.04  | 0.02                | 0.41 | 0.31     | Efficiency (%)  |

| Power (W)    | 73.72  | 24.56 | 0.00  | 3.06  | 0.24                           | 5.02 | 6.85  | 0.10                | 2.10 | 3.79     | 62              |

| Vdrop Result | _      | PASS  |       | PASS  | PASS                           | PASS | PASS  | PASS                | PASS | PASS     | 02              |

#### Table 3. PL35Q power consumption — BIOS (stable)

|              | AC     | 4-pin | 8-pin | 2     | .0/24-pin n | nain powe | r connecto | Peripher            | al (HDD) | Consumption (W) |                |

|--------------|--------|-------|-------|-------|-------------|-----------|------------|---------------------|----------|-----------------|----------------|

|              | Input  | +12V  | +12V  | +12V  | -12V        | +5V       | +3.3V      | +5V <sub>STBY</sub> | +5V      | +12V            | 46             |

| Voltage (V)  | 118.90 | 12.22 |       | 12.22 | 11.93       | 5.12      | 3.35       | 5.08                | 5.12     | 12.22           | 1 70           |

| Current (A)  | 0.64   | 1.96  |       | 0.31  | 0.01        | 0.96      | 2.02       | 0.02                | 0.43     | 0.33            | Efficiency (%) |

| Power (W)    | 76.10  | 23.95 | 0.00  | 3.79  | 0.12        | 4.92      | 6.77       | 0.10                | 2.20     | 4.03            | 60             |

| Vdrop Result | _      | PASS  |       | PASS  | PASS        | PASS      | PASS       | PASS                | PASS     | PASS            |                |

#### Table 4. PL35Q power consumption — Windows desktop idle (stable)

|              | AC     | 4-pin | 8-pin | 2     | 20/24-pin main power connector |      |       |                     |      | al (HDD) | Consumption (W) |

|--------------|--------|-------|-------|-------|--------------------------------|------|-------|---------------------|------|----------|-----------------|

|              | Input  | +12V  | +12V  | +12V  | -12V                           | +5V  | +3.3V | +5V <sub>STBY</sub> | +5V  | +12V     | 44              |

| Voltage (V)  | 119.70 | 12.22 |       | 12.22 | 11.94                          | 5.12 | 3.36  | 5.08                | 5.12 | 12.22    | 77              |

| Current (A)  | 0.62   | 1.85  |       | 0.29  | 0.03                           | 1.03 | 2.09  | 0.02                | 0.43 | 0.25     | Efficiency (%)  |

| Power (W)    | 74.21  | 22.61 | 0.00  | 3.54  | 0.36                           | 5.27 | 7.02  | 0.10                | 2.20 | 3.06     | 60              |

| Vdrop Result | _      | PASS  |       | PASS  | PASS                           | PASS | PASS  | PASS                | PASS | PASS     | ] 00            |

#### Table 5. PL35Q power consumption — CPU stress (max)

|              | AC     | 4-pin | 8-pin | 2     | 0/24-pin n | nain powe | r connecto | Peripher            | al (HDD) | Consumption (W) |                |

|--------------|--------|-------|-------|-------|------------|-----------|------------|---------------------|----------|-----------------|----------------|

|              | Input  | +12V  | +12V  | +12V  | -12V       | +5V       | +3.3V      | +5V <sub>STBY</sub> | +5V      | +12V            | 66             |

| Voltage (V)  | 119.40 | 12.20 |       | 12.20 | 11.93      | 5.12      | 3.35       | 5.08                | 5.12     | 12.20           |                |

| Current (A)  | 0.82   | 3.63  |       | 0.27  | 0.01       | 1.01      | 2.08       | 0.01                | 0.43     | 0.34            | Efficiency (%) |

| Power (W)    | 97.91  | 44.29 | 0.00  | 3.29  | 0.12       | 5.17      | 6.97       | 0.05                | 2.20     | 4.15            | 68             |

| Vdrop Result | _      | PASS  |       | PASS  | PASS       | PASS      | PASS       | PASS                | PASS     | PASS            | 00             |

#### Table 6. PL35Q power consumption — Windows stress (max)

|              | AC     | 4-pin | 8-pin | 2     | 0/24-pin n | nain powe | r connecto | Peripher            | al (HDD) | Consumption (W) |                |

|--------------|--------|-------|-------|-------|------------|-----------|------------|---------------------|----------|-----------------|----------------|

|              | Input  | +12V  | +12V  | +12V  | -12V       | +5V       | +3.3V      | +5V <sub>STBY</sub> | +5V      | +12V            | 49             |

| Voltage (V)  | 119.20 | 12.21 |       | 12.22 | 11.93      | 5.12      | 3.36       | 5.08                | 5.12     | 12.22           | 1 7)           |

| Current (A)  | 0.67   | 2.04  |       | 0.28  | 0.05       | 1.15      | 2.27       | 0.01                | 0.47     | 0.33            | Efficiency (%) |

| Power (W)    | 79.86  | 24.91 | 0.00  | 3.42  | 0.60       | 5.89      | 7.63       | 0.05                | 2.41     | 4.03            | 61             |

| Vdrop Result | _      | PASS  |       | PASS  | PASS       | PASS      | PASS       | PASS                | PASS     | PASS            | 01             |

#### PL35Q motherboard power leakage

These tests were run on a revision 1.01 PL35Q motherboard.

Table 7. PL35Q power leakage – Suspend (S3) with LAN connected

|              | AC     | 4-pin | 8-pin | 2    | 20/24-pin main power connector |      |       |                     |      | al (HDD) | Consumption (W) |

|--------------|--------|-------|-------|------|--------------------------------|------|-------|---------------------|------|----------|-----------------|

|              | Input  | +12V  | +12V  | +12V | -12V                           | +5V  | +3.3V | +5V <sub>STBY</sub> | +5V  | +12V     | 2               |

| Voltage (V)  | 119.70 | 0.00  |       | 0.00 | 0.00                           | 0.10 | 0.01  | 5.08                | 0.10 | 0.00     |                 |

| Current (A)  | 0.07   | 0.01  |       | 0.02 | 0.02                           | 0.01 | 0.00  | 0.36                | 0.04 | 0.02     | Efficiency (%)  |

| Power (W)    | 8.38   | 0.00  | 0.00  | 0.00 | 0.00                           | 0.00 | 0.00  | 1.83                | 0.00 | 0.00     |                 |

| Vdrop Result | _      | PASS  |       | PASS | PASS                           | PASS | PASS  | _                   | PASS | PASS     | _               |

#### Table 8. PL35Q power leakage – Suspend (S3) without LAN connected

|              | AC     | 4-pin | 8-pin | 2    | 0/24-pin r | nain powe | r connecto | or                  | Peripher | al (HDD) | DD) Consumption (W) |  |  |

|--------------|--------|-------|-------|------|------------|-----------|------------|---------------------|----------|----------|---------------------|--|--|

|              | Input  | +12V  | +12V  | +12V | -12V       | +5V       | +3.3V      | +5V <sub>STBY</sub> | +5V      | +12V     | 2                   |  |  |

| Voltage (V)  | 119.60 | 0.06  |       | 0.00 | 0.00       | 0.10      | 0.01       | 5.07                | 0.10     | 0.00     |                     |  |  |

| Current (A)  | 0.06   | 0.01  |       | 0.00 | 0.03       | 0.00      | 0.03       | 0.43                | 0.01     | 0.02     | Efficiency (%)      |  |  |

| Power (W)    | 7.18   | 0.00  | 0.00  | 0.00 | 0.00       | 0.00      | 0.00       | 2.18                | 0.00     | 0.00     |                     |  |  |

| Vdrop Result | _      | PASS  |       | PASS | PASS       | PASS      | PASS       | _                   | PASS     | PASS     | _                   |  |  |

#### Table 9. PL35Q power leakage — Hibernate (S4) with LAN connected

|              | AC     | 4-pin | 8-pin | 2    | 0/24-pin n | nain powe | r connecto | or                  | Peripheral (HDD) |      | Consumption (W) |

|--------------|--------|-------|-------|------|------------|-----------|------------|---------------------|------------------|------|-----------------|

|              | Input  | +12V  | +12V  | +12V | -12V       | +5V       | +3.3V      | +5V <sub>STBY</sub> | +5V              | +12V | 1               |

| Voltage (V)  | 119.40 | 0.00  |       | 0.00 | 0.00       | 0.00      | 0.00       | 5.08                | 0.00             | 0.00 | ] '             |

| Current (A)  | 0.05   | 0.00  |       | 0.02 | 0.00       | 0.01      | 0.00       | 0.14                | 0.01             | 0.01 | Efficiency (%)  |

| Power (W)    | 5.97   | 0.00  | 0.00  | 0.00 | 0.00       | 0.00      | 0.00       | 0.71                | 0.00             | 0.00 |                 |

| Vdrop Result | _      | PASS  |       | PASS | PASS       | PASS      | PASS       | _                   | PASS             | PASS | _               |

#### Table 10. PL35Q power leakage - Hibernate (S4) without LAN connected

|              | AC     | 4-pin | 8-pin | 2    | 0/24-pin n | nain powe | r connecto | Peripheral (HDD)    |      | Consumption (W) |                |

|--------------|--------|-------|-------|------|------------|-----------|------------|---------------------|------|-----------------|----------------|

|              | Input  | +12V  | +12V  | +12V | -12V       | +5V       | +3.3V      | +5V <sub>STBY</sub> | +5V  | +12V            | 1              |

| Voltage (V)  | 119.30 | 0.00  |       | 0.00 | 0.00       | 0.00      | 0.00       | 5.08                | 0.00 | 0.00            | 1              |

| Current (A)  | 0.06   | 0.01  |       | 0.00 | 0.00       | 0.01      | 0.00       | 0.24                | 0.02 | 0.00            | Efficiency (%) |

| Power (W)    | 7.16   | 0.00  | 0.00  | 0.00 | 0.00       | 0.00      | 0.00       | 1.22                | 0.00 | 0.00            |                |

| Vdrop Result | _      | PASS  |       | PASS | PASS       | PASS      | PASS       | _                   | PASS | PASS            | _              |

#### Table 11. PL35Q power leakage - Soft Off (S5) with LAN connected

|              | AC     | 4-pin | 8-pin | 2    | .0/24-pin n | nain powe | r connecto | Peripheral (HDD)    |      | Consumption (W) |                |

|--------------|--------|-------|-------|------|-------------|-----------|------------|---------------------|------|-----------------|----------------|

|              | Input  | +12V  | +12V  | +12V | -12V        | +5V       | +3.3V      | +5V <sub>STBY</sub> | +5V  | +12V            | 1              |

| Voltage (V)  | 119.30 | 0.00  |       | 0.00 | 0.00        | 0.00      | 0.00       | 5.08                | 0.00 | 0.00            | 1              |

| Current (A)  | 0.05   | 0.00  |       | 0.01 | 0.01        | 0.00      | 0.02       | 0.14                | 0.01 | 0.00            | Efficiency (%) |

| Power (W)    | 5.97   | 0.00  | 0.00  | 0.00 | 0.00        | 0.00      | 0.00       | 0.71                | 0.00 | 0.00            |                |

| Vdrop Result | _      | PASS  |       | PASS | PASS        | PASS      | PASS       | _                   | PASS | PASS            | _              |

Table 12. PL35Q power leakage – Soft Off (S5) without LAN connected

|              | AC     | 4-pin | 8-pin | 2    | .0/24-pin n | nain powe | r connecto | or                  | Peripheral (HDD) |      | Consumption (W) |

|--------------|--------|-------|-------|------|-------------|-----------|------------|---------------------|------------------|------|-----------------|

|              | Input  | +12V  | +12V  | +12V | -12V        | +5V       | +3.3V      | +5V <sub>STBY</sub> | +5V              | +12V | 1               |

| Voltage (V)  | 119.20 | 0.00  |       | 0.00 | 0.00        | 0.00      | 0.00       | 5.08                | 0.00             | 0.00 | · I             |

| Current (A)  | 0.06   | 0.01  |       | 0.01 | 0.00        | 0.01      | 0.00       | 0.22                | 0.02             | 0.00 | Efficiency (%)  |

| Power (W)    | 7.15   | 0.00  | 0.00  | 0.00 | 0.00        | 0.00      | 0.00       | 1.12                | 0.00             | 0.00 |                 |

| Vdrop Result | _      | PASS  |       | PASS | PASS        | PASS      | PASS       | _                   | PASS             | PASS | _               |

#### Power delivery to expansion slots

The following table indicates the maximum current that should be drawn from each expansion slot. PCI Express slots are limited to 75W in total on the main +12V and +3.3V supplies, all of which can be drawn from either voltage rail. The total for the riser are for the total current/power delivered to the riser through the motherboard. If more is required, the riser must draw power from an additional source such as a separate power connector from the PSU.

**WARNING!** Do not exceed the limits for each slot or voltage rail shown in this table.

Table 13. Maximum expansion slot currents on PL35Q

| Expansion slot                | +3.3V (A) | +5V (A) | +12V (A) | -12V (A) | +5V standby (A) |

|-------------------------------|-----------|---------|----------|----------|-----------------|

| PCI Express x16 graphics slot | 3         | _       | 5.5      | _        | _               |

| PCI Express x4 slot           | 3         | _       | 2.1      | _        | _               |

| PCI Express x1 slot           | 3         | _       | 0.5      | _        | _               |

| PCI slot                      | 7.6       | 5       | 0.5      | 0.1      | _               |

#### Power budget

Before choosing a power supply, it is recommended that you always create a power budget for your system. A sample power budget for the Q35 motherboards populated with processor, memory, expansion cards, etc. are shown below.

*Note:* These sample values may not apply to to your system.

Table 14. Power budget for PL35Q

| Component               |        | Mo     | therboard | current |             | Power consumption |  |

|-------------------------|--------|--------|-----------|---------|-------------|-------------------|--|

| Component               | +3.3V  | +5V    | +12V      | -12V    | +5V standby | rowei consumption |  |

| Motherboard             | 2.6A   | 1.0A   | 3.7A      | 0.03A   | 0.1A        | 59W               |  |

| 12 USB ports            | _      | 6A     | _         | _       | _           | 30W               |  |

| 4 SATA ports            | _      | 1.6A   | 1.2A      | _       | _           | 22.4W             |  |

| 2 serial ports          | _      | 0.02A  | 0.02A     | _       | _           | 0.3W              |  |

| 1 IDE connector         | _      | 1.5A   | 1.5A      | _       | _           | 25.5W             |  |

| Expansion slots (total) | 16.6A  | 5A     | 8.6A      | 0.1A    | _           | 184.2W            |  |

| Heatsink                | _      | _      | 0.4A      | _       | _           | 4.8W              |  |

| Front panel I/O         | 0.1A   | _      | _         | _       | _           | 0.3W              |  |

| Video DDC channel       | _      | 0.05A  | _         | _       | _           | 0.3W              |  |

| Total                   | 19.32A | 15.27A | 15.42A    | 0.13A   | 0.1A        | 327W              |  |

### **Environmental specifications**

All Q35 motherboards comply with the following environmental specifications.

Table 15. Environmental specifications

| Characteristic    | State              | Value                                                                               |  |  |  |  |  |

|-------------------|--------------------|-------------------------------------------------------------------------------------|--|--|--|--|--|

| Temperature       | Operating          | 0° to +55° C                                                                        |  |  |  |  |  |

| (ambient)         |                    | Operation above +30° C reduces the maximum operational relative humidity            |  |  |  |  |  |

|                   | Operating gradient | ±5°C per minute                                                                     |  |  |  |  |  |

|                   | Non-operating      | -40° C to +85° C, 5° C per minute maximum excursion gradient                        |  |  |  |  |  |

| Relative humidity | Operating          | 15% to 95% RH non-condensing                                                        |  |  |  |  |  |

|                   | Non-operating      | 15% to 90% RH non-condensing at +40°C                                               |  |  |  |  |  |

| Vibration         | Operating          | 0.25 G at 5 to 200 Hz. Approx. 15 min./axis.                                        |  |  |  |  |  |

|                   | Non-operating      | 0.5 G at 5 to 200 Hz. Approx. 15 min./axis.                                         |  |  |  |  |  |

| Shock             | Non-operating      | 30g 11ms, half-sine, 3 axes                                                         |  |  |  |  |  |

|                   | Packaged           | Drop test, 10-up bulk packaging, 30 inches free-fall, 152 inches/s velocity change. |  |  |  |  |  |

| Altitude          | Operating          | To 15,000 ft. (4,500m)                                                              |  |  |  |  |  |

|                   | Non-operating      | To 40,000 ft. (12,000m)                                                             |  |  |  |  |  |

| MTBF              |                    | See MTBF reliability predictions on page 19.                                        |  |  |  |  |  |

| Airflow           |                    | Based on standard Intel guidelines                                                  |  |  |  |  |  |

| Fuses             |                    | Self-resetting PTC fuse                                                             |  |  |  |  |  |

#### **Compliance**

#### **EMC** compliance

When correctly installed in a suitable chassis, Q35 motherboards meet these EMC regulations.

Table 16. EMC compliance

| Characteristic <sup>1</sup>  | State     | Value                                            |

|------------------------------|-----------|--------------------------------------------------|

| ESD                          | Operating | IEC 1000-4-2/EN61000-4-2                         |

|                              |           | 4kV direct contact, performance criteria B       |

|                              |           | 6kV direct contact, performance criteria C       |

|                              |           | 4kV air discharge, performance criteria B        |

|                              |           | 8kV air discharge, performance criteria C        |

| Fast transient/burst         | Operating | IEC 1000-4-4/EN61000-4-4, performance criteria B |

| Surge voltages               | Operating | IEC 1000-4-5/EN61000-4-5, performance criteria B |

| Conducted                    | Operating | IEC 1000-4-6/EN61000-4-6, performance criteria B |

| Radiated emissions           | Operating | - CISPR 22 Class B                               |

|                              |           | ■ EN55022, EN55024                               |

|                              |           | FCC Class B                                      |

| Radiated immunity            | Operating | EN61000-4-3, performance criteria A              |

| Conducted immunity           | Operating | EN61000-4-6, performance criteria A              |

| AC power dips and interrupts | Operating | EN61000-4-11, performance criteria B and C       |

These are system-level tests. Because the Q35 motherboard is part of a larger system, radiated emissions and immunity are agency tested, but not certified, to these specifications. Other aspects of system performance will affect this motherboard's ability to conform to these specifications.

#### Safety compliance

When correctly installed in a suitable chassis, Q35 motherboards are designed to meet these safety regulations:

- UL60950, CSA60950, EN60950 and IEC60950

- CB report to IEC60950-1

- Accessory listing from UL to UL60950-1

#### **Environmental compliance**

- European RoHS

- China RoHS

- Designed for lead-free manufacturing processes

#### **Industry compliance**

Q35 motherboards are designed to the industry standards shown in *Appendix C, "Industry Standard References"* on page 71.

### MTBF reliability predictions

The predicted MTBF for Q35 motherboards at 35°C and 55°C are shown in Table 17. The predictions are based on Telcordia SR-332 Issue 1, Method 1, Case 3 with the following underlying assumptions:

- 50% default stress ratio for all modeled components

- Application-specific stress ratios applied for electrolytic capacitors when available

- Ground benign in a controlled environment

- Level II quality grade on all components

- Mechanical components are not modeled

- No burn-in or pre-testing specified

- MTTR specified to be 30 minutes

- No component-specific thermal rises or other voltage/current stress applied

- Relex 7.7 modeling software

Table 17. MTBF reliability predictions

| Product code | MTBF (hours) @ 35°C | MTBF (hours) @ 55°C |

|--------------|---------------------|---------------------|

| PLV03-0-0    | 423,562             | 222,005             |

| PLVDS03-0-0  | 382,598             | 200,534             |

## HARDWARE REFERENCE

## **General specifications**

Table 18. General specifications: PL35Q

| Item        | Description                                                                                                                                                         |  |  |  |  |

|-------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Dimensions  | 9.6" x 9.6"                                                                                                                                                         |  |  |  |  |

| Form Factor | MicroATX revision 2.2                                                                                                                                               |  |  |  |  |

| _           | These processors are supported:                                                                                                                                     |  |  |  |  |

|             | Intel Core 2 Duo E8400                                                                                                                                              |  |  |  |  |

|             | Intel Core 2 Duo E6400                                                                                                                                              |  |  |  |  |

|             | Intel Core 2 Duo E4300                                                                                                                                              |  |  |  |  |

|             | Intel Pentium Dual-Core E2160                                                                                                                                       |  |  |  |  |

|             | Intel Celeron 440                                                                                                                                                   |  |  |  |  |

|             | <ul> <li>Intel Core 2 Quad processors (future)</li> </ul>                                                                                                           |  |  |  |  |

|             | • FSB frequency at 800/1066/1333 MHz                                                                                                                                |  |  |  |  |

|             | LGA775 socket                                                                                                                                                       |  |  |  |  |

| _           | Intel Q35 Express GMCH chipset and ICH9 chipset                                                                                                                     |  |  |  |  |

| Туре        | Four 240-pin DIMM slots for single or dual channel non-ECC unbuffered DDR2 667/800 MHz memory                                                                       |  |  |  |  |

| Capacity    | Maximum 8GB, minimum 256MB                                                                                                                                          |  |  |  |  |

| _           | <ul> <li>VGA output for analog display, with a maximum VGA resolution of 2048x1536 with 32-bit color at<br/>75Hz</li> </ul>                                         |  |  |  |  |

|             | <ul> <li>One PCI Express x16 graphics slot for PEG graphics cards, with a maximum digital display<br/>1920x1200@60Hz</li> </ul>                                     |  |  |  |  |

|             | <ul> <li>Integrated DVI-D for flat panel displays (model PLVDS03-0-0 only)</li> </ul>                                                                               |  |  |  |  |

|             | <ul> <li>Integrated S-Video for TV monitors and video printers (model PLVDS03-0-0 only)</li> </ul>                                                                  |  |  |  |  |

|             | Support for dual independent displays (model PLVDS03-0-0 only)                                                                                                      |  |  |  |  |

|             | <ul> <li>Support for ADD2 and Media Expansion Cards (model PLV03-0-0 only)</li> </ul>                                                                               |  |  |  |  |

| _           | Intel High Definition Audio using Realtek ALC883 eight channel CODEC                                                                                                |  |  |  |  |

|             | - Three audio jacks on rear I/O panel, with two hardware configuration options for two jacks (Microphone, Line Out) and three jacks (Microphone, Line Out, Line In) |  |  |  |  |

|             | Audio enable header capable of enabling onboard audio connections                                                                                                   |  |  |  |  |

|             | One CD-ROM header for audio CD playback                                                                                                                             |  |  |  |  |

|             | Dimensions Form Factor                                                                                                                                              |  |  |  |  |

Table 18. General specifications: PL35Q

| Item         | Item          | Description                                                                                                                                  |  |  |  |  |  |  |

|--------------|---------------|----------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| Network      | _             | Single Intel Gigabit Ethernet via Intel 82566DM PHY controller                                                                               |  |  |  |  |  |  |

|              |               | Two Ethernet LEDs for Ethernet link and activity indication                                                                                  |  |  |  |  |  |  |

|              |               | PXE boot and Wake-On-LAN support                                                                                                             |  |  |  |  |  |  |

|              |               | One RJ45 Ethernet connector on rear I/O panel                                                                                                |  |  |  |  |  |  |

| I/O          | USB           | Support for 12 USB 2.0 ports with a speed of up to 480Mbps: six ports on rear I/O panel, two onboard ports, and two onboard dual USB headers |  |  |  |  |  |  |

|              | SATA          | 4 devices supported with 3 SATA ports and 1 eSATA port (identified by a blue connector)                                                      |  |  |  |  |  |  |

|              | IDE           | One Ultra ATA 100 interface via PCI controller                                                                                               |  |  |  |  |  |  |

|              | Serial ports  | Two Fast UART 16500 compatible onboard serial headers                                                                                        |  |  |  |  |  |  |

|              | Miscellaneous | PS/2 mouse and keyboard on rear I/O panel                                                                                                    |  |  |  |  |  |  |

| Expansion    | PCI Express   | One PCI Express x16 slot                                                                                                                     |  |  |  |  |  |  |

| capabilities |               | One PCI Express x4 slot                                                                                                                      |  |  |  |  |  |  |

|              |               | One PCI Express x1 slot                                                                                                                      |  |  |  |  |  |  |

|              | PCI           | One PCI 2.3 32-bit at 33MHz slot                                                                                                             |  |  |  |  |  |  |

| BIOS         |               | - 2MB Firmware SPI Phoenix® TrustedCore™ BIOS including video BIOS, network boot, and PXE                                                    |  |  |  |  |  |  |

|              |               | Clear CMOS jumper selection header capable of restoring factory defaults                                                                     |  |  |  |  |  |  |

|              |               | Customizable logo during boot BIOS default settings                                                                                          |  |  |  |  |  |  |

| System       |               | Voltage, temperature, and fan monitoring (3 fans)                                                                                            |  |  |  |  |  |  |

| management   |               | Lithium cell voltage monitoring                                                                                                              |  |  |  |  |  |  |

|              |               | Automatic fan speed control (3 fans)                                                                                                         |  |  |  |  |  |  |

|              |               | Programmable watchdog timer                                                                                                                  |  |  |  |  |  |  |

|              |               | - SMBus header                                                                                                                               |  |  |  |  |  |  |

|              |               | Chassis intrusion detection                                                                                                                  |  |  |  |  |  |  |

|              |               | Watchdog time-out for SMI interrupt and system reset                                                                                         |  |  |  |  |  |  |

| Power        | Requirement   | Standard 24-pin ATX power supply connector and 4-pin +12V ATX power supply connector                                                         |  |  |  |  |  |  |

|              | 1             | Hard-switched or soft-switched power supplies                                                                                                |  |  |  |  |  |  |

|              | Management    | ACPI 3.0 supporting states S0, S3, S4, S5, and C0, C1, C2, C3, C4                                                                            |  |  |  |  |  |  |

| OS support   |               | Windows XP® Professional SP2                                                                                                                 |  |  |  |  |  |  |

|              |               | ■ Windows XP® Embedded SP2                                                                                                                   |  |  |  |  |  |  |

|              |               | Windows Vista Premium                                                                                                                        |  |  |  |  |  |  |

|              |               | Red-Hat® Enterprise Linux® 5.0 AS                                                                                                            |  |  |  |  |  |  |

|              |               | Novell SUSE Linux Enterprise Server 10  Novell SUSE Linux Enterprise Server 10                                                               |  |  |  |  |  |  |

|              |               | Knoppix Linux 5.1.1                                                                                                                          |  |  |  |  |  |  |

|              |               | • •                                                                                                                                          |  |  |  |  |  |  |

|              |               | - Solaris 10 Update 4                                                                                                                        |  |  |  |  |  |  |

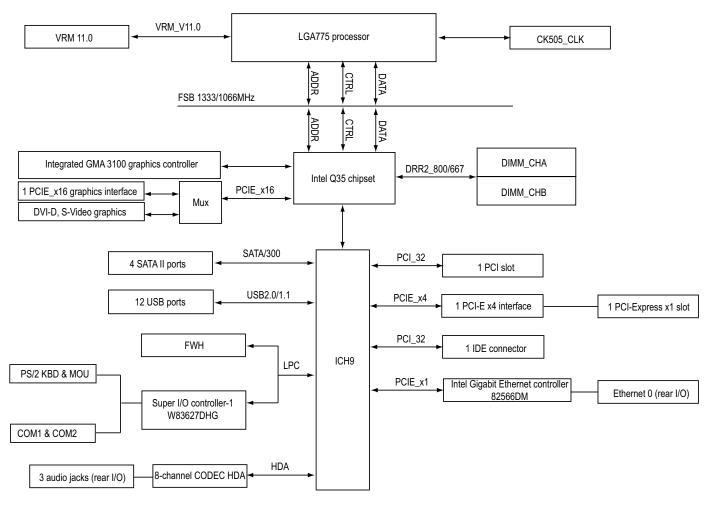

### Block diagram

Figure 5. PL35Q block diagram

#### **Power supply**

Q35 motherboards support soft-switched and hard-switched ATX power supplies. The standard 24-pin ATX power connector provides +12V, -12V, +5V standby, +5V, +3.3V power rails and an extra 4-pin ATX power connector provides +12V for CPU use only.

A 20-pin ATX power connector can also be used. In this case, plug the 20-pin cable in on the pin #1 side of the connector and leave the two pairs of pins on the other side exposed. No adaptor is required.

**WARNING!** The power supply must be approved by a third-party agency for use in IEC/EN/UL/CSA 60950 applications.

#### **Voltage requirements**

Table 19 shows the maximum load currents on all ATX power rails. Ensure that the power supply can support the required load current on all rails, otherwise, it can cause damage to the power supply or the motherboard.

A 5V standby power rail is optional, but if not provided, the soft-switched power supply control features of the motherboard cannot be used. When there is a standby rail, make sure it can provide sufficient current for the motherboard, taking into account the Ethernet controllers and any adapter card that draws current from the auxiliary 3.3V supply. The ATX -5.0V rail is not used by the Q35 motherboards.

Table 19. Maximum load currents on ATX power rails

| Power Rail  | Maximum Load Current |

|-------------|----------------------|

| +12V        | 12A                  |

| -12V        | 0.1A                 |

| +5V         | 18.75A               |

| +3.3V       | 6.72A                |

| +5V standby | 1.25A                |

#### **Processor**

Q35 motherboards support Intel Celeron, Pentium Dual-Core, and Core 2 Duo processors in a socketable LGA775 package.

For support of other processors, refer to the *Procelerant Endura Q35 Supported Processors List* on the RadiSys Web site.

| Processor Branding | Process | CPU#  | Clock<br>Speed<br>MHz | FSB MHz | L2 Cache | TDP | Number of Cores |

|--------------------|---------|-------|-----------------------|---------|----------|-----|-----------------|

| Core 2 Duo         | 45nm    | E4800 | 3.0                   | 1333    | 3M       | 65W | 2               |

| Core 2 Duo         | 65nm    | E6400 | 2.13                  | 1066    | 2M       | 65W | 2               |

| Core 2 Duo         | 65nm    | E4300 | 1.80                  | 800     | 2M       | 65W | 2               |

| Pentium Dual-Core  | 65nm    | E2160 | 1.80                  | 800     | 1M       | 65W | 2               |

| Celeron            | 65nm    | 440   | 2.0                   | 800     | 512K     | 35W | 1               |

Table 20. Supported processors

#### Voltage requirements

The power supply connects to a standalone 4-pin ATX +12V power connector on the motherboard to provide power for the processor.

An onboard DC-to-DC voltage regulator generates the processor core voltages from the +12V power supply, and core PLLs and processor I/O from the +5V power rail. Both the processor voltage and the operating frequency are automatically adjusted by the motherboard to suit the installed processor.

#### Thermal requirements

The Intel Celeron, Pentium Dual-Core, and Core 2 Duo processors support the THERMTRIP# signal for catastrophic thermal protection. An external thermal monitor, Winbond Super IO W83627DHG (www.winbond.com/), is also implemented to protect the processor and the system against excessive temperature. If the external thermal monitor detects a catastrophic processor temperature of 125°C (maximum), or if the THERMATRIP# signal is asserted, the voltage supply to the processor will be turned off within 500ms to prevent permanent silicon damage due to thermal runaway of the processor.

The thermal monitor feature and the Thermal Control Circuit (TCC) will be enabled in the CPU by the board BIOS. The CPU temperature can be read over the SMbus at any time.

See *Table 20* on page 25 for the thermal design power (TDP) values for each processor type, for which the junction temperature (Tj) specifications fall within  $0^{\circ}$ C –  $100^{\circ}$ C. The processor must remain within the minimum and maximum junction temperature.

#### Memory

Q35 motherboards have four 240-pin DIMM sockets to support up to 8GB of 64-bit, unbuffered non-ECC DDR2 800/667MHz dual-channel memory modules. Each socket can accept either single channel mode or dual-channel interleaved mode.

In general, compatible memory modules must:

- Support 512Mb and 1Gb memory technology in x8 and x16 organization.

- Supports maximum memory bandwidth of 6.4 GB/s in single-channel or dualchannel asymmetric mode, or 12.8 GB/s in dual-channel symmetric mode assuming DDR2 800 MHz.

- Using 512 Mb device technologies, the smallest memory capacity possible is 256 MB, assuming Single Channel Mode with a single x16 single sided un-buffered non-ECC DIMM memory configuration.

- Using 1 Gb device technologies, the largest memory capacity possible is 8 GB, assuming Dual Channel Mode with four x8 double sided un-buffered non-ECC DIMM memory configuration.

The BIOS automatically configures the motherboard for the correct size, speed, and type. For a list of qualified memory modules, refer to the *Procelerant Endura Q35 Qualified Memory List* on the RadiSys Web site.

#### Chipset

#### **Graphics and Memory Controller Hub**

The Intel 82Q35 graphics and memory controller hub (GMCH) includes four interfaces:

- Host interface

- System memory interface

- External graphics interface

- I/O controller through DMI interface

For further information, refer to the *Intel 3 Series Express Chipset Family Datasheet for the Intel 82Q35 Graphics and Memory.*

#### I/O Controller Hub

The Intel ICH9 and ICH9DO I/O provide extensive I/O support:

- Direct Media Interface (DMI) support for chip-to-chip connection between the GMCH and ICH

- PCI Express Base Specification, Revision 1.1 support

- PCI Local Bus Specification, Revision 2.3 support for 33 MHz PCI operations

- ACPI Power Management Logic Revision 3.0b support

- Enhanced DMA controller, interrupt controller, and timer functions

- Integrated Serial ATA host controllers with independent DMA operation up to six ports and AHCI support

- USB host interface with support for up to 12 USB ports, 6 UHCI host controllers, and 2 EHCI high-speed USB 2.0 host controllers

- Integrated 10/100/1000 Mbps Gigabit Ethernet MAC with system defense

- System Management Bus (SMBUs) Specification, Revision 2.0 with additional support for I2C devices

- Intel High Definition Audio support

- Intel Matrix Storage Technology support

- Intel Active Management Technology support (ICH9 Digital Office only)

- Intel Virtualization Technology for directed I/O support

- Intel Trusted Execution Technology support

- Low Pin Count (LPC) interface support

- Firmware Hub (FWH) interface support

- Serial Peripheral Interface (SPI) support

- Intel Quiet System Technology support

For further information, refer to the *Intel 3 Series Express Chipset Family Datasheet for the Intel 82Q35 Graphics and Memory Controller Hub.*

#### Video

The GMCH provides an integrated graphics device (IGD) delivering cost-competitive 3D, 2D and video capabilities. The GMCH contains an extensive set of instructions for 3D operations, 2D operations, motion compensation, overlay, and display control. The GMCH's video engines support video conferencing and other video applications.

The GMCH also has the capability to support external graphics accelerators via the PCI Express graphics (PEG) port but cannot work concurrently with the integrated graphics device. However, the dual independent display can work via the ADD2/Media Expansion Card attachment.

High bandwidth access to data is provided through the system memory port.

#### System memory allocation

The GMCH uses a UMA configuration with DVMT for graphics memory. When the onboard video controller is not used, it is recommended to disable it via the BIOS setup utility to prevent unnecessary system memory allocation.

By default, the system BIOS allocates 8MB of system memory to the video controller to support legacy VGA displays. The amount of system memory reported by the BIOS will reflect this reduction when the onboard video controller is enabled. Once the operating system loads, the video driver dynamically allocates further system memory depending on availability and the application requirement. Systems should have at least 256MB of system memory when using these graphics drivers.

#### PCI Express graphics

The Q35 motherboards support PCI Express graphics acceleration cards via the PCI Express x16 graphics slots. This support includes:

- One PCI Express x16 graphics slot on the PL35Q motherboard, electrically x16 interface

- PCI Express frequency of 1.25 GHz resulting in 2.5 Gb/s each direction per lane

- Raw bit-rate of 2.5Gb/s on each lane while employing 8b/10b encoding to transmit data across the interface.

- Maximum theoretical bandwidth of 4GB/s in each direction simultaneously, for an aggregate bandwidth of 8GB/s when using 16 lanes.

- ADD2/media expansion cards support with capabilities of dual independent displays with the integrated graphics devices.

**Note:** The PLVDS03-0-0 motherboard does not support this functionality, since the SDVO channel is tied to the onboard DVI controller. If MEC cards are required in your application, use the entry-level PLV03-0-0 motherboard, which has the DVI controller depopulated.

#### **VGA**

Q35 motherboards provide a standard DA15F VGA connector on the rear I/O panel. The integrated Intel GMA 3100 video controller supports:

- 350MHz integrated 24-bit RAMDAC

- Resolution up to 2048x1536 pixels at 75Hz refresh

- DDC2B Compliant Interface

#### **Dual DVI MEC**

Use this procedure to set up dual DVI monitors using a dual DVI MEC.

- 1. Start the system and press the Delete key when prompted to enter the BIOS setup utility.

- 2. In the BIOS setup, navigate to the Advanced menu, then the Advanced Chipset Control menu. Set the DVMT 4.0 Mode option to DVMT. Save this change and exit, and allow the system to restart.

- 3. Visit the Intel download center Web site, <a href="www.dowloadcenter.intel.com">www.dowloadcenter.intel.com</a>, and download the Intel Embedded Graphics Driver (IEGD) with CED, version 8.0.0. The file name is "IEGD\_8\_0\_GOLD\_1063.exe". Also download and review the IEGD Release Notes.

- 4. Uninstall the existing graphics driver on the motherboard. (If you are running Windows, go to the Control Panel and select Add or Remove Programs.)

- 5. Install the IEGD according to the instructions provided in the IEGD User's Guide. This will disable the onboard video.

- 6. Install the dual DVI MEC in the PCI Express x16 slot. The bottom DVI port on the MEC is the primary port, and should be functional immediately.

- 7. Use the IEGD Configuration Editor to set up your monitors as required (Clone, Extended, etc.)

#### DVI-D

The PLVDS03-0-0 motherboard supports the attachment of one digital monitor to the DVI-D port on the rear I/O panel with display resolution up to 1920 x 1200 @ 60 Hz.

#### S-Video

The PLVDS03-0-0 motherboard supports the attachment of TV monitors and video printers via an S-Video port on the rear I/O panel. The TV-Out display resolution is up to  $1400 \times 1050 \otimes 85$  Hz.

#### **Audio**

The Q35 motherboards support:

- Intel High Definition Audio using the Realtek ALC883 eight-channel stereo CODEC

- Triple 3.5mm audio jacks on the rear I/O panel for surround sound.

- One 1x4-pin CD-ROM header to support onboard sound for audio CD playback

**Note:** An onboard PC speaker is not provided, but it is recommended that you connect an external speaker to the front panel I/O header to hear the beep signals.

#### Network

The PL35Q motherboard has a single Gigabit Ethernet controller.

Ethernet port 0 uses the Intel 82566DM PHY controller, which connects to the ICH9/ICH9DO LAN (the MAC integrated on the ICH9/ICH9DO chipset) through a dedicated interconnect.

#### Ethernet features include:

- Standard IEEE 802.3 Ethernet interface for 10BASE-T, 100BASE-TX, and 1000BASE-T applications (802.3, 802.3u, and 802.3ab)

- Remote boot and PXE via BIOS configuration

- Wake-On-LAN support via BIOS configuration with the option to use the native operating system, as well as support for legacy operating systems

- Onboard RJ45 connector with 2 integrated programmable LEDs showing link speed and speed.

Table 21. Ethernet LEDs

| LED color   | LED state        | Ethernet link and activity                            |

|-------------|------------------|-------------------------------------------------------|

| Green/Amber | Off              | 10Mbps link speed                                     |

|             | Green steady on  | 100Mbps link speed                                    |

|             | Amber steady on  | 1000Mbps link speed                                   |

| Yellow      | Off              | No link established                                   |

|             | Yellow steady on | Link established; communication activity not detected |

|             | Yellow blinking  | Link established; communication activity detected     |

#### I/O

#### **SATA**

The PL35Q motherboards provide four SATA headers to attach SATA disk drives via the SATA controller on the ICH9/ICH9DO chipset. The blue SATA connector supports eSATA for use with external devices at a distance of up to 2m.

**Note:** SATA interface transfer rates are independent of Ultra DMA mode settings in the BIOS setup utility. SATA interface transfer rates will operate at the bus' maximum speed, regardless of the Ultra DMA mode reported by the SATA device or the system BIOS.

#### **UART**

Q35 motherboards support two or four Fast UART serial ports, depending on product options, via the Winbond W83627DHG Super I/O controller(s). The serial ports are headers for serial port connectors on the chassis.

Serial port support includes:

- High-speed, 16550-compatible UARTs with 16-byte send/receive FIFOs

- Fully programmable serial interface characteristics

- Maximum baud rate for clock source 14.769MHz is up to 921Kbps. The baud rate at 24MHz is 1.5Mbps.

#### **USB**

Q35 motherboards support 12 USB 2.0/1.1 ports at a speed of 480 Mbps:

- Six USB ports on the rear I/O panel

- Two onboard USB ports and two onboard dual USB headers.

All USB ports support high-speed, full-speed, and low-speed operations. The ICH9/ICH9DO chipset determines whether a USB port is controlled by a UHCI controller or by an EHCI controller.

The BIOS provides emulations of standard USB keyboards and mice using SMI-based routines to intercept traffic. Operating systems that do not support USB devices suffer performance degradation due to this activity. Legacy support is automatically switched off once a USB-aware operating system loads.

#### PS/2 mouse and keyboard

With the Winbond® W83627DHG Super I/O controller, the Q35 motherboards support the PS/2 keyboard and mouse interfaces on the rear I/O panel.

Mouse and keyboard features include:

- 8042-based keyboard controller with support for PS/2 mouse and keyboard

- Fast Gate A20 and hardware keyboard reset

- User options for the clock frequency of 6, 8, 12, and 16MHz via the BIOS setup utility configuration.

#### Super I/O

The Winbond W83627EHG Super I/O controllers is capable of supporting a wide range of I/O functions with the LPC (Low Pin Count) interface. The Q35 motherboards support the following legacy devices via this super I/O chip:

- UART ports (page 31)

- PS/2 mouse and keyboard (page 32)

*Note:* Though the W83627EHG super I/O chip is capable of supporting 40 GPIO lines by itself, these GPIO lines are unavailable on the Q35 motherboards.

#### **Expansion interfaces**

#### IDE

The Q35 motherboard provide a standard IDE connector to support IDE hard disks and ATAPI devices via the ICH9's PCI controller.

#### PCI

PCI slots are compliant with the *PCI Local Bus Specification Version 2.3*. The PL35Q motherboard has one 32-bit, 33MHz, 3.3V PCI slot.

#### **PCI Express**

All PCI Express interfaces on the PL35Q motherboard are compliant with the PCI Express Base Specification Version 1.1.

- One PCI Express x16 graphics interface

- One PCI Express x4 interface

- One PCI Express x1 interface.

#### **CMOS RAM and RTC**

The chipset integrates real-time clock (RTC) and 256 bytes of CMOS RAM that is used by the BIOS to store configuration information. A replaceable lithium cell battery (type CR2032) backs up both the RTC and the CMOS RAM, and provides approximately 5 years of un-powered backup.

When available, the RTC and CMOS RAM are powered from the +3.3V standby power rather than the lithium battery cell. The system management hardware can monitor the lithium cell voltage directly.

One 1x3-pin Clear CMOS jumper is available to clear the CMOS from the BIOS RAM. By default, pins 1 and 2 are jumpered for normal system operation. To clear the CMOS, jumper pins 2 and 3.

**WARNING!** For an ATX power supply, you must completely shut down the system, remove the AC power cord and then clear the CMOS.

#### Firmware hub (FWH)

Q35 motherboards provide a 2MB Firmware Hub (FWH) via the SPI bus. The FWH uses the Intel FWH protocol and does not require an ISA bus. The BIOS ROM is stored in a 2MB flash memory chip. The system BIOS provides support for all functions and devices present on the Q35 motherboards.

#### Power management

#### **ACPI** power states

Table 22 shows the Advanced Configuration and Power Interface (ACPI) 3.0 power states that the Q35 motherboards support.

Table 22. Supported ACPI power states

|                            | VCC sta          | Supported ACPI states |                    |                    |                    |                    |                 |

|----------------------------|------------------|-----------------------|--------------------|--------------------|--------------------|--------------------|-----------------|

|                            | 12V/-12V/5V/3.3V | 5V standby            | G0/S0 <sup>1</sup> | G1/S3 <sup>2</sup> | G1/S4 <sup>3</sup> | G2/S5 <sup>4</sup> | G3 <sup>5</sup> |

| Full power                 | On               | On                    | Yes                | -                  | -                  | -                  | -               |

| Standby                    | Off              | On                    | -                  | Yes                | Yes                | Yes                | -               |

| Power off                  | Off              | Off                   | -                  | -                  | -                  | -                  | Yes             |

| Hard-switched power supply | On               | N/A                   | Yes                | -                  | -                  | -                  | -               |

| Hard-switched power supply | Off              | N/A                   | -                  | -                  | -                  | -                  | Yes             |

<sup>&</sup>lt;sup>1</sup> G0/S0 – Fully operational; working

For information about power consumption of major sources and power supply requirements, see *Electrical specifications* on page 12.

### ACPI wake-up

Q35 modules are capable of supporting these wake-up events from S3 and S5 sleep states by configuring the BIOS setup utility:

- Power button

- Onboard LAN. To wake on LAN, make sure that the embedded Ethernet is enabled in the BIOS setup utility and the Ethernet connection is available.

- PS/2 mouse and keyboard

- USB device wake up

<sup>&</sup>lt;sup>2</sup> G1/S3 — Standby (Suspend to RAM). Main memory is still powered. This state allows the resumption of work exactly where it was left at the start of standby.

<sup>&</sup>lt;sup>3</sup> G1/S4 — Non-volatile sleep (Suspend to disk). System context is saved to disk and power removed from all circuits except those required to resume.

<sup>&</sup>lt;sup>4</sup> G2/S5 – Soft off. All devices are un-powered. Memory contents and context are lost.

<sup>&</sup>lt;sup>5</sup> G3 – Mechanical off. System is un-powered with no standby rails. No wake-up is possible.

#### System management

The Q35 motherboard includes hardware system management functions using the Winbond W83627DHG chipset. These functions include monitoring system voltages, monitoring temperatures, and monitoring and controlling the system fan.

#### Voltage monitoring

Table 23 identifies the motherboard voltage rails that are monitored and explains how they are used.

| Voltage rail      | Usage on motherboard                                                                                                                                        |

|-------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------|

| +12V              | Fans, expansion slots                                                                                                                                       |

| -12V              |                                                                                                                                                             |

| +5V               | Processor voltage regulator, internal voltage regulator for chipset and system memory, internal logic, USB and video ports, expansion slots                 |

| +3.3V             | Internal voltage regulator for chipset and processor interface, firmware hub (FWH), clock generator, system monitor, audio, internal logic, expansion slots |

| 3.3Vsb            | 3.3V standby                                                                                                                                                |

| VBat_RTC          | CMOS battery voltage                                                                                                                                        |

| V <sub>core</sub> | Processor core voltage                                                                                                                                      |

| V_DIMM            | Memory voltage                                                                                                                                              |

Table 23. Monitored voltage rails

#### **Temperature monitoring**

Up to three thermal sensors can be used to monitor temperatures in the system.

- The first sensor measures the motherboard temperature, and is contained within the W83627DHG chipset. This is a localized reading dominated by the motherboard surface temperature around the component.

- The second sensor is located on the processor die to accurately measure the local die temperature. Since the local die temperature fluctuates rapidly with activity, the controller within the W83627DHG filters the signal to produce an average temperature.

- There are temperature deviations across the processor die that cannot be observed by this sensor. See Intel's processor datasheet for further information.

- The third sensor can be connected to the remote thermal sensor header. This sensor should be a silicon diode or transistor connected as a diode, such as a Fairchild MMBT3904 and is used to measure temperatures of the external device connected to the motherboard.

**Note:** In the BIOS setup utility, you can set a CPU temperature overheat threshold in the Advanced Features > Hardware Monitor menu. When this threshold temperature is reached, the system BIOS will activate the alarm system.

#### Fan control

The Q35 motherboards support three fan monitors that check the fan tachometer signals to determine the fan's rotational speed. The three monitors are assigned to the processor fan, system fan 1, and system fan 2.

Fan speed modes are controlled in the BIOS setup utility, Advanced Features > Hardware Monitor menu. By default, all fans run at the full speed.

*Note:* To configure the fan speed modes, be sure to use all 3-pin fans or all 4-pin fans.

#### Front panel connections and indicators

The Front panel I/O provides support for power switches and LED indicators via an internal 2x8-pin header. See *Front panel I/O header* on page 46 for the pinout definitions of this header.

#### Power switch

If a soft-switched power supply is used, a momentary switch should be connected between pins 1 and 2 of the power connector. When the switch is closed for more than about 4 seconds, the motherboard powers off—regardless of the state of the operating system. (The action of the switch is configurable in the BIOS.) This power off will cause any system context information to be lost.