# MOS INTEGRATED CIRCUIT $\mu PD71055$

#### **PARALLEL INTERFACE UNIT**

#### uPD71055

#### PARALLEL INTERFACE UNIT

The uPD71055 is a programmable parallel interface unit for use in microcomputer systems. The uPD71055 is provided with three I/O ports and is capable of operations ranging from basic input/output to high level operations using handshaking protocols. The uPD71055, fabricated by CMOS technology, realizes low power consumption.

#### FEATURES

- Three 8-bit I/O ports

- Three programmable operation modes

- Bit manipulation command

- Microcomputer compatible

- No-wait operation with uPD70108-10 and uPD70116-10

- CMOS

- Single power supply

#### ORDERING INFORMATION

| Part Number       | Package            | Recovery time [ns] |

|-------------------|--------------------|--------------------|

| uPD71055C         | 40-pin plastic DIP | 200                |

| uPD71055C-10      | 40-pin plastic DIP | 150                |

| uPD71055GB-3B4    | 44-pin plastic QFP | 200                |

| uPD71055GB-10-3B4 | 44-pin plastic QFP | 150                |

| uPD71055L         | 44-pin PLCC        | 200                |

| uPD71055L-10      | 44-pin PLCC        | 150                |

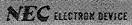

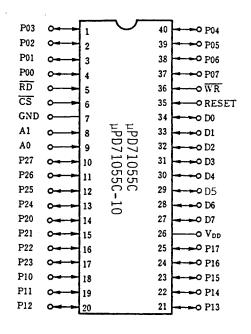

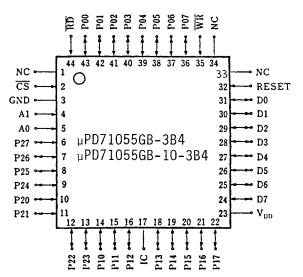

#### PIN CONFIGURATION (Top View)

Pin Identification

| D7 | to D0: | Data Bus     | RESET :     | Reset  |

|----|--------|--------------|-------------|--------|

| RD | :      | Read Strobe  | P07 to P00: | Port 0 |

| WR | :      | Write Strobe | P17 to P10: | Port 1 |

| CS | :      | Chip Select  | P27 to P20: | Port 2 |

A1, A0 : Address NC : Non-connection

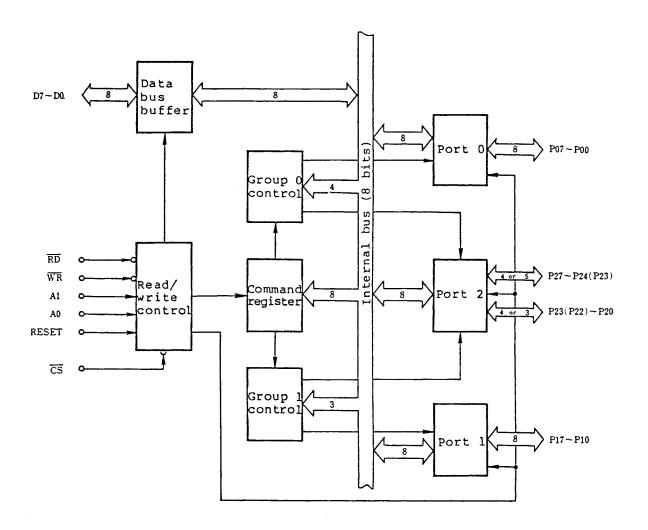

#### BLOCK DIAGRAM

#### 1. PIN FUNCTIONS

#### 1.1 D7 to D0 (data bus) - Three-state input/output

These pins form an 8-bit, three-state, bidirectional data bus. They are connected to the system data bus and are used for data communication. Active when CS=0 and RD=0 or WR=0, otherwise these pins enter the high impedance.

#### 1.2 CS (chip select) - Input

This signal is used to select the uPD71055. When CS=0, the uPD71055 is selected. CS=1 indicates nonselect and causes the lines of the data bus to become high impedance.

#### 1.3 RD (read strobe) - Input

This signal is logic 0 when a read operation of data from the uPD71055 is being performed.

#### 1.4 WR (write strobe) - Input

When data are to be written to the uPD71055, a logic 0 signal should be input to this pin. The contents of the data bus are then written to the uPD71055 at the rising edge (from 0 to 1) of the WR signal.

#### 1.5 Al, AO (address) - Input

These two inputs are used in combination with the RD and WR signals and select from among the three ports and the command register. These pins are normally connected to the lower 2 bits (A1, A0) of the system address bus.

#### 1.6 RESET (reset) - Input

When the input to the RESET pin become high level, the group 0 and group 1 ports are set to mode 0 (basic I/O port mode) and all ports are set for input.

#### 1.7 P07 to P00 (Port 0) - Three-state input/output

These are the port 0 input/output pins.

- 1.8 P17 to P10 (Port 1) Three-state input/output These are the port 1 input/output pins.

- 1.9 P27 to P20 (Port 2) Three-state input/output

These are the port 2 input/output pins.

- 1.10 IC (Internally Connected)

This pin must be left unconnected.

#### 2. BLOCK FUNCTIONS

The uPD71055 is designed to be used as a parallel interface between a microcomputer system and its peripheral devices. Because the uPD71055 can be controlled by the program of the microcomputer system, external logic circuits can be reduced to a minimum. The uPD71055 consists of these five blocks: the data bus buffer, the read/write control, the command register, group control, and three I/O ports.

#### 2.1 Data Bus Buffer

This is an 8-bit, three-state, bidirectional buffer that serves as an interface between the uPD71055 and the system data bus. When the CPU executes IN or OUT instructions for the uPD71055, the data is sent or received via this buffer.

#### 2.2 Read/Write Control

This block decodes the data input from the system bus and controls the data bus buffer data direction, the command register, and the three ports.

#### 2.3 Command Register

Command words sent from the CPU are written to this register. Then, in accordance with the command, control signals are sent either to the group 0 control, the group 1 control, or to both. Note that the contents of this register cannot be read.

#### 2.4 Group 0 Control, Group 1 Control

These blocks control the operation of the group 0 and group 1 ports in accordance with the mode set for each group.

#### 2.5 Ports 0, 1, 2

The uPD71055 has three 8-bit I/O ports, referred to as port 0, port 1, and port 2. These ports are further divided into two groups with port 0 and the higher bits of port 2 belonging to group 0, and port 1 and the lower bits of port 2 belonging to group 1. Modes can be set independently for each group. There is also a bit manipulation instruction that can be used for bit-wise set/reset operations for port 2.

#### 3. READ/WRITE TO THE uPD71055

To access the uPD71055, the CS signal should first be set to 0. Then the WR or RD signal should be set to 0 to specify a write or read operation. The input at the A1 and A0 pins specifies the port or command register to which the read or write operation is to be performed. When a write operation is performed to the command register, it is assumed that the data written is a command word.

Table 3-1 Control Signals and Operation

| CS | RD | WR | A1 | Α0 | Operation                   | CPU Operation |  |  |  |  |

|----|----|----|----|----|-----------------------------|---------------|--|--|--|--|

| 0  | 0  | 1  | 0  | 0  | Port 0 Data bus             | Input         |  |  |  |  |

| 0  | 0  | 1  | 0  | 1  | Port 1 — Data bus           | Input         |  |  |  |  |

| 0  | 0  | 1  | 1  | 0  | Port 2 - Data bus           | Input         |  |  |  |  |

| 0  | 0  | 1  | 1  | 1  | Mac probibited              |               |  |  |  |  |

| 0  | 0  | 0  | х  | х  | Use prohibited              |               |  |  |  |  |

| 0  | 1  | 0  | 0  | 0  | Data bus Port 0             | Output        |  |  |  |  |

| 0  | 1  | 0  | 0  | 1  | Data bus — Port 1           | Output        |  |  |  |  |

| 0  | 1  | 0  | 1  | 0  | Data bus — Port 2           | Output        |  |  |  |  |

| 0  | 1  | 0  | 1  | 1  | Data bus — Command register | Output        |  |  |  |  |

| 0  | 1  | 1  | х  | х  |                             |               |  |  |  |  |

| 1  | х  | х  | х  | х  | Data bus high impedance     |               |  |  |  |  |

x: don't care

#### 4. uPD71055 COMMANDS

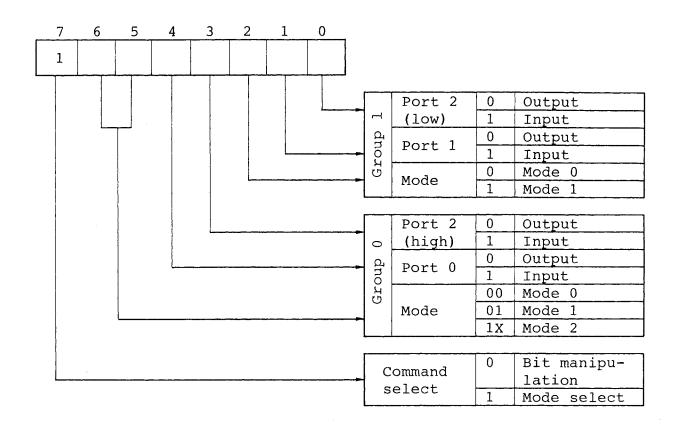

The uPD71055 is provided with two commands that it uses to control its own operation. These are the mode select command that determines the operation of the group 0 and group 1 ports and the other is the bit manipulation command that sets/resets the bits of port 2. Both of these commands are executed by writing an 8-bit command word to the command register.

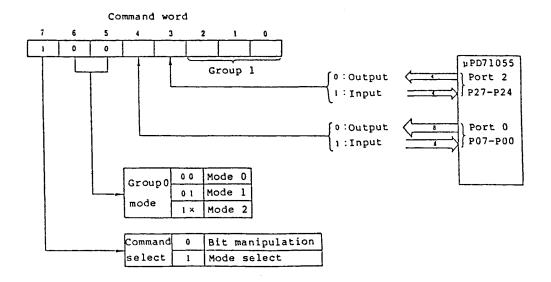

#### 4.1 Mode Select

The uPD71055 has three modes that can be specified for the different groups. Mode 2, however, can only be specified for group 0.

#### (1) Mode 0

Specifies basic input/output port operation.

#### (2) Mode 1

Specifies operation controlled by a control/status signal (4 or 3 bits of port 2).

#### (3) Mode 2

This mode can only be specified for group 0 and specifies port operation in which the higher 5 bits of port 2 are used for control and status signals and port 0 is used as a bidirectional I/O port.

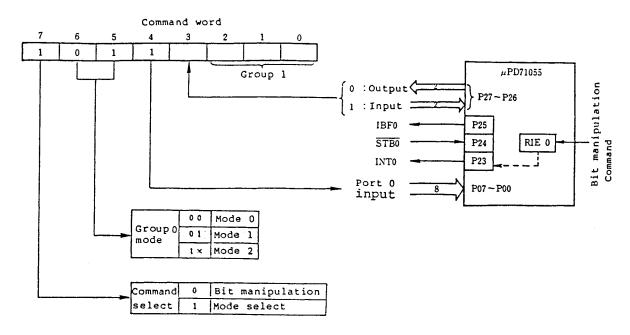

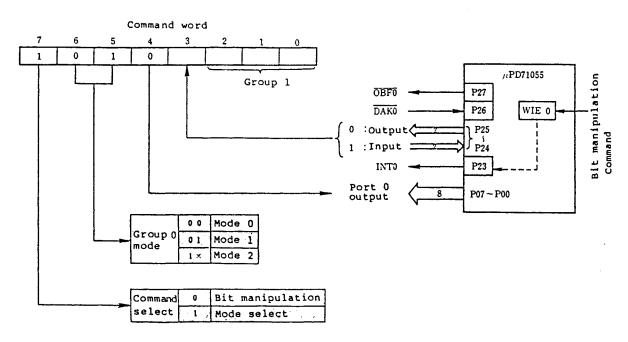

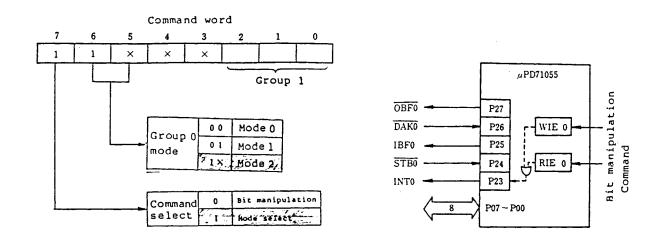

To specify the mode, set bit 7 of the command word to '1' and then write to the command register (A1A0=11) setting the value of each bit in accordance with the values shown in Fig. 4-1.

Fig. 4-1 Mode Select Command Word

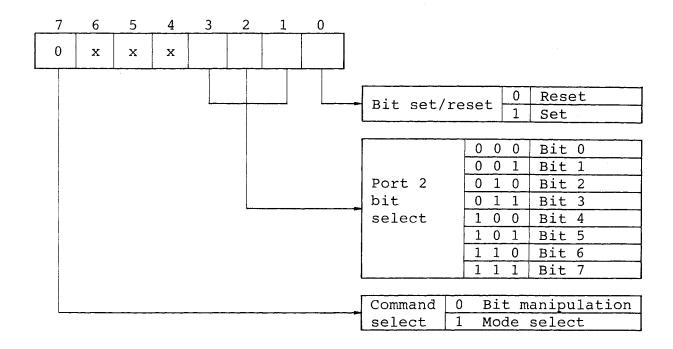

#### 4.2 Bit Manipulation Command

This command port 2. This type of operation is especially useful in mode 1 and mode 2 where the bits of port 2 are used as control/status signals. By executing this command, interrupts can be enabled and disabled from the CPU. Also, since direct write to port 2 (AlA0=10) is only possible in mode 0, this command can be used in mode 1 to directly write 1- or 2-bit output values.

Fig. 4-2 Bit Manipulation Command Word

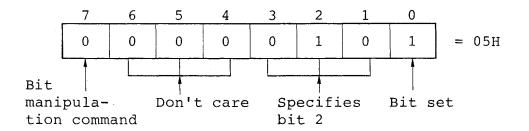

For example, to set bit 2 of port 2 to '1', the command word shown below (05H) should be set in the command register.

Fig. 4-3 Bit Manipulation Instruction Example

#### Note:

The bits of all ports are cleared when the PD71055 is reset, or when mode selection is performed.

#### 5. OPERATION IN EACH MODE

In the uPD71055, the operation mode for each group can be set according to the application. The following mode setting combinations are possible:

- (1) Group 0: mode 0; group 1: mode 0

- (2) Group 0: mode 0; group 1: mode 1

- (3) Group 0: mode 1; group 1: mode 0

- (4) Group 0: mode 1; group 1: mode 1

- (5) Group 0: mode 2; group 1: mode 0

- (6) Group 0: mode 2; group 1: mode 1

The RD and WR signals that appear in the descriptions of each mode refer to the RD and WR signals of the port in question; these same signals for other ports are not affected.

Where the port in question is not clear, a numeric value in the range 0 to 2 is appended to the end of the signal name to

#### 5.1 Mode 0

indicate the port.

In this mode the ports of the uPD71055 are used to perform basic input/output operations. Each port operates with a bufferred input and a latched output.

According to the control word sent from the CPU, port 0, port 1, and the higher and lower 4 bits of port 2 can be independently specified for input or output.

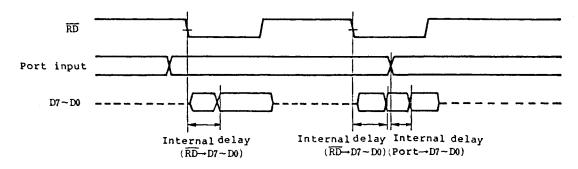

#### (1) Input port operation

While the RD signal of a port specified for input is low level, data is taken into the port and the data of the port selected by the AOA1 signals is output to the data bus.

Fig. 5-1 Mode 0 Input Timing

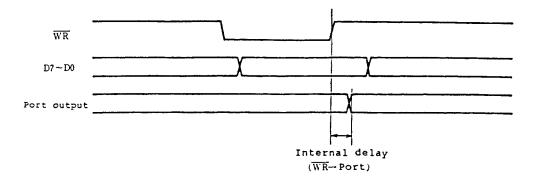

#### (2) Output port operation

Ports specified for output constantly latch output values and output these to the port pins. When the CPU sets WR to low level and sends new data to the uPD71055, this data will be latched in the port selected by the AOA1 signals at the rising edge of WR and output to the port pins.

Low level is output immediately after the mode setting.

Fig. 5-2 Mode 0 Output Timing

By reading the contents of the ports set for output, the output value of the port can be ascertained.

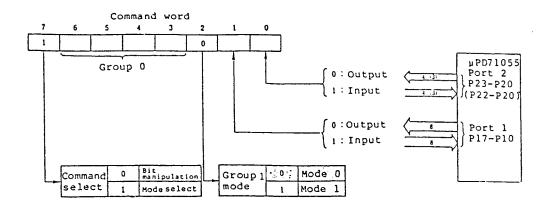

#### (3) Group 0 mode 0

Fig. 5-3 Group 0 Mode 0

Fig. 5-4 Group 1 Mode 0

#### Note:

When group 0 is not set to mode 0, the bits of port 2 that can be used by group 1 are the 3 bits P22-P20.

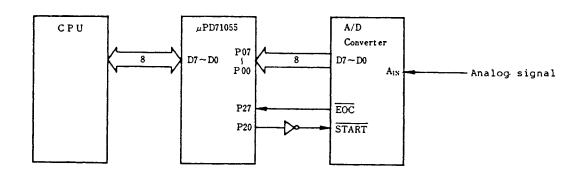

#### (5) Mode 0 example

This is an example of connecting a CPU to an A/D converter. Here group 0 and group 1 are both set to mode 0 and port 2 is used to start conversion and detect termination of the conversion process.

Fig. 5-5 A/D Converter Connection Example

This program is a subroutine that reads the converted data from an A/D converter.

| READ_A/D:MOV<br>OUT<br>MOV<br>OUT<br>MOV<br>OUT | AL,10011000B CTRLPORT,AL AL,00000001B CTRLPORT,AL AL,00000000B CTRLPORT,AL | uPD71055 mode setting o Group 0, group 1: mode 0 o Port 0, port 2 (high): input o Port 1, port 2 (low): output Conversion start  START |

|-------------------------------------------------|----------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------|

| WAIT_EOC:IN TEST1 BNZ IN RET                    | AL, PORT2 AL, 7 WAIT_EOC AL, PORT0                                         | End of conversion wait loop  Conversion  EOC ends  Read A/D converted values                                                           |

#### 5.2 Mode 1

In this mode, control and status signals are used to control data input/output. In group 0, the bits of port 0 function as the data port (for data input/output) and the higher 5 bits of port 2 as the control/status. In group 1, the bits of port 1 function as the data port and the lower 3 bits of port 2 as the control/status.

In mode 1, the bit manipulation instruction is used to write the bits of port 2.

Table 5-1 Functions of Port 2 in Mode 1

| Bit  | During data input                                     | During data output                                               |

|------|-------------------------------------------------------|------------------------------------------------------------------|

| P20  | INT1 (INTerrupt request)                              | INT1 (INTerrupt request)                                         |

| P21  | IBF1 (Input Buffer Full F/F)                          | OBF1 (Output Buffer Full F/F)                                    |

| P22  | STB1 (STroBe input) RIE1 (Read Interrupt Enable flag) | DAK1 (Data AcKnowledge input) WIE1 (Write Interrupt Enable flag) |

| P23* | Input/output                                          | Input/output                                                     |

| P23  | INTO (INTerrupt request)                              | INTO (INTerrupt request)                                         |

| P24  | STBO (STruBe input) RIEO (Read Interrupt Enable flag) | Input/output                                                     |

| P25  | IBFO (Input Buffer Full F/F)                          | Input/output                                                     |

| P26  | Input/output                                          | DAKO (Data AcKnowledge input) WIEO (Write Interrupt Enable flag) |

| P27  | Input/output                                          | OBFO (Output Buffer Full F/F)                                    |

<sup>\*</sup> Can only be used when group 0 is set to mode 0. At all other times, P23 belongs to group 0.

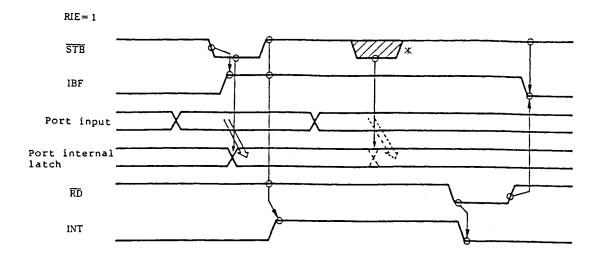

#### (1) Operation when data port is specified for input

When the data port (port 0 for group 0, and port 1 for group 1) is specified for input, the 8 bits of the data port are used for input. The bits of the control/status port (port 2) are used as follows:

- (a) STB (strobe input) input [STB0 P24, STB1 P22]

When this input is low level, the signals being sent form the peripheral to the data port are latched.

- (b) IBF (input buffer full F/F) output  $[\overline{1BF0} P25, \overline{STB1} P21]$ This output becomes high level to inform the peripheral that the input buffer has become full and to prohibit further data transfer. This signal becomes high level at the falling edge of the STB signal and becomes low level at the rising edge of the RD signal when STB=1 (CPU completes read).

Initial value immediately after the mode setting is low level.

- (c) INT (interrupt request) output [INTO → P23, INT1 → P20]

This output becomes high level when the data from the peripheral is latched in the input port and functions as a data read request interrupt signal to the CPU. INT become high level when RIE (read interrupt enable flag) is 1 and STB, IBF and RD are all high. INT becomes low level at the falling edge of the RD signal. Initial value immediately after the mode setting is low level.

(d) RIE (read interrupt enable flag) [RIEO - P24, RIE1 - P22]

is not affected.

This is a read interrupt enable flag for read operation by the CPU. This bit controls interrupt request output to the CPU. Interrupts can be enabled by using the bit manipulation command to set this bit to '1' and disabled by resetting this bit to '0'. Even if RIE is set/reset, the STB function of this bit

Fig. 5-6 Mode 1 Input Timing

\* Here if STB becomes low level before IBF becomes low, the contents of the port latch will change. STB must therefore be kept high until IBF becomes low.

When input is specified in mode 1, the status of IBF, INT, and RIE can be ascertained by reading the contents of port 2.

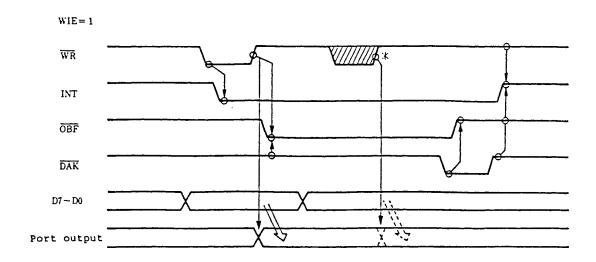

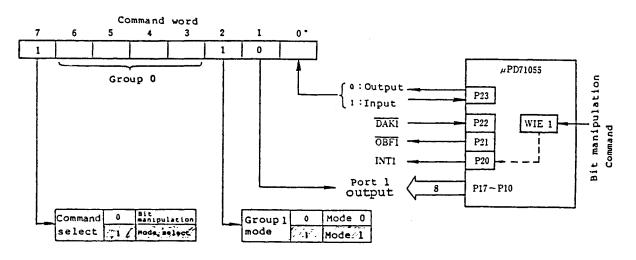

(2) Operation when data port is specified for output

When the data port (Port 0 for group 0; Port 1 for group 1) is specified for output, the 8 bits of the data port are used for output (low level is output immediately after the mode setting) and the bits of the control/status port (port 2) function as follows:

(a)  $\overline{\text{OBF}}$  (output buffer full F/F) - output  $[\overline{\text{OBF0}} + P27, \overline{\text{OFB1}} + P21]$

This signal become low when data is received from the CPU and is latched in the output port. OBF therefore functions as a data receive request to the peripheral. OBF becomes low level at the rising edge of WR when DAK=1 (CPU completes write) and becomes high at the falling edge of the DAK signal when the peripheral receives the data from the uPD71055.

Initial value immediately after the mode setting is high level.

- (b) DAK (data acknowledge) input [DAK0 P26, DAK1 P20]

This input is used to inform the uPD71055 that output port data has been received by the peripheral. The peripheral must be set so that it outputs a low level signal when it has received data.

- (c) INT (interrupt request) output [INTO P23, INT1 P20]

This output becomes high level when the output data from the uPD71055 has been received by the peripheral. INT therefore functions as a write request signal to the CPU indicating that it should send the next output data to the uPD71055. INT becomes high level when WIE (write interrupt enable flag) is set to '1' and WR, OBF, and DAK are all high and becomes low level at the falling edge of the WR signal.

Initial value immediately after the mode setting is low level.

(d) WIE (write interrupt enable flag) [WIE0 - P26, WIE1 - P22]

This is a request interrupt enable flag for write operation by the CPU. This bit controls interrupt request output to the CPU. Interrupts can be enabled by using the bit manipulation command to set this bit to '1' and disabled by resetting this bit to '0'. Even if RIE is set/reset, the DAK function of this bit is not affected.

Fig. 5-7 Mode 1 Output Timing

\* If data is written from the CPU before OBF becomes high, the contents of the port latch will change. Data write must therefore not be performed while OBF is low.

When output is specified in mode 1, the status of OBF, INT, and WIE can be ascertained by reading the contents of port 2.

#### (3) Group 0 mode 1

When group 0 is used in mode 1, the higher 5 bits of port 2 become part of group 0. Of these 5 bits, 3 are used as control/status and the remaining 2 bits can be used by the user for input/output (bit manipulation instruction).

(a) To input from the data port (port 0)

Fig. 5-8 Group 0 Mode 1 Input

(b) To output from the data port (port 0)

Fig. 5-9 Group 0 Mode 1 Input

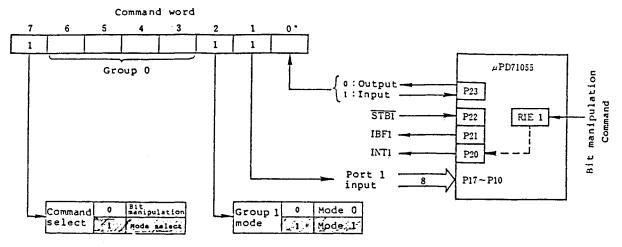

#### (4) Group 1 mode 1

When group 1 is used in mode 1, the lower 4 bits of port 2 become part of group 1. Of these 4 bits, 3 are used as control/status and the remaining 1 bit\* can be used by the user for input/output (bit manipulation command).

(a) To input from the data port (port 1)

Fig. 5-10 Group 1 Mode 1 Input

(b) To output from the data port (port 1)

Fig. 5-11 Group 1 Mode 1 Input

\* P23 belongs to group 1 only when group 0 is in mode 0, otherwise P23 belongs to group 0.

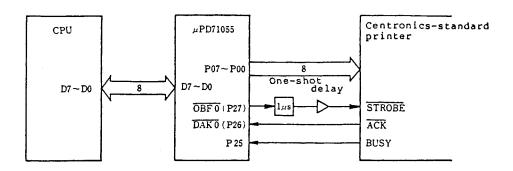

#### (5) Mode 1 examples

This is an example of connecting a printer with a Centronics interface. Group 0 is used in mode 1. Group 1 can operate in any mode; in this example mode 0 is set.

Fig. 5-12 Connection to a Printer

The program shown below is as subroutine that sends character strings to the printer.

|         |       |                | uPD71055 mode setting             |

|---------|-------|----------------|-----------------------------------|

| INIT:   | MOV   | AL, 10101000B) | o Group 0: mode 1                 |

|         | OUT   | CTRLPORT, AL   | o Port 0: output                  |

|         | RET   |                | o Port 2 (high): input            |

| SENDPRN | : MOV | BW, DATA       | Output data address               |

| PRNLOOP | :MOVE | AL,[BW]        |                                   |

|         | CMP   | AL, OFFH       | End if data FFH                   |

|         | BNZ   | WAIT           |                                   |

|         | RET   |                |                                   |

| WAIT:   | IN    | AL, PORT2      |                                   |

|         | TEST1 | AL,7           | Wait until output buffer is empty |

|         | BZ    | WAIT           | -                                 |

|         | TEST1 | AL,5           | Wait until printer can            |

|         | BNZ   | WAIT           | accept data                       |

|         | MOV   | AL,[BW]        | Send data to printer              |

|         | OUT   | PORTO,AL       |                                   |

|         | INC   | BW             |                                   |

|         | BR    | PRNLOOP        |                                   |

#### 5.3 Mode 2

This mode can only be used for group 0. In this mode port 0 functions as a bidirectional 8-bit data port operating under the control of the control/status signals (higher 5 bits of port 2). In this mode, port 0 combines the input and output operations of mode 1.

| Bit | Function                                                         |

|-----|------------------------------------------------------------------|

| P23 | INTO (INTerrupt request)                                         |

| P24 | STBO (StroBe input) RIEO (Read Interrupt Enable flag)            |

| P25 | IBF0 (Input Buffer Full F/F)                                     |

| P26 | DAKO (Data AcKnowledge input) WIEO (Write Interrupt Enable flag) |

| P27 | OBFO (Output Buffer Full F/F)                                    |

Table 5-2 Functions of Port 2 in Mode 2

The DAKO and STBO signals are used to select input or output mode for port 0. By using these signals, bidirectional operation between the CPU and the peripheral can be realized. In mode 2, the bit manipulation instruction is used to write to port 2.

- (1) Operation of the control/status port

- o Signals used when port 0 is used for output

- (a) OBFO (output buffer full F/F) output [P27]

This signal becomes low level when data is received from the  $\underline{CPU}$  and is latched in the port 0 output buffer.  $\underline{OBF0}$  therefore functions as a receive request signal to the peripheral.  $\underline{OBF0}$  becomes low level at the rising edge of the  $\underline{WR0}$  signal (indicates the end of CPU data write) and becomes high level at the falling edge of the  $\underline{DAK0}$  signal (indicates that the peripheral has received the output data from port 0).

Initial value immediately after the mode setting is high level.

(b) DAKO (data acknowledge) - input [P26]

When this input becomes low level, the three-state output buffer is set for output mode. This signal is sent from the peripheral in response to the OBFO signal from the uPD71055 and should be set to become low level when data is received from port 0.

(c) WIEO (write interrupt enable flag) [P26]

This is a write interrupt enable flag for write operation by the CPU. This bit controls interrupt request output to the CPU. This bit controls interrupt request output to the CPU. Interrupts can be enabled by using the bit manipulation command to set this bit to '1' and disabled by resetting this bit to '0'.

Even if WIEO is set/reset, the DAKO function of this bit is not affected.

- o Signals used when port 0 is used for input

- (d) STBO (strobe input) input [P24]

When this signal becomes low level, the data signals being sent from the peripheral to port 0 are latched.

(e) IBFO (input buffer full F/F) - output [P25]

When this output becomes high level, it indicates that the input buffer is full and functions as a transfer prohibit signal to the peripheral. This signal becomes high level at the falling edge of the STBO signal and becomes low level at the rising edge of the RDO signal when STBO=1 (CPU completes read). Initial value immediately after the mode setting is low level.

(f) RIEO (read interrupt enable flag) - [P24]

This is a read interrupt enable flag for read operation by the CPU. This bit controls interrupt request output to the CPU. Interrupts can be enabled by using the bit manipulation command to set this bit to '1' and disabled by resetting this bit to '0'. Even if RIEO is set/reset, the STBO function of this bit is not affected.

- o Signal used for both input and output

- (g) INTO (interrupt request) output [P23]

This signal is used for both input and output operations of port 0. During input operation, it functions as a read request interrupt signal to the CPU and during output as a write request interrupt signal. The output of this signal is the logical sum (OR) of the INT signal during input operation and the INT signal during output operation in mode 1. Initial value immediately after the mode setting is low level.

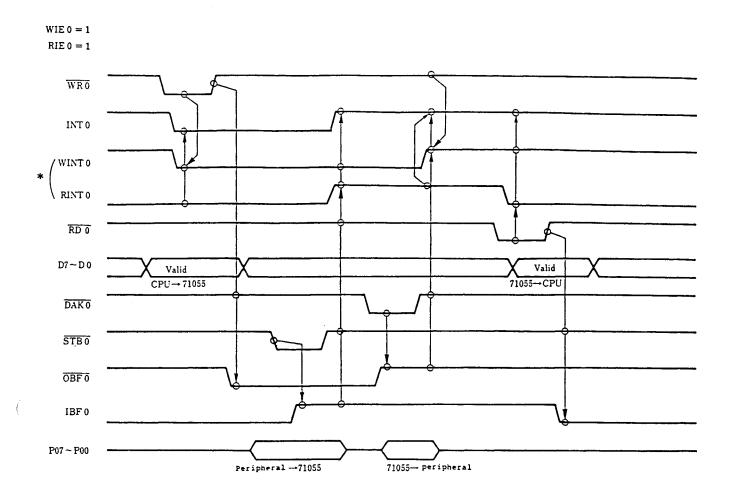

\* WINTO and RINTO are internal signals and are write and read interrupt request signals to the CPU, respectively.

WINTO =  $\overline{\text{OBFO}}$  .  $\overline{\text{WIEO}}$  .  $\overline{\text{DAKO}}$  .  $\overline{\text{WRO}}$

$RINTO = IBFO \cdot REIO \cdot \overline{STBO} \cdot \overline{RDO}$

Also note that

INTO = WINTO + RINTO

Fig. 5-13 Mode 2 Timing

#### (2) Mode 2 specification

In this mode, the status of the following signals can be ascertained by reading port 2:  $\overline{\text{OBFO}}$ ,  $\overline{\text{IBFO}}$ ,  $\overline{\text{INTO}}$ ,  $\overline{\text{WIEO}}$ , and  $\overline{\text{RIEO}}$ .

Fig. 5-14 Group 0 Mode 2

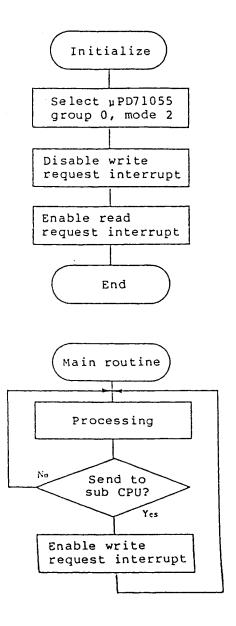

#### (3) Mode 2 example

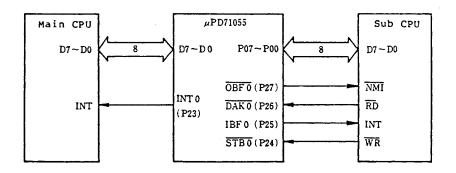

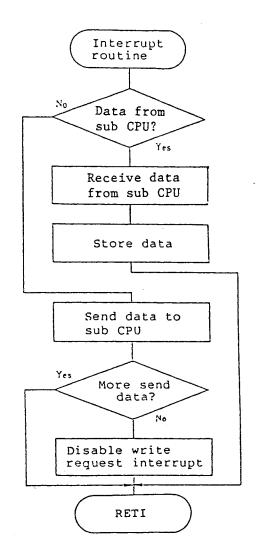

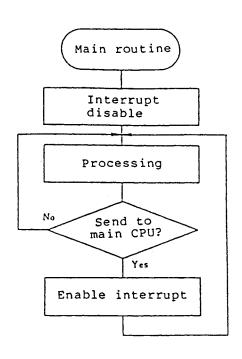

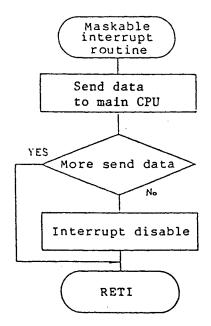

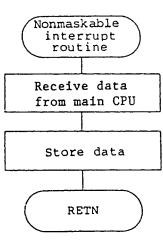

This is an example of transferring data between two CPUs.

Fig. 5-15 Connecting Two CPUs

#### Main CPU Flowchart

Sub CPU Flowchart

Table 6-1 Mode Combinations and Bit Functions of Port 2

Mode Combinations and Port 2 Bit Functions

|      | Group O |                 |                 |                 |                 |                 | Group 1 |         |                 |                 |                 |                 |  |

|------|---------|-----------------|-----------------|-----------------|-----------------|-----------------|---------|---------|-----------------|-----------------|-----------------|-----------------|--|

| Mode | P07-P00 | P2 <sub>7</sub> | P2 <sub>6</sub> | P2 <sub>5</sub> | P2 <sub>4</sub> | P2 <sub>3</sub> | Mode    | P17-P10 | P2 <sub>3</sub> | P2 <sub>2</sub> | P2 <sub>1</sub> | P2 <sub>0</sub> |  |

| 0    | In      | D               | D               | D               | D               | NA              | 0       | In      | D               | D               | D               | D               |  |

| 0    | In      | D               | D               | D               | D               | NA              | 0       | Out     | D               | D               | D               | D               |  |

| 0    | ln      | D               | D               | D               | D               | NA              | 1       | În      | В               | STB1<br>(RIE1)  | IBF1            | INT1            |  |

| 0    | ln      | D               | D               | D               | D               | NA              | 1       | Out     | В               | DAK1<br>(WIE1)  | ÖBF1            | INT1            |  |

| 0    | Out     | D               | D               | D               | D               | NA              | 0       | In      | D               | D               | D               | D               |  |

| 0    | Out     | D               | D               | D               | D               | NA              | 0       | Out     | D               | D               | D               | D               |  |

| 0    | Out     | D               | D               | D               | D               | NA              | 1       | In      | В               | STB1<br>(RIE1)  | IBF1            | INT1            |  |

| 0    | Out     | D               | D               | D               | D               | NA              | 1       | Out     | В               | DAK1<br>(WIE1)  | OBF1            | INT1            |  |

| 1    | ln      | В               | В               | IBF0            | STB0<br>(RIE0)  | INTO            | 0       | In      | NA              | D               | D               | D               |  |

| 1    | In      | В               | В               | IBF0            | STBO<br>(RIEO)  | INTO            | 0       | Out     | NA              | D               | D               | D               |  |

| 1    | In      | В               | В               | IBF0            | STB0<br>(RIE0)  | INTO            | 1       | in      | NA              | STB1<br>(RIE1)  | IBF1            | INT1            |  |

| 1    | In      | В               | В               | IBF0            | STB0<br>(RIE0)  | INTO            | 1       | Out     | NA              | DAK1<br>(WIE1)  | OBF1            | INT1            |  |

| 1    | Out     | OBF0            | DAKO<br>(WIEO)  | В               | В               | INT0            | 0       | In      | NA              | D               | D               | D               |  |

| 1    | Out     | OBF0            | DAKO<br>(WIEO)  | В               | В               | INTO            | ٥       | Out     | NA              | D               | D               | D               |  |

| 1    | Out     | 08F0            | DAKO<br>(WIEO)  | В               | В               | INTO            | 1       | In      | NA              | STB1<br>(RIE1)  | IBF1            | INT1            |  |

| 1    | Out     | 0BF0            | DAKO<br>(WIEO)  | В               | В               | INTO            | 1       | Out     | NA              | DAK1<br>(WIE1)  | OBF1            | INT1            |  |

| 2    | 1/0     | OBFO            | DAKO<br>(WIEO)  | IBF0            | STB0<br>(RIE0)  | INT0            | 0       | In      | NA              | D               | D               | D               |  |

| 2    | 1/0     | 0BF0            | DAKO<br>(WIEO)  | IBF0            | STB0<br>(RIE0)  | INT0            | 0       | Out     | NA              | D               | D               | D               |  |

| 2    | 1/0     | 08F0            | DAKO<br>(WIEO)  | IBF0            | STB0<br>(RIE0)  | INTO            | 1       | In      | NA              | STB1<br>(RIE1)  | IBF1            | INT1            |  |

| 2    | 1/0     | OBF0            | DAKO<br>(WIEO)  | IBF0            | STB0<br>(RIE0)  | INTO            | 1       | Out     | NA              | DAK1<br>(WIE1)  | OBF1            | INT1            |  |

#### Note:

<sup>(1)</sup> In this chart, "NA" indicates that the bit cannot be used by this group.

<sup>(2)</sup> The symbol "B" indicates bits that can only be rewritten by the bit manipulation command.

<sup>(3)</sup> In this chart, "D" indicates that is used by the user.

<sup>(4)</sup> Symbols in parentheses are internal flags.

<sup>(5)</sup> In indicates Input, Out indicates Output, and I/O indicates Input/Output.

#### ABSOLUTE MAXIMUM RATINGS (Ta = 25°C)

| PARAMETER             | SYMBOL         | TEST CONDITIONS | RATINGS                      | UNIT |

|-----------------------|----------------|-----------------|------------------------------|------|

| Power Supply Voltage  | V<br>DD        |                 | -0.5 to +7.0                 | V    |

| Input Voltage         | v <sub>I</sub> |                 | -0.5 to V <sub>DD</sub> +0.3 | V    |

| Output Voltage        | v <sub>O</sub> |                 | -0.5 to V <sub>DD</sub> +0.3 | V    |

| Operating Temperature | T<br>opt       |                 | -40 to +85                   | °C   |

| Storage Temperature   | T<br>stg       |                 | -65 to +150                  | °C   |

### DC CHARACTERISTICS (Ta = -40 to +85°C, $V_{DD}$ = 5V $\pm$ 10%)

| PARAMETER                   | SYMBOL   | TEST CONDITIONS          | MIN.           | TYP. | MAX.            | UNIT |

|-----------------------------|----------|--------------------------|----------------|------|-----------------|------|

| Input Voltage High          | VIH      |                          | 2.2            |      | V<br>DD<br>+0.3 | V    |

| Input Voltage Low           | V<br>IL  |                          | -0.5           |      | 0.8             | V    |

| Output Voltage High         | V        | I <sub>OH</sub> = -400uA | 0.7<br>V<br>DD |      |                 | V    |

| Output Voltage Low          | VOL      | I_OL = 2.5mA             |                |      | 0.4             | V    |

| Darlington Drive Current    | I<br>DAR | *                        | -1.0           |      | -4.0            | mA   |

| Input Leakage Current High  | I        | V=V<br>I DD              |                |      | 10              | uA   |

| Input Leakage Current Low   | ILIL     | v <sub>I</sub> =0v       |                |      | -10             | uA   |

| Output Leakage Current High |          | V =V                     |                |      | 10              | uA   |

| Output Leakage Current Low  | ILOH     | V <sub>I</sub> =0V       |                |      | -10             | uA   |

| Supply Current              | I<br>DD1 | Operation mode           |                | 5    | 10              | mA   |

DC CHARACTERISTICS (Ta = -40 to +85°C,  $V_{DD} = 5V \pm 10\%$ ) (Cont'd)

| PARAMETER      | SYMBOL   | TEST CONDITIONS                                           | MIN. | TYP. | MAX. | UNIT |

|----------------|----------|-----------------------------------------------------------|------|------|------|------|

| Supply Current | I<br>DD2 | Standby mode Inputs: RESET=0.1V Others=V DD Outputs: Open |      | 2    | 50   | uA   |

\* For up to 8 lines arbitrarily chosen from ports B and C.

#### CAPACITANCE

| PARAMETER         | SYMBOL | TEST CONDITIONS                | MIN. | TYP. | MAX. | UNIT |

|-------------------|--------|--------------------------------|------|------|------|------|

| Input Capacitance | CI     | fc = 1 MHz                     |      |      | 10   | рF   |

| I/O Capacitance   | CIO    | Unmeasured pins returned to OV |      |      | 20   | pF   |

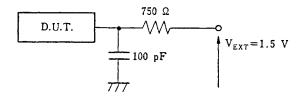

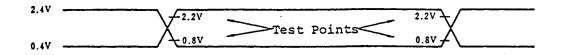

AC CHARACTERISTICS (Ta = -40 to +85°C,  $V_{DD}$  = 5V  $\pm$ 10%) READ CYCLE:

| DADAMEMUD               | CYMPOT   | TEST<br>CONDITIONS                  | uPD71055 |      | uPD71055-10 |      |      |

|-------------------------|----------|-------------------------------------|----------|------|-------------|------|------|

| PARAMETER               | SYMBOL   |                                     | MIN.     | MAX. | MIN.        | MAX. | UNIT |

| Address Set-up to RD    | t<br>SAR |                                     | 0        |      | 0           |      | ns   |

| Address Hold from RD    | t<br>HRA |                                     | 0        |      | 0           |      | ns   |

| RD Pulse Width          | t<br>RRL |                                     | 160      |      | 150         |      | ns   |

| Data Delay Time from RD | t<br>DRD | C <sub>L</sub> =150pF               |          | 120  |             | 100  | ns   |

| Data Float Time from RD | t<br>FRD | $C_L = 20pF$ $R_L = 2K \text{ ohm}$ | 10       | 85   | 10          | 60   | ns   |

| Read out Recovery Time  | t<br>RV  |                                     | 200      |      | 150         |      | ns   |

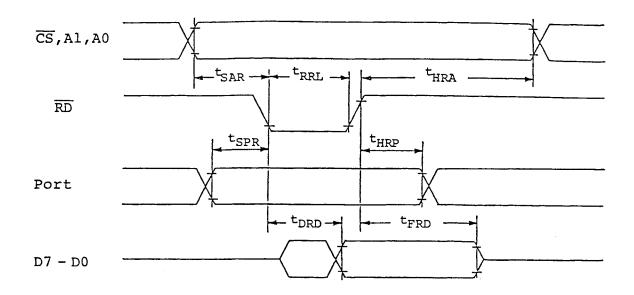

#### WRITE CYCLE:

|                        | a        | TEST<br>CONDITIONS | uPD71055 |      | uPD71055-10 |      |      |

|------------------------|----------|--------------------|----------|------|-------------|------|------|

| PARAMETER              | SYMBOL   |                    | MIN.     | MAX. | MIN.        | MAX. | UNIT |

| Address Set-up to WR   | t<br>SAW |                    | 0        |      | 0           |      | ns   |

| Address Hold from WR   | t<br>HWA |                    | 0        |      | 0           |      | ns   |

| WR Pulse Width         | t<br>WWL |                    | 120      |      | 100         |      | ns   |

| Data Set-up Time to WR | t        |                    | 100      |      | 100         |      | ns   |

| Data Hold Time from WR | t<br>HWD |                    | 0        |      | 0           |      | ns   |

| Write Recovery Time    | t<br>RV  |                    | 200      |      | 150         |      | ns   |

<sup>\*:</sup>  $\overline{CS}$ , Al and AO

AC CHARACTERISTICS (Ta = -40 to +85°C,  $V_{DD}$  = 5V  $\pm$ 10%) (Cont'd) OTHERS:

| PARAMETER                         | SYMBOL            | TEST                                    | uPD71055 |      | uPD71055-10 |      | IINTE |

|-----------------------------------|-------------------|-----------------------------------------|----------|------|-------------|------|-------|

| PARAMETER                         | PIMPOT            | CONDITIONS                              | MIN.     | MAX. | MIN.        | MAX. | UNIT  |

| Port Setup Time to RD             | t<br>SPR          |                                         | 0        |      | 0           |      | ns    |

| Port Hold Time from RD            | t<br>HRP          |                                         | 0        |      | 0           |      | ns    |

| Port Setup Time to STB            | t<br>SPS          |                                         | 0        |      | 0           |      | ns    |

| Port Hold Time from STB           | t <sub>HSP</sub>  |                                         | 150      |      | 150         |      | ns    |

| Port Delay Time from WR           | t<br>DWP          | $C_{L} = 150pF$                         |          | 350  | -           | 200  | ns    |

| STB Pulse Width                   | <sup>t</sup> ssL  |                                         | 350      |      | 100         |      | ns    |

| DAK Pulse Width                   | t<br>DADAL        |                                         | 300      |      | 100         |      | ns    |

| Port Delay Time from DAK (Mode 2) | t<br>DDAP         | C <sub>L</sub> = 150pF                  |          | 300  |             | 150  | ns    |

| Port Float Time from DAK (Mote 2) | t<br>FDAP         | $C_{L} = 20pF$ $R_{L} = 2K \text{ ohm}$ | 20       | 250  | 20          | 250  | ns    |

| OBF Set Delay from WR             | t <sub>DWOB</sub> |                                         |          | 300  |             | 150  | ns    |

| OBF Clear Delay from DAK          | t<br>DDAOB        |                                         |          | 350  |             | 150  | ns    |

| IBF Set Delay from STB            | t <sub>DSIB</sub> |                                         |          | 300  |             | 150  | ns    |

| IBF Clear Delay from RD           | t <sub>DRIB</sub> | $C_{T_i} = 150 pF$                      |          | 300  |             | 150  | ns    |

| INT Set Delay from DAK            | t <sub>DDAI</sub> |                                         |          | 350  |             | 150  | ns    |

| INT Clear Delay from WR           | t <sub>DWI</sub>  |                                         |          | 450  |             | 200  | ns    |

| INT Set Delay from STB            | t <sub>DSI</sub>  |                                         |          | 300  |             | 150  | ns    |

| INT Clear Delay from RD           | t <sub>DRI</sub>  |                                         |          | 400  |             | 200  | ns    |

| RESET Pulse Width                 | t<br>RESET1       | *1                                      | 50       |      | 50          |      | us    |

| TODDI LAISE MIACII                | t<br>RESET2       | *2                                      | 500      |      | 500         |      | ns    |

<sup>\*1:</sup> During power-on or right after power-on\*2: During operation

#### AC TEST INPUT WAVEFORM

#### TIMING

MODE 0: Input

MODE 0: Output

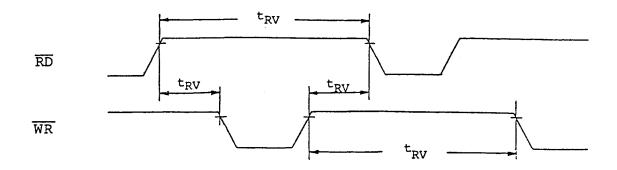

#### RECOVERY TIME

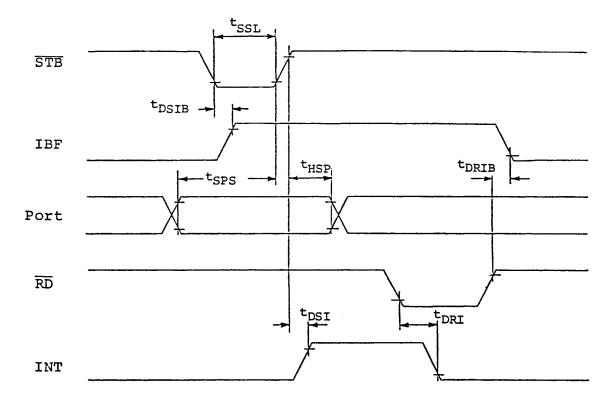

MODE 1: Input

MODE 1: Output

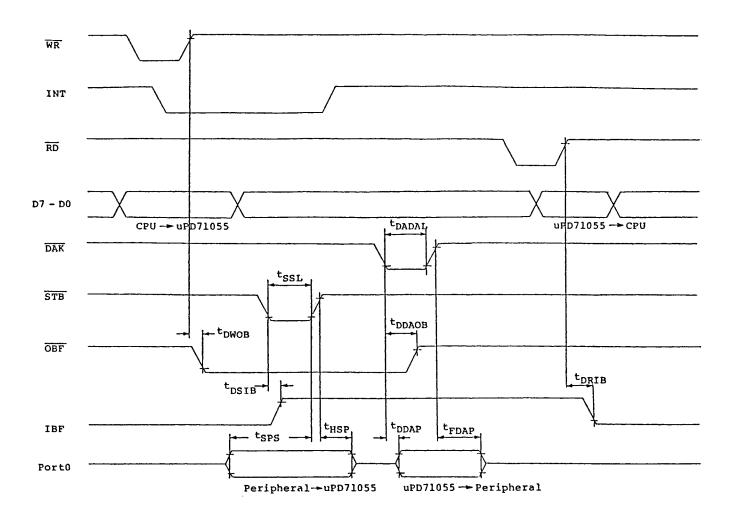

#### MODE 2:

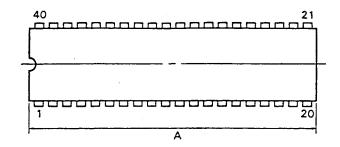

#### PACKAGE OUTLINES

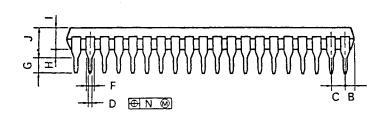

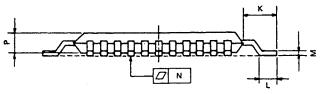

#### 40-pin Plastic

P40C-100-600A

#### **NOTES**

- Each lead centerline is located within 0.25 mm (0.01 inch) of its true position (T.P.) at maximum material condition.

- 2) Item "K" to center of leads when formed parallel.

| ITEM | MILLIMETERS            | INCHES       |

|------|------------------------|--------------|

| Α    | 53.34 MAX.             | 2.100 MAX.   |

| В    | 2.54 MAX.              | 0.100 MAX.   |

| С    | 2.54 (T.P.)            | 0.100 (T.P.) |

| D    | 0.50 <sup>± 0.10</sup> | 0.020-0.004  |

| F    | 1.2 MIN.               | 0.047 MIN.   |

| G    | 3.6 <sup>-0.3</sup>    | 0.142 *0.012 |

| н    | 0.51 MIN.              | 0.020 MIN.   |

| 1    | 4.31 MAX.              | 0.170 MAX.   |

| J    | 5.72 MAX.              | 0.226 MAX.   |

| к    | 15.24 (T.P.)           | 0.600 (T.P.) |

| L    | 13.2                   | 0.520        |

| М    | 0.25 -0.05             | 0.010 -0.003 |

| N    | 0.25                   | 0.01         |

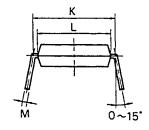

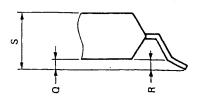

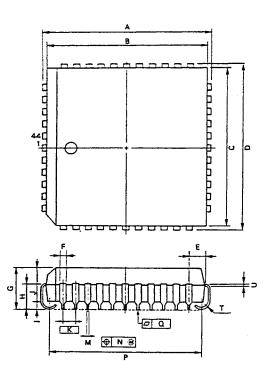

#### 44-pin Plastic QFP (bent lead)

#### detail of lead end

P44GB-80-3B4

## NOTE Each lead centerline is located within 0.15 mm (0.006 inch) of its true position (T.P.) at maximum material condition.

| ITEM | MILLIMETERS | INCHES        |

|------|-------------|---------------|

| A    | 13.6**      | 0.535:8816    |

| В    | 10***       | 0.394-888     |

| C    | 10**2       | 0.394:888     |

| D    | 13.6***     | 0.535-88%     |

| F    | 1.0         | 0.039         |

| G    | 1.0         | 0.039         |

| Н    | 0.35 20 10  | 0.014-888     |

| t    | 0.15        | 0.006         |

| J    | 0.8 (T.P.)  | 0.031 (T.P.)  |

| K    | 1.8***      | - 0.071:888   |

| L    | 0.8 * 6 \$  | 0.031-888     |

| М    | 0.15-00     | 0.006 -0 005  |

| N    | 0.15        | 0.006         |

| P    | 2.7         | 0.106         |

| Q    | 0.1101      | 0.004*****    |

| R    | 0.1 = 0.1   | 0.004 2 0 004 |

| s    | 3.0 MAX.    | 0.119 MAX.    |

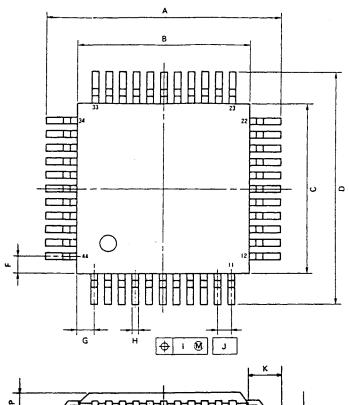

P44L-50A1

#### NOTE

Each lead centerline is located within 0.12 mm (0.005 inch) of its true position (T.P.) at maximum material condition.

| ITEM | MILLIMETERS            | INCHES                  |

|------|------------------------|-------------------------|

| Α    | 17.5 <sup>±0.2</sup>   | 0.689 <sup>±0.008</sup> |

| В    | 16.58                  | 0.653                   |

| С    | 16.58                  | 0.653                   |

| D    | 17.5 <sup>±0.2</sup> . | 0.689 <sup>±0.008</sup> |

| E    | 1.94 <sup>±0.15</sup>  | 0.076-0.007             |

| F    | 0.6                    | 0.024                   |

| G    | 4.4 <sup>±0.2</sup>    | 0.173-0.009             |

| Н    | . 2.8 <sup>±0.2</sup>  | 0.110-0.009             |

| I    | 0.9 MIN.               | 0.035 MIN.              |

| J    | 3.4                    | 0.134                   |

| К    | 1.27 (T.P.)            | 0.050 (T.P.)            |

| М    | 0.40 <sup>±0.10</sup>  | 0.016-0.004             |

| N    | 0.12                   | 0.005                   |

| Р    | 15.50 <sup>±0.20</sup> | 0.610-0.009             |

| a    | 0.15                   | 0.006                   |

| Т    | R 0.8                  | R 0.031                 |

| U    | 0.20+0.10              | 0.008 - 0.002           |