## 8284A/8284A-1

Clock Generator and Driver for 8086, 8088 Processors

#### DISTINCTIVE CHARACTERISTICS

- Generates the System Clock for the 8086, 8088 Processors: 5MHz, 8MHz with 8284A; 10MHz with 8284A-1

- Uses a crystal or a TTL signal for frequency source

Provides local READY and Multibus\* READY synchroni-

- Provides local READY and Multibus\* READY synchronization

- Generates system reset output from Schmitt trigger input

- Capable of clock synchronization with other 8284As

#### **GENERAL DESCRIPTION**

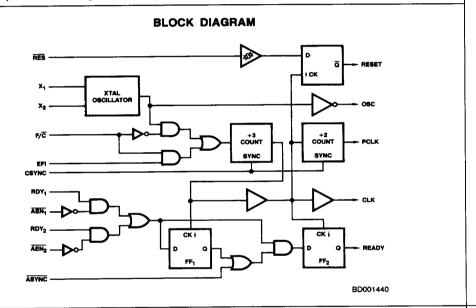

The 8284A is a single chip clock generator/driver for the 8086, 8088 processors. The chip contains a crystal-con-

trolled oscillator, a divide-by-three counter, complete MULTIBUS\* "Ready" synchronization and reset logic.

#### **RELATED AMD PRODUCTS**

| Part No. | Description           |

|----------|-----------------------|

| Am8086   | 16-Bit Microprocessor |

| 8288     | Bus Controller        |

\*MULTIBUS is a registered trademark of Intel Corp.

Publication # Rev. Amendment

03359 D /0

Issue Date: April 1987

3-389

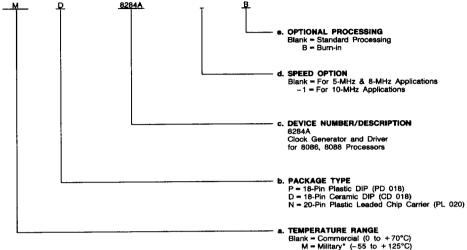

#### ORDERING INFORMATION

#### **Commodity Products**

AMD commodity products are available in several packages and operating ranges. The order number (Valid Combination) is formed by a combination of: a. Temperature Range

- b. Package Type

- c. Device Number

- d. Speed Option

- e. Optional Processing

| Valid Combinations |          |  |  |

|--------------------|----------|--|--|

| MD, D, P, N        | 8284A    |  |  |

| MD, D, P           | 8284AB   |  |  |

| D                  | 8284A-1  |  |  |

|                    | 8284A-1B |  |  |

#### Valid Combinations

Valid Combinations list configurations planned to be supported in volume for this device. Consult the local AMD sales office to confirm availability of specific valid combinations, to check on newly released valid combinations, and to obtain additional data on AMD's standard military grade products.

\* Military temperature range products are NPL (Non-Compliant Products List) or Non-MIL-STD-883C Compliant products only.

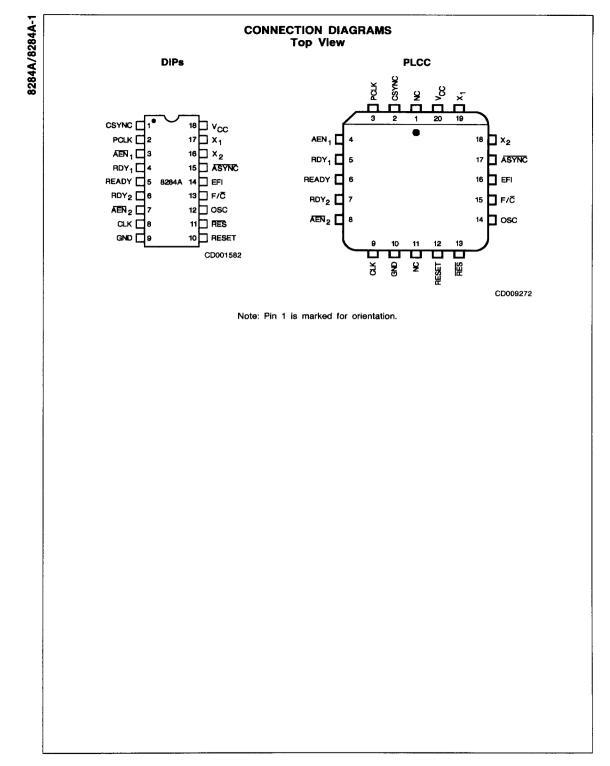

#### PIN DESCRIPTION

| Pin No. | Name                                   | 1/0 | Description                                                                                                                                                                                                                                                                                                                                                                            |

|---------|----------------------------------------|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 3, 7    | AEN <sub>1</sub> .<br>AEN <sub>2</sub> | -   | Address Enable. The AEN signal is used to qualify the Bus Ready signal (RDY <sub>1</sub> or RDY <sub>2</sub> ). AEN <sub>1</sub> validates RDY <sub>1</sub> while AEN <sub>2</sub> validates RDY <sub>2</sub> . It is possible for the processor to access two Multi-Master System Busses if you use both signals. Both signals are tied LOW in non Multi-Master Systems.              |

| 4, 6    | RDY <sub>1</sub> ,<br>RDY <sub>2</sub> | 1   | Bus Ready. These signals are indications from a device located on the system bus that it is available or data has been received. RDY <sub>1</sub> and RDY <sub>2</sub> are qualified by AEN <sub>1</sub> and AEN <sub>2</sub> respectively.                                                                                                                                            |

| 15      | ASYNC                                  | i   | Ready Synchronous Select. The ASYNC signal defines the synchronization mode of the READY logic. When ASYNC is open (Internal pull-up resistor is provided) or pulled HIGH, there is one stage of READY Synchronization. When ASYNC is LOW, there are two stages of READY Synchronization.                                                                                              |

| 5       | READY                                  | 0   | Ready. READY is the synchronized RDY signal input. After the guaranteed hold time to the processor has been met, the READY signal is cleared.                                                                                                                                                                                                                                          |

| 7, 16   | X <sub>1</sub> ,X <sub>2</sub>         | 1   | Crystal In. These are the input pins for the attached crystal. The crystal frequency is 3 times the desired process clock frequency.                                                                                                                                                                                                                                                   |

| 13      | F/C                                    | 1   | Frequency/Crystal Select. When F/C is strapped HIGH, CLK is generated from the EFI input. When strapped LOW, the F/C allows the processor clock to be generated by the crystal.                                                                                                                                                                                                        |

| 14      | EFI                                    | 1   | External Frequency. Used in conjunction with a HIGH signal on F/C, CLK is generated from the input frequency appearing on this pin. The input signal is a square wave 3 times the frequency of the desired CLK output.                                                                                                                                                                 |

| В       | CLK                                    | 0   | Processor Clock. CLK is the clock output used by the processor and all devices which directly connect to the processor's local bus (including bipolar support chips and other MOS devices). An output HIGH of 4.5V (V <sub>CC</sub> = 5V) is provided on this pin to drive MOS devices. The output frequency of CLK is 1/3 of the crystal on EFI input frequency and a 1/3 duty cycle. |

| 2       | PCLK                                   | 0   | Peripheral Clock. This signal is a TTL level peripheral clock signal whose output frequency is 1/2 that of CLK and has a 50% duty cycle.                                                                                                                                                                                                                                               |

| 12      | osc                                    | ٥   | Oscillator Output. This signal is the TTL level output of the internal oscillator circuitry. Its frequency is equal to that of the crystal.                                                                                                                                                                                                                                            |

| 11      | RES                                    | '   | Reset In. This signal is used to generate a RESET. The 8284A provides a Schmitt trigger input so that an RC connection can be used to establish the power-up reset of proper duration.                                                                                                                                                                                                 |

| 10      | RESET                                  | 0   | Reset. This signal is used to reset the 8086 family processors.                                                                                                                                                                                                                                                                                                                        |

| 1       | CSYNC                                  | ı   | Clock Synchronization. This signal is designed to allow multiple 8284As to be synchronized to provide clocks that are in phase. CSYNC HIGH will reset the internal counters, when CSYNC goes LOW the counters will resume counting. CSYNC needs to be externally synchronized to EFI. When used with the internal oscillator, CSYNC should be hard wired to ground.                    |

#### **DETAILED DESCRIPTION**

#### **OSCILLATOR**

The oscillator circuit of the 8284A is designed primarily for use with a fundamental mode, series resonant crystal from which the operating frequency is derived.

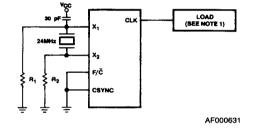

The crystal frequency should be selected at three times the required CPU clock.  $X_1$  and  $X_2$  are the two crystal input crystal connections. The output of the oscillator is buffered and brought out on OSC so that other system timing signals can be derived from this stable, crystal-controlled source.

Two  $510\Omega$  series resistors are optional for systems which have a V<sub>CC</sub> ramp time greater than (or equal to) 1V/ms and/or inherent board capacitance between X<sub>1</sub> or X<sub>2</sub> exceeding 10pF. This capacitance value should not include the 8284A's pin capacitance. By limiting the stray capacitance to less than 10pF on X<sub>1</sub> or X<sub>2</sub>, the deviation from the desired fundamental frequency is minimized.

#### **CLOCK GENERATOR**

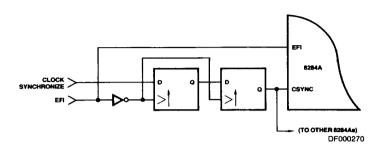

The clock generator consists of a synchronous divide-by-three counter with a special clear input that inhibits the counting. This clear input, (CSYNC), allows the output clock to be synchronized with an external event (such as another 8284A clock). It is necessary to synchronize the CSYNC input to the EFI clock external to the 8284A (see Figure 1). This is accomplished with two Schottky flip-flops. The counter output is a 33% duty cycle clock at one-third the input frequency.

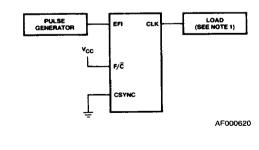

The F/ $\overline{C}$  input is a strapping pin that selects either the EFI input or the crystal oscillator as the clock for the  $\div$  3 counter. If the EFI input is selected as the clock source, the oscillator section can be used independently for another clock source. Output is taken from OSC.

#### **CLOCK OUTPUTS**

The CLK output is a 33% duty cycle MOS clock driver designed to drive the 8086 or 8088 processors directly. PCLK is a TTL level peripheral clock signal whose output frequency is ½2 that of CLK. PCLK has a 50% duty cycle.

#### RESET LOGIC

Reset logic for the 8284A is provided by a Schmitt trigger input (RES) and a synchronizing flip-flop to generate the reset timing.

The reset signal is synchronized to the falling edge of CLK. A simple RC network can be used to provide power-on reset by utilizing this function of the 8284A.

#### **READY SYNCHRONIZATION**

Two READY inputs (RDY<sub>1</sub>, RDY<sub>2</sub>) are provided to accommodate two Multi-Master system busses. Each input has a qualifier (AEN<sub>1</sub> and AEN<sub>2</sub>, respectively). The AEN signals validate their respective RDY signals. If a Multi-Master system is not being used the AEN pin should be tied LOW.

To assure RDY setup and hold times are met, synchronization is required for all asynchronous active going edges of either RDY input. Inactive-going edges of RDY (in normally ready systems) do not require synchronization, but must satisfy RDY setup and hold as a matter of proper system design.

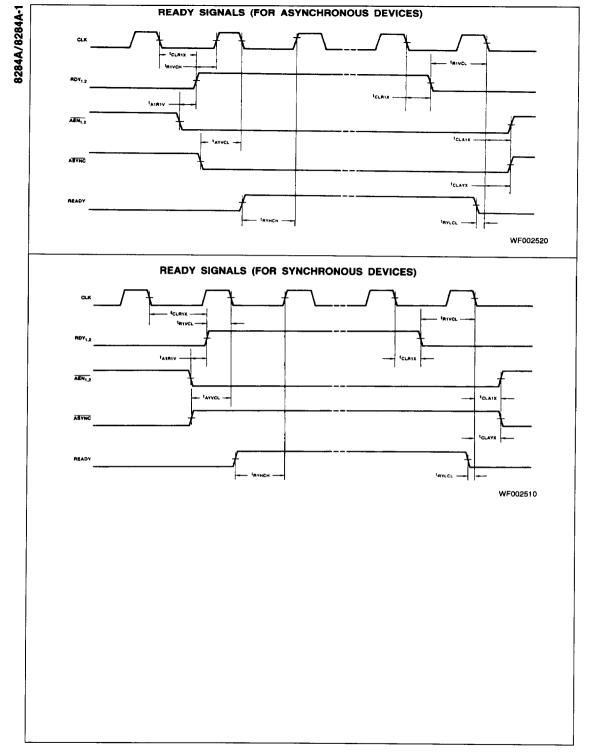

The two modes of RDY synchronization operation are defined by the ASYNC input.

When ASYNC is LOW, two stages of synchronization are provided for active RDY input signals. Positive-going asynchronous RDY inputs will first be synchronized to flip-flop one at the rising edge of CLK and then synchronized to flip-flop two at the next falling edge of CLK; after which time the READY output will go active (HIGH). Negative-going asynchro-

nous RDY inputs will be synchronized directly to flip-flop two at the falling edge of CLK, after which time the READY output will go inactive. This mode of operation is intended for use by asynchronous, (normally not ready), devices in the system which cannot be guaranteed by design to meet the required RDY setup timing to 11/00 on each bus cycle.

When ASYNC is high or left open, the first READY flip-flop is bypassed in the READY synchronization logic. RDY inputs are

synchronized by flip-flop two on the falling edge of CLK before they are presented to the processor. This mode is available for synchronous devices that can be guaranteed to meet the required RDY setup time.

ASYNC can be changed on every bus cycle to select the appropriate mode of synchronization for each device in the system.

Figure 1. CSYNC Synchronization

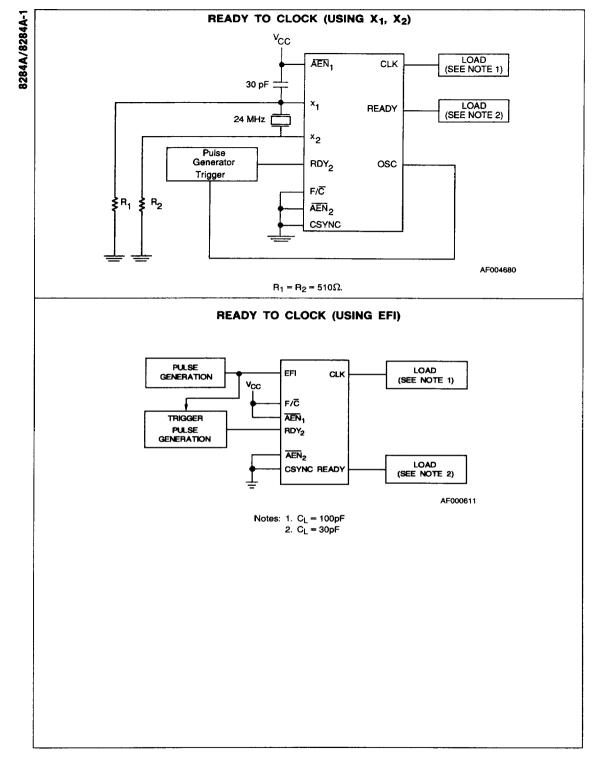

#### CLOCK HIGH AND LOW TIME (USING X1, X2)

$R_1 = R_2 = 510\Omega$ .

#### CLOCK HIGH AND LOW TIME (USING EFI)

3-393

# ABSOLUTE MAXIMUM RATINGS Storage Temperature ........-65°C to +150°C Ambient Temperature with Powers Applied (COML, A-1) ............0°C to +70°C (MIL) ......-55°C to +125°C All Output and Supply Voltages .....-0.5V to +7.0V

Stresses above those listed under ABSOLUTE MAXIMUM RATINGS may cause permanent device failure. Functionality at or above these limits is not implied. Exposure to absolute maximum ratings for extended periods may affect device reliability.

#### **OPERATING RANGES**

Commercial (C) Devices

| remperature          | 0 0 10 770 0     |

|----------------------|------------------|

| Supply Voltage       | +4.75V to +5.25V |

| ,,,,                 |                  |

| Military (M) Devices |                  |

| Temperature          | 55°C to +125°C   |

Supply Voltage ...... + 4.5V to +5.5V

Operating ranges define those limits between which the functionality and parameters of the device are guaranteed.

#### DC CHARACTERISTICS over operating ranges unless otherwise specified

| Parameters      | Description                   | Test Conditions                  | Min  | Max  | Units |  |

|-----------------|-------------------------------|----------------------------------|------|------|-------|--|

|                 | Forward Input Current (ASYNC) | V <sub>F</sub> = 0.45V           |      | -1.3 |       |  |

| lF              | Other Inputs                  | V <sub>F</sub> = 0.45V           |      | -0.5 | mA    |  |

|                 | Reverse Input Current (ASYNC) | V <sub>R</sub> = V <sub>CC</sub> |      | 50   |       |  |

| IR              | Other Inputs                  | V <sub>R</sub> = 5.25V           |      | 50   | μΑ    |  |

| Vc              | input Forward Clamp Voltage   | I <sub>C</sub> = -5mA            |      | -1.0 | Volts |  |

| lcc             | Power Supply Current          |                                  |      | 162  | mA    |  |

| VIL             | Input LOW Voltage             |                                  |      | 0.8  | Volts |  |

| V <sub>1H</sub> | Input HIGH Voltage            |                                  | 2.0  |      | Volts |  |

| VIHR            | Reset Input HIGH Voltage      |                                  | 2.6  |      | Volts |  |

| Vol             | Output LOW Voltage            | 5mA •                            |      | 0.45 | Volts |  |

| Voн             | Output HIGH Voltage CLK       | -1mA                             | 4.0  | 2.5  |       |  |

|                 | Other Outputs                 | -1mA                             | 2.4  |      | Volts |  |

| VIHR-VILR       | RES Input Hysteresis (Note 1) |                                  | 0.25 |      | Volts |  |

Note 1. This specification is provided for reference only.

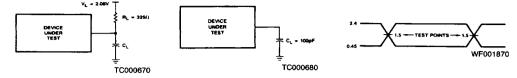

$C_L$  = 100pF for CLK  $C_L$  = 100pF AC testing inputs are driven at 2.4V for  $C_L$  = 30pF for READY a logic "1" and 0.45V for a logic "0". Timing measurements are made at 1.5V for both a logic "1" and "0".

### SWITCHING CHARACTERISTICS over operating ranges unless otherwise specified

#### TIMING REQUIREMENTS

8284A/824A-1

| Parameters         | Description                                               | Test Conditions          | Min                 | Тур      | Max | Units |

|--------------------|-----------------------------------------------------------|--------------------------|---------------------|----------|-----|-------|

| <sup>t</sup> EHEL  | External Frequency HIGH Time                              | 90% - 90%V <sub>IN</sub> | 13                  | +        |     | ns    |

| <sup>t</sup> ELEH  | External Frequency LOW Time                               | 10% - 10%VIN             | 13                  | <u> </u> |     | ns    |

| †ELEL              | EFI Period                                                | MIL (Note 1)             | tehet + teleh + δ   |          |     | ns    |

|                    |                                                           | COM'L, A-1               | 33                  | 1        |     |       |

|                    | XTAL Frequency                                            |                          | 12                  |          | 25  | MHz   |

| <sup>t</sup> R1VCL | RDY <sub>1</sub> , RDY <sub>2</sub> Active Setup to CLK   | ASYNC = HIGH             | 35                  | 1        |     | ns    |

| <sup>t</sup> R1VCH | RDY <sub>1</sub> , RDY <sub>2</sub> Active Setup to CLK   | ASYNC - LOW              | 35                  |          |     | ns    |

| <sup>t</sup> R1VCL | RDY <sub>1</sub> , RDY <sub>2</sub> Inactive Setup to CLK |                          | 35                  | 1        |     | ns    |

| tCLR1X             | RDY <sub>1</sub> , RDY <sub>2</sub> Hold to CLK           |                          | 0                   |          |     | ns    |

| tayvcl.            | ASYNC Setup to CLK                                        |                          | 50                  | †        |     | ns    |

| t <sub>CLAYX</sub> | ASYNC Hold to CLK                                         |                          | 0                   | <b>†</b> |     | ns    |

| tA1VR1V            | AEN1, AEN2 Setup to RDY1, RDY2                            |                          | 15                  |          |     | ns    |

| tCLA1X             | AEN1, AEN2 Hold to CLK                                    |                          | 0                   | 1        |     | ns    |

| TYHEH              | CSYNC Setup to EFI                                        |                          | 20                  |          |     | ns    |

| <sup>†</sup> EHYL  | CSYNC Hold to EFI                                         | MIL                      | 20                  |          |     |       |

|                    |                                                           | COM'L, A-1               | 10                  |          |     | ns    |

| tyhyL              | CSYNC Width                                               |                          | 2-t <sub>ELEL</sub> |          |     | ns    |

| t <sub>11HCL</sub> | RES Setup to CLK                                          | (Note 2)                 | 65                  |          |     | ns    |

| t <sub>CLI1H</sub> | RES Hold to CLK                                           | (Note 2)                 | 20                  |          |     | ns    |

| tılıH              | Input Rise Time                                           | From 0.8V to 2.0V        | ···                 |          | 20  | ns    |

| t <sub>ILIL</sub>  | Input Fall Time                                           | From 2.0V to 0.8V        |                     |          | 12  | ns    |

#### TIMING RESPONSES Units Тур Max Min **Parameters** Description **Test Conditions** 125 MIL, COM'L กร CLK Cycle Period t<sub>CLCL</sub> 100 A-1 MIL, COM'L (1/3 t<sub>CLCL</sub>) + 2 ns **CLK HIGH Time** tCHCL. A-1 MIL, COM'L (2/3 t<sub>CLCL</sub>) - 15 ns CLK LOW Time <sup>t</sup>CLCH A-1 53 tCH1CH2 10 CLK Rise or Fall Time 1.0V to 3.5V ne tCL2CL1 t<sub>CLCL</sub> - 20 ns **tPHPL** PCLK HIGH Time t<sub>CLCL</sub> - 20 PCLK LOW Time t<sub>PLPH</sub> ns -8 Ready Inactive to CLK (See Note 4) **tRYLCL** (2/3 t<sub>CLCL</sub>) - 15 MIL, COM'L ns Ready Active to CLK (See Note 3) **tRYHCH** A-1 53 40 ns t<sub>CLIL</sub> CLK to Reset Delay 22 CLK to PCLK HIGH Delay t<sub>CLPH</sub> 22 ns CLK to PCLK LOW Delay t<sub>CLPL</sub> 22 ns OSC to CLK HIGH Delay -5 **tolch** 35 ns OSC to CLK LOW Delay 2 **tOLCL** From 0.8V to 2.0V 20 ns Output Rise Time (except CLK) **tOLOH** From 2.0V to 0.8V 12 ns Output Fall Time (except CLK)

- <sup>t</sup>OHOL Notes:

- $\delta$  = EFI rise (5ns max) + EFI fall (5ns max). Setup and hold necessary only to guarantee recognition at next clock. Applies only to T\_2 states. Applies only to T\_2 states.

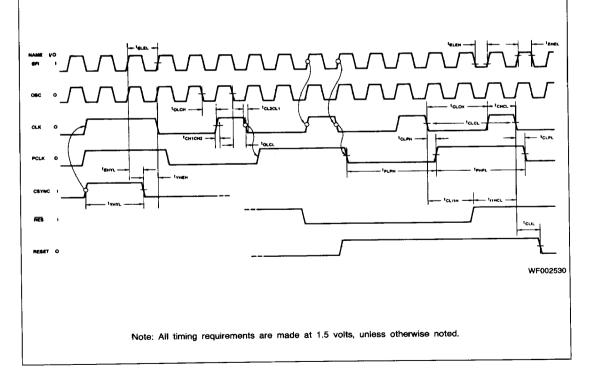

#### SWITCHING WAVEFORMS

#### **CLOCKS AND RESET SIGNALS**