# 32192 Group

## 32-BIT RISC MICROCOMPUTER

REJ03B0019-0100Z Rev.1.00 July 08, 2004

# Description

The 32192 Group is a 32-bit, single-chip RISC microcomputer with built-in flash memory, which was developed for use in general industrial and household equipment. To accomplish high-precision arithmetic operations, it incorporates a fully IEEE754 compliant, single-precision FPU.

This microcomputer contains a variety of peripheral functions. With the software necessary to run these peripheral functions stored in its large-capacity flash memory, this microcomputer meets the needs of application systems for high functionality, high-performance arithmetic capability, and sophisticated control, thereby adaptation to the embedded applications can be easily configured.

Table 1.0.1 Product List

|             | ROM RAM                          |            | Power sup | ply voltage | Temperature range      |                 |

|-------------|----------------------------------|------------|-----------|-------------|------------------------|-----------------|

| Type name   | Type name ROM RAM capacity capac |            | Frequency |             | at double-<br>supplies | (Note 1)        |

| M32192F8VFP | 1 Mbytes                         | 176 Kbytes | 128MHz    | 3.3V        | 5V, 3.3V               | -40°C to +125°C |

| M32192F8UFP | 1 Mbytes                         | 176 Kbytes | 160MHz    | 3.3V        | 5V, 3.3V               | -40°C to +105°C |

| M32192F8TFP | 1 Mbytes                         | 176 Kbytes | 160MHz    | 5V or 3.3V  | 5V, 3.3V               | -40°C to +85°C  |

Note 1: This does not guarantee continuous operation and there is a limitation on the length of use (temperature profile).

# **Features**

| CPU M32R-FPU core  (M32R Family common instruc-                                | tion set + single-precision FPU / bit manipulation instructions) |

|--------------------------------------------------------------------------------|------------------------------------------------------------------|

|                                                                                | 6-stage structure                                                |

| • Instruction set                                                              | 100 discrete instructions / 6 addressing modes                   |

| Instruction format                                                             |                                                                  |

| <ul> <li>Built-in multiplier-accumulator (DSP function instruction)</li> </ul> |                                                                  |

|                                                                                |                                                                  |

| Built-in flash memory                                                          |                                                                  |

| Built-in RAM                                                                   |                                                                  |

|                                                                                | 8 Kbytes x 16 blocks                                             |

|                                                                                |                                                                  |

|                                                                                | ended 0-15 wait cycles and external signal for each of 4 areas   |

|                                                                                |                                                                  |

| • External interrupt input pin                                                 |                                                                  |

| Multiunation timers (MIT)                                                      |                                                                  |

|                                                                                | 55 channels                                                      |

|                                                                                | 4 channels (clock synchronized/UART), 2 channels (UART)          |

|                                                                                | 2 channels (Gock synchronized/OAKT), 2 channels (OAKT)           |

| Direct RAM Interface (DRI)                                                     | Ordernoto, each having 52 message stots                          |

| Real-time debugger (RTD)                                                       |                                                                  |

| Non-Break Debug (NBD)                                                          |                                                                  |

| JTAG (boundary scan function)                                                  |                                                                  |

| • Debug interface common to the M32R Family (SDI: S                            | calable Debug Interface)                                         |

|                                                                                |                                                                  |

| -                                                                              | • • • • • • • • • • • • • • • • • • • •                          |

# **Applications**

Automobile equipment control (e.g., Engine, ABS, AT, CCD, and Radar sensing applications), industrial equipment system control, and high-function OA equipment (e.g., PPC)

Since this group is under development, its specifications are subject to change.

# 1.1 Outline of the 32192 Group

# 1.1.1 M32R Family CPU Core with Built-in FPU (M32R-FPU)

## (1) Based on a RISC architecture

- The 32192 group (hereafter simply the 32192) is a 32-bit RISC single-chip microcomputer. The M32R-FPU incorporates a fully IEEE 754-compliant, single-precision FPU in order to materialize the common instruction set and the high-precision arithmetic operation of the M32R CPU. The 32192 products are built around the M32R-FPU and incorporates flash memory, RAM and various peripheral functions, all integrated into a single chip.

- The M32R-FPU is constructed based on a RISC architecture. Memory is accessed using load/store instructions, and various arithmetic/logic operations are executed using register-to-register operation instructions.

- The M32R-FPU internally contains sixteen 32-bit general-purpose registers. The instruction set consists of 100 discrete instructions in total (83 instructions common to the M32R family plus 17 FPU and extended instructions). These instructions are either 16 bits or 32 bits long.

- In addition to the ordinary load/store instructions, the M32R-FPU supports compound instructions such as Load & Address Update and Store & Address Update. These instructions help to speed up data transfers.

# (2) Five-stage pipelined processing

- The M32R-FPU supports five-stage pipelined instruction processing consisting of Instruction Fetch, Decode, Execute, Memory Access and Write Back (processed in six stages when performing floating-point arithmetic). Not just load/store instructions and register-to-register operation instructions, but also floating-point arithmetic instructions and compound instructions such as Load & Address Update and Store & Address Update are executed in one CPUCLK period (which is equivalent to 6.25 ns when f(CPUCLK) = 160 MHz).

- Although instructions are supplied to the execution stage in the order in which they were fetched, it is possible that if the load/store instruction supplied first is extended by wait cycles inserted in memory access, the subsequent register-to-register operation instruction will be executed before that instruction. Using such a facility, which is known as the "out-of-order-completion" mechanism, the M32R-FPU is able to control instruction execution without wasting clock cycles.

## (3) Compact instruction code

- The M32R-FPU supports two instruction formats: one 16 bits long, and one 32 bits long. Use of the 16-bit instruction format especially helps to suppress the code size of a program.

- Moreover, the availability of 32-bit instructions makes programming easier and provides higher performance at the same clock speed than in architectures where the address space is segmented. For example, some 32-bit instructions allow control to jump to an address 32 Mbytes forward or backward from the currently executed address in one instruction, making programming easy.

# 1.1.2 Built-in Multiplier/Accumulator

## (1) Built-in high-speed multiplier

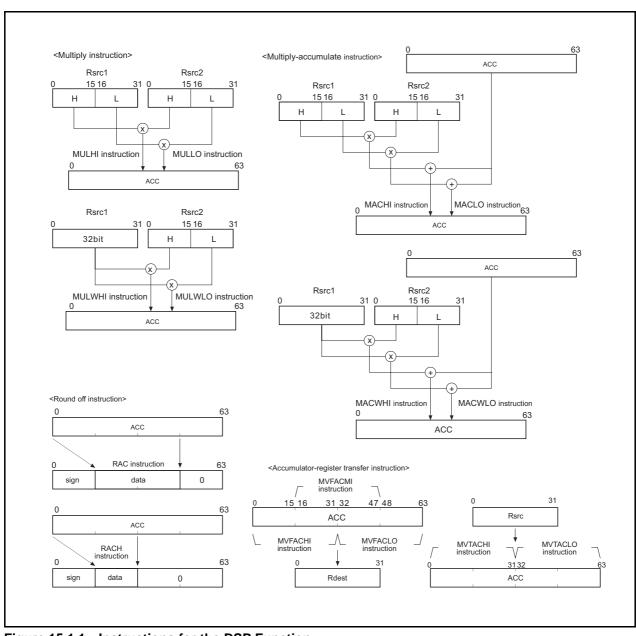

• The M32R-FPU contains a 32 bits × 16 bits high-speed multiplier which enables the M32R-FPU to execute a 32 bits × 32 bits integral multiplication instruction in three CPUCLK periods.

## (2) DSP-comparable multiply-accumulate instructions

- The M32R-FPU supports the following four types of multiply-accumulate instructions (or multiplication instructions) which each can be executed in one CPUCLK period using a 56-bit accumulator.

- (1) 16 high-order bits of register  $\times$  16 high-order bits of register

- (2) 16 low-order bits of register × 16 low-order bits of register

- (3) All 32 bits of register × 16 high-order bits of register

- (4) All 32 bits of register  $\times$  16 low-order bits of register

- The M32R-FPU has some special instructions to round the value stored in the accumulator to 16 or 32 bits or shift the accumulator value before storing in a register to have its digits adjusted. Because these instructions too are executed in one CPUCLK period, when used in combination with high-speed data transfer instructions such as Load & Address Update or Store & Address Update, they enable the M32R-FPU to exhibit superior data processing capability comparable to that of a DSP.

# 1.1.3 Built-in Single-precision FPU

• The M32R-FPU supports single-precision floating-point arithmetic fully compliant with IEEE 754 standards. Specifically, five exceptions specified in IEEE 754 standards (Inexact, Underflow, Division by Zero, Overflow and Invalid Operation) and four rounding modes (round to nearest, round toward 0, round toward + Infinity and round toward – Infinity) are supported. What's more, because general-purpose registers are used to perform floating-point arithmetic, the overhead associated with transferring the operand data can be reduced.

# 1.1.4 Built-in Flash Memory and RAM

- The 32192 contains a RAM that can be accessed with zero wait state, allowing to design a high-speed embedded system.

- The internal flash memory can be written to while mounted on a printed circuit board (on-board writing). Use of flash memory facilitates development work, because the chip used at the development stage can be used directly in mass-production, allowing for a smooth transition from prototype to mass-production without the need to change the printed circuit board.

- The internal flash memory can be rewritten as many as 100 times.

Page 3 of 46

- The internal flash memory has a virtual flash emulation function, allowing the internal RAM to be superficially mapped into part of the internal flash memory. When combined with the internal Real-Time Debugger (RTD) and the M32R family's common debug interface (Scalable Debug Interface or SDI), this function makes the ROM table data tuning easy.

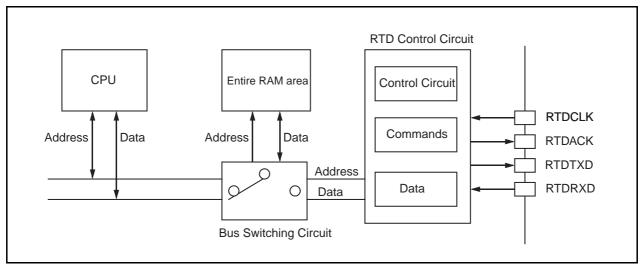

- The internal RAM can be accessed for reading or rewriting data from an external device independently of the M32R-FPU by using the Real-Time Debugger. The external device is communicated using the Real-Time Debugger's exclusive clock-synchronized serial interface.

# 1.1.5 Built-in Clock Frequency Multiplier

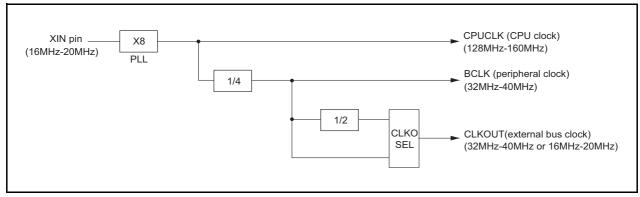

• The 32192 contains a clock frequency multiplier, which is schematically shown in Figure 1.1.1 below.

Figure 1.1.1 Conceptual Diagram of the Clock Frequency Multiplier

Table 1.1.1 Clock

| Functional Block | Features                                                                                                                                                                                                         |

|------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CPUCLK           | CPU clock: Defined as f(CPUCLK) when it indicates the operating clock frequency for the M32R-FPU core, internal flash memory and internal RAM.                                                                   |

| BCLK             | Peripheral clock: Defined as f(BCLK) when it indicates the operating clock frequency for the internal peripheral I/O and external data bus.                                                                      |

| Clock output     | <ul> <li>BCLK pin output: A clock with the same frequency as f(BCLK) is output from this pin.</li> <li>CLKOUT pin output: A clock with the same or half frequency as f(BCLK) is output from this pin.</li> </ul> |

# 1.1.6 Powerful Peripheral Functions Built-in

- (1) 8-level interrupt controller (ICU)

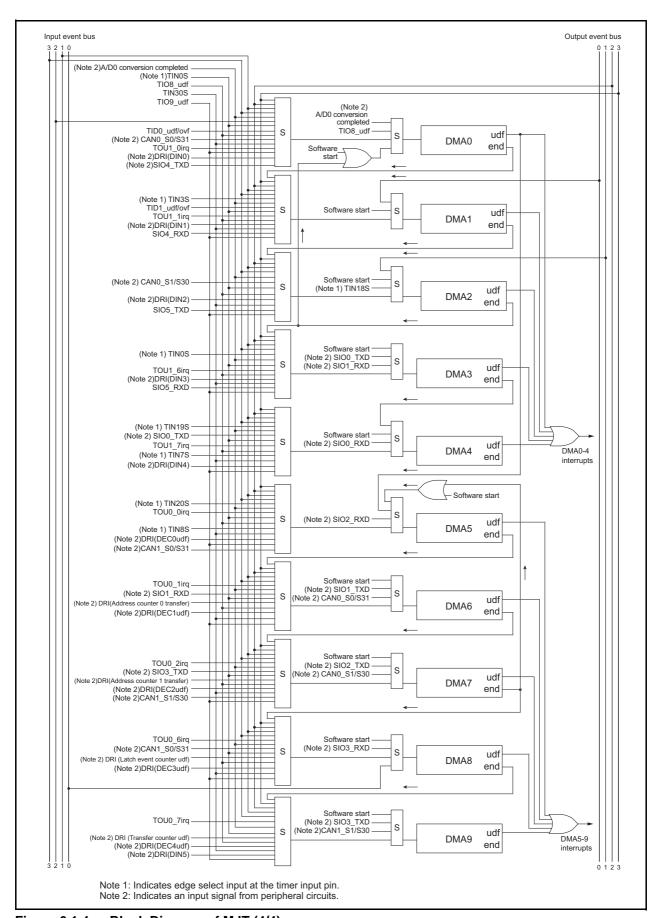

- (2) 10-channel DMAC

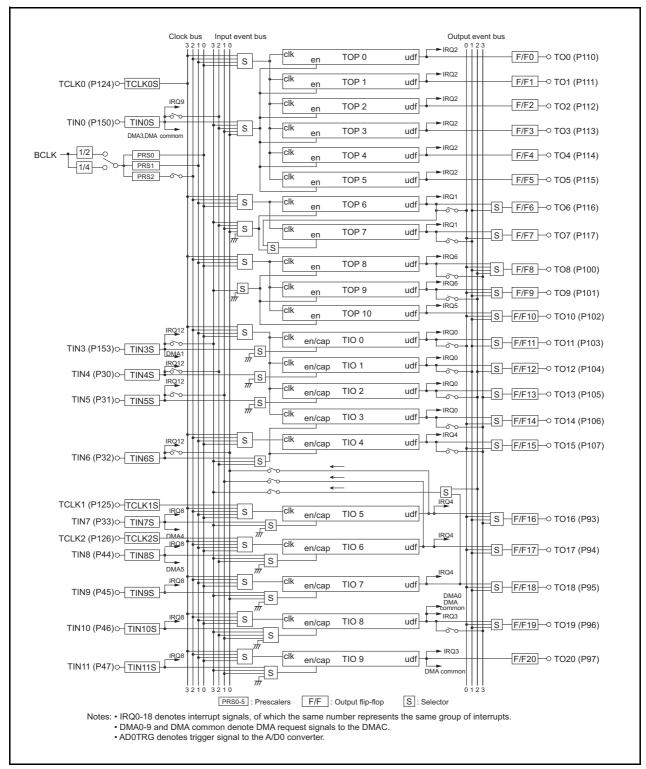

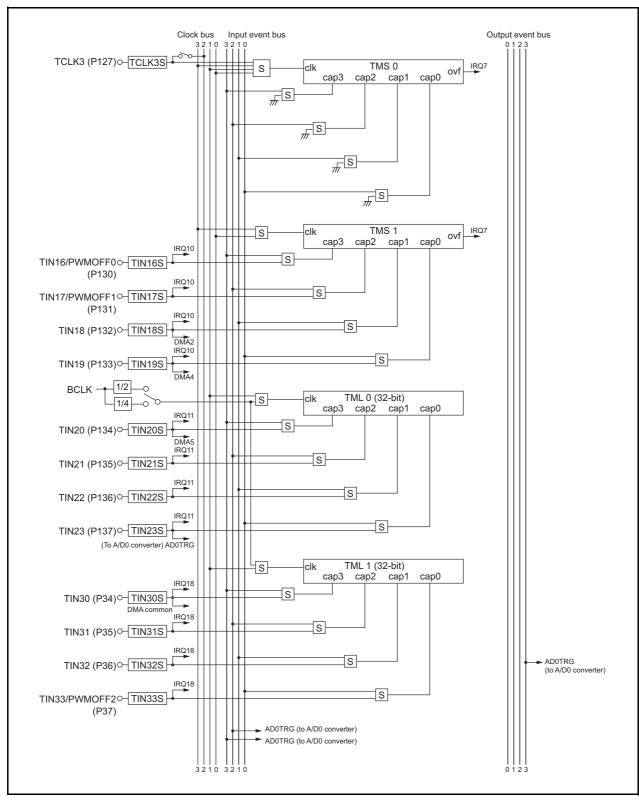

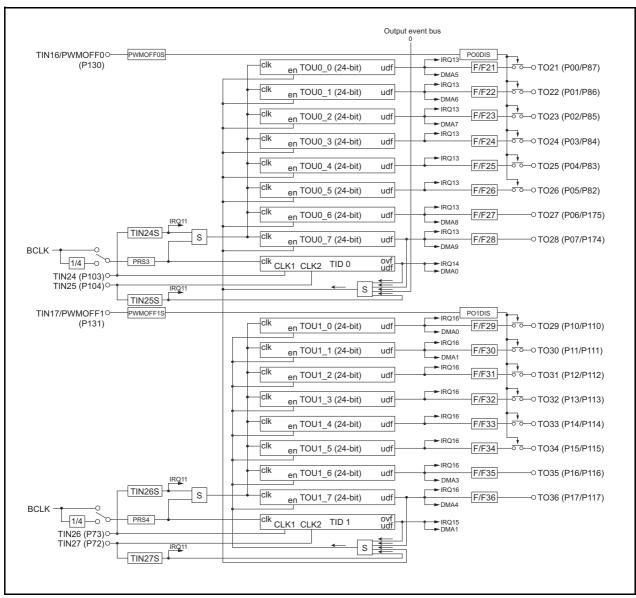

- (3) 55-channel Multijunction timers (MJT)

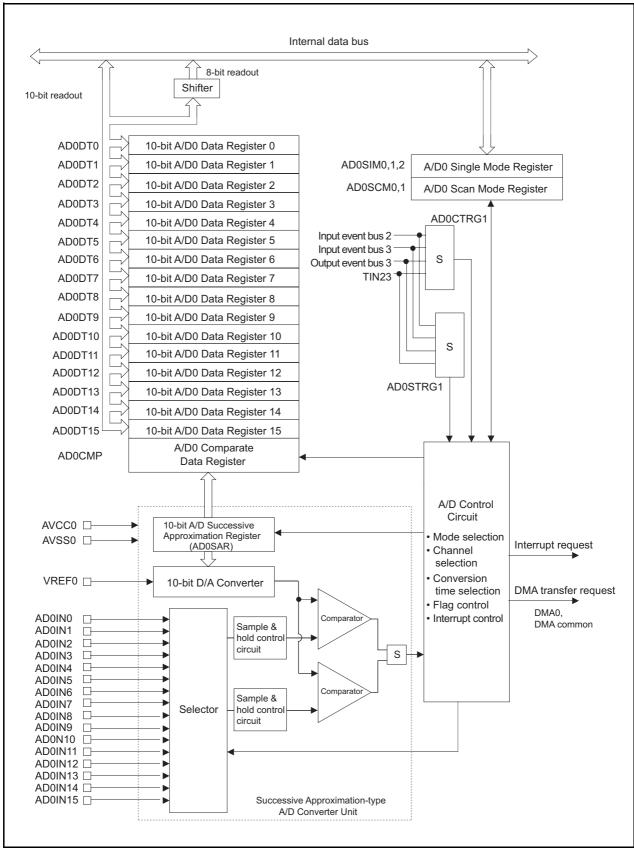

- (4) 16-channel A/D converter (ADC)

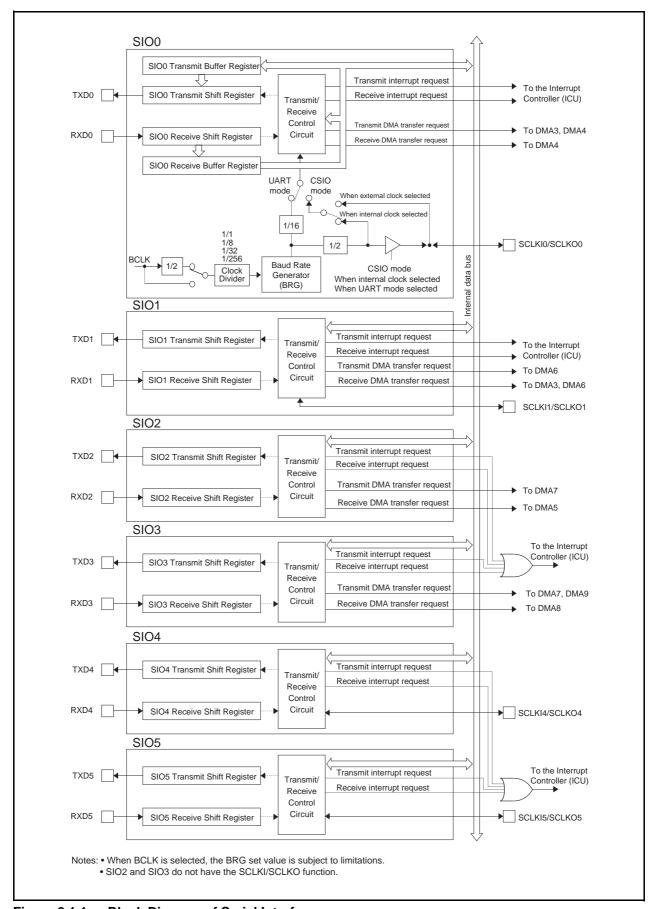

- (5) 6-channel serial interface (SIO)

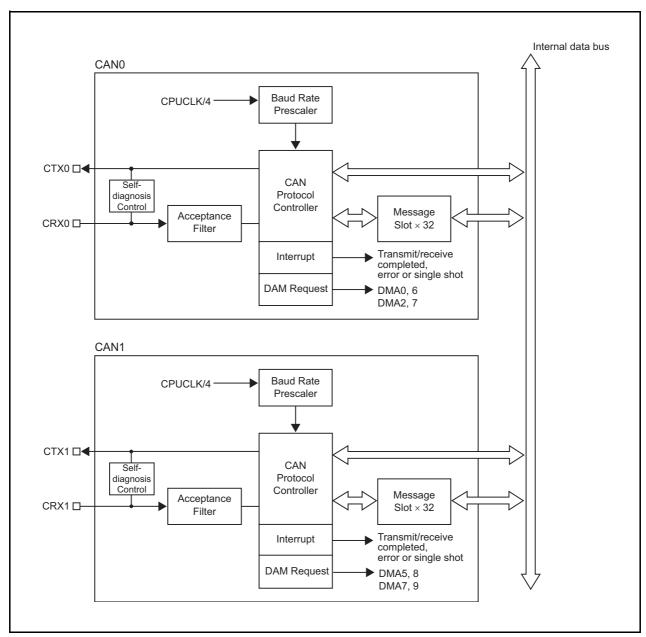

- (6) 2-channel Full-CAN

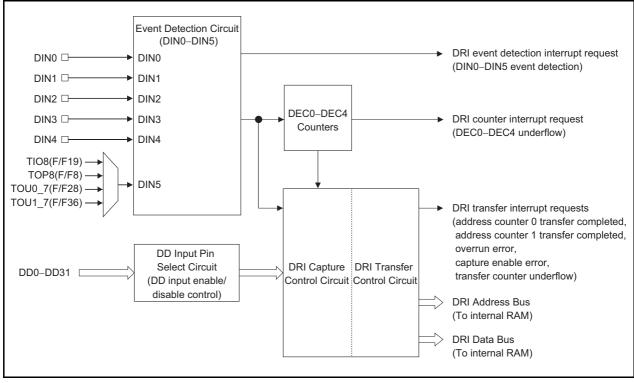

- (7) Direct RAM interface (DRI)

- (8) Real-time debugger (RTD)

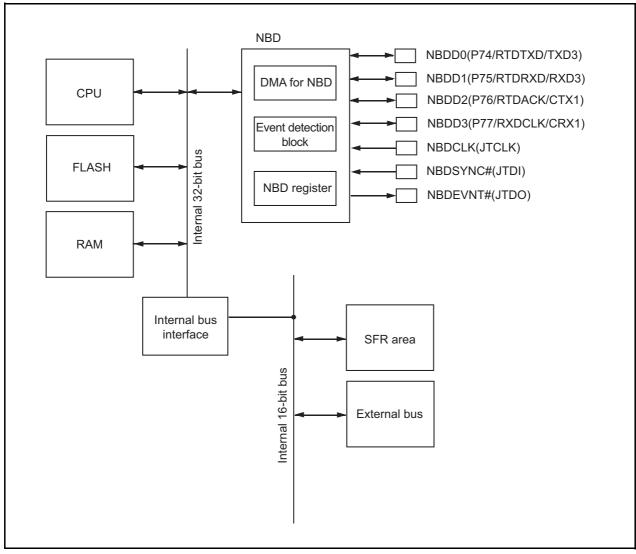

- (9) Non-break debug (NBD)

- (10) Wait controller

- (11) M32R family's common debug function (Scalable Debug Interface or SDI)

32192 Group 1.2 Block Diagram

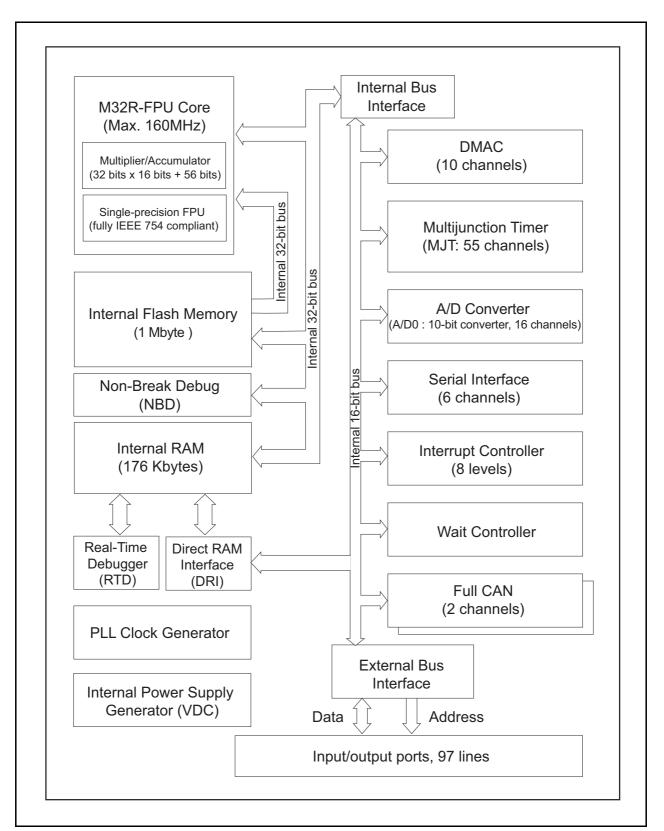

# 1.2 Block Diagram

Figure 1.2.1 shows a block diagram of the 32192. The features of each block are described in Table 1.2.1.

Figure 1.2.1 Block Diagram of the 32192

32192 Group 1.2 Block Diagram

Features of the 32102 /1 / 2\ Table 1 2 1

|                     | es of the 32192 (1 / 2)                                                                                                                                                 |

|---------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Functional Block    | Features                                                                                                                                                                |

| M32R-FPU CPU core   | Implementation: six-stage pipelined instruction processing                                                                                                              |

|                     | Internal 32-bit structure of the core                                                                                                                                   |

|                     | Register configuration                                                                                                                                                  |

|                     | General-purpose registers: 32 bits × 16 registers                                                                                                                       |

|                     | Control registers: 32 bits × 6 registers                                                                                                                                |

|                     | • Instruction set                                                                                                                                                       |

|                     | 16 and 32-bit instruction formats                                                                                                                                       |

|                     | 100 discrete instructions and six addressing modes • Internal multiplier/accumulator (32 bits × 16 bits + 56 bits)                                                      |

|                     | Internal single-precision floating-point arithmetic unit (FPU)                                                                                                          |

|                     |                                                                                                                                                                         |

| Flash memory        | Capacity: 1 Mbyte (1,024 Kbytes), accessible with one wait state     Dynability: Payritchia 100 times.                                                                  |

|                     | Durability: Rewritable 100 times                                                                                                                                        |

| RAM                 | <ul> <li>Capacity: 176 Kbytes, accessible with zero wait state</li> </ul>                                                                                               |

|                     | The internal RAM can be accessed for reading or rewriting data from the outside                                                                                         |

|                     | independently of the M32R-FPU by using the Real-Time Debugger, without ever                                                                                             |

|                     | causing the CPU performance to decrease.                                                                                                                                |

| Bus specification   | <ul> <li>Fundamental bus cycle: 6.25 ns (when f(CPUCLK) = 160 MHz)</li> </ul>                                                                                           |

|                     | Logical address space: 4 Gbytes linear                                                                                                                                  |

|                     | <ul> <li>Internal bus specification: Internal 32-bit data bus (for CPU &lt;-&gt; internal flash memory</li> </ul>                                                       |

|                     | and RAM access)(or accessed in 64 bits when accessing                                                                                                                   |

|                     | the internal flash memory for instructions)                                                                                                                             |

|                     | : Internal 16-bit data bus (for internal peripheral I/O access)                                                                                                         |

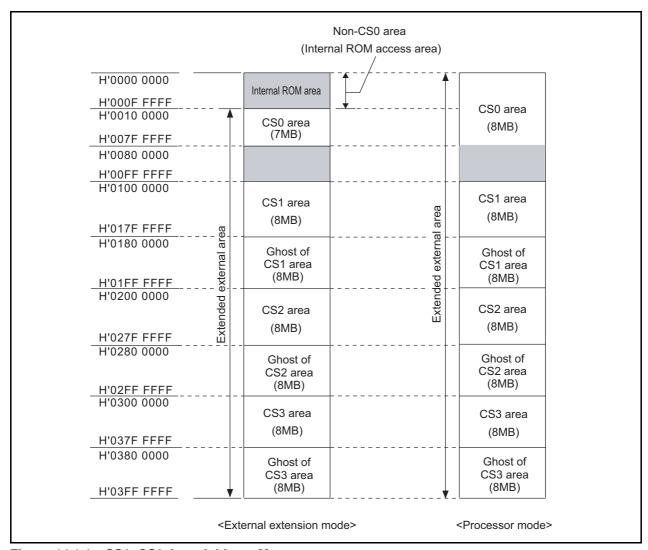

|                     | External extension area: During processor mode: maximum 32 Mbytes                                                                                                       |

|                     | During external extension mode: maximum 31 Mbytes                                                                                                                       |

|                     | (7 Mbytes + 8 Mbytes × 3 blocks)                                                                                                                                        |

|                     | External data address: 22-bit address                                                                                                                                   |

|                     | External data bus: 16-bit data bus                                                                                                                                      |

|                     | Shortest external bus access: 1 CLKOUT during read, 1 CLKOUT during write                                                                                               |

| Multijunction timer | 55-channel multi-functional timer                                                                                                                                       |

| (MJT)               | 16-bit output related timer × 11 channels, 16-bit input/output related timer × 10                                                                                       |

|                     | channels, 16-bit input related timer x 8 channels, 32-bit input related timer x 8                                                                                       |

|                     | channels, 16-bit input related up/down timer x 2 channels, and 24-bit output related                                                                                    |

|                     | timer x 16 channels                                                                                                                                                     |

|                     | • Flexible timer configuration is possible by interconnecting these timer channels.                                                                                     |

|                     | • Interrupt request: Counter underflow or overflow and rising or falling or both edges or                                                                               |

|                     | high or low level from the TIN pin (TIN pin can be used as external                                                                                                     |

|                     | interrupt inputs irrespective of timer operation.)                                                                                                                      |

|                     | DMA transfer request: Counter underflow or overflow and rising or falling or both edges                                                                                 |

|                     | or high or low level from the TIN pin (TIN pin can be used as                                                                                                           |

|                     | DMA transfer request inputs irrespective of timer operation.)                                                                                                           |

| DMAC                | Number of channels: 10                                                                                                                                                  |

|                     | Transfers between internal peripheral I/O's or internal RAM's or between internal                                                                                       |

|                     | peripheral I/O and internal RAM are supported.                                                                                                                          |

|                     | Capable of advanced DMA transfers when used in combination with internal peripheral                                                                                     |

|                     | I/O                                                                                                                                                                     |

|                     | Transfer request: Software or internal peripheral I/O (A/D converter, MJT, serial     Transfer request: Software or internal peripheral I/O (A/D converter, MJT, serial |

|                     | interface or CAN)  • DMA channels can be especiated (DMA transfer on a channel can be started by                                                                        |

|                     | <ul> <li>DMA channels can be cascaded. (DMA transfer on a channel can be started by<br/>completion of a transfer on another channel.)</li> </ul>                        |

|                     | Interrupt request: DMA transfer counter register underflow                                                                                                              |

| A/D 1               | <del>-</del>                                                                                                                                                            |

| A/D converter       | • 16 channels: 10-bit resolution A/D converter × 1 blocks                                                                                                               |

| (ADC)               | Conversion modes: In addition to ordinary A/D conversion modes, the ADC                                                                                                 |

|                     | incorporates comparator mode and 2-channel simultaneous                                                                                                                 |

|                     | sampling mode.                                                                                                                                                          |

|                     | • Operation modes: Single conversion mode and n-channel scan mode (n = 1–16)                                                                                            |

|                     | • Sample-and-hold function: Performs A/D conversion with the analog input voltages                                                                                      |

|                     | sampled at start of A/D conversion.                                                                                                                                     |

32192 Group 1.2 Block Diagram

Table 1.2.1 Features of the 32192 (2 / 2)

| Functional Block              | Features                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|-------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| A/D converter<br>(ADC)        | A/D disconnection detection assist function: Suppresses effects of the analog input voltage leakage from the preceding channel during A/D conversion.                                                                                                                                                                                                                                                                                                                                   |

|                               | <ul> <li>An inflow current bypass circuit is built-in.</li> <li>Can generate an interrupt or start DMA transfer upon completion of A/D conversion.</li> <li>Either 8 or 10-bit conversion results can be read out.</li> <li>Interrupt request: Completion of A/D conversion</li> <li>DMA transfer request: Completion of A/D conversion</li> </ul>                                                                                                                                      |

| Serial interface<br>(SIO)     | <ul> <li>6-channel serial interface</li> <li>Can be chosen to be clock-synchronized serial interface or UART.</li> <li>Data can be transferred at high speed (5 Mbits per second during clock-synchronized mode or 2.5 Mbits per second during UART mode when f(BCLK) = 40 MHz).</li> <li>Interrupt request: Reception completed, receive error, transmit buffer empty or transmission completed</li> <li>DMA transfer request: Reception completed or transmit buffer empty</li> </ul> |

| CAN                           | <ul> <li>32 message slots × 2 blocks</li> <li>Compliant with CAN specification 2.0B active.</li> <li>Interrupt request: Transmission completed, reception completed, bus error, error-passive, bus-off or single shot</li> <li>DMA transfer request: Failed to send, transmission completed or reception completed</li> </ul>                                                                                                                                                           |

| Real-Time Debugger (RTD)      | <ul> <li>Internal RAM can be rewritten or monitored independently of the CPU by entering a command input from the outside.</li> <li>Comes with exclusive clock-synchronized serial ports.</li> <li>Interrupt request: RTD interrupt command input</li> </ul>                                                                                                                                                                                                                            |

| Non-Break Debug<br>(NBD)      | <ul> <li>Can access to all resources on the address map from the outside</li> <li>Clock-synchronized parallel I/O (4-bit)</li> <li>Event output function</li> <li>RAM monitor function</li> </ul>                                                                                                                                                                                                                                                                                       |

| Direct RAM Interface<br>(DRI) | <ul> <li>Controls capture of clock-synchronized parallel data to the internal RAM</li> <li>Clock-synchronized parallel input (8, 16 or 32-bit)</li> <li>Maximum transfer rate: 40 Mbytes/sec (when f(CPUCLK)=160 MHz) .</li> </ul>                                                                                                                                                                                                                                                      |

| Interrupt Controller (ICU)    | <ul> <li>Controls interrupt requests from the internal peripheral I/O.</li> <li>Supports 8-level interrupt priority including an interrupt disabled state.</li> <li>External interrupt: 27 sources (SBI#, TIN0, TIN3–TIN11, TIN16–TIN27, TIN30–TIN33)</li> <li>TIN pin input sensing: Rising, falling or both edges or high or low level</li> </ul>                                                                                                                                     |

| Wait Controller               | <ul> <li>Controls wait states for access to the external extension area.</li> <li>Insertion of 0–15 wait states by setting up in software + wait state extension by entering WAIT# signal</li> </ul>                                                                                                                                                                                                                                                                                    |

| PLL                           | A multiply-by-8 clock generating circuit                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| Clock                         | <ul> <li>Maximum external input clock frequency (XIN) is 20.0 MHz. (Note 1)</li> <li>CPUCLK: Operating clock for the M32R-FPU core, internal flash memory and internal RAM</li> </ul>                                                                                                                                                                                                                                                                                                   |

|                               | <ul> <li>The maximum CPU clock is 160 MHz (when f(XIN) = 20 MHz).</li> <li>BCLK: Operating clock for the internal peripheral I/O and external data bus The maximum peripheral clock is 40 MHz (peripheral module access when f(XIN) = 20 MHz).</li> <li>BCLK pin output: A clock with the same frequency as f(BCLK) is output from this pin.</li> <li>CLKOUT pin output: A clock with the same or half frequency as f(BCLK) is output from</li> </ul>                                   |

| JTAG                          | this pin.  • Boundary scan function                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| VDC                           | Internal power supply generating circuit: Generates the internal power supply from an external power supply (5 or 3.3 V).                                                                                                                                                                                                                                                                                                                                                               |

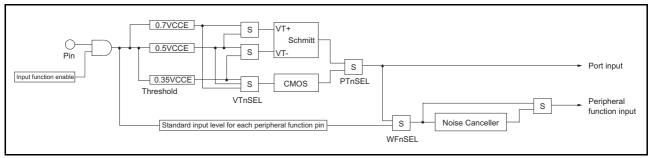

| Ports                         | <ul> <li>Input/output pins: 97 pins</li> <li>The port input threshold can be set in a program to one of three levels individually for each port group (with or without Schmitt circuit, selectable).</li> </ul>                                                                                                                                                                                                                                                                         |

Note 1: The maximum external input clock frequency (XIN) for the M32192F8VFP is 16.0 MHz.

32192 Group 1.3 Pin Functions

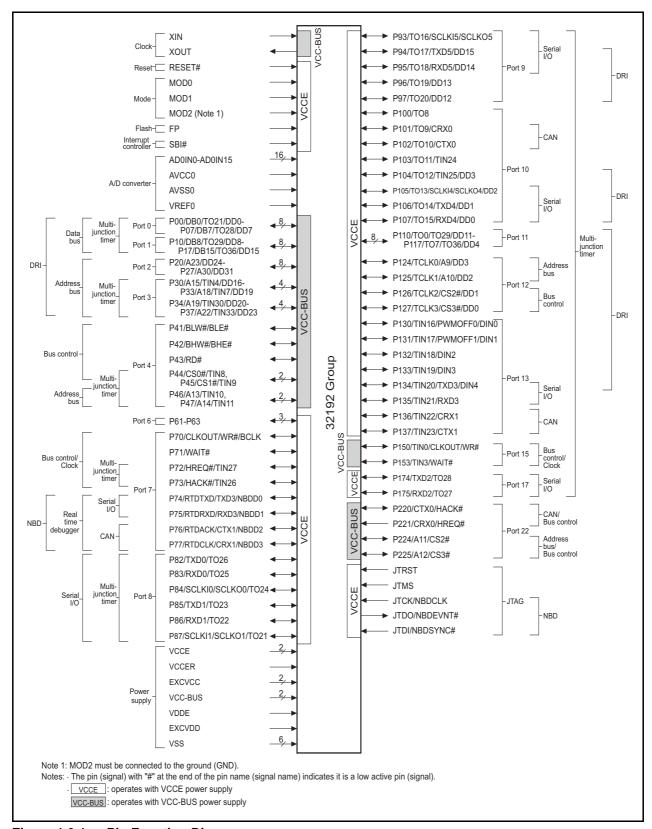

## 1.3 Pin Functions

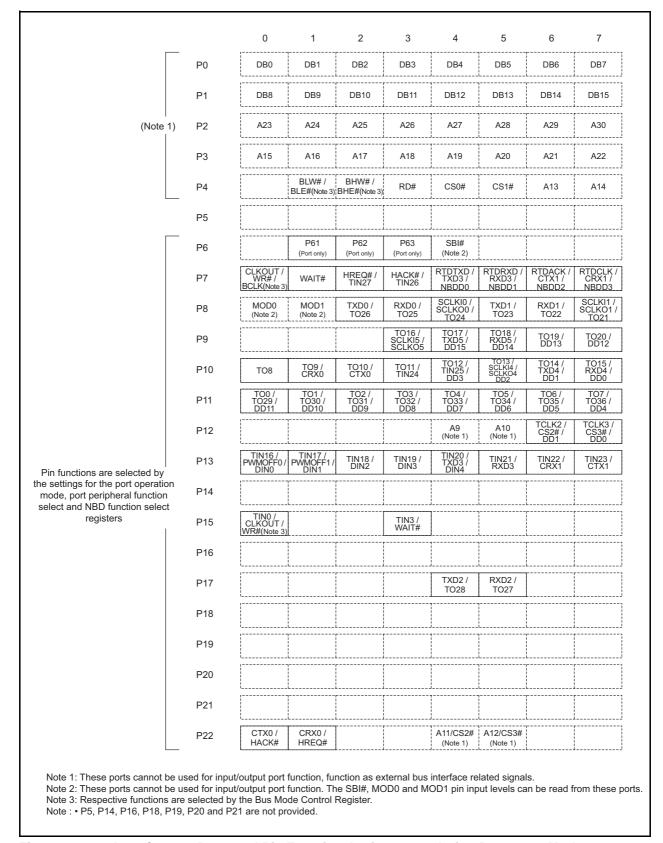

Figure 1.3.1 shows the 32192's pin function diagram. Pin functions are described in Table 1.3.1.

Figure 1.3.1 Pin Function Diagram

32192 Group 1.3 Pin Functions

**Table 1.3.1 Description of Pin Functions (1/3)**

| Type         | Pin Name        | Signal Name                                         | Input/Output    | Descrip                                                                                | tion                                                                                       |                                                                           |                                                                                                                                                                                                    |

|--------------|-----------------|-----------------------------------------------------|-----------------|----------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------|---------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Power supply | VCCER           | Internal power supply input                         | _               | Power s                                                                                | upply inp                                                                                  |                                                                           | internal voltage<br>0.5 V or 3.3 V ± 0.3 V)                                                                                                                                                        |

| Зарріу       | VCCE            | Port/internal peripheral I/O pin power supply input | -               | Power s                                                                                | supply inp<br>ral I/O pin                                                                  | ut for the<br>s (5.0 V :                                                  | port and internal<br>± 0.5 V or 3.3 V ± 0.3 V)<br>all VCCE pins.                                                                                                                                   |

|              | VCC-BUS         | Port/bus interface<br>pin power supply<br>input     | -               | Power s                                                                                | upply inp                                                                                  | ut for the<br>V or 3.3 \                                                  | port and bus interface<br>V± 0.3 V).<br>all VCC-BUS pins.                                                                                                                                          |

|              | VDDE            | RAM power supply                                    | -               |                                                                                        | power su<br>0.5 V or                                                                       |                                                                           | t for the internal RAM .3 V).                                                                                                                                                                      |

|              | VSS             | Ground                                              | _               | Connec                                                                                 | t all VSS                                                                                  | pins to gi                                                                | round (GND).                                                                                                                                                                                       |

|              | EXCVCC          | VCCER control                                       | -               |                                                                                        | connects<br>voltage g                                                                      |                                                                           | nal capacitor for the circuit.                                                                                                                                                                     |

|              | EXCVDD          | VDDE control                                        | _               |                                                                                        |                                                                                            |                                                                           | rnal capacitor for the<br>ne internal RAM.                                                                                                                                                         |

| Clock        | XIN,<br>XOUT    | Clock input<br>Clock output                         | Input<br>Output | frequen<br>input a c<br>CPU clo                                                        | cy multipli<br>clock who                                                                   | ier is incl<br>se freque<br>ncy. (XIN                                     | out pins. A PLL-based x8<br>uded, which accepts as<br>ency is 1/8 of the interna<br>I input is 20 MHz when                                                                                         |

|              | CLKOUT,<br>BCLK | System clock                                        | Output          | the exter<br>CLKOU<br>MHz), o<br>40 MHz<br>The BC<br>external<br>output is<br>This clo | rnal input<br>T output is<br>r two time<br>when f(C<br>LK pin ou<br>input clos<br>s 40 MHz | clock frees 20 MHz es of XIN PUCLK) tputs a clock freque when f(CI when o | a clock that is equal to equency, XIN (i.e., z when f(CPUCLK) = 160 (i.e.,CLKOUT output is = 160 MHz). lock that is two times the ency, XIN (i.e., BCLK CPUCLK) = 160 MHz). perations are the chip |

| Reset        | RESET#          | Reset                                               | Input           |                                                                                        |                                                                                            |                                                                           | ernal circuit.                                                                                                                                                                                     |

| Mode         | MOD0 –          | Mode                                                | Input           | Set the microcomputer's operation mod                                                  |                                                                                            |                                                                           |                                                                                                                                                                                                    |

|              | MOD2            |                                                     | ·               | MOD0                                                                                   | MOD1                                                                                       | MOD2                                                                      | Mode                                                                                                                                                                                               |

|              |                 |                                                     |                 | L                                                                                      | L                                                                                          | L                                                                         | Single-chip mode                                                                                                                                                                                   |

|              |                 |                                                     |                 | L                                                                                      | Н                                                                                          | L                                                                         | External extension mode                                                                                                                                                                            |

|              |                 |                                                     |                 | Н                                                                                      | L                                                                                          | L                                                                         | Processor mode (boot mode) (Note 1)                                                                                                                                                                |

|              |                 |                                                     |                 | Н                                                                                      | Н                                                                                          | L                                                                         | (Settings inhibited)                                                                                                                                                                               |

|              |                 |                                                     |                 | Х                                                                                      | Х                                                                                          | Н                                                                         | (Settings inhibited)                                                                                                                                                                               |

|              |                 |                                                     |                 | X: Don't                                                                               | care                                                                                       |                                                                           |                                                                                                                                                                                                    |

| Flash        | FP              | Flash protect                                       | Input           |                                                                                        | ecial pin p<br>in hardwa                                                                   |                                                                           | ne flash memory against                                                                                                                                                                            |

| Address bus  | A9–A30          | Address bus                                         | Output          | allowing                                                                               | four bloc<br>be conn                                                                       | ks each                                                                   | (A9–A30) are included,<br>up to 8 MB memory<br>ternal to the chip. A31 is                                                                                                                          |

Note 1: Boot mode requires that the FP pin should be at the high level.

32192 Group 1.3 Pin Functions

**Table 1.3.1 Description of Pin Functions (2/3)**

| Туре                    | Pin Name                                                            | Signal Name                                                                                   | Input/Output | Description                                                                                                                                                                                                                                                                                                                             |

|-------------------------|---------------------------------------------------------------------|-----------------------------------------------------------------------------------------------|--------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Data bus                | DB0-DB15                                                            | Data bus                                                                                      | Input/output | This 16-bit data bus is used to connect external devices. When writing in byte units during a write cycle, the output data at the invalid byte position is undefined. During a read cycle, data on the entire 16-bit bus is always read in. However, only the data at the valid byte position is transferred into the internal circuit. |

| Bus control             | CS0#-CS3#                                                           | Chip select                                                                                   | Output       | These are chip select signals for external devices.                                                                                                                                                                                                                                                                                     |

|                         | RD#                                                                 | Read                                                                                          | Output       | This signal is output when reading an external device.                                                                                                                                                                                                                                                                                  |

|                         | WR#                                                                 | Write                                                                                         | Output       | This signal is output when writing to an external device.                                                                                                                                                                                                                                                                               |

|                         | BHW#/BLW#                                                           | Byte high/low write                                                                           | Output       | When writing to an external device, this signal indicates the valid byte position to which data is transferred. BHW# and BLW# correspond to the upper address side (bits 0–7 are valid) and the lower address side (bits 8–15 are valid), respectively.                                                                                 |

|                         | BHE#                                                                | Byte high enable                                                                              | Output       | During an external device access, this signal indicates that the high-order data (bits 0–7) is valid                                                                                                                                                                                                                                    |

|                         | BLE#                                                                | Byte low enable                                                                               | Output       | During an external device access, this signal indicates that the low-order data (bits 8–15) is valid                                                                                                                                                                                                                                    |

|                         | WAIT#                                                               | Wait                                                                                          | Input        | When accessing an external device, a low-level input on WAIT# pin extends the wait cycle.                                                                                                                                                                                                                                               |

|                         | HREQ#                                                               | Hold request                                                                                  | Input        | This input pin is used by an external device to request control of the external bus. A low-level input on HREQ# pin places the CPU in a hold state                                                                                                                                                                                      |

|                         | HACK#                                                               | Hold acknowledge                                                                              | Output       | This signal notifies that the CPU has entered a hold state and relinquished control of the external bus.                                                                                                                                                                                                                                |

| Multijunction<br>timer  | TIN0, TIN3-TIN11,<br>TIN16-TIN27,<br>TIN30-TIN33                    | Timer input                                                                                   | Input        | Input pins for the multijunction timer.                                                                                                                                                                                                                                                                                                 |

|                         | TO0-TO36                                                            | Timer output                                                                                  | Output       | Output pins for the multijunction timer.                                                                                                                                                                                                                                                                                                |

|                         | TCLK0 -TCLK3                                                        | Timer clock                                                                                   | Input        | Clock input pins for the multijunction timer.                                                                                                                                                                                                                                                                                           |

| A/D<br>converter        | AVCC0                                                               | Analog power supply input                                                                     | -            | AVCC0 is the power supply input for the A/D0 converter. Connect AVCC0 to the power supply rail                                                                                                                                                                                                                                          |

|                         | AVSS0                                                               | Analog ground                                                                                 | -            | AVSS0 is the analog ground for the A/D0 converter. Connect AVSS0 to ground.                                                                                                                                                                                                                                                             |

|                         | AD0IN0 –AD0IN15                                                     | Analog input                                                                                  | Input        | 16-channel analog input pins for the A/D0 converter.                                                                                                                                                                                                                                                                                    |

|                         | VREF0                                                               | Reference voltage input                                                                       | Input        | VREF0 is the reference voltage input pin for the A/D0 converter.                                                                                                                                                                                                                                                                        |

| Interrupt<br>controller | SBI#                                                                | System break interrupt                                                                        | Input        | This is the system break interrupt (SBI) input pin for the interrupt controller.                                                                                                                                                                                                                                                        |

| Serial<br>interface     | SCLKI0/SCLKO0,<br>SCLKI1/SCLKO1,<br>SCLKI4/SCLKO4,<br>SCLKI5/SCLKO5 | UART transmit/<br>receive clock output<br>or CSIO transmit/<br>receive clock input/<br>output | Input/output | When in UART mode: This pin outputs a clock derived from BRG output by dividing it by 2. When in CSIO mode: This pin accepts as input a transmit/receive clock when external clock is selected or outputs a transmit/receive clock when internal clock is selected.                                                                     |

|                         | TXD0-TXD5                                                           | Transmit data                                                                                 | Output       | Transmit data output pin for serial interface.                                                                                                                                                                                                                                                                                          |

|                         | RXD0-RXD5                                                           | Received data                                                                                 | Input        | Received data input pin for serial interface.                                                                                                                                                                                                                                                                                           |

32192 Group 1.3 Pin Functions

**Table 1.3.1 Description of Pin Functions (3/3)**

| Type         | Pin Name                              | Signal Name               | Input/Output | Description                                                                                                                                                                                                                         |

|--------------|---------------------------------------|---------------------------|--------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Real-time    | RTDTXD                                | RTD transmit data         | Output       | Serial data output pin for the real-time debugger.                                                                                                                                                                                  |

| debugger     | RTDRXD                                | RTD received data         | Input        | Serial data input pin for the real-time debugger.                                                                                                                                                                                   |

| (RTD)        | RTDCLK                                | RTD clock input           | Input        | Serial data transmit/receive clock input pin for the real-time debugger.                                                                                                                                                            |

|              | RTDACK                                | RTD acknowledge           | Output       | A low-level pulse is output from this pin synchronously with the start clock for the real-time debugger's serial data output word. The low-level pulse width indicates the type of command/data received by the real-time debugger. |

| CAN          | CTX0, CTX1                            | Transmit data             | Output       | This pin outputs data from the CAN module.                                                                                                                                                                                          |

|              | CRX0, CRX1                            | Received data             | Input        | This pin accepts as input the data for the CAN module.                                                                                                                                                                              |

| JTAG         | JTMS                                  | Test mode select          | Input        | Test mode select input to control the state transition of the test circuit.                                                                                                                                                         |

|              | JTCK                                  | Test clock                | Input        | Clock input for the debug module and test circuit.                                                                                                                                                                                  |

|              | JTRST                                 | Test reset                | Input        | Test reset input to initialize the test circuit asynchronously with device operation.                                                                                                                                               |

|              | JTDI                                  | Test data input           | Input        | This pin accepts as input the test instruction code or test data that is serially received.                                                                                                                                         |

|              | JTDO                                  | Test data output          | Output       | This pin outputs the test instruction code or test data serially.                                                                                                                                                                   |

| NBD          | NBDD0 –NBDD3                          | Command/Address/<br>Data  | Input/output | NBD command, address, and data input/output pins.                                                                                                                                                                                   |

|              | NBDCLK                                | Synchronizing clock input | Input        | NBD synchronizing clock input pin.                                                                                                                                                                                                  |

|              | NBDSYNC#                              | Top of data input         | Input        | This pin controls the start position of NBD data.                                                                                                                                                                                   |

|              | NBDEVNT#                              | Event output              | Output       | This pin is used for event output when an NBD event occurs.                                                                                                                                                                         |

| DRI          | DD0-DD31                              | DD input                  | Input        | DRI data input pin.                                                                                                                                                                                                                 |

|              | DIN0-DIN4                             | DIN input                 | Input        | DRI event input pin.                                                                                                                                                                                                                |

| Input/output | P00-P07                               | Input/output port 0       | Input/output | Programmable input/output port.                                                                                                                                                                                                     |

| ports        | P10-P17                               | Input/output port 1       | Input/output | •                                                                                                                                                                                                                                   |

| (Note 1)     | P20-P27                               | Input/output port 2       | Input/output | -                                                                                                                                                                                                                                   |

|              | P30-P37                               | Input/output port 3       | Input/output | -                                                                                                                                                                                                                                   |

|              | P41-P47                               | Input/output port 4       | Input/output | -                                                                                                                                                                                                                                   |

|              | P61-P63                               | Input/output port 6       | Input/output | •                                                                                                                                                                                                                                   |

|              | P70-P77                               | Input/output port 7       | Input/output | -                                                                                                                                                                                                                                   |

|              | P82-P87                               | Input/output port 8       | Input/output | -                                                                                                                                                                                                                                   |

|              | P93-P97                               | Input/output port 9       | Input/output | •                                                                                                                                                                                                                                   |

|              | P100-P107                             | Input/output port 10      | Input/output | •                                                                                                                                                                                                                                   |

|              | P110-P117                             | Input/output port 11      | Input/output | •                                                                                                                                                                                                                                   |

|              | P124-P127                             | Input/output port 12      | Input/output | •                                                                                                                                                                                                                                   |

|              | P130-P137                             | Input/output port 13      | Input/output | -                                                                                                                                                                                                                                   |

|              | P150, P153                            | Input/output port 15      | Input/output | -                                                                                                                                                                                                                                   |

|              | P174, P175                            | Input/output port 17      | Input/output | -                                                                                                                                                                                                                                   |

|              | P220,<br>P221 (Note 2),<br>P224, P225 | Input/output port 22      |              | •                                                                                                                                                                                                                                   |

Note 1: Input/output ports 5, 14, 16 and 18–21 are nonexistent.

Note 2: P221 is input-only port.

32192 Group 1.4 Pin Assignments

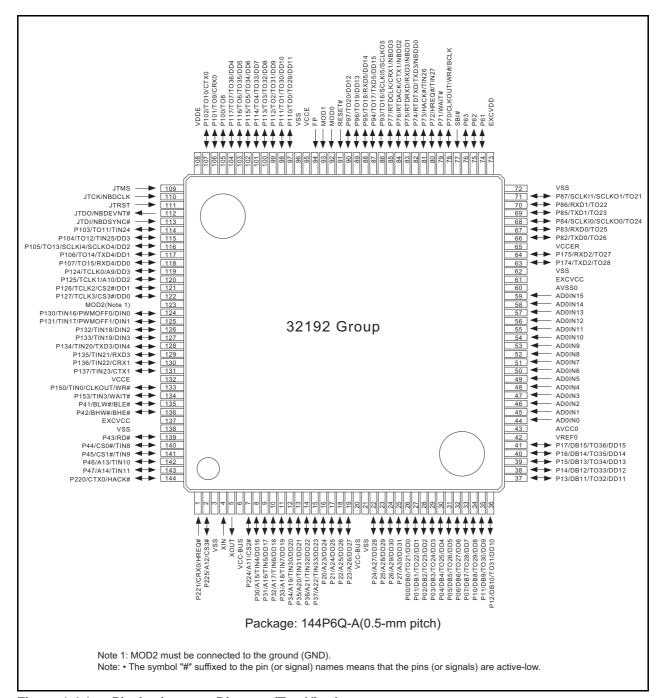

# 1.4 Pin Assignments

Figure 1.4.1 shows the 32192's pin assignment diagram.

Figure 1.4.1 Pin Assignment Diagram (Top View)

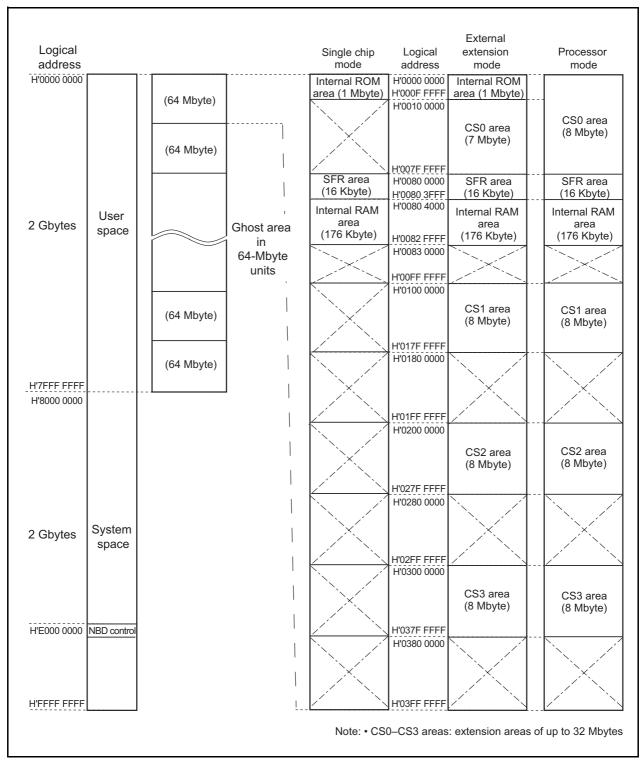

### 2.1 **Outline of the Address Space**

The logical addresses of the M32R are always handled in 32 bits, providing a linear address space of up to 4 Gbytes. The address space of the M32R/ECU consists of the following:

- (1) User space

- Internal ROM area

- External extension area

- Internal RAM area

- SFR (Special Function Register) area

- (2) System space (not open to the user)

# (1) User space

The 2 Gbytes from the address H'0000 0000 to the address H'7FFF FFFF comprise the user space. Located in this space are the internal ROM area, an external extension area, the internal RAM area and the SFR (Special Function Register) area (in which a set of internal peripheral I/O registers exist). Of these, the internal ROM and external extension areas are located differently depending on mode settings as will be described later.

# (2) System space

The 2 Gbytes from the address H'8000 0000 to the address H'FFFF FFFF comprise the system space. This space (except for SFR area for NBD control) is reserved for use by development tools such as an in-circuit emulator and debug monitor.

### 2.2 **Operation Modes**

The microcomputer is placed in one of the following modes depending on how CPU operation mode is set by MOD0 and MOD1 pins.

**Table 2.2.1 Operation Mode Settings**

| MOD0 | MOD1 | MOD2 (Note 1) | Operation mode            |

|------|------|---------------|---------------------------|

| VSS  | VSS  | VSS           | Single-chip mode          |

| VSS  | VCCE | VSS           | External extension mode   |

| VCCE | VSS  | VSS           | Processor mode (FP = VSS) |

| VCCE | VCCE | VSS           | (Settings inhibited)      |

| _    | _    | VCCE          | (Settings inhibited)      |

Note 1: Connect VCCE and VSS to the VCCE input power supply and ground, respectively.

The internal ROM and external extension areas are located differently depending on how operation mode is set. (All other areas in the address space are located the same way.) The following diagram shows how the internal ROM and external extension areas are mapped into the address space in each operation mode.

32192 Group 2.2 Operation Modes

**Figure 2.2.1 Address Space**

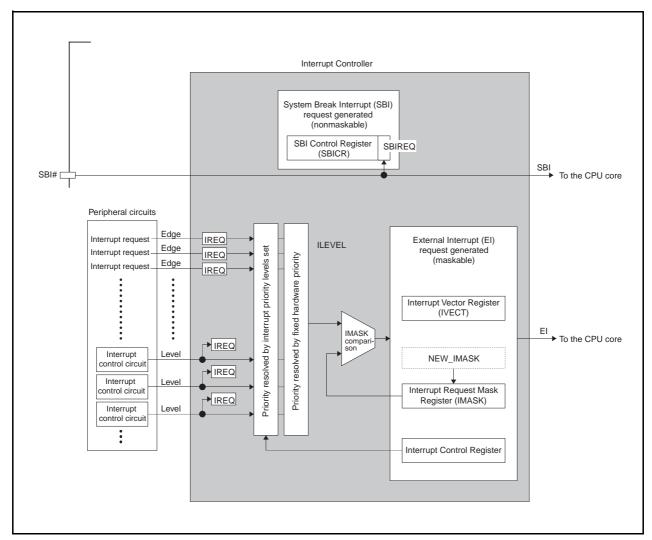

## 3.1 **Outline of the Interrupt Controller**

The Interrupt Controller (ICU) manages maskable interrupts from internal peripheral I/Os and a system break interrupt (SBI). The maskable interrupts from internal peripheral I/Os are sent to the M32R CPU as external interrupts (EI).

The maskable interrupts from internal peripheral I/Os are managed by assigning them one of eight priority levels including an interrupt-disabled state. If two or more interrupt requests with the same priority level occur at the same time, their priorities are resolved by predetermined hardware priority. The source of an interrupt request generated in internal peripheral I/Os is identified by reading the relevant interrupt status register provided for internal peripheral I/Os.

On the other hand, the system break interrupt (SBI) is recognized when a low-going transition occurs on the SBI# signal input pin. This interrupt is used for emergency purposes such as when power outage is detected or a fault condition is notified by an external watchdog timer, so that it is always accepted irrespective of the PSW register IE bit status. When the CPU has finished servicing an SBI, shut down or reset the system without returning to the program that was being executed when the interrupt occurred.

Specifications of the Interrupt Controller are outlined below.

**Table 3.1.1 Outline of the Interrupt Controller (ICU)**

| Item                     | Specification                                                                                                                                                         |

|--------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Interrupt request source | Maskable interrupt requests from internal peripheral I/Os : 40 sources (Note 1) System break interrupt request : 1 source (entered from SBI# pin)                     |

| Priority management      | 8 priority levels including an interrupt-disabled state (However, interrupts with the same priority level have their priorities resolved by fixed hardware priority.) |

Note 1: There are actually 256 interrupt request resources in total when counted individually, which are grouped into 40 interrupt request resources.

**Figure 3.1.1 Block Diagram of the Interrupt Controller**

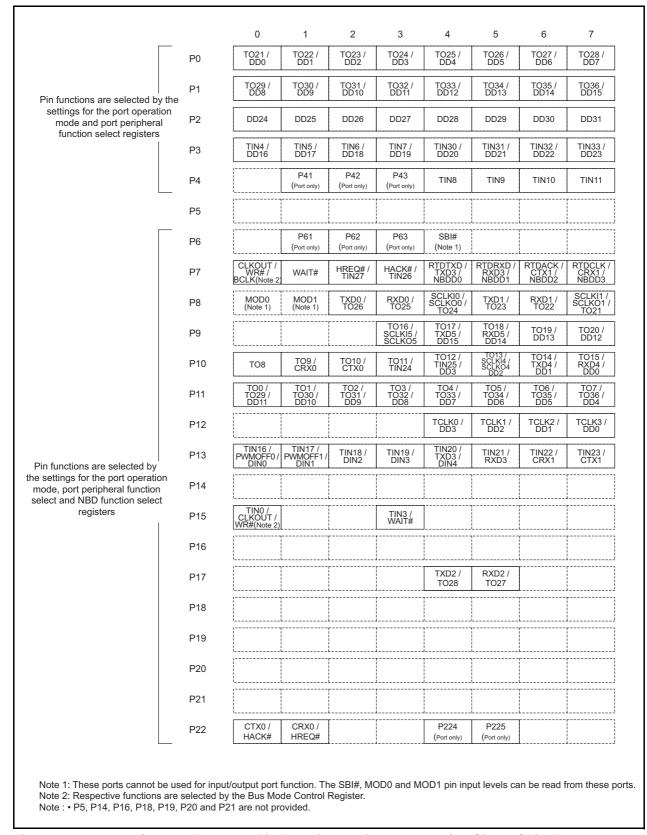

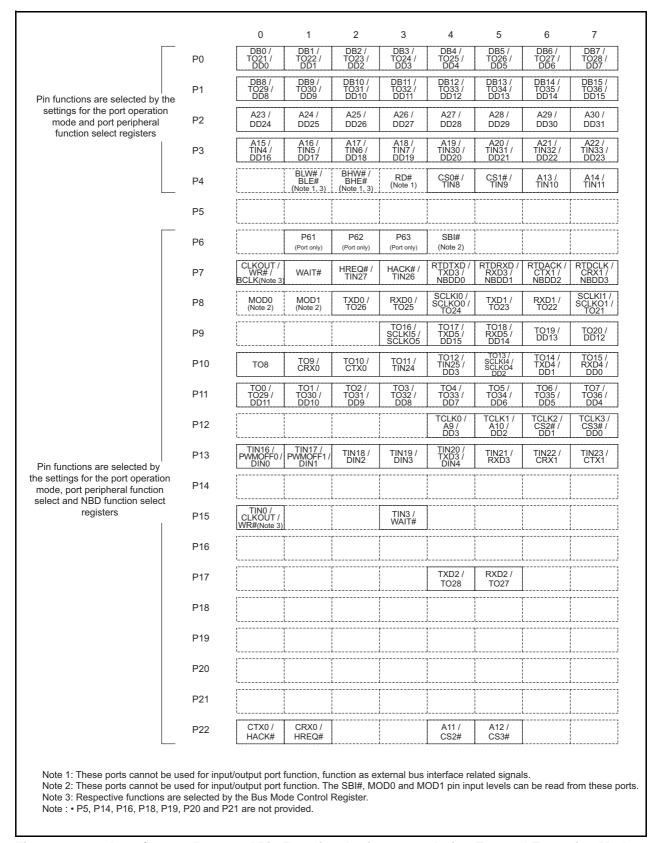

### 4.1 **Outline of Input/Output Ports**

The 32192 has a total of 97 input/output ports from P0-P13, P15, P17 and P22 (except P5, which is reserved for future use). These input/output ports can be used as input or output ports by setting the respective direction registers.

Each input/output port has double or triple functions shared with other internal peripheral I/O or external bus interface related signal lines, or multiple functions shared with multi-function peripheral I/Os. Pin functions are selected depending on the operation mode of the CPU or by setting the operation mode register and peripheral function select register for the input/output port. (If any internal peripheral I/O has still another function, it is also necessary to set the register provided for that internal peripheral I/O.)

Abundant port functions are incorporated, including a port input level switching function, port output drive capability setting function, and noise canceller control function.

Note that before any ports can be used in input mode, this port input function enable bit must be set accordingly. The input/output ports are outlined below.

**Table 4.1.1 Outline of Input/Output Ports**

| Item            | Specification                                                                                                                                                                            |  |  |

|-----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Number of ports | Total 97 ports                                                                                                                                                                           |  |  |

|                 | P0: P00–P07 (8 ports)                                                                                                                                                                    |  |  |

|                 | P1: P10–P17 (8 ports)                                                                                                                                                                    |  |  |