# 200-V Half-Bridge Driver

#### **Features**

- I<sub>O+</sub> / I<sub>O-</sub> of 290 mA / 600 mA typical gate current

- Gate drive voltage up to 20 V per channel

- Independent under-voltage lockout for V<sub>CC</sub>, V<sub>BS</sub>

- 3.3 V, 5 V, 15 V input logic compatible

- Tolerant to negative transient voltage

- Designed for use with bootstrap power supplies

- Cross-conduction prevention logic

- Matched propagation delay for both channels

- Internal set dead-time

- · High-side output in phase with HIN input

- Low-side output out of phase with LIN input

- -40 °C to 125 °C operating range

- 2 kV HBM ESD

- RoHS compliant

# Product Summary

| V <sub>OFFSET</sub>                       | ≤ 200 V         |

|-------------------------------------------|-----------------|

| V <sub>OUT</sub>                          | 10 V – 20 V     |

| I <sub>O+</sub> & I <sub>O-</sub> (typ.)  | 290 mA & 600 mA |

| t <sub>ON</sub> & t <sub>OFF</sub> (typ.) | 160 ns & 150 ns |

| Dead-time (typ.)                          | 520 ns          |

#### **Description**

The IRS2007S is a high voltage, high speed power MOSFET driver with dependent high and low side referenced output channels. Proprietary HVIC and latch immune CMOS technologies enable ruggedized monolithic construction. The logic input is compatible with standard CMOS or LSTTL output, down to 3.3 V logic. The output drivers feature a high pulse current buffer stage designed for minimum driver cross-conduction. The floating channel can be used to drive an N-channel power MOSFET or IGBT in the high side configuration which operates up to 200 V. Propagation delays are matched to simplify the HVIC's use in high frequency applications.

#### **Package Options**

### **Typical Applications**

- Battery operated power tools

- Battery operated garden equipment

- Light electric vehicles (e-bikes, e-scooters, e-toys)

- Wireless Charging

- Other general battery driven applications

| Door Dord Number        | Deelsene Tyme | Standar       | d Pack   | Orderskie Dert Normber |  |

|-------------------------|---------------|---------------|----------|------------------------|--|

| Base Part Number        | Package Type  | Form          | Quantity | Orderable Part Number  |  |

| IRS2007SPBF 8-Lead SOIC |               | Tube/Bulk     | 95       | IRS2007SPBF            |  |

|                         |               | Tape and Reel | 2500     | IRS2007STRPBF          |  |

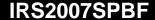

# **Typical Connection Diagram**

(Refer to Lead Assignments for correct pin configuration). This diagram shows electrical connections only. Please refer tour Application Notes & Design Tips for proper circuit board layout.

#### **Absolute Maximum Ratings**

Absolute maximum ratings indicate sustained limits beyond which damage to the device may occur. All voltage parameters are absolute voltages referenced to COM unless otherwise stated in the table. The thermal resistance and power dissipation ratings are measured under board mounted and still air conditions.

| Symbol              | Definition                                          | Min.                                   | Max.                 | Units                |      |

|---------------------|-----------------------------------------------------|----------------------------------------|----------------------|----------------------|------|

| V <sub>CC</sub>     | Low side supply voltage                             |                                        | -0.3                 | 25 <sup>†</sup>      |      |

| V <sub>IN</sub>     | Logic input voltage (HIN & LIN)                     |                                        | COM - 0.3            | $V_{CC} + 0.3$       |      |

| $V_{B}$             | High-side floating well supply voltage              |                                        | -0.3                 | 225                  |      |

| Vs                  | High-side floating well supply return v             | /oltage                                | V <sub>B</sub> - 25  | V <sub>B</sub> + 0.3 | V    |

| V <sub>HO</sub>     | Floating gate drive output voltage                  |                                        | V <sub>S</sub> - 0.3 | V <sub>B</sub> + 0.3 |      |

| V <sub>LO</sub>     | Low-side output voltage                             | Low-side output voltage                |                      |                      |      |

| COM                 | Power ground                                        | Power ground                           |                      |                      |      |

| dV <sub>S</sub> /dt | Allowable V <sub>S</sub> offset supply transient r  | elative to COM                         | _                    | 50                   | V/ns |

| P <sub>D</sub>      | Package power dissipation @ T <sub>A</sub> ≤ +25 °C | Package power dissipation 8-l ead SOIC |                      | 0.625                | W    |

| Rth <sub>JA</sub>   | Thermal resistance, junction to ambient 8-Lead SOIC |                                        | _                    | 200                  | °C/W |

| TJ                  | Junction temperature                                |                                        | _                    | 150                  |      |

| T <sub>S</sub>      | Storage temperature                                 |                                        | -55                  | 150                  | ٥C   |

| $T_L$               | Lead temperature (soldering, 10 second              | onds)                                  |                      | 300                  |      |

<sup>†</sup> All supplies are tested at 25 V.

#### **Recommended Operating Conditions**

For proper operation, the device should be used within the recommended conditions. All voltage parameters are absolute voltages referenced to COM unless otherwise stated in the table. The offset rating is tested with supplies of  $(V_{CC} - COM) = (V_B - V_S) = 15 \text{ V}$ .

| Symbol          | Definition                                                 | Min                  | Max                 | Units |

|-----------------|------------------------------------------------------------|----------------------|---------------------|-------|

| V <sub>CC</sub> | Low-side supply voltage                                    | 10                   | 20                  |       |

| V <sub>IN</sub> | Logic input voltage(HIN & LIN)                             | 0                    | V <sub>cc</sub>     |       |

| $V_{B}$         | High-side floating well supply voltage                     | V <sub>S</sub> + 10  | V <sub>S</sub> + 20 |       |

| Vs              | High-side floating well supply offset voltage <sup>†</sup> | COM - 8 <sup>†</sup> | 200                 | V     |

| V <sub>HO</sub> | Floating gate drive output voltage                         | Vs                   | V <sub>B</sub>      |       |

| $V_{LO}$        | Low-side output voltage                                    | COM                  | V <sub>cc</sub>     |       |

| T <sub>A</sub>  | Ambient temperature                                        | -40                  | 125                 | °C    |

<sup>†</sup> Logic operation for VS of -8 V to 200 V. Logic state held for  $V_S$  of -8 V to  $-V_{BS}$ . Please refer to Design Tip DT97-3 for more details.

#### **Static Electrical Characteristics**

$(V_{CC} - COM) = (V_B - V_S) = 15V$ .  $T_A = 25$ °C unless otherwise specified. The  $V_{IN}$  and  $I_{IN}$  parameters are referenced to COM. The  $V_O$  and  $I_O$  parameters are referenced to respective  $V_S$  and COM and are applicable to the respective output leads HO or LO. The  $V_{CCUV}$  parameters are referenced to COM. The  $V_{BSUV}$  parameters referenced to  $V_S$ . Output Current Direction is defined as positive out of the pin and negative into the pin

| Symbol              | Definition                                                        | Min. | Тур. | Max. | Units | Test Conditions                                                        |

|---------------------|-------------------------------------------------------------------|------|------|------|-------|------------------------------------------------------------------------|

| V <sub>BSUV+</sub>  | V <sub>BS</sub> supply under voltage positive threshold           | 8.0  | 8.9  | 9.8  |       |                                                                        |

| V <sub>BSUV</sub> - | V <sub>BS</sub> supply under voltage negative threshold           | 7.4  | 8.2  | 9    |       |                                                                        |

| V <sub>BSUVHY</sub> | V <sub>BS</sub> supply under voltage hysteresis                   |      | 0.7  | _    | V     |                                                                        |

| V <sub>CCUV+</sub>  | V <sub>CC</sub> supply under voltage positive threshold           | 8.0  | 8.9  | 9.8  | _ v   |                                                                        |

| V <sub>CCUV</sub> - | V <sub>CC</sub> supply under voltage negative threshold           | 7.4  | 8.2  | 9    |       |                                                                        |

| V <sub>CCUVHY</sub> | V <sub>CC</sub> supply under voltage hysteresis                   |      | 0.7  | _    |       |                                                                        |

| $I_{LK}$            | High-side floating well offset supply leakage                     |      |      | 50   |       | $V_B = V_S = 200 \text{ V}$                                            |

| $I_{QBS}$           | Quiescent V <sub>BS</sub> supply current                          |      | 45   | 75   | μΑ    | All inputs are in the off state                                        |

| I <sub>QCC</sub>    | Quiescent V <sub>CC</sub> supply current                          | _    | 300  | 520  |       |                                                                        |

| V <sub>OH</sub>     | High level output voltage drop, V <sub>BIAS</sub> -V <sub>O</sub> | _    | 0.05 | 0.2  | V     | I <sub>O</sub> = 2 mA                                                  |

| $V_{OL}$            | Low level output voltage drop, V <sub>O</sub>                     | _    | 0.02 | 0.1  | V     | -                                                                      |

| I <sub>o+</sub>     | Output high short circuit pulsed current                          | 200  | 290  | _    |       | $V_O = 0 \text{ V}, V_{IN} = V_{IH}$<br>PW \leq 10 \mus                |

| <sub>0-</sub>       | Output low short circuit pulsed current                           | 420  | 600  | _    | mA    | $V_O = 15 \text{ V},$ $V_{IN} = V_{IL}$ $PW \le 10  \mu\text{s}$       |

| V <sub>IH</sub>     | Logic "1" (HIN) & Logic "0" (LIN) input voltage                   | 2.5  |      |      | V     | \/ _10\/ 20\/                                                          |

| V <sub>IL</sub>     | Logic "0" (HIN) & Logic "1" (LIN) input voltage                   | _    | _    | 0.8  | V     | V <sub>CC</sub> =10 V - 20 V                                           |

| I <sub>IN+</sub>    | Logic "1" Input bias current                                      | _    | 3    | 10   |       | $\frac{\text{HIN} = 5 \text{ V}}{\overline{\text{LIN}} = 0 \text{ V}}$ |

| I <sub>IN-</sub>    | Logic "0" Input bias current                                      | _    | _    | 5    | μΑ    | HIN = 0 V<br>LIN = 5 V                                                 |

#### **Dynamic Electrical Characteristics**

$V_{CC} = V_B = 15V$ ,  $V_S = COM$ ,  $T_A = 25$ °C, and  $C_L = 1000 pF$  unless otherwise specified.

| Symbol           | Definition                                                        | Min. | Тур. | Max. | Units | Test Conditions                       |

|------------------|-------------------------------------------------------------------|------|------|------|-------|---------------------------------------|

| t <sub>ON</sub>  | Turn-on propagation delay                                         | _    | 160  | 220  |       |                                       |

| t <sub>OFF</sub> | Turn-off propagation delay                                        | _    | 150  | 220  |       |                                       |

| t <sub>R</sub>   | Turn-on rise time                                                 | _    | 70   | 170  |       |                                       |

| t <sub>F</sub>   | Turn-off fall time                                                | _    | 30   | 90   | ns    | $V_S = 0 \text{ V or } 200 \text{ V}$ |

| MT               | Delay matching time (t <sub>ON</sub> , t <sub>OFF</sub> )         | _    | _    | 50   | 110   |                                       |

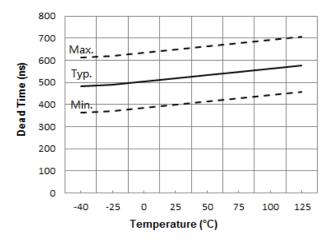

| DT               | Deadtime, LO turn-off to HO turn-on & HO turn-off to LO turn-on   | 400  | 520  | 650  |       |                                       |

| MDT              | Deadtime matching = I DT <sub>LO-HO</sub> – DT <sub>HO-LO</sub> I |      | _    | 30   |       |                                       |

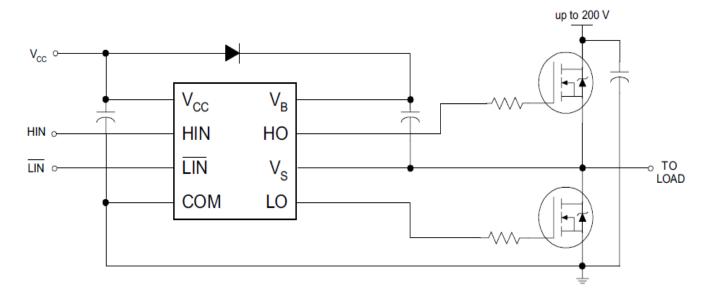

# **Functional Block Diagram**

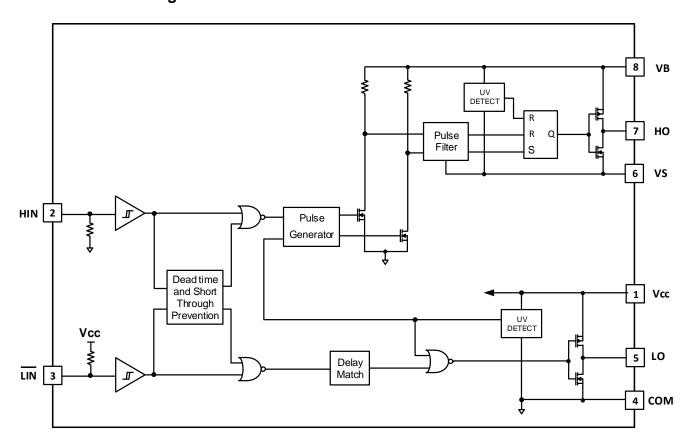

### **Lead Definitions**

| Symbol | Description                                                     |  |  |

|--------|-----------------------------------------------------------------|--|--|

| Vcc    | Low-side and logic supply voltage                               |  |  |

| VB     | High-side gate drive floating supply                            |  |  |

| VS     | High voltage floating supply return                             |  |  |

| HIN    | Logic inputs for high-side gate driver output (HO), in phase    |  |  |

| LIN    | Logic inputs for low-side gate driver output (LO), out of phase |  |  |

| НО     | High-side driver output                                         |  |  |

| LO     | Low-side driver output                                          |  |  |

| COM    | Low-side gate drive return                                      |  |  |

# **Lead Assignments**

# **Application Information and Additional Details**

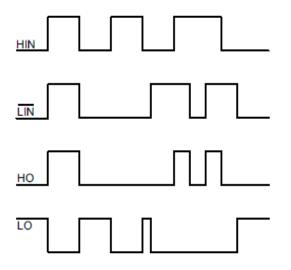

Figure 1. Input/Output Timing Diagram

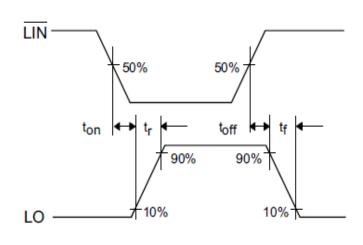

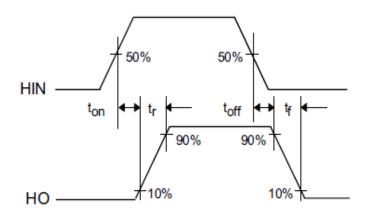

Figure 2. Switching Time Waveform Definitions

50% HIN LIN HO LO DTHO-LO 90%

Figure 3. Deadtime Waveform Definitions

MDT= | DTLO-HO-DTHO-LO |

www.infineon.com

Rev 1.0 2017-09-1

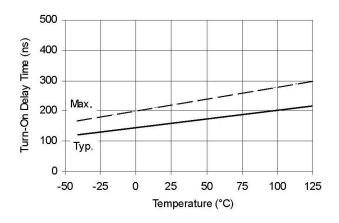

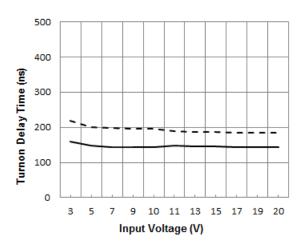

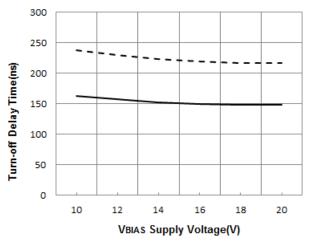

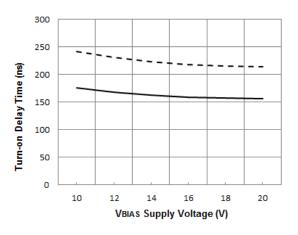

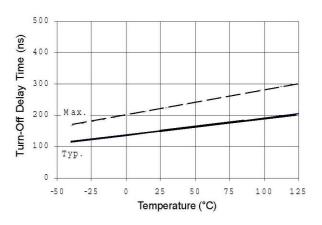

### Parameters trend with different temperature and voltage bias. (Fig. 4 ~ Fig. 20)

Figure 4A. Turn-On Time vs. Temperature

Figure 4C. Turn-On Time vs. Input Voltage

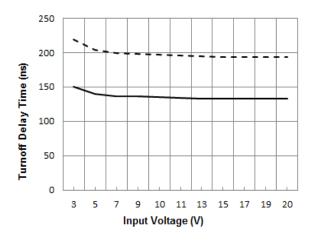

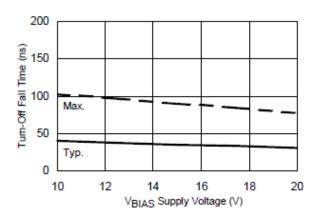

Figure 5B. Turn-Off Time vs. Supply Voltage

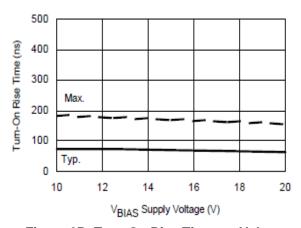

Figure 4B. Turn-On Time vs. Supply Voltage

Figure 5A. Turn-Off Time vs. Temperature

Figure 5C. Turn-Off Time vs. Input Voltage

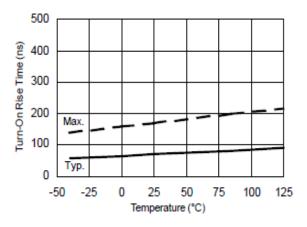

Figure 6A. Turn-On Rise Time vs. Temperature

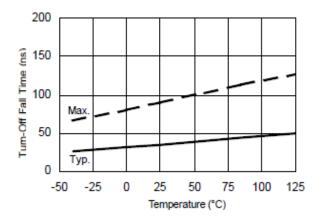

Figure 7A. Turn-Off Fall Time vs. Temperature

Figure 8A. Deadtime vs. Temperature

Figure 6B. Turn-On Rise Time vs. Voltage

Figure 7B. Turn-Off Fall Time vs. Voltage

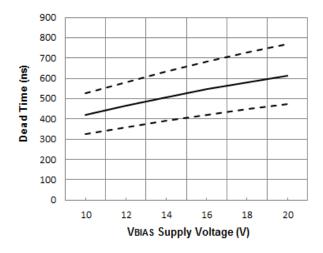

Figure 8A. Deadtime vs. Supply Voltage

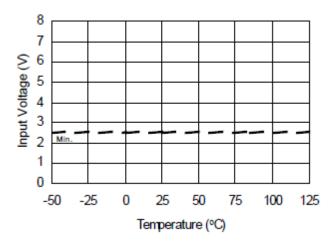

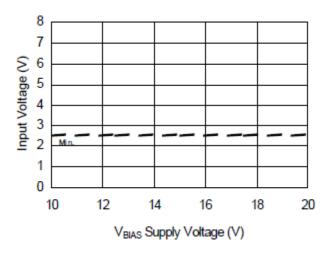

Figure 9A. Logic "1"(HIN) & Logic "0"(LIN) Input Voltage vs. Temperature

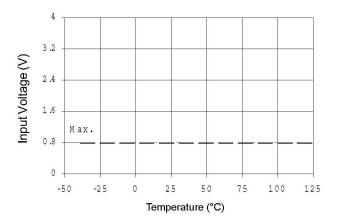

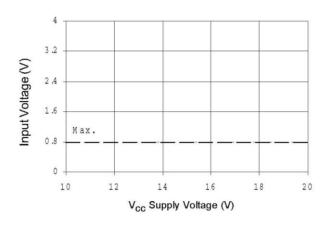

Figure 10A. Logic "0"(HIN) & Logic "1"(LIN) Input Voltage vs. Temperature

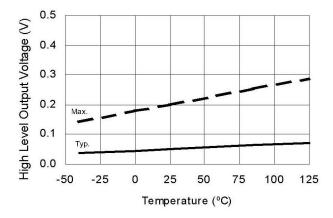

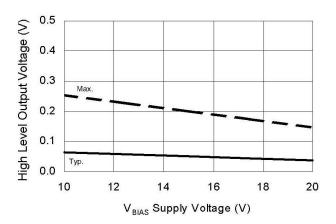

Figure 11A. High Level Output Voltage vs. Temperature

Figure 9B. Logic "1"(HIN) & Logic "0"(LIN) Input Voltage vs. Supply Voltage

Figure 10B. Logic "0"(HIN) & Logic "1"(LIN) Input Voltage vs. Supply Voltage

Figure 11B. High Level Output Voltage vs. Supply Voltage

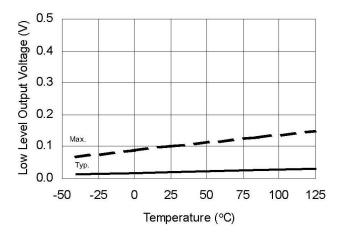

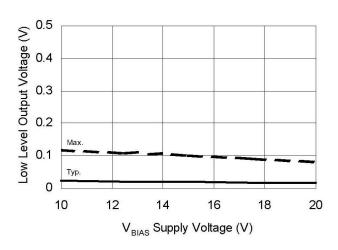

Figure 12A. Low Level Output Voltage vs. Temperature

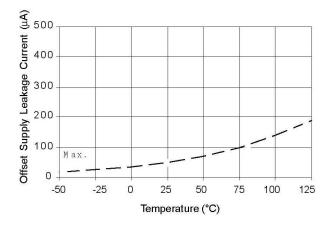

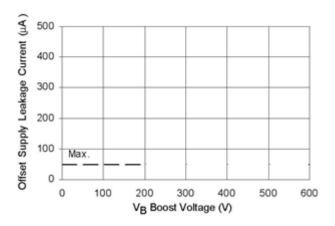

Figure 13A. Offset Supply Current vs. Temperature

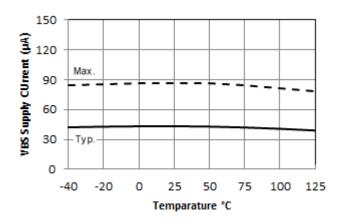

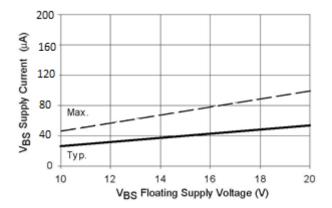

Figure 14A. V<sub>BS</sub> Supply Current vs. Temperature

Figure 12B. Low Level Output Voltage vs. Supply Voltage

Figure 13B. Offset Supply Current vs. Boost Voltage

Figure 14B. V<sub>BS</sub> Supply Current vs. Supply Voltage

Typ.

1000

Max.

Typ.

10 12 14 16 18 20

V<sub>CC</sub> Supply Voltage (V)

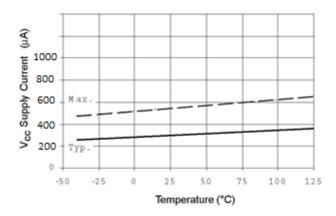

Figure 15A. V<sub>CC</sub> Supply Current vs. Temperature

Figure 15B. V<sub>CC</sub> Supply Current vs. Supply Voltage

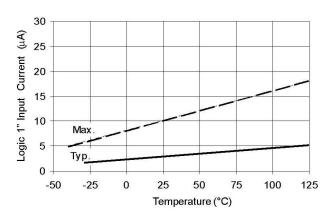

Figure 16A. Logic "1" Input Current vs. Temperature

Figure 16B. Logic "1" Input Current vs. Supply Voltage

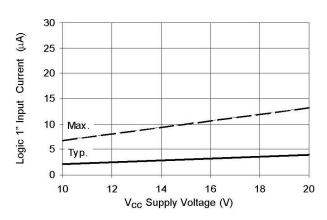

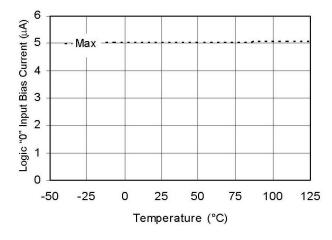

Figure 17A. Logic "0" Input Bias Current vs.

Temperature

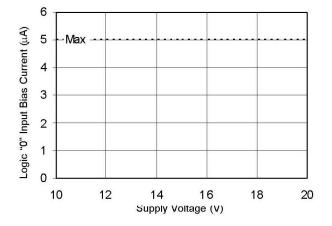

Figure 17B. Logic "0" Input Bias Current Supply Voltage

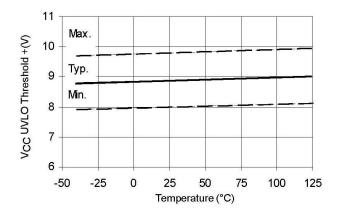

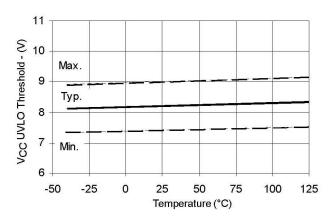

Figure 18A. V<sub>CC</sub>\V<sub>BS</sub> Under-voltage Threshold(+) vs. Temperature

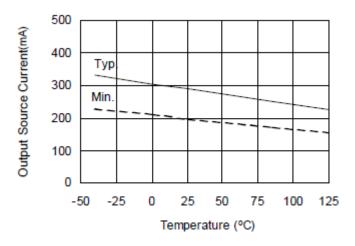

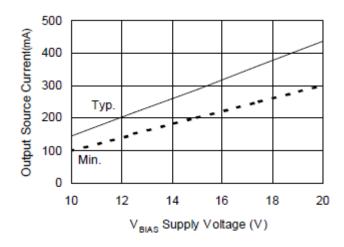

Figure 19A. Output Source Current vs. Temperature

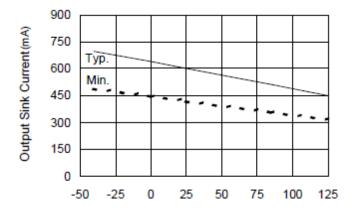

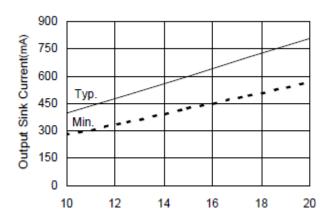

Figure 20A. Output Sink Current vs. Temperature

Figure 18B. V<sub>CC</sub>\V<sub>BS</sub> Under-voltage Threshold(-) vs. Temperature

Figure 19B. Output Source Current vs. Supply Voltage

Figure 20B. Output Sink Current vs. Supply Voltage

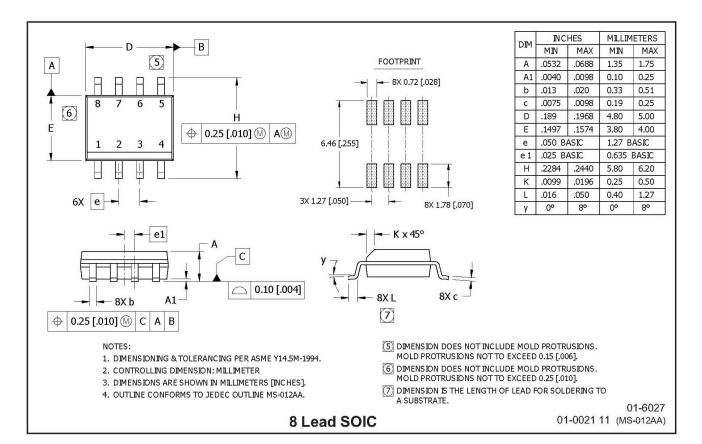

### Package Details: 8-Lead SOIC

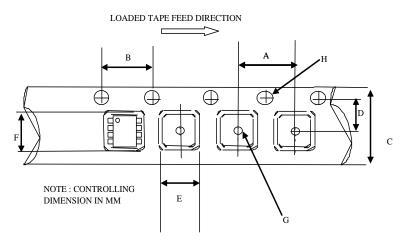

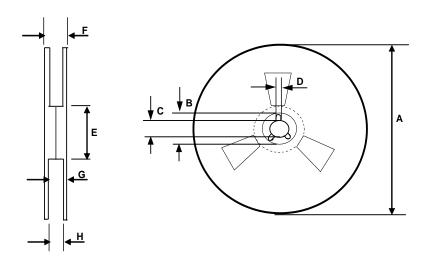

# **Tape and Reel Details: 8-Lead SOIC**

#### CARRIER TAPE DIMENSION FOR 8SOICN

|      | Metric |       | Imperial |       |

|------|--------|-------|----------|-------|

| Code | Min    | Max   | Min      | Max   |

| Α    | 7.90   | 8.10  | 0.311    | 0.318 |

| В    | 3.90   | 4.10  | 0.153    | 0.161 |

| С    | 11.70  | 12.30 | 0.46     | 0.484 |

| D    | 5.45   | 5.55  | 0.214    | 0.218 |

| E    | 6.30   | 6.50  | 0.248    | 0.255 |

| F    | 5.10   | 5.30  | 0.200    | 0.208 |

| G    | 1.50   | n/a   | 0.059    | n/a   |

| Н    | 1.50   | 1.60  | 0.059    | 0.062 |

REEL DIMENSIONS FOR 8SOICN

|      | Metric |        | Imperial |        |

|------|--------|--------|----------|--------|

| Code | Min    | Max    | Min      | Max    |

| Α    | 329.60 | 330.25 | 12.976   | 13.001 |

| В    | 20.95  | 21.45  | 0.824    | 0.844  |

| С    | 12.80  | 13.20  | 0.503    | 0.519  |

| D    | 1.95   | 2.45   | 0.767    | 0.096  |

| E    | 98.00  | 102.00 | 3.858    | 4.015  |

| F    | n/a    | 18.40  | n/a      | 0.724  |

| G    | 14.50  | 17.10  | 0.570    | 0.673  |

| Н    | 12.40  | 14.40  | 0.488    | 0.566  |

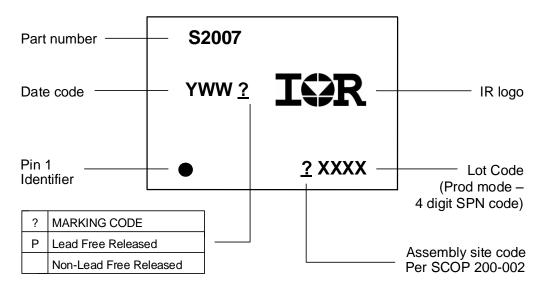

# **Part Marking Information**

8-Lead SOIC8 IRS2007SPBF

### **Qualification Information**<sup>†</sup>

| Qualification Level |                                     | Industrial <sup>††</sup>                                                                                                                                       |                                                  |  |  |

|---------------------|-------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------|--|--|

|                     |                                     | Comments: This family of ICs has passed JEDEC's Industrial qualification. Consumer qualification level is granted by extension of the higher Industrial level. |                                                  |  |  |

| Moisture Sensitivit | y Level                             | 8 Lead SOIC MSL2 <sup>†††</sup> , 260°C (per IPC/JEDEC J-STD-0                                                                                                 |                                                  |  |  |

| ESD                 | ESD Human Body Model  Machine Model |                                                                                                                                                                | Class 2<br>(per JEDEC standard JESD22-A114)      |  |  |

| 230                 |                                     |                                                                                                                                                                | Class A (per EIA/JEDEC standard EIA/JESD22-A115) |  |  |

| IC Latch-Up Test    |                                     | Class I                                                                                                                                                        |                                                  |  |  |

| To Lateri-op Test   |                                     | (per JESD78)                                                                                                                                                   |                                                  |  |  |

| RoHS Compliant      |                                     | Yes                                                                                                                                                            |                                                  |  |  |

- † Higher qualification ratings may be available should the user have such requirements. Please contact your Infineon sales representative for further information.

- †† Higher MSL ratings may be available for the specific package types listed here. Please contact your Infineon sales representative for further information.

Published by Infineon Technologies AG 81726 München, Germany © Infineon Technologies AG 2017 All Rights Reserved.

#### IMPORTANT NOTICE

The information given in this document shall in <u>no event</u> be regarded as a guarantee of conditions or characteristics ("Beschaffenheitsgarantie"). With respect to any examples, hints or any typical values stated herein and/or any information regarding the application of the product, Infineon Technologies hereby disclaims any and all warranties and liabilities of any kind, including without limitation warranties of non-infringement of intellectual property rights of any third party.

In addition, any information given in this document is subject to customer's compliance with its obligations stated in this document and any applicable legal requirements, norms and standards concerning customer's products and any use of the product of Infineon Technologies in customer's applications.

The data contained in this document is exclusively intended for technically trained staff. It is the responsibility of customer's technical departments to evaluate the suitability of the product for the intended application and the completeness of the product information given in this document with respect to such application.

For further information on the product, technology, delivery terms and conditions and prices please contact your nearest Infineon Technologies office (<a href="www.infineon.com">www.infineon.com</a>).

#### **WARNINGS**

Due to technical requirements products may contain dangerous substances. For information on the types in question please contact your nearest Infineon Technologies office.

Except as otherwise explicitly approved by Infineon Technologies in a written document signed by authorized representatives of Infineon Technologies, Infineon Technologies' products may <u>not</u> be used in any applications where a failure of the product or any consequences of the use thereof can reasonably be expected to result in personal injury.